Analog Devices AD7710 g Datasheet

a

Signal Conditioning ADC

FEATURES

Charge Balancing ADC

24 Bits, No Missing Codes

ⴞ0.0015% Nonlinearity

2-Channel Programmable Gain Front End

Gains from 1 to 128

Differential Inputs

Low-Pass Filter with Programmable Filter Cutoffs

Ability to Read/Write Calibration Coefficients

Bidirectional Microcontroller Serial Interface

Internal/External Reference Option

Single- or Dual-Supply Operation

Low Power (25 mW Typ) with Power-Down Mode

(7 mW Typ)

APPLICATIONS

Weigh Scales

Thermocouples

Process Control

Smart Transmitters

Chromatography

GENERAL DESCRIPTION

The AD7710 is a complete analog front end for low frequency

measurement applications. The device accepts low level signals

directly from a strain gage or transducer and outputs a serial

digital word. It employs a sigma-delta conversion technique to

realize up to 24 bits of no missing codes performance. The input

signal is applied to a proprietary programmable gain front end

based around an analog modulator. The modulator output is

processed by an on-chip digital filter. The first notch of this

digital filter can be programmed via the on-chip control register,

allowing adjustment of the filter cutoff and settling time.

The part features two differential analog inputs and a differential reference input. Typically, one of the channels will be used

as the main channel with the second channel used as an auxiliary input to measure a second voltage periodically. It can be

operated from a single supply (by tying the V

pin to AGND),

SS

provided that the input signals on the analog inputs are more

positive than –30 mV. By taking the V

can convert signals down to –V

REF

pin negative, the part

SS

on its inputs. The AD7710

thus performs all signal conditioning and conversion for a singleor dual-channel system.

The AD7710 is ideal for use in smart, microcontroller based

systems. Input channel selection, gain settings, and signal polarity can be configured in software using the bidirectional serial

port. The AD7710 contains self-calibration, system calibration,

and background calibration options, and also allows the user to

read and write the on-chip calibration registers.

*Protected by U.S. Patent No. 5,134,401.

REV. G

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

AD7710

*

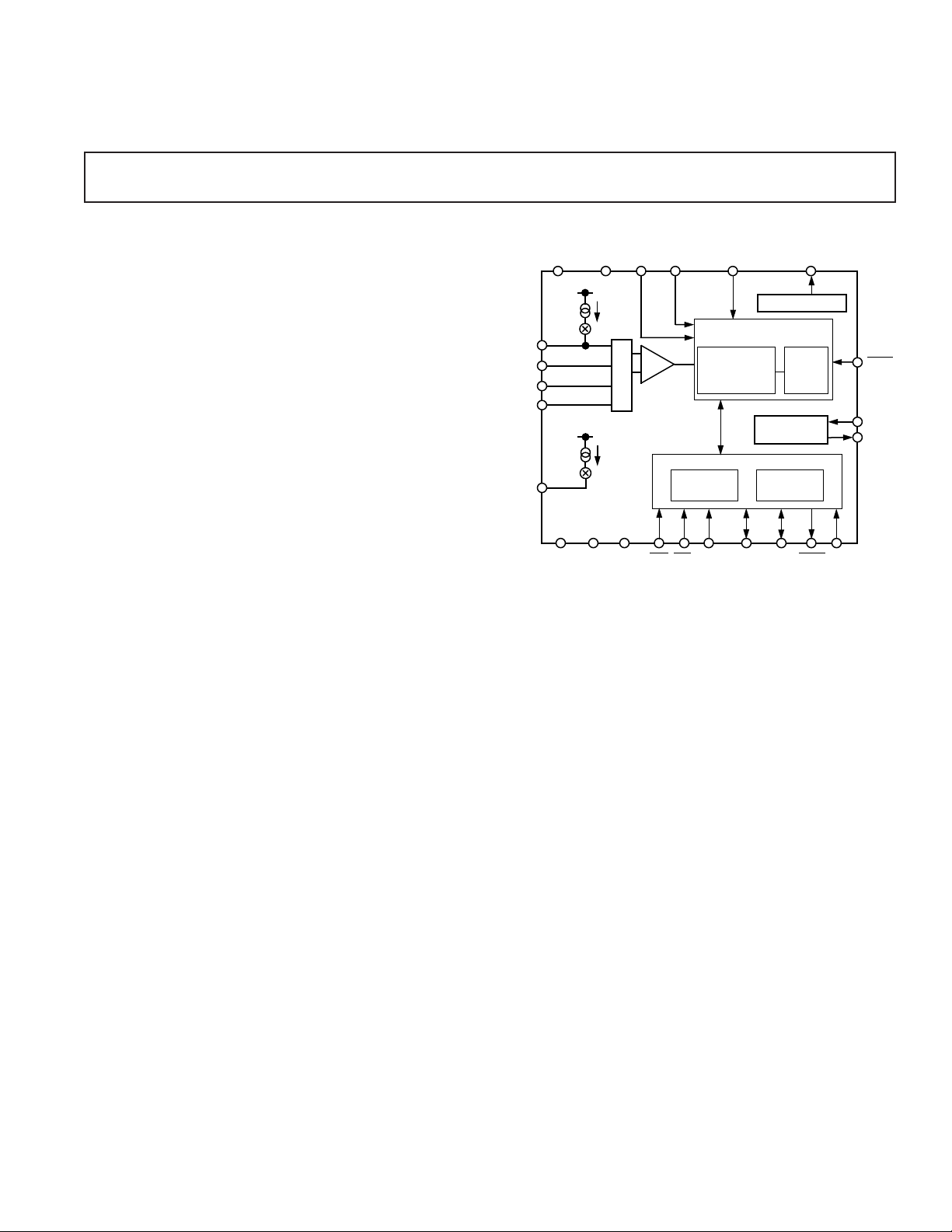

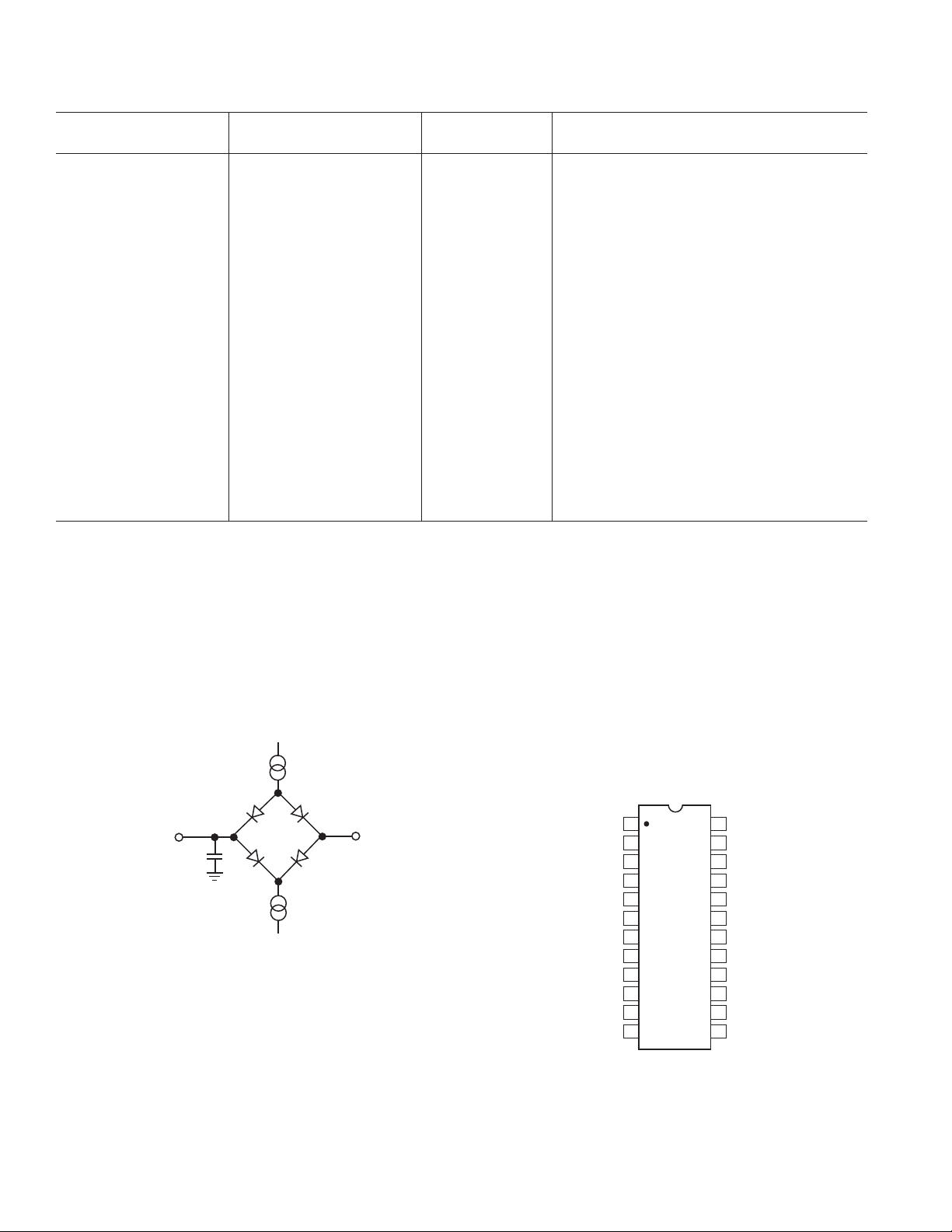

FUNCTIONAL BLOCK DIAGRAM

REF

AV

AIN1(+)

AIN1(–)

AIN2(+)

AIN2(–)

I

OUT

AGND DGND MODE SDATA SCLK A0

DD

AV

AV

AD7710

DV

DD

DD

4.5A

M

U

X

DD

20A

V

IN (–)

A = 1 – 128

SS

PGA

REF

IN (+)

V

BIAS

CHARGE-BALANCING A/D

CONVERTER

AUTO-ZEROED

⌺-⌬

MODULATOR

SERIAL INTERFACE

CONTROL

REGISTER

TFSRFS

REF OUT

2.5V REFERENCE

DIGITAL

FILTER

CLOCK

GENERATION

OUTPUT

REGISTER

DRDY

SYNC

MCLK

IN

MCLK

OUT

CMOS construction ensures low power dissipation, and a software programmable power-down mode reduces the standby

power consumption to only 7 mW typical. The part is available

in a 24-lead, 0.3 inch-wide, plastic and hermetic dual-in-line

package (DIP) as well as a 24-lead small outline (SOIC) package.

PRODUCT HIGHLIGHTS

1. The programmable gain front end allows the AD7710 to

accept input signals directly from a strain gage or transducer,

removing a considerable amount of signal conditioning.

2. The AD7710 is ideal for microcontroller or DSP processor

applications with an on-chip control register that allows

control over filter cutoff, input gain, channel selection, signal

polarity, and calibration modes.

3. The AD7710 allows the user to read and write the on-chip

calibration registers. This means that the microcontroller has

much greater control over the calibration procedure.

4. No missing codes ensures true, usable, 23-bit dynamic range

coupled with excellent ±0.0015% accuracy. The effects of

temperature drift are eliminated by on-chip self-calibration,

which removes zero-scale and full-scale errors.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

AD7710–SPECIFICATIONS

REF IN(–) = AGND; MCLK IN = 10 MHz unless otherwise noted. All specifications T

(AVDD = +5 V ⴞ 5%; DVDD = +5 V ⴞ 5%; VSS = 0 V or –5 V ⴞ 5%; REF IN(+) = +2.5 V;

to T

MIN

, unless otherwise noted.)

MAX

Parameter A, S Versions1Unit Conditions/Comments

STATIC PERFORMANCE

No Missing Codes 24 Bits min Guaranteed by Design. For Filter Notches ≤ 60 Hz

22 Bits min For Filter Notch = 100 Hz

18 Bits min For Filter Notch = 250 Hz

15 Bits min For Filter Notch = 500 Hz

12 Bits min For Filter Notch = 1 kHz

Output Noise Tables I and II Depends on Filter Cutoffs and Selected Gain

Integral Nonlinearity @ +25°C ±0.0015 % of FSR max Filter Notches ≤ 60 Hz

T

to T

MIN

Positive Full-Scale Error2,

Full-Scale Drift

Unipolar Offset Error

Unipolar Offset Drift

Bipolar Zero Error

Bipolar Zero Drift

MAX

5

2

5

2

5

3

±0.003 % of FSR max Typically ± 0.0003%

See Note 4 Excluding Reference

1 µV/°C typ Excluding Reference. For Gains of 1, 2

0.3 µV/°C typ Excluding Reference. For Gains of 4, 8, 16, 32, 64, 128

See Note 4

0.5 µV/°C typ For Gains of 1, 2

0.25 µV/°C typ For Gains of 4, 8, 16, 32, 64, 128

See Note 4

0.5 µV/°C typ For Gains of 1, 2

0.25 µV/°C typ For Gains of 4, 8, 16, 32, 64, 128

Gain Drift 2 ppm/°C typ

Bipolar Negative Full-Scale Error

T

to T

MIN

MAX

Bipolar Negative Full-Scale Drift

2

@ 25°C ±0.003 % of FSR max Excluding Reference

5

±0.006 % of FSR max Typically ± 0.0006%

1 µV/°C typ Excluding Reference. For Gains of 1, 2

0.3 µV/°C typ Excluding Reference. For Gains of 4, 8, 16, 32, 64, 128

ANALOG INPUTS/REFERENCE INPUTS

Input Common-Mode Rejection (CMR) 100 dB min At DC and AV

Common-Mode Voltage Range

Normal-Mode 50 Hz Rejection

Normal-Mode 60 Hz Rejection

Common-Mode 50 Hz Rejection

Common-Mode 60 Hz Rejection

6

7

7

7

7

90 dB min At DC and AV

VSS to AV

DD

V min to V max

100 dB min For Filter Notches of 10, 25, 50 Hz, ± 0.02 × f

100 dB min For Filter Notches of 10, 30, 60 Hz, ± 0.02 × f

150 dB min For Filter Notches of 10, 25, 50 Hz, ± 0.02 × f

150 dB min For Filter Notches of 10, 30, 60 Hz, ± 0.02 × f

= 5 V

DD

= 10 V

DD

NOTCH

NOTCH

NOTCH

NOTCH

DC Input Leakage Current7 @ 25°C10 pA max

T

to T

MIN

Sampling Capacitance

Analog Inputs

Input Voltage Range

Input Sampling Rate, f

Reference Inputs

REF IN(+) – REF IN(–) Voltage

Input Sampling Rate, f

NOTES

1

Temperature ranges are as follows: A Version, –40°C to +85°C; S Version, –55°C to +125°C. See also Note 16.

2

Applies after calibration at the temperature of interest.

3

Positive full-scale error applies to both unipolar and bipolar input ranges.

4

These errors will be of the order of the output noise of the part as shown in Table I after system calibration. These errors will be 20 µV typical after self-calibration

or background calibration.

5

Recalibration at any temperature or use of the background calibration mode will remove these drift errors.

6

This common-mode voltage range is allowed, provided that the input voltage on AIN(+) and AIN(–) does not exceed AV

7

These numbers are guaranteed by design and/or characterization.

8

The analog inputs present a very high impedance dynamic load that varies with clock frequency and input sample rate. The maximum recommended source

resistance depends on the selected gain (see Tables IV and V).

9

The analog input voltage range on the AIN1(+) and AIN2(+) inputs is given here with respect to the voltage on the AIN1(–) and AIN2(–) inputs. The absolute

voltage on the analog inputs should not go more positive than AVDD + 30 mV or go more negative than VSS – 30 mV.

10

V

= REF IN(+) – REF IN(–).

REF

11

The reference input voltage range may be restricted by the input voltage range requirement on the V

MAX

8

7

9

S

11

S

1 nA max

20 pF max

For Normal Operation. Depends on Gain Selected

0 to +V

±V

REF

REF

10

nom Unipolar Input Range (B/U Bit of Control Register = 1)

nom Bipolar Input Range (B/U Bit of Control Register = 0)

See Table III

2.5 to 5 V min to V max For Specified Performance. Part Is Functional with

f

CLK IN

Lower V

/256

BIAS

input.

Voltages

REF

+ 30 mV and VSS – 30 mV.

DD

REV. G–2–

AD7710

Parameter A, S Versions

1

Unit Conditions/Comments

REFERENCE OUTPUT

Output Voltage 2.5 V nom

Initial Tolerance @ 25°C ±1% max

Drift 20 ppm/°C typ

Output Noise 30 µV typ Peak-peak Noise 0.1 Hz to 10 Hz Bandwidth

Line Regulation (AV

)1 mV/V max

DD

Load Regulation 1.5 mV/mA max Maximum Load Current 1 mA

External Current 1 mA max

INPUT

V

BIAS

Input Voltage Range AVDD – 0.85 × V

V

BIAS

12

or AV

– 3.5 V max Whichever Is Smaller: +5 V/–5 V or +10 V/0 V

DD

REF

See V

Nominal AV

Input Section

BIAS

DD/VSS

or AVDD – 2.1 V max Whichever Is Smaller; +5 V/0 V Nominal AVDD/V

VSS + 0.85 × V

or V

+ 3 V min Whichever Is Greater; +5 V/–5 V or +10 V/0 V

SS

REF

See V

Input Section

BIAS

Nominal AV

DD/VSS

or VSS + 2.1 V min Whichever Is Greater; +5 V/0 V Nominal AVDD/V

Rejection 65 to 85 dB typ Increasing with Gain

SS

SS

LOGIC INPUTS

Input Current ±10 µΑ max

All Inputs Except MCLK IN

V

, Input Low Voltage 0.8 V max

INL

, Input High Voltage 2.0 V min

V

INH

MCLK IN Only

V

, Input Low Voltage 0.8 V max

INL

V

, Input High Voltage 3.5 V min

INH

LOGIC OUTPUTS

V

, Output Low Voltage 0.4 V max I

OL

V

, Output High Voltage DVDD – 1 V min I

OH

= 1.6 mA

SINK

SOURCE

= 100 µA

Floating State Leakage Current ±10 µA max

Floating State Output Capacitance139 pF typ

TRANSDUCER BURNOUT

Current 4.5 µA nom

Initial Tolerance @ 25°C ±10 % typ

Drift 0.1 %/°C typ

COMPENSATION CURRENT

Output Current 20 µA nom

Initial Tolerance @ 25°C ±4 µA max

Drift 35 ppm/°C typ

Line Regulation (AV

)20 nA/V max AVDD = +5 V

DD

Load Regulation 20 nA/V max

Output Compliance AVDD – 2 V max

SYSTEM CALIBRATION

Positive Full-Scale Calibration Limit

Negative Full-Scale Calibration Limit

Offset Calibration Limits

Input Span

NOTES

12

The AD7710 is tested with the following V

AVDD = 5 V and VSS = –5 V, V

13

Guaranteed by design, not production tested.

14

After calibration, if the analog input exceeds positive full scale, the converter will output all 1s. If the analog input is less than negative full scale then the device will

output all 0s.

15

These calibration and span limits apply, provided the absolute voltage on the analog inputs does not exceed AVDD + 30 mV or go more negative than VSS – 30 mV.

The offset calibration limit applies to both the unipolar zero point and the bipolar zero point.

15

15

BIAS

= 0 V.

l4

(1.05 × V

l4

–(1.05 × V

–(1.05 × V

0.8 × V

(2.1 × V

voltages. With AVDD = 5 V and VSS = 0 V, V

BIAS

)/GAIN V max GAIN Is the Selected PGA Gain (Between 1 and 128)

REF

)/GAIN V max GAIN Is the Selected PGA Gain (Between 1 and 128)

REF

)/GAIN V max GAIN Is the Selected PGA Gain (Between 1 and 128)

REF

/GAIN V min GAIN Is the Selected PGA Gain (Between 1 and 128)

REF

)/GAIN V max GAIN Is the Selected PGA Gain (Between 1 and 128)

REF

= 2.5 V; with AVDD = 10 V and VSS = 0 V, V

BIAS

= 5 V; and with

BIAS

REV. G

–3–

AD7710–SPECIFICATIONS

Parameter A, S VersionslUnit Conditions/Comments

POWER REQUIREMENTS

Power Supply Voltages

AV

Voltage

DD

DV

DD

AV

DD-VSS

Power Supply Currents

AVDD Current 4 mA max

DV

DD

V

Current 1.5 mA max VSS = –5 V

SS

Power Supply Rejection

Positive Supply (AV

Negative Supply (V

Power Dissipation

Normal Mode 45 mW max AV

Standby (Power-Down) Mode 15 mW max AVDD = DVDD = 5 V, VSS = 0 V or –5 V; Typically 7 mW

NOTES

16

The AD7710 is specified with a 10 MHz clock for AVDD voltages of +5 V ± 5%. It is specified with an 8 MHz clock for AVDD voltages greater than 5.25 V and less

than 10.5 V. Operating with AVDD voltages in the range 5.25 V to 10.5 V is only guaranteed over the 0 °C to 70°C temperature range.

17

The ± 5% tolerance on the DVDD input is allowed provided that DVDD does not exceed AVDD by more than 0.3 V.

18

Measured at dc and applies in the selected passband. PSRR at 50 Hz will exceed 120 dB with filter notches of 10 Hz, 25 Hz, or 50 Hz. PSRR at 60 Hz will exceed

120 dB with filter notches of 10 Hz, 30 Hz or 60 Hz.

19

PSRR depends on gain: Gain of 1: 70 dB typ; Gain of 2: 75 dB typ; Gain of 4: 80 dB typ; Gains of 8 to 128: 85 dB typ. These numbers can be improved (to 95 dB

typ) by deriving the V

Specifications subject to change without notice.

Voltage

16

17

5 to 10 V nom ±5% for Specified Performance

5V nom ±5% for Specified Performance

Voltage 10.5 V max For Specified Performance

Current 4.5 mA max

18

and DVDD) See Note 19 dB typ

DD

)90 dB typ

SS

52.5 mW max AV

voltage (via Zener diode or reference) from the AVDD supply.

BIAS

Rejection w.r.t. AGND; Assumes V

= DVDD = 5 V, VSS = 0 V; Typically 25 mW

DD

= DVDD = 5 V, VSS = –5 V; Typically 30 mW

DD

BIAS

Is Fixed

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C, unless otherwise noted.)

AVDD to DVDD . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +12 V

to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +12 V

AV

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +12 V

AV

DD

to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +12 V

AV

DD

DV

to AGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

DD

to DGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

DV

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –6 V

V

SS

V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –6 V

SS

Analog Input Voltage to AGND

. . . . . . . . . . . . . . . . . . . . . . . . . V

– 0.3 V to AVDD + 0.3 V

SS

Reference Input Voltage to AGND

. . . . . . . . . . . . . . . . . . . . . . . . . V

– 0.3 V to AVDD + 0.3 V

SS

REF OUT to AGND . . . . . . . . . . . . . . . . . . . . –0.3 V to AV

Digital Input Voltage to DGND . . . . . –0.3 V to AVDD + 0.3 V

Digital Output Voltage to DGND . . . . –0.3 V to DV

Operating Temperature Range

Commercial (A Version) . . . . . . . . . . . . . . . –40°C to +85°C

Extended (S Version) . . . . . . . . . . . . . . . . . –55°C to +125°C

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . . . 300°C

Power Dissipation (Any Package) to +75°C . . . . . . . . 450 mW

Derates Above +75°C . . . . . . . . . . . . . . . . . . . . . . . . 6 mW/°C

*Stresses above those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those listed in the operational

DD

sections of the specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7710 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

+ 0.3 V

DD

ESD SENSITIVE DEVICE

–4–

REV. G

TIMING CHARACTERISTICS1,

AD7710

(DVDD = +5 V ⴞ 5%; AVDD = +5 V or +10 V3 ⴞ 5%; VSS = 0 V or –5 V ⴞ 10%; AGND = DGND =

2

0 V; f

=10 MHz; Input Logic 0 = 0 V, Logic 1 = DVDD, unless otherwise noted.)

CLK IN

Limit at T

MIN

, T

MAX

Parameter (A, S Versions) Unit Conditions/Comments

4, 5

f

CLK IN

Master Clock Frequency: Crystal Oscillator or Externally

400 kHz min Supplied for Specified Performance

= +5 V ± 5%

DD

= +5.25 V to +10.5 V

DD

CLK IN

= 1/f

CLK IN

t

CLK IN LO

t

CLK IN HI

6

t

r

6

t

f

t

1

10 MHz max AV

8 MHz max AV

0.4 × t

0.4 × t

CLK IN

CLK IN

ns min Master Clock Input Low Time. t

ns min Master Clock Input High Time

50 ns max Digital Output Rise Time. Typically 20 ns

50 ns max Digital Output Fall Time. Typically 20 ns

1000 ns min SYNC Pulse Width

Self-Clocking Mode

t

2

t

3

t

4

t

5

t

6

7

t

7

7

t

8

t

9

t

10

t

14

t

15

t

16

t

17

t

18

t

19

NOTES

1

Guaranteed by design, not production tested. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

See Figures 10 to 13.

3

The AD7710 is specified with a 10 MHz clock for AVDD voltages of 5 V ± 5%. It is specified with an 8 MHz clock for AVDD voltages greater than 5.25 V and less

than 10.5 V.

4

CLK IN duty cycle range is 45% to 55%. CLK IN must be supplied whenever the AD7710 is not in STANDBY mode. If no clock is present in this case, the device

can draw higher current than specified and possibly become uncalibrated.

5

The AD7710 is production tested with f

6

Specified using 10% and 90% points on waveform of interest.

7

These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

0 ns min DRDY to RFS Setup Time

0 ns min DRDY to RFS Hold Time

2 × t

CLK IN

ns min A0 to RFS Setup Time

0 ns min A0 to RFS Hold Time

4 × t

4 × t

t

CLK IN

t

CLK IN

t

CLK IN

3 × t

+ 20 ns max RFS Low to SCLK Falling Edge

CLK IN

+ 20 ns max Data Access Time (RFS Low to Data Valid)

CLK IN

/2 ns min SCLK Falling Edge to Data Valid Delay

/2 + 30 ns max

/2 ns nom SCLK High Pulse Width

/2 ns nom SCLK Low Pulse Width

CLK IN

50 ns min A0 to TFS Setup Time

0 ns min A0 to TFS Hold Time

4 × t

4 × t

+ 20 ns max TFS to SCLK Falling Edge Delay Time

CLK IN

CLK IN

ns min TFS to SCLK Falling Edge Hold Time

0 ns min Data Valid to SCLK Setup Time

10 ns min Data Valid to SCLK Hold Time

at 10 MHz (8 MHz for AVDD > 5.25 V). It is guaranteed by characterization to operate at 400 kHz.

CLK IN

REV. G

ORDERING GUIDE

Temperature Package

Range Options

2

Model

1

AD7710AN –40°C to +85°C N-24

AD7710AR –40°C to +85°C R-24

AD7710AR-REEL –40°C to +85°C R-24

AD7710AR-REEL7 –40°C to +85°C R-24

AD7710ARZ

AD7710ARZ-REEL

AD7710ARZ-REEL7

3

–40°C to +85°C R-24

3

–40°C to +85°C R-24

3

–40°C to +85°C R-24

AD7710AQ –40°C to +85°C Q-24

AD7710SQ –55°C to +125°C Q-24

EVAL-AD7710EB Evaluation Board

NOTES

1

Contact your local sales office for military data sheet and availability.

2

N = PDIP; Q = CERDIP; R = SOIC.

3

Z = Pb-free part.

–5–

AD7710

Limit at T

MIN

, T

MAX

Parameter (A, S Versions) Unit Conditions/Comments

External Clocking Mode

f

SCLK

t

20

t

21

t

22

t

23

7

t

24

7

t

25

t

26

t

27

t

28

8

t

29

t

30

8

t

31

t

32

t

33

t

34

t

35

t

36

NOTES

8

These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then

extrapolated back to remove effects of charging or discharging the 100 pF capacitor. This means that the times quoted in the timing characteristics are the true bus

relinquish times of the part and, as such, are independent of external bus loading capacitances.

Specifications subject to change without notice.

f

/5 MHz max Serial Clock Input Frequency

CLK IN

0 ns min DRDY to RFS Setup Time

0 ns min DRDY to RFS Hold Time

2 × t

CLK IN

ns min A0 to RFS Setup Time

0 ns min A0 to RFS Hold Time

4 × t

CLK IN

ns max Data Access Time (RFS Low to Data Valid)

10 ns min SCLK Falling Edge to Data Valid Delay

2 × t

2 × t

2 × t

t

CLK IN

+ 20 ns max

CLK IN

CLK IN

CLK IN

ns min SCLK High Pulse Width

ns min SCLK Low Pulse Width

+ 10 ns max SCLK Falling Edge to DRDY High

10 ns min SCLK to Data Valid Hold Time

+ 10 ns max

t

CLK IN

10 ns min RFS/TFS to SCLK Falling Edge Hold Time

5 × t

/2 + 50 ns max RFS to Data Valid Hold Time

CLK IN

0 ns min A0 to TFS Setup Time

0 ns min A0 to TFS Hold Time

4 × t

2 × t

CLK IN

– SCLK High ns min Data Valid to SCLK Setup Time

CLK IN

ns min SCLK Falling Edge to TFS Hold Time

30 ns min Data Valid to SCLK Hold Time

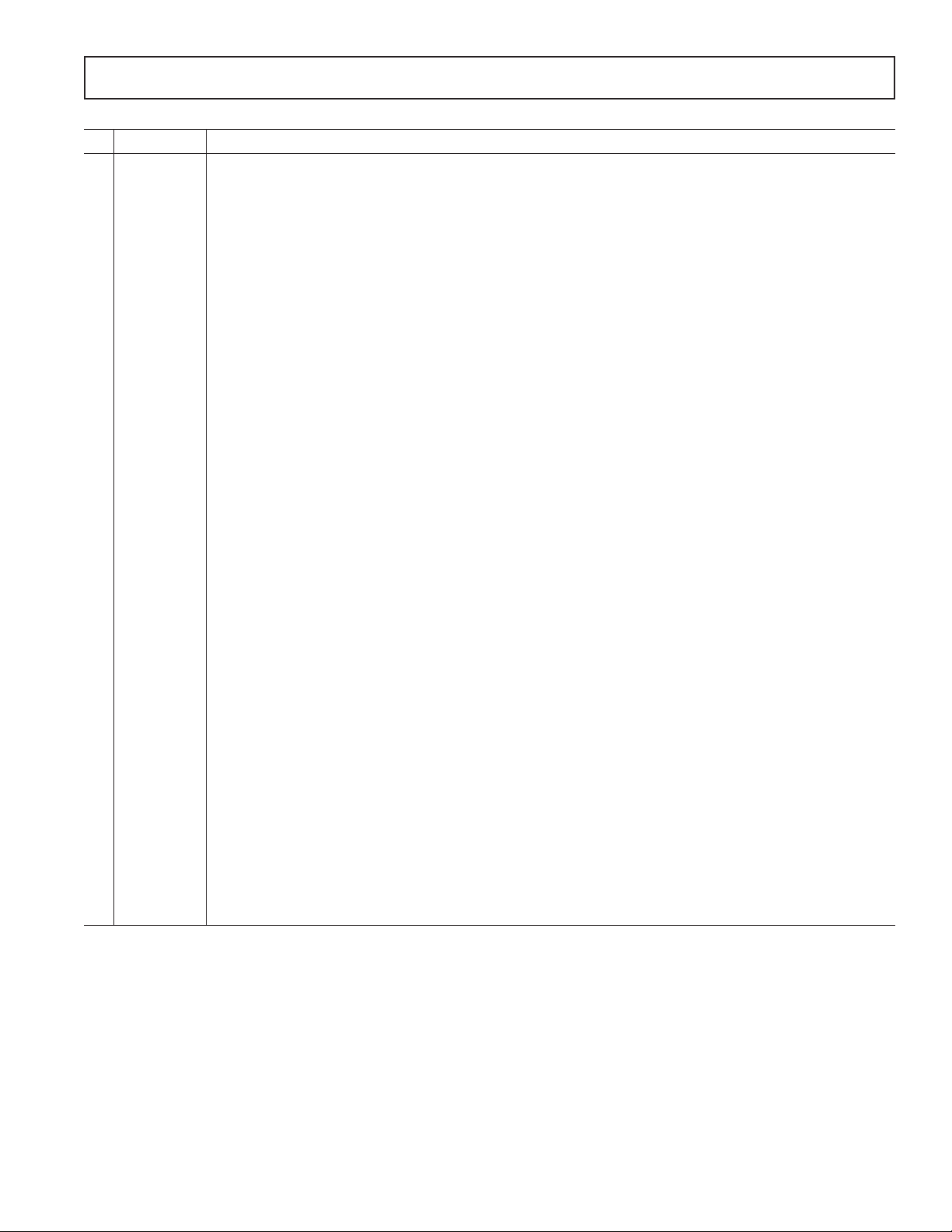

1.6mA

TO OUTPUT

PIN

100pF

200A

+2.1V

Figure 1. Load Circuit for Access Time and

Bus Relinquish Time

–6–

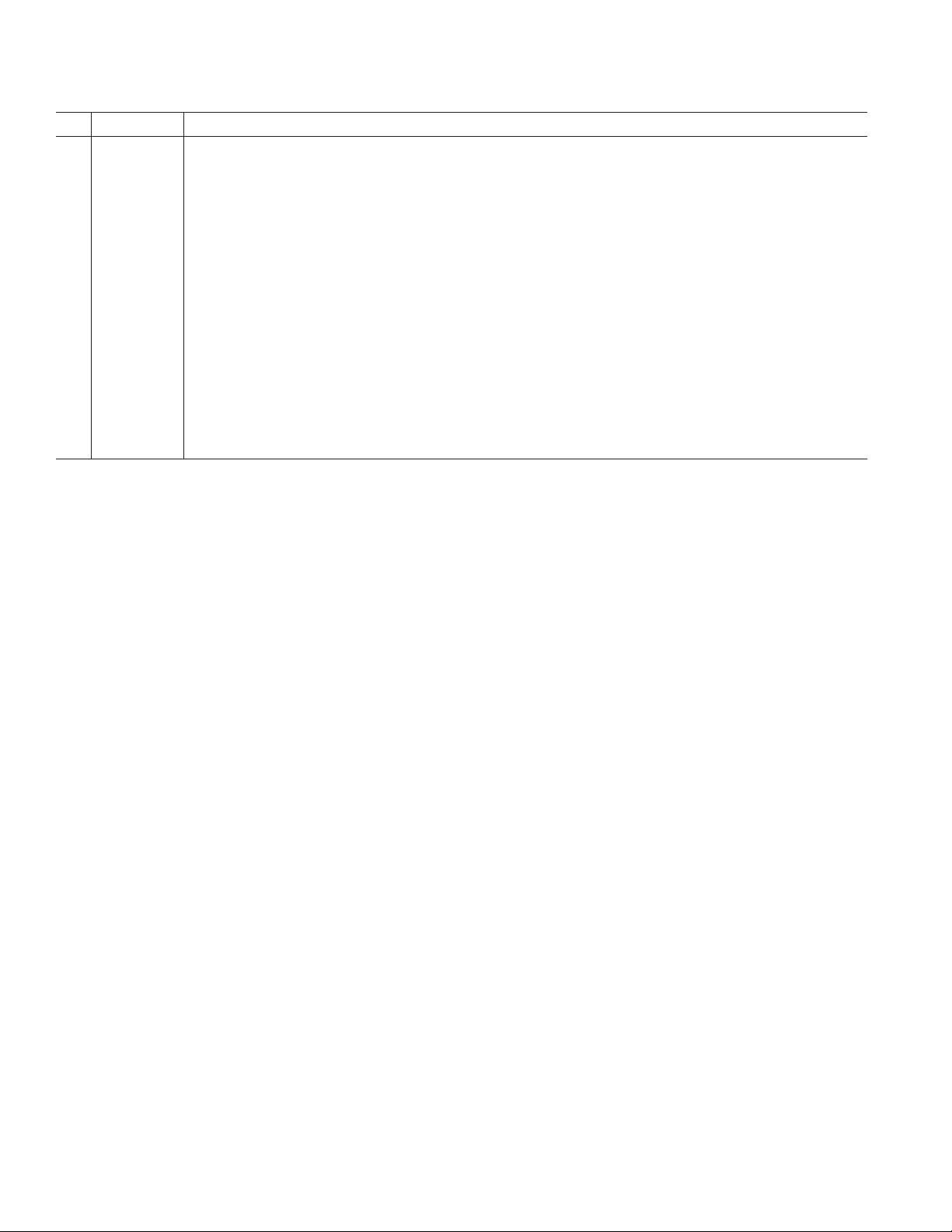

PIN CONFIGURATION

DIP AND SOIC

1

SCLK

MCLK IN

MCLK OUT

2

3

4

A0

AD7710

5

SYNC

6

MODE

AIN1(+) AGND

AIN1(–)

AIN2(+)

AIN2(–)

V

AV

SS

DD

TOP VIEW

7

(Not to Scale)

8

9

10

11

11

12

24

23

22

21

20

19

18

17

16

15

14

13

DGND

DV

DD

SDATA

DRDY

RFS

TFS

I

OUT

REF OUT

REF IN(+)

REF IN(–)

V

BIAS

REV. G

AD7710

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1 SCLK Serial Clock. Logic input/output, depending on the status of the MODE pin. When MODE is high, the

device is in its self-clocking mode, and the SCLK pin provides a serial clock output. This SCLK becomes

active when RFS or TFS goes low, and it goes high impedance when either RFS or TFS returns high or when

the device has completed transmission of an output word. When MODE is low, the device is in its external

clocking mode, and the SCLK pin acts as an input. This input serial clock can be a continuous clock with all

data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the

information being transmitted to the AD7710 in smaller batches of data.

2 MCLK IN Master Clock Signal for the Device. This can be provided in the form of a crystal or external clock. A crystal

can be tied across the MCLK IN and MCLK OUT pins. Alternatively, the MCLK IN pin can be driven with

a CMOS compatible clock and MCLK OUT left unconnected. The clock input frequency is nominally 10 MHz.

3 MCLK OUT When the master clock for the device is a crystal, the crystal is connected between MCLK IN and MCLK OUT.

4A0Address Input. With this input low, reading and writing to the device is to the control register. With this

input high, access is to either the data register or the calibration registers.

5 SYNC Logic Input. Allows for synchronization of the digital filters when using a number of AD7710s. It resets

the nodes of the digital filter.

6 MODE Logic Input. When this pin is high, the device is in its self-clocking mode; with this pin low, the device is in

its external clocking mode.

7 AIN1(+) Analog Input Channel 1. Positive input of the programmable gain differential analog input. The AIN1(+)

input is connected to an output current source that can be used to check that an external transducer has

burned out or gone open circuit. This output current source can be turned on/off via the control register.

8 AIN1(–) Analog Input Channel 1. Negative input of the programmable gain differential analog input.

9 AIN2(+) Analog Input Channel 2. Positive input of the programmable gain differential analog input.

10 AIN2(–) Analog Input Channel 2. Negative input of the programmable gain differential analog input.

11 V

12 AV

13 V

SS

DD

BIAS

14 REF IN(–) Reference Input. The REF IN(–) can lie anywhere between AV

15 REF IN(+) Reference Input. The reference input is differential providing that REF IN(+) is greater than REF IN(–).

16 REF OUT Reference Output. The internal 2.5 V reference is provided at this pin. This is a single-ended output which

17 I

OUT

18 AGND Ground Reference Point for Analog Circuitry.

Analog Negative Supply, 0 V to –5 V. Tied to AGND for single-supply operation. The input voltage on

AIN1 or AIN2 should not go > 30 mV negative w.r.t. V

for correct operation of the device.

SS

Analog Positive Supply Voltage, 5 V to 10 V.

Input Bias Voltage. This input voltage should be set such that V

0.85 × V

AV

DD

and V

> VSS where V

REF

and VSS. Thus with AVDD = 5 V and VSS = 0 V, it can be tied to REF OUT; with AVDD = 5 V

= –5 V, it can be tied to AGND; with AVDD = 10 V, it can be tied to 5 V.

SS

is REF IN(+) – REF IN(–). Ideally, this should be tied halfway between

REF

+ 0.85 × V

BIAS

and VSS provided REF IN(+) is greater

DD

< AVDD and V

REF

BIAS

–

than REF IN(–).

REF IN(+) can lie anywhere between AV

and VSS.

DD

is referred to AGND. It is a buffered output which is capable of providing 1 mA to an external load.

Compensation Current Output. A 20 µA constant current is provided at this pin. This current can be used in

association with an external thermistor to provide cold junction compensation in thermocouple applications.

This current can be turned on or off via the control register.

REV. G

–7–

AD7710

Pin Mnemonic Function

19 TFS Transmit Frame Synchronization. Active low logic input used to write serial data to the device with serial data

expected after the falling edge of this pulse. In the self-clocking mode, the serial clock becomes active after

TFS goes low. In the external clocking mode, TFS must go low before the first bit of the data-word is written

to the part.

20 RFS Receive Frame Synchronization. Active low logic input used to access serial data from the device. In the

self-clocking mode, the SCLK and SDATA lines both become active after RFS goes low. In the external

clocking mode, the SDATA line becomes active after RFS goes low.

21 DRDY Logic Output. A falling edge indicates that a new output word is available for transmission. The DRDY pin

will return high upon completion of transmission of a full output word. DRDY is also used to indicate when

the AD7710 has completed its on-chip calibration sequence.

22 SDATA Serial Data. Input/output with serial data being written to either the control register or the calibration regis-

ters, and serial data being accessed from the control register, calibration registers, or the data register.

During an output data read operation, serial data becomes active after RFS goes low (provided DRDY is low).

During a write operation, valid serial data is expected on the rising edges of SCLK when TFS is low. The

output data coding is natural binary for unipolar inputs and offset binary for bipolar inputs.

23 DV

DD

24 DGND Ground Reference Point for Digital Circuitry.

Digital Supply Voltage, 5 V. DVDD should not exceed AVDD by more than 0.3 V in normal operation.

Terminology Integral Nonlinearity

This is the maximum deviation of any code from a straight line

passing through the endpoints of the transfer function. The

endpoints of the transfer function are zero scale (not to be confused with bipolar zero), a point 0.5 LSB below the first code

transition (000 . . . 000 to 000 . . . 001) and full scale, a point

0.5 LSB above the last code transition (111 . . . 110 to 111 . . .

111). The error is expressed as a percentage of full scale.

Positive Full-Scale Error

Positive full-scale error is the deviation of the last code transition (111 . . . 110 to 111 . . . 111) from the ideal AIN(+) voltage

(AIN(–) + V

/GAIN – 3/2 LSBs). It applies to both unipolar

REF

and bipolar analog input ranges.

Unipolar Offset Error

Unipolar offset error is the deviation of the first code transition

from the ideal AIN(+) voltage (AIN(–) + 0.5 LSB) when operating in the unipolar mode.

Bipolar Zero Error

This is the deviation of the midscale transition (0111 . . . 111 to

1000 . . . 000) from the ideal AIN(+) voltage (AIN(–) – 0.5 LSB)

when operating in the bipolar mode.

Bipolar Negative Full-Scale Error

This is the deviation of the first code transition from the ideal

AIN(+) voltage (AIN(–) – V

/GAIN + 0.5 LSB) when operat-

REF

ing in the bipolar mode.

Positive Full-Scale Overrange

Positive full-scale overrange is the amount of overhead available

to handle input voltages on AIN(+) input greater than AIN(–) +

/GAIN (for example, noise peaks or excess voltages due to

V

REF

system gain errors in system calibration routines) without introducing errors due to overloading the analog modulator or to

overflowing the digital filter.

Negative Full-Scale Overrange

This is the amount of overhead available to handle voltages on

AIN(+) below AIN(–) –V

/GAIN without overloading the

REF

analog modulator or overflowing the digital filter. Note that the

analog input will accept negative voltage peaks even in the unipolar mode provided that AIN(+) is greater than AIN(–) and

greater than V

Offset Calibration Range

– 30 mV.

SS

In the system calibration modes, the AD7710 calibrates its offset

with respect to the analog input. The offset calibration range

specification defines the range of voltages that the AD7710 can

accept and still calibrate offset accurately.

Full-Scale Calibration Range

This is the range of voltages that the AD7710 can accept in the

system calibration mode and still calibrate full scale correctly.

Input Span

In system calibration schemes, two voltages applied in sequence

to the AD7710’s analog input define the analog input range.

The input span specification defines the minimum and maximum input voltages from zero- to full-scale that the AD7710 can

accept and still calibrate gain accurately.

–8–

REV. G

AD7710

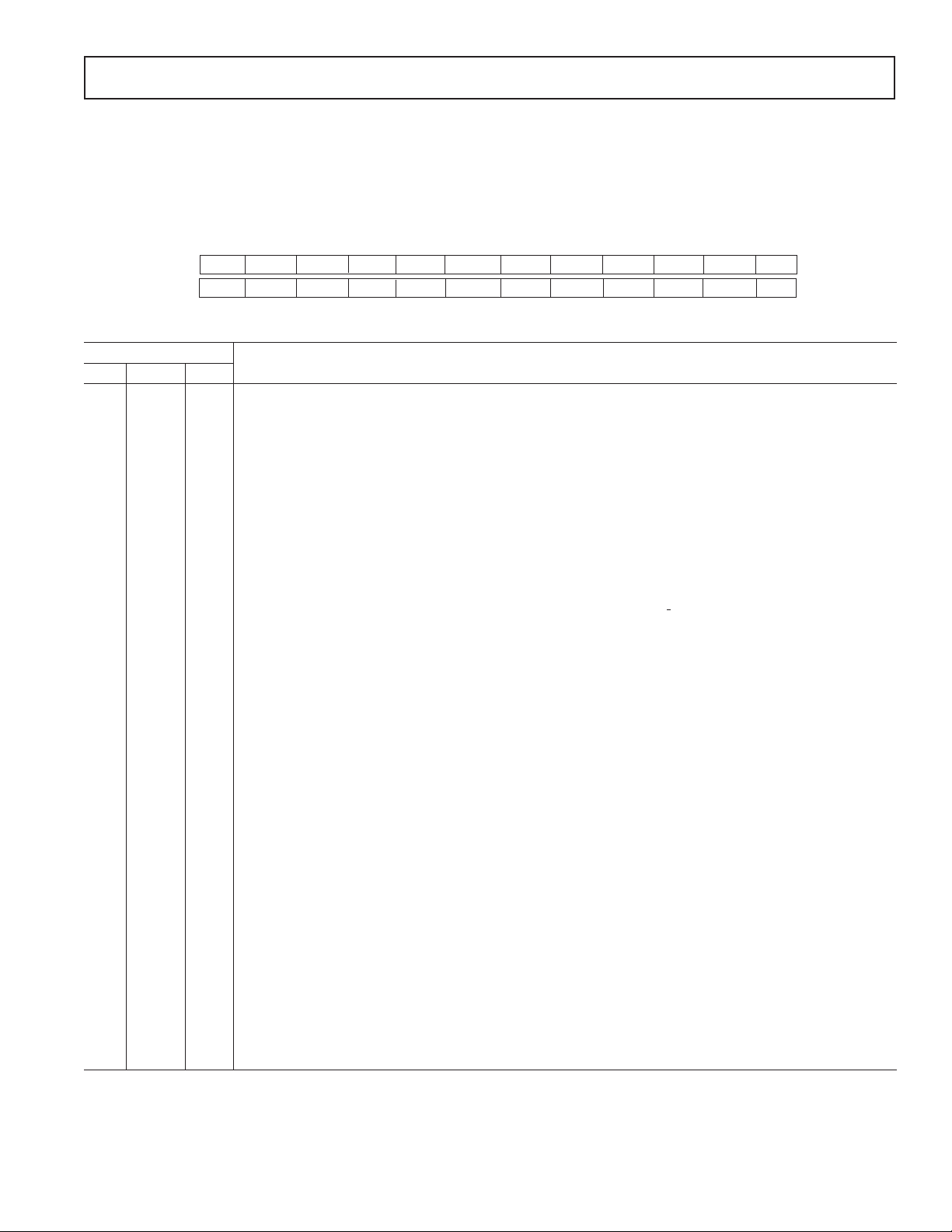

CONTROL REGISTER (24 BITS)

A write to the device with the A0 input low writes data to the control register. A read to the device with the A0 input low accesses the

contents of the control register. The control register is 24 bits wide; 24 bits of data must be written to the register or the data will not

be loaded. In other words, it is not possible to write just the first 12 bits of data into the control register. If more than 24 clock pulses

are provided before TFS returns high, then all clock pulses after the 24th clock pulse are ignored. Similarly, a read operation from the

control register should access 24 bits of data.

MSB

MD2 MD1 MD0 G2 G1 G0 CH PD WL IO BO B/U

FS11 FS10 FS9 FS8 FS7 FS6 FS5 FS4 FS3 FS2 FS1 FS0

LSB

Operating Mode

MD2 MD1 MD0 Operating Mode

00 0Normal Mode. This is the normal mode where a read to the device with A0 high accesses data from

the data register. This is the default condition of these bits after the internal power-on reset.

00 1Activate Self-Calibration. This activates self-calibration on the channel selected by CH. This is a one-step

calibration sequence, and when complete, the part returns to normal mode (with MD2, MD1, MD0 of

the control register returning to 0, 0, 0). The DRDY output indicates when this self-calibration is complete.

For this calibration type, the zero-scale calibration is done internally on shorted (zeroed) inputs, and the

full-scale calibration is done internally on V

01 0Activate System Calibration. This activates system calibration on the channel selected by CH. This is a

two-step calibration sequence, with the zero-scale calibration done first on the selected input channel and

DRDY indicating when this zero-scale calibration is complete. The part returns to normal mode at the

end of this first step in the two-step sequence.

01 1Activate System Calibration. This is the second step of the system ca

calibration being performed on the selected input channel. Once again, DRDY indicates when the fullscale calibration is complete. When this calibration is complete, the part returns to normal mode.

10 0Activate System Offset Calibration. This activates system offset calibration on the channel selected by

CH. This is a one-step calibration sequence and, when complete, the part returns to normal mode with

DRDY indicating when this system offset calibration is complete. For this calibration type, the zero-scale

calibration is done on the selected input channel, and the full-scale calibration is done internally on V

10 1Activate Background Calibration. This activates background calibration on the channel selected by CH. If

the background calibration mode is on, then the AD7710 provides continuous self-calibration of the

reference and shorted (zeroed) inputs. This calibration takes place as part of the conversion sequence,

extending the conversion time and reducing the word rate by a factor of 6. The major advantage of using

this mode is that the user does not have to recalibrate the device when there is a change in the ambient

temperature. In this mode, the shorted (zeroed) inputs and V

continuously monitored and the calibration registers of the device are automatically updated.

11 0Read/Write Zero-Scale Calibration Coefficients. A read to the device with A0 high accesses the contents

of the zero-scale calibration coefficients of the channel selected by CH. A write to the device with A0 high

writes data to the zero-scale calibration coefficients of the channel selected by CH. The word length for

reading and writing these coefficients is 24 bits, regardless of the status of the WL bit of the control

register. Therefore, 24 bits of data must be written to the calibration register, or the new data will not be

transferred to the calibration register.

11 1Read/Write Full-Scale Calibration Coefficients. A read to the device with A0 high accesses the contents of

the full-scale calibration coefficients of the channel selected by CH. A write to the device with A0 high

writes data to the full-scale calibration coefficients of the channel selected by CH. The word length for

reading and writing these coefficients is 24 bits, regardless of the status of the WL bit of the control

register. Therefore, 24 bits of data must be written to the calibration register, or the new data will not be

transferred to the calibration register.

REF

.

libration sequence with full-scale

.

REF

, as well as the analog input voltage, are

REF

REV. G

–9–

AD7710

PGA GAIN

G2 G1 G0 Gain

000 1(Default Condition after the Internal Power-On Reset)

001 2

010 4

011 8

100 16

101 32

110 64

111 128

CHANNEL SELECTION

CH Channel

0 AIN1 (Default Condition after the Internal Power-On Reset)

1 AIN2

Power-Down

PD

0Normal Operation (Default Condition after the Internal Power-On Reset) 1 Power-Down

Word Length

WL Output Word Length

0 16-Bit (Default Condition after Internal Power-On Reset)

1 24-Bit

Output Compensation Current

IO

0Off (Default Condition after Internal Power-On Reset)

1On

Burn-Out Current

BO

0Off (Default Condition after Internal Power-On Reset)

1On

Bipolar/Unipolar Selection (Both Inputs)

B/U

0 Bipolar (Default Condition after Internal Power-On Reset)

1 Unipolar

FILTER SELECTION (FS11–FS0)

The on-chip digital filter provides a sinc3 (or (sinx/x)3) filter

response. The 12 bits of data programmed into these bits determine the filter cutoff frequency, the position of the first notch of

the filter and the data rate for the part. In association with the

gain selection, it also determines the output noise (and therefore

the effective resolution) of the device.

The first notch of the filter occurs at a frequency determined by

the relationship: filter first notch frequency = (f

CLK IN

/512)/code

where code is the decimal equivalent of the code in bits FS0 to

FS11 and is in the range 19 to 2,000. With the nominal f

CLK IN

of 10 MHz, this results in a first notch frequency range from

9.76 Hz to 1.028 kHz. To ensure correct operation of the

AD7710, the value of the code loaded to these bits must be

within this range. Failure to do this will result in unspecified

operation of the device.

Changing the filter notch frequency, as well as the selected gain,

impacts resolution. Tables I and II and Figure 2 show the effect

of the filter notch frequency and gain on the effective resolution

of the AD7710. The output data rate (or effective conversion

time) for the device is equal to the frequency selected for the

–10–

first notch of the filter. For example, if the first notch of the

filter is selected at 50 Hz, then a new word is available at a 50 Hz

rate or every 20 ms. If the first notch is at 1 kHz, a new word is

available every 1 ms.

The settling time of the filter to a full-scale step input change is

worst case 4 × 1/(output data rate). This settling time is to

100% of the final value. For example, with the first filter notch

at 50 Hz, the settling time of the filter to a full-scale step input

change is 80 ms max. If the first notch is at 1 kHz, the settling

time of the filter to a full-scale input step is 4 ms max. This

settling time can be reduced to 3 × l/(output data rate) by synchronizing the step input change to a reset of the digital filter. In

other words, if the step input takes place with SYNC low, the

settling time will be 3 × l/(output data rate). If a change of channels takes place, the settling time is 3 × l/(output data rate)

regardless of the SYNC input.

The –3 dB frequency is determined by the programmed first

notch frequency according to the relationship:

filter –3 dB frequency = 0.262 × first notch frequency.

REV. G

Loading...

Loading...