16-Bit - ADC with

a

FEATURES

16-Bit - ADC

Programmable Gain Front End

Simultaneous 50 Hz and 60 Hz Rejection at 20 Hz

Update Rate

VREF Select

Measurement Capability

ISOURCE Select

16-Bit No Missing Codes

13-Bit p-p Resolution @ 20 Hz, 20 mV Range

16-Bit p-p Resolution @ 20 Hz, 2.56 V Range

INTERFACE

3-Wire Serial

SPI®, QSPI™, MICROWIRE™, and DSP Compatible

Schmitt Trigger on SCLK

POWER

Specified for Single 3 V and 5 V Operation

Normal: 1.25 mA Typ @ 3 V

Power-Down: 7 A (32.768 kHz Crystal Running)

ON-CHIP FUNCTIONS

Rail-to-Rail Input Buffer and PGA

Selectable Reference Inputs

3 Switchable, Ratioed Current Sources for

V

BE

4-Bit Digital I/O Port

Low-Side Power Switches

™ Allows Absolute and Ratiometric

™

Measurements

Switchable Current Sources

AD7709

APPLICATIONS

Sensor Measurement

Temperature Measurement

Pressure Measurements

Weigh Scales

Portable Instrumentation

4–20 mA Loops

GENERAL DESCRIPTION

The AD7709 is a complete analog front end for low frequency

measurement applications. It contains a 16-bit ⌺-⌬ ADC, selectable

reference inputs, three switchable matched excitation current

sources, low-side power switches, and a digital I/O port. The

16-bit channel with PGA accepts fully differential, unipolar,

and

bipolar input signal ranges from 1.024 ⫻ REFIN/128 to

1.024 ⫻ REFIN. It can be configured as two fully differential

input channels or four pseudo-differential input channels. Signals

can be converted directly from a transducer without the need for

signal conditioning.

The device operates from a 32.768 kHz crystal with an on-chip

PLL generating the required internal operating frequency. The

output data rate from the part is software programmable. The

p-p

resolution from the part varies with the programmed gain

and output data rate.

The part operates from a single 3 V or 5 V supply. When

operating from 3 V supplies, the power dissipation for the part

is 3.75 mW. The AD7709 is housed in a 24-lead TSSOP package.

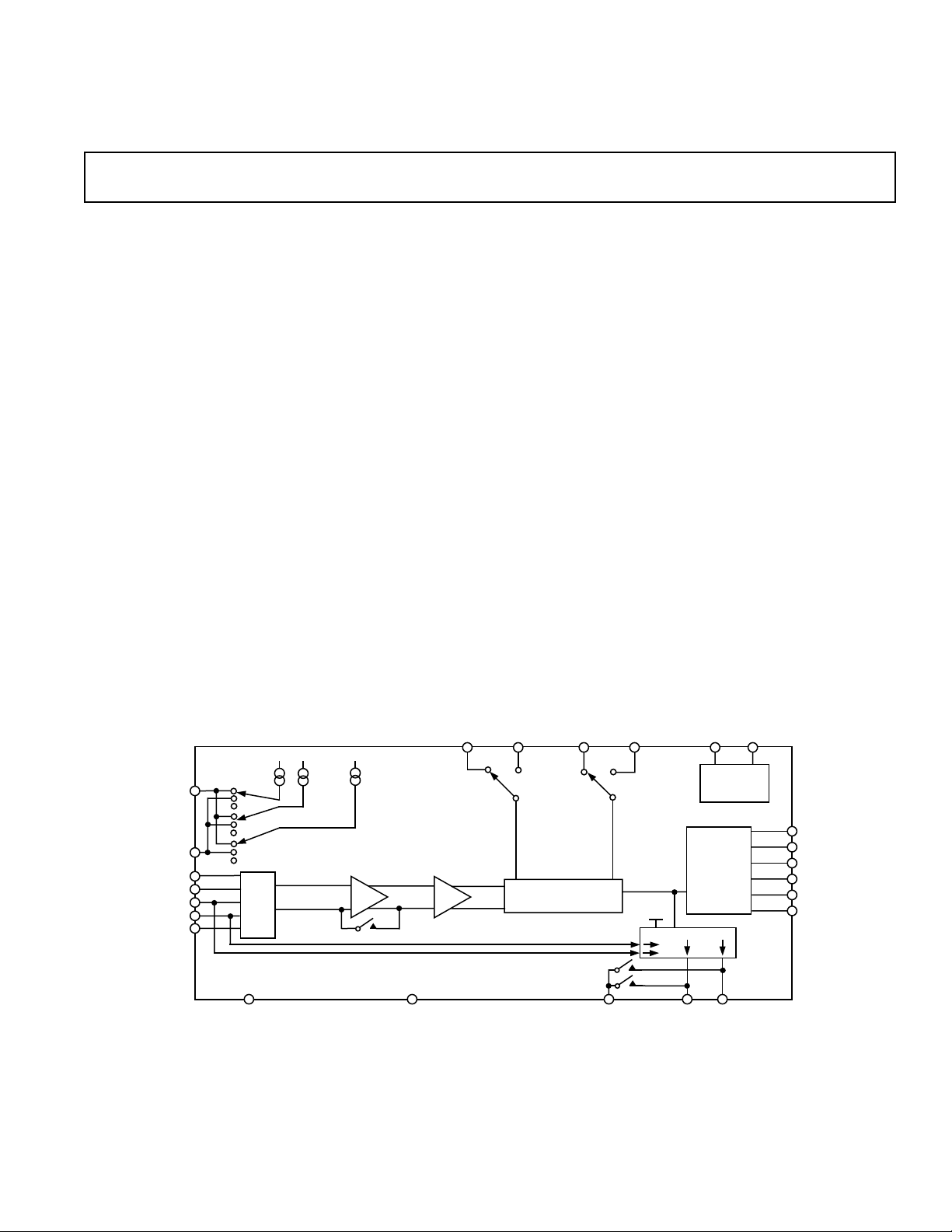

FUNCTIONAL BLOCK DIAGRAM

V

DD

IOUT1

IOUT2

AIN1

AIN2

AIN3/P3

AIN4/P4

AINCOM

IEXC1

8I

MUX

AD7709

V

DD

IEXC2

8I

IEXC3

I = 25A

BUF

I

PGA

GND

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

XTAL2REFIN1(–) REFIN2(–)REFIN1(+) REFIN2(+) XTAL1

OSCILLATOR

AND

PLL

DOUT

SERIAL

INTERFACE

AND

CONTROL

16-BIT - ADC

PWRGND

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

V

DD

I/O PORT

LOGIC

P1/SW1 P2/SW2

DIN

SCLK

CS

RDY

RESET

AD7709

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 1

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . 1

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . 6

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . 8

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . 9

TYPICAL PERFORMANCE CHARACTERISTICS . . . . 10

ADC CIRCUIT INFORMATION . . . . . . . . . . . . . . . . . . . 11

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

S-D ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

NOISE PERFORMANCE . . . . . . . . . . . . . . . . . . . . . . . . . 13

ON-CHIP REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Communications Register . . . . . . . . . . . . . . . . . . . . . . . . 14

Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Filter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

ADC Data Result Register . . . . . . . . . . . . . . . . . . . . . . . . 18

CONFIGURING THE AD7709 . . . . . . . . . . . . . . . . . . . . . 19

DIGITAL INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

MICROCOMPUTER/MICROPROCESSOR

INTERFACING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

AD7709-to-68HC11 Interface . . . . . . . . . . . . . . . . . . . . . 21

AD7709-to-8051 Interface . . . . . . . . . . . . . . . . . . . . . . . . 21

AD7709-to-ADSP-2103/ADSP-2105 Interface . . . . . . . . 21

CIRCUIT DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . 22

Analog Input Channels . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Programmable Gain Amplifier . . . . . . . . . . . . . . . . . . . . . 23

Bipolar/Unipolar Configuration . . . . . . . . . . . . . . . . . . . . 23

Data Output Coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Excitation Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Reference Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Reset Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Power-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Grounding and Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Pressure Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Temperature Measurement . . . . . . . . . . . . . . . . . . . . . . . 26

3-Wire RTD Configurations . . . . . . . . . . . . . . . . . . . . . . 27

Smart Transmitters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 29

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

–2–

REV. A

AD7709

(VDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V; REFIN(–) = GND; GND = 0 V; XTAL1/XTAL2 =

2, 4

2, 4

1

32.768 kHz Crystal; all specifications T

105 Hz max

16 Bits min 20 Hz Update Rate

16 Bits p-p ± 2.56 V Range, 20 Hz Update Rate

± 30 ppm of FSR max Typically 2 ppm

± 0.75 LSB typ B Grade, VDD = 4 V

± 0.2 % of FS typ A Grade

±¥1 024. REFIN

GAIN

2

GND + 100 mV V min

– 100 mV V max

V

DD

± 1 nA max

2

GND – 30 mV V min

+ 30 mV V max

V

DD

100 dB min 50 Hz ± 1 Hz, Range = ± 2.56 V, AIN = 1 V

100 dB min 60 Hz ± 1 Hz, Range = ± 2.56 V, AIN = 1 V

1V min

V

2

DD

GND – 30 mV V min

+ 30 mV V max

V

DD

to T

MIN

, unless otherwise noted.)

MAX

FSR

¥21024.

=

GAIN

100 dB typ on ± 20 mV Range

V nom REFIN = REFIN(+) – REFIN(–)

GAIN = 1 to 128

50 Hz ± 1Hz, 16.65 Hz Update Rate, SF = 82

110 dB typ on ± 20 mV Range

V max

REFIN

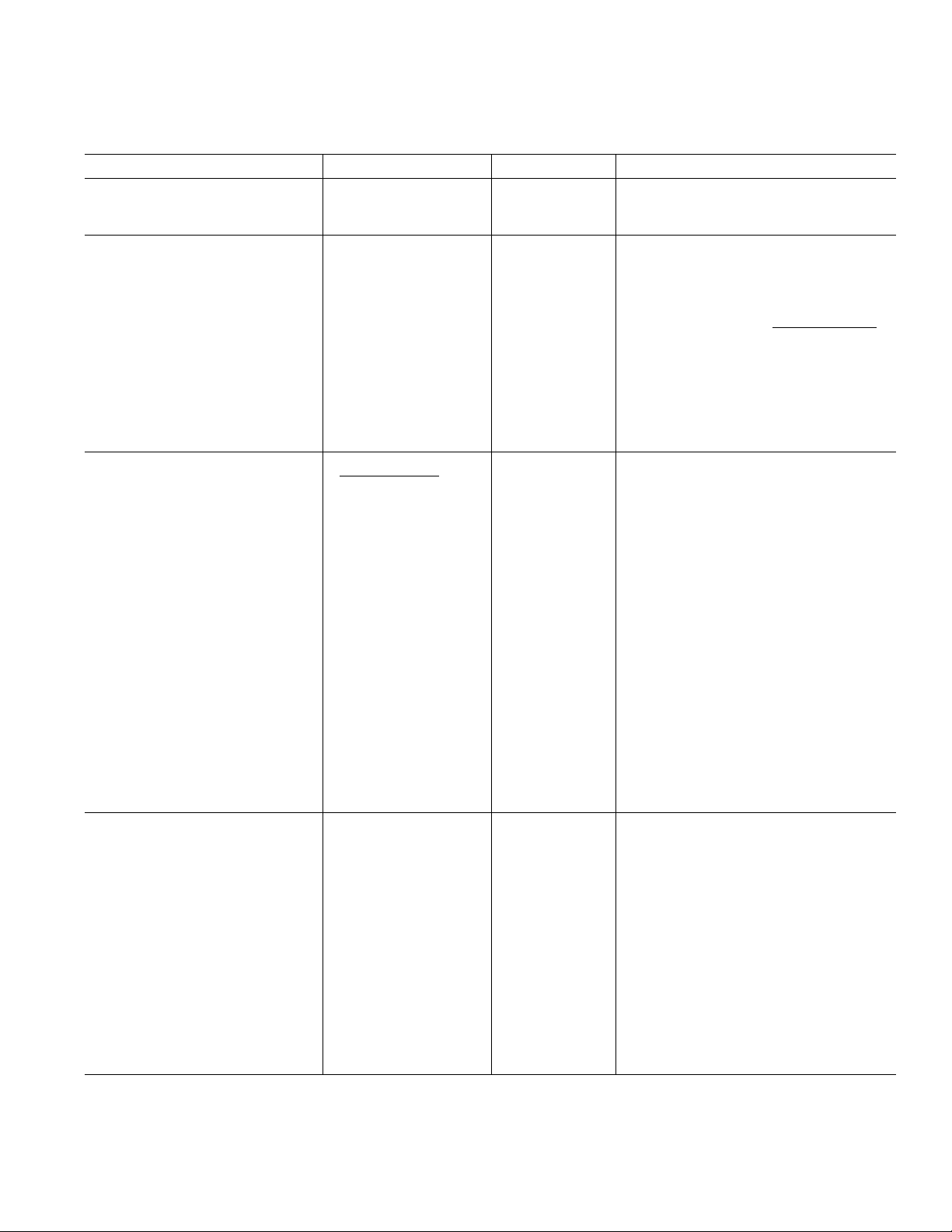

SPECIFICATIONS

Parameter AD7709A, AD7709B Unit Test Conditions

ADC CHANNEL SPECIFICATION

Output Update Rate 5.4 Hz min 0.732 ms Increments

ADC CHANNEL

No Missing Codes

Resolution 13 Bits p-p ± 20 mV Range, 20 Hz Update Rate

Output Noise and Update Rates See Tables II to V

Integral Nonlinearity

Offset Error ± 3 mV typ

Offset Error Drift vs. Temperature ± 10 nV/∞C typ

Full-Scale Error

Gain Drift vs. Temperature ± 0.5 ppm/∞C typ

Power Supply Rejection (PSR) 85 dB typ Input Range = ± 2.56 V

ANALOG INPUTS

Differential Input Voltage Ranges

ADC Range Matching ± 2 mV typ Input Voltage = 19 mV on All Ranges

Absolute AIN1–AIN4 Voltage Limits

AIN1–AIN4 Analog Input Current

DC Input Current

DC Input Current Drift ± 5 pA /∞C typ

Absolute AINCOM Voltage Limits

AINCOM Analog Input Current Pseudo-Differential Mode of Operation

DC Input Current ± 125 nA/V typ Input Current Varies with Input Range

DC Input Current Drift ± 2 pA/V/∞C typ

Normal-Mode Rejection

@ 50 Hz 100 dB min

@ 60 Hz 100 dB min 60 Hz ± 1 Hz, 20 Hz Update Rate, SF = 68

Common-Mode Rejection

@ DC 100 dB typ Input Range = ± 2.56 V, AIN = 1 V

@ 50 Hz

@ 60 Hz

REFERENCE INPUTS

(REFIN1 and REFIN2)

REFIN Voltage 2.5 V nom REFIN = REFIN(+) – REFIN(–)

REFIN Voltage Range

Absolute REFIN Voltage Limits

Average Reference Input Current 0.5 mA/V typ

Average Reference Input Current Drift ± 0.01 nA/V/∞C typ

Normal-Mode Rejection

@ 50 Hz 100 dB min 50 Hz ± 1 Hz, SF = 82

@ 60 Hz 100 dB min 60 Hz ± 1 Hz, SF = 68

Common-Mode Rejection

@ DC 110 dB typ Input Range = ± 2.56 V, AIN = 1 V

@ 50 Hz 110 dB typ 50 Hz ± 1 Hz, Range = 2.56 V, AIN = 1 V

@ 60 Hz 110 dB typ 60 Hz ± 1 Hz, Range = 2.56 V, AIN = 1 V

See Notes on page 5.

2

2

3

2

2

2

2

REV. A

–3–

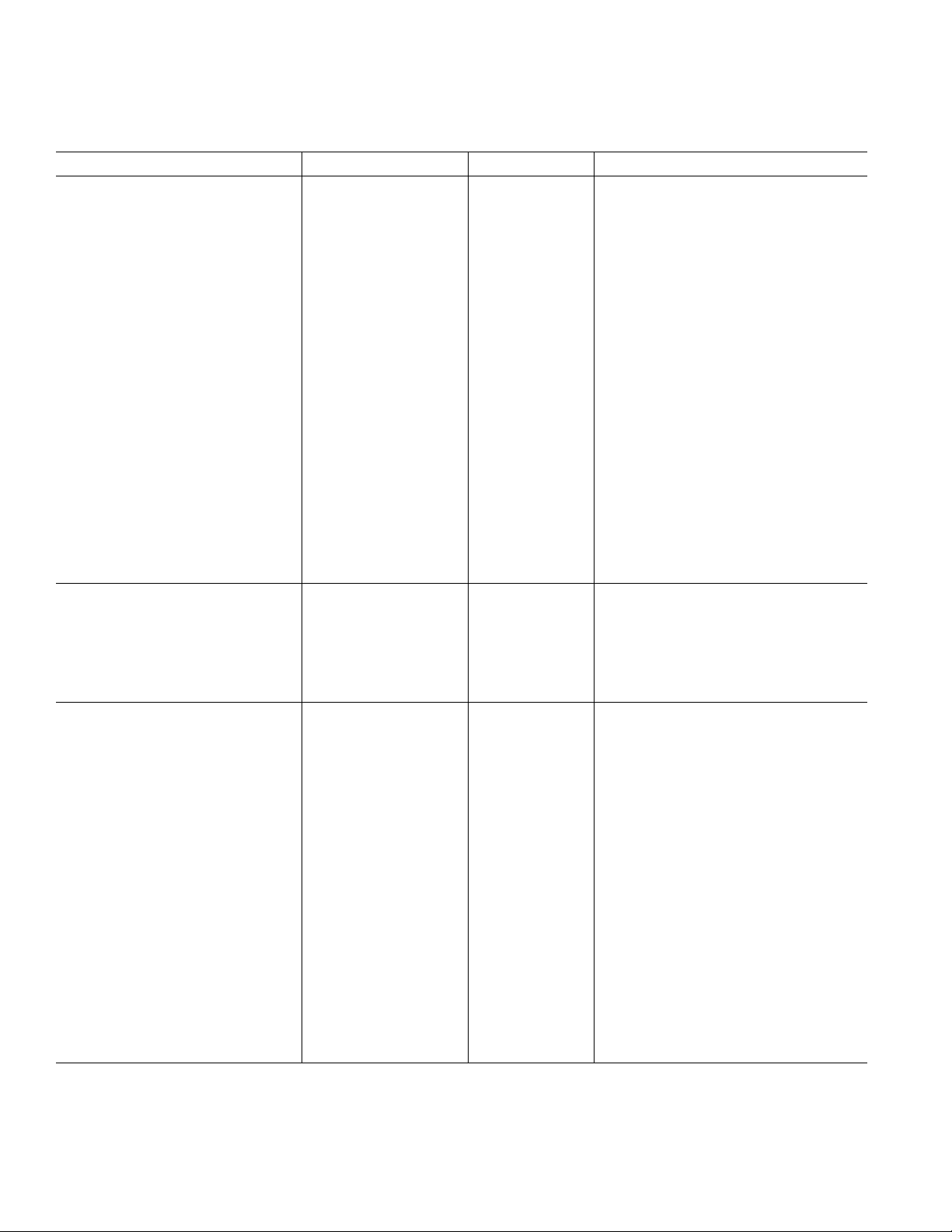

AD7709

SPECIFICATIONS

(continued)

Parameter AD7709A, AD7709B Unit Test Conditions

EXCITATION CURRENT SOURCES

(IEXC1, IEXC2, and IEXC3)

Output Current

IEXC1, IEXC2 200 mA nom

IEXC3 25 mA nom

Initial Tolerance at 25∞C ± 10 % typ

Drift 200 ppm/∞C typ

Initial Current Matching at 25∞C ± 2.5 % max B Grade, No Load

(between IEXC1 and IEXC2) ± 2.5 % typ A Grade, No Load

Drift Matching

(between IEXC1 and IEXC2) 20 ppm/∞C typ

Initial Current Matching at 25∞C ± 5% max B Grade, No Load

(between 8 ⫻ IEXC3 and

IEXC1/IEXC2) ± 5% typ A Grade, No Load

Drift Matching

(between 8 ⫻ IEXC3 and

IEXC1/IEXC2) 20 ppm/∞C typ

Line Regulation V

= 5 V ± 5%

DD

IEXC1, IEXC2 1.25 mA/V typ A, B Grades

2.6 mA/V max B Grade

IEXC3 1 mA/V max B Grade

1 mA/V typ A Grade

Load Regulation 300 nA/V typ

Output Compliance V

– 0.6 V max

DD

GND –30 mV V min

LOW-SIDE POWER SWITCHES

(SW1 and SW2)

R

ON

3 W typ VDD = 5 V, A and B Grade

5 W max B Grade

4.5 W typ V

Allowable Current

2

LOGIC INPUTS

All Inputs Except SCLK and XTAL1

V

, Input Low Voltage 0.8 V max VDD = 5 V

INL

7 W max B Grade

20 mA max Continuous Current per Switch

2

0.4 V max V

V

, Input High Voltage 2.0 V min VDD = 3 V or 5 V

INH

SCLK Only (Schmitt-Triggered Input)

V

T(+)

V

T(–)

– V

V

T(+)

V

V

V

XTAL1 Only

V

V

V

V

T(–)

T(+)

T(–)

– V

T(+)

T(–)

2

, Input Low Voltage 0.8 V max VDD = 5 V

INL

, Input High Voltage 3.5 V min VDD = 5 V

INH

, Input Low Voltage 0.4 V max VDD = 3 V

INL

, Input High Voltage 2.5 V min VDD = 3 V

INH

2

1.4/2 V min/V max VDD = 5 V

0.8/1.4 V min/V max VDD = 5 V

0.3/0.85 V min/V max VDD = 5 V

0.95/2 V min/V max VDD = 3 V

0.4/1.1 V min/V max VDD = 3 V

0.3/0.85 V min/V max VDD = 3 V

Input Currents (except XTAL) ± 2 mA max V

= 3 V, A and B Grade

DD

= 3 V

DD

= V

IN

DD

–70 mA max VIN = GND, Typically –40 mA @ 5 V and

–20 mA at 3 V; Weak Pull-Ups on the

Logic Inputs

Input Capacitance 10 pF typ All Digital Inputs

–4–

REV. A

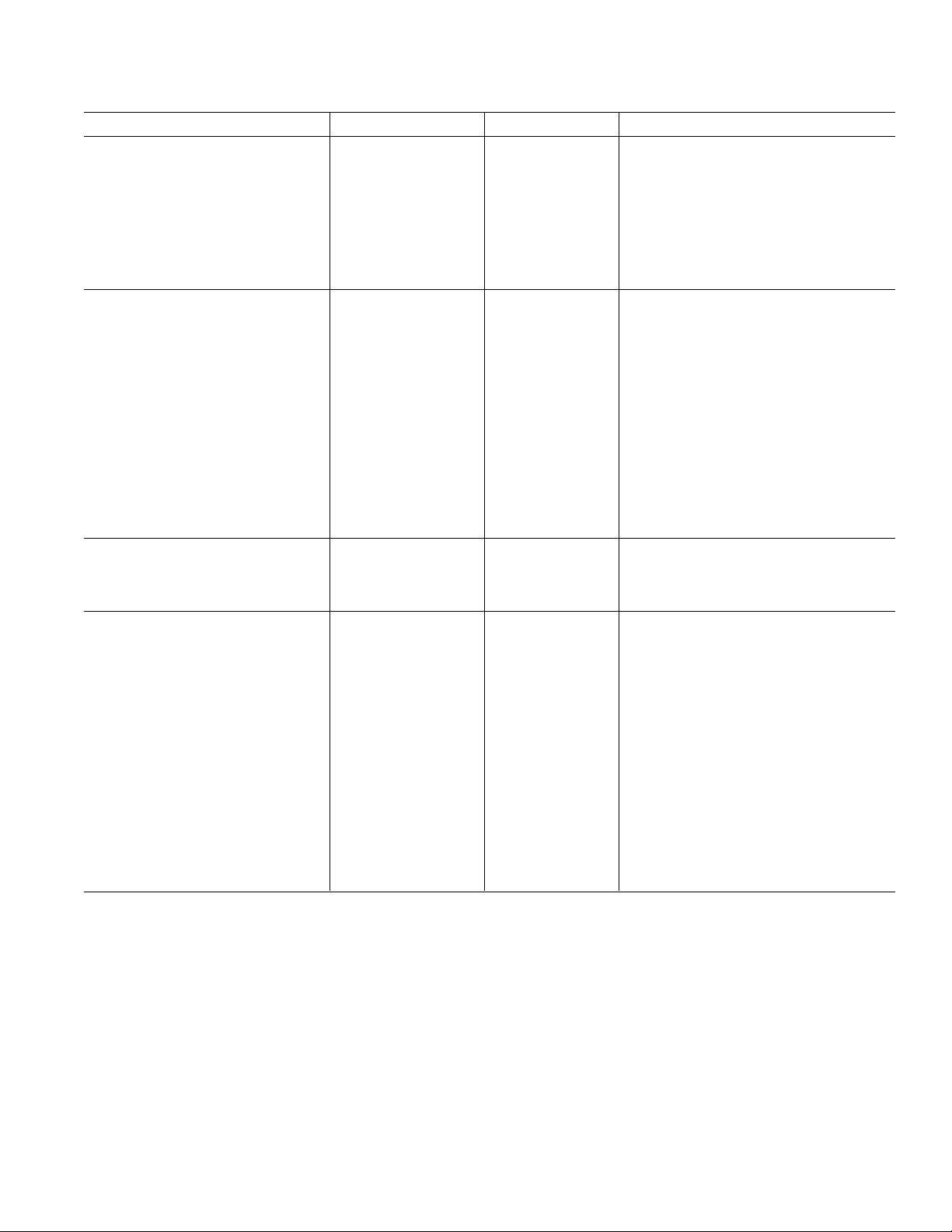

AD7709

Parameter AD7709A,

LOGIC OUTPUTS (Excluding XTAL2)

, Output High Voltage

V

OH

VOL, Output Low Voltage

, Output High Voltage

V

OH

, Output Low Voltage

V

OL

2

2

2

2

VDD – 0.6 V min VDD = 3 V, I

0.4 V max VDD = 3 V, I

4V min VDD = 5 V, I

0.4 V max VDD = 5 V, I

AD7709

BUnit Test Conditions

SOURCE

SINK

SOURCE

SINK

= 100 mA

= 100 mA

= 200 mA

= 1.6 mA

Floating-State Leakage Current ± 10 mA max

Floating-State Output Capacitance ± 10 pF typ

Data Output Coding Binary Unipolar Mode

Offset Binary Bipolar Mode

I/O PORT

, Input Low Voltage

V

INL

, Input High Voltage

V

INH

Input Currents ± 2 mA max V

2

2

0.8 V max VDD = 5 V

0.4 V max V

DD

= 3 V

2.0 V min VDD = 3 V or 5 V

= V

IN

DD

–70 mA max VIN = GND, Typically –40 mA @ VDD = 5 V

and –20 mA at V

= 3 V; Weak Pull-Ups on

DD

the Logic Inputs

Input Capacitance 10 pF typ All Digital Inputs

, Output High Voltage

V

OH

, Output Low Voltage

V

OL

, Output High Voltage

V

OH

VOL, Output Low Voltage

2

2

2

2

VDD – 0.6 V min VDD = 3 V, I

0.4 V max VDD = 3 V, I

4V min VDD = 5 V, I

0.4 V max VDD = 5 V, I

SOURCE

= 100 mA

SINK

SOURCE

= 1.6 mA

SINK

= 100 mA

= 200 mA

Floating-State Output Leakage Current ± 10 mA max

Floating-State Output Capacitance ±10 pF typ

START-UP TIME

From Power-On 300 ms typ

From Standby Mode 1 ms typ OSCPD = 0

From Power-Down Mode 300 ms typ OSCPD = 1

POWER REQUIREMENTS

Power Supply Voltage

– GND 2.7/3.6 V min/max VDD = 3 V nom

V

DD

4.75/5.25 V min/max V

= 5 V nom

DD

Power Supply Currents

Current 1.5 mA max VDD = 3 V, 1.25 mA typ

I

DD

1.75 mA max V

(Low Power Mode) 7 mA max B Grade, VDD = 3 V, Standby Mode

I

DD

= 5 V, 1.45 mA typ

DD

7 mA typ A Grade, VDD = 3 V, Standby Mode

1.5 mA max B Grade, V

1.5 mA typ A Grade, V

= 3 V, Power-Down Mode

DD

= 3 V, Power-Down Mode

DD

26 mA max B Grade, VDD = 5 V, Standby Mode

26 mA typ A Grade, V

6.5 mA max B Grade, V

6.5 mA typ A Grade, VDD = 5 V, Power-Down Mode

134

5

5

mA typ VDD = 3 V, Standby Mode

mA typ VDD = 5 V, Standby Mode

for One Conversion Second 107

I

DD

NOTES

1

Temperature Range –40∞C to +85∞C.

2

Guaranteed by design and/or characterization data on production release.

3

Full-scale error applies to both positive and negative full scale.

4

Simultaneous 50 Hz and 60 Hz rejection is achieved using 19.79 Hz update rate. Normal mode rejection in this case is 60 dB min.

5

When the part is placed in power-down mode for a single conversion/second, at an update rate of 19.79 Hz, the current consumption is higher compared to when the

part is placed in standby mode as the crystal oscillator takes approximately 100 ms to begin clocking. The device will, therefore, use full current for the conversion

time and the 100 ms period required for the oscillator to begin clocking. However, if the conversion rate is lower, the current consumption will be reduced so that it

is worthwhile to use the power-down rather than the standby mode.

Specifications subject to change without notice.

= 5 V, Standby Mode

DD

= 5 V, Power-Down Mode

DD

REV. A

–5–

AD7709

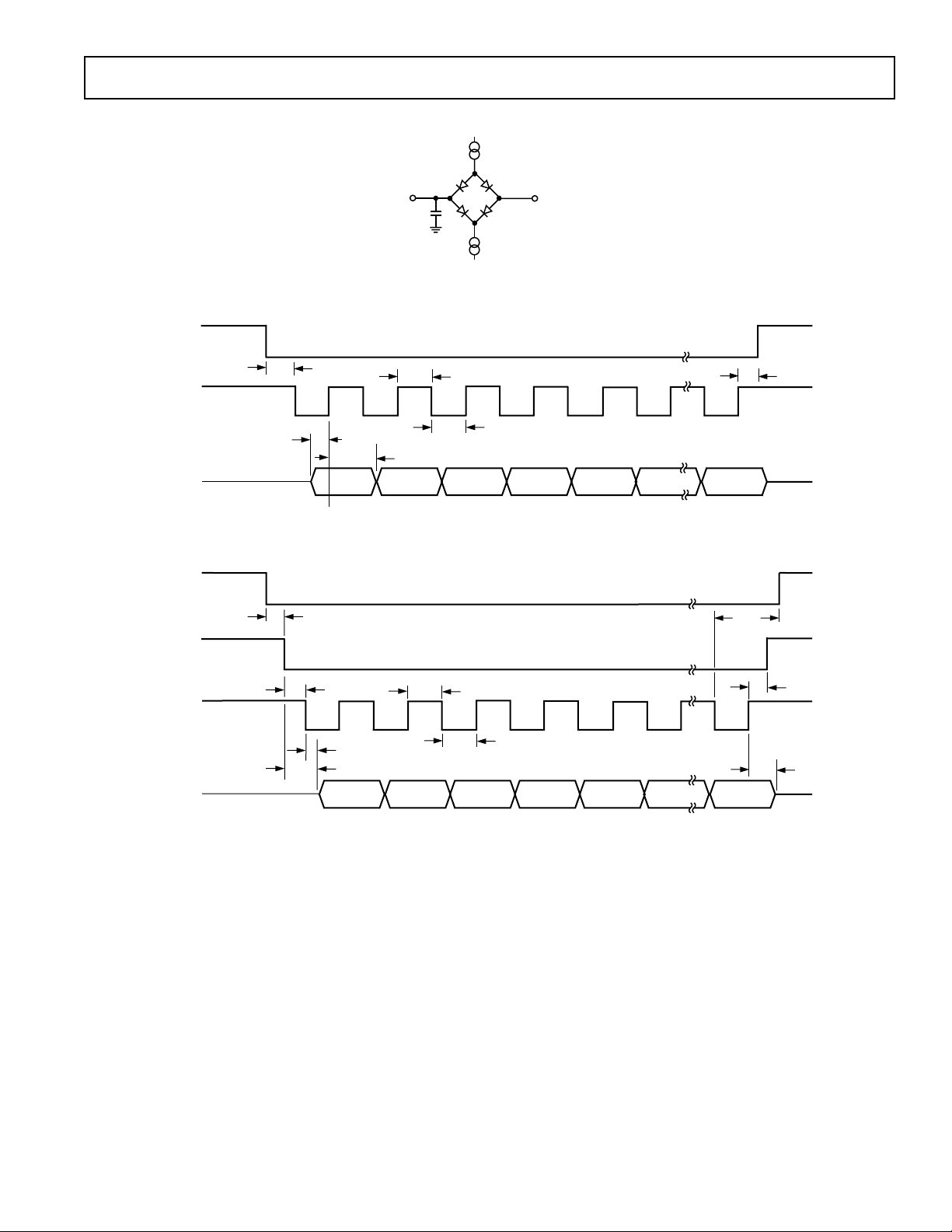

TIMING CHARACTERISTICS

Limit at T

MIN

(VDD = 2.7 V to 3.6 V or VDD = 4.75 V to 5.25 V; GND = 0 V; X

1, 2

Logic 1 = VDD unless otherwise noted.)

, T

MAX

= 32.768 kHz; Input Logic 0 = 0 V,

TAL

Parameter (A, B Version) Unit Conditions/Comments

t

1

t

2

30.5176

ms

typ Crystal Oscillator Period

50 ns min RESET Pulsewidth

Read Operation

t

3

t

4

4

t

5

0 ns min RDY to CS Setup Time

0 ns min CS Falling Edge to SCLK Active Edge Setup Time

0 ns min SCLK Active Edge to Data Valid Delay

3

3

60 ns max VDD = 4.75 V to 5.25 V

4, 5

t

5A

80 ns max V

0 ns min CS Falling Edge to Data Valid Delay

60 ns max V

80 ns max V

t

6

t

7

t

8

6

t

9

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Inactive Edge Hold Time

10 ns min Bus Relinquish Time after SCLK Inactive Edge

80 ns max

t

10

100 ns max SCLK Active Edge to RDY High

Write Operation

t

11

t

12

t

13

t

14

t

15

t

16

NOTES

1

Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of VDD) and timed from a voltage level of 1.6 V.

2

See Figures 2 and 3.

3

SCLK active edge is falling edge of SCLK.

4

These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross the V

5

This specification comes into play only if CS goes low while SCLK is low. It is required primarily for interfacing to DSP machines.

6

These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the Timing Characteristics table are the true bus relinquish

times of the part and as such are independent of external bus loading capacitances.

7

RDY returns high after a read of the ADC. The same data can be read again, if required, while RDY is high, although care should be taken that subsequent reads do not occur

close to the next output update.

0 ns min CS Falling Edge to SCLK Active Edge Setup Time

30 ns min Data Valid to SCLK Edge Setup Time

25 ns min Data Valid to SCLK Edge Hold Time

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Edge Hold Time

= 2.7 V to 3.6 V

DD

= 4.75 V to 5.25 V

DD

= 2.7 V to 3.6 V

DD

or VOH limits.

OL

3

3

3, 7

3

–6–

REV. A

I

(1.6mA WITH VDD = 5V

SINK

100A WITH V

DD

AD7709

= 3V)

CS

SCLK

DIN

RDY

TO OUTPUT

PIN

50pF

I

SOURCE

1.6V

(200A WITH VDD = 5V

100A WITH V

DD

= 3V)

Figure 1. Load Circuit for Timing Characterization

t

11

t

12

t

13

MSB

t

14

t

15

LSB

t

16

Figure 2. Write Cycle Timing Diagram

t

3

t

10

SCLK

DOUT

CS

t

LSB

8

t

9

t

4

t

5

t

5A

MSB

t

6

t

7

Figure 3. Read Cycle Timing Diagram

REV. A

–7–

AD7709

ABSOLUTE MAXIMUM RATINGS*

(TA = 25∞C, unless otherwise noted.)

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

PWRGND to AGND . . . . . . . . . . . . . . –20 mV to +20 mV

Analog Input Voltage to GND . . . . . –0.3 V to V

Reference Input Voltage to GND . . . –0.3 V to V

+ 0.3 V

DD

+ 0.3 V

DD

Total AIN/REFIN Current (Indefinite) . . . . . . . . . . 30 mA

Digital Input Voltage to GND . . . . . . . –0.3 V to V

+ 0.3 V

DD

Digital Output Voltage to GND . . . . –0.3 V to VDD + 0.3 V

Operating Temperature Range . . . . . . . . . . –40∞C to +85∞C

Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . 150∞C

Thermal Impedance . . . . . . . . . . . . . . . . . . . 97.9∞C/W

q

JA

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 14∞C/W

q

JC

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . 215∞C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 220∞C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD7709ARU –40∞C to +85∞C TSSOP RU-24

AD7709BRU –40∞C to +85∞C TSSOP RU-24

EVAL-AD7709EB Evaluation Board

PIN CONFIGURATION

IOUT1

IOUT2

REFIN1(+)

REFIN1(–)

AIN1

AIN2

AIN3/P3

AIN4/P4

AINCOM

REFIN2(+)

REFIN2(–)

P2/SW2

1

2

3

4

5

AD7709

6

TOP VIEW

(Not to Scale)

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

XTAL1

XTAL2

V

DD

GND

DIN

DOUT

RDY

CS

SCLK

RESET

P1/SW1

PWRGND

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

WARNING!

AD7709 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

ESD SENSITIVE DEVICE

–8–

REV. A

AD7709

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1 IOUT1 Output for Internal Excitation Current Source. Either current source IEXC1, IEXC2, IEXC3, or a combina-

tion of the current sources, can be switched to this output.

2 IOUT2 Output for Internal Excitation Current Source. Either current source IEXC1, IEXC2, IEXC3, or a combina-

tion of the current sources, can be switched to this output.

3 REFIN1(+) Positive Reference Input. REFIN1(+) can lie anywhere between V

voltage (REFIN1(+) – REFIN1(–)) is 2.5 V, but the part is functional with a reference range from 1 V to VDD.

ence

4 REFIN1(–) Negative Reference Input. This reference input can lie anywhere between GND and VDD – 1 V.

5 AIN1 Analog Input. Programmable gain input that can be used as a pseudo-differential input when used with

AINCOM or as the positive input of a fully differential input pair when used with AIN2.

6 AIN2 Analog Input. Programmable gain input that can be used as a pseudo-differential input when used with

AINCOM or as the negative input of a fully differential input pair when used with AIN1.

7 AIN3/P3 Analog Input/Digital Port Bit. Programmable gain input that can be used as a pseudo-differential input when

used with AINCOM or as the positive input of a fully differential input pair when used with AIN4. This pin

can also be programmed as a general-purpose digital input bit.

8 AIN4/P4 Analog Input/Digital Port Bit. Programmable gain input that can be used as a pseudo-differential input when

used with AINCOM or as the negative input of a fully-differential input pair when used with AIN3. This pin

can also be programmed as a general-purpose digital input bit.

9 AINCOM All analog inputs are referenced to this input when configured in pseudo-differential input mode.

10 REFIN2(+) Positive Reference Input. REFIN2(+) can lie anywhere between V

voltage (REFIN2(+) – REFIN2(–)) is 2.5 V, but the part is functional with a reference range from 1 V to V

11 REFIN2(–) Negative Reference Input. This reference input can lie anywhere between GND and VDD – 1 V.

12 P2/SW2 Dual-Purpose Pin. It can act as a general-purpose output (P2) bit or as a low-side power switch (SW2) to

PWRGND.

13 PWRGND Ground Point for the Low-Side Power Switches SW2 and SW1. PWRGND must be tied to GND.

14 P1/SW1 Dual-Purpose Pin. It can act as a general-purpose output (P1) bit or as a low-side power switch (SW1) to

PWRGND.

15 RESET

Digital Input Used to Reset the ADC to Its Power-On-Reset Status. This pin has a weak pull-up internally to VDD.

16 SCLK Serial Clock Input for Data Transfers to and from the ADC. The SCLK has a Schmitt-triggered input making

the interface suitable for opto-isolated applications. The serial clock can be continuous with all data transmitted

in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being

transmitted to or from the AD7709 in smaller batches of data. A weak pull-up to V

SCLK input.

17 CS Chip Select Input. This is an active low logic input used to select the AD7709. CS can be used to select the

AD7709 in systems with more than one device on the serial bus or as a frame synchronization signal in com-

municating with the device. CS can be hardwired low allowing the AD7709 to operate in 3-wire mode with

SCLK, DIN, and DOUT used to interface with the device. A weak pull-up to VDD is provided on the CS input.

18 RDY RDY is a Logic Low Status Output from the AD7709. RDY is low if the ADC has valid data in its data

register. This output returns high on completion of a read operation from the data register. If data is not

read, RDY will return high prior to the next update indicating to the user that a read operation should

not be initiated.

19 DOUT Serial Data Output Accessing the Output Shift Register of the AD7709. The output shift register can contain

data from any of the on-chip data or control registers.

20 DIN Serial Data Input Accessing the Input Shift Register on the AD7709. Data in this shift register is transferred to

the control registers within the ADC, the selection bits of the communications register selecting which

control register. A weak pull-up to V

is provided on the DIN input.

DD

21 GND Ground Reference Point for the AD7709

22 V

DD

Supply Voltage, 3 V or 5 V Nominal

23 XTAL2 Output from the 32.768 kHz Crystal Oscillator Inverter

24 XTAL1 Input to the 32.768 kHz Crystal Oscillator Inverter

and GND + 1 V. The nominal refer-

DD

and GND + 1 V. The nominal reference

DD

is provided on the

DD

DD

.

REV. A

–9–

AD7709–Typical Performance Characteristics

32772

32771

32770

32769

32768

CODE READ

32767

32766

32765

32764

1000 200 400300

VDD = 5V

INPUT RANGE = 20mV

UPDATE RATE = 19.79Hz

500

READING NUMBER

600 700 800 900 1000

V

REF

T

A

= 2.5V

= 25 C

TPC 1. Typical Noise Plot on ±20 mV Input Range

3.0

= 2.5V

= 25C

2.56V RANGE

20mV RANGE

2.5

2.0

VDD = 5V

V

REF

1.5

INPUT RANGE = 2.56V

UPDATE RATE = 19.79Hz

T

A

RMS NOISE – V

1.0

0.5

700

600

500

400

300

OCCURRENCE

200

100

0

VDD = 5V

= 25C

T

A

V

DD

OSCILLATOR

3276732766 32768 3277032769

CODE

TPC 3. Noise Histogram

TIME BASE = 100ms/DIV

TRACE 1 = TRACE 2 = 2V/DIV

32771

0

1.0 3.02.52.01.5 3.5 5.04.54.0

V

– V

REF

TPC 2. RMS Noise vs. Reference Input

TPC 4. Typical Oscillator Power-Up

–10–

REV. A

Loading...

Loading...