Analog Devices AD7707 a Datasheet

3 V/5 V, ⴞ10 V Input Range, 1 mW

a

3-Channel 16-Bit, Sigma-Delta ADC

FEATURES

Charge Balancing ADC

16 Bits No Missing Codes

0.003% Nonlinearity

High Level (ⴞ10 V) and Low Level (ⴞ10 mV) Input

Channels

True Bipolar ⴞ100 mV Capability on Low Level Input

Channels Without Requiring Charge Pumps

Programmable Gain Front End

Gains from 1 to 128

Three-Wire Serial Interface

SPI™, QSPI™, MICROWIRE™ and DSP Compatible

Schmitt Trigger Input on SCLK

Ability to Buffer the Analog Input

2.7 V to 3.3 V or 4.75 V to 5.25 V Operation

Power Dissipation 1 mW max @ 3␣ V

Standby Current 8 A max

20-Lead SOIC and TSSOP Packages

GENERAL DESCRIPTION

The AD7707 is a complete analog front end for low frequency

measurement applications. This three-channel device can accept

either low level input signals directly from a transducer or high

level (±10 V) signals and produce a serial digital output. It

employs a sigma-delta conversion technique to realize up to

16 bits of no missing codes performance. The selected input

signal is applied to a proprietary programmable gain front end

based around an analog modulator. The modulator output is

processed by an on-chip digital filter. The first notch of this

digital filter can be programmed via an on-chip control register

allowing adjustment of the filter cutoff and output update rate.

The AD7707 operates from a single 2.7 V to 3.3 V or 4.75 V to

5.25 V supply. The AD7707 features two low level pseudodifferential analog input channels, one high level input channel

and a differential reference input. Input signal ranges of 0 mV to

+20 mV through 0 V to +2.5 V can be accommodated on both

low level input channels when operating with a V

of 5 V and a

DD

reference of 2.5 V. They can also handle bipolar input signal

ranges of ±20 mV through ±2.5 V, which are referenced to the

LCOM input. The AD7707, with a 3 V supply and a 1.225 V

reference, can handle unipolar input signal ranges of 0 mV to

+10 mV through 0 V to +1.225 V. Its bipolar input signal ranges

are ±10 mV through ±1.225 V.

The high level input channel can accept input signal ranges of

±10 V, ±5 V, 0 V to +10 V and 0 V to +5 V. The AD7707 thus

performs all signal conditioning and conversion for a threechannel system.

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corporation.

AD7707

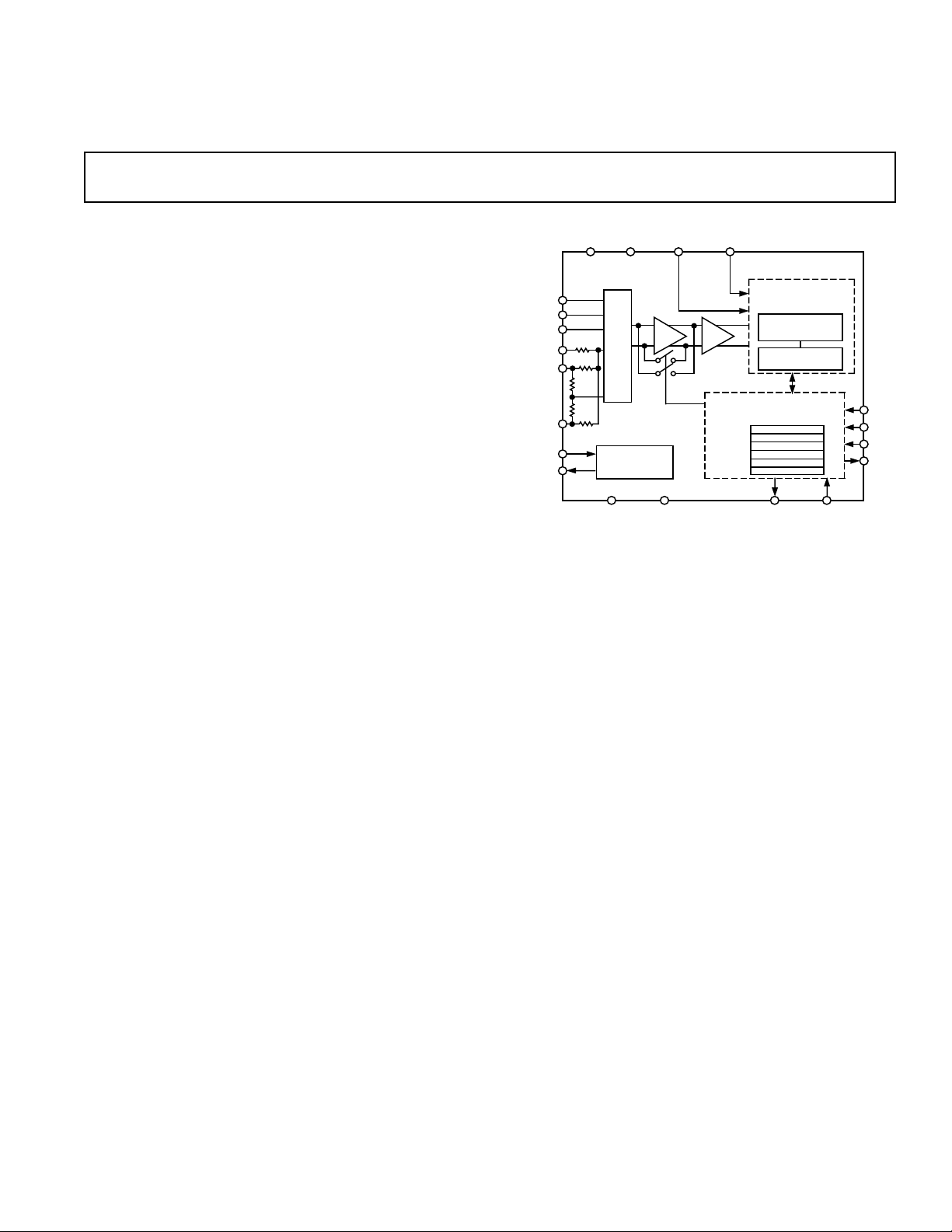

FUNCTIONAL BLOCK DIAGRAM

AV

DV

AIN1

AIN2

LOCOM

MCLK IN

MCLK OUT

AIN3

VBIAS

HICOM

30kV

5kV

5kV

15kV

30kV

The AD7707 is ideal for use in smart, microcontroller or DSPbased systems. It features a serial interface that can be configured for three-wire operation. Gain settings, signal polarity and

update rate selection can be configured in software using the

input serial port. The part contains self-calibration and system

calibration options to eliminate gain and offset errors on the

part itself or in the system.

CMOS construction ensures very low power dissipation, and the

power-down mode reduces the standby power consumption to

20␣ µW typ. These parts are available in a 20-lead wide body

(0.3 inch) small outline (SOIC) package and a low profile 20-lead

TSSOP.

PRODUCT HIGHLIGHTS

1. The AD7707 consumes less than 1 mW at 3 V supplies and

1␣ MHz master clock, making it ideal for use in low power

systems. Standby current is less than 8␣ µA.

2. On-chip thin-film resistors allow ±10 V, ±5 V, 0 V to +10 V

and 0 V to +5 V high level input signals to be directly accommodated on the analog inputs without requiring split supplies

or charge-pumps.

3. The low level input channels allow the AD7707 to accept

input signals directly from a strain gage or transducer removing a considerable amount of signal conditioning.

4. The part features excellent static performance specifications

with 16 bits, no missing codes, ±0.003% accuracy and low

rms noise. Endpoint errors and the effects of temperature

drift are eliminated by on-chip calibration options, which

remove zero-scale and full-scale errors.

DD

MUX

CLOCK

GENERATION

AGND

DD

REF IN(–) REF IN(+)

BUF

DGND

PGA

A = 1<128

SERIAL INTERFACE

REGISTER BANK

AD7707

CHARGE

BALANCING

A/D CONVERTER

S – D

MODULATOR

DIGITAL FILTER

DRDY RESET

SCLK

CS

DIN

DOUT

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

(AVDD = DVDD = +3 V or 5 V, REF IN(+) = +1.225␣ V with AVDD = 3 V and +2.5 V with AV

AD7707–SPECIFICATIONS

noted. All specifications T

Parameter B Version

STATIC PERFORMANCE

Low Level Input Channels (AIN1 and AIN2)

No Missing Codes 16 Bits min Guaranteed by Design. Filter Notch < 60 Hz

Output Noise See Tables I and III Depends on Filter Cutoffs and Selected Gain

Integral Nonlinearity

Unipolar Offset Error See Note 3

Unipolar Offset Drift

Bipolar Zero Error See Note 3

Bipolar Zero Drift

Positive Full-Scale Error

Full-Scale Drift

Gain Error

Gain Drift

Bipolar Negative Full-Scale Error

Bipolar Negative Full-Scale Drift

HIGH LEVEL INPUT CHANNEL (AIN3)

No Missing Codes 16 Bits min Guaranteed by Design. Filter Notch < 60␣ Hz

Output Noise See Tables IV and VI Depends on Filter Cutoffs and Selected Gain

Integral Nonlinearity

Unipolar Offset Error

Unipolar Offset Drift 4 µV/°C typ

Bipolar Zero Error

Bipolar Zero Drift 4 µV/°C typ For Gains 1, 2 and 4

Gain Error ±0.2 % typ Typically Within ±0.05%

Gain Drift 0.5 ppm of FSR/°C typ

Negative Full-Scale Error

LOW LEVEL ANALOG INPUTS/REFERENCE INPUTS Specifications for AIN and REF IN Unless Noted

Input Common-Mode Rejection (CMR)

AVDD = 5 V

Gain = 1 100 dB typ

Gain = 2 105 dB typ

Gain = 4 110 dB typ

Gain = 8 to 128 130 dB typ

AVDD = 3 V

Gain = 1 105 dB typ

Gain = 2 110 dB typ

Gain = 4 120 dB typ

Gain = 8 to 128 130 dB typ

Normal-Mode 50 Hz Rejection

Normal-Mode 60 Hz Rejection

Common-Mode 50 Hz Rejection

Common-Mode 60 Hz Rejection

Absolute/Common-Mode REF IN Voltage2AGND to AV

Absolute/Common-Mode AIN Voltage

AIN DC Input Current

AIN Sampling Capacitance

AIN Differential Voltage Range

AIN Input Sampling Rate, f

Reference Input Range

REF IN(+) – REF IN(–) Voltage 1/1.75 V min/max AVDD = 2.7 V to 3.3 V. V

REF IN(+) – REF IN(–) Voltage 1/3.5 V min/max AVDD = 4.75 V to 5.25 V. V

REF IN Input Sampling Rate, f

±100 mV INPUT RANGE Low Level Input Channels, (AIN1 and AIN2)

2

INL

Input Common-Mode Rejection (CMR)280 dB typ

Power Supply Rejection (PSR)

4

4, 6

7

4, 8

9

to T

MIN

2

4

unless otherwise noted.)

MAX

±0.003 % of FSR max Filter Notch < 60␣ Hz. Typically ±0.0003%

0.5 µV/°C typ

0.5 µV/°C typ For Gains 1, 2 and 4

5

0.1 µV/°C typ For Gains 8, 16, 32, 64 and 128

See Note 3

0.5 µV/°C typ

See Note 3

2

4

0.5 ppm of FSR/°C typ

±0.003 % of FSR max Typically ±0.0007%

1 µV/°C typ For Gains of 1 to 4

0.6 µV/°C typ For Gains of 8 to 128

2

9

±0.003 % of FSR max Filter Notch < 60␣ Hz. Typically ±0.0003%

±10 mV max Typically Within ±1.5 mV

±10 mV max Typically Within ±1.5 mV

1 µV/°C typ For Gains 8, 16, 32, 64 and 128

2

2

2

2

2

±0.0012 % of FSR typ

2

98 dB typ For Filter Notches of 10 Hz, 25 Hz, 50 Hz, ±0.02 × f

98 dB typ For Filter Notches of 10 Hz, 20 Hz, 60 Hz, ±0.02 × f

150 dB typ For Filter Notches of 10 Hz, 25 Hz, 50 Hz, ±0.02 × f

150 dB typ For Filter Notches of 10 Hz, 20 Hz, 60 Hz, ±0.02 × f

2, 10

AGND – 100 mV V min BUF Bit of Setup Register = 0

AVDD + 30␣ mV V max

AGND + 50␣ mV V min BUF Bit of Setup Register = 1

2

2

11

S

S

AVDD – 1.5␣ V V max

1 nA max

10 pF max BUF = 0

0 to +V

±V

REF

GAIN × f

f

CLKIN

f

CLKIN

±0.003 % of FSR max Filter Notch < 60 Hz

2

90 dB typ

= 5 V; REF␣ IN(–) = GND; VBIAS = REFIN(+); MCLK IN = 2.4576␣ MHz unless otherwise

1

DD

/GAIN12nom Unipolar Input Range (B/U Bit of Setup Register = 1)

REF

/GAIN nom Bipolar Input Range (B/U Bit of Setup Register = 0)

CLKIN

/8 For Gains of 8 to 128

/64

Units Conditions/Comments

Low Level Input Channels, AIN1 and AIN2

V min to V max

/64 For Gains of 1 to 4

Specified Performance

Specified Performance

Gain = 16, Unbuffered Mode

= 1.225 V ± 1% for

REF

= 2.5 V ± 1% for

REF

DD

NOTCH

NOTCH

NOTCH

NOTCH

–2–

REV. A

Parameter B Version

1

Units Conditions/Comments

HIGH LEVEL ANALOG INPUT CHANNEL (AIN3) AIN3 is with respect to HICOM.

AIN3 Voltage Range +10 V max

–10 V min

Normal Mode 50 Hz Rejection 78 dB typ For Filter Notches of 10 Hz, 25 Hz, 50 Hz, ± 0.02 × f

Normal Mode 60 Hz Rejection 78 dB typ For Filter Notches of 10 Hz, 20 Hz, 60 Hz, ± 0.02 × f

AIN3 Input Sampling Rate, f

AIN3 Input Impedance

AIN3 Sampling Capacitance

S

2

2

VBIAS Input Range 0 V/AV

GAIN × f

f

CLKIN

/64 For Gains of 1 to 4

CLKIN

/8 For Gains of 8 to 128

27 kΩ min Typically 30 kΩ ±10%; Typical Resistor Tempco is –30 ppm/°C

10 pF max

DD

V min/max Typically = REFIN(+) = 2.5 V

LOGIC INPUTS

Input Current

All Inputs Except MCLK IN ±1 µA max Typically ±20 nA

MCLK ±10 µA max Typically ±2 µA

All Inputs Except SCLK and MCLK IN

V

, Input Low Voltage 0.8 V max DVDD = 5 V

INL

0.4 V max DVDD = 3 V

V

, Input High Voltage 2.0 V min DVDD = 3 V and 5 V

INH

SCLK Only (Schmitt Triggered Input) DVDD = 5 V Nominal

V

T+

V

T–

VT+ – V

T–

1.4/3 V min/V max

0.8/1.4 V min/V max

0.4/0.8 V min/V max

SCLK Only (Schmitt Triggered Input) DVDD = 3 V Nominal

V

T+

V

T–

VT+ – V

T–

1/2.5 V min/V max

0.4/1.1 V min/V max

0.375/0.8 V min/V max

MCLK IN Only DVDD = 5 V Nominal

V

, Input Low Voltage 0.8 V max

INL

V

, Input High Voltage 3.5 V min

INH

MCLK IN Only DVDD = 3 V Nominal

V

, Input Low Voltage 0.4 V max

INL

V

, Input High Voltage 2.5 V min

INH

LOGIC OUTPUTS (Including MCLK OUT)

VOL, Output Low Voltage 0.4 V max I

0.4 V max I

VOH, Output High Voltage 4 V min I

DVDD – 0.6 V min I

Floating State Leakage Current ±10 µA max

Floating State Output Capacitance

14

9 pF typ

= 800␣ µA Except for MCLK OUT.

SINK

= 100␣ µA Except for MCLK OUT.

SINK

= 200 µA Except for MCLK OUT.

SOURCE

= 100␣ µA Except for MCLK OUT.

SOURCE

13

DVDD = 5 V

13

DVDD = 3 V

13

13

Data Output Coding Binary Unipolar Mode

Offset Binary Bipolar Mode

SYSTEM CALIBRATION

Low Level Input Channels (AIN1 and AIN2)

Positive Full-Scale Calibration Limit

Negative Full-Scale Calibration Limit

Offset Calibration Limit

Input Span

16

16

High Level Input Channels (AIN3)

Positive Full-Scale Calibration Limit

Negative Full-Scale Calibration Limit

Offset Calibration Limit

Input Span

16

16

15

15

15

15

(1.05 × V

– (1.05 × V

– (1.05 × V

(0.8 × V

REF

(2.1 × V

REF

(8.4 × V

REF

– (8.4 × V

– (8.4 × V

(6.4 × V

REF

(16.8 × V

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

REF

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

REF

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

REF

)/GAIN V min GAIN Is The Selected PGA Gain (1 to 128)

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

REF

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

REF

)/GAIN V min GAIN Is The Selected PGA Gain (1 to 128)

)/GAIN V max GAIN Is The Selected PGA Gain (1 to 128)

REF

POWER REQUIREMENTS

Power Supply Voltages

AVDD Voltage +2.7 to +3.3 or

+4.75 to +5.25 V For Specified Performance

DVDD Voltage +2.7 to +5.25 V For Specified Performance

Power Supply Currents

AVDD Current AVDD = 3␣ V or 5␣ V. Gain = 1 to 4

0.27 mA max Typically 0.22 mA. BUF = 0. f

CLK IN

= 1 MHz

or 2.4576␣ MHz

0.6 mA max Typically 0.45 mA. BUF = 1. f

CLK IN

= 1 MHz

or 2.4576 MHz

AVDD = 3 V or 5␣ V. Gain = 8 to 128

0.5 mA max Typically 0.38␣ mA. BUF = 0. f

1.1 mA max Typically 0.81␣ mA. BUF = 1. f

= 2.4576␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

AD7707

NOTCH

NOTCH

DVDD = 5 V

DVDD = 3 V

REV. A –3–

AD7707–SPECIFICATIONS

Parameter B Version

POWER REQUIREMENTS (Continued)

DVDD Current

17

0.080 mA max Typically 0.06␣ mA. DVDD = 3␣ V. f

0.15 mA max Typically 0.13 mA. DVDD = 5␣ V. f

0.18 mA max Typically 0.15␣ mA. DVDD = 3␣ V. f

Power Supply Rejection

Normal Mode Power Dissipation

19

17

0.35 mA max Typically 0.3␣ mA. DVDD = 5␣ V. f

See Note 20 dB typ

1

Units Conditions/Comments

Digital I/Ps = 0␣ V or DVDD. External MCLK IN

= 1␣ MHz

CLK IN

= 1␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

= 2.4576␣ MHz

CLK IN

AVDD = DVDD = +3 V. Digital I/Ps = 0 V or DVDD.

External MCLK IN Excluding Dissipation in the AIN3

Attenuator

1.05 mW max Typically 0.84 mW. BUF = 0. f

2.04 mW max Typically 1.53 mW. BUF = 1. f

1.35 mW max Typically 1.11 mW. BUF = 0. f

= 1␣ MHz, All Gains.

CLK IN

= 1␣ MHz, All Gains.

CLK IN

= 2.4576 MHz,

CLK IN

Gain = 1 to 4.

Normal Mode Power Dissipation

17

2.34 mW max Typically 1.9 mW. BUF = 1. f

Gain = 1 to 4.

AVDD = DVDD = +5 V. Digital I/Ps = 0␣ V or DVDD.

= 2.4576 MHz,

CLK IN

External MCLKIN

Standby (Power-Down) Current

18

2.1 mW max Typically 1.75 mW. BUF = 0. f

3.75 mW max Typically 2.9 mW. BUF = 1. f

3.1 mW max Typically 2.6 mW. BUF = 0. f

4.75 mW max Typically 3.75 mW. BUF = 1. f

18 µA max External MCLK IN = 0 V or DVDD. Typically 9␣ µA.

= 1␣ MHz, All Gains.

CLK IN

= 1␣ MHz, All Gains.

CLK IN

= 2.4576 MHz.

CLK IN

= 2.4576 MHz.

CLK IN

AVDD = +5 V

8 µA max External MCLK IN = 0 V or DVDD. Typically 4␣ µA.

AVDD = +3 V␣

NOTES

1

Temperature range as follows: B Version, –40°C to +85°C.

2

These numbers are established from characterization or design at initial product release.

3

A calibration is effectively a conversion so these errors will be of the order of the conversion noise shown in Tables I and III for the low level input channels AIN1

and AIN2. This applies after calibration at the temperature of interest.

4

Recalibration at any temperature will remove these drift errors.

5

Positive full-scale error includes zero-scale errors (unipolar offset error or bipolar zero error) and applies to both unipolar and bipolar input ranges.

6

Full-scale drift includes zero-scale drift (unipolar offset drift or bipolar zero drift) and applies to both unipolar and bipolar input ranges.

7

Gain error does not include zero-scale errors. It is calculated as full-scale error–unipolar offset error for unipolar ranges and full-scale error–bipolar zero error for

bipolar ranges.

8

Gain error drift does not include unipolar offset drift/bipolar zero drift. It is effectively the drift of the part if zero scale calibrations only were performed.

9

Error is removed following a system calibration.

10

This common-mode voltage range is allowed provided that the input voltage on analog inputs does not go more positive than AVDD + 30 mV or go more negative

than AGND – 100␣ mV. Parts are functional with voltages down to AGND – 200 mV, but with increased leakage at high temperature.

11

The analog input voltage range on AIN(+) is given here with respect to the voltage on LCOM on the low level input channels (AIN1 and AIN2) and is given with

respect to the HCOM input on the high level input channel AIN3. The absolute voltage on the low level analog inputs should not go more positive than AV

100␣ mV, or go more negative than GND␣ – 100␣ mV for specified performance. Input voltages of AGND – 200 mV can be accommodated, but with increased leakage

at high temperature.

12

V

= REF IN(+) – REF IN(–).

REF

13

These logic output levels apply to the MCLK OUT only when it is loaded with one CMOS load.

14

Sample tested at +25°C to ensure compliance.

15

After calibration, if the analog input exceeds positive full scale, the converter will output all 1s. If the analog input is less than negative full scale, the device will

output all 0s.

16

These calibration and span limits apply provided the absolute voltage on the analog inputs does not exceed AVDD + 30␣ mV or go more negative than AGND –

30␣ mV. The offset calibration limit applies to both the unipolar zero point and the bipolar zero point.

17

When using a crystal or ceramic resonator across the MCLK pins as the clock source for the device, the DVDD current and power dissipation will vary depending on

the crystal or resonator type (see Clocking and Oscillator Circuit section).

18

If the external master clock continues to run in standby mode, the standby current increases to 150␣ µA typical at 5 V and 75 µA at 3 V. When using a crystal or

ceramic resonator across the MCLK pins as the clock source for the device, the internal oscillator continues to run in standby mode and the power dissipation

depends on the crystal or resonator type (see Standby Mode section).

19

Measured at dc and applies in the selected passband. PSRR at 50␣ Hz will exceed 120␣ dB with filter notches of 25 Hz or 50␣ Hz. PSRR at 60␣ Hz will exceed 120␣ dB

with filter notches of 20 Hz or 60␣ Hz.

20

PSRR depends on both gain and AVDD.

Low Level Input Channels, AIN1 and AIN2 High Level Input Channel, AIN3

Gain 1 2 4 8–128 Gain 1 2 4 8–128

= 3 V 86 78 85 93 AVDD = 3 V68606775

AV

DD

AVDD = 5 V 90 78 84 91 AVDD = 5 V72606673

Specifications subject to change without notice.

DD

+

–4–

REV. A

AD7707

TIMING CHARACTERISTICS

(AVDD = DVDD = +2.7 V TO +5.25 V, AGND = DGND = 0 V; f

1, 2

Logic = 0, Logic 1 = DVDD unless otherwise noted.)

= 2.4576 MHz; Input

CLKIN

Limit at

T

, T

MIN

MAX

Parameter (B Version) Units Conditions/Comments

f

CLKIN

3, 4

400 kHz min Master Clock Frequency: Crystal Oscillator or Externally Supplied for

5 MHz max Specified Performance

t

CLKIN LO

t

CLKIN HI

t

1

t

2

0.4 × t

CLKIN

0.4 × t

CLKIN

500 × t

CLKIN

100 ns min RESET Pulsewidth

ns min Master Clock Input Low Time. t

CLKIN

ns min Master Clock Input High Time

ns nom DRDY High Time

= 1/f

CLKIN

Read Operation

t

3

t

4

5

t

5

t

6

t

7

t

8

6

t

9

t

10

0 ns min DRDY to CS Setup Time

120 ns min CS Falling Edge to SCLK Rising Edge Setup Time

0 ns min SCLK Falling Edge to Data Valid Delay

80 ns max DV

100 ns max DV

= +5␣ V

DD

= +3.0␣ V

DD

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Rising Edge Hold Time

10 ns min Bus Relinquish Time after SCLK Rising Edge

60 ns max DV

100 ns max DV

100 ns max SCLK Falling Edge to DRDY High

= +5␣ V

DD

= +3.0␣ V

DD

7

Write Operation

t

11

t

12

t

13

t

14

t

15

t

16

NOTES

1

Sample tested at +25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of DV

2

See Figures 16 and 17.

3

f

Duty Cycle range is 45% to 55%. f

CLKIN

draw higher current than specified and possibly become uncalibrated.

4

The AD7707 is production tested with f

5

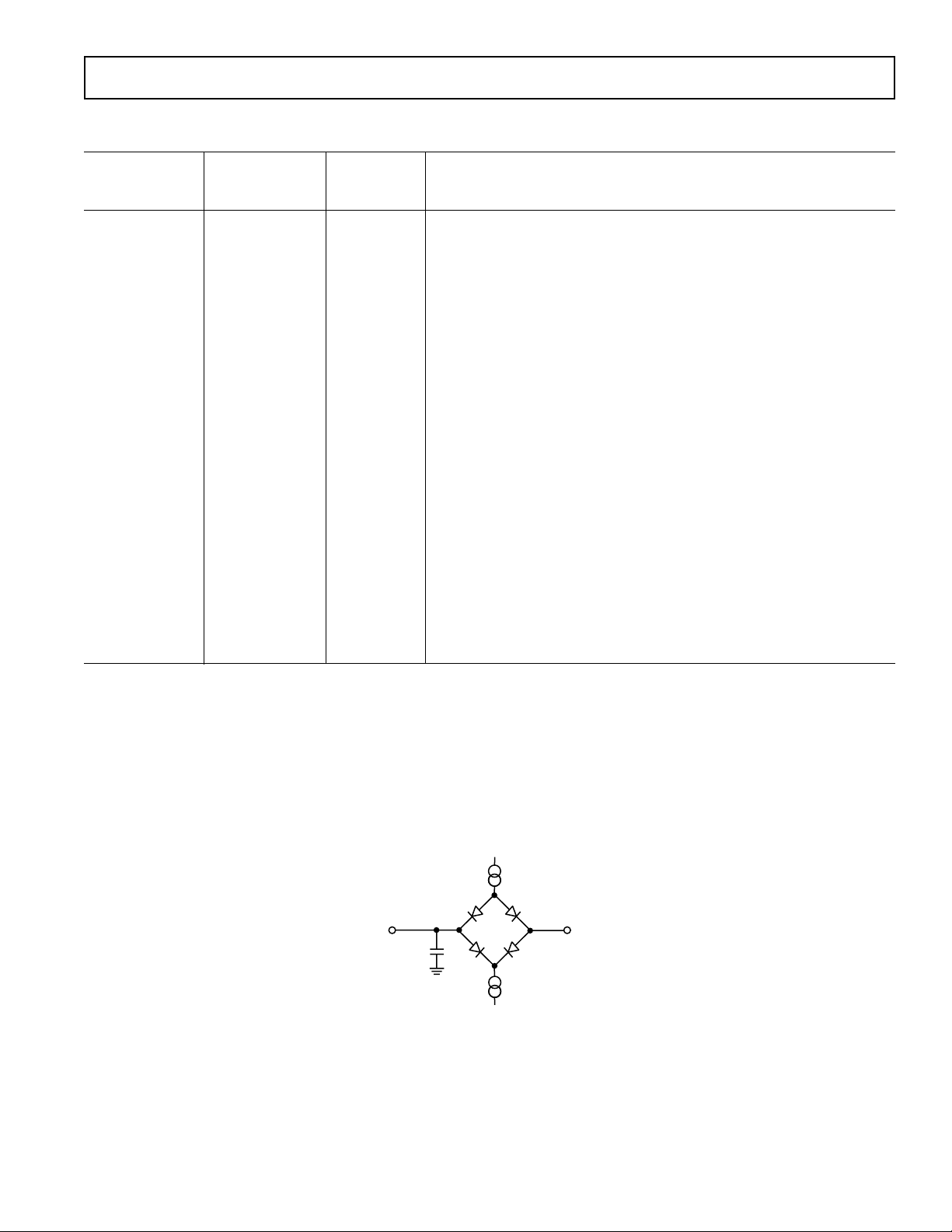

These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross the VOL or VOH limits.

6

These numbers are derived from the measured time taken by the data output to change 0.5␣ V when loaded with the circuit of Figure 1. The measured number is then

extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus

relinquish times of the part and as such are independent of external bus loading capacitances.

7

DRDY returns high after the first read from the device after an output update. The same data can be read again, if required, while DRDY is high, although care

should be taken that subsequent reads do not occur close to the next output update.

120 ns min CS Falling Edge to SCLK Rising Edge Setup Time

30 ns min Data Valid to SCLK Rising Edge Setup Time

20 ns min Data Valid to SCLK Rising Edge Hold Time

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Rising Edge Hold Time

) and timed from a voltage level of 1.6 V.

DD

must be supplied whenever the AD7707 is not in Standby mode. If no clock is present in this case, the device can

CLKIN

at 2.4576␣ MHz (1␣ MHz for some IDD tests). It is guaranteed by characterization to operate at 400␣ kHz.

CLKIN

REV. A

TO OUTPUT

PIN

50pF

(800mA AT V

I

SINK

100mA AT V

I

(200mA AT VDD = +5V

SOURCE

100mA AT V

DD

+1.6V

DD

= +5V

= +3V)

= +3V)

DD

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

–5–

AD7707

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

(T

= +25°C unless otherwise noted)

A

AVDD to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

AV

to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

DV

DD

DV

to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7␣ V

DD

AV

to DVDD . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7 V

DD

DGND to AGND . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +0.3␣ V

AIN1, AIN2 Input Voltage to

LOCOM . . . . . . . . . . . . . . . . . . . . –0.3 V to AV

+ 0.3␣ V

DD

AIN3 Input Voltage to HICOM . . . . . . . . . . . –11 V to +30␣ V

VBIAS to AGND . . . . . . . . . . . . . . . . –0.3 V to AV

HICOM, LOCOM to AGND . . . . . . –0.3 V to AV

REF(+), REF(–) to AGND . . . . . . . . –0.3 V to AV

Digital Input Voltage to DGND . . . . –0.3 V to DV

Digital Output Voltage to DGND . . . –0.3 V to DV

+ 0.3␣ V

DD

+ 0.3␣ V

DD

+ 0.3␣ V

DD

+ 0.3 V

DD

+ 0.3 V

DD

Operating Temperature Range

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

SOIC Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 75°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

TSSOP Package, Power Dissipation . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 139°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C

␣␣␣␣ Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 kV

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

Industrial (B Version) . . . . . . . . . . . . . . . . –40°C to +85°C

ORDERING GUIDE

V

DD

Temperature Package Package

Model Supply Range Description Options

AD7707BR 2.7 V to 5.25 V –40°C to +85°C SOIC R-20

AD7707BRU 2.7 V to 5.25 V –40°C to +85°C TSSOP RU-20

EVAL-AD7707EB Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7707 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–6–

REV. A

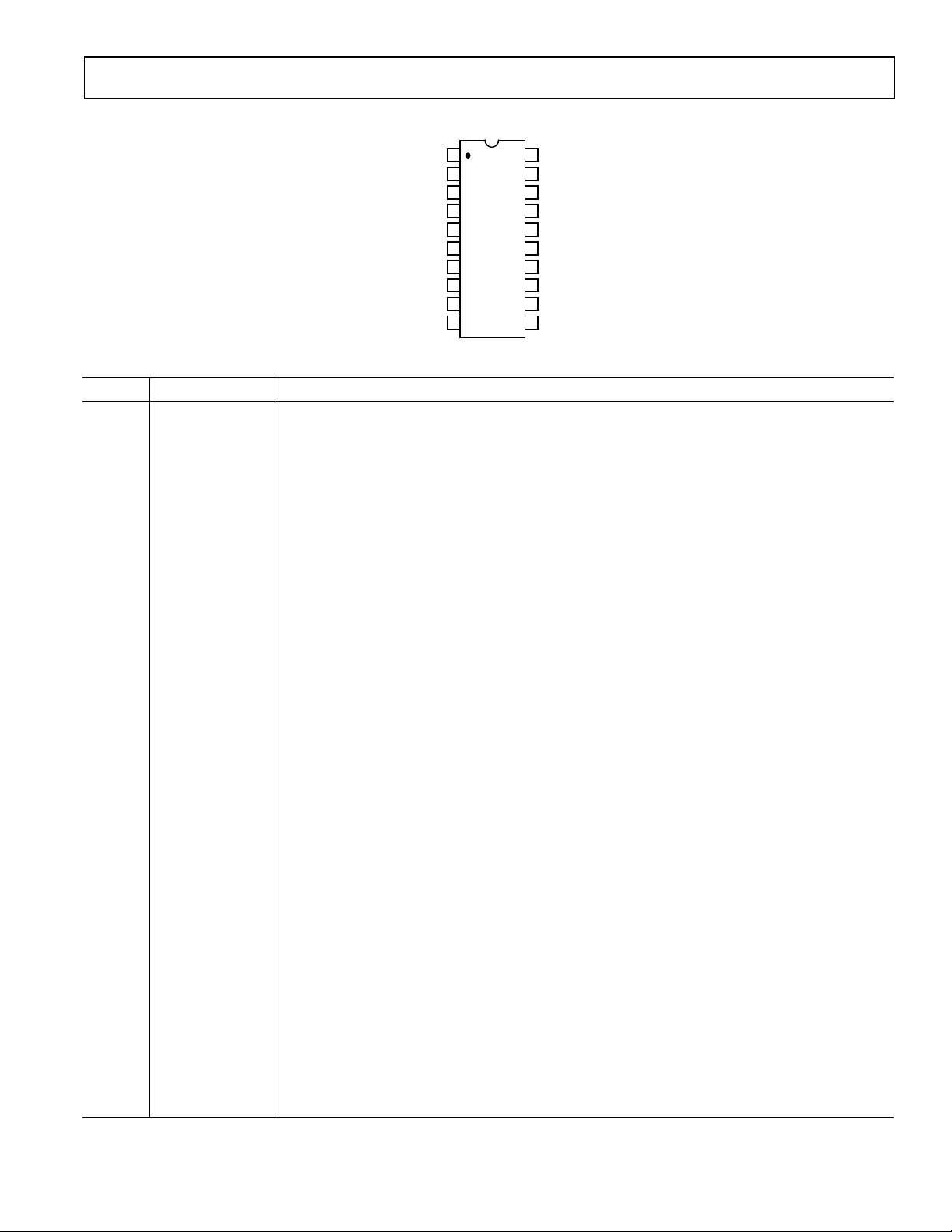

PIN CONFIGURATION

AD7707

SCLK

MCLK IN

MCLK OUT

CS

RESET

AV

DD

AIN1

LOCOM

AIN2

AIN3

1

2

3

4

5

AD7707

TOP VIEW

6

(Not to Scale)

7

8

9

10

20

DGND

19

DV

18

DIN

17

DOUT

16

DRDY

15

AGND

14

REF IN(–)

13

REF IN(+)

12

VBIAS

11

HICOM

DD

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1 SCLK Serial Clock. Schmitt-Triggered Logic Input. An external serial clock is applied to this input to

access serial data from the AD7707. This serial clock can be a continuous clock with all data

transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with

the information being transmitted to the AD7707 in smaller batches of data.

2 MCLK IN Master Clock signal for the device. This can be provided in the form of a crystal/resonator or

external clock. A crystal/resonator can be tied across the MCLK IN and MCLK OUT pins.

Alternatively, the MCLK IN pin can be driven with a CMOS-compatible clock and MCLK

OUT left unconnected. The part can be operated with clock frequencies in the range 500 kHz to

5 MHz.

3 MCLK OUT When the master clock for the device is a crystal/resonator, the crystal/resonator is connected

between MCLK IN and MCLK␣ OUT. If an external clock is applied to MCLK IN, MCLK

OUT provides an inverted clock signal. This clock can be used to provide a clock source for

external circuitry and is capable of driving one CMOS load. If the user does not require it, this

MCLK OUT can be turned off via the CLK DIS bit of the Clock Register. This ensures that the

part is not wasting unnecessary power driving capacitive loads on MCLK OUT.

4 CS Chip Select. Active low Logic Input used to select the AD7707. With this input hard-wired low,

the AD7707 can operate in its three-wire interface mode with SCLK, DIN and DOUT used to

interface to the device. CS can be used to select the device in systems with more than one device

on the serial bus or as a frame synchronization signal in communicating with the AD7707.

5 RESET Logic Input. Active low input that resets the control logic, interface logic, calibration coeffi-

cients, digital filter and analog modulator of the part to power-on status.

6AV

DD

Analog Supply Voltage, +2.7 V to +5.25 V operation.

7 AIN1 Low Level Analog Input Channel 1. This is used as a pseudo-differential input with respect to

LOCOM.

8 LOCOM COMMON Input for low level input channels. Analog inputs on AIN1 and AIN2 must be refer-

enced to this input.

9 AIN2 Low Level Analog Input Channel 2. This is used as a pseudo-differential input with respect to

LOCOM.

10 AIN3 Single-Ended High Level Analog Input Channel with respect to HICOM.

11 HICOM COMMON Input for high level input channel. Analog input on AIN3 must be referenced to

this input.

12 VBIAS VBIAS is used to level shift the high level input channel signal. This signal is used to ensure that

the AIN(+) and AIN(–) signals seen by the internal modulator are within its common-mode

range. VBIAS is normally connected to 2.5 V when AV

= 5 V and 1.225 V when AVDD = 3 V.

DD

13 REF IN(+) Reference Input. Positive input of the differential reference input to the AD7707. The reference

input is differential with the provision that REF IN(+) must be greater than REF IN(–).

REF␣ IN(+) can lie anywhere between AVDD and AGND.

REV. A

–7–

AD7707

Pin No. Mnemonic Function

14 REF IN(–) Reference Input. Negative input of the differential reference input to the AD7707. The

REF␣ IN(–) can lie anywhere between AVDD and AGND provided REF␣ IN(+) is greater than

REF␣ IN(–).

15 AGND Analog Ground. Ground reference point for the AD7707’s internal analog circuitry.

16 DRDY Logic Output. A logic low on this output indicates that a new output word is available from the

AD7707 data register. The DRDY pin will return high upon completion of a read operation of a

full output word. If no data read has taken place between output updates, the DRDY line will

return high for 500 × t

operation should neither be attempted nor in progress to avoid reading from the data register as

it is being updated. The DRDY line will return low again when the update has taken place.

DRDY is also used to indicate when the AD7707 has completed its on-chip calibration

sequence.

17 DOUT Serial Data Output with serial data being read from the output shift register on the part. This

output shift register can contain information from the setup register, communications register,

clock register or data register, depending on the register selection bits of the Communications

Register.

18 DIN Serial Data Input with serial data being written to the input shift register on the part. Data from

this input shift register is transferred to the setup register, clock register or communications

register, depending, on the register selection bits of the Communications Register.

19 DV

DD

Digital Supply Voltage, +2.7 V to +5.25 V operation.

20 DGND Ground reference point for the AD7707’s internal digital circuitry.

cycles prior to the next output update. While DRDY is high, a read

CLK␣ IN

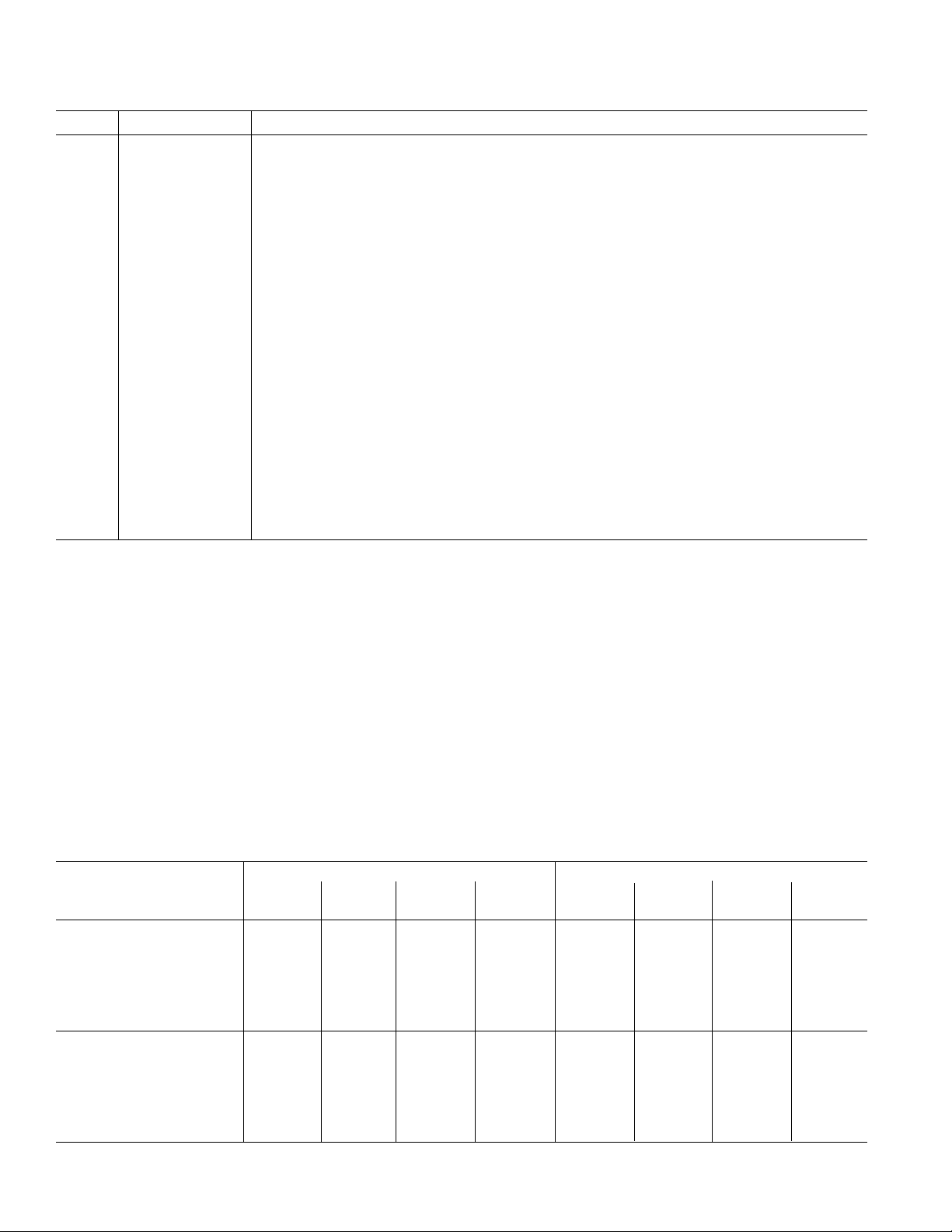

OUTPUT NOISE FOR LOW LEVEL INPUT CHANNELS (5 V OPERATION)

Table I shows the AD7707 output rms noise and peak-to-peak resolution in unbuffered mode for the selectable notch and –3␣ dB

frequencies for the part, as selected by FS0, FS1 and FS2 of the Clock Register. The numbers given are for the bipolar input ranges

with a V

of +2.5␣ V and AVDD = 5 V. These numbers are typical and are generated at an analog input voltage of 0 V. Table II

REF

shows the rms noise and peak-to-peak resolution when operating in unbuffered mode. It is important to note that the peak-to-peak num-

bers represent the resolution for which there will be no code flicker. They are not calculated based on rms noise but on peak-to-peak noise. The

numbers given are for bipolar input ranges with a V

of +2.5 V. These numbers are typical and are rounded to the nearest LSB.

REF

The numbers apply for the CLK DIV bit of the Clock Register set to 0. The output noise comes from two sources. The first is the

electrical noise in the semiconductor devices (device noise) used in the implementation of the modulator. Secondly, when the analog

input is converted into the digital domain, quantization noise is added. The device noise is at a low level and is independent of frequency. The quantization noise starts at an even lower level but rises rapidly with increasing frequency to become the dominant noise

source. The numbers in the tables are given for the bipolar input ranges. For the unipolar ranges the rms noise numbers will be the

same as the bipolar range but the peak-to-peak resolution is now based on half the signal range which effectively means losing 1 bit of

resolution.

Table I. Output RMS Noise/Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +5 V

AIN1 and AIN2 Unbuffered Mode Only

Filter First Typical Output RMS Noise in V (Peak-to-Peak Resolution in Bits)

Notch and O/P –3␣ dB Gain of Gain of Gain of Gain of Gain of Gain of Gain of Gain of

Data Rate Frequency 1 2 4 8 16 32 64 128

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 1.2 (16) 0.7 (16) 0.7 (16) 0.54 (16) 0.28 (16) 0.28 (16) 0.28 (15.5) 0.27 (14.5)

50␣ Hz 13.1␣ Hz 3.6 (16) 2.1 (16) 1.25 (16) 0.89 (16) 0.62 (16) 0.60 (15.5) 0.56 (14.5) 0.56 (13.5)

60␣ Hz 15.72␣ Hz 4.7 (16) 2.6 (16) 1.5 (16) 0.94 (16) 0.73 (16) 0.68 (15.5) 0.66 (14.5) 0.63 (13.5)

250␣ Hz 65.5␣ Hz 95 (13) 65 (13) 23.4 (13) 11.6 (13) 6.5 (13) 3.4 (13) 2.1 (12.5) 1.5 (12)

500␣ Hz 131␣ Hz 600 (10.5) 316 (10.5) 138 (10.5) 71 (10.5) 38 (10.5) 18 (10.5) 10 (10) 5.7 (10)

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 1.19 (16) 0.69 (16) 0.71 (16) 0.63 (16) 0.27 (16) 0.27 (16) 0.26 (15.5) 0.24 (15)

20␣ Hz 5.24␣ Hz 3.68 (16) 2.18 (16) 1.19 (16) 0.94 (16) 0.6 (16) 0.6 (15.5) 0.56 (14.5) 0.56 (13.5)

25␣ Hz 6.55␣ Hz 4.78 (16) 2.66 (16) 1.51 (16) 1.07 (16) 0.7 (16) 0.67 (15.5) 0.66 (14.5) 0.65 (13.5)

100␣ Hz 26.2␣ Hz 100 (13) 50.1 (13) 23.5 (13) 11.9 (13) 5.83 (13) 3.64 (13) 2.16 (12.5) 1.5 (12)

200␣ Hz 52.5␣ Hz 543 (10.5) 318 (10.5) 132 (10.5) 68.1 (10.5) 33.1 (10.5) 17.6 (10.5) 9.26 (10.5) 6.13 (10)

–8–

REV. A

AD7707

Table II. Output RMS Noise/Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +5 V

AIN1 and AIN2 Buffered Mode Only

Filter First Typical Output RMS Noise in V (Peak-to-Peak Resolution in Bits)

Notch and O/P –3␣ dB Gain of Gain of Gain of Gain of Gain of Gain of Gain of Gain of

Data Rate Frequency 1 248163264128

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 1.47 (16) 0.95 (16) 0.88 (16) 0.55 (16) 0.42 (16) 0.42 (16) 0.42 (15) 0.41 (14)

50␣ Hz 13.1␣ Hz 4.2 (16) 2.6 (16) 1.6 (16) 1 (16) 0.89 (15.5) 0.94 (15) 0.9 (14) 0.9 (13)

60␣ Hz 15.72␣ Hz 4.9 (16) 3 (16) 1.8 (16) 1.1 (16) 1 (15.5) 1 (14.5) 0.94 (14) 0.94 (13)

250␣ Hz 65.5␣ Hz 104 (13) 52 (13) 26 (13) 14 (13) 6.5 (13) 4.1 (12.5) 2.7 (12.5) 2.3 (11.5)

500␣ Hz 131␣ Hz 572 (10.5) 293 (10.5) 125 (10.5) 69 (10.5) 40 (10.5) 19 (10.5) 10 (10.5) 5.9 (10)

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 1.48 (16) 8.95 (16) 0.87 (16) 0.67 (16) 0.41 (16) 0.40 (16) 0.40 (15) 0.40 (14)

20␣ Hz 5.24␣ Hz 3.9 (16) 2.46 (16) 1.77 (16) 1.19 (16) 0.94 (16) 0.93 (15) 0.95 (14) 0.9 (13)

25␣ Hz 6.55␣ Hz 5.37 (16) 3.05 (16) 1.89 (16) 1.33 (16) 1.11 (15.5) 1.06 (14.5) 1.04 (13.5) 1.02 (12.5)

100␣ Hz 26.2␣ Hz 98.9 (13) 52.4 (13) 26.1 (13) 12.7 (13) 6.08 (13) 4.01 (12.5) 2.62 (12.5) 2.33 (11.5)

200␣ Hz 52.4␣ Hz 596 (10.5) 298 (10.5) 133 (10.5) 69.3 (10.5) 34.7 (10.5) 16.9 (10.5) 9.67 (10.5) 6.34 (10)

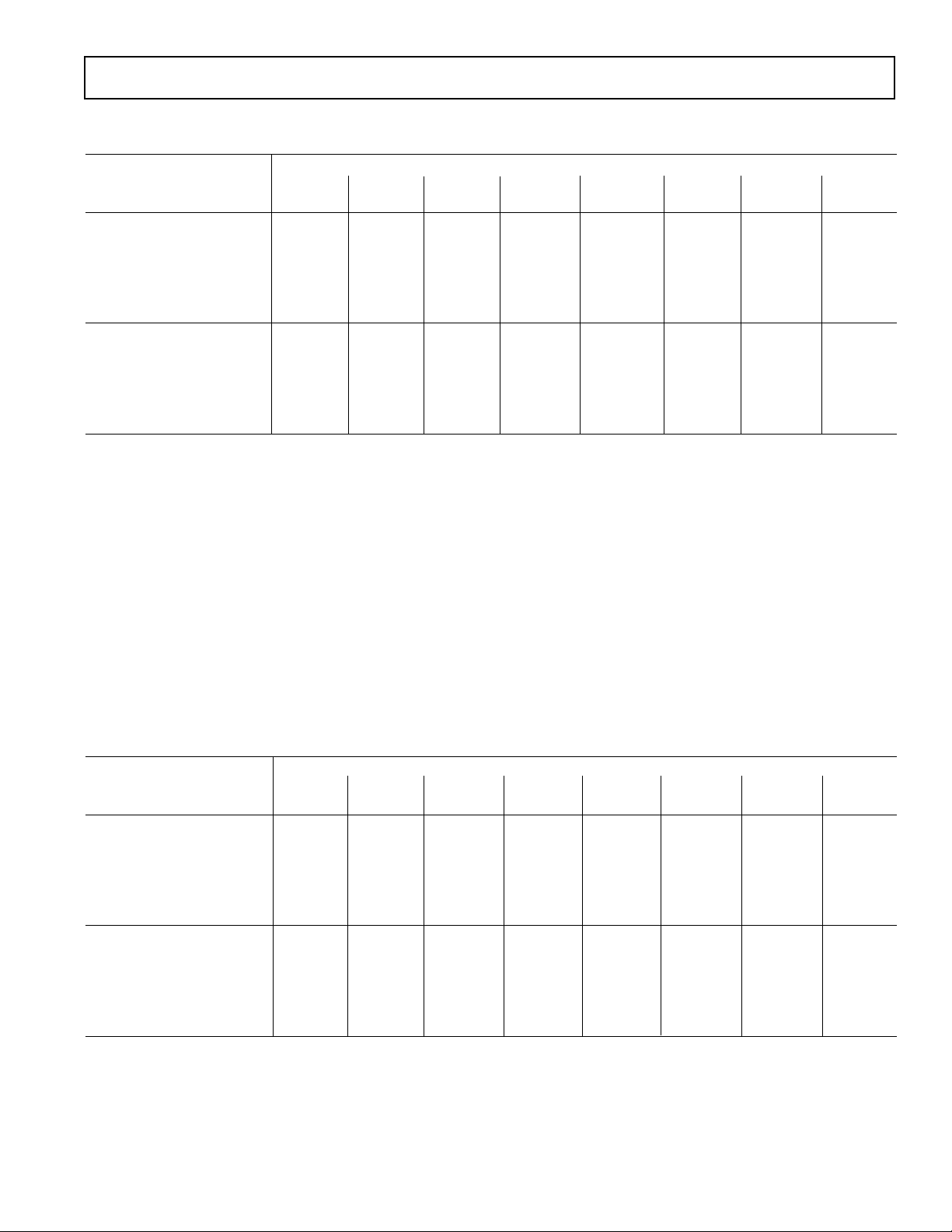

OUTPUT NOISE FOR LOW LEVEL INPUT CHANNELS (3 V OPERATION)

Table III shows the AD7707 output rms noise and peak-to-peak resolution in unbuffered mode for the selectable notch and –3␣ dB

frequencies for the part, as selected by FS0, FS1 and FS2 of the Clock Register. The numbers given are for the bipolar input ranges

with a V

IV shows the rms noise and peak-to-peak resolution when operating in unbuffered mode. It is important to note that the peak-to-peak

numbers represent the resolution for which there will be no code flicker. They are not calculated based on rms noise but on peak-to-peak noise.

The numbers given are for bipolar input ranges with a V

are typical and are rounded to the nearest LSB. The numbers apply for the CLK DIV bit of the Clock Register set to 0. The first is

the electrical noise in the semiconductor devices (device noise) used in the implementation of the modulator. Secondly, when the

analog input is converted into the digital domain, quantization noise is added. The device noise is at a low level and is independent of

frequency. The quantization noise starts at an even lower level but rises rapidly with increasing frequency to become the dominant

noise source. The numbers in the tables are given for the bipolar input ranges. For the unipolar ranges the rms noise numbers will be

the same as the bipolar range but the peak-to-peak resolution is now based on half the signal range which effectively means losing

1 bit of resolution.

of +1.225␣ V and an AVDD = 3 V. These numbers are typical and are generated at an analog input voltage of 0 V. Table

REF

of +1.225 V and for either buffered or unbuffered mode. These numbers

REF

Table III. Output RMS Noise/Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +3 V

AIN1 and AIN2 Unbuffered Mode Only

Filter First Typical Output RMS Noise in V (Peak-to-Peak Resolution in Bits)

Notch and O/P –3␣ dB Gain of Gain of Gain of Gain of Gain of Gain of Gain of Gain of

Data Rate Frequency 1 248163264128

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 1.60 (16) 0.8 (16) 0.48 (16) 0.29 (16) 0.29 (16) 0.27 (15.5) 0.26 (14.5) 0.26 (13.5)

50␣ Hz 13.1␣ Hz 3.8 (16) 1.9 (16) 1.1 (16) 0.64 (16) 0.60 (15.5) 0.6 (14.5) 0.6 (13.5) 0.6 (12.5)

60␣ Hz 15.72␣ Hz 4.4 (16) 2.2 (16) 1.35 (16) 0.78 (16) 0.7 (15) 0.68 (14.5) 0.64 (13.5) 0.64 (12.5)

250␣ Hz 65.5␣ Hz 53 (13) 24 (13) 15 (13) 6.8 (13) 3.6 (12.5) 2.1 (12.5) 1.5 (12) 1.3 (11)

500␣ Hz 131␣ Hz 300 (10.5) 138 (10.5) 80 (10.5) 34 (10.5) 18 (10.5) 8.7 (10.5) 4.8 (10) 3.4 (10)

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 1.56 (16) 0.88 (16) 0.52 (16) 0.3 (16) 0.28 (16) 0.27 (15.5) 0.27 (14.5) 0.26 (13.5)

20␣ Hz 5.24␣ Hz 3.85 (16) 2.02 (16) 1.15 (16) 0.74 (16) 0.63 (15.5) 0.57 (14.5) 0.61 (13.5) 0.58 (12.5)

25␣ Hz 6.55␣ Hz 4.56 (16) 2.4 (16) 1.4 (16) 0.79 (16) 0.68 (15) 0.66 (14.5) 0.64 (13.5) 0.64 (12.5)

100␣ Hz 26.2␣ Hz 45.7 (13) 22 (13) 13.7 (13) 5.27 (13) 2.64 (13) 2 (12.5) 1.59 (12) 1.4 (11)

200␣ Hz 52.4␣ Hz 262 (10.5) 125 (10.5) 66 (10.5) 32.4 (10.5) 18.4 (10.5) 8.6 (10.5) 4.64 (10.5) 3.3 (10)

REV. A

–9–

AD7707

Table IV. Output RMS Noise/Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +3 V

AIN1 and AIN2 Buffered Mode Only

Filter First Typical Output RMS Noise in V (Peak-to-Peak Resolution in Bits)

Notch and O/P –3␣ dB Gain of ␣ Gain of Gain of Gain of Gain of Gain of Gain of Gain of

Data Rate Frequency 1 ␣ ␣ 2 4 8 16 32 64␣␣␣␣ 128

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 1.80 (16) 1 (16) 0.7 (16) 0.41 (16) 0.41 (16) 0.41 (15) 0.41 (14) 0.41 (13)

50␣ Hz 13.1␣ Hz 4.1 (16) 2.4 (16) 1.5 (16) 1 (15.5) 0.91 (15) 0.89 (14) 0.86 (13) 0.83 (12)

60␣ Hz 15.72␣ Hz 5.1 (16) 3 (16) 1.8 (16) 1.1 (15.5) 0.94 (14.5) 0.94 (13.5) 0.99 (13) 0.99 (11.5)

250␣ Hz 65.5␣ Hz 50 (13) 27 (13) 12.3 (13) 6.4 (13) 4 (12.5) 2.7 (12.5) 2.2 (11.5) 1.8 (11)

500␣ Hz 131␣ Hz 275 (10.5) 125 (10.5) 80 (10.5) 39 (10.5) 16 (10.5) 8.9 (10.5) 5.2 (10) 4.2 (9.5)

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 1.75 (16) 1.18 (16) 0.67 (16) 0.44 (16) 0.41 (16) 0.44 (15) 0.43 (14) 0.43 (13)

20␣ Hz 5.24␣ Hz 4.21 (16) 2.5 (16) 1.48 (16) 1 (15.5) 0.94 (15) 0.96 (14) 0.89 (13) 0.86 (12)

25␣ Hz 6.55␣ Hz 5.15 (16) 2.8 (16) 1.8 (16) 1.15 (15.5) 1 (14.5) 1.02 (13.5) 0.96 (13) 1.03 (11.5)

100␣ Hz 26.2␣ Hz 46.1 (13) 24.3 (13) 13.6 (13) 6.71 (13) 4.1 (12.5) 2.54 (12.5) 2.3 (11.5) 2.15 (10.5)

200␣ Hz 52.4␣ Hz 282 (10.5) 123 (10.5) 66 (10.5) 35.3 (10.5) 14.8 (10.5) 9.91 (10.5) 5.48 (10) 4.01 (9.5)

OUTPUT NOISE FOR HIGH LEVEL INPUT CHANNEL AIN3 (5 V OPERATION)

Table V shows the AD7707 output rms noise and peak-to-peak resolution in unbuffered for the selectable notch and –3␣ dB

frequencies for the part, as selected by FS0, FS1 and FS2 of the Clock Register. The numbers given are for the ±10 V,

±5 V, 0 to 5 V and 0 V to +10 V ranges with a V

numbers are typical and are generated at an analog input voltage of 0 V. Table VI meanwhile shows the output rms noise and

peak-to-peak resolution in buffered mode. It is important to note that these numbers represent the resolution for which there will be

no code flicker. They are not calculated based on rms noise but on peak-to-peak noise. Operating the high level channel with a gain

of 2 in bipolar mode gives an operating range of ±10 V. Operating at a gain of 2 in unipolar mode gives a range of 0 V to

+10 V. Operating the high level channel with a gain of 4 in bipolar mode gives the ±5 V operating range. Operating at a gain

of 4 in unipolar mode gives an operating range of 0 V to +5 V. Noise for all input ranges is shown in Appendix 1. The output noise comes from two sources. The first is the electrical noise in the semiconductor devices (device noise) used in the

implementation of the modulator. Secondly, when the analog input is converted into the digital domain, quantization noise

is added. The device noise is at a low level and is independent of frequency. The quantization noise starts at an even lower

level but rises rapidly with increasing frequency to become the dominant noise source. The numbers in the tables are given

for the bipolar input ranges. For the unipolar ranges the rms noise numbers will be the same as the bipolar range but the

peak-to-peak resolution is now based on half the signal range which effectively means losing 1 bit of resolution.

of +2.5 V, HBIAS = 2.5 V, HICOM = AGND and AVDD = 5 V. These

REF

Table V. Output RMS Noise/Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +5 V

AIN3 Unbuffered Mode Only

F

ilter First ⴞ10 V Range ⴞ5 V Range 0 V to +10 V Range 0 V to +5 V Range

Notch and O/P –3␣ dB RMS Noise P-P (Bits) RMS Noise P-P (Bits) RMS Noise P-P (Bits) RMS Noise P-P (Bits)

Data Rate Frequency (V) Resolution (V) Resolution (V) Resolution (V) Resolution

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 5.10 16 3.52 16 5.10 16 3.52 16

50␣ Hz 13.1␣ Hz 15.82 16 9.77 16 15.82 16 9.77 16

60␣ Hz 15.72␣ Hz 20.36 16 12.29 16 20.36 16 12.29 16

250␣ Hz 65.5␣ Hz 430 13 212 13 430 12 212 12

500␣ Hz 131␣ Hz 2350 10 1287 10 2350 9 1287 9

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 5.13 16 3.53 16 5.13 16 3.53 16

20␣ Hz 5.24␣ Hz 18.9 16 13.25 16 18.9 16 13.25 16

25␣ Hz 6.55␣ Hz 23.7 16 15.3 16 23.7 16 15.3 15.5

100␣ Hz 26.2␣ Hz 406 13 174 13 406 12 174 12

200␣ Hz 52.4␣ Hz 2184 10.5 1144 10.5 2184 9.5 1144 9.5

–10–

REV. A

AD7707

Table VI. Output RMS Noise/ Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +5 V

AIN3 Buffered Mode Only

Filter First ⴞ10 V Range ⴞ5 V Range 0 V to +10 V Range 0 to +5 V Range

Notch and O/P –3␣ dB RMS Noise P-P (Bits) RMS Noise P-P (Bits) RMS Noise P-P (Bits) RMS Noise P-P (Bits)

Data Rate Frequency (V) Resolution (V) Resolution (V) Resolution (V) Resolution

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 7.4 16 5.2 16 7.4 16 5.2 16

50␣ Hz 13.1␣ Hz 22.2 16 14.3 16 22.2 16 14.3 16

60␣ Hz 15.72␣ Hz 26.6 16 15.85 16 26.6 16 15.85 16

250␣ Hz 65.5␣ Hz 475 13 187 13 475 12 187 12

500␣ Hz 131␣ Hz 2423 10.5 1097 10.5 2423 9.5 1097 9.5

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 7.63 16 5.45 16 7.63 16 5.45 16

20␣ Hz 5.24␣ Hz 20.25 16 13.3 16 20.25 16 13.3 16

25␣ Hz 6.55␣ Hz 23.5 16 14.6 16 23.5 16 14.6 15.5

100␣ Hz 26.2␣ Hz 377 13 210 13 377 12 210 12

200␣ Hz 52.4␣ Hz 2226 10.5 1132 10.5 2226 9.5 1132 9.5

OUTPUT NOISE FOR HIGH LEVEL INPUT CHANNEL AIN3 (5 V OPERATION)

Table VII shows the AD7707 output rms noise and peak-to-peak resolution for the selectable notch and –3␣ dB frequencies for the

part, as selected by FS0, FS1 and FS2 of the Clock Register. The numbers given are for the ±5 V, 0 V to +5 V and 0 V to +10 V

ranges with a V

ated at an analog input voltage of 0 V for unbuffered mode of operation. The above operating ranges are only achievable in unbuffered mode when operating at 3 V due to common-mode limitations on the input amplifier. It is important to note that these numbers

represent the resolution for which there will be no code flicker. They are not calculated based on rms noise but on peak-to-peak noise. Operating

at a gain of 1 in unipolar mode provides a range of 0 V to +10 V. Operating the high level channel with a gain of 2 in bipolar mode

provides a ±5 V operating range. Operating at a gain of 2 in unipolar mode provides an operating range of 0V to +5 V. The output

noise comes from two sources. The first is the electrical noise in the semiconductor devices (device noise) used in the implementation

of the modulator. Secondly, when the analog input is converted into the digital domain, quantization noise is added. The device

noise is at a low level and is independent of frequency. The quantization noise starts at an even lower level but rises rapidly with

increasing frequency to become the dominant noise source. The numbers in the tables are given for the bipolar input ranges. For the

unipolar ranges the rms noise numbers will be the same as the bipolar range but the peak-to-peak resolution is now based on half the

signal range which effectively means losing 1 bit of resolution.

of +1.225 V, HBIAS = 1.225 V, HICOM = AGND and AVDD = 3 V. These numbers are typical and are gener-

REF

Table VII. Output RMS Noise/ Peak-to-Peak Resolution vs. Gain and Output Update Rate @ +3 V

AIN3 Unbuffered Mode Only

Filter First 0 V to +10 V Range ⴞ5 V Range 0 to +5 V Range

Notch and O/P –3␣ dB RMS Noise

P-P (Bits)

RMS Noise

P-P (Bits)

RMS Noise

P-P (Bits)

Data Rate Frequency (V) Resolution (V) Resolution (V) Resolution

MCLK IN = 2.4576 MHz

10␣ Hz 2.62␣ Hz 12.4 16 7.02 16 7.02 16

50␣ Hz 13.1␣ Hz 30.35 16 16.4 16 16.4 15.5

60␣ Hz 15.72␣ Hz 34.55 16 19.13 16 19.13 15

250␣ Hz 65.5␣ Hz 498 12.5 204 13 204 12

500␣ Hz 131␣ Hz 2266 10.5 1151 10.5 1151 9.5

MCLK IN = 1 MHz

4.05␣ Hz 1.06␣ Hz 13.9 16 7.3 16 7.3 16

20␣ Hz 5.24␣ Hz 32.2 16 17.4 16 17.4 15

25␣ Hz 6.55␣ Hz 33.4 16 18.57 16 18.57 15

100␣ Hz 26.2␣ Hz 430 13 200 13 200 12

200␣ Hz 52.4␣ Hz 2207 10.5 1048 10.5 1048 9.5

REV. A

–11–

AD7707

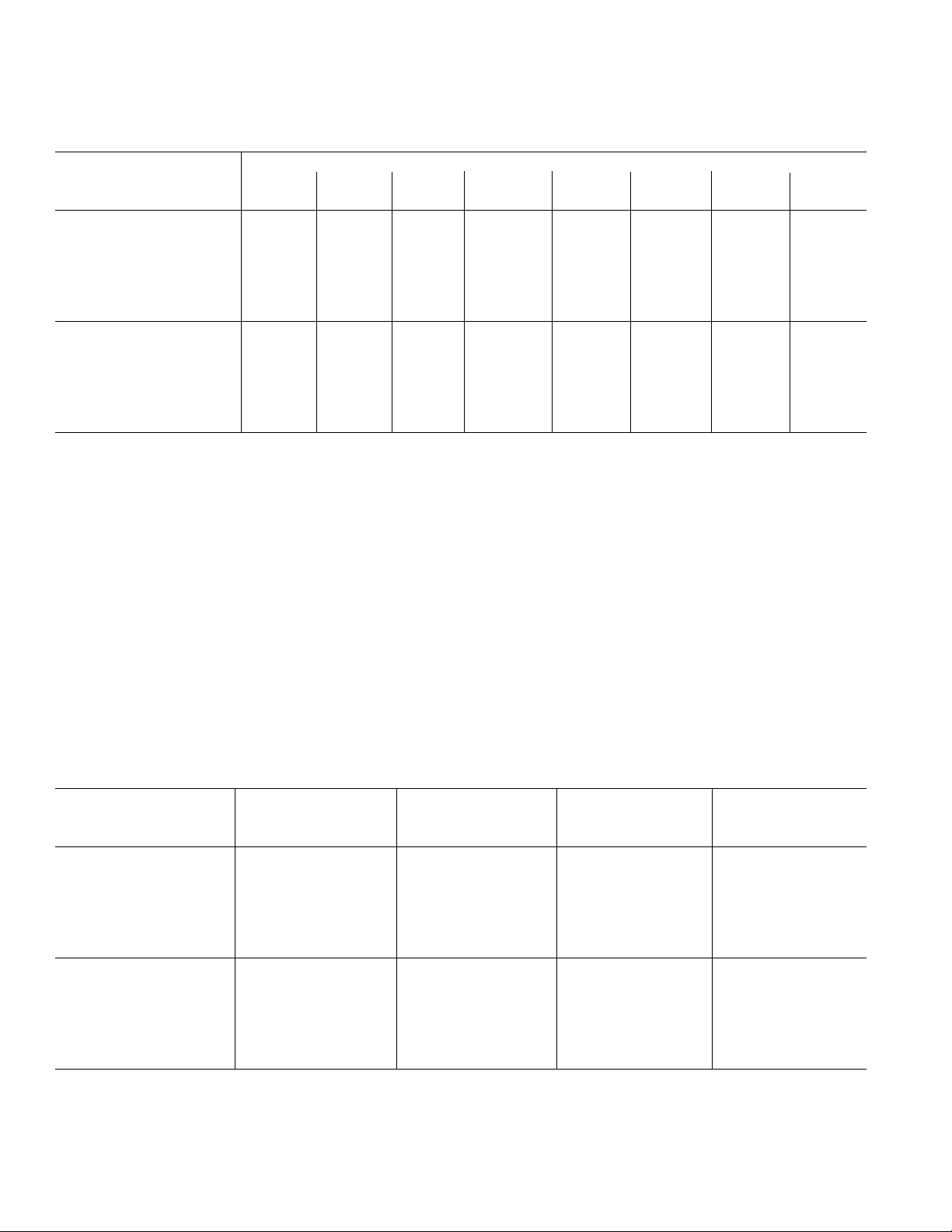

32771

32770

32769

32768

32767

CODE READ

32766

32765

32764

32763

0 100

VDD = 5V

V

= 2.5V

REF

GAIN = 128

50Hz UPDATE RATE

200 300 400 500 600 700 800 900 1000

TA = +258C

RMS NOISE = 600nV

READING NO.

Figure 2. Typical Noise Plot @ Gain = 128 with 50 Hz

Update Rate for Low Level Input Channel

32769

10Hz UPDATE RATE, UNBUFFERED MODE

GAIN = 2, (610V INPUT RANGE)

BIPOLAR MODE

ANALOG INPUT SET ON CODE TRANSITION

32768

400

300

200

OCCURRENCE

100

0

32764

32765 32766 32767 32768 32769 32770

CODE

Figure 5. Histogram of Data in Figure 2

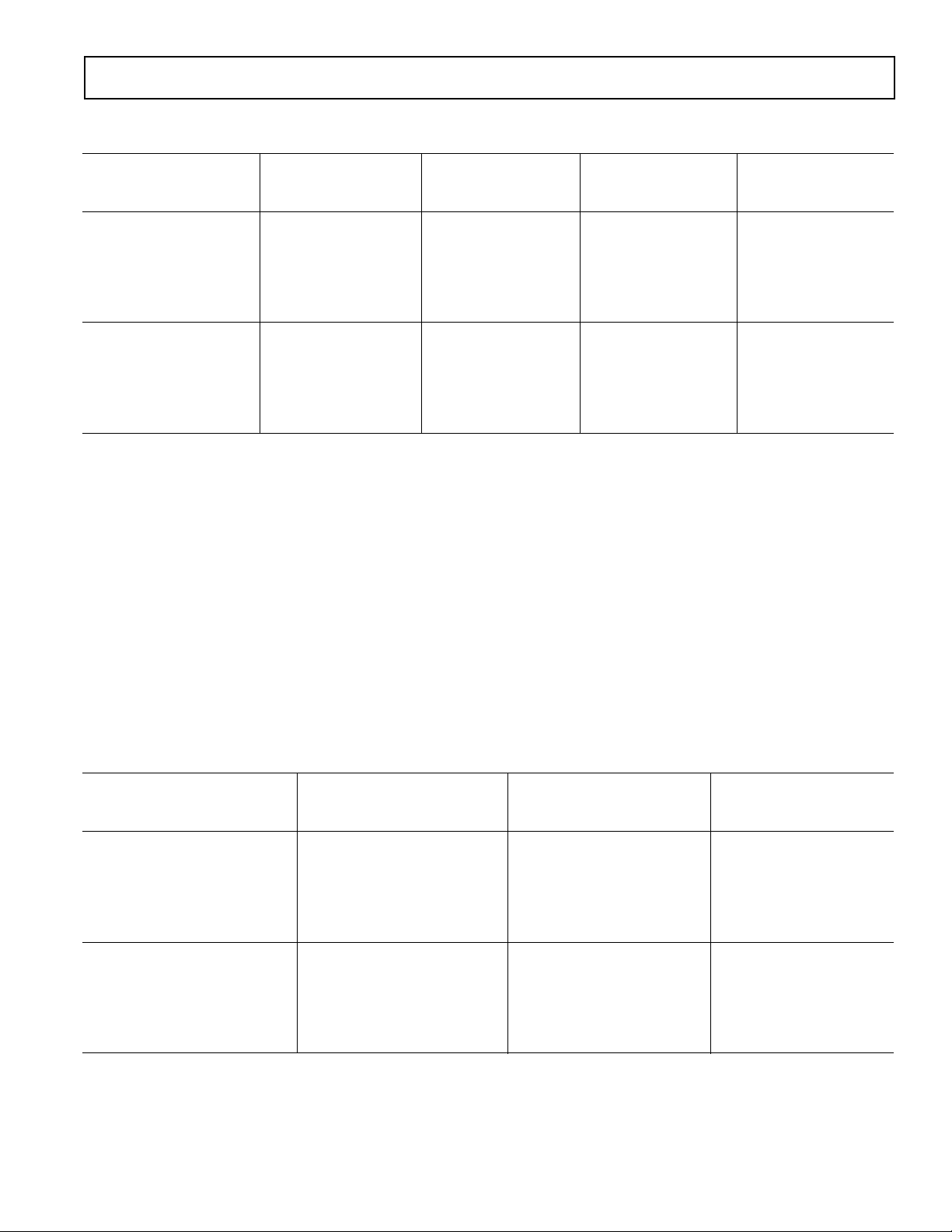

800

10Hz UPDATE RATE

UNBUFFERED MODE

700

BIPOLAR MODE

GAIN = 2,

(610V INPUT RANGE)

600

500

CODE

32767

32766

0

200 400 600 800 1000

READING NO.

Figure 3. Typical Noise Plot for AIN3, High Level Input

Channel

10

9

8

7

6

5

4

RMS NOISE – mV

3

2

1

0

–10

AV

= DV

= 5V

DD

REFIN(+) = 2.5V

REFIN(–) = AGND

TA = +258C

DD

–6 –2 2 6 10

HIGH LEVEL INPUT CHANNEL

610V INPUT RANGE

10Hz UPDATE RATE

BUFFERED MODE

UNBUFFERED MODE

AIN3 – Volts

400

300

OCCURRENCE

200

100

0

12

32767 32768

CODE

Figure 6. Histogram of Data in Figure 3

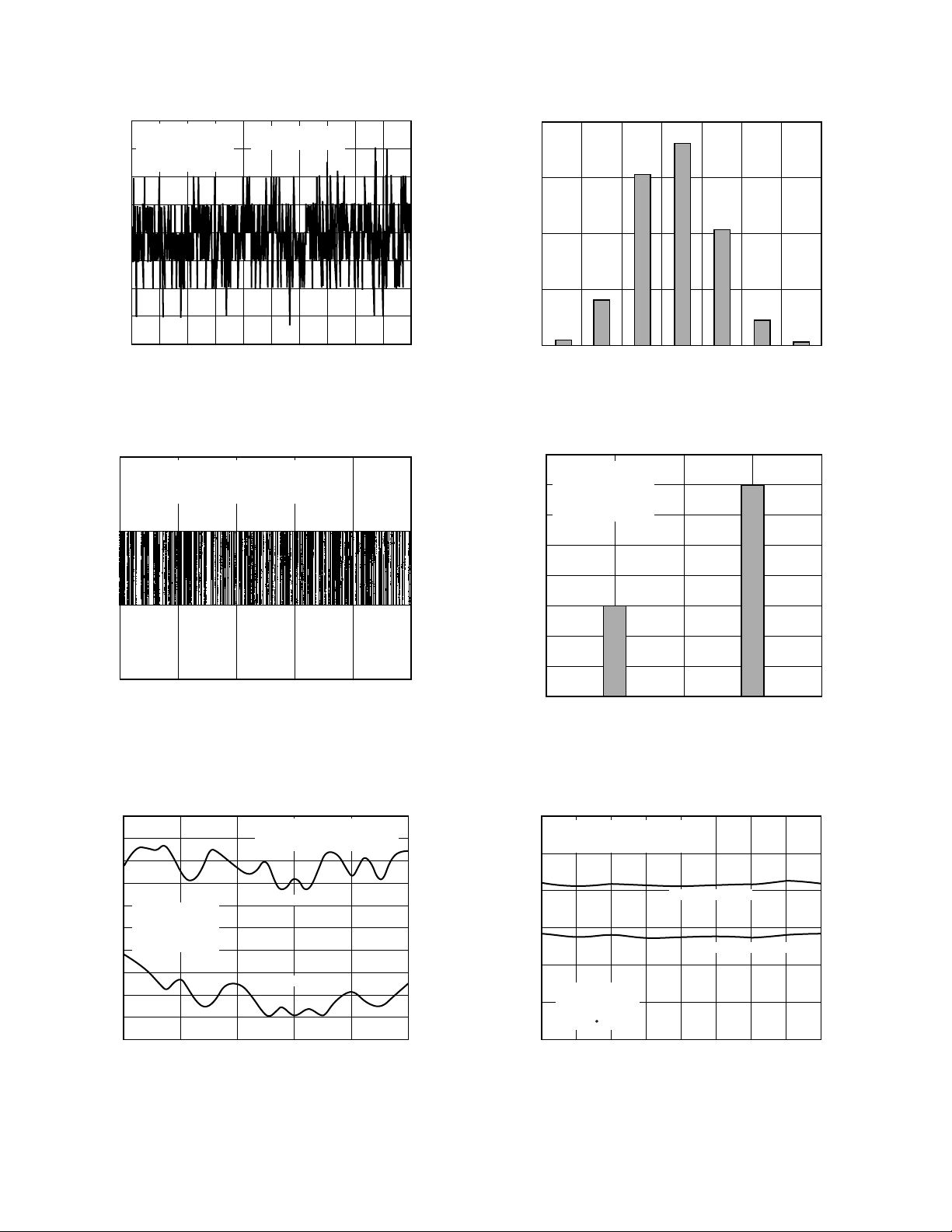

0.6

LOW LEVEL INPUT CHANNEL

GAIN = 128

10Hz UPDATE RATE

0.5

0.4

0.3

RMS NOISE – mV

0.2

0.1

0

–20

AV

= DV

= 5V

DD

REFIN(+) = 2.5V

REFIN(–) = AGND

TA = +25 C

DD

–15 –10 10 15 20

BUFFERED MODE

UNBUFFERED MODE

–5 0 5

INPUT VOLTAGE – mV

Figure 4. Typical RMS Noise vs. Analog Input Voltage for

High Level Input Channel, AIN3

Figure 7. Typical RMS Noise vs. Analog Input Voltage for

Low Level Input Channels, AIN1 and AIN2

–12–

REV. A

Loading...

Loading...