3 V, Parallel Input

a

FEATURES

Micropower: 100 A/DAC

0.1 A Typical Power Shutdown

Single Supply +2.7 V to +5.5 V Operation

Compact 1.1 mm Height TSSOP 24-Lead Package

AD7396: 12-Bit Resolution

AD7397: 10-Bit Resolution

0.9 LSB Differential Nonlinearity Error

APPLICATIONS

Automotive Output Span Voltage

Portable Communications

Digitally Controlled Calibration

PC Peripherals

GENERAL DESCRIPTION

The AD7396/AD7397 series of dual, 12-bit and 10-bit voltageoutput digital-to-analog converters are designed to operate from

a single +3 V supply. Built using a CBCMOS process, these

monolithic DACs offer the user low cost and ease of use in

single supply +3 V systems. Operation is guaranteed over the

supply voltage range of +2.7 V to +5.5 V, making this device

ideal for battery operated applications.

A 12-bit wide data latch loads with a 45 ns write time allowing

interface to fast processors without wait states. The double

buffered input structure allows the user to load the input

registers one at a time, then a single load strobe tied to both

LDA+LDB inputs will simultaneously update both DAC outputs. LDA and LDB can also be independently activated to

immediately update their respective DAC registers. An address

input (A/B) decodes DACA or DACB when the chip select CS

input is strobed. Additionally, an asynchronous RS input sets

the output to zero-scale at power on or upon user demand.

Power shutdown to submicroamp levels is directly controlled by

the active low SHDN pin. While in the power shutdown state

register data can still be changed even though the output buffer

is in an open circuit state. Upon return to the normal operating

state the latest data loaded in the DAC register will establish the

output voltage.

Dual 12-Bit /10-Bit DACs

AD7396/AD7397

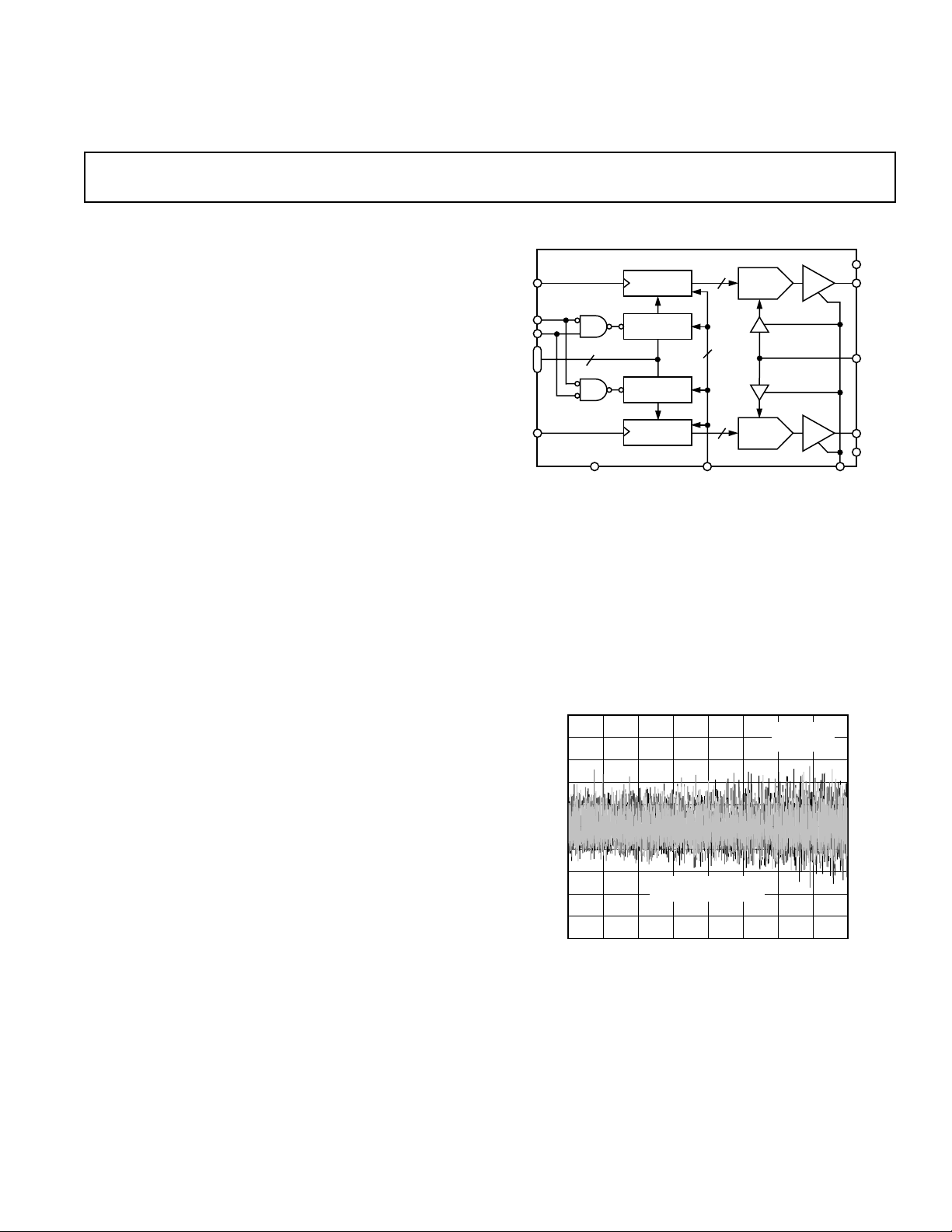

FUNCTIONAL BLOCK DIAGRAM

V

DD

V

OUTA

V

REF

V

OUTB

AGND

LDA

CS

A/B

DATA

LDB

AD7396

12

DGND

DACA

REGISTER

INPUTA

REGISTER

INPUTB

REGISTER

DACB

REGISTER

12

12-BIT

DACA

1

12

12-BIT

DACB

RS SHDN

Both parts are offered in the same pinout, allowing users to

select the amount of resolution appropriate for their applications

without circuit card changes.

The AD7396/AD7397 are specified for operation over the ex-

tended industrial (–40°C to +85°C) temperature range. The

AD7397AR is specified for the –40°C to +125°C automotive

temperature range. AD7396/AD7397s are available in plastic

DIP, and 24-lead SOIC packages. The AD7397ARU is available for ultracompact applications in a thin 1.1 mm height

TSSOP 24-lead package.

1.0

0.8

0.6

0.4

0.2

0.0

DNL – LSB

–0.2

–0.4

–0.6

–0.8

–1.0

0

TA = +258C, +858C, –558C

SUPERIMPOSED

512 1024 1536 2048 2560 3072 3584 4096

CODE – Decimal

VDD = +3V

= +2.5V

V

REF

Figure 1. DNL vs. Digital Code at Temperature

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998

AD7396/AD7397–SPECIFICATIONS

AD7396 12-BIT

ELECTRICAL CHARACTERISTICS

(@ V

= +2.5 V, –40ⴗC < TA < +85ⴗC, unless otherwise noted)

REF IN

Parameter Symbol Conditions +3 V ⴞ 10% +5 V ⴞ 10% Units

STATIC PERFORMANCE

Resolution

Relative Accuracy

Relative Accuracy

Differential Nonlinearity

Differential Nonlinearity

Zero-Scale Error V

Zero-Scale Error V

Full-Scale Voltage Error V

Full-Scale Voltage Error V

Full-Scale Tempco

1

2

2

2

2

3

N 12 12 Bits

INL T

INL T

DNL T

= +25°C ±1.75 ±1.75 LSB max

A

= –40°C, +85°C ±2.0 ±2.0 LSB max

A

= +25°C, Monotonic ±0.9 ±0.9 LSB max

A

DNL Monotonic ±1 ±1 LSB max

ZSE

ZSE

FSE

FSE

TCV

FS

Data = 000H, T

Data = 000H, T

T

= +25°C, +85°C, Data = FFFH±8 ±8mV max

A

T

= –40°C, Data = FFF

A

= +25°C, +85°C 4.0 4.0 mV max

A

= –40°C 8.0 8.0 mV max

A

H

±20 ±20 mV max

–45 –45 ppm/°C typ

REFERENCE INPUT

V

Range V

REF

Input Resistance R

Input Capacitance

3

REF

REF

C

REF

0/V

DD

0/V

DD

V min/max

2.5 2.5 MΩ typ

55pF typ

ANALOG OUTPUT

Output Current (Source) I

Output Current (Sink) I

Capacitive Load

3

OUT

OUT

C

L

Data = 800

Data = 800

H

H

, ∆V

, ∆V

= 5 LSB 1 1 mA typ

OUT

= 5 LSB 3 3 mA typ

OUT

No Oscillation 100 100 pF typ

LOGIC INPUTS

Logic Input Low Voltage V

Logic Input High Voltage V

Input Leakage Current I

Input Capacitance

INTERFACE TIMING

3

3, 5

Chip Select Write Width t

DAC Select Setup t

DAC Select Hold t

Data Setup t

Data Hold t

Load Setup t

Load Hold t

Load Pulsewidth t

Reset Pulsewidth t

IL

C

CS

AS

AH

DS

DH

LS

LH

LDW

RSW

IL

IH

IL

0.5 0.8 V max

VDD – 0.6 4.0 V min

10 10 µA max

10 10 pF max

45 35 ns min

30 15 ns min

0 0 ns min

30 15 ns min

20 10 ns min

20 20 ns min

10 10 ns min

30 30 ns min

40 30 ns min

AC CHARACTERISTICS

Output Slew Rate SR Data = 000

Settling Time

Shutdown Recovery Time t

6

t

S

SDR

To ±0.1% of Full Scale 70 60 µs typ

DAC Glitch Q Code 7FF

to FFFH to 000

H

to 800H to 7FF

H

H

0.05 0.05 V/µs typ

90 80 µs typ

H

65 65 nV/s typ

Digital Feedthrough Q 15 15 nV/s typ

V

Feedthrough V

OUT/VREF

= 1.5 VDC +1 V p-p

REF

,

Data = 000H, f = 100 kHz –63 –63 dB typ

SUPPLY CHARACTERISTICS

Power Supply Range V

Positive Supply Current I

Shutdown Supply Current I

Power Dissipation P

DD RANGE

DD

DD_SD

DISS

DNL < ±1 LSB 2.7/5.5 2.7/5.5 V min/max

V

= 0 V, No Load 125/200 125/200 µA typ/max

IL

SHDN = 0, V

V

= 0 V, No Load 600 1000 µW max

IL

= 0 V, No Load 0.1/1.5 0.1/1.5 µA typ/max

IL

Power Supply Sensitivity PSS ∆VDD = ±5% 0.006 0.006 %/% max

NOTES

1

One LSB = V

2

The first two codes (000H, 001H) are excluded from the linearity error measurement.

3

These parameters are guaranteed by design and not subject to production testing.

4

Typicals represent average readings measured at +25°C.

5

All input control signals are specified with tR = tF = 2 ns (10% to 90% of +3 V) and timed from a voltage level of +1.6 V.

6

The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

Specifications subject to change without notice.

/4096 V for the 12-bit AD7396.

REF

–2–

4

REV. 0

AD7397 10-BIT

AD7396/AD7397

ELECTRICAL CHARACTERISTICS

(@ V

= +2.5 V, –40ⴗC < TA < +85ⴗC, unless otherwise noted)

REF IN

Parameter Symbol Conditions +3 V ⴞ 10% +5 V ⴞ 10% Units

STATIC PERFORMANCE

Resolution

Relative Accuracy

Relative Accuracy

Differential Nonlinearity

Zero-Scale Error V

Full-Scale Voltage Error V

Full-Scale Voltage Error V

Full-Scale Tempco

1

2

2

2

3

N 10 10 Bits

INL T

INL T

= +25°C ±1.75 ±1.75 LSB max

A

= –40°C, +85°C, +125°C ±2.0 ±2.0 LSB max

A

DNL Monotonic ±1 ±1LSB max

ZSE

FSE

FSE

TCV

FS

Data = 000

T

= +25°C, +85°C, +125°C, Data = 3FFH±42 ±42 mV max

A

T

= –40°C, Data = 3FF

A

H

H

9.0 9.0 mV max

±48 ±48 mV max

–45 –45 ppm/°C typ

REFERENCE INPUT

V

Range V

REF

Input Resistance R

Input Capacitance

3

REF

REF

C

REF

0/V

DD

0/V

DD

V min/max

2.5 2.5 MΩ typ

5 5 pF typ

ANALOG OUTPUT

Output Current (Source) I

Output Current (Sink) I

Capacitive Load

3

C

OUT

OUT

L

Data = 200

Data = 200

H

H

, ∆V

, ∆V

= 5 LSB 1 1 mA typ

OUT

= 5 LSB 3 3 mA typ

OUT

No Oscillation 100 100 pF typ

LOGIC INPUTS

Logic Input Low Voltage V

Logic Input High Voltage V

Input Leakage Current I

Input Capacitance

INTERFACE TIMING

3

3, 5

Chip Select Write Width t

DAC Select Setup t

DAC Select Hold t

Data Setup t

Data Hold t

Load Setup t

Load Hold t

Load Pulsewidth t

Reset Pulsewidth t

IL

C

CS

AS

AH

DS

DH

LS

LH

LDW

RSW

IL

IH

IL

0.5 0.8 V max

VDD – 0.6 4.0 V min

10 10 µA max

10 10 pF max

45 35 ns min

30 15 ns min

0 0 ns min

30 15 ns min

20 10 ns min

20 20 ns min

10 10 ns min

30 30 ns min

40 30 ns min

AC CHARACTERISTICS

Output Slew Rate SR Data = 000

Settling Time

Shutdown Recovery Time t

6

t

S

SDR

To ±0.1% of Full Scale 70 60 µs typ

DAC Glitch Q Code 7FF

to 3FFH to 000

H

to 800H to 7FF

H

H

0.05 0.05 V/µs typ

90 80 µs typ

H

65 65 nV/s typ

Digital Feedthrough Q 15 15 nV/s typ

Feedthrough V

OUT/VREFVREF

= 1.5 VDC +1 V p-p

,

Data = 000H, f = 100 kHz –63 –63 dB typ

SUPPLY CHARACTERISTICS

Power Supply Range V

Positive Supply Current I

Shutdown Supply Current I

Power Dissipation P

DD RANGE

DD

DD_SD

DISS

DNL < ±1 LSB 2.7/5.5 2.7/5.5 V min/max

V

= 0 V, No Load 125/200 125/200 µA typ/max

IL

SHDN = 0, V

V

= 0 V, No Load 600 1000 µW max

IL

= 0 V, No Load 0.1/1.5 0.1/1.5 µA typ/max

IL

Power Supply Sensitivity PSS ∆VDD = ±5% 0.006 0.006 %/% max

NOTES

1

One LSB = V

2

The first two codes (000H, 001H) are excluded from the linearity error measurement.

3

These parameters are guaranteed by design and not subject to production testing.

4

Typicals represent average readings measured at +25°C.

5

All input control signals are specified with tR = tF = 2 ns (10% to 90% of +3 V) and timed from a voltage level of +1.6 V.

6

The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

Specifications subject to change without notice.

/4096 V for the 10-bit AD7397.

REF

4

–3–REV. 0

AD7396/AD7397

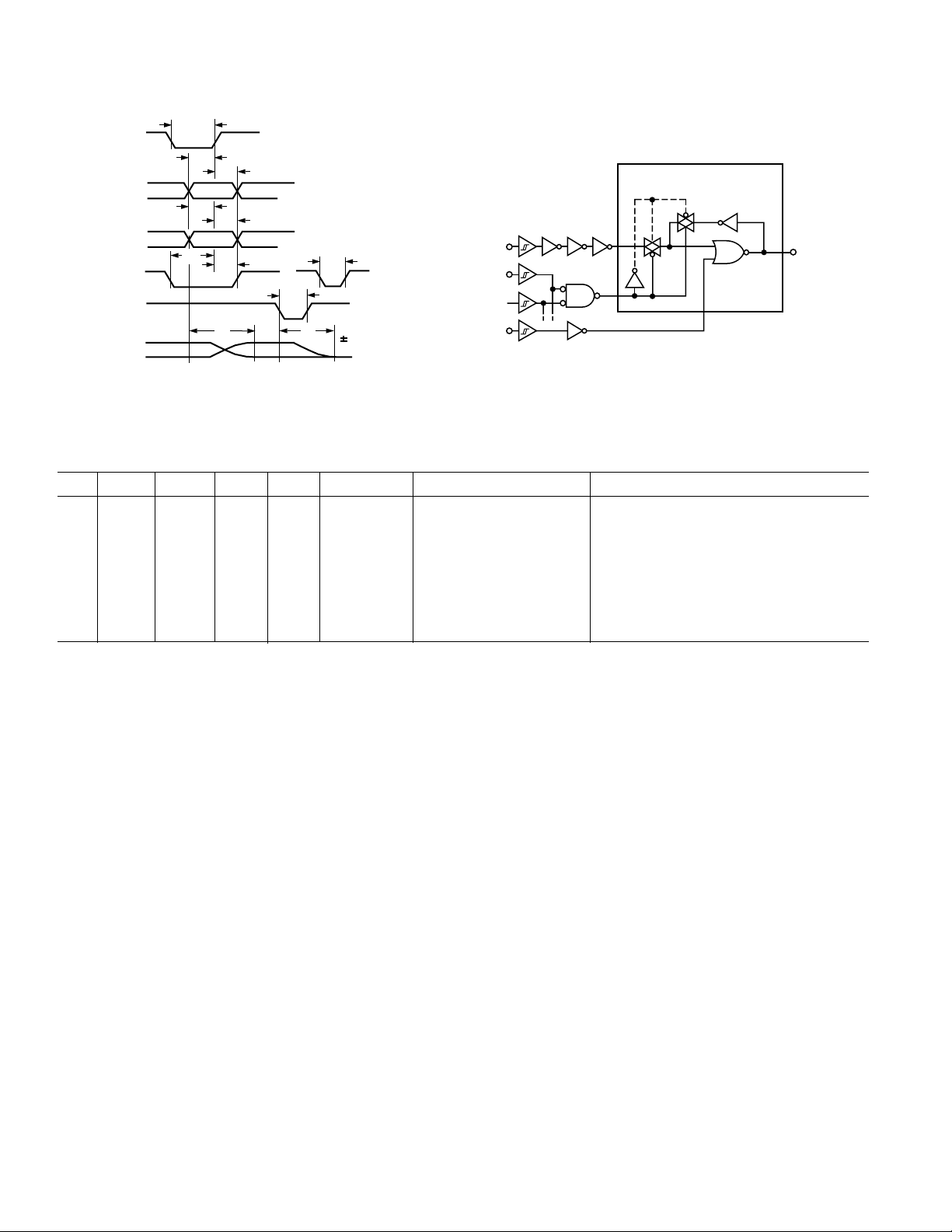

t

CS

A/B

D0–D11

LDA, LDB

RS

V

OUT

CSW

t

LS

t

AS

t

DS

t

AH

t

DH

t

t

RSW

t

S

LDW

1 LSB

ERROR BAND

t

LH

t

S

DBx

CS

A/B

RS

B REGISTER

1 OF 12

LATCHES

OF THE 2 INPUT

REGISTERS

TO DAC

REGISTERS

Figure 2. Timing Diagram

Figure 3. Digital Control Logic

Table I. Control Logic Truth

CS A/B LDA LDB RS SHDN Input Register DAC Register

L L HHHX Write to B Latched with Previous Data

L HHHHX Write to A Latched with Previous Data

L L H L H X Write to B B Transparent

L H L H H X Write to A A Transparent

H X L L H X Latched A and B Transparent

H X ^ ^ H X Latched Latched with New Data from Input REG

XXXXLX Reset to Zero Scale Reset to Zero Scale

HXXX^ X Latched to Zero Latched to Zero

^Denotes positive edge. The SHDN pin has no effect on the digital interface data loading; however, while in the SHDN state (SHDN = 0) the output amplifiers V

and V

exhibit an open circuit condition. Note, the LDx inputs are level-sensitive, the respective DAC registers are in a transparent state when LDx = “0.”

OUTB

OUTA

–4–

REV. 0

AD7396/AD7397

ABSOLUTE MAXIMUM RATINGS*

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V, +8 V

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, V

V

REF

Logic Inputs to GND . . . . . . . . . . . . . . . . . . . . . –0.3 V, +8 V

V

to GND . . . . . . . . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V

OUT

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +2 V

Short Circuit to GND . . . . . . . . . . . . . . . . . . . . +50 mA

I

OUT

Package Power Dissipation . . . . . . . . . . . . . (T

Thermal Resistance θ

JA

max – T

J

)/θ

A

24-Lead Plastic DIP Package (N-24) . . . . . . . . . . +63°C/W

24-Lead SOIC Package (R-24) . . . . . . . . . . . . . . . +70°C/W

24-Lead Thin Shrink Surface Mount (RU-24) . . +143°C/W

Maximum Junction Temperature (T

max) . . . . . . . . .+150°C

J

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

DD

AD7397AN, AD7397AR Only . . . . . . . . –40°C to +125°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature

␣ ␣ N-24 (Soldering, 10 sec) . . . . . . . . . . . . . . . . . . . . . .+300°C

␣ ␣ R-24 (Vapor Phase, 60 sec) . . . . . . . . . . . . . . . . . . . .+215°C

␣ ␣ RU-24 (Infrared, 15 sec) . . . . . . . . . . . . . . . . . . . . . .+224°C

JA

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ORDERING GUIDE

Res Temperature Package Package

Model (LSB) Ranges Descriptions Options

AD7396AN 12 –40°C to +85°C 24-Lead P-DIP N-24

AD7396AR 12 –40°C to +85°C 24-Lead SOIC R-24

AD7397AN 10 –40°C to +125°C 24-Lead P-DIP N-24

AD7397AR 10 –40°C to +125°C 24-Lead SOIC R-24

AD7397ARU 10 –40°C to +85°C 24-Lead Thin Shrink Small Outline Package (TSSOP) RU-24

The AD7396/AD7397 contains 1365 transistors. The die size measures 89 mil × 106 mil = 9434 sq mil.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7396/AD7397 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–5–REV. 0

AD7396/AD7397

PIN FUNCTION DESCRIPTIONS

Pin No. Name

1V

OUTA

2 AGND Analog Ground.

3 DGND Digital Ground.

4 LDA Load DAC A Register Strobe. Transfers input register data to the DAC A register. Active

5 SHDN Power Shutdown Active Low Input. DAC register contents are saved as long as power stays

6 RS Resets Input and DAC Register to Zero Condition. Asynchronous active low input.

7–18 D0–D11 Twelve Parallel Input Data Bits. D11 = MSB Pin 18, D0 = LSB Pin 7, AD7396.

7, 8 NC No Connect Pins 7 and 8 On the AD7397 Only.

9–18 D0–D9 Ten Parallel Input Data Bits. D9 = MSB Pin 18, D0 = LSB Pin 9, AD7397 Only.

19 CS Chip Select Latch Enable, Active Low.

20 A/B DAC Input Register Address Select DACA = 1 or DACB = 0.

21 LDB Load DAC B Register Strobe. Transfers input register data to the DAC B register. Active low

22 V

23 V

24 V

DD

REF

OUTB

DAC A Voltage Output.

low inputs, Level sensitive latch. May be connected together with LDB to double-buffer load

both DAC registers simultaneously.

on the V

DD

pin.

inputs, Level sensitive latch. May be connected together with LDA to double-buffer load

both DAC registers simultaneously.

Positive Power Supply Input. Specified range of operation +2.7 V to +5.5 V.

DAC Reference Input Pin. Establishes DAC full-scale voltage.

DAC B Voltage Output.

V

OUTA

AGND

DGND

LDA

SHDN

RS

D0

D1

D2

D3

D4

D5

1

2

3

4

5

AD7396

6

TOP VIEW

(Not to Scale)

7

8

9

10

11

12

PIN CONFIGURATIONS

1

24

V

OUTB

23

V

REF

22

V

DD

21

LDB

20

A/B

19

CS

18

D11

17

D10

16

D9

15

D8

14

D7

13

D6

V

OUTA

2

AGND

3

DGND

4

LDA

5

SHDN

6

RS

7

NC

8

NC

9

D0

10

D1

11

D2

12

D3

NC = NO CONNECT

(Not to Scale)

AD7397

TOP VIEW

24

V

OUTB

23

V

REF

22

V

DD

21

LDB

20

A/B

19

CS

18

D9

17

D8

16

D7

15

D6

14

D5

13

D4

–6–

REV. 0

Typical Performance Characteristics–

pp

AD7396/AD7397

1.5

VDD = +3V

= +2.5V

V

REF

1.0

0.5

0.0

INL – LSB

–0.5

–1.0

–1.5

0

512 1024 1536 2048 2560 3072 3584 4096

TA = –558C

TA = +258C, +858C

CODE – Decimal

AD7396

Figure 4. AD7396 INL vs. Code and

Temperature

1.0

AD7397

0.8

0.6

0.4

0.2

0.0

–0.2

DNL – LSB

–0.4

–0.6

–0.8

–1.0

TA = +258C, +858C, –558C

SUPERIMPOSED

0

128 256 384 512 640 768 896 1024

CODE – Decimal

VDD = +2.7V

= +2.5V

V

REF

Figure 7. AD7397 DNL vs. Code and

Temperature

1.0

VDD = +2.7V

0.8

V

= +2.5V

REF

0.6

0.4

0.2

0.0

–0.2

INL – LSB

–0.4

–0.6

TA = +258C, +858C

–0.8

–1.0

0

128 256 384 512 640 768 896 1024

TA = –558C

CODE – Decimal

AD7397

Figure 5. AD7397 INL vs. Code and

Temperature

60

40

FREQUENCY

20

0

AD7396

–55

–50 –45 –40

FULL-SCALE OUTPUT TEMPCO

HISTOGRAM –

SS = 200 UNITS

V

= +2.7V

DD

= +2.5V

V

REF

= –408C TO +858C

T

A

–35 –30

m/8C

Figure 8. AD7396 Full-Scale Tempco

Histogram

30

20

FREQUENCY

10

0

AD7397

–5

0

TOTAL UNADJUSTED ERROR

HISTOGRAM – LSB

SS = 200 UNITS

T

= +258C

A

= +2.7V

V

DD

V

= +2.5V

REF

510

Figure 6. AD7397 TUE Histogram

100

80

60

40

FREQUENCY

20

0

SS = 200 UNITS

V

= +2.7V

DD

= +2.5V

V

REF

= –408C TO +858C

T

A

–70 –60 –50 –40

FULL-SCALE TEMPCO – ppm/8C

AD7397

–30

Figure 9. AD7397 Full-Scale Tempco

Histogram

1.5

1.0

0.5

0

INL – LSB

–0.5

–1.0

–1.5

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

VDD = +5V

= +258C

T

A

CODE = HALF SCALE

V

– Volts

REF

Figure 10. INL Error vs. Reference

Voltage

40

40

AD7396

20

0

FSE – mV

–20

VDD = +5V

= +258C

T

A

FSE (LSB) = FSE (V) 3 4096/V

–40

01 5

23 4

V

REF

REF

– V

20

0

–20

(V)

–40

Figure 11. Full-Scale Error vs. Reference Voltage

–7–REV. 0

10

8

6

FSE – LSB

4

2

OUTPUT NOISE DENSITY – mV/ Hz

0

10 100 1k 10k 100k

1

FREQUENCY – Hz

Figure 12. Output Noise Voltage

Density vs. Frequency

VDD = +5V

= +2.5V

V

REF

= +258C

T

A

AD7396/AD7397

0

–5

–10

VDD = +3V

–15

CODE = FULL SCALE

–20

–25

GAIN – dB

–30

–35

–40

–45

–50

100 1k 10k 100k 1M

FREQUENCY – Hz

Figure 13. Reference Multiplying

Gain vs. Frequency

5.0

TA = +258C

4.5

4.0

3.5

3.0

2.5

2.0

LOGIC THRESHOLD – V

1.5

1.0

2

V

FROM

LOGIC

LOW TO HIGH

V

FROM

LOGIC

HIGH TO LOW

34 56 7

VDD – V

Figure 16. Logic Threshold Voltage

vs. V

DD

1.262

1.257

1.252

– Volts

OUT

1.247

V

1.242

1.237

VDD = +5V

V

= +2.5V

REF

= +25 C

T

A

CODE = 800

5mV/DIV

TIME – 2ms/DIV

TO 7FF

H

Figure 14. Midscale Transition

Performance

35

30

25

20

15

10

CURRENT SOURCING – mA

OUT

I

5

0

–120

–100 –80 –60 –40 –20

Figure 17. I

∆

V

OUT

OUT

VDD = +5V

DV

OUT

Source Current vs.

V

T

VDD = +3V

– mV

= +2.5V

REF

= +258C

A

145

140

H

135

130

125

– mA

120

DD

I

115

110

105

100

0

VIN = 0V TO +3V

VIN = +3V TO 0V

0.5 1 1.5 2 2.5 3

LOGIC INPUT – VIN (Volts)

Figure 15. IDD vs. Logic Input Voltage

45

V

= +2.5V

REF

40

= +258C

T

A

35

30

25

20

15

CURRENT SINKING – mA

10

OUT

I

5

0

0

Figure 18. I

∆

V

VDD = +5V

VDD = +3V

0

24 6810

DV

– mV

OUT

Sink Current vs.

OUT

OUT

VDD = +3V

T

= +258C

A

12

170

V

= +2.5V

REF

160

VDD = +3.6V, V

150

140

130

– mA

120

DD

I

110

100

90

80

–200 204060

–40

= +2.4V

LOGIC

VDD = +5V, V

VDD = +3V, V

TEMPERATURE – 8C

LOGIC

80

= +5V

LOGIC

100 120 140

Figure 19. IDD vs. Temperature

= +3V

200

TA = +258C

180

160

140

120

100

– mA

DD

I

80

60

40

20

0

0

12345

V

REF

VDD = +5V

VDD = +3V

– Volts

Figure 20. IDD vs. Reference Voltage

–8–

1000

V

= +2.5V

REF

= +5V

V

DD

SHDN = 0V

100

10

SHUTDOWN CURRENT – nA

SD

_

DD

I

1

–40

–20020 40 60 80 100 120 140

TEMPERATURE – 8C

Figure 21. Shutdown Current vs.

Temperature

REV. 0

AD7396/AD7397

1400

AD7396

1200

A: VDD = +2.7V, CODE = 555

B: VDD = +2.7V, CODE = 3FF

1000

C: VDD = +5.5V, CODE = 155

D: VDD = +5.5V, CODE = 3FF

800

– mA

DD

600

I

400

200

0

1k 10M

10k 100k 1M

DIGITAL INPUT FREQUENCY – Hz

H

H

H

H

C

Figure 22. IDD vs. Digital Input

D

A

B

80

70

60

50

40

VDD = +3V, 65%

PSRR – dB

30

20

10

0

1 10k

VDD = +5V, 65%

10 100 1k

FREQUENCY – Hz

Figure 23. PSRR vs. Frequency

Frequency

OPERATION

The AD7396 and AD7397 are a set of pin compatible, 12-bit

and 10-bit digital-to-analog converters. These single-supply

operation devices consume less than 200 µA of current while

operating from power supplies in the +2.7 V to +5.5 V range,

making them ideal for battery operated applications. They

contain a voltage-switched, 12-bit/10-bit, digital-to-analog

converter, rail-to-rail output op amps, and a parallel-input

DAC register. The external reference input has constant

2.5 MΩ input resistance independent of the digital code

setting of the DAC. In addition, the reference input can be tied

to the same supply voltage as V

output voltage span of 0 to V

resulting in a maximum

DD

. The parallel data interface

DD

consists of 12 data bits, DB0–DB11, for the AD7396, 10 data

bits, DB0–DB9, for the AD7397, and a CS write strobe. An RS

pin is available to reset the DAC register to zero scale. This

function is useful for power-on reset or system failure recovery

to a known state. Additional power savings are accomplished by

activating the SHDN pin resulting in a 1.5 µA maximum con-

sumption sleep mode. As long as the supply voltage, remains

data will be retained in the DAC and input register to supply

the DAC output when the part is taken out of shutdown.

V

LDA

CS

A/B

DATA

AD7396

DACA

REGISTER

INPUTA

REGISTER

12

INPUTB

REGISTER

12

12-BIT

DACA

1

V

V

DD

OUTA

REF

1.0

AD7396

0.9

SAMPLE SIZE = 77

0.8

V

= +2.5V

REF

0.7

0.6

0.5

0.4

0.3

0.2

0.1

NOMINAL CHANGE IN VOLTAGE – mV

0

0

CODE = FFF

CODE = 000

100 200 300 400 500 600

HOURS OF OPERATION AT +1508C

H

H

Figure 24. Long-Term Drift Accelerated by Burn-In

× D/2

N

(1)

= V

V

OUT

REF

where D is the decimal data word loaded into the DAC register,

and N is the number of bits of DAC resolution. In the case of

the 10-bit AD7397 using a 2.5 V reference, Equation 1 simplifies to:

= 2.5 × D/1024 (2)

V

OUT

Using Equation 2, the nominal midscale voltage at V

OUT

is

1.25 V for D = 512; full-scale voltage is 2.497 V. The LSB step

size is = 2.5 × 1/1024 = 0.0024 V.

For the 12-bit AD7396 operating from a 5.0 V reference equation [1] becomes:

V

= 5.0 × D/4096 (3)

OUT

Using Equation 3, the AD7396 provides a nominal midscale

voltage of 2.50 V for D = 2048, and a full-scale output of

4.998 V. The LSB step size is = 5.0 × 1/4096 = 0.0012 V.

AMPLIFIER SECTION

The internal DAC’s output is buffered by a low power con-

sumption precision amplifier. The op amp has a 60 µs typical

settling time to 0.1% of full scale. There are slight differences in

settling time for negative slewing signals versus positive. Also,

negative transition settling time to within the last 6 LSBs of zero

volts has an extended settling time. The rail-to-rail output stage

of this amplifier has been designed to provide precision performance while operating near either power supply. Figure 26

shows an equivalent output schematic of the rail-to-rail-amplifier with its N-channel pull-down FETs that will pull an output

load directly to GND. The output sourcing current is provided

by a P-channel pull-up device that can source current to GND

terminated loads.

LDB

DGND

DACB

REGISTER

12

12-BIT

DACB

RS SHDN

V

OUTB

AGND

Figure 25. Functional Block Diagram

D/A CONVERTER SECTION

The voltage switched R-2R DAC generates an output voltage

dependent on the external reference voltage connected to the

REF pin according to the following equation:

V

DD

P-ch

V

N-ch

OUT

AGND

Figure 26. Equivalent Analog Output Circuit

–9–REV. 0

AD7396/AD7397

V

DD

LOGIC

IN

GND

The rail-to-rail output stage provides ±1 mA of output current.

The N-channel output pull-down MOSFET shown in Figure 26

has a 35 Ω ON resistance, which sets the sink current capability

near ground. In addition to resistive load driving capability, the

amplifier has also been carefully designed and characterized for

up to 100 pF capacitive load driving capability.

REFERENCE INPUT

The reference input terminal has a constant input resistance

independent of digital code, which results in reduced glitches on

the external reference voltage source. The high 2.5 MΩ input

resistance minimizes power dissipation within the AD7396/

AD7397 D/A converters. The V

ranging from ground to the positive-supply voltage V

input accepts input voltages

REF

. One of

DD

the simplest applications, which saves an external reference voltage

source, is connection of the V

terminal to the positive V

REF

DD

supply. This connection results in a rail-to-rail voltage output

span maximizing the programmed range. The reference input

will accept AC signals as long as they are kept within the supply

voltage range, 0 < V

< VDD. The reference bandwidth

REF IN

and integral nonlinearity error performance are plotted in the

Typical Performance Characteristics section, see Figures 10 and

13. The ratiometric reference feature makes the AD7396/AD7397

an ideal companion to ratiometric analog-to-digital converters

such as the AD7896.

POWER SUPPLY

The very low power consumption of the AD7396/AD7397 is a

direct result of a circuit design optimizing the use of a CBCMOS

process. By using the low power characteristics of CMOS for

the logic, and the low noise, tight matching of the complementary bipolar transistors, excellent analog accuracy is achieved.

One advantage of the rail-to-rail output amplifiers used in the

AD7396/AD7397 is the wide range of usable supply voltage.

The part is fully specified and tested for operation from +2.7 V

to +5.5 V.

POWER SUPPLY BYPASSING AND GROUNDING

Precision analog products such as the AD7396/AD7397 require

a well filtered power source. Since the AD7396/AD7397 operates from a single +3 V to +5 V supply, it seems convenient to

simply tap into the digital logic power supply. Unfortunately,

the logic supply is often a switch-mode design, which generates

noise in the 20 kHz to 1 MHz range. In addition, fast logic gates

can generate glitches, hundred of millivolts in amplitude, due to

wiring resistance and inductance. The power supply noise generated thereby means that special care must be taken to assure

that the inherent precision of the DAC is maintained. Good

engineering judgment should be exercised when addressing the

power supply grounding and bypassing of the 12-bit AD7396.

The AD7396 should be powered directly from the system power

supply. Whether or not a separate power supply trace is available generous supply bypassing will reduce supply line-induced

errors. Local supply bypassing consisting of a 10 µF tantalum

electrolytic in parallel with a 0.1 µF ceramic capacitor is recom-

mended in all applications (Figure 27).

+2.7V TO +5.5V

*

CS

A/B

LDA

LDB

DATA

*

OPTIONAL EXTERNAL

REFERENCE BYPASS

C

REF V

DGND AGND

AD7396

OR

AD7397

DD

+

0.1mF 10mF

V

V

OUTA

OUTB

Figure 27. Recommended Supply Bypassing

INPUT LOGIC LEVELS

All digital inputs are protected with a Zener-type ESD protection structure (Figure 28) that allows logic input voltages to

exceed the V

supply voltage. This feature can be useful if the

DD

user is driving one or more of the digital inputs with a 5 V CMOS

logic input-voltage level while operating the AD7396/AD7397

on a +3 V power supply. If this mode of interface is used, make

sure that the V

of the 5 V CMOS meets the VIL input require-

OL

ment of the AD7396/AD7397 operating at 3 V. See Figure 16

for a graph for digital logic input threshold versus operating V

DD

supply voltage.

Figure 28. Equivalent Digital Input ESD Protection

In order to minimize power dissipation from input-logic levels

that are near the V

and VIL logic input voltage specifications, a

IH

Schmitt trigger design was used that minimizes the input-buffer

current consumption compared to traditional CMOS input

stages. Figure 15 shows a plot of incremental input voltage

versus supply current showing that negligible current consumption takes place when logic levels are in their quiescent state.

The normal crossover current still occurs during logic transitions. A secondary advantage of this Schmitt trigger is the prevention of false triggers that would occur with slow moving logic

transitions when a standard CMOS logic interface or optoisolators are used. The logic inputs DB11–DB0, A/B CS, RS,

SHDN all contain Schmitt trigger circuits.

DIGITAL INTERFACE

The AD7396/AD7397 has a double-buffered, parallel-data

input. A functional block diagram of the digital section is shown

in Figure 25, while Table I contains the truth table for the logic

control inputs. The chip select (CS) and A/B pins control loading of data from the data inputs on pins DB11–DB0 into the

internal Input Register. The CS active low input places data

into the decoded A/B input register. When CS returns to logic

high within the data setup-and-hold time specifications the new

value of data in the input register will be latched. See Truth

Table for complete set of conditions. New data can only be

transferred to the corresponding DAC register when its LDx pin

is strobed active low. The LDx inputs are level-sensitive (DAC

Registers are transparent latches) and can be tied active low

–10–

REV. 0

AD7396/AD7397

allowing any new Input Register data updates to directly control

the DAC output voltages for single-buffered applications. For

doubled-buffered applications where both DAC outputs, V

and V

, need to be changed simultaneously to a new value,

OUTB

OUTA

the two inputs, LDA and LDB, can be tied together and pulsed

active low in a synchronous manner.

RESET (RS) PIN

Forcing the asynchronous RS pin low will set the Input and

DAC registers to all zeros and the DAC output voltage will be

zero volts. The reset function is useful for setting the DAC

outputs to zero at power-up or after a power supply interruption. Test systems and motor controllers are two of many applications that benefit from powering up to a known state. The

external reset pulse can be generated by the microprocessor’s

power-on RESET signal, from the microprocessor, or by an

external resistor and capacitor. RESET has a Schmitt trigger

input which results in a clean reset function when using external

resistor/capacitor generated pulses. See Table I, Control-Logic

Truth.

POWER SHUTDOWN (SHDN)

Maximum power savings can be achieved by using the power

shutdown control function. This hardware-activated feature is

controlled by the active low input SHDN pin. This pin has a

Schmitt trigger input which helps to desensitize it to slowly

changing inputs. By placing a logic low on this pin the internal

consumption of the AD7397 or AD7397 is reduced to nanoamp

levels, guaranteed to 1.5 µA maximum over the operating tem-

perature range. If power is present at all times on the V

DD

pin

while in the shutdown mode, the internal DAC register will

retain the last programmed data value. This data will be used

when the part is returned to the normal active state by placing

the DAC back to its programmed voltage setting. Shutdown

recovery time measures 80 µs. In the shutdown state the DAC

output amplifier exhibits an open-circuit high-resistance state.

Any load connected will stabilize at its termination voltage. If

the power shutdown feature is not needed then the user should

tie the SHDN pin to the V

voltage thereby disabling this

DD

function.

UNIPOLAR OUTPUT OPERATION

This is the basic mode of operation for the AD7396. As shown

in Figure 29, the AD7396 has been designed to drive loads as

low as 5 kΩ in parallel with 100 pF. The code table for this

operation is shown in Table II.

+2.7V TO +5.5V

R

0.01mF

EXT

REF

mC

16/14

V

DD

AD7396

V

REF

DAC A

DIGITAL

DAC B

DGND AGND

DIGITAL INTERFACE

CIRCUITRY OMITTED

FOR CLARITY.

75kV

75kV

0.1mF 10mF

V

OUTA

100pF

V

OUTB

100pF

Figure 29. Unipolar Output Operation

Table II. Unipolar Code Table

Hexadecimal Decimal Output

Number Number Voltage (V)

In DAC Register In DAC Register (V

= 2.5 V)

REF

FFF 4095 2.4994

801 2049 1.2506

800 2048 1.2500

7FF 2047 1.2494

000 0 0

The circuit can be configured with an external reference plus

power supply, or powered from a single dedicated regulator or

reference, depending on the application performance requirements.

BIPOLAR OUTPUT OPERATION

Although the AD7397 has been designed for single supply operation, the output can easily be configured for bipolar operation. A typical circuit is shown in Figure 30. This circuit uses a

clean regulated +5 V supply for power, which also provides

the circuit’s reference voltage. Since the AD7397 output span

swings from ground to very near +5 V, it is necessary to choose

an external amplifier with a common-mode input voltage range

that extends to its positive supply rail. The micropower consumption OP196 has been designed just for this purpose and

results in only 50 µA of maximum current consumption. Con-

nection of the equal-value 470 kΩ resistors results in a differen-

tial amplifier mode of operation with a voltage gain of two,

which produces a circuit output span of ten volts, that is,

–5 V to +5 V. As the AD7397 DAC is programmed from zerocode 000

put voltage V

output voltage V

to midscale 200H to full-scale 3FFH, the circuit out-

H

is set at –5 V, 0 V and +5 V (–1 LSB). The

O

is coded in offset binary according to

O

Equation 3.

V

= [(D/512)–1] × 5 (4)

OUT

where D is the decimal code loaded in the AD7397 DAC register. Note that the LSB step size is 10/1024 = 10 mV. This

circuit has been optimized for micropower consumption includ-

ing the 470 kΩ gain setting resistors, which should have low

temperature coefficients to maintain accuracy and matching

(preferably the same resistor material, such as metal film). If

better stability is required, the power supply could be substituted with a precision reference voltage such as the low dropout

REF195, which can easily supply the circuit’s 262 µA of current

and still provide additional power for the load connected to VO.

The micropower REF195 is guaranteed to source 10 mA output

drive current, but consumes only 50 µA internally. If higher

resolution is required, the AD7396 can be used with the addition of two more bits of data inserted into the software coding,

which would result in a 2.5 mV LSB step size. Table III shows

examples of nominal output voltages, V

, provided by the bipo-

O

lar operation circuit application.

–11–REV. 0

AD7396/AD7397

< 262mA

I

SY

+5V

200mA

V

REF

DD

C

AD7397

GND

Figure 30. Bipolar Output Operation

470kV 470kV

< 50mA

V

OUTA

ONLY ONE CHANNEL SHOWN.

DIGITAL INTERFACE CIRCUITRY

OMITTED FOR CLARITY.

OP196

–5V

Hexadecimal Number Decimal Number Analog Output

In DAC Register In DAC Register Voltage (V)

3FF 1023 4.9902

201 513 0.0097

200 512 0.0000

V

O

+5V

BIPOLAR

OUTPUT

SWING

–5V

1FF 511 –0.0097

000 0 –5.0000

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

Table III. Bipolar Code Table

C3425–8–10/98

24

1

0.0118 (0.30)

0.0040 (0.10)

PIN 1

24-Lead SOIC Package

(R-24)

0.6141 (15.60)

0.5985 (15.20)

0.1043 (2.65)

0.0926 (2.35)

0.0500

0.0192 (0.49)

(1.27)

0.0138 (0.35)

BSC

13

12

SEATING

PLANE

0.2992 (7.60)

0.2914 (7.40)

0.4193 (10.65)

0.0125 (0.32)

0.0091 (0.23)

24-Lead Narrow Body Plastic DIP Package

1.275 (32.30)

1.125 (28.60)

24

112

PIN 1

0.022 (0.558)

0.014 (0.356)

0.100 (2.54)

0.3937 (10.00)

88

08

0.0291 (0.74)

0.0098 (0.25)

0.0500 (1.27)

0.0157 (0.40)

3 458

0.210

(5.33)

MAX

0.200 (5.05)

0.125 (3.18)

24-Lead Thin Surface Mount TSSOP Package

(RU-24)

0.311 (7.90)

0.303 (7.70)

24 13

BSC

(N-24)

0.070 (1.77)

0.045 (1.15)

13

0.280 (7.11)

0.240 (6.10)

0.060 (1.52)

0.015 (0.38)

0.150

(3.81)

MIN

SEATING

PLANE

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

0.195 (4.95)

0.115 (2.93)

0.177 (4.50)

0.006 (0.15)

0.002 (0.05)

SEATING

PLANE

0.169 (4.30)

1

PIN 1

0.0256 (0.65)

BSC

0.0118 (0.30)

0.0075 (0.19)

12

–12–

0.256 (6.50)

0.246 (6.25)

0.0433

(1.10)

MAX

0.0079 (0.20)

0.0035 (0.090)

88

08

PRINTED IN U.S.A.

0.028 (0.70)

0.020 (0.50)

REV. 0

Loading...

Loading...