ANALOG DEVICES AD5764 Service Manual

Complete Quad, 16-Bit, High Accuracy,

Data Sheet

FEATURES

Complete quad, 16-bit digital-to-analog

converter (DAC)

Programmable output range

±10 V, ±10.2564 V, or ±10.5263 V

±1 LSB maximum INL error, ±1 LSB maximum DNL error

Low noise: 60 nV/√Hz

Settling time: 10 μs maximum

Integrated reference buffers

Output control during power-up/brownout

Programmable short-circuit protection

Simultaneous updating via

Asynchronous

Digital offset and gain adjust

Logic output control pins

DSP-/microcontroller-compatible serial interface

Temperature range: −40°C to +85°C

iCMOS process technology

CLR

to zero code

LDAC

1

Serial Input, Bipolar Voltage Output DAC

AD5764

GENERAL DESCRIPTION

The AD5764 is a quad, 16-bit, serial input, bipolar voltage

output DAC that operates from supply voltages of ±11.4 V to

±16.5 V. Nominal full-scale output range is ±10 V. The AD5764

provides integrated output amplifiers, reference buffers, and

proprietary power-up/power-down control circuitry. The part

also features a digital I/O port that is programmed via the serial

interface. The part incorporates digital offset and gain adjust

registers per channel.

The AD5764 is a high performance converter that offers guaranteed monotonicity, integral nonlinearity (INL) of ±1 LSB, low

noise, and 10 µs settling time. During power-up (when the

supply voltages are changing), VOUTx is clamped to 0 V via a

low impedance path.

The AD5764 uses a serial interface that operates at clock rates of

up to 30 MHz and is compatible with DSP and microcontroller

interface standards. Double buffering allows the simultaneous

updating of all DACs. The input coding is programmable to

APPLICATIONS

Industrial automation

Open-loop/closed-loop servo control

Process control

Data acquisition systems

Automatic test equipment

Automotive test and measurement

High accuracy instrumentation

either twos complement or offset binary formats. The asynchronous clear function clears the data register to either bipolar zero or

zero scale depending on the coding used. The AD5764 is ideal

for both closed-loop servo control and open-loop control applications. The AD5764 is available in a 32-lead TQFP, and offers

guaranteed specifications over the −40°C to +85°C industrial

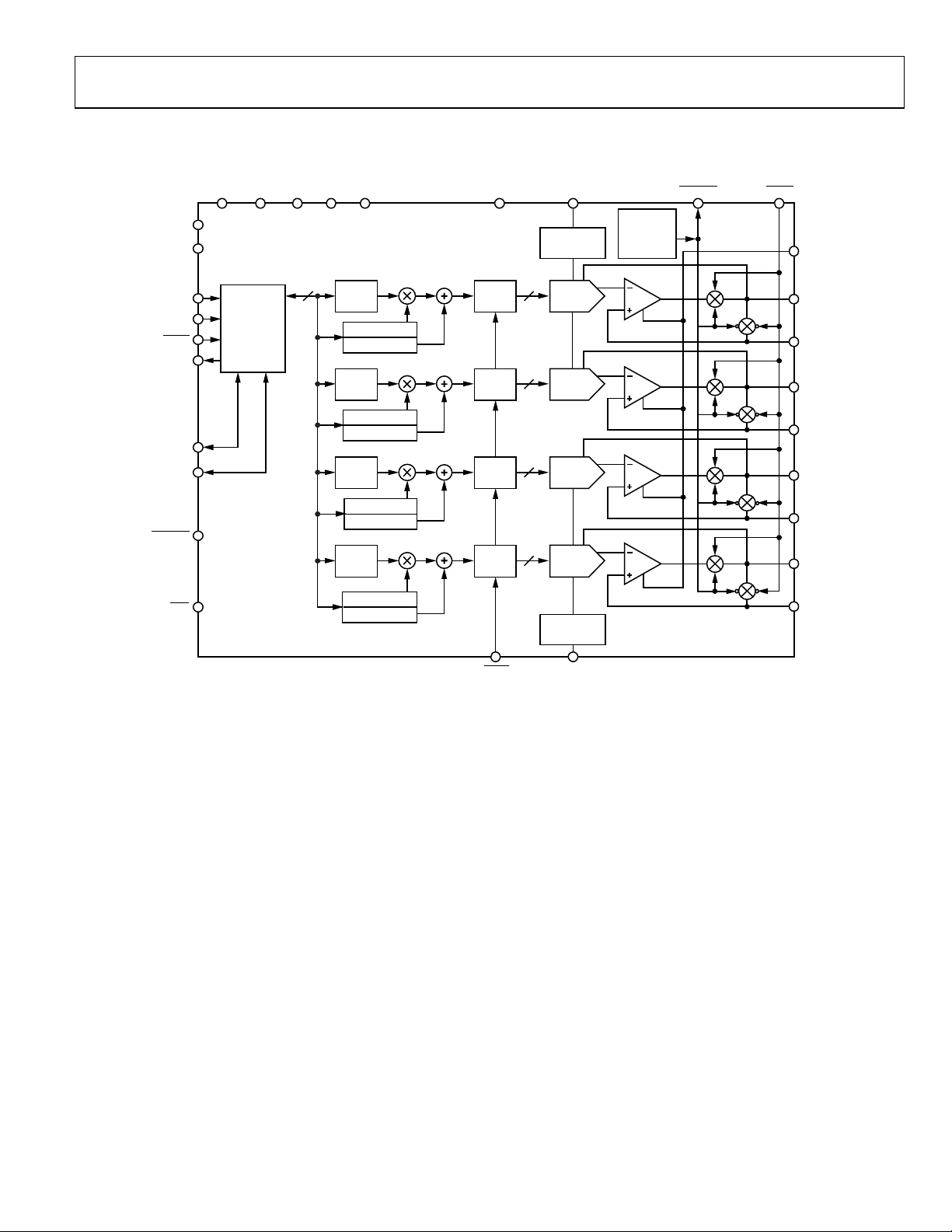

temperature range. See Figure 1 for the functional block diagram.

Table 1. Related Devices

Part No. Description

AD5764R AD5764 with internal voltage reference

AD5744R

Complete quad, 14-bit, high accuracy, serial

input, bipolar voltage output DAC with

internal voltage reference

1

For analog systems designers within industrial/instrumentation equipment OEMs who need high performance ICs at higher voltage levels, iCMOS® is a technology

platform that enables the development of analog ICs capable of 30 V and operating at ±15 V supplies, allowing dramatic reductions in power consumption and package

size, and increased ac and dc performance.

Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006–2011 Analog Devices, Inc. All rights reserved.

AD5764 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Functional Block Diagram .............................................................. 3

Specifications..................................................................................... 4

AC Performance Characteristics ................................................ 5

Timing Characteristics ................................................................ 6

Absolute Maximum Ratings............................................................ 9

ESD Caution.................................................................................. 9

Pin Configuration and Function Descriptions........................... 10

Typical Performance Characteristics ........................................... 12

Terminology .................................................................................... 17

Theory of Operation ...................................................................... 18

DAC Architecture....................................................................... 18

Reference Buffers........................................................................ 18

Serial Interface ............................................................................ 18

Simultaneous Updating via

LDAC

........................................... 19

Transfer Function .......................................................................20

Asynchronous Clear (

CLR

)....................................................... 20

REVISION HISTORY

9/11—Rev. E to Rev. F

Changed 30 MHz to 50 MHz Throughout.................................... 1

Changes to t

7/11—Rev. D to Rev. E

Changed 30 MHz to 50 MHz Throughout.................................... 1

Changes to t

8/09—Rev. C to Rev. D

Changes to Table 2 and Table 3 Endnotes ..................................... 6

Changes to t

1/09—Rev. B to Rev. C

Changes to General Description Section ...................................... 1

Changes to Figure 1.......................................................................... 3

Changes to Table 2 Conditions ....................................................... 4

Changes to Table 3 Conditions ....................................................... 5

Changes to Table 4 Conditions ....................................................... 6

Changes to Figure 5.......................................................................... 8

Changes to Table 5............................................................................ 9

Changes to Table 6.......................................................................... 10

Changes to Figure 34...................................................................... 19

Changes to Table 7 and Table 10................................................... 20

Added Table 8; Renumbered Sequentially .................................. 20

Changes to Table 11 and Table 12 ................................................ 21

Changes to Digital Offset and Gain Control Section ................ 24

, t2, and t3 Parameters, Table 4.................................. 6

1

, t2, and t3 Parameters, Table 4.................................. 6

1

Parameter and Endnotes, Table 4 ........................... 7

6

Rev. F | Page 2 of 28

Function Register ....................................................................... 21

Data Register............................................................................... 21

Coarse Gain Register ................................................................. 21

Fine Gain Register...................................................................... 22

Offset Register ............................................................................ 22

Offset and Gain Adjustment Worked Example...................... 23

Design Features............................................................................... 24

Analog Output Control............................................................. 24

Digital Offset and Gain Control............................................... 24

Programmable Short-Circuit Protection ................................ 24

Digital I/O Port........................................................................... 24

Local Ground Offset Adjust...................................................... 24

Applications Information.............................................................. 25

Typical Operating Circuit ......................................................... 25

Layout Guidelines........................................................................... 27

Galvanically Isolated Interface ................................................. 27

Microprocessor Interfacing....................................................... 27

Evaluation Board........................................................................ 27

Outline Dimensions....................................................................... 28

Ordering Guide .......................................................................... 28

Changes to Table 20 ....................................................................... 26

Deleted AD5764 to MC68HC11 Interface Section.................... 27

Deleted Figure 38; Renumbered Sequentially ............................ 27

Deleted AD5764 to 8XC51 Interface Section, Figure 39,

AD5764 to ADSP-2101 Interface Section, Figure 40, and

AD5764 to PIC16C6x/PIC16C7x Interface Section .................. 28

04/08—Rev. A to Rev. B

Changes to Table Summary Statement, Specifications Section...4

Changes to Power Requirements Parameter, Table 2 and

Table Summary Statement................................................................5

Changes to t

Parameter, Table 4 ....................................................6

16

Changes to Table 6.......................................................................... 10

Changed V

to AVSS/AVDD in Typical Performance

SS/VDD

Characteristics Section .................................................................. 13

Changes to Table 16 ....................................................................... 22

Changes to Table 18 ....................................................................... 23

Changes to Typical Operating Circuit Section........................... 28

Changes to AD5764 to ADSP-2101 Section ............................... 29

Changes to Ordering Guide.......................................................... 30

1/07—Rev. 0 to Rev. A

Changes to Absolute Maximum Ratings..................................... 10

Changes to Figure 25 and Figure 26............................................. 16

3/06—Revision 0: Initial Version

Data Sheet AD5764

FUNCTIONAL BLOCK DIAGRAM

DV

DGND

AVDDAVSSAVDDAV

PGND

CC

SS

AD5764

REFABREFGND

REFERENCE

BUFFERS

VOLTAGE

MONITOR

AND

CONTROL

RSTINRSTOUT

ISCC

SDIN

SCLK

SYNC

SDO

BIN/2sCOMP

CLR

16

INPUT

SHIFT

REGISTER

AND

CONTRO L

LOGIC

D0

D1

INPUT

REG A

GAIN REG A

OFFSET REG A

INPUT

REG B

GAIN REG B

OFFSET REG B

INPUT

REG C

GAIN REG C

OFFSET REG C

INPUT

REG D

GAIN REG D

OFFSET REG D

16

DATA

REG A

DATA

REG B

DATA

REG C

DATA

REG D

LDAC REFCD

16

16

16

DAC A

DAC B

DAC C

DAC D

REFERENCE

BUFFERS

G1

G1

G1

G1

G2

G2

G2

G2

VOUTA

AGNDA

VOUTB

AGNDB

VOUTC

AGNDC

VOUTD

AGNDD

05303-001

Figure 1.

Rev. F | Page 3 of 28

AD5764 Data Sheet

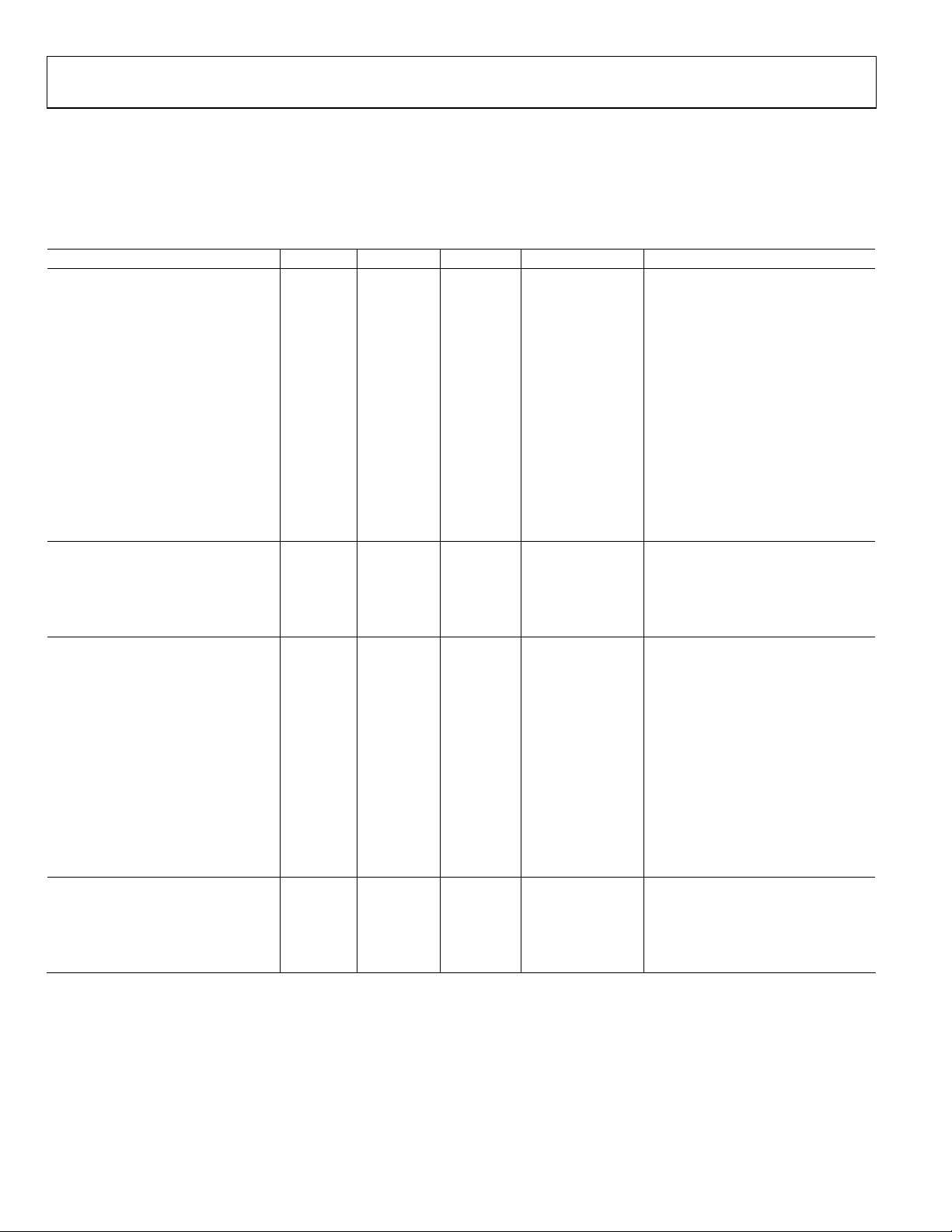

SPECIFICATIONS

AVDD = 11.4 V to 16.5 V, AVSS = −11.4 V to −16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;

= 2.7 V to 5.25 V, R

DV

CC

guaranteed to +105°C with degraded performance. All specifications T

Table 2.

Parameter A Grade B Grade C Grade Unit Test Conditions/Comments

ACCURACY Outputs unloaded

Resolution 16 16 16 Bits

Relative Accuracy (INL) ±4 ±2 ±1 LSB max

Differential Nonlinearity ±1 ±1 ±1 LSB max Guaranteed monotonic

Bipolar Zero Error ±2 ±2 ±2 mV max

Bipolar Zero Temperature

Coefficient (TC)

1

Zero-Scale Error ±2 ±2 ±2 mV max

Zero-Scale TC1 ±2 ±2 ±2 ppm FSR/°C max

Gain Error ±0.02 ±0.02 ±0.02 % FSR max

Gain TC1 ±2 ±2 ±2 ppm FSR/°C max

DC Crosstalk1 0.5 0.5 0.5 LSB max

REFERENCE INPUT1

Reference Input Voltage 5 5 5 V nom ±1% for specified performance

DC Input Impedance 1 1 1 MΩ min Typically 100 MΩ

Input Current ±10 ±10 ±10 μA max Typically ±30 nA

Reference Range 1 to 7 1 to 7 1 to 7 V min to V max

OUTPUT CHARACTERISTICS1

Output Voltage Range2 ±10.5263 ±10.5263 ±10.5263 V min to V max AVDD/AVSS = ±11.4 V, V

±14 ±14 ±14 V min to V max AVDD/AVSS = ±16.5 V, V

Output Voltage Drift vs. Time ±13 ±13 ±13

±15 ±15 ±15

Short-Circuit Current 10 10 10 mA typ R

Load Current ±1 ±1 ±1 mA max For specified performance

Capacitive Load Stability

R

= ∞ 200 200 200 pF max

LOAD

R

= 10 kΩ 1000 1000 1000 pF max

LOAD

DC Output Impedance 0.3 0.3 0.3 Ω max

DIGITAL INPUTS DVCC = 2.7 V to 5.25 V, JEDEC compliant

Input High Voltage, VIH 2 2 2 V min

Input Low Voltage, VIL 0.8 0.8 0.8 V max

Input Current ±1 ±1 ±1 μA max Per pin

Pin Capacitance 10 10 10 pF max Per pin

= 10 kΩ, CL = 200 pF. Temperature range: −40°C to +85°C; typical at +25°C. Device functionality is

LOAD

to T

MIN

, unless otherwise noted.

MAX

At 25°C; error at other temperatures

obtained using bipolar zero TC

±2 ±2 ±2 ppm FSR/°C max

At 25°C; error at other temperatures

obtained using zero-scale TC

At 25°C; error at other temperatures

obtained using gain TC

ppm FSR/

500 hours typ

ppm FSR/

1000 hours typ

= 6 kΩ, see Figure 31

ISCC

REFIN

REFIN

= 5 V

= 7 V

Rev. F | Page 4 of 28

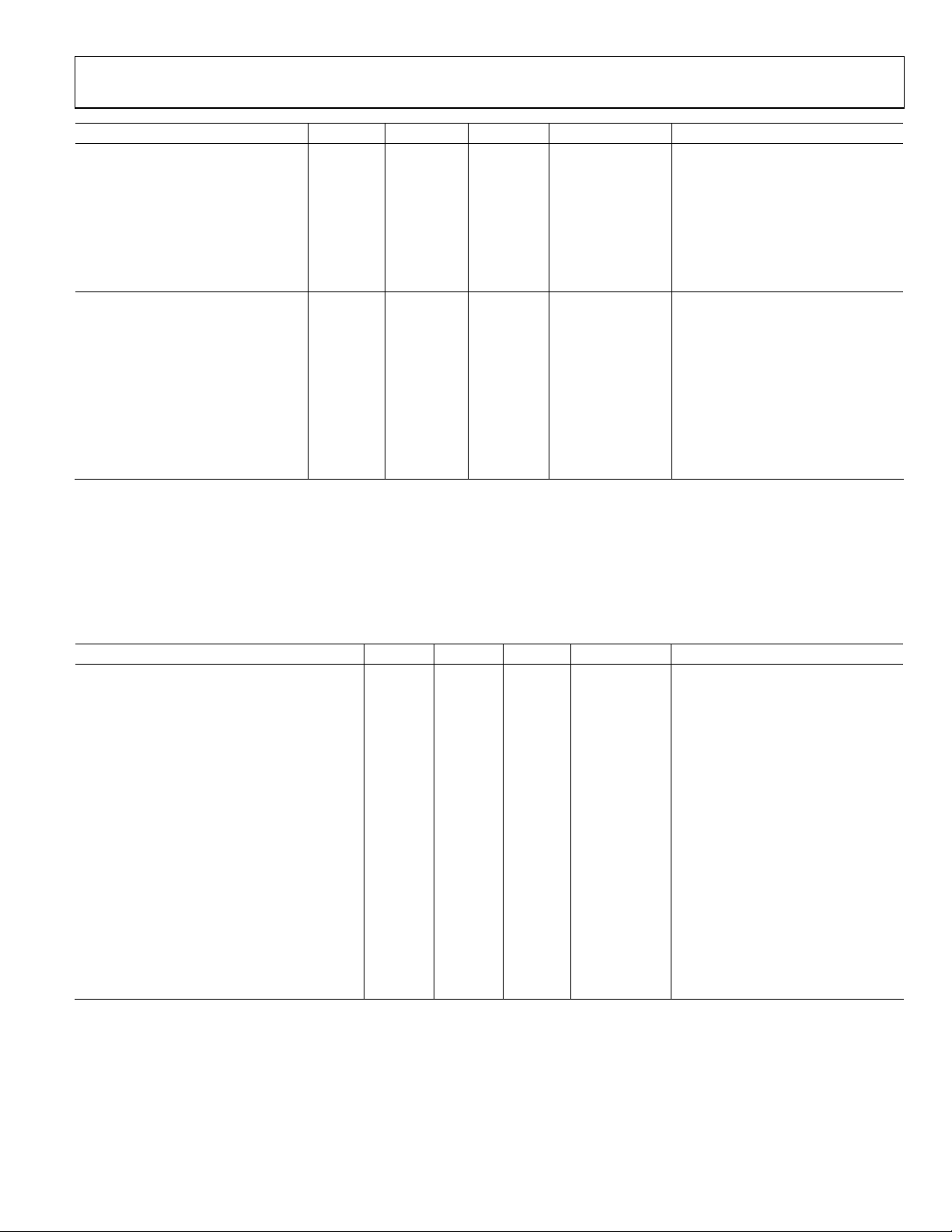

Data Sheet AD5764

Parameter A Grade B Grade C Grade Unit Test Conditions/Comments

DIGITAL OUTPUTS (D0, D1, SDO)1

Output Low Voltage 0.4 0.4 0.4 V max DVCC = 5 V ± 5%, sinking 200 μA

Output High Voltage DVCC − 1 DVCC − 1 DVCC − 1 V min DVCC = 5 V ± 5%, sourcing 200 μA

Output Low Voltage 0.4 0.4 0.4 V max DVCC = 2.7 V to 3.6 V, sinking 200 μA

Output High Voltage DVCC − 0.5 DVCC − 0.5 DVCC − 0.5 V min DVCC = 2.7 V to 3.6 V, sourcing 200 μA

High Impedance Leakage Current ±1 ±1 ±1 μA max SDO only

High Impedance Output

Capacitance

POWER REQUIREMENTS

AVDD/AVSS

DVCC 2.7 to 5.25 2.7 to 5.25 2.7 to 5.25 V min to V max

Power Supply Sensitivity1

∆V

/∆ΑVDD −85 −85 −85 dB typ

OUT

AIDD 3.5 3.5 3.5 mA/channel max Outputs unloaded

AISS 2.75 2.75 2.75 mA/channel max Outputs unloaded

DICC 1.2 1.2 1.2 mA max VIH = DVCC, VIL = DGND, 750 μA typical

Power Dissipation 275 275 275 mW typ ±12 V operation output unloaded

1

Guaranteed by design and characterization; not production tested.

2

Output amplifier headroom requirement is 1.4 V minimum.

5 5 5 pF typ SDO only

±11.4 to

±16.5

±11.4 to

±16.5

±11.4 to

±16.5

V min to V max

AC PERFORMANCE CHARACTERISTICS

AVDD = 11.4 V to 16.5 V, AVSS = −11.4 V to −16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;

DV

= 2.7 V to 5.25 V, R

CC

Table 3.

Parameter A Grade B Grade C Grade Unit Test Conditions/Comments

DYNAMIC PERFORMANCE1

Output Voltage Settling Time 8 8 8 μs typ Full-scale step to ±1 LSB

10 10 10 μs max

2 2 2 μs typ 512 LSB step settling

Slew Rate 5 5 5 V/μs typ

Digital-to-Analog Glitch Energy 8 8 8 nV-sec typ

Glitch Impulse Peak Amplitude 25 25 25 mV max

Channel-to-Channel Isolation 80 80 80 dB typ

DAC-to-DAC Crosstalk 8 8 8 nV-sec typ

Digital Crosstalk 2 2 2 nV-sec typ

Digital Feedthrough 2 2 2 nV-sec typ

Output Noise (0.1 Hz to 10 Hz) 0.1 0.1 0.1 LSB p-p typ

Output Noise (0.1 Hz to 100 kHz) 45 45 45 μV rms max

1/f Corner Frequency 1 1 1 kHz typ

Output Noise Spectral Density 60 60 60 nV/√Hz typ Measured at 10 kHz

Complete System Output Noise Spectral

1

Guaranteed by design and characterization; not production tested.

2

Includes noise contributions from integrated reference buffers, 16-bit DAC, and output amplifier.

Density

2

= 10 kΩ, CL = 200 pF. All specifications T

LOAD

80 80 80 nV/√Hz typ Measured at 10 kHz

MIN

to T

, unless otherwise noted.

MAX

Effect of input bus activity on DAC

outputs

Rev. F | Page 5 of 28

AD5764 Data Sheet

TIMING CHARACTERISTICS

AVDD = 11.4 V to 16.5 V, AVSS = −11.4 V to −16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;

DV

= 2.7 V to 5.25 V, R

CC

= 10 kΩ, CL = 200 pF. All specifications T

LOAD

MIN

to T

, unless otherwise noted.

MAX

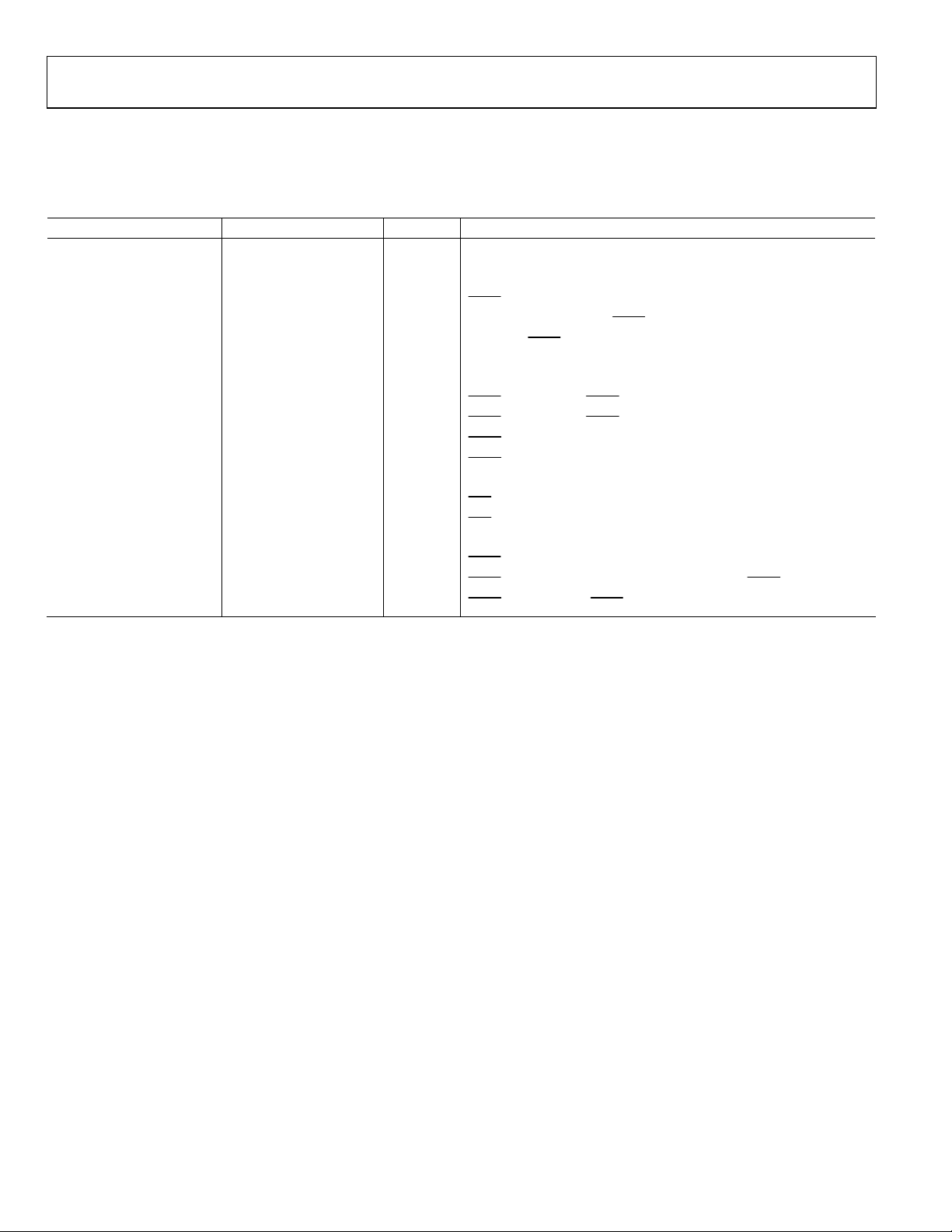

Table 4.

Parameter

1, 2, 3

Limit at T

, T

Unit Description

MIN

MAX

t1 33 ns min SCLK cycle time

t2 13 ns min SCLK high time

t3 13 ns min SCLK low time

t4 13 ns min

4

t

13 ns min

5

t6 90 ns min

falling edge to SCLK falling edge setup time

SYNC

th

SCLK falling edge to SYNC rising edge

24

Minimum SYNC

high time

t7 2 ns min Data setup time

t8 5 ns min Data hold time

t9 1.7 μs min

480 ns min

t10 10 ns min

t11 500 ns max

rising edge to LDAC falling edge (all DACs updated)

SYNC

rising edge to LDAC falling edge (single DAC updated)

SYNC

pulse width low

LDAC

falling edge to DAC output response time

LDAC

t12 10 μs max DAC output settling time

t13 10 ns min

t14 2 μs max

5, 6

t

25 ns max SCLK rising edge to SDO valid

15

t16 13 ns min

t17 2 μs max

t18 170 ns min

1

Guaranteed by design and characterization; not production tested.

2

All input signals are specified with tR = tF = 5 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V.

3

See Figure 2, Figure 3, and Figure 4.

4

Standalone mode only.

5

Measured with the load circuit of Figure 5.

6

Daisy-chain mode only.

pulse width low

CLR

pulse activation time

CLR

rising edge to SCLK falling edge

SYNC

rising edge to DAC output response time (LDAC = 0)

SYNC

falling edge to SYNC rising edge

LDAC

Rev. F | Page 6 of 28

Data Sheet AD5764

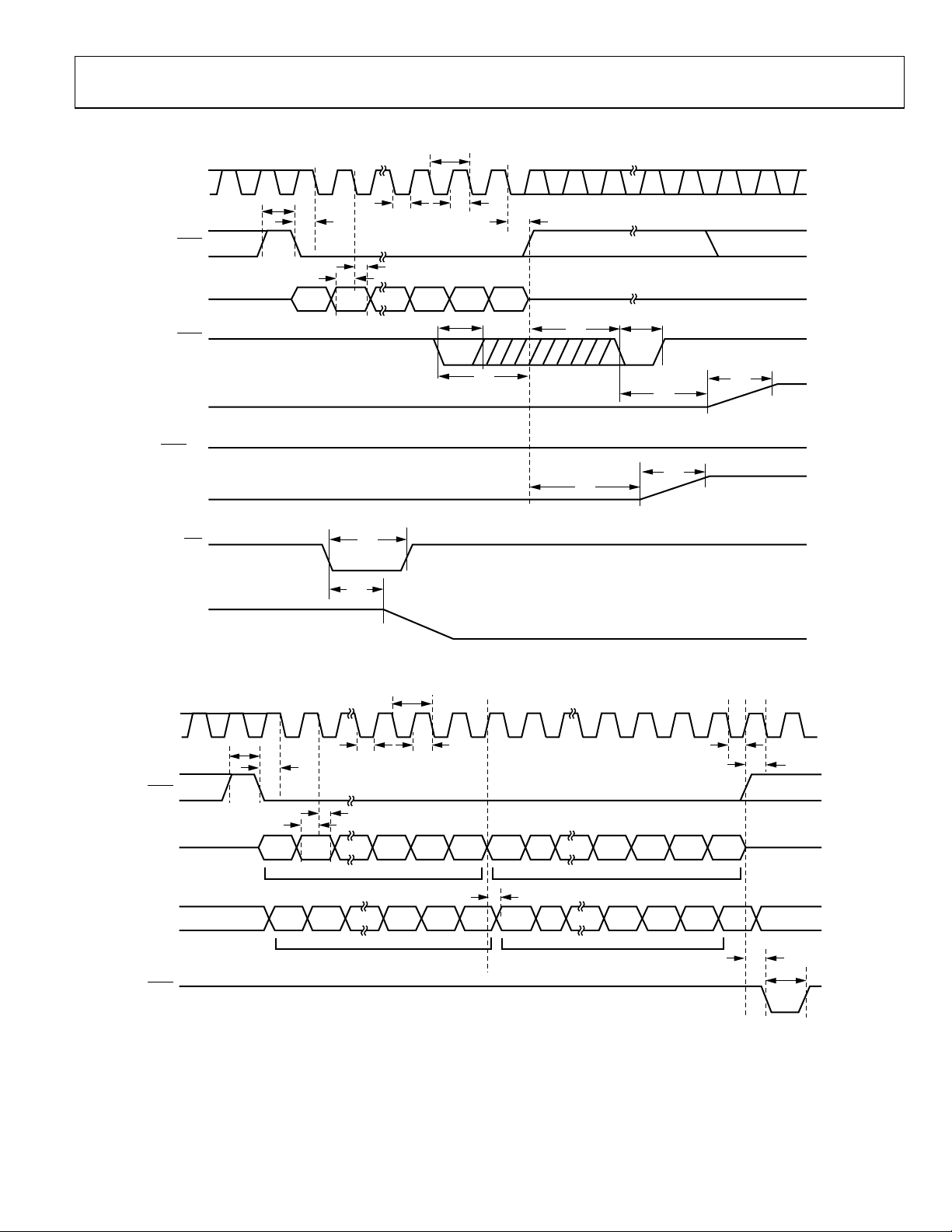

Timing Diagrams

t

1

SCLK

SYNC

SDIN

LDAC

VOUTx

LDAC = 0

VOUTx

CLR

VOUTx

12 24

t

6

t

4

t

7

DB23

t

t

3

t

8

t

13

14

t

2

t

10

t

5

DB0

t

t

9

t

18

t

17

10

t

t

11

t

12

12

SCLK

SYNC

SDIN

SDO

LDAC

Figure 2. Serial Interface Timing Diagram

t

1

24 48

t

6

t

4

t

7

DB23 DB0 DB23 DB0

t

3

t

8

t

2

INPUT WO RD FOR DAC N–1INPUT WORD FOR DAC N

t

15

DB23

INPUT WO RD FOR DAC NUNDEFINED

Figure 3. Daisy-Chain Timing Diagram

DB0

05303-002

t

5

t

16

t

9

t

10

05303-003

Rev. F | Page 7 of 28

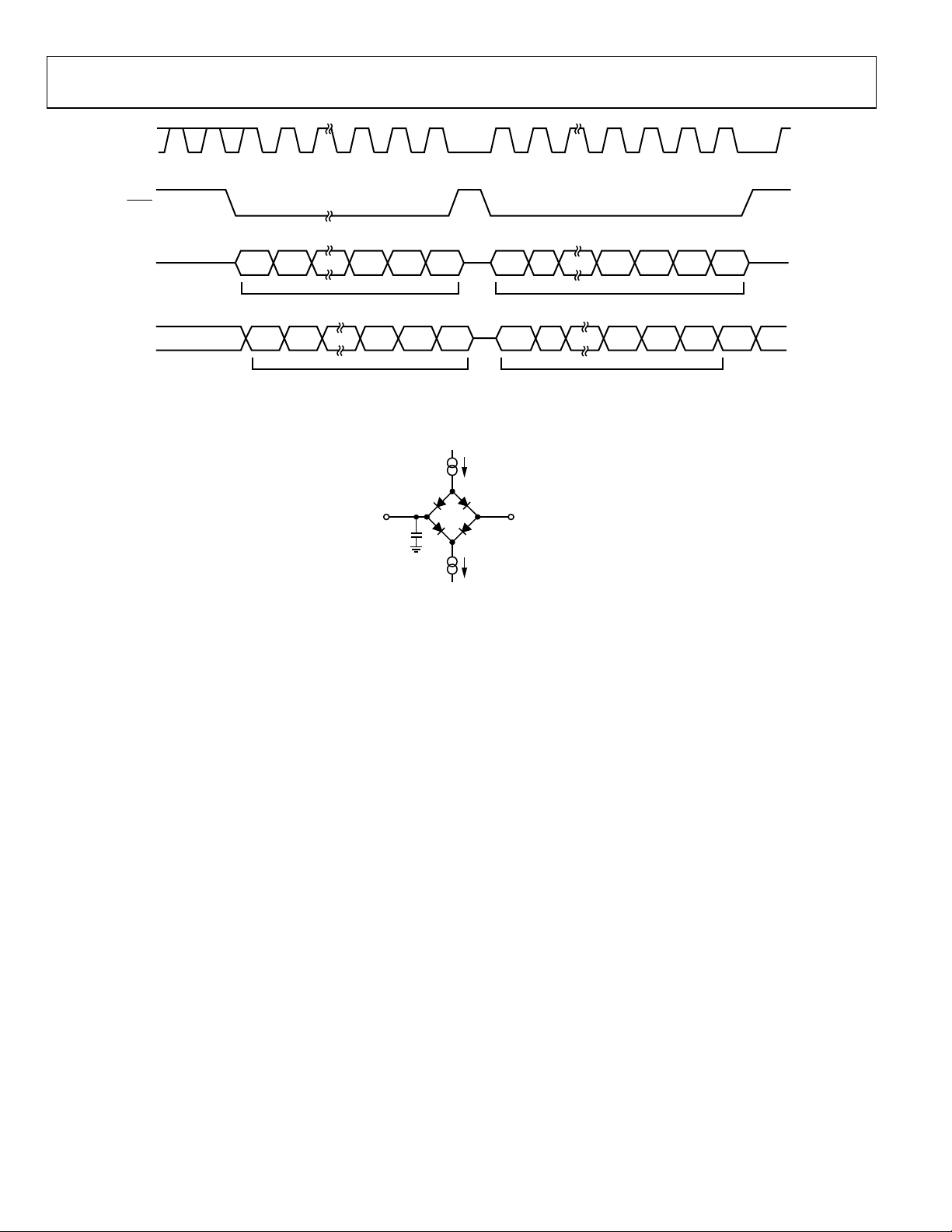

AD5764 Data Sheet

SYNC

T

SCLK

24 48

SDIN

SDO

DB23 DB0 DB23 DB0

INPUT WORD SPECIFIES

REGISTER TO BE READ

UNDEFINED

DB23

NOP CONDITI ON

SELECTED REG ISTER DATA

CLOCKED OUT

DB0

05303-004

Figure 4. Readback Timing Diagram

200µA I

O SDO

PIN

C

L

50pF

200µA I

Figure 5. Load Circuit for SDO Timing Diagram

OL

OH

VOH (MIN) OR

V

(MAX)

OL

05303-005

Rev. F | Page 8 of 28

Data Sheet AD5764

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted. Transient currents of up to

100 mA do not cause SCR latch-up.

Table 5.

Parameter Rating

AVDD to AGNDx, DGND −0.3 V to +17 V

AVSS to AGNDx, DGND +0.3 V to −17 V

DVCC to DGND −0.3 V to +7 V

Digital Inputs to DGND

Digital Outputs to DGND −0.3 V to DVCC + 0.3 V

REFAB, REFCD to AGNDx, PGND −0.3 V to AVDD + 0.3 V

VOUTA, VOUTB, VOUTC, VOUTD to

AGNDx

AGNDx to DGND −0.3 V to +0.3 V

Operating Temperature Range

Industrial −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Junction Temperature (TJ max) 150°C

32-Lead TQFP

θJA Thermal Impedance 65°C/W

θJC Thermal Impedance 12°C/W

Lead Temperature JEDEC industry standard

Soldering J-STD-020

−0.3 V to DV

(whichever is less)

to AVDD

AV

SS

+ 0.3 V or 7 V

CC

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. F | Page 9 of 28

Loading...

Loading...