Dual, 12-Bit, 40 MSPS MCM A/D Converter

a

with Analog Input Signal Conditioning

FEATURES

2 Matched ADCs with Input Signal Conditioning

Selectable Bipolar Input Voltage Range

(ⴞ0.5 V, ⴞ1.0 V, ⴞ2.0 V)

Full MIL-STD-883B Compliant

80 dB Spurious-Free Dynamic Range

Trimmed Channel-Channel Matching

APPLICATIONS

Radar Processing

Communications Receivers

FLIR Processing

Secure Communications

Any I/Q Signal Processing Application

GENERAL DESCRIPTION

The AD10242 is a complete dual signal chain solution including

on-board amplifiers, references, ADCs, and output buffering

providing unsurpassed total system performance. Each channel is

laser trimmed for gain and offset matching and provides channelto-channel crosstalk performance better than 80 dB. The AD10242

utilizes two each of the AD9632, OP279, and AD9042 in a custom MCM to gain space, performance, and cost advantages over

solutions previously available.

AD10242

The AD10242 operates with ±5.0 V for the analog signal conditioning with a separate 5.0 V supply for the analog-to-digital

conversion. Each channel is completely independent, allowing

operation with independent encode or analog inputs. The AD10242

also offers the user a choice of analog input signal ranges to minimize additional signal conditioning required for multiple functions

within a single system. The heart of the AD10242 is the AD9042,

which is designed specifically for applications requiring wide

dynamic range.

The AD10242 is manufactured on Analog Devices’

MIL-PRF-38534 MCM line and is completely qualified. Units

are packaged in a custom, cofired, ceramic 68-lead gull wing

package and specified for operation from –55°C to +125°C.

Contact the factory for additional custom options including those

that allow the user to ac couple the ADC directly, bypassing the

front end amplifier section. Also see the AD9042 data sheet for

additional details on ADC performance.

PRODUCT HIGHLIGHTS

1. Guaranteed sample rate of 40 MSPS.

2. Dynamic performance specified over entire Nyquist band;

spurious signals @ 80 dBc for –1 dBFS input signals.

3. Low power dissipation: <2 W off ±5.0 V supplies.

4. User defined input amplitude.

5. Packaged in 68-lead ceramic leaded chip carrier.

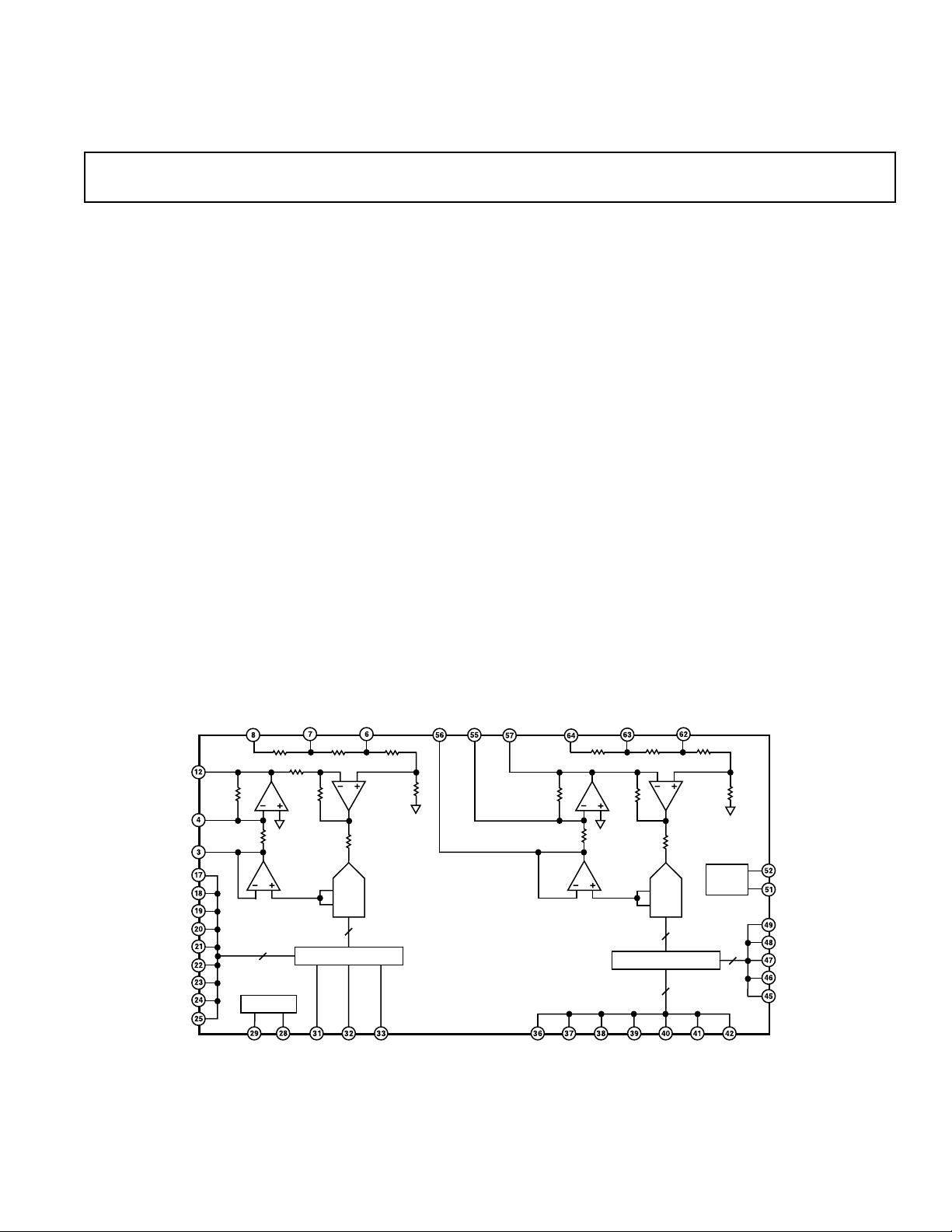

FUNCTIONAL BLOCK DIAGRAM

3

OP279

OP279

9

ENC

A

IN

AD9632

AD9042

V

REF

12

OUTPUT BUFFERING

D9A D10A D11A

(MSB)

AD10242

UPOS

UCOM

UNEG

(LSB) D0A

D1A

D2A

D3A

D4A

D5A

D6A

D7A

D8A

A

IN

TIMING

ENC

2AIN1

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

A

A

UPOSUNEG UCOM

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AIN3

OP279

D0B

D1B D2B D3B D4B D5B D6B

(LSB)

2

IN

OP279

AD9042

OUTPUT BUFFERING

1

IN

AD9632

TIMING

V

REF

12

7

5

ENC

ENC

D11B (MSB)

D10B

D9B

D8B

D7B

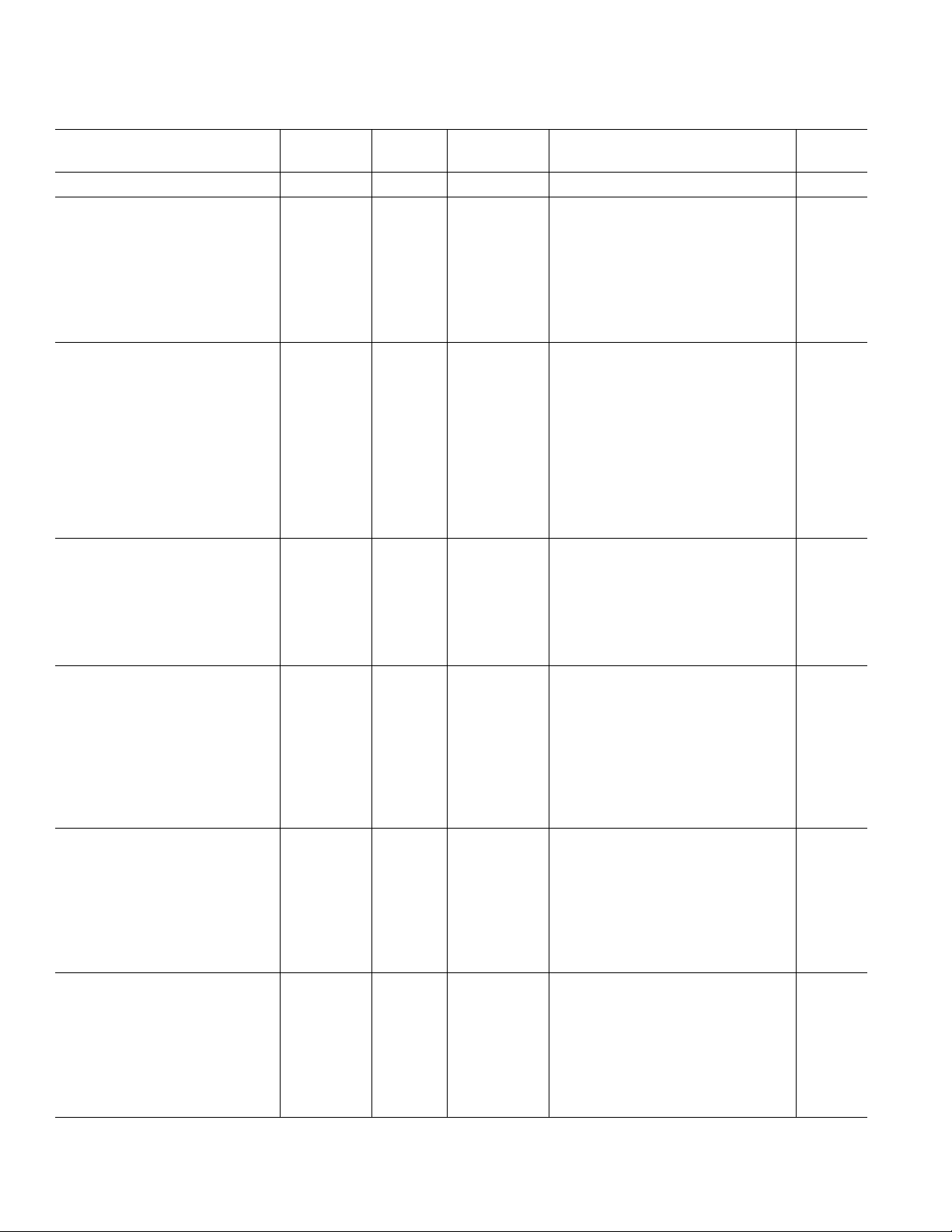

AD10242–SPECIFICATIONS

Electrical Characteristics

(AVCC = +5 V; AVEE = –5.0 V; DVCC = +5 V; applies to each ADC, unless otherwise noted.)

Test Mil AD10242BZ/TZ

Parameter Temp Level Subgroup Min Typ Max Unit

RESOLUTION 12 Bits

DC ACCURACY

No Missing Codes Full VI 1, 2, 3 Guaranteed

Offset Error 25°CI 1 –0.5 ± 0.05 +0.5 % FS

Full VI 2, 3 –2.0 ± 1.0 +2.0 % FS

Offset Error Channel Match Full V ± 0.1 %

Gain Error

1

25°CI 1 –1.0 ± 0.5 +1.0 % FS

Full VI 2, 3 –1.5 ± 0.8 +1.5 % FS

Gain Error Channel Match Full V ± 0.1 %

ANALOG INPUT (A

)

IN

Input Voltage Range

1 Full I ± 0.5 V

A

IN

A

2 Full I ± 1.0 V

IN

AIN3 Full I ± 2V

Input Resistance

1 Full IV 12 99 100 101 Ω

A

IN

AIN2 Full IV 12 198 200 202 Ω

3 Full IV 12 396 400 404 Ω

A

IN

Input Capacitance

Analog Input Bandwidth

ENCODE INPUT

4, 5

2

3

25°CIV 12 0 4.0 7.0 pF

Full V 60 MHz

Logic Compatibility TTL/CMOS

Logic “1” Voltage Full I 1, 2, 3 2.0 5.0 V

Logic “0” Voltage Full I 1, 2, 3 0 0.8 V

Logic “1” Current (V

Logic “0” Current (V

= 5 V) Full I 1, 2, 3 625 800 µA

INH

= 0 V) Full I 1, 2, 3 –400 –300 µA

INL

Input Capacitance 25°CV 12 7.0 pF

SWITCHING PERFORMANCE

Maximum Conversion Rate

Minimum Conversion Rate

6

6

Full VI 4, 5, 6 40 50 MSPS

Full V 12 5 MSPS

Aperture Delay (tA)25°CV 1.0 ns

Aperture Delay Matching 25°CV ± 2.0 ns

Aperture Uncertainty (Jitter) 25°CV 1 ps rms

ENCODE Pulsewidth High 25°CIV 12 12 10 ns

ENCODE Pulsewidth Low 25°CIV 12 10 41ns

Output Delay (tOD) Full IV 12 10 12 14 ns

7

SNR

Analog Input @ 1.2 MHz 25°CV 68 dB

@ 4.85 MHz 25°CI 4 63 66 dB

Full II 5, 6 62 66 dB

@ 9.9 MHz 25°CI 4 63 65 dB

Full II 5, 6 62 65 dB

@ 19.5 MHz 25°CI 4 60 63 dB

Full II 5, 6 59 62 dB

8

SINAD

Analog Input @ 1.2 MHz 25°CV 67 dB

@ 4.85 MHz 25°CI 4 62 65 dB

Full II 5, 6 61 64 dB

@ 9.9 MHz 25°CI 4 60 64 dB

Full II 5, 6 60 63 dB

@ 19.5 MHz 25°CI 4 58 61 dB

Full II 5, 6 58 60 dB

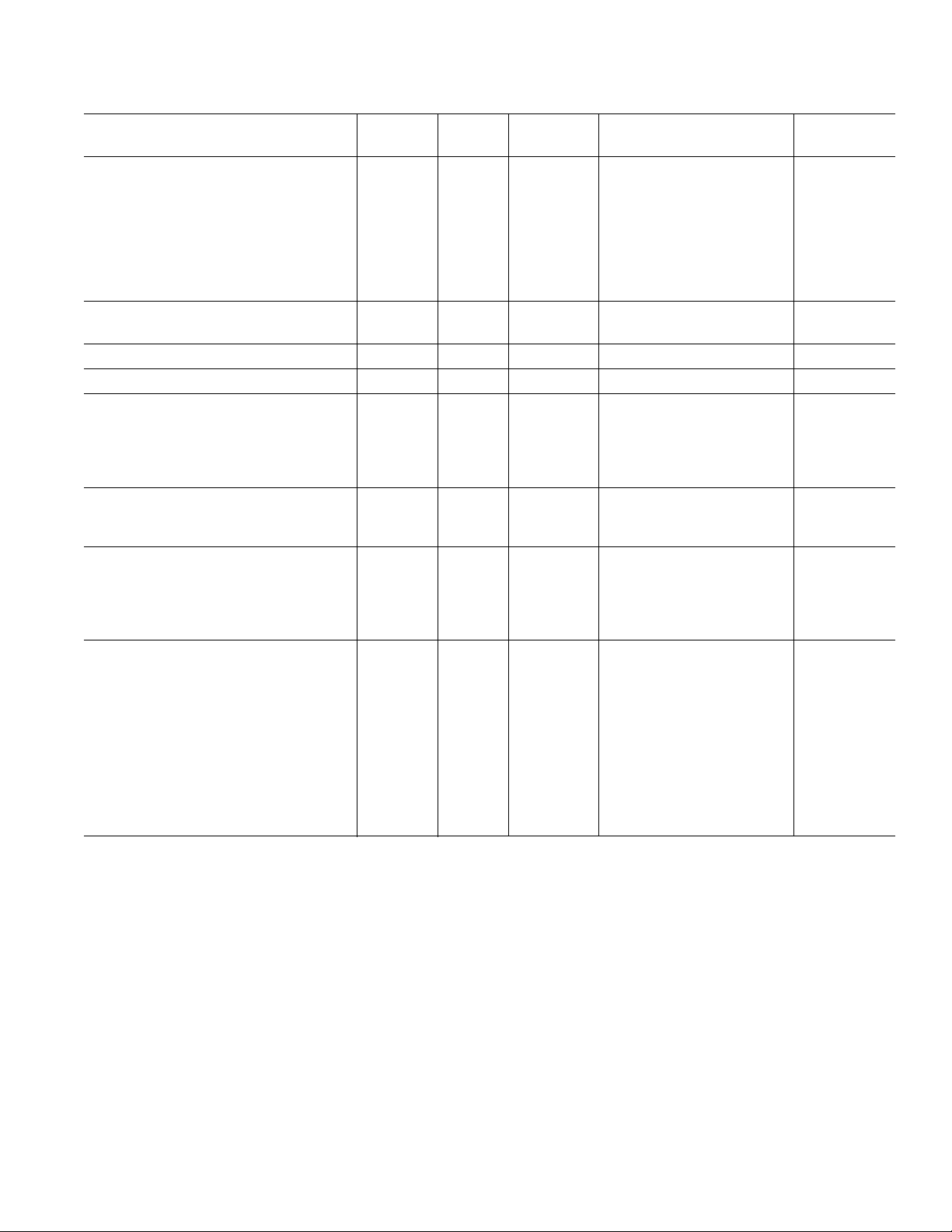

–2–

REV. C

AD10242

Test Mil AD10242BZ/TZ

Parameter Temp Level Subgroup Min Typ Max Unit

SPURIOUS-FREE DYNAMIC RANGE

Analog Input @ 1.2 MHz 25°CI 81 dBFS

@ 4.85 MHz 25°CI 47080 dBFS

@ 9.9 MHz 25°CI 46370 dBFS

@ 19.5 MHz 25°CI 46067 dBFS

TWO-TONE IMD REJECTION

F1, F2 @ –7 dBFS Full II 4, 5, 6 70 76 dBc

CHANNEL-TO-CHANNEL ISOLATION

TRANSIENT RESPONSE 25°CV 10 ns

LINEARITY

Differential Nonlinearity 25°CIV12 0.3 1.0 LSB

(Encode = 20 MHz) Full IV 12 0.5 1.25 LSB

Integral Nonlinearity 25°CV 0.3

(

Encode

= 20 MHz) Full V 0.5 LSB

OVERVOLTAGE RECOVERY TIME

V

= 2.0 × FS Full IV 12 50 100 ns

IN

VIN = 4.0 × FS

DIGITAL OUTPUTS

Logic Compatibility CMOS

Logic “1” Voltage

Logic “0” Voltage

13

14

Output Coding Twos Complement

POWER SUPPLY

AVCC Supply Voltage Full VI 5.0 V

I (AVCC) Current Full V 260 mA

Supply Voltage Full VI –5.0 V

AV

EE

I (AVEE) Current Full V 55 mA

DVCC Supply Voltage Full VI 5.0 V

I (DV

) Current Full V 25 mA

CC

ICC (Total) Supply Current Full I 1, 2, 3 350 400 mA

Power Dissipation (Total) Full I 1, 2, 3 1.75 2.0 W

Power Supply Rejection Ratio (PSRR) Full I 7, 8 0.01 0.02 % FSR/% V

Pass-Band Ripple to 10 MHz Full IV 12 0.2 dB

NOTES

1

Gain tests are performed on AIN3 over specified input voltage range.

2

Input capacitance specifications combine AD9632 die capacitance and ceramic package capacitance.

3

Full power bandwidth is the frequency at which the spectral power of the fundamental frequency (as determined by FFT analysis) is reduced by 3 dB.

4

ENCODE driven by single-ended source; ENCODE bypassed to ground through 0.01 µF capacitor.

5

ENCODE may also be driven differentially in conjunction with ENCODE; see Encoding the AD10242 section for details.

6

Minimum and maximum conversion rates allow for variation in Encode Duty Cycle of 50% ± 5%.

7

Analog Input signal power at –1 dBFS; signal-to-noise ratio (SNR) is the ratio of signal level to total noise (first five harmonics removed). Encode = 40.0 MSPS.

8

Analog Input signal power at –1 dBFS; signal-to-noise and distortion (SINAD) is the ratio of signal level to total noise + harmonics. Encode = 40.0 MSPS.

9

Analog Input signal equals –1 dBFS; SFDR is the ratio of converter full scale to worst spur.

10

Both input tones at –7 dBFS; two-tone intermodulation distortion (IMD) rejection is the ratio of either tone to the worst third order intermod product. f1 = 10.0 MHz

± 100 kHz, 50 kHz ≤ f1 – f2 ≤ 300 kHz.

11

Channel-to-channel isolation tested with A channel grounded and a full-scale signal applied to B channel (A

12

Input driven to 2× and 4× AIN1 range for >4 clock cycles. Output recovers in band in specified time with Encode = 40 MSPS. No foldover guaranteed.

13

Outputs are sourcing 10 µA.

14

Outputs are sinking 10 µA.

All specifications guaranteed within 100 ms of initial power-up regardless of sequencing.

Specifications subject to change without notice.

9

Full II 5, 6 70 79 dBFS

Full II 5, 6 63 69 dBFS

Full II 5, 6 60 66 dBFS

10

11

25°CIV12 75 80 dB

LSB

12

Full IV 12 75 200 ns

Full I 1, 2, 3 3.5 4.2 V

Full I 1, 2, 3 0.45 0.65 V

S

1).

IN

REV. C

–3–

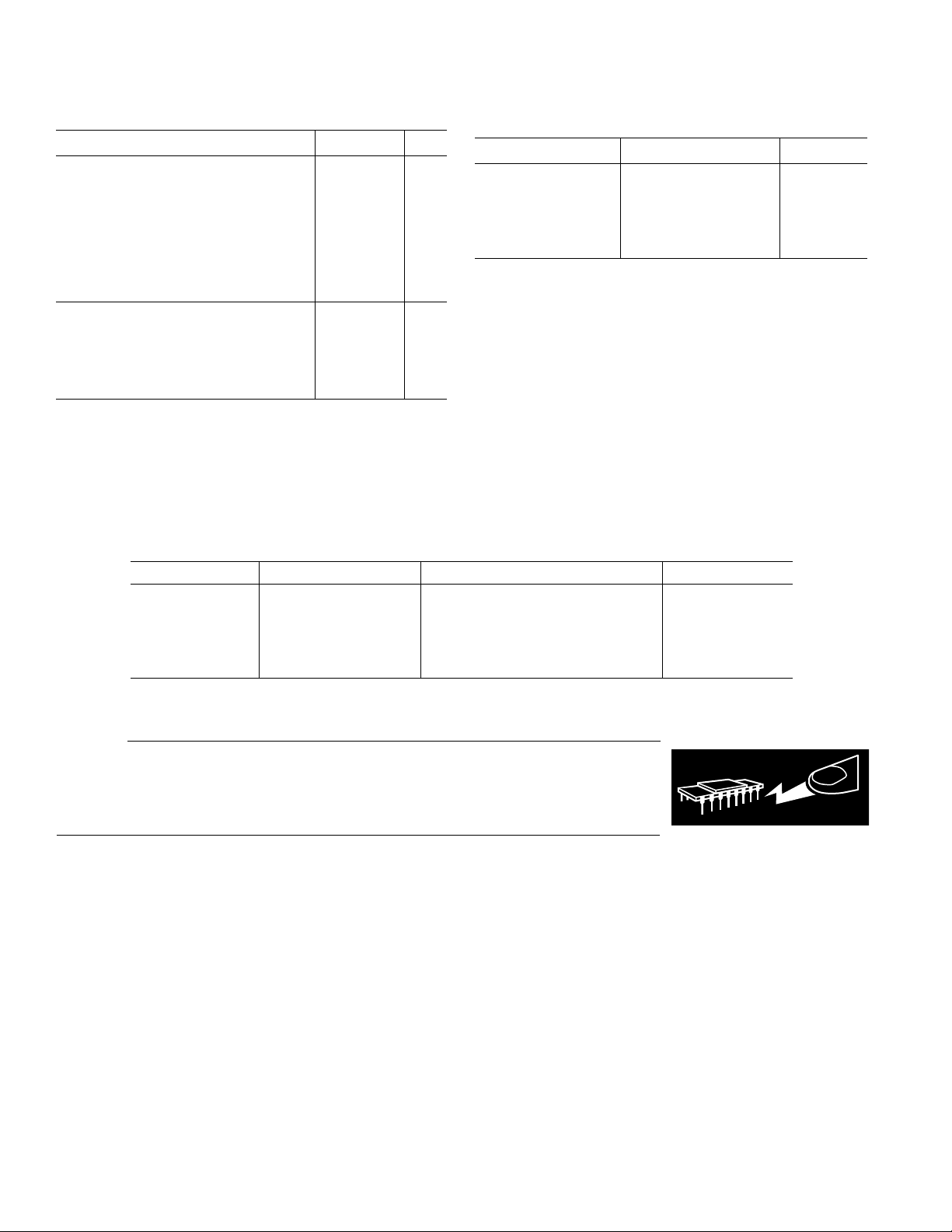

AD10242

ABSOLUTE MAXIMUM RATINGS

1

Parameter Min Max Unit

ELECTRICAL

V

Voltage 0 7 V

CC

Voltage –7 0 V

V

EE

Analog Input Voltage V

EE

V

V

CC

Analog Input Current –10 +10 mA

Digital Input Voltage (ENCODE) 0 V

CC

V

ENCODE, ENCODE Differential Voltage 4 V

Digital Output Current –40 +40 mA

ENVIRONMENTAL

2

Operating Temperature (Case) –55 +125 °C

Maximum Junction Temperature 175 °C

Lead Temperature (Soldering, 10 sec) 300 °C

Storage Temperature Range (Ambient) –65 +150 °C

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and beyond

which the serviceability of the circuit may be impaired. Functional operability is not

necessarily implied. Exposure to absolute maximum rating conditions for an

extended period of time may affect device reliability.

2

Typical thermal impedances for “Z” package: θJC = 11°C/W; θJA = 30°C/W.

ORDERING GUIDE

Table I. Output Coding

MSB LSB Base 10 Input

0111111111111 2047 +FS

0000000000001 +1

0000000000000 0 0.0 V

1111111111111 –1, 4095

1000000000000 –2047, 2048 –FS

EXPLANATION OF TEST LEVELS

Test Level

I–100% Production Tested.

II – 100% production tested at 25°C, and sample tested at

specified temperatures. AC testing done on sample basis.

III – Sample Tested Only.

IV – Parameter is guaranteed by design and characterization

testing.

V–Parameter is a typical value only.

VI – All devices are 100% production tested at 25°C; sample

tested at temperature extremes.

M

odel Temperature Range Package Description Package Option

AD10242BZ –40°C to +85°C (Case) 68-Lead Ceramic Leaded Chip Carrier Z-68A

AD10242TZ –55°C to +125°C (Case) 68-

Lead

Ceramic

Leaded Chip

Carrier Z-68A

AD10242TZ/883B –55°C to +125°C (Case) 68-Lead Ceramic Leaded Chip Carrier Z-68A

5962-9581501HXA –55°C to +125°C (Case) 68-

Lead

Ceramic

Leaded Chip

Carrier Z-68A

AD10242/PCB 25°C Evaluation Board with AD10242BZ

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD10242 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–4–

REV. C

10

GNDA

11

GNDA

12

UPOSA

13

AV

EE

14

AV

CC

15

NC

16

NC

D1A

D2A

D3A

D4A

D5A

D6A

D7A

D8A

GNDA

17

18

19

20

21

22

23

24

25

26

(LSB) D0A

NC = NO CONNECT

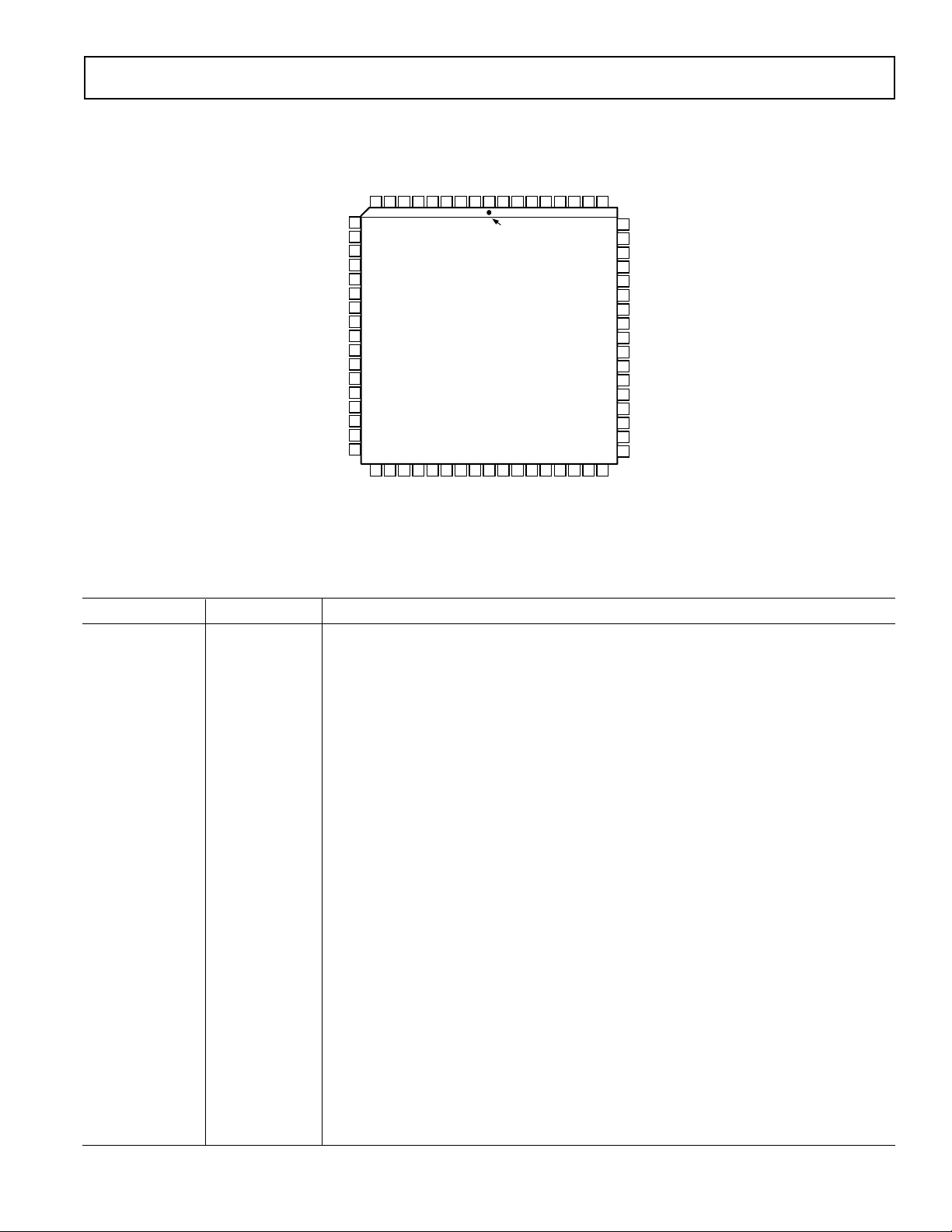

PIN CONFIGURATION

68-Lead Ceramic Leaded Chip Carrier

A3

A2

A1

IN

IN

IN

A

A

GNDA

UCOMA

UNEGA

GNDA

SHIELD

GNDA

A

9618765 676665 64 63 62432168

GNDB

PIN 1

IDENTIFIER

AD10242

TOP VIEW

(Not to Scale)

27 4328 29 30 31 32 33 34 35 36 37 38 39 40 41 42

GNDA

ENCODEA

CC

D9A

DV

ENCODEA

D10A

(MSB) D11A

NC

NC

(LSB) D0B

EEAVCC

AV

D1B

D2B

B3

GNDB

A

D3B

D4B

B2

B1

IN

IN

IN

A

A

GNDB

D6B

D5B

GNDB

60

GNDB

59

GNDB

58

GNDB

UPOSB

57

UNEGB

56

55

UCOMB

54

GNDB

53

GNDB

52

ENCODEB

51

ENCODEB

50

DV

49

D11B (MSB)

48

D10B

47

D9B

46

D8B

45

D7B

44

GNDB

AD10242

CC

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1 SHIELD Internal Ground Shield between Channels.

2, 5, 9–11, 26–27 GNDA A Channel Ground. A and B grounds should be connected as close to the device as possible.

3 UNEGA Unipolar Negative.

4 UCOMA Unipolar Common.

6A

7A

8A

A1 Analog Input for A Side ADC (Nominally ± 0.5 V).

IN

A2 Analog Input for A Side ADC (Nominally ± 1.0 V).

IN

A3 Analog Input for A Side ADC (Nominally ± 2.0 V).

IN

12 UPOSA Unipolar Positive.

13 AV

14 AV

EE

CC

Analog Negative Supply Voltage (Nominally –5.0 V or –5.2 V).

Analog Positive Supply Voltage (Nominally 5.0 V).

15, 16, 34, 35 NC No Connect.

17–25, 31–33 D0A–D11A Digital Outputs for ADC A. (D0 LSB.)

28 ENCODEA ENCODE is the complement of ENCODE.

29 ENCODEA Data conversion is initiated on the rising edge of the ENCODE input.

30, 50 DV

CC

Digital Positive Supply Voltage (Nominally 5.0 V).

36–42, 45–49 D0B–D11B Digital Outputs for ADC B. (D0 LSB.)

43–44, 53–54, GNDB B Channel Ground. A and B grounds should be connected as close to the device

58–61, 65, 68 as possible.

51 ENCODEB Data conversion is initiated on the rising edge of the ENCODE input.

52 ENCODEB ENCODE is the complement of ENCODE.

55 UCOMB Unipolar Common.

56 UNEGB Unipolar Negative.

57 UPOSB Unipolar Positive.

62 A

63 A

64 A

66 AV

67 AV

B1 Analog Input for B Side ADC (Nominally ± 0.5 V).

IN

B2 Analog Input for B Side ADC (Nominally ± 1.0 V).

IN

B3 Analog Input for B Side ADC (Nominally ± 2.0 V).

IN

CC

EE

Analog Positive Supply Voltage (Nominally 5.0 V).

Analog Negative Supply Voltage (Nominally –5.0 V or –5.2 V).

REV. C

–5–

Loading...

Loading...