Page 1

查询DS42516供应商

DS42516

Stacked Multi-Chip Package (MCP) Flash Memory and SRAM

Am29DL324D Bottom Boot 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 V o lt-only,

Simultaneous Operation Flash Memory and 4 Mbit (512 K x 8-Bit/ 256 K x 16-Bit) Static RAM

DISTINCTIVE CHARACTERISTICS

MCP Features

■ Power supply voltage of 2.7 to 3.3 volt

■ High performance

— 90 ns maximum access time

■ Package

— 73-Ball FBGA

■ Operating Temperature

— –25°C to +85°C

Flash Memory Features

ARCHITECTURAL ADVANTAGES

■ Simultaneous Read/Write oper at io ns

— Data can be continuously read from one bank while

executing erase/program functions in other bank

— Zero latency between read and write operations

■ Secured Silicon (SecSi) Sector: Extra 64 KByte sector

— Factory locked and identifiable: 16 bytes available for

secure, random factory Electronic Serial Number; verifiable

as factory locked through autoselect function.

— Customer lockable: Can be read, programmed, or erased

just like other sectors. Once locked, data cannot be changed

■ Zero Power Operation

— Sophisticated power management circuits reduce power

consumed during inactive periods to nearly zero

■ Bottom boot block

■ Manufactured on 0.23 µm process technology

■ Compatible with JEDEC standards

— Pinout and software compatible with single-power-supply

flash standard

PERFORMANCE CHARACTERISTICS

■ High performance

— Access time as fast 70 ns

— Program time: 7 µs/word typical utilizing Accelerate function

■ Ultra low power consump tion (typical values)

— 2 mA active read current at 1 MHz

— 10 mA active read current at 5 MHz

— 200 nA in standby or automatic sleep mode

■ Minimum 1 mill i on write cycl es guaranteed per sector

■ 20 Year data retention at 125°C

— Reliable operation for the life of the system

SOFTWARE FEATURES

■ Data Management Software (DMS)

— AMD-supplied software manages data programming and

erasing, enabling EEPROM emulation

— Eases sector erase limitations

■ Supports Common Flash Memory Interface (CFI)

■ Erase Suspend/Erase Resume

— Suspends erase operations to allow programming in same

bank

■ Data# Polling and Toggle Bits

— Provides a software method of detecting the status of

program or erase cycles

■ Unlock Bypass Program command

— Reduces overall programming time when issuing multiple

program command sequences

HARDWARE FEATURES

■ Any combination of sectors can be erased

■ Ready/Busy# output (RY/BY#)

— Hardware method for detecting program or erase cycle

completion

■ Hardware reset pin (RESET#)

— Hardware method of resetting the internal state machine to

reading array data

■ WP#/ACC input pin

— Write protect (WP#) function allows protection of two outermost

boot sectors, regardless of sector protect status

— Acceleration (ACC) function accelerates program timing

■ Sector protection

— Hardware method of locking a sector, either in-system or

using programming equipment, to prevent any program or

erase operation within that sector

— Temporary Sector Unprotect allows changing data in

protected sectors in-system

SRAM Features

■ Power dissipation

— Operating: 50 mA maximum

— Standby: 7 µA maximum

■ CE1s# and CE2s Chip Select

■ Power down features us in g C E 1s # and CE2s

■ Data retention supply voltage: 1.5 to 3.3 volt

■ Byte data control: LB#s (DQ0–DQ7), UB#s (DQ8–DQ15)

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate thi s product. AMD reserves t he right to chan ge or discontinue work o n this proposed

product without notice.

Refer to AMD’s Website (www.amd.com) for the latest information.

Publication# 23763 Rev: B Amendment/1

Issue Date: March 15, 2001

Page 2

GENERAL DESCRIPTION

Am29DL324 Features

The Am2 9DL324 is a 3 2 megabit, 3.0 volt-only flash

memory devices, organiz ed as 2,097, 152 words of 16

bits each or 4,194,304 bytes of 8 bits each. Word

mode data appears on DQ0–DQ15; byte mode data

appears on DQ0–DQ7. The device is designed to be

programmed in-system with the standard 3.0 volt V

supply, and can also be progr ammed in standar d

EPROM programmers.

The device is available with an access time of 90 ns.

The device is offered in a 73-ball FBGA package.

Standard con trol pins—chip enable (CE#f), write enable (WE#), and out put enab le (OE #)—c ontro l nor mal

read and write operations, and avoid bus contention

issues.

The device requires only a single 3.0 volt power sup-

ply for both read and write functions. Internally

generated and regulated voltag es are pr ovided for the

program and erase operations.

CC

Simultaneous Read/Write Ope rations with

Zero Latency

The Simultaneous Read/Write architecture provides

simultaneous operation by dividing the memory

space into two banks. The device can improve overall

system performance b y a llowi ng a hos t sy ste m to pr ogram or erase in one bank, then immediately and

simultaneously read from the othe r bank, with zero latency. This releases the system from waiting for the

completion of program or erase operations.

The Am29DL324D has 16 Mb in each bank.

The Secured Silicon (SecSi) Sector is an extra 64

Kbit sector capable of being permanently lo cked by

AMD or customers. The SecSi Sector Indicator Bit

(DQ7) is permane ntly set to a 1 if the part is factory

locked, and set to a 0 if c ustomer lockable. This

way, customer lockable parts ca n nev er be us ed to re place a factory locked part.

Factory locked parts provide several options. The

SecSi Sector may store a secu re, random 16 by te

ESN (Electronic Serial Number). Customer Lockable

parts may utilize the Sec Si Sector as bonus space ,

reading and writing like any other flash sector, or may

permanently lock their own code there.

DMS (Data Management Software) allows systems

to easily take ad vantag e of the adva nced ar chitec ture

of the simultaneous read/write product line by allowing

removal of EEPROM devices. DMS will also allow the

system software to be simplified, as it will p erform all

functions necessary to modify data in file structures,

as opposed to single-byte modi fications. To write or

update a particular piece of data (a phone number or

configuration data, for example), the user only needs

to state which piece of data is to be updated, and

where the updated data is located in the system. This

is an advantage compared to systems where

user-written software must keep tr ack of the old da ta

location, status, logical to physical translation of the

data onto the Flash memory device (or m emory devices), and more. Using DMS, user-written software

does not need to interface with the Flash memory directly. Instead, the user's software accesses t he Fl ash

memory by calling one of onl y six func tions . AMD provides this software to simplify system design and

software integration efforts.

The device offers complete compatibility with the

JEDEC single-power-supply Flash command set

standard. Commands ar e written to the comman d

register using standard microprocessor write timings.

Reading data out of the device is similar to reading

from other Flash or EPROM devices.

The host system can detect whether a program or

erase operation is complete by using the device sta-

tus bits: RY/BY# pin, DQ7 (D ata# Polling) and

DQ6/DQ2 (toggle bits). After a program or erase cycle

has been completed, the device automatically returns

to reading array data.

The sector erase architecture allows memory sectors to be erased and reprogra mmed withou t affecting

the data contents of other sectors. The device is fully

erased when shipped from the factory.

Hardware data protection measures include a low

detector that automatically inhibits write opera-

V

CC

tions during power transitions. The hardware secto r

protection feature disables both program and erase

operations in any combination of the sectors of memory. This can be achieved in-system or via

programming equipment.

The device offers two power-saving features. Whe n

addresses have been sta ble f or a spe cified am ount o f

time, the device enters the automatic sleep mode.

The system can also place the device into the

standby mode. Power consumption is greatly reduced in both modes.

2 DS42516

Page 3

TABLE OF CONTENTS

Distinctive Characteristics . . . . . . . . . . . . . . . . . . 1

MCP Features . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Flash Memory Features . . . . . . . . . . . . . . . . . . . . .1

Architectural Advantages . . . . . . . . . . . . . . . . . . .1

Performance Characteristics . . . . . . . . . . . . . . . .1

Software Features . . . . . . . . . . . . . . . . . . . . . . . .1

Hardware Features . . . . . . . . . . . . . . . . . . . . . . .1

SRAM Features . . . . . . . . . . . . . . . . . . . . . . . . . . .1

General Description. . . . . . . . . . . . . . . . . . . . . . . . 2

Am29DL324 Features . . . . . . . . . . . . . . . . . . . . . .2

Simultaneous Read/Write Operations with

Zero Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 5

MCP Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . 5

Flash Memory Block Diagram. . . . . . . . . . . . . . . . 6

Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . 7

Special Handling Instructions for FBGA Package .7

Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . 8

Device Bus Operations . . . . . . . . . . . . . . . . . . . . . 8

Table 1. Device Bus Operations—Flash Word

Mode, CIOf = V

CIOs = V

CC

Table 2. Device Bus Operations—Flash Word

Mode, CIOf = V

CIOs = V

SS

Table 3. Device Bus Operations—Flash Byte

Mode, CIOf = V

CIOs = V

SS

Word/Byte Configuration . . . . . . . . . . . . . . . . . . . 12

Requirements for Reading Array Data . . . . . . . . .12

Writing Commands/Command Sequences . . . . .12

Accelerated Program Operation . . . . . . . . . . . .12

Autoselect Functions . . . . . . . . . . . . . . . . . . . . .12

Simultaneous Read/Write Operations with Zero

Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Standby Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Automatic Sleep Mode . . . . . . . . . . . . . . . . . . . . .13

RESET#: Hardware Reset Pin . . . . . . . . . . . . . . .13

Output Disable Mode . . . . . . . . . . . . . . . . . . . . . .13

Table 4. Device Bank Division . . . . . . . . . . . . . .13

Table 5. Sector Addresses for Bottom Boot

Sector Devices . . . . . . . . . . . . . . . . . . . . . . . . . .14

Table 6. SecSi Sector Addresses for Bottom

Boot Devices . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Autoselect Mode . . . . . . . . . . . . . . . . . . . . . . . . . 16

Sector/Sector Block Protection and Unprotection 16

Table 7. Bottom Boot Sector/Sector Block

Addresses for Protection/Unprotection . . . . . . .16

Write Protect (WP#) . . . . . . . . . . . . . . . . . . . . . . .16

Temporary Sector/Sector Block Unprotect . . . . . .17

Figure 1. Temporary Sector Unprotect

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 2. In-System Sector/Sec tor Blo ck

Protect and Unprotect Algorithms. . . . . . . . . . . 18

; SRAM Word Mode,

IH

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

; SRAM Byte Mode,

IH

. . . . . . . . . . . . . . . . . . . . . . . . . . . .10

; SRAM Byte Mode,

IL

. . . . . . . . . . . . . . . . . . . . . . . . . . . .11

SecSi (Secured Silicon) Sector Flash Memory

Region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Factory Locked: SecSi Sector Programmed

and Protected At the Factory . . . . . . . . . . . . . . 19

Customer Lockable: SecSi Sector NOT

Programmed or Protected At the Factory . . . . . 19

Hardware Data Protection . . . . . . . . . . . . . . . . . . 19

Low V

Write Inhibit . . . . . . . . . . . . . . . . . . . . 19

CC

Write Pulse “Glitch” Protection . . . . . . . . . . . . . 19

Logical Inhibit . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Power-Up Write Inhibit . . . . . . . . . . . . . . . . . . . 20

Common Flash Memory Interface (CFI) . . . . . . . 20

Table 8. CFI Query Identification String . . . . . . 20

Table 9. System Interface String . . . . . . . . . . . 21

Table 10. Device Geometry Definition . . . . . . . 21

Table 11. Primary Vendor-Specific Extended

Query . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Command Definitions. . . . . . . . . . . . . . . . . . . . . . 23

Reading Array Data . . . . . . . . . . . . . . . . . . . . . . . 23

Reset Command . . . . . . . . . . . . . . . . . . . . . . . . . 23

Autoselect Command Sequence . . . . . . . . . . . . . 23

Enter SecSi Sector/Exit SecSi Sector

Command Sequence . . . . . . . . . . . . . . . . . . . . . . 24

Byte/Word Program Command Sequence . . . . . 24

Unlock Bypass Command Sequence . . . . . . . . 24

Figure 3. Program Operation. . . . . . . . . . . . . . . 25

Chip Erase Command Sequence . . . . . . . . . . . . 25

Sector Erase Command Sequence . . . . . . . . . . . 25

Erase Suspend/Erase Resume Commands . . . . 26

Figure 4. Erase Operation . . . . . . . . . . . . . . . . . 26

Table 12. DS42516 Command Definitions . . . . 27

Write Operation Status. . . . . . . . . . . . . . . . . . . . . 28

DQ7: Data# Polling . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 5. Data# Polling Algorithm . . . . . . . . . . . 28

RY/BY#: Ready/Busy# . . . . . . . . . . . . . . . . . . . . . 29

DQ6: Toggle Bit I . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 6. Toggle Bit Algorithm. . . . . . . . . . . . . . 29

DQ2: Toggle Bit II . . . . . . . . . . . . . . . . . . . . . . . . 30

Reading Toggle Bits DQ6/DQ2 . . . . . . . . . . . . . . 30

DQ5: Exceeded Timing Limits . . . . . . . . . . . . . . . 30

DQ3: Sector Erase Timer . . . . . . . . . . . . . . . . . . 30

Table 13. Write Operation Status . . . . . . . . . . . 31

Absolute Maximum Ratings. . . . . . . . . . . . . . . . . 32

Operating Ranges. . . . . . . . . . . . . . . . . . . . . . . . . 32

Industrial (I) Devices . . . . . . . . . . . . . . . . . . . . . 32

f/VCCs Supply Voltage . . . . . . . . . . . . . . . . . 32

V

CC

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 33

CMOS Compatible . . . . . . . . . . . . . . . . . . . . . . . 33

SRAM DC and Operating Characteristics. . . . . . 34

Zero-Power Flash . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 9. I

Current vs. Time (Showing

CC1

Active and Automatic Sleep Currents). . . . . . . . 35

Figure 10. Typical I

vs. Frequency . . . . . . . . 35

CC1

Test Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 11. Test Setup . . . . . . . . . . . . . . . . . . . . 36

Table 14. Test Specifications . . . . . . . . . . . . . . 36

DS42516 3

Page 4

Key To Switching Waveforms. . . . . . . . . . . . . . . 36

Figure 12. Input Waveforms and

Measurement Levels . . . . . . . . . . . . . . . . . . . . 36

AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . 37

SRAM CE#s Timing . . . . . . . . . . . . . . . . . . . . . . .37

Figure 13. Timing Diagram for Alternating

Between SRAM to Flash. . . . . . . . . . . . . . . . . . 37

Flash Read-Only Operations . . . . . . . . . . . . . . . .38

Figure 14. Read Operation Timings . . . . . . . . . 38

Hardware Reset (RESET#) . . . . . . . . . . . . . . . . .39

Figure 15. Reset Timings . . . . . . . . . . . . . . . . . 39

Flash Word/Byte Configuration (CIOf) . . . . . . . . .40

Figure 16. CIOf Timings for Read Operations . 40

Figure 17. CIOf Timings for Write Operations. . 40

Flash Erase and Program Operations . . . . . . . . .41

Figure 18. Program Operation Timings. . . . . . . 42

Figure 19. Accelerated Program Timing

Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 20. Chip/Sector Erase Operation

Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 21. Back-to-back Read/Write Cycle

Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 22. Data# Polling Timings (During

Embedded Algorithms) . . . . . . . . . . . . . . . . . . . 44

Figure 23. Toggle Bit Timings (During

Embedded Algorithms) . . . . . . . . . . . . . . . . . . . 45

Figure 24. DQ2 vs. DQ6 . . . . . . . . . . . . . . . . . . 45

Temporary Sector/Sector Block Unprotect . . . . . .46

Figure 25. Temporary Sector/Sector Block

Unprotect Timing Diagram . . . . . . . . . . . . . . . . 46

Figure 26. Sector/Sector Block Protect and

Unprotect Timing Diagram . . . . . . . . . . . . . . . . 47

Alternate CE#f Controlled Erase and Program

Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Figure 27. Flash Alternate CE#f Controlled

Write (Erase/Program) Operation Timings . . . . 49

SRAM Read Cycle . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 28. SRAM Read Cycle—Address

Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 29. SRAM Read Cycle . . . . . . . . . . . . . . 51

SRAM Write Cycle . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 30. SRAM Write Cycle—WE# Control . . 52

Figure 31. SRAM Write Cycle—CE1#s Control. 53

Figure 32. SRAM Write Cycle—UB#s and

LB#s Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Flash Erase And Programming Performance . . . 55

Flash Latchup Characteristics. . . . . . . . . . . . . . . 55

Package Pin Capacitance . . . . . . . . . . . . . . . . . . 55

Flash Data Retention . . . . . . . . . . . . . . . . . . . . . . 55

SRAM Data Retention. . . . . . . . . . . . . . . . . . . . . . 56

Figure 33. CE1#s Controlled Data Retention

Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 34. CE2s Controlled Data Retention

Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . 57

FLB073—73-Ball Fine-Pitch Grid Array

8 x 11 mm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Revision Summary . . . . . . . . . . . . . . . . . . . . . . . . 58

Revision A (October 9, 2000) . . . . . . . . . . . . . . . 58

Revision B (March 8, 2001) . . . . . . . . . . . . . . . . . 58

Global . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Flash Memory Block Diagram . . . . . . . . . . . . . . 58

Sector/Sector Block Protection/Unprotection . . 58

Customer Lockable: SecSi Sector NOT

Programmed or Protected At the Factory . . . . . 58

Common Flash Memory Interface (CFI) . . . . . . 58

Command Definitions . . . . . . . . . . . . . . . . . . . . 58

Revision B+1 (March 15, 2001) . . . . . . . . . . . . . . 58

4 DS42516

Page 5

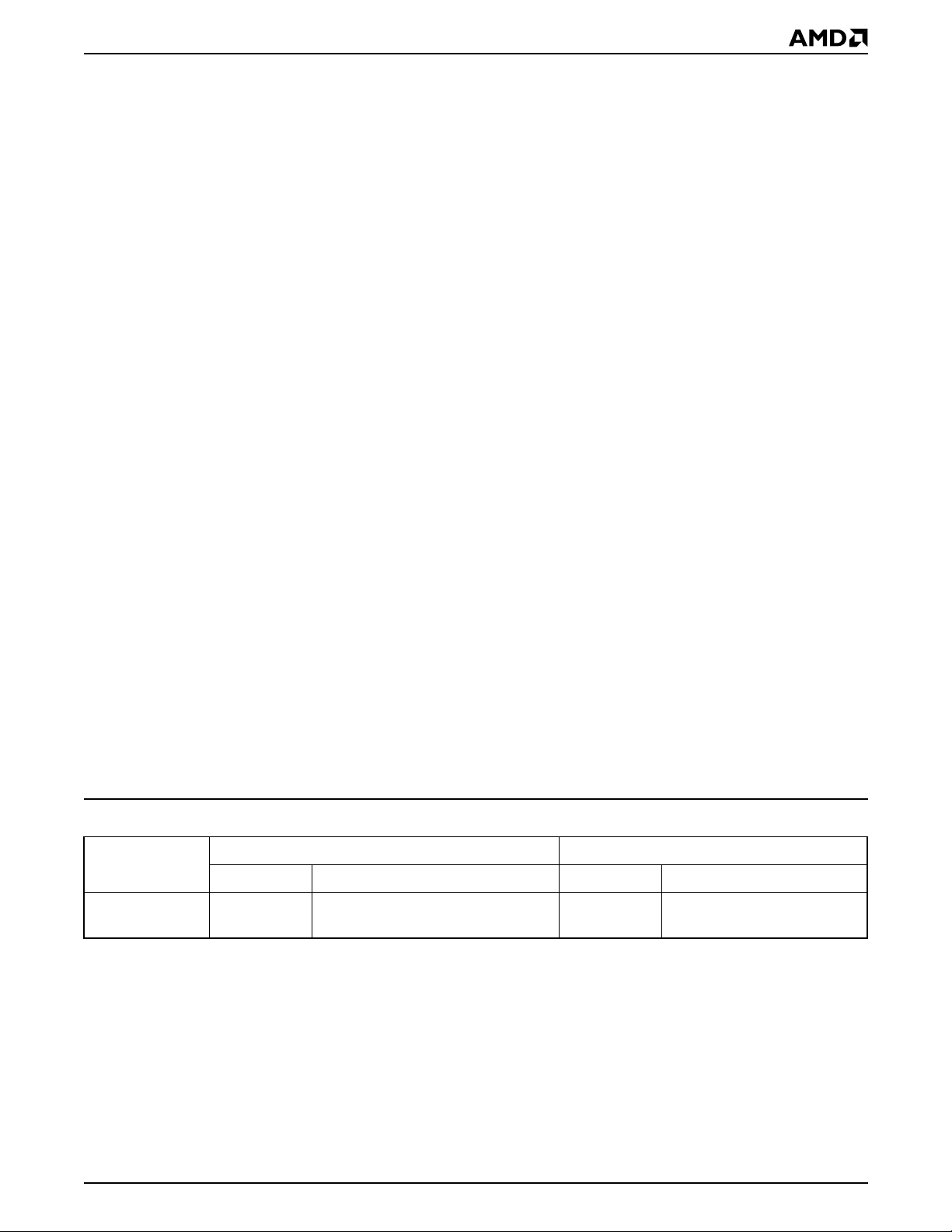

PRODUCT SELECTOR GUIDE

Part Number DS42516

Standard Voltage Range: VCC = 2.7–3.3 V Flash Memory SRAM

Max Access Time (ns) 90 85

CE# Access (ns) 90 85

OE# Access (ns) 40 45

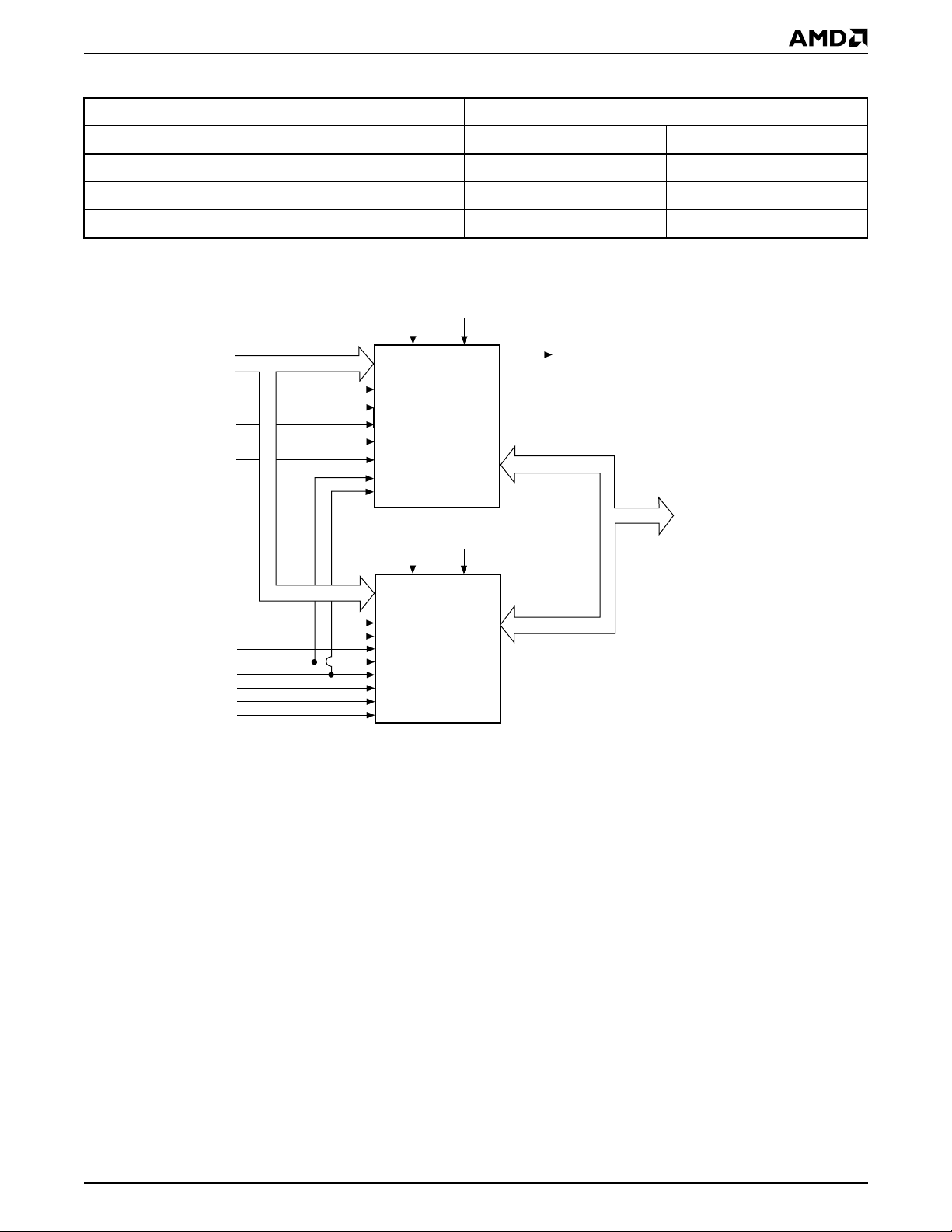

MCP BLOCK DIAGRAM

A0 to A20

–

A

WP#/ACC

RESET#

CE#f

CIOf

LB#s

UB#s

WE#

OE#

CE1#s

CE2s

CIOs

1

SA

A0 to A20

A0 to A19

A0 to A17

VCCf

32 M Bit

Flash Memory

VCCs/V

CCQ

4 M Bit

Static RAM

V

SS

VSS/V

DQ0 to DQ15/A

SSQ

DQ0 to DQ15/A

RY/BY#

–

1

DQ0 to DQ15/A

–

1

–

1

DS42516 5

Page 6

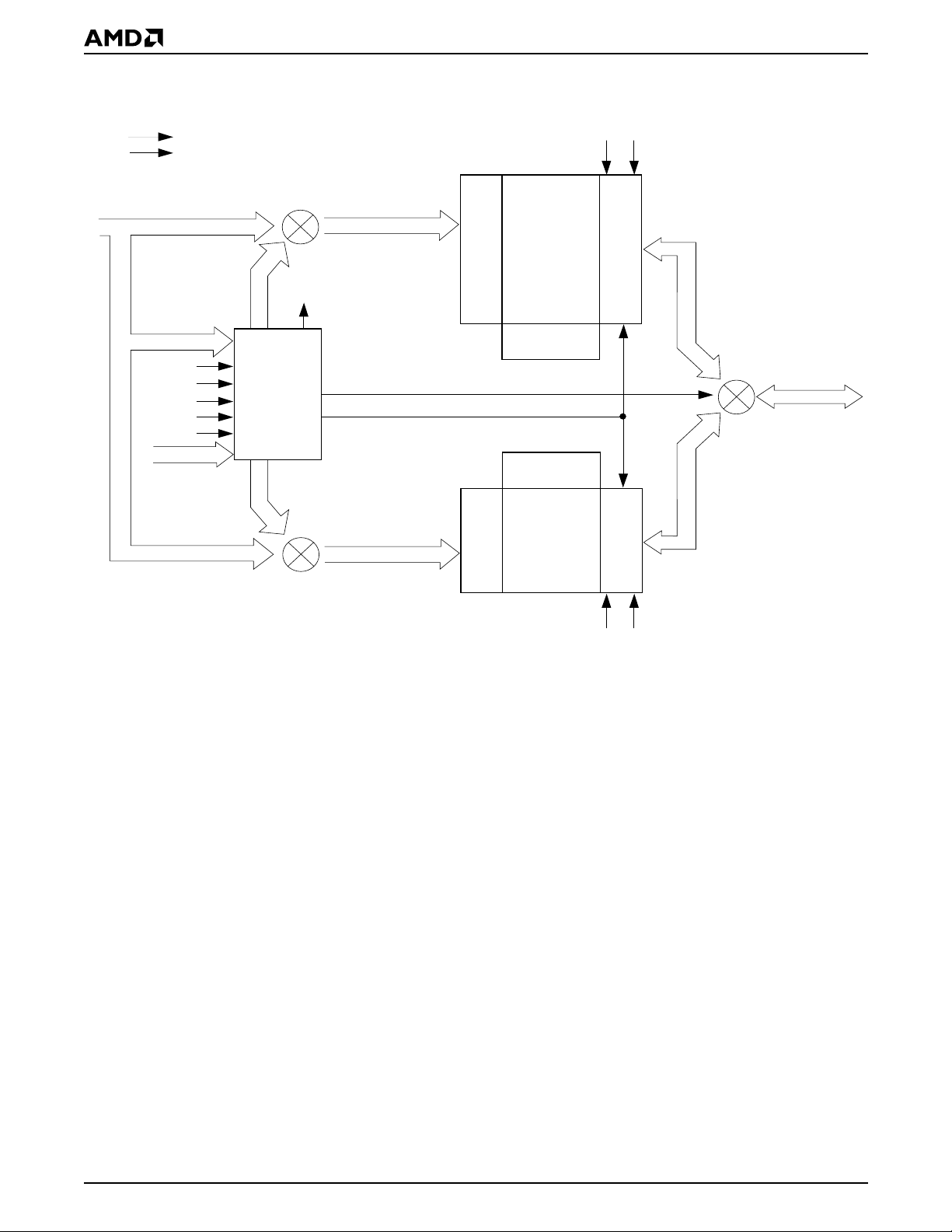

FLASH MEMORY BLOCK DIAGRAM

V

CC

V

SS

A0–A20

Upper Bank Address

Upper Bank

OE# BYTE#

Y-Decoder

A0–A20

RESET#

WE#

CE#

BYTE#

WP#/ACC

DQ0–DQ15

RY/BY#

A0–A20A0–A20

STATE

CONTROL

&

COMMAND

REGISTER

X-Decoder

Status

Control

X-Decoder

Latches and Control Logic

DQ0–DQ15

DQ0–DQ15 DQ0–DQ15

A0–A20

Lower Bank Address

Lower Bank

Y-Decoder

Latches and

Control Logic

OE# BYTE#

6 DS42516

Page 7

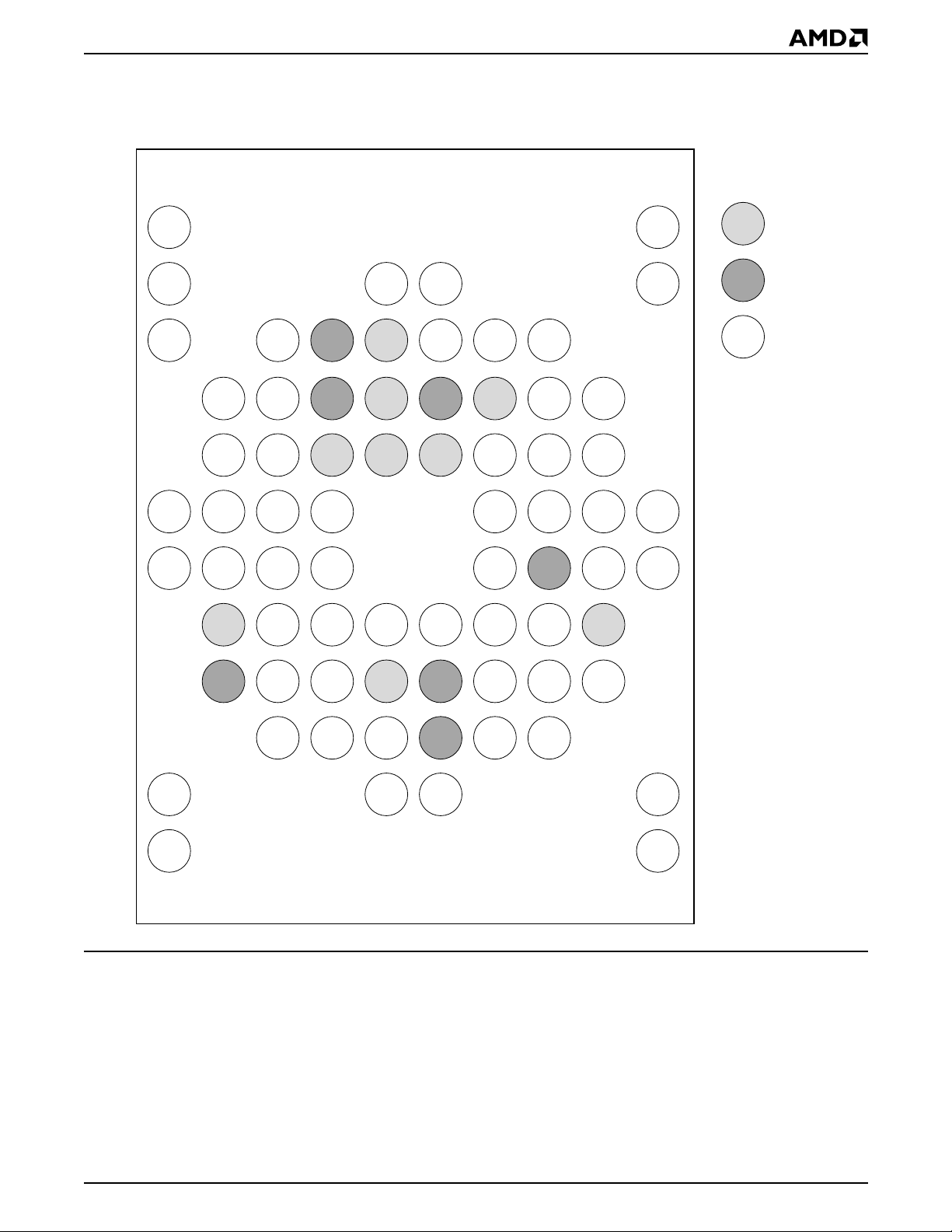

CONNECTION DIAGRAM

73-Ball FBGA

Top View

A1

NC

B1

NC

C1

NC

F1

NC

G1

NC

D2

A3

E2

A2

F2

A1

G2

A0

H2

CE#f

C3

A7

D3

A6

E3

A5

F3

A4

G3

V

SS

H3

OE#

C4

LB#

D4

UB#

E4

A18

F4

A17

G4

DQ1

H4

DQ9

B5

NC

C5

WP#/ACC

D5

RESET#

E5

RY/BY#

H5

DQ3

B6

NC

C6

WE#

D6

CE2s

E6

A20

H6

DQ4

C7

A8

D7

A19

E7

A9

F7

A10

G7

DQ6

H7

DQ13

C8

A11

D8

A12

E8

A13

F8

A14

G8

SA

H8

DQ15/A-1

D9

A15

E9

NC

F9

NC

G9

A16

H9

CIOf

A10

NC

B10

NC

F10

NC

G10

NC

Flash only

SRAM only

Shared

J2

CE1#s

L1

NC

J3

DQ0

K3

DQ8

J4

DQ10

K4

DQ2

J5

V

CC

K5

DQ11

L5

NC

J6

V

f

CC

K6

CIOs

L6

NC

M1

NC

Special Handling Instructions for FBGA

Package

Special handling is required for Flash Memory products in FBGA packages.

J7

s

DQ12

K7

DQ5

J8

DQ7

K8

DQ14

V

J9

SS

L10

NC

M10

NC

Flash memory dev ices in FBGA pa ckages may be

damaged if exposed to ultrasonic cleaning methods.

The package and/or data integrity may be compromised if the package body is exposed to temperatures

above 150

°C for prolonged periods of time.

DS42516 7

Page 8

PIN DESCRIPTION

A0–A17 = 18 Address Inputs (Common)

A-1, A18–A20 = 4 Address Inputs (Flash)

SA = Highest Order Address Pin (SRAM)

Byte mode

DQ0–DQ15 = 16 Data Inpu ts /Outpu ts (Co mmo n)

CE#f = Chip Enable (Flash)

CE#s = Chip Enable (SRAM)

OE# = Output Enable (Common)

WE# = Write Enable (Common)

RY/BY# = Ready/Busy Output

UB#s = Upper Byte Control (SRAM)

LB#s = Lower Byte Control (SRAM)

CIOf = I/O Configuration (Flash)

CIOf = V

CIOf = V

CIOs = I/O Configuration (SRAM)

CIOs = V

CIOs = V

RESET# = Hardware Reset Pin, Active Low

= Word mode (x16),

IH

= Byte mode (x8)

IL

= Word mode (x16),

IH

= Byte mode (x8)

IL

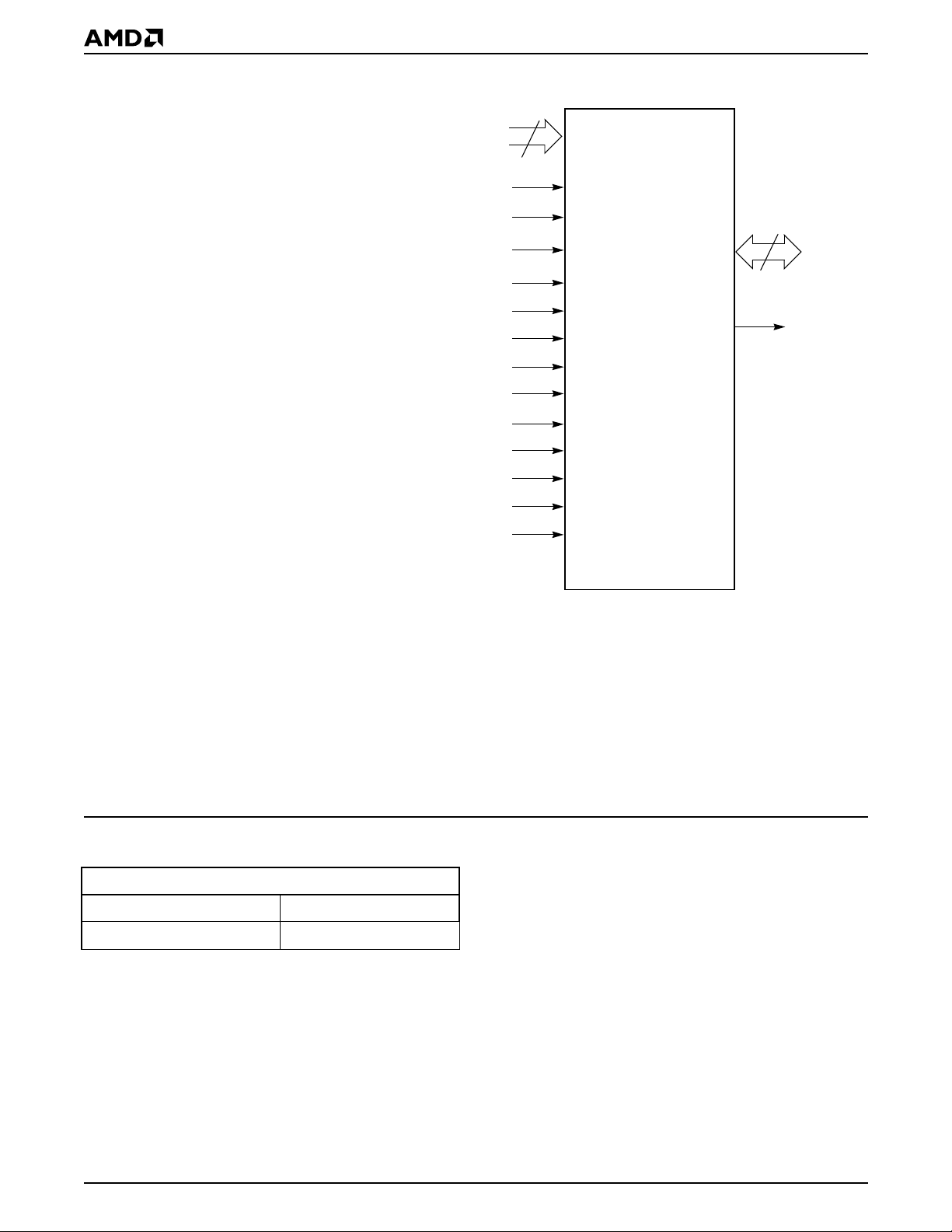

LOGIC SYMBOL

18

A0–A17

A-1, A18–A20

SA

CE#f

CE1#s

CE2s

OE#

WE#

WP#/ACC

RESET#

UB#s

LB#s

CIOf

CIOs

16 or 8

DQ0–DQ15

RY/BY#

WP#/ACC = Hardware Write Protect/

Acceleration Pin (Flash)

V

f = Flash 3.0 volt-only single power sup-

CC

ply (see Product Selector Guide for

speed options and voltage sup p ly

tolerances)

s = SRAM Power Supply

V

CC

V

SS

= Device Ground (Common)

NC = Pin Not Connected Internally

ORDERING INFORMATION

Valid Combination

Order Number Package Marking

DS42516 DS42516

DEVICE BUS OPERATIONS

This section describe s the requirements and use of

the device bus operations, which are initiated through

the internal co mmand reg ister. The comma nd regist er

itself does not occupy any addressable memory location. The register is a latch used to store the

commands, along with the address and data information needed to execu te th e c omm and . The c on ten ts of

the register serve as inputs to the internal state machine. The state machine outputs dictate the function

of the device. Tables 1 through 3 lists the de vice bus

operations, the inputs and control levels they require,

and the resulting output. The following subsections describe each of these operations in further detail.

8 DS42516

Page 9

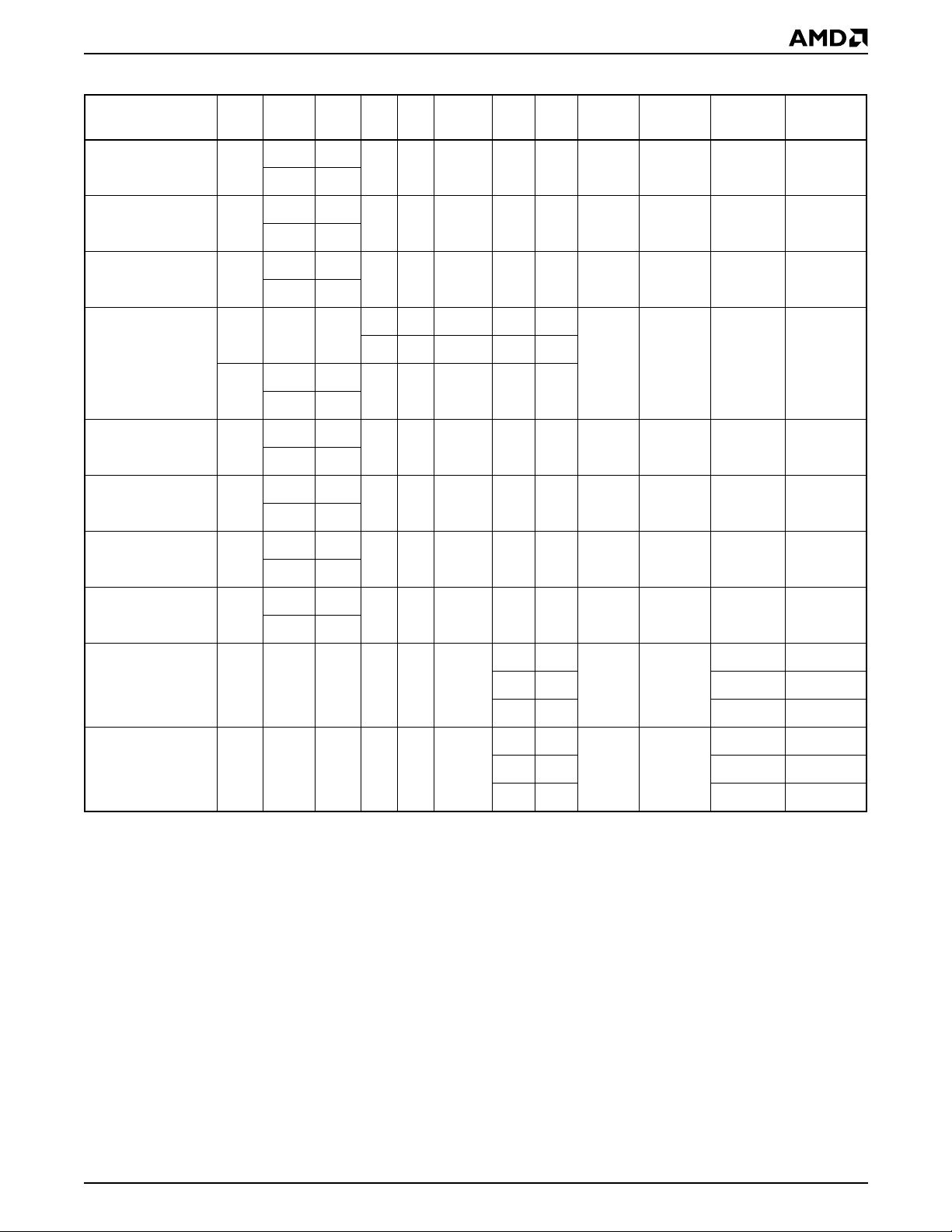

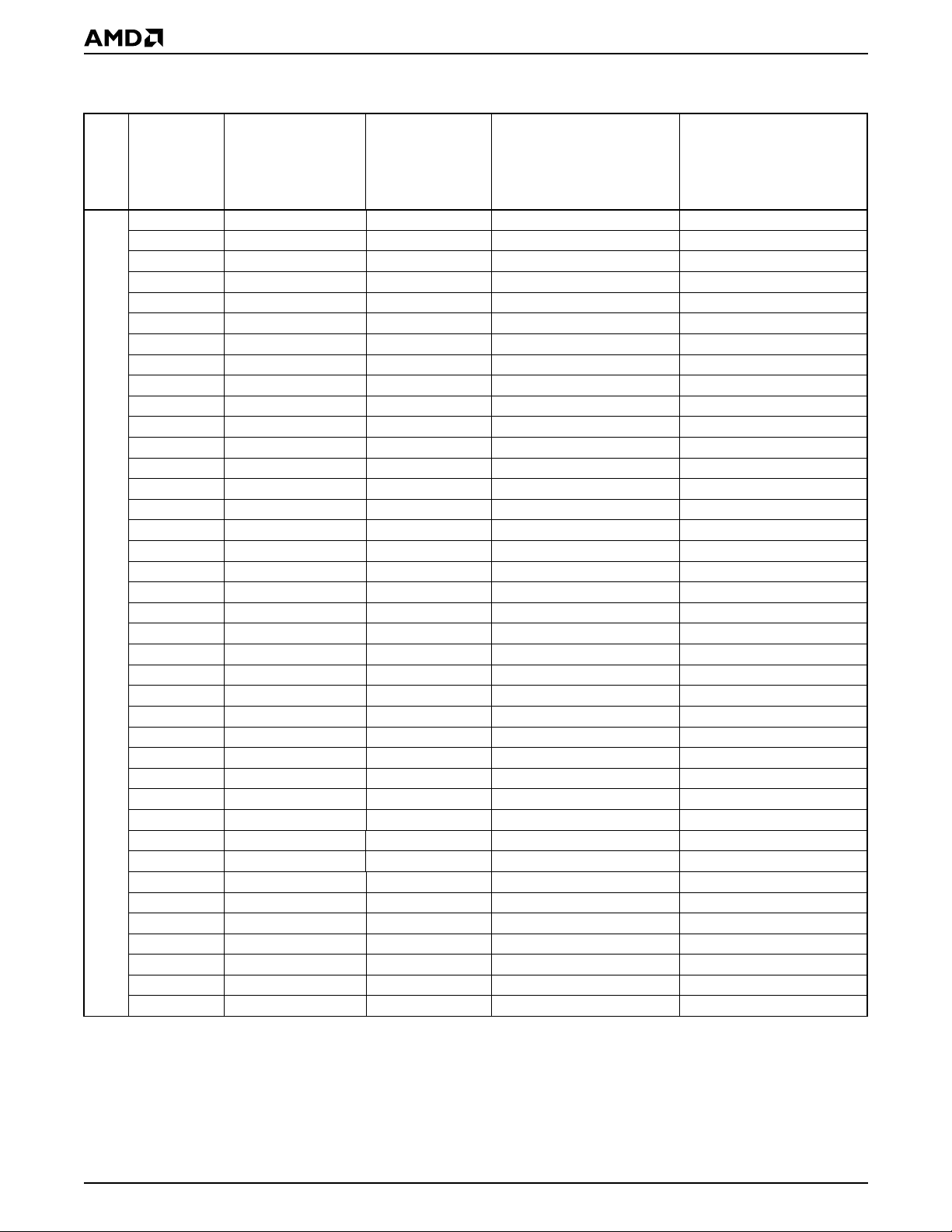

Table 1. Device Bus Operations—Flash Word Mode, CIOf = VIH; SRAM Word Mode, CIOs = VCC

Operation

(Notes 1, 2)

CE#f CE1#s CE2s OE# WE# SA LB#s UB#s RESET#

Read from Flash L

Write to Flash L

Standby

V

0.3 V

Output Disable

Flash Hardware

Reset

Sector Protect

(Note 4)

Sector Unprotect

(Note 4)

HX

XL

HX

XL

HX

±

CC

XL

HLH

HX

L

XL

HX

X

XL

HX

L

XL

HX

L

XL

WP#/ACC

(Note 3)

LH X X X H L/H D

H L X X X H ( No te 3) D

±

V

XX X X X

CC

0.3 V

DQ0– DQ7 DQ8–DQ15

OUT

IN

D

OUT

D

IN

HHigh-ZHigh-Z

HH X L X

HH X X L

H L/H High-Z High-Z

HH X X X

X X X X X L L/H High-Z High-Z

HL X X X V

HL X X X V

ID

ID

L/H D

(Note 5) D

IN

IN

X

X

Temporary Sector

Unprotect

X

Read from SRAM H L H L H X

Write to SRAM H L H X L X

HX

XL

XX X X X V

ID

LL

HL High-Z D

HX

LH D

LL

HL High-Z D

HX

(Note 5) D

D

D

IN

OUT

OUT

IN

High-Z

D

OUT

OUT

High-Z

D

IN

IN

LH DINHigh-Z

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 8.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = Sector Address,

= Address In, DIN = Data In, D

A

IN

= Data Out

OUT

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

3. If WP#/ACC = V

If WP#/ACC = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

, the boot sectors will be protected. If WP#/ACC = VIH the boot sectors protection will be removed.

IL

(9V), the program time will be reduced by 40%.

ACC

4. The sector protect and sector unprotect functions may also be implemented via programming equipment. See the “Sector/Sector

Block Protection and Unprotection” section.

5. If WP#/ACC = V

, the two outermost boot sectors remain protected. If WP#/ACC = VIH, the two outermost boot sector protection

IL

depends on whether they were last protected or unprotected using the method described in “Sector/Sector Block Protection and

Unprotection”. If WP#/ACC = V

all sectors will be unprotected.

HH,

DS42516 9

Page 10

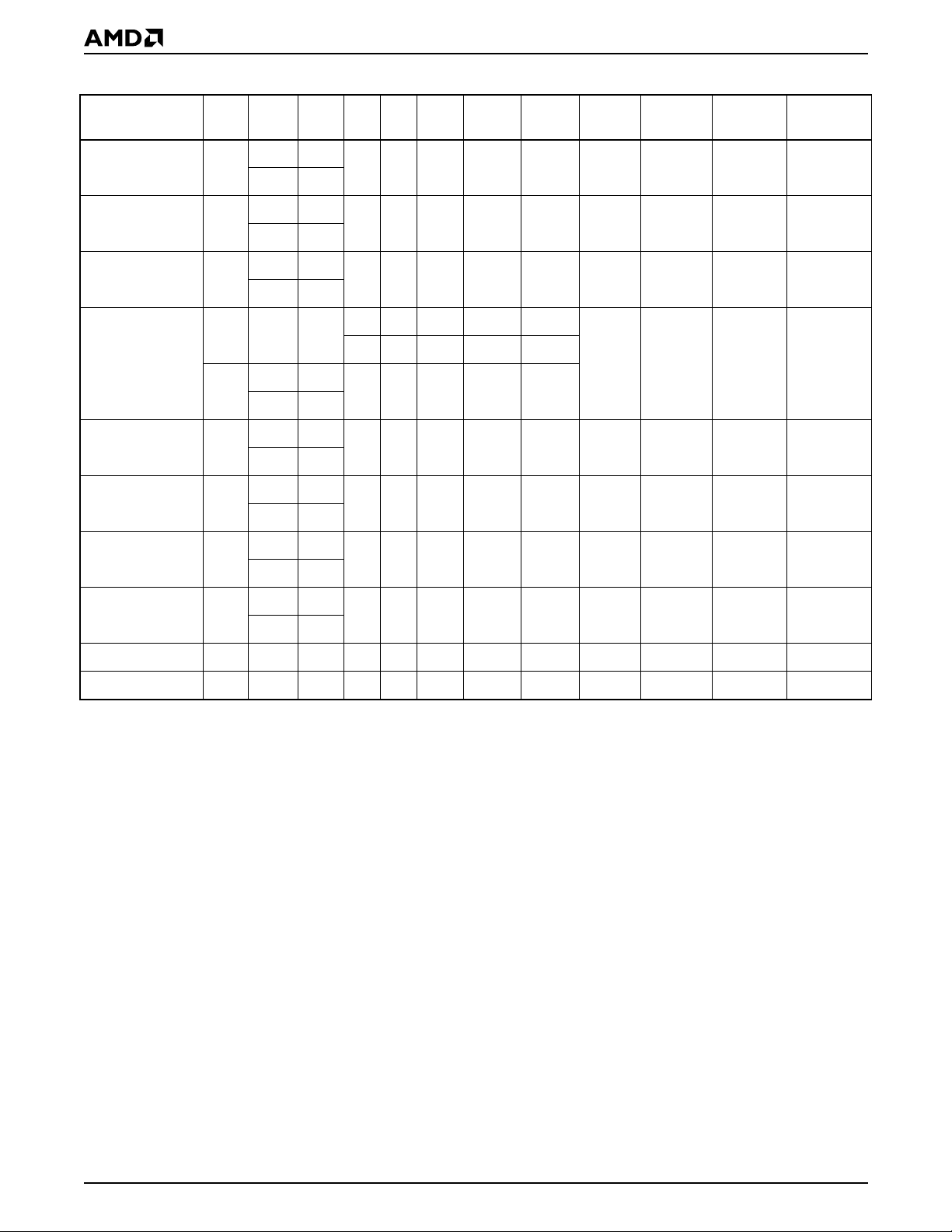

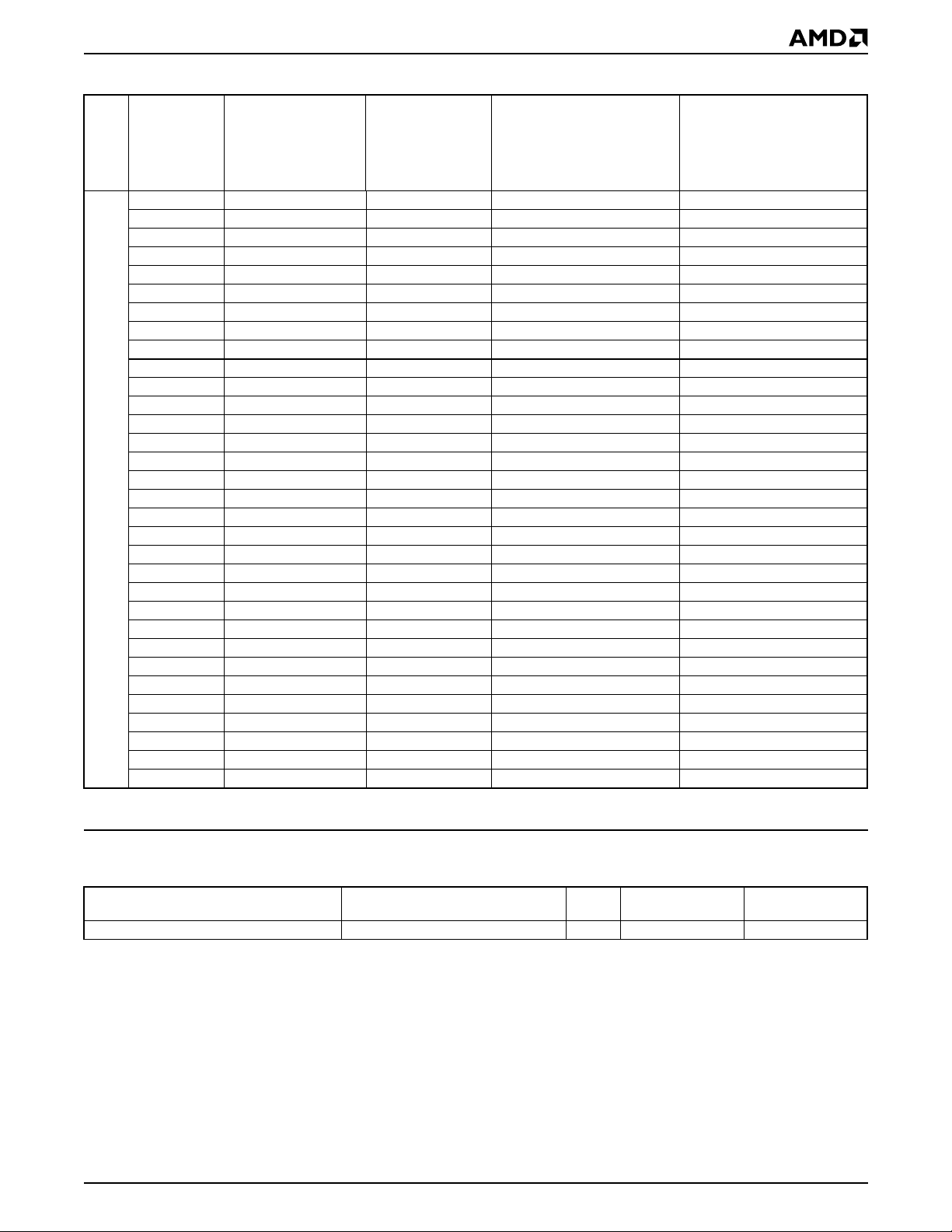

Table 2. Device Bus Operations—Flash Word Mode, CIOf = V

Operation

(Notes 1, 2)

CE#f CE1#s CE2s OE# WE# SA

Read from Flash L

Write to Flash L

V

Standby

CC

0.3 V

Output Disable

Flash Hardware

Reset

Sector Protect

(Note 5)

HX

XL

HX

XL

HX

±

XL

HLH

HX

L

XL

HX

X

XL

HX

L

XL

LH X X X H L/H D

H L L X X H (Note 3) D

XX X X X

HH X L X

HH X X L

HH X X X

X X X X X L L/H High-Z High-Z

HL X X X V

LB#s

(Note 3)

UB#s

(Note 3)

; SRAM Byte Mode, CIOs = VSS

IH

CC

±

WP#/ACC

(Note 4)

DQ0–DQ7 DQ8–DQ15

OUT

IN

H High-Z High-Z

RESET#

V

0.3 V

H L/H High-Z High-Z

ID

L/H D

IN

D

OUT

D

IN

X

Sector Unprotect

(Note 5)

Temporary Sector

Unprotect

X

Read from SRAM H L H L H SA X X H X D

Write to SRAM H L H X L SA X X H X D

L

HX

XL

HX

XL

HL X X X V

XX X X X V

ID

ID

(Note 6) D

(Note 6) D

IN

IN

OUT

IN

X

High-Z

High-Z

High-Z

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 8.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = Sector Address,

= Address In, DIN = Data In, D

A

IN

= Data Out

OUT

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

3. Don’t care or open LB#s or UB#s.

4. If WP#/ACC = V

If WP#/ACC = V

, the boot sectors will be protected. If WP#/ACC = VIH the boot sectors protection will be removed.

IL

(9V), the program time will be reduced by 40%.

ACC

5. The sector protect and sector unprotect functions may also be implemented via programming equipment. See the “Sector/Sector

Block Protection and Unprotection” section.

6. If WP#/ACC = V

, the two outermost boot sectors remain protected. If WP#/ACC = VIH, the two outermost boot sector protection

IL

depends on whether they were last protected or unprotected using the method described in “Sector/Sector Block Protection and

Unprotection”. If WP#/AC C = V

all sectors will be unprotected.

HH,

10 DS42516

Page 11

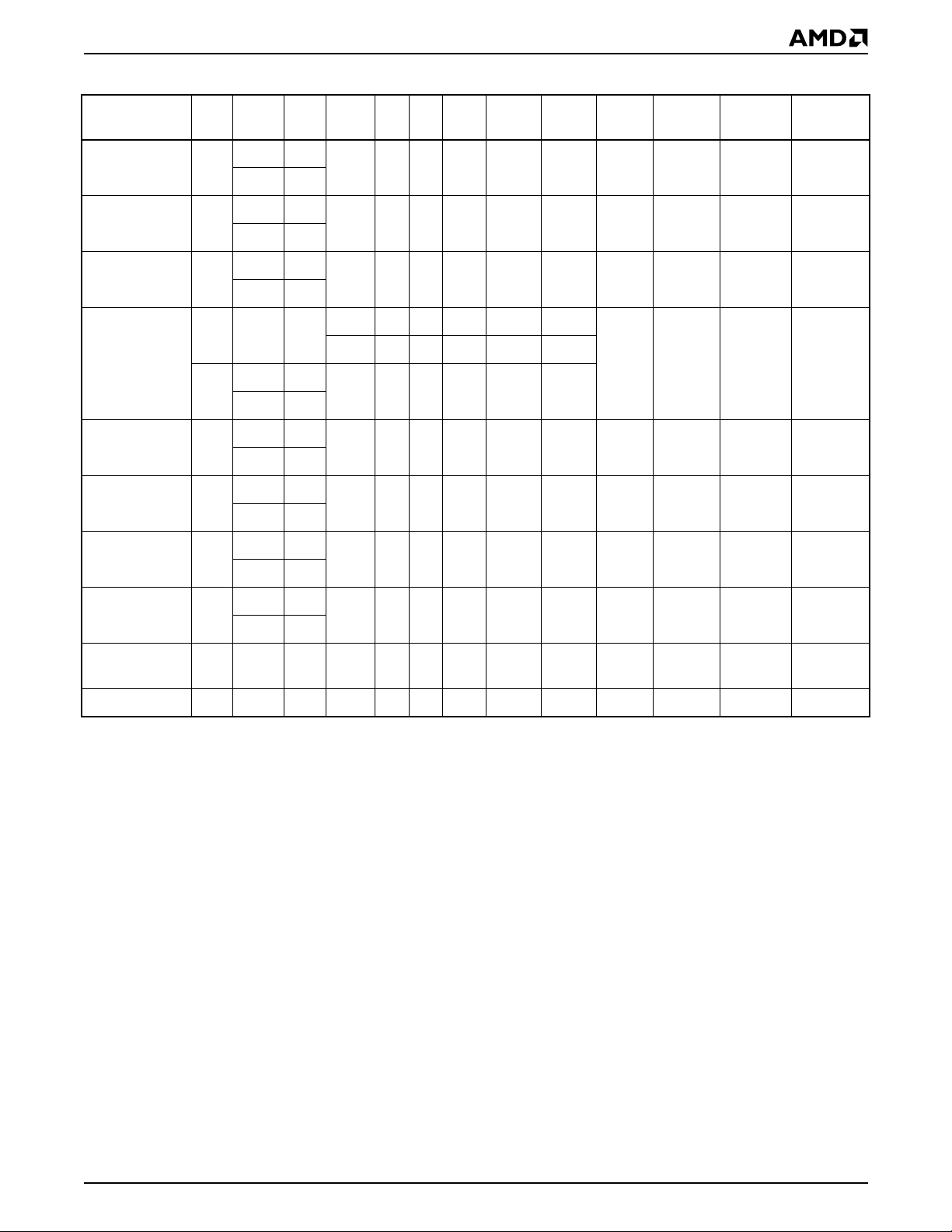

T a ble 3. Device Bus Operations—Flash Byte Mode, CIOf = VIL; SRAM Byte Mode, CIOs = VSS

Operation

(Notes 1, 2 )

CE#f CE1#s CE2s

Read from Flash L

Write to Flash L

V

Standby

CC

0.3 V

Output Disable

Flash Hardware

Reset

Sector Protect

(Note 5)

Sector Unprotect

(Note 5)

DQ15/

HX

XL

HX

XL

HX

±

XL

HLH

HX

L

XL

HX

X

XL

HX

L

XL

HX

L

XL

LB#s

(Note 3)

A–1

OE#

WE# SA

A–1LH X X X H L/H D

A–1HL X X X H

XX X X X

UB#s

(Note 3)

RESET#

±

V

CC

0.3 V

WP#/ACC

(Note 4)

(Note 3)

DQ0–DQ7 DQ8–DQ15

OUT

D

IN

H High-Z High-Z

High-Z

High-Z

XHHX L X

HHXX X L

H L/H High-Z High-Z

A–1HH X X X

X X X X X X L L/H High-Z High-Z

HL X X X V

HL X X X V

ID

ID

L/H D

(Note 6) D

IN

IN

X

X

Temporary

Sector Unprotect

Read from

SRAM

X

HLHXLHSAX X H X D

Write to SRAM H L H X X L SA X X H X D

Hx

XL

XX X X X V

ID

(Note 6) D

IN

OUT

IN

High-Z

High-Z

High-Z

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 8.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = Sector Address,

A

= Address In, DIN = Data In, D

IN

= Data Out

OUT

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

3. Don’t care or open LB#s or UB#s.

4. If WP#/ACC = V

If WP#/ACC = V

, the boot sectors will be protected. If WP#/ACC = VIH the boot sectors protection will be removed.

IL

(9V), the program time will be reduced by 40%.

ACC

5. The sector protect and sector unprotect functions may also be implemented via programming equipment. See the “Sector/Sector

Block Protection and Unprotection” section.

6. If WP#/ACC = V

, the two outermost boot sectors remain protected. If WP#/ACC = VIH, the two outermost boot sector protection

IL

depends on whether they were last protected or unprotected using the method described in “Sector/Sector Block Protection and

Unprotection”. If WP#/AC C = V

all sectors will be unprotected.

HH,

DS42516 11

Page 12

Word/Byte Configuration

The CIOf pin controls whether the device data I/O pins

operate in the byte or word conf iguratio n. If the CIOf

pin is set at lo gic ‘1’, the device is in wor d configuration, DQ0–DQ15 are active and controlled by CE# and

OE#.

If the CIOf pin is set at logic ‘0’, the device is in byte

configuration, and o nly data I/O pi ns DQ0–DQ7 are

active and control led by CE# and OE# . The data I/O

pins DQ8–DQ14 are tri-stated, and the DQ15 pin is

used as an input for the LSB (A-1) address function.

Requirements for Reading Array Data

To read array data from the outputs, the system must

drive the CE#f and OE# pins to V

. CE#f is the power

IL

control and sele cts the de vice. OE# is the outpu t control and gates array data to the output pins. WE#

should remain at V

. The CIOf pin dete rmines

IH

whether the de vice outputs a rray data in word s or

bytes.

The internal state machine is set for reading array data

upon device power-up, or af ter a har dware r eset. This

ensures that no sp urious alteration of th e memory

content occurs during the power transition. No command is necessary in this m ode to obtai n array data .

Standard micropr ocess or read cyc les that asse rt vali d

addresses on the de vice addre ss in puts produ ce vali d

data on the device data outp uts. Each bank remai ns

enabled for read access until the co mmand register

contents are altered.

See “Requirements for Reading Array Data” for more

information. Refer to the AC Flash Read-Only Operations table for timing specifications and to Figure 14 for

the timing diagram. I

in the DC Char acteristics

CC1

table represents the active current specification for

reading array data.

Writing Commands/Command Sequences

To write a command or command sequence (which includes programming data to the device and erasin g

sectors of memory), th e system must driv e WE# an d

CE#f to V

For program operation s, the CIOf pin determines

whether the device accept s program data in by tes or

words. Refer to “Word/Byte Configuration” for more

information.

The device features an Unlock Bypas s mode to facilitate faster programming. Once a bank enters the

Unlock Bypass mode, only two write cycles are required to program a word or byte, instead of four. The

“Word/Byte Configuration” section has details on programming data to the device using both standard and

Unlock Bypass command sequences.

, and OE# to VIH.

IL

An erase operation can erase one sector, multiple sectors, or the entire device. Tables 5–6 indicate the

address space that each sector occupies. The device

address space is divided into two banks: Bank 1 contains the boot/parameter sec tor s, and Ban k 2 co ntai ns

the larger, c ode sectors of uniform size. A “bank address” is the address b its r equ ir ed t o un iqu ely s el ect a

bank. Similarly, a “sector address” is the address bits

required to uniquely select a sector.

in the DC Characteristics table represents the ac-

I

CC2

tive current specification for the write mode. The AC

Characteristics section contains timing specification

tables and timing diagrams for write operations.

Accelerated Program Operation

The device offers accelerated p rogram oper ations

through the ACC function. This is one of two functions

provided by the WP#/ACC pin. This function is primarily intended to allow faster manufacturing throughput

at the factory.

If the system asserts V

on this pin, the devic e auto-

HH

matically enters th e aforemention ed Unlock B ypass

mode, temporarily unprotects any protected sectors,

and uses the h igher vo ltage on the pin to re duce th e

time required for program operations. The system

would use a two-cycle program command sequence

as required by the Unloc k Bypass mo de. Removing

from the WP#/ACC pin returns the device to nor-

V

HH

mal operation. Note that the WP#/ACC pin must not

be at V

for operations other than accelerated pro-

HH

gramming, or device damage may result. In ad dition,

the WP#/ACC pin must not be left floating or unconnected; inconsistent behavior of the device may result.

Autoselect Functions

If the system writes the autoselect command sequence, the device enters the autoselect mode. The

system can then read autosel ect co des from the internal register (which is separate from the memory array)

on DQ7–DQ0. Standar d read cycle timings app ly in

this mode. Refer to the Autoselect Mode and Autoselect Command Sequence sections for more

information.

Simultaneous Read/Write Operations with

Zero Latency

This device is capable of reading data from one bank

of memory while programming or erasing in the other

bank of memory. An erase operation may also be su spended to read from or program to another location

within the same bank (except the sector being

erased). Figu re 21 s hows how read and w rite cycles

may be initiated for simultaneous operation with zero

latency. I

CC6

and I

represent the current specifications for read-while-program and read-while-erase, respectively.

in the DC Characterist ics table

CC7

12 DS42516

Page 13

Standby Mode

When the system is not reading or writing to the device, it can place the device in the standby mode. In

this mode, current consumption is greatly reduced,

and the outputs are placed in the high impedance

state, independent of the OE# input.

The device enters th e CMOS s tandby m ode when th e

CE#f and RESET# pins are both held at V

± 0.3 V.

CC

(Note that this is a more restricted voltage range than

.) If CE#f and RESET# are held at VIH, but not

V

IH

within V

± 0.3 V, the device will be in the standby

CC

mode, but the stan dby cur ren t will b e gr eater. The device requires standard access time (t

) for read

CE

access when the devi ce is in either of these stand by

modes, before it is ready to read data.

If the device is deselecte d during erasur e or programming, the device draws active current until the

operation is completed.

in the DC Characteristics table represents the

I

CC3

standby current specif ic ati on.

Automatic Sleep Mode

The automatic sleep mode minimizes Flash device energy consumption. The device automati cally enables

this mode w hen ad dresses remain s table for t

ACC

+

30 ns. The aut omatic sle ep mode is in dependent o f

the CE#f, WE#, and OE# control signals. Standard address access timi ngs provide new data when

addresses are changed. While in sleep mode, o utput

data is latc hed and always a vailable to the system.

in the DC Characteristics table represents the

I

CC4

automatic sleep mode current specification.

RESET#: Hardware Reset Pin

The RESET# pin provides a hardware method of resetting the device to reading array data. When th e

RESET# pin is driven low for at least a period of t

RP

the device immediately terminates any operation in

progress, tristates all output pins, and ignores all

read/write commands for the duration of the RESET#

pulse. The device al so resets the i nternal state machine to reading arra y data. The o peration that was

interrupted should be reinitiated once the device is

ready to accept another command sequence, to ensure data integrity.

Current is reduced for the duration of the RESET#

pulse. When RESET# is held at V

vice draws CMOS standby current (I

held at V

but not within V

IL

± 0.3 V, the standby cur-

SS

± 0.3 V, the de-

SS

). If RESET# is

CC4

rent will be greater.

The RESET# pin may be tied to the system reset cir-

cuitry. A system reset would thus also reset the Flash

memory, enabling the system to read the boot-up firmware from the Flash memory.

If RESET# is asserted during a program or erase operation, the RY/BY# pin remains a “0” (busy) until the

internal reset operation is complete, which requires a

time of t

(during Embed ded Algorithm s). The

READY

system can thus monitor RY/BY# to determine

whether the reset ope ratio n is co mplete . If RES ET# is

asserted when a program or erase operation is not executing (RY/ BY# pin is “1”), the reset operation is

completed within a time of t

ded Algorithms). The system can read data t

the RESET# pin returns to V

(not during Embed-

READY

.

IH

RH

after

Refer to the AC Characteristics tables for RESET# parameters and to Figure 15 for the timing diagram.

Output Disable Mode

When the OE# input is at VIH, output from the device is

disabled. The output pins are placed in the high

impedance state.

,

Device

Part Number

Am29DL324D 16 Mbit

Megabits Sector Sizes Megabits Sector Sizes

T a ble 4. Device Bank Division

Bank 1 Bank 2

Eight 8 Kbyte/4 Kword,

thirty-one 64 Kbyte/32 Kword

16 Mbit

DS42516 13

Thirty-two

64 Kbyte/32 Kword

Page 14

Table 5. Sector Addresses for Bottom Boot Sector Devices

Am29DL324DB

Bank 1

Sector

SA0 000000000 8/4 000000h–001FFFh

SA1 000000001 8/4 002000h–003FFFh

SA2 000000010 8/4 004000h–005FFFh

SA3 000000011 8/4 006000h–007FFFh

SA4 000000100 8/4 008000h–009FFFh

SA5 000000101 8/4 00A000h–00BFFFh

SA6 000000110 8/4 00C000h–00DFFFh

SA7 000000111 8/4 00E000h–00FFFFh

SA8 000001XXX 64/32 010000h–01FFFFh

SA9 000010XXX 64/32 020000h–02FFFFh

SA10 000011XXX 64/32 030000h–03FFFFh

SA11 000100XXX 64/32 040000h–04FFFFh

SA12 000101XXX 64/32 050000h–05FFFFh

SA13 000110XXX 64/32 060000h–06FFFFh

SA14 000111XXX 64/32 070000h–07FFFFh

SA15 001000XXX 64/32 080000h–08FFFFh

SA16 001001XXX 64/32 090000h–09FFFFh

SA17 001010XXX 64/32 0A0000h–0AFFFFh

SA18 001011XXX 64/32 0B0000h–0BFFFFh

SA19 001100XXX 64/32 0C0000h–0CFFFFh

SA20 001101XXX 64/32 0D0000h–0DFFFFh

SA21 001110XXX 64/32 0E0000h–0EFFFFh

SA22 001111XXX 64/32 0F0000h–0FFFFFh

SA23 010000XXX 64/32 100000h–10FFFFh

SA24 010001XXX 64/32 110000h–11FFFFh

SA25 010010XXX 64/32 120000h–12FFFFh

SA26 010011XXX 64/32 130000h–13FFFFh

SA27 010100XXX 64/32 140000h–14FFFFh

SA28 010101XXX 64/32 150000h–15FFFFh

SA29 010110XXX 64/32 160000h–16FFFFh

SA30 010111XXX 64/32 170000h–17FFFFh

SA31 011000XXX 64/32 180000h–18FFFFh

SA32 011001XXX 64/32 190000h–19FFFFh

SA33 011010XXX 64/32 1A0000h–1AFFFFh

SA34 011011XXX 64/32 1B0000h–1BFFFFh

SA35 011100XXX 64/32 1C0000h–1CFFFFh

SA36 011101XXX 64/32 1D0000h–1DFFFFh

SA37 011110XXX 64/32 1E0000h–1EFFFFh

SA38 011111XXX 64/32 1F0000h–1FFFFFh

Sector Address

A20–A12

Sector Size

(Kbytes/Kwords)

(x8)

Address Range

(x16)

Address Range

000000h–000FFFh

001000h–001FFFh

002000h–002FFFh

003000h–003FFFh

004000h–004FFFh

005000h–005FFFh

006000h–006FFFh

007000h–007FFFh

008000h–00FFFFh

010000h–017FFFh

018000h–01FFFFh

020000h–027FFFh

028000h–02FFFFh

030000h–037FFFh

038000h–03FFFFh

040000h–047FFFh

048000h–04FFFFh

050000h–057FFFh

058000h–05FFFFh

060000h–067FFFh

068000h–06FFFFh

070000h–077FFFh

078000h–07FFFFh

080000h–087FFFh

088000h–08FFFFh

090000h–097FFFh

098000h–09FFFFh

0A0000h–0A7FFFh

0A8000h–0AFFFFh

0B0000h–0B7FFFh

0B8000h–0BFFFFh

0C0000h–0C7FFFh

0C8000h–0CFFFFh

0D0000h–0D7FFFh

0D8000h–0DFFFFh

0E0000h–0E7FFFh

0E8000h–0EFFFFh

0F0000h–0F7FFFh

0F8000h–0FFFFFh

14 DS42516

Page 15

T a ble 5. Sector Addresses for Bottom Boot Sector Devices (Continued)

Am29DL324DB

Bank 2

Sector

SA39 100000XXX 64/32 200000h–20FFFFh 100000h–107FFFh

SA40 100001XXX 64/32 210000h–21FFFFh 108000h–10FFFFh

SA41 100010XXX 64/32 220000h–22FFFFh 110000h–117FFFh

SA42 100011XXX 64/32 230000h–23FFFFh 118000h–11FFFFh

SA43 100100XXX 64/32 240000h–24FFFFh 120000h–127FFFh

SA44 100101XXX 64/32 250000h–25FFFFh 128000h–12FFFFh

SA45 100110XXX 64/32 260000h–26FFFFh 130000h–137FFFh

SA46 100111XXX 64/32 270000h–27FFFFh 138000h–13FFFFh

SA47 101000XXX 64/32 280000h–28FFFFh 140000h–147FFFh

SA48 101001XXX 64/32 290000h–29FFFFh 148000h–14FFFFh

SA49 101010XXX 64/32 2A0000h–2AFFFFh 150000h–157FFFh

SA50 101011XXX 64/32 2B0000h–2BFFFFh 158000h–15FFFFh

SA51 101100XXX 64/32 2C0000h–2CFFFFh 160000h–167FFFh

SA52 101101XXX 64/32 2D0000h–2DFFFFh 168000h–16FFFFh

SA53 101110XXX 64/32 2E0000h–2EFFFFh 170000h–177FFFh

SA54 101111XXX 64/32 2F0000h–2FFFFFh 178000h–17FFFFh

SA55 111000XXX 64/32 300000h–30FFFFh 180000h–187FFFh

SA56 110001XXX 64/32 310000h–31FFFFh 188000h–18FFFFh

SA57 110010XXX 64/32 320000h–32FFFFh 190000h–197FFFh

SA58 110011XXX 64/32 330000h–33FFFFh 198000h–19FFFFh

SA59 110100XXX 64/32 340000h–34FFFFh 1A0000h–1A7FFFh

SA60 110101XXX 64/32 350000h–35FFFFh 1A8000h–1AFFFFh

SA61 110110XXX 64/32 360000h–36FFFFh 1B0000h–1B7FFFh

SA62 110111XXX 64/32 370000h–37FFFFh 1B8000h–1BFFFFh

SA63 111000XXX 64/32 380000h–38FFFFh 1C0000h–1C7FFFh

SA64 111001XXX 64/32 390000h–39FFFFh 1C8000h–1CFFFFh

SA65 111010XXX 64/32 3A0000h–3AFFFFh 1D0000h–1D7FFFh

SA66 111011XXX 64/32 3B0000h–3BFFFFh 1D8000h–1DFFFFh

SA67 111100XXX 64/32 3C0000h–3CF FFFh 1E0000h–1E7FFFh

SA68 111101XXX 64/32 3D0000h–3DF FFFh 1E8000h–1EFFFFh

SA69 111110XXX 64/32 3E0000h–3EFFFFh 1F0000h–1F7FFFh

SA70 111111XXX 64/32 3F0000h–3FFFFFh 1F8000h–1FFFFFh

Sector Address

A20–A12

Sector Size

(Kbytes/Kwords)

(x8)

Address Range

(x16)

Address Range

Note: The address range is A20:A-1 in byte mode (CIOf=VIL) or A20:A0 in word mode (CIOf=VIH). The bank address bit is A20

for Am29DL324DB.

Table 6. SecSi Sector Addresses for Bottom Boot Devices

Sector Address

Device

Am29DL324DB 000000XXX 64/32 000000h–00FFFFh 00000h–07FFFh

A20–A12

Sector

Size

(x8)

Address Range

(x16)

Address Range

DS42516 15

Page 16

Autoselect Mode

The autoselect mode prov ides manufactur er and device identification, and sector protection verification,

through identifier codes output on DQ7–DQ0. This

mode is primarily intended for programming equipment to automatically match a device to be

programmed wi th its corres ponding pr ogrammin g algorithm. However, the autoselect codes can also be

accessed in-system through the command register.

To access the autoselect codes in-system, the host

system can issue the autoselect command via the

command register, as shown in Table 12. This method

does not require V

. Refer to the Autoselect Com-

ID

mand Sequence section for more information.

Sector/Sector Block Protec ti on and

Unprotection

(Note: For the following discussi on, the term “sector”

applies to both sectors and sector blocks. A sector

block consists of two or more adjacent sectors that are

protected or unprotected at the same time (see Table

7).

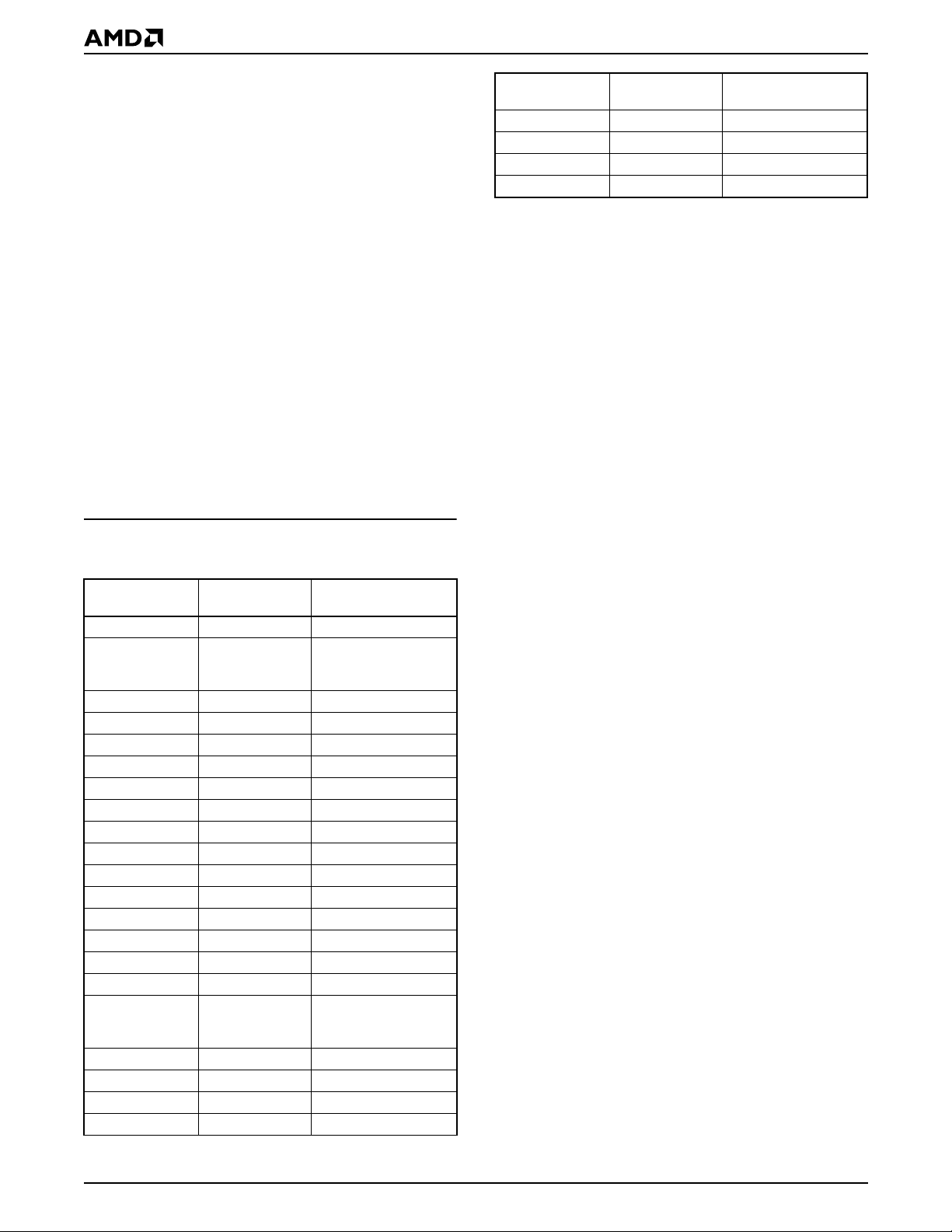

Table 7. Bottom Boot Sector/Sector Block

Addresses for Protection/Unpro tect ion

Sector A20–A12

SA70

SA69–SA67

SA66–SA63

SA62–SA59

SA58–SA55

SA54–SA51

SA50–SA47

SA46–SA43

SA42–SA39

SA38–SA35

SA34–SA31

SA30–SA27

SA26–SA23

SA22–SA19

SA18–SA15

SA14–SA11

SA10–SA8

SA7

SA6

SA5

SA4

111111XXX 64 Kbytes

111110XXX,

111101XXX,

111100XXX

1110XXXXX 256 (4x64) Kbytes

1101XXXXX 256 (4x64) Kbytes

1100XXXXX 256 (4x64) Kbytes

1011XXXXX 256 (4x64) Kbytes

1010XXXXX 256 (4x64) Kbytes

1001XXXXX 256 (4x64) Kbytes

1000XXXXX 256 (4x64) Kbytes

0111XXXXX 256 (4x64) Kbytes

0110XXXXX 256 (4x64) Kbytes

0101XXXXX 256 (4x64) Kbytes

0100XXXXX 256 (4x64) Kbytes

0011XXXXX 256 (4x64) Kbytes

0010XXXXX 256 (4x64) Kbytes

0001XXXXX 256 (4x64) Kbytes

000011XXX,

000010XXX,

000001XXX

000000111 8 Kbytes

000000110 8 Kbytes

000000101 8 Kbytes

000000100 8 Kbytes

Sector/Sector Block

Size

192 (3x64) Kbytes

192 (3x64) Kbytes

Sector

SA3 000000011 8 Kbytes

SA2 000000010 8 Kbytes

SA1

SA0

A20–A12

000000001 8 Kbytes

000000000 8 Kbytes

Sector/Sector Block

Size

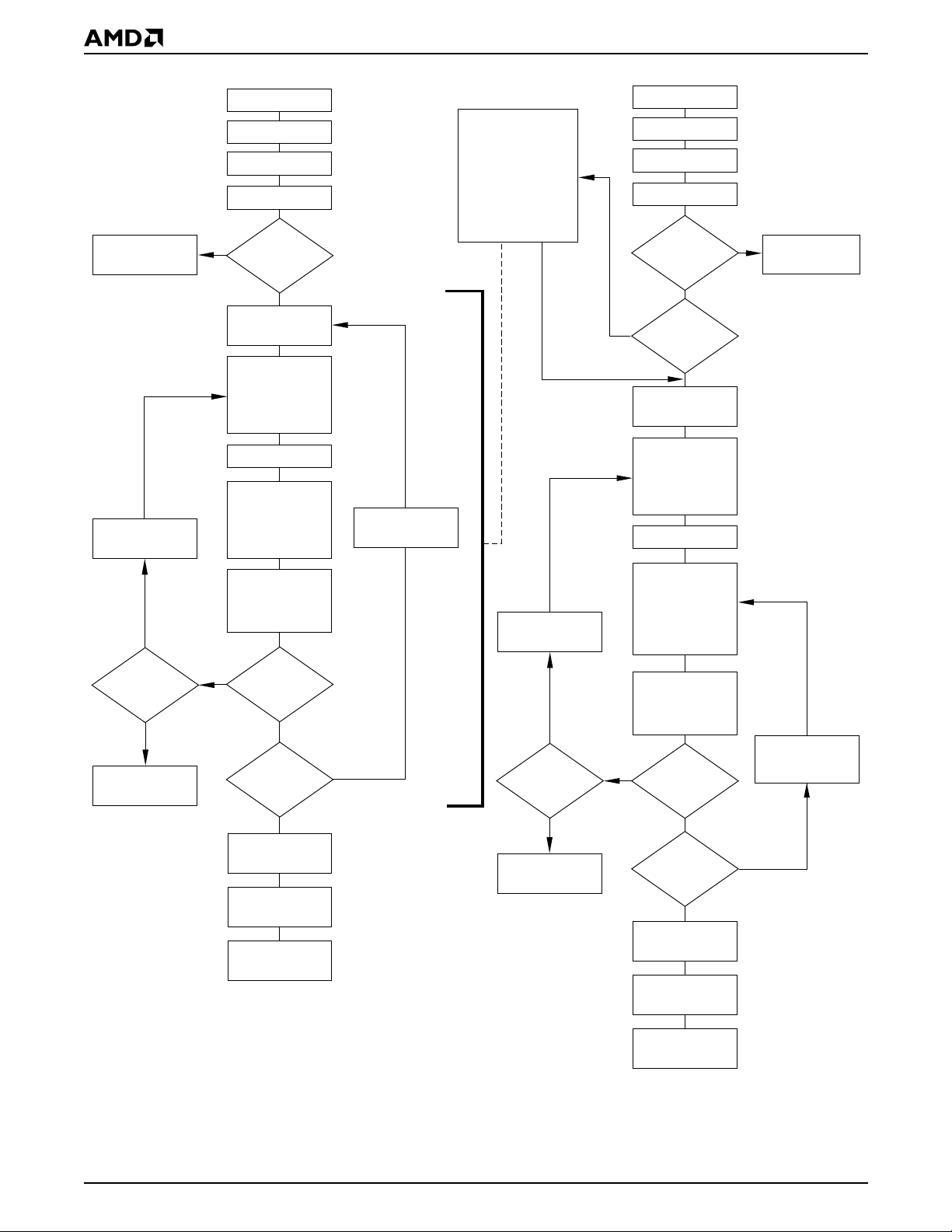

The hardware sector protection feature disables both

program and erase operations in any sector. The hardware sector unpr otection feature re- enables both

program and erase operations in previously protected

sectors. Note th at the sect or unprote ct algorit hm unprotects all sectors in par allel. All previously protected

sectors must be individually re-protected. To change

data in protected sect ors efficiently, the temporary

sector un protect function is available. See “Temporary

Sector/Sector Bloc k Unpr ote ct ”.

Sector protectio n and unprotection ca n be implemented as follows.

Sector protection and unprotection r e qui res V

on the

ID

RESET# pin only, and can be implemented either

in-system or via programming equipment. Figure 2

shows the algorithms and Figure 26 shows the timing

diagram. This method uses standard m icroprocess or

bus cycle timing. Fo r sector unpr otect, all unprotecte d

sectors must first be protected prior to the first sector

unprotect write cycle.

The device is shipped with all sectors unprotected.

It is possible to determine whether a secto r is pro-

tected or unprotected. See the Autoselect Mode

section for details.

Write Protect (WP#)

The Write Protect function provides a hardware

method of protecting certai n boot sectors without

using V

WP#/ACC pin.

If the system asserts V

vice disables program and erase functions in the two

“outermost” 8 Kbyte b oot sectors indep endently of

whether those sectors were protected or unprotected

using the method described in “Sector/Sector Block

Protection and Unprotection”. The two outermost 8

Kbyte boot sectors are the two sectors containing the

lowest addresses in the bottom-boot-configured

device.

If the system asserts V

vice reverts to whether the two outermost 8 Kbyte boot

sectors were last set to be protected or unp rotected.

That is, sector protecti on or unprotection for these tw o

sectors depends on whether they were last protected

or unprotected using the method desc ribed in “Sec-

tor/Sector Block Protection and Unprotection”.

. This function is one of two provided by the

ID

on the WP#/ACC pin, the de-

IL

on the WP#/ACC pin, the de-

IH

16 DS42516

Page 17

Note that the WP#/ACC pin must not be left floating or

unconnected; incons istent be havior of the de vice may

result.

Temporary Sector/Sector Block Unprotect

(Note: For the following discussi on, the term “sector”

applies to both sectors and sector blocks. A sector

block consists of two or more adjacent sectors that are

protected or unprotected at the same time (see Table

7).

This feature allows temporary unprotection of previ-

ously protected sectors to change data in-system. The

Sector Unprotect mo de is activa ted by setti ng the R ESET# pin to V

formerly protected sectors can be programmed or

erased by select ing t he se ctor addr esse s. Onc e V

removed from the RESET# pin, all the previously protected sectors are protected again. Figure 1 shows the

algorithm, and Figure 25 shows the timin g diagrams,

for this feature.

(8.5 V – 12.5 V). During this mode,

ID

is

ID

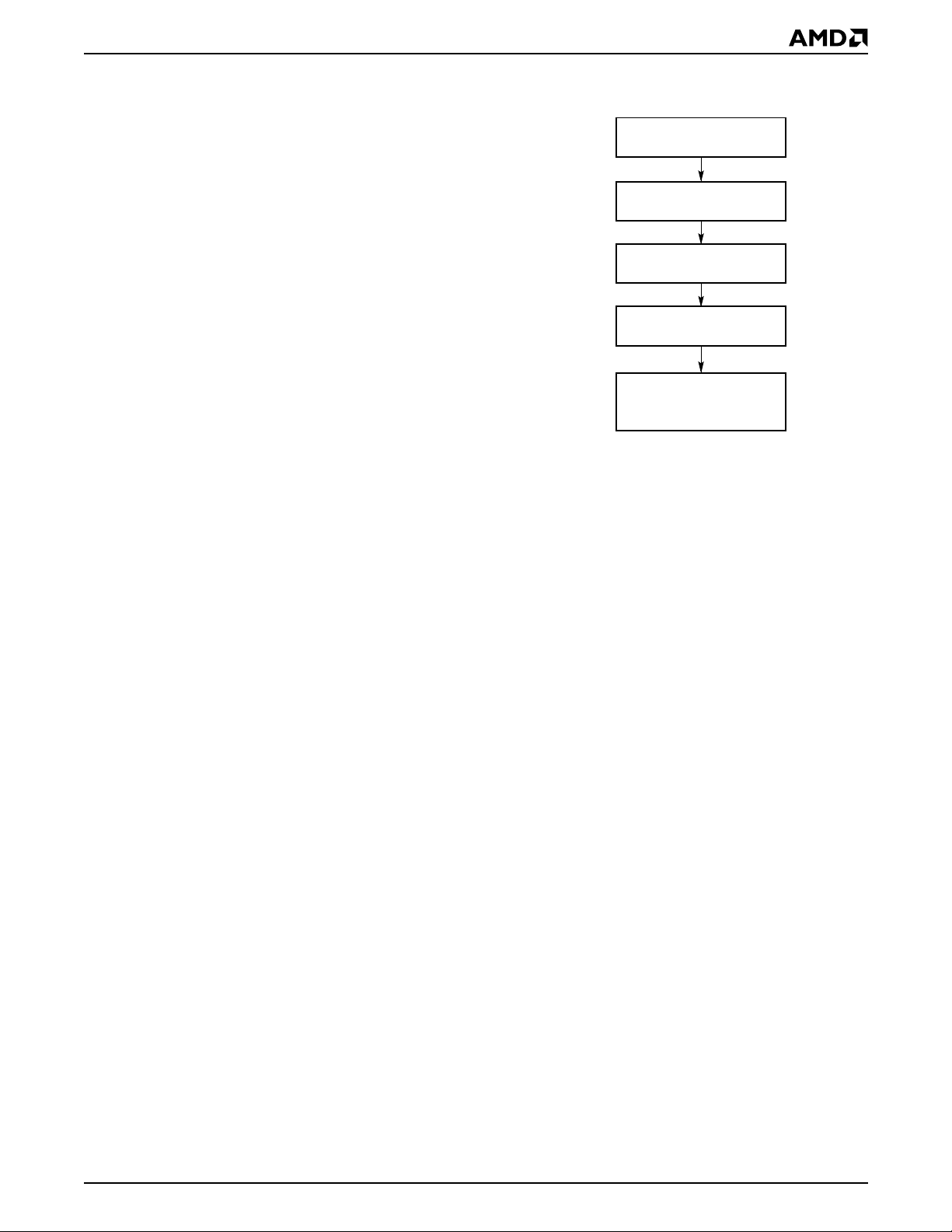

START

RESET# = V

(Note 1)

Perform Erase or

Program Operations

RESET# = V

Temporary Sector

Unprotect Completed

(Note 2)

ID

IH

Notes:

1. All protected sectors unprotected (If WP#/ACC = V

outermost boot sectors will remain protected).

2. All previously protected sectors are prote cte d once

again.

,

IL

Figure 1. Temporary Sector Unprotect Operation

DS42516 17

Page 18

Temporary Sector

Unprotect Mode

Increment

PLSCNT

No

PLSCNT

= 25?

Yes

Device failed

Sector Protect

Algorithm

START

PLSCNT = 1

RESET# = V

Wait 1 µs

No

First Write

Cycle = 60h?

Set up sector

address

Sector Protect:

Write 60h to sector

address with

A6 = 0, A1 = 1,

A0 = 0

Wait 150 µs

Verify Sector

Protect: Write 40h

to sector address

with A6 = 0,

A1 = 1, A0 = 0

Read from

sector address

with A6 = 0,

A1 = 1, A0 = 0

No

Data = 01h?

Protect another

sector?

Remove V

from RESET#

Write reset

command

Sector Protect

complete

Yes

Yes

No

START

Protect all sectors:

The indicated portion

of the sector protect

ID

Reset

PLSCNT = 1

Yes

ID

algorithm must be

performed for all

unprotected sectors

prior to issuing the

first sector

unprotect address

Increment

PLSCNT

No

PLSCNT

= 1000?

Yes

Device failed

Sector Unprotect

PLSCNT = 1

RESET# = V

Wait 1 µs

First Write

Cycle = 60h?

No

All sectors

protected?

Set up first sector

address

Sector Unprotect:

Write 60h to sector

address with

A6 = 1, A1 = 1,

A0 = 0

Wait 15 ms

Verify Sector

Unprotect: Write

40h to sector

address with

A6 = 1, A1 = 1,

A0 = 0

Read from

sector address

with A6 = 1,

A1 = 1, A0 = 0

No

Data = 00h?

Last sector

verified?

Remove V

from RESET#

Yes

Yes

Yes

Yes

ID

No

Temporary Sector

Unprotect Mode

Set up

next sector

address

No

ID

Algorithm

Write reset

command

Note: The term “sector” in the figure applies to both sectors and sector blocks.

Figure 2. In-System Sector/Sector Block Protect and Unprotect Algorithms

18 DS42516

Sector Unprotect

complete

Page 19

SecSi (Secured Silicon) Sector Flash

Memory R egion

The SecSi (Secured Silicon) Sector feature provides a

Flash memory region that enables perm anent part

identification through an Electronic Serial Number

(ESN). The SecSi Sector is 64 Kbytes in length, and

uses a SecSi Sector Indicator Bit to indicate whether

or not the SecSi Sector is locked wh en shipped from

the factory. This bit is permanently set at the factory

and cannot be chan ged, whic h prevents cloning of a

factory locked part. This ensures th e security of the

ESN once the product is shipped to the field.

AMD offers the dev ice with the Sec Si Sector ei ther

factory locked or customer lockable. The factory-locked versi on is al ways p rotec ted wh en shi pped

from the factory, and has the SecSi Sector Indicator

Bit permanently set to a “1.” The customer-lock able

version is shipped with the unprotected, allowing customers to utilize the that sector in any manner they

choose. The custom er-loc kable v ersion has th e Sec Si

Sector Indicator Bit permanently set to a “0.” Thus, the

SecSi Sector Indic ator Bit prev ents cus tomer-loc kable

devices from being used to replace devices that are

factory locked.

The system accesses the SecSi Sector through a

command sequence (s ee “Enter SecSi Sector/Exit

SecSi Sector Comman d Seq uence ”). Afte r the system

has written the Enter SecSi Sector command sequence, it may read the SecSi Sector by using the

addresses normally occupied by the boot sectors. This

mode of operation continues until the system issues

the Exit SecSi Sector command sequence, or until

power is removed from the device. On power-up, or

following a hardware reset, the device reverts to sending commands to the boot sectors.

ated programming (ACC) and unlock bypass functions

are not available wh en pro gram ming t he SecS i Se cto r.

The SecSi Sector area can be protected using one of

the following procedures:

■ Write the three-cycle Enter SecSi Sector Region

command sequence, and the n fol low th e in-s ys te m

sector protect algorithm as sho wn in Figure 2, except that RESET# may be at eith er V

or VID. This

IH

allows in-system protection of the without raising

any device pin to a high voltage. Note that this

method is only applicable to the SecSi Sector.

■ Write the three-cycle Enter SecSi Sector Region

command sequence, and then use the alternate

method of sector protection desc ribed in the “Sec-

tor/Sector Block Protection and Unprotection”.

Once the SecSi Sec tor i s locke d and v erified, t he system must write the Exit SecSi Sector Region

command sequence to return to reading and writing

the remainder of the array.

The SecSi Sector protection must be used with caution since, once protected, there is no procedure

available for unpro tecting the SecS i Sector area an d

none of the bits in th e SecSi Sect or memory space

can be modified in any way.

Hardware Data Protection

The command sequence r equ irement of unlock cycles

for programming or erasing provides data protection

against inadverten t writes ( refer to Table 12 for command definitions). In addition, the following hardware

data protection measures prevent accidental erasure

or programming , which might ot herwise be cause d by

spurious system level signals during V

and power-down transitions, or from system noise.

power-up

CC

Factory Locked: SecSi Sector Programmed and

Protected At the Factory

In a factory locked device, the SecSi Sector is protected when the device is shipped from the factory.

The SecSi Sector ca nnot b e mod ified in any w ay. The

device is available preprogrammed with a random, secure ESN only

In devices that have an ESN, the Bottom Boot device

will have the 16 -byte ES N in the lowe st addre ssable

memory area at addresses 00000h–00007h in word

mode (or 000000h–000 00Fh in byt e mo de).

Customer Lockable: SecSi Sect or NOT

Programmed or Protected At the Factory

If the security feature is not requi red, the Sec Si Sec tor

can be treated as an additional Flash memory space,

expanding the size of the available Flash array by 64

Kbytes. The SecSi Sector can be read, programmed,

and erased as often as required. Note that the acceler-

DS42516 19

Low V

When V

cept any write cycles. This protects data during V

Write Inhibit

CC

is less than V

CC

, the device d oes not ac-

LKO

CC

power-up and power-down. The command register

and all internal program/erase circuits are disabled,

and the device resets to reading array data. Subsequent writes are ignored until V

is greater than V

CC

LKO

The system must provide the proper signa ls to the

control pins to prevent unintentional writes when V

is greater than V

LKO

.

CC

Write Pulse “Glitch” Prote c t io n

Noise pulses of less than 5 n s (typi cal) on OE#, CE #f

or WE# do not initiate a write cycle.

Logical Inhibit

Write cycles are inhibited by holding any one of OE# =

, CE#f = VIH or WE# = VIH. To initiate a write cycle,

V

IL

CE#f and WE# must be a logical zero while OE# is a

logical one.

.

Page 20

Power-Up Write Inhibit

If WE# = CE#f = V

and OE# = VIH during power up,

IL

the device does not accept commands on the rising

edge of WE#. The internal state machine is automatically reset to reading array data on power-up.

COMMON FLASH MEMORY INTERFACE

(CFI)

The Common Flash Interface ( CFI) specific ation outlines device and hos t system software interrogation

handshake, which allows specific vendor-spe cified

software algorithms to be used for entire families of

devices. Software support can then be device-in dependent, JEDEC ID-i ndependent, an d forward- and

backward-compatible for the specified flash device

families. Flash vendors can standardize their existing

interfaces for long-term compatibility.

This device enters th e CF I Query mode when the system writes the CFI Query c ommand, 98 h, to address

Table 8. CFI Query Identification String

Addresses

(Word Mode)

Addresses

(Byte Mode)

Data Description

55h in word mode (or address AAh in byte mode), any

time the device is ready to read array data. The system can read CFI information at the addresses given

in Tables 8–11. To terminate reading CFI data, the system must write the reset command. The CFI Query

mode is not acces sible wh en the de vice i s executin g

an Embedded Program or embedded erase algorithm.

The system can also write the CFI query command

when the device is in the autoselect mode. The device

enters the CFI query mode, and the system can read

CFI data at the addresses given in Tables 8–11. T he

system must write the reset command to return the device to the autoselect mode.

For further information, please refer to the CFI Specification and CFI Publication 100, available via the

World Wide Web at http://www.amd.com/products/nvd/overview/cfi.html. Alternatively, contact an

AMD representative for copies of these documents.

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

20h

22h

24h

26h

28h

2Ah

2Ch

2Eh

30h

32h

34h

0051h

0052h

0059h

0002h

0000h

0040h

0000h

0000h

0000h

0000h

0000h

Query Unique ASCII string “QRY”

Primary OEM Command Set

Address for Primary Extended Table

Alternate OEM Command Set (00h = none exists)

Address for Alternate OEM Extended Table (00h = none exists)

20 DS42516

Page 21

T able 9. System Interface String

Addresses

(Word Mode)

1Bh 36h 0027h

1Ch 38h 0036h

1Dh 3Ah 0000h V

Addresses

(Byte Mode)

Data Description

Min. (write/erase)

V

CC

D7–D4: volt, D3–D0: 100 millivolt

Max. (write/erase)

V

CC

D7–D4: volt, D3–D0: 100 millivolt

Min. voltage (00h = no VPP pin present)

PP

1Eh 3Ch 0000h VPP Max. voltage (00h = no VPP pin present)

1Fh 3Eh 0004h Typical timeout per single byte/word write 2N µs

20h 40h 0000h Typic al timeout for Min. size buffer write 2N µs (00h = not supported)

21h 42h 000Ah Typical timeout per individual block erase 2N ms

22h 44h 0000h Typical timeout for full chip erase 2N ms (00h = not supported)

23h 46h 0005h Max. timeout for byte/word write 2N times typical

24h 48h 0000h Max. timeout for buffer write 2N times typical

25h 4Ah 0004h Max. timeout per individual block erase 2N times typical

26h 4Ch 0000h Max. timeout for full chip erase 2N times typical (00h = not supported)

T able 10. Device Geometry Definition

Addresses

(Word Mode)

27h 4Eh 0015h Device Size = 2

28h

29h

2Ah

2Bh

Addresses

(Byte Mode)

50h

52h

54h

56h

Data Description

N

byte

0002h

0000h

0000h

0000h

Flash Device Interface des cri pti on (refe r to CFI publica t io n 100)

Max. number of byte in multi-byte write = 2

(00h = not supported)

2Ch 58h 0002h Number of Erase Block Regions within device

2Dh

2Eh

2Fh

30h

31h

32h

33h

34h

35h

36h

37h

38h

39h

3Ah

3Bh

3Ch

5Ah

5Ch

5Eh

60h

62h

64h

66h

68h

6Ah

6Ch

6Eh

70h

72h

74h

76h

78h

0007h

0000h

0020h

0000h

001Eh

0000h

0000h

0001h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

Erase Block Region 1 Information

(refer to the CFI specification or CFI publication 100)

Erase Block Region 2 Information

Erase Block Region 3 Information

Erase Block Region 4 Information

N

DS42516 21

Page 22

Table 11. Primary Vendor-Specific Extended Query

Addresses

(Word Mode)

40h

41h

42h

43h 86h 0031h Major version number, ASCII

44h 88h 0031h Minor version number, ASCII

45h 8Ah 0000h

46h 8Ch 0002h

47h 8Eh 0001h

48h 90h 0001h

49h 92h 0004h

4Ah 94h

Addresses

(Byte Mode)

80h

82h

84h

Data Description

0050h

0052h

0049h

00XXh

(See Note)

Query-unique ASCII string “PRI”

Address Sensitive Unlock (Bits 1-0)

0 = Required, 1 = Not Required

Silicon Revision Number (Bits 7-2)

Erase Suspend

0 = Not Supported, 1 = To Read Only, 2 = To Read & Write

Sector Protect

0 = Not Supported, X = Number of sectors in per group

Sector Temporary Unprotect

00 = Not Supported, 01 = Supported

Sector Protect/Unprotect scheme

04 = 29LV800 mode

Simultaneous Operation

00 = Not Supported, X= Number of Sectors in Bank 2 (Uniform Bank)

4Bh 96h 0000h

4Ch 98h 0000h

4Dh 9Ah 0085h

4Eh 9Ch 0095h

4Fh 9Eh 000Xh

Note:

The number of sectors in Bank 2 is device dependent, Am29DL324 = 20h.

Burst Mode Type

00 = Not Supported, 01 = Supported

Page Mode Type

00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word Page

ACC (Acceleration) Supply Minimum

00h = Not Supported, D7-D4: Volt, D3-D0: 100 mV

ACC (Acceleration) Supply Maxim um

00h = Not Supported, D7-D4: Volt, D3-D0: 100 mV

Top/Bottom Boot Sector Flag

02h = Bottom Boot Device, 03h = Top Boot Device

22 DS42516

Page 23

COMMAND DEFINITIO N S

Writing specific address and data commands or sequences into the command register initiates device

operations. Ta ble 12 defines th e valid register command sequences. Writing incorrect address and

data values or writing them in the improper sequence resets the device to reading array data.

All addresses are latched on the falling edge of WE#

or CE#f, whiche ver ha ppens late r. All data is latc hed

on the rising edge of W E# or CE#f, whiche ver happens first. Refer to the AC Characteristics section for

timing diagrams.

Reading Array Data

The device is automati cally set to re ading array dat a

after device power-up. No commands are required to

retrieve data. Each bank is ready to read array data

after completing an Embedded Program or Embedded

Erase algorithm.

After the device accepts an Erase Suspend command,

the corresponding bank enters the erase-suspend-read mode, after which the system can read

data from any non-erase-suspended sector within the

same bank. After completing a programming operation

in the Erase Suspend mode, the system may once

again read array data with the same exception. See

the Erase Suspend/Erase Resume Commands section for more information.

The system must issu e the re set c omm and to r eturn a

bank to the read (or erase-suspend-read) mode if DQ5

goes high during an active program or erase operation, or if the bank is in the autoselect mode. See the

next section, Reset Command, for more information.

See also Requirements for Reading Array Data in the

Device Bus Operations section for more information.

The Flash Read-Only Operations table provides the

read parameters, and Figure 14 shows the timing

diagram.

Reset Command

Writing the reset command resets the banks to the

read or erase-suspend-read mode. Address bits are

don’t cares for this command.

The reset command may be written between the sequence cycles in an erase co mm and s equ enc e befo re

erasing begins. Th is rese ts the b ank to w hich t he system was writing to reading a rray data . Once eras ure

begins, however, the device ignores reset commands

until the operation is complete.

The reset command may be written between the

sequence cycles in a program command sequence

before programming begins. This resets the bank to

which the system was writing to reading array data. If

the program command sequence is written to a bank

that is in the Erase Suspend mode, writing the reset

command returns that ban k to the erase-suspend-read mode. Once programming begins,

however, the device ignores reset comman ds unti l the

operation is complete.

The reset command may be written between the sequence cycles in an autosel ect comm and sequen ce.

Once in the autoselect mode, the reset command

must be written to return to reading array data. If a

bank entered the autoselect mode while in the Erase

Suspend mode, writing the reset command returns

that bank to the erase-suspend-read mode.

If DQ5 goes high during a program or erase operation,

writing the reset command returns the banks to reading array data (or erase-suspend-read mode if that

bank was in Erase Suspend).

Autoselect Command Sequence

The autoselect command sequenc e allows the host

system to access the manufac ture r and de vice codes ,

and determine whether or not a sector is p rotected.

Table 12 shows the address and data requirements.

The autoselect command sequence may be written to

an address within a ba nk that is ei ther in the rea d or

erase-suspend-read mode. The autoselect command

may not be written while the device is actively programming or erasing in the other bank.

The autoselect comm and s equen ce i s init iated by first

writing two unlock cycles. This is followed by a third

write cycle that con tain s t he ba nk add ress an d the autoselect comman d. The bank then enters the

autoselect mode. The system may read at any address within the same bank any number of times

without initiating another autoselect command

sequence:

■ A read cycle at addres s (BA)XX00h (where BA is

the bank address) returns the manufacturer code.

■ A read cy cle at address (BA)X X01h in word mode

(or (BA)XX02h in byte mode) returns the dev ice

code.

■ A read cy cle to an a ddress co ntaining a sector address (SA) within the same bank , and the address

02h on A7–A0 in word mode (or the address 04h on

A6–A-1 in byte mode) returns 01h if the sector is

protected, or 00h if it is unprotected. (Refer to Tables 5–6 for valid sector addre sses ) .

The system must write the reset command to return to

reading array data (or erase-suspend-read mode if the

bank was previously in Erase Suspend).

DS42516 23

Page 24

Enter SecSi Sector/Exit SecSi Sector

Command Sequence

The system can acces s the S ec Si Se ct or re gio n by issuing the thre e-cycle Ente r SecSi S ector co mmand

sequence. The device continues to access the SecSi

Sector region until the sy stem issues the four-cyc le

Exit SecSi Sector command sequence. The Exit SecSi

Sector command sequence returns the device to normal operation. Table 12 shows th e address and data

requirements for bot h com ma nd seq ue nces. Se e also

“SecSi (Secured Silicon) Sector Flash Memory Region” for fu rther information. Note that a har dware

reset (RESET# =V

) will reset the device to reading

IL

array data.

Byte/Word Program Command Sequence

The system may program the device by word or byte,

depending on the state of the CIOf pin. Programming

is a four-bus-cycle operation. The program command

sequence is initiated by writi ng two unlock write cycles, follo wed by th e progr am set-up command . The

program address and data are written next, which in

turn initiate the Embedded Program algorithm. The

system is not required to provide fur ther controls or

timings. The device automatically provides internally

generated program pulses and verifies the programmed cell margin. Table 12 shows the address

and data requirements for the byte program command

sequence.

When the Embedded Program algorithm is complete,

that bank then returns to reading array data and addresses are no longer latched. The system can

determine the status of the prog ram operation by

using DQ7, DQ6, or RY/BY#. Refer to the Write O peration Status se ction for info rmation on the se status

bits.

Any commands written to the device during the Embedded Program Algorithm are i gnored. Note that a

hardware reset immediately terminates the p rogram

operation. The program command sequence should

be reinitiated once th at bank ha s retur ned to readin g

array data, to ensure data integrity.

Programming is allowed in any sequence and across

sector bounda ries. A bit cannot be programmed

from “0” back to a “1.” Attempting to do so may

cause that bank to set DQ5 = 1, or cause the DQ7 and

DQ6 status bits to indicate the operation was success-

ful. However, a succeeding read will show that the

data is still “0.” Only erase operations can convert a

“0” to a “1.”

Unlock Bypass Command Sequence

The unlock bypass feature allows the system to program bytes or words to a bank faster than using the

standard program command sequence. The unlock

bypass command sequence is initiated by first writing

two unlock cycles. Th is is followed by a third write

cycle containing the unlock bypass command, 20h.

That bank then enters the unlock bypass mode. A