AMD Advanced Micro Devices AMMCL004AWP-150I, AMMCL004AWP-150, AMMCL002AWP-150I Datasheet

PRELIMINARY

AmMCL00XA

2 or 4 Megabyte 3.0 Volt-only Flash Miniature Card

DISTINCTIVE CHARACTERISTICS

■ 2 or 4 Mbytes of addressable Flash memory

■ 2.7 V to 3.6 V, single power supply operation

— Write and read voltage: 3.0 V –10/+20%

— No additional supply current required for V

■ Fast access time

— 150 ns maximum access time

■ CMOS low power consumption

— Typical active read current:

35 mA (word mode)

— Typical active erase/write current:

40 mA (word mode)

— Typical standby current:

10 µA (4 Mbyte); 5 µA (2 Mbyte)

■ High write endurance

— Guaranteed minimum 100,000 write/erase

cycles per card

— More than 1,000,000 cycles per card typical

■ Uniform sector architecture

— 64K byte individually useable sectors

— Erase Suspend/Resume increases system level

performance

— BUSY# and RESET# signals

■ Zero data retention power

— No power required to retain data

PP

■ Available in industrial temperature grade

(–40°C to +85°C)

■ Miniature Card standard form factor

— True interchangeability

— 60-pad elastomeric connector

— Supports multiple technologies

— Sonic welded stainless steel case

— PCMCIA Type II adapter available

— Selectable byte- or word-wide configuration

— Small Form Factor (38 mm x 33 mm x 3.5 mm)

■ 60 connection bus

— 16-bit data bus

— 25-bit address bus

— Easy system integration

— Low cost implementation

— Low cost card s

■ Consumer-friendly mechanicals

— User can easily insert and remove card, upgrade

memory, and add applications

■ Voltage level keying

— Does not allow a 3 V card to plug into a 5 V

system and vice versa

— Single power supply design

— System does not need a separate program

voltage supply; only one is necessary to read

and write

GENERAL DESCRIPTION

The Miniature Card is an expansion card that provides a low cost, low power, high-performance, small

form factor solution for data and file storage to the

portable, handheld market, which includes audio,

digital film, wireless, and PDA (Por table Digital

Assistant) applications.

Miniature cards can be e asily “snappe d” into the back

of an electronic system and can be readily removed

and replaced by end users. AMD’s 3 V Flash Miniature

Cards are manufactured using AMD’s industry leading

3.0 volt-only, single-power-supply Am29LV081 Flash

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this product. AMD re serves the right to cha nge or discontinue work o n this proposed

product without notice.

Memory device, ensuring h igh reliability and excellent

performance. The Miniature Card is less than 30% of

the size of a PCMCIA memory card. Applications

include digital voice recorders, pocket P Cs and intelligent organizers, smart ce llular telephones, voice and

data messaging pagers, digital still came ras and portable instrumentation equipment.

The Miniature Card sp ecification will be defined by

PCMCIA as of October 1997. The participating association members include major Flash memory vendors

and leading consumer electronics OE Ms. The goal of

the Miniature Card specification is to promote an open,

Publication# 21138 Rev: E Amendment/0

Issue Date: September 1997

PRELIMINARY

interoperable small-form-factor memory card standard.

For more information on the Miniatu re Card specification, visit the PCMCIA web site at

http://www.pc-card.com.

AMD Flash Miniature Cards can be read in either a

byte-wide or word-wide mode, which allows for flexible

integration into various system platforms. Compatibility

is assured at the hardware interface and software interchange specification.

The Miniature Card is also designed with low-cost and

rugged handling in mind. The card contains virtually no

control logic, which keeps cost and power consumption

to a minimum. The Miniature Card is packaged in a

sonic welded, stainless steel case that guarantees

durability, provides good ESD protection and ease of

handling.

The Miniature Card has extensive third-party support,

including socket and connector solutions, software

Table 1. Miniature Card Definitions

Term Meaning

support from the major FTL software vendors, and

PCMCIA adapter solutions and programmer support.

AMD's Miniature Flash cards can be used for both code

and data stor age. Since fas t random access is possible, code can be direct ly executed from the card,

reducing the amount of system RAM required. In addition. AMD’s Flash technology offers unsurpassed

endurance, data retention and reliability, eliminating

the need for complex error correctio n an d de fect ma nagement hardware and software. Each Flash sector

provides a min imum of 100,00 0 cycles, and a typ ical

card life of one million or more cycles.

For more informat ion, please contact yo ur local AMD

sales office or visit our Web site at

http://www.amd.com/html/products/nvd/nvd.html.

DEFINITIONS

Table 1 lists the terms and definitions that may be used

in conjunction with Miniature Card specifications.

AIS

ESD Acronym for Electrostatic Discharge. ESD is part of the Miniature Card physical test.

FAT

Flash

Host Any system that incorporates a Miniature Card socket.

Insertion, Cold

Insertion, Hot

Insertion, Pseudo Hot

Acronym for Attribute Informati on Stru cture. AIS is a Miniature Card sp ecifi cation for stor ing

Miniature Card attribute information.

Acronym for File Alloca tion Table. Using an F AT is a common method for managing files in a

DOS-based system.

A type of non-volatil e me mory tha t is both read abl e and writea ble , but requir es th e media to

be erased before it is rewritten.

User Perception:

Host State:

host is non-op erati onal by the user. The user inserts the Miniature Card and then presses a

button to turn the host on before the syste m is operational.

User Perception:

Host State:

operational by the user. The user inserts the card, the host recognizes it, and the host

continues to be operation al. Note: Ho t insert ion ma y require bu ff ering on the host sy stem for

proper operation.

User Perception:

Host State:

operational by th e user . The user in serts the card, the ho st immediately powers off be fore the

Miniature Card makes contac t with the host’s intern al bus. The user would then need to press

a button to turn the host on for it to become operational.

Insertion of the Miniature Card when the host is of f.

The host would be either off or in sleep mode, no bus activity is occurring, the

Insertion of a Miniature Card when the host is running.

The host would be in running mode, bus activity is occurring, the host is

Insertion of a Miniature Card when the host is running.

The host would be in running mode, bus activity is occurring, the host is

Interface Signals Miniature Card signals that make connection through the 60-pad connector area.

JEDEC Acronym for Joint Electronic Device Engineering Council.

Miniature Card Backside

Miniature Card Bottomside

The side of the Miniature Card that contains the latching mechanism. The backside is

opposite the frontside.

The side of the Min iature Card that conta ins the in terface signals . The bottomside i s opposite

the topside.

2 AmMCL00XA

PRELIMINARY

Table 1. M iniature Card Definitions (Continued)

Term Meaning

Miniature Card Frontside

Miniature Card Topside

PC Card A memory or I/O card compatible with the PC Card Standard.

PC Card Adapter

Power/Insertion Signals

Pull-Ups Resistors used to ensure that signals do not float when no device is driving them.

Removal, Cold

Removal, Hot

Removal, Pseudo Hot

The side of the Miniature Card that contains power, insertion, ground, voltage keys, and

alignment notch. The frontside is opposite the backside.

The side of the Mini ature Card that co ntains the Mi niature Card labe l. The topsi de is opposite

the bottomside.

The hardware that connects the Miniature Card 60 contact bus to the PC Card 68 pin bus.

This hardware can be mechanically implemented by following the PC Card Type II

specification.

The three signals on the frontside of the Minia ture Card that provide grou nd, power and early

detection of insertio n.

User Perception:

Host State:

host is non-opera tion al by the use r. User would turn off the host, then remove the Miniature

Card and then press a button to turn the host on for it to become operational again.

User Perception:

Host State:

operational by th e user. User removes the card, the host reco gnize s the ev ent, and th e ho st

continues to be operati ona l.

User Perception:

Host State:

operational by the user. User removes the card, the host recognizes the event, the hos t

immediately powers off before the Miniature Card removes contact with the host’s internal

bus. The user would then need to press a button to turn the host on for it to be operational

again.

Removal of a Miniature Card when the host is off.

The host would either be off or in sleep mode, no bus activity is occurring, the

Removal of the Miniature Card when the host is running.

The host would be in running mode, bus activity is occurring, the host is

Removal of the Miniature Card when the host is running.

The host would be in running mode, bus activity is occurring, the host is

Sector Usually 64 KBytes. In word mode, a sector is 64 Kwords .

Tuple

User Insertable

User Removable

User Non-Removable

XIP

An element of the PC Ca rd Standard CIS that provides card at trib ute information, and a link

to the next tuple in a string of tuples.

All Miniature Cards should be inserted into the host by the user without the need for any

special tools.

This type of Miniature Card can be removed by the user withou t the need for any specia l

tools. It conta ins progra ms and data that users may want to switch ofte n. The use o f this typ e

of card is similar to a floppy disk.

This type of Miniature Card must be removed by the user with a special tool. It contains

memory upgrades or boot prog ram that us ers switc he s onl y whe n they require an upgrade.

The use of this type of card is similar to a SIMM memory expansion or boot hard disk.

Acronym for eXecute-In-Place, which refers to code that executes directly from a Miniature

Card.

AmMCL00XA 3

PRELIMINARY

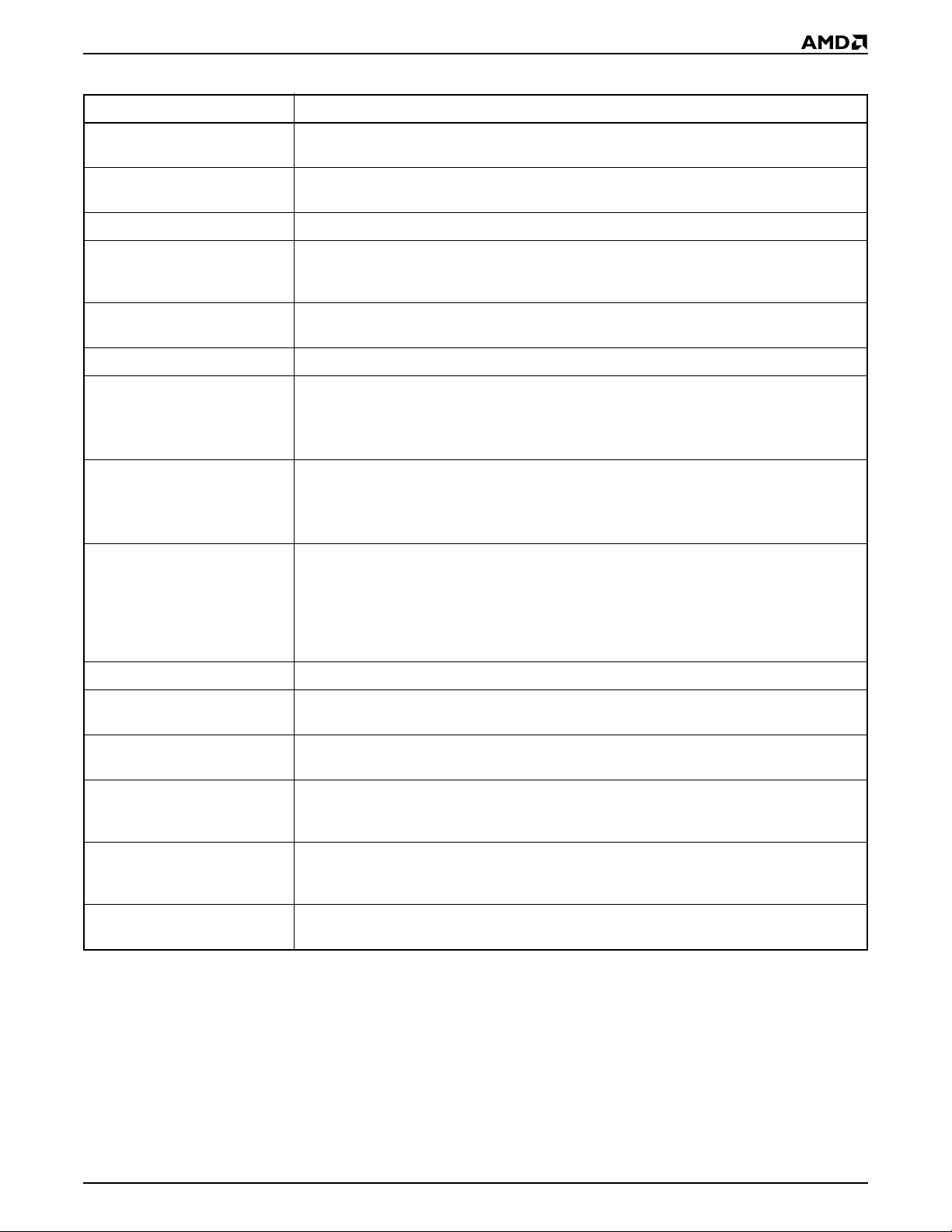

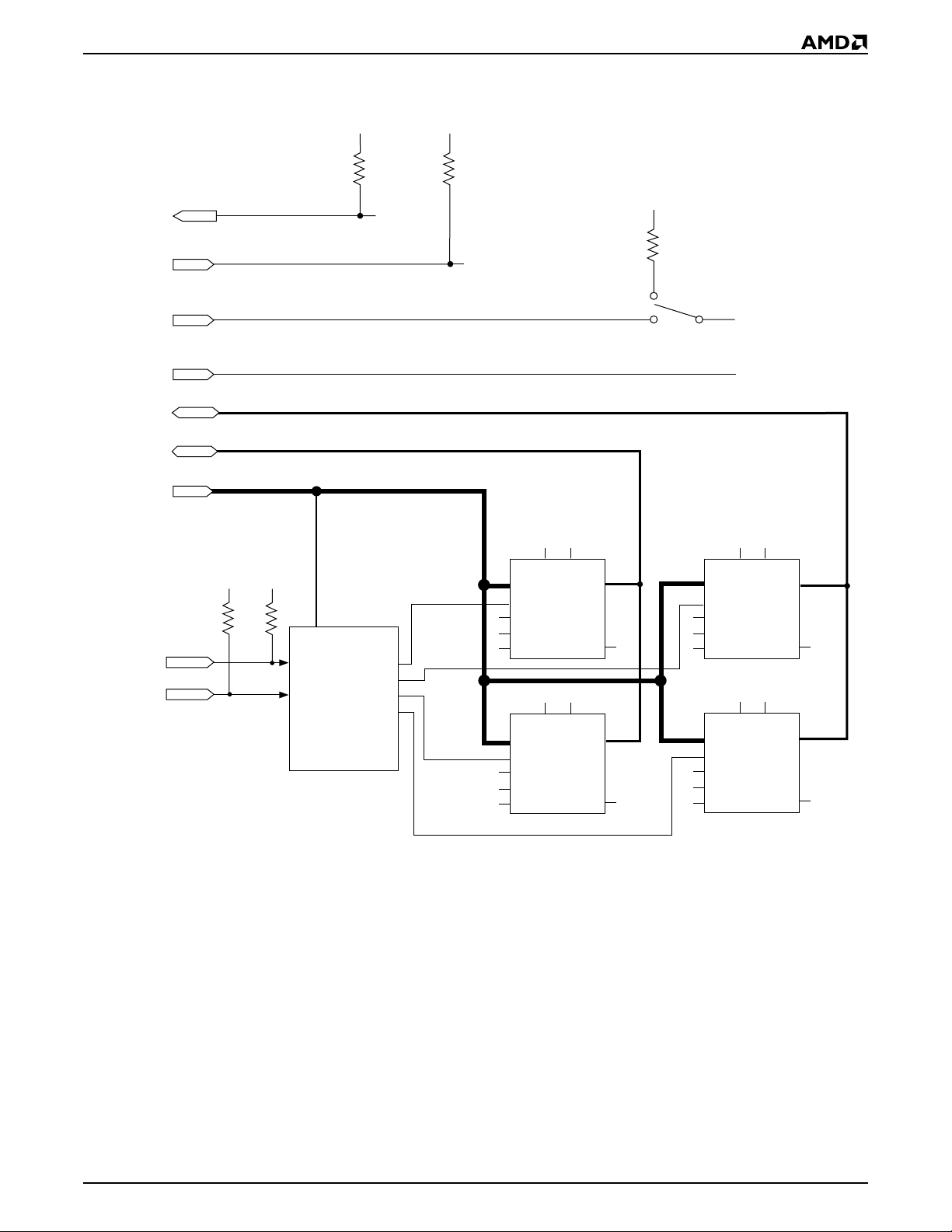

Write Protect Switch (optional)

Pad 60 Pad 31

Pad 30 Pad 1

Key

Alignment

Notch

CINS# GND

21138E-1

V

CC

3V/5V

Figure 1. Miniature Card Connector (Card Bottom View)

Note: Refer to the Physical Dimens ions section for more information. Als o refer to the MCIF spe cification for det ailed mechan ical

information, available on the Web at http://www.mcif.org.

Table 2. AMD Flash Miniature Cards and Flash Devices

Family Part Number Density No. of Flash Devices AMD Flash Memory

AmMCL002AWP 2 Mbyte 2 Am29LV081

AmMCL004AWP 4 Mbyte 4 Am29LV081

4 AmMCL00XA

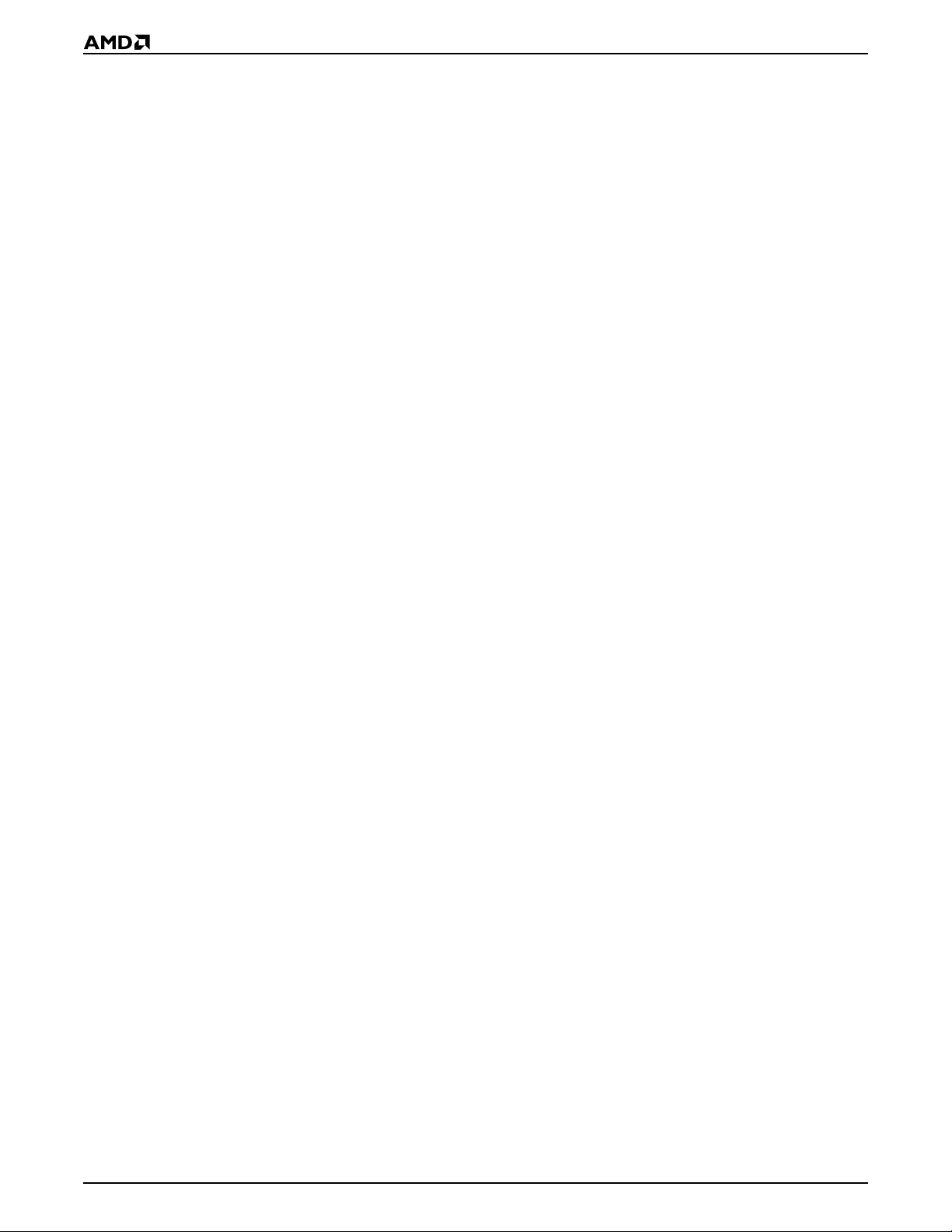

BLOCK DIAGRAM

PRELIMINARY

BUSY#

RESET#

WE#

OE#

D8-D15

D0-D7

A0-A20

CEL#

CEH#

100K

V

CCVCC

100K

A20

Decoder*

V

CC

RY/BY#

CEL0#

CEH0#

CEL1#

CEH1#

V

CC

100K100K

V

CC

10K

RESET# to all Flash devices

WE# to all Flash devices

Write Protect

Switch

OE# to all Flash devices

V

A0-A19

CE#

WE#

OE#

RESET#

V

A0-A19

CE#

WE#

OE#

RESET#

SSVCC

D0-D7

S0**

RY/BY#

SSVCC

D0-D7

S2**

RY/BY#

V

A0-A19

CE#

WE#

OE#

RESET#

V

A0-A19

CE#

WE#

OE#

RESET#

SSVCC

D8-D15

S1**

RY/BY#

SSVCC

D8-D15

S3**

RY/BY#

21138E-2

* 4 Mbyte card only. Not used on 2 Mbyte card.

** 2 Mbyte card: Two Am29LV081 devices, S0 and S1

4 Mbyte card: Four Am29LV081 devices, S0...S3

Note: On the 2 Mbyte card, A20–A24 are not connected. On the 4 Mbyte card, A21– A24 are not co nne cte d. Connections not

shown in this diagram are not connected internally.

AmMCL00XA 5

PRELIMINARY

MINIATURE CARD PAD ASSIGNMENTS

A0–A24

Address A0 to A24 are the address bus lines that can

address up to 32 Mwords (64 Mbytes ). The address

lines are word addressed. The Miniat ure Card specification does not requ ire the Miniature Card to decode

the upper address lines. A 2 Mbyte Miniature Card that

does not decode the upper address lines would repeat

its address space every 2 Mbytes. Address 0h would

access the same ph ysical location as 200000h,

400000h, 600000h, etc. On t he 2 Mbyte cards, A20–

A24 are not connected. On the 4 Mbyte cards,

A21–A24 are not connected.

D0–D15

Data lines D0 through D15 constitute the data bus. The

data bus is composed of two bytes; the low byte is

D0–D7 and the hig h byte is D8–D15. Th ese lines are

tristated when OE# is high.

OE#

OE# indicates to the card that the current bus cycle is

a read cycle. The output enable access time (t

delay from the falling edge of OE# to val id data at the

output pins (assuming the addresses have been stable

for at least t

– tOE time).

ACC

OE

) is the

WE#

WE# indicates to the card tha t th e current bus cy cle is

a write cycle. The falling edge of WE# (or CE#), whichever occurs later, latches address information and the

rising edge of WE# (or CE#), whichever occurs first

latches data/command information.

VS1#

Voltage Sense 1 signal. This signal is grounded.

VS2#

Voltage Sense 2 signal. This signal is left open or no t

connected.

CEL#

CEL# enables the low byte of the data bus (D0–D7) on

the card.

CEH#

CEH# enables the high byte of the data bus (D8–D15)

on the card.

RESET#

RESET# controls card initializ ation. When RESET#

transitions from a low state to a high state, the Miniature Card resets to the Read state after a maximum

delay of 20 µs.

BUSY#

BUSY# is a signal generated by the card to indicate the

status of operations within the Miniature Card. When

BUSY# is high, the Mini ature Card is ready to accept

the next command from the host. When BUSY# is low,

the Miniature Card is busy and unable t o accept most

data operations from the host. In Flash Miniature Cards

the BUSY# si gnal is ti ed to the co mponents’ RY/B Y#

signal.

CD#

CD# is a groun ded inte rface signa l. After a Mi niature

Card has been inserted, CD# will be forced low. T he

card detect signal is located in the center of the second

row of interface signals, and shou ld be one of the last

interface signals to connect to the host. Do not confuse

CD# with CINS#.

CINS#

CINS# is a grounded signal on the front of the Miniature

Card that is used for early detection of a card insertion.

CINS# makes contact on the host when the front of the

card is inserted into the socket, before the interface

signals connect.

BS8#

The BS8# (Bus size 8) signal indi cates to the Miniature Card that the host has an 8-bit bus. AMD F lash

Miniature Cards ignore this signal ( no internal connection). An 8-bit host m ust connect its D0–D7 data

lines to D8–D15 on the Mi niatur e Card to retr ieve the

upper (odd) byte.

GND

Ground

V

CC

Vcc is used to supply power to the card.

NC

No connect

RFU

Reserved for future use

6 AmMCL00XA

PRELIMINARY

ORDERING INFORMATION

Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is

formed by a combination of the following:

AM MC 004 WP

L

A

-150

I

TEMPERATURE RANGE

Blank = Commercial (0°C to +70°C)

I = Industrial (–40°C to +85°C)

SPEED OPTION

WRITE PROTECT SWITCH OPTION

WP = Switch installed

REVISION LEVEL

MEMORY CARD DENSITY

002 = 2 Megabyte Card

004 = 4 Megabyte Card

3 V, SINGLE SUPPLY OPERATION

2.7 V to 3.6 V, extended

operating voltage

MINIA TURE CARD

AMD

AmMCL00XA 7

PRELIMINARY

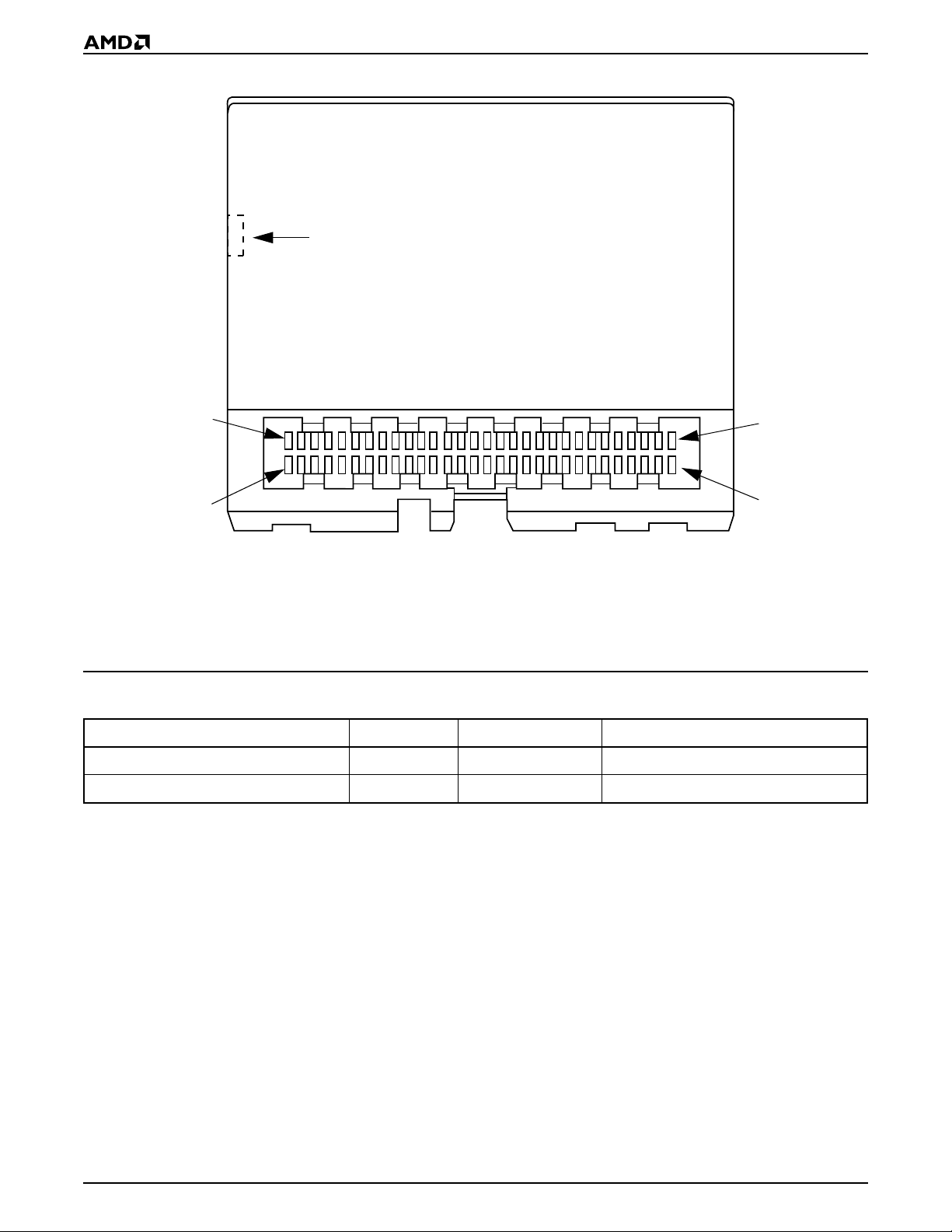

INTERFACE SIGNAL ASSIGNMENTS

Pad Number Signal Name Pad Number Signal Name Pad Number Signal Name

1 A18 21 D12 41 A4

2 A16 22 D10 42 CEL#

3 A14 23 D9 43 A1

4NC24D044NC

5 CEH# 25 D2 45 NC

6 A11 26 D4 46 CD#

7 A9 27 RFU 47 A21

8 A8 28 D7 48 BUSY#

9 A629NC49WE#

10 A5 30 NC 50 D14

11 A3 31 A19 51 RFU

12 A2 32 A17 52 D11

13 A0 33 A15 53 VS2#

14 NC 34 A13 54 D8

15 A24 35 A12 55 D1

16 A23 36 RESET# 56 D3

17 A22 37 A10 57 D5

18 OE# 38 VS1# 58 D6

19 D15 39 A7 59 RFU

20 D13 40 BS8# 60 A20

Note: NC = No Connect; RFU = Reserved for Future Use.

FLASH MINIATURE CARD OPERATIONS

Voltage Sensing

AMD Miniature Cards provide two voltage sense

signals for hosts that support multiple voltages. The

multivolta ge host can s ense the volt age level o f the

Miniature Card and power up the card at that voltage.

See Table 3 for a description of the voltage

sense signal s.

In addition to th e voltage sens e pins, there are a lso

mechanical voltage keys on the Miniature Card that

ensure the card can only be inserted into host systems

that can su pply the prop er voltage le vels to the card.

Refer to Section 4.1.2 in the Min iature Card specification for more information on mechanical keying.

Table 3. Voltage Sense Signals

Miniature Card

Power-Up Voltage VS1# VS2#

3 volt-only Gnd Open

8 AmMCL00XA

PRELIMINARY

Data Accesses

The Miniatur e Card has a 16-bit data bu s that can

accommodate word or byte a ccesses. By individually

asserting CEL# and CEH#, a host can access either

byte. However, byte swapping (moving the high byte

data to the low byte) is not supported.

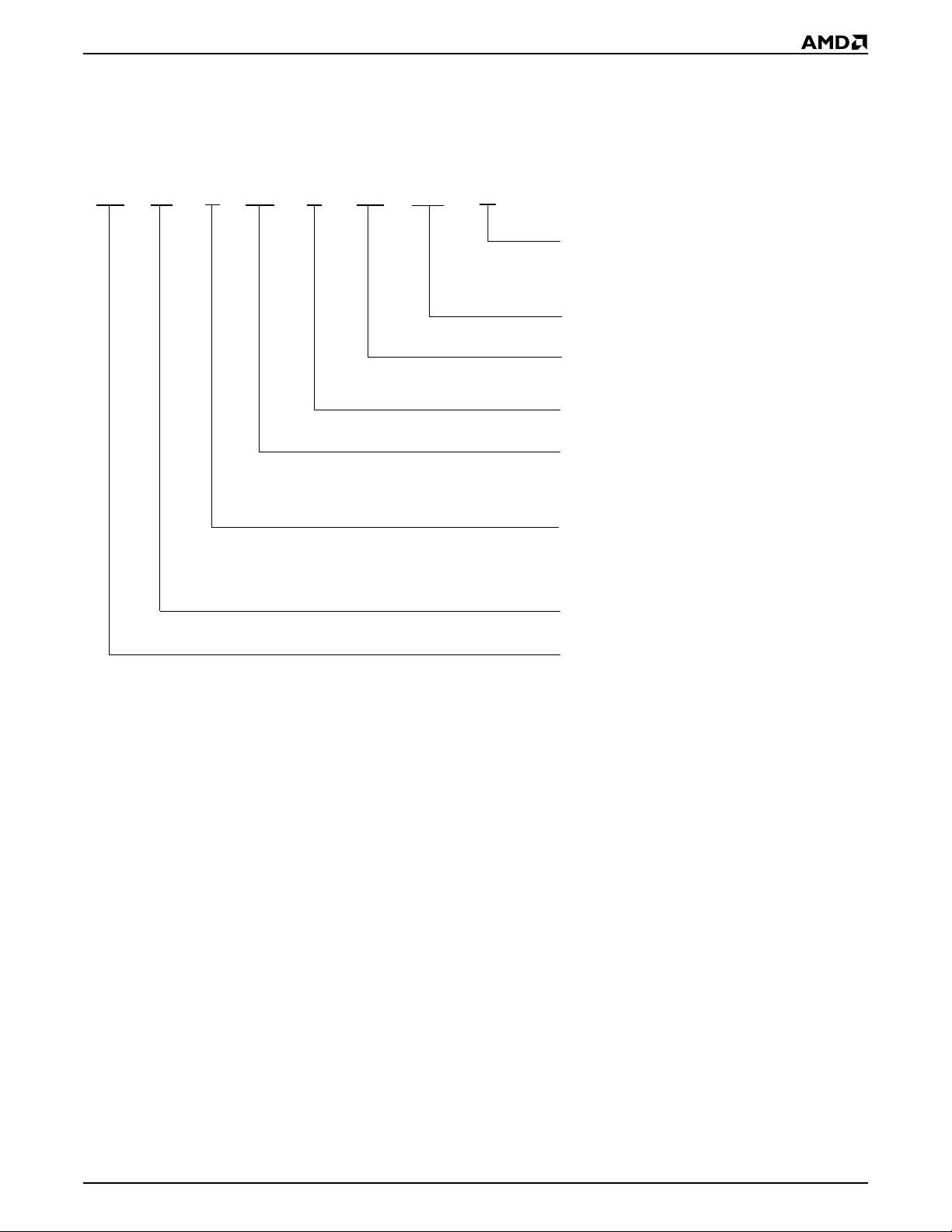

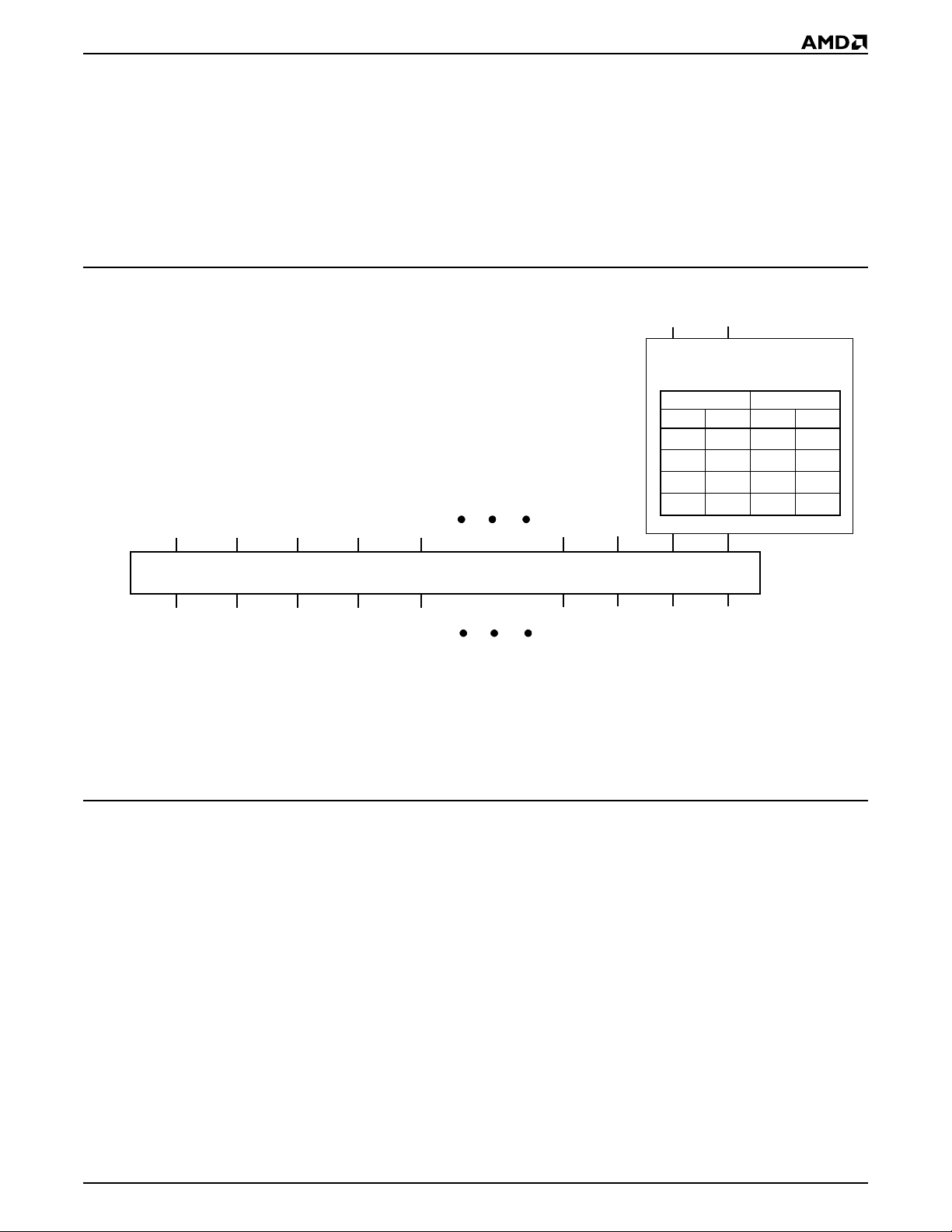

Figure 2 shows the connections betw een t he h ost and

Miniature Card. The host system address lines range

from A0–A25, whereas the Miniatur e Card address

Host Bus

A22

A21

A25

A24

A23

lines range f rom A0–A24. On the host, A0 and the

byte/word line are sent to a decoder and output to

CEL# and CEH# on the Miniature Card. These two bits

enable a single devi ce for byte accesses and two

devices for word accesses, as shown by the decoder

truth table in Figure 2. Again, the Miniature Card

address lines do not receive input from host address bit

A0. In this document, all address references are

addresses

, unless otherwise noted. T able 4 shows the

card

read/write modes for Miniature Cards.

Byte/Word

A0

Decoder

Decoder Truth Table

Input Output

A0 B/W CEL# CEH#

0000

0101

1000

A2

A1

1110

60-Pad Connector

A23*A24*

A22*

A21*

A20**

Card Bus

* Not connected

** Not connected on 2 Mbyte card

Figure 2. Host/Card Address Connections

Word-Wide Operations

The AMD Miniature Card provide the flexibility to

operate on data in a byte-wide or word-wide format. In

word-wide operations, the low bytes are controlled with

CEL#. The high bytes are controlled with CEH#. Refer to

the block diagram for more information.

Byte-Wide Operations

Byte-wide data is available for read and write operations (CEL# = 0, CEH# = 1). Even and odd bytes are

stored in separate memory devices (for example, S0

and S1) and are accessed by controlling CEL# and

CEH#. The even byte is the low order byte and the odd

byte is the high order byte of a 16-bit word.

Each memory sector or device pair must be addressed

separately for erase operations. Refer to the block

diagram for more information.

A1

CEH#CEL#A0

21138E-3

Card Detection

Each CD# (output) pin should be detected by the host

system to determine if the memory card is adequately

seated in the socket. CD# and CINS# are internally tied

to ground. If both bits are not d etected, the system

should indicate that the card must be re-inserted.

Data Protection

An optional mechanical write protect switch provides

user-initiated write protection. When this switch is acti-

WE# is internally forced high. The Flash memory

vated,

command register is disabled from accepting any write

commands. This prevents the card from responding to

any commands (for example, an Autoselect command). See Figure 3.

AmMCL00XA 9

PRELIMINARY

Write Enabled

Write Disabled

Figure 3. Write Protect Switch

21138E-1

(Card Right Side View)

In addition to card-level data protection, AMD Flash

Miniature Cards offer several device-level data protection features.

Device-Level Data Protection

AMD Flash memory devices offer protection against

accidental erasure or programming caused by spurious

system level signals that may exist during pow er transitions. During power up, each device automatically

resets the internal state machine to the read mode. The

control register architectur e allows alteration of the

memory contents only occurs after successful completion of specific multi-bus cycle command sequences.

AMD Flash memory devices also incorporates the following features to prevent inadvertent write cycles

resulting from V

tions or system noise.

Low V

Write Inhibit

CC

To avoid initiation of a write cycle during V

and power-down, the AMD memory devices in the Miniature Card lock out write cycles for V

“DC Characteristics” on page 22 for voltages). When

< V

V

CC

LKO

internal program/erase circuits are disabled, and the

device resets to the read mode. The memory devices

ignore all write s until V

power-up and power-down transi-

CC

power-up

CC

CC

< V

LKO

(see

, the command register is disabled, all

CC

> V

. The user must

LKO

ensure that the control pins are in the correct logical

state when V

CC

> V

to prevent unintentional writes.

LKO

Write Pulse “Glitch” Protection

Noise pulses of less than 5 ns (typical) on OE#, CE# ,

or WE# will neither initiate a write cycle nor change the

command registers.

Logical Inhibit

Writing is inhibited by holding any one of OE# = V

CE# = V

, or WE# = VIH. To initiate a write cycle CE#

IH

IL

and WE# must be a lo gical ze ro whil e OE# is a logical

one.

Power-Up Write Inhibit

Power-up of the device with CE# = WE# = V

will not accept command s on the rising ed ge of

= V

IH

and OE#

IL

WE#. The internal state machine is automatically reset

to the read mode on power-up.

Read Mode

Two Card Enable (CE#) pin s are available on th e

memory card. Both CE # pins must be active low f or

word-wide read accesses. Only one CE# is required for

byte-wide accesses. The CE# pins select and determine when to appl y power to the high-byte and

low-byte memory devices. The Output Enable (OE#)

controls gating accessed data from the memory device

outputs. Refer to Table 4.

The Miniature Car d automatically power s up in the

read/reset state. In this case, a command sequence is

not required to read data. Standard microprocessor

read cycles will retrieve arra y data. This default state

ensures that no spurious alteration of the memory

content occurs during the power transition. Refer to the

AC Read Characteristics and Waveforms for the specific timing parameters.

Output Disable

Data outputs from th e card are di sabled when OE # is

at a logic-high level. Und er this conditio n, outputs are

in the high-impedance state.

,

10 AmMCL00XA

PRELIMINARY

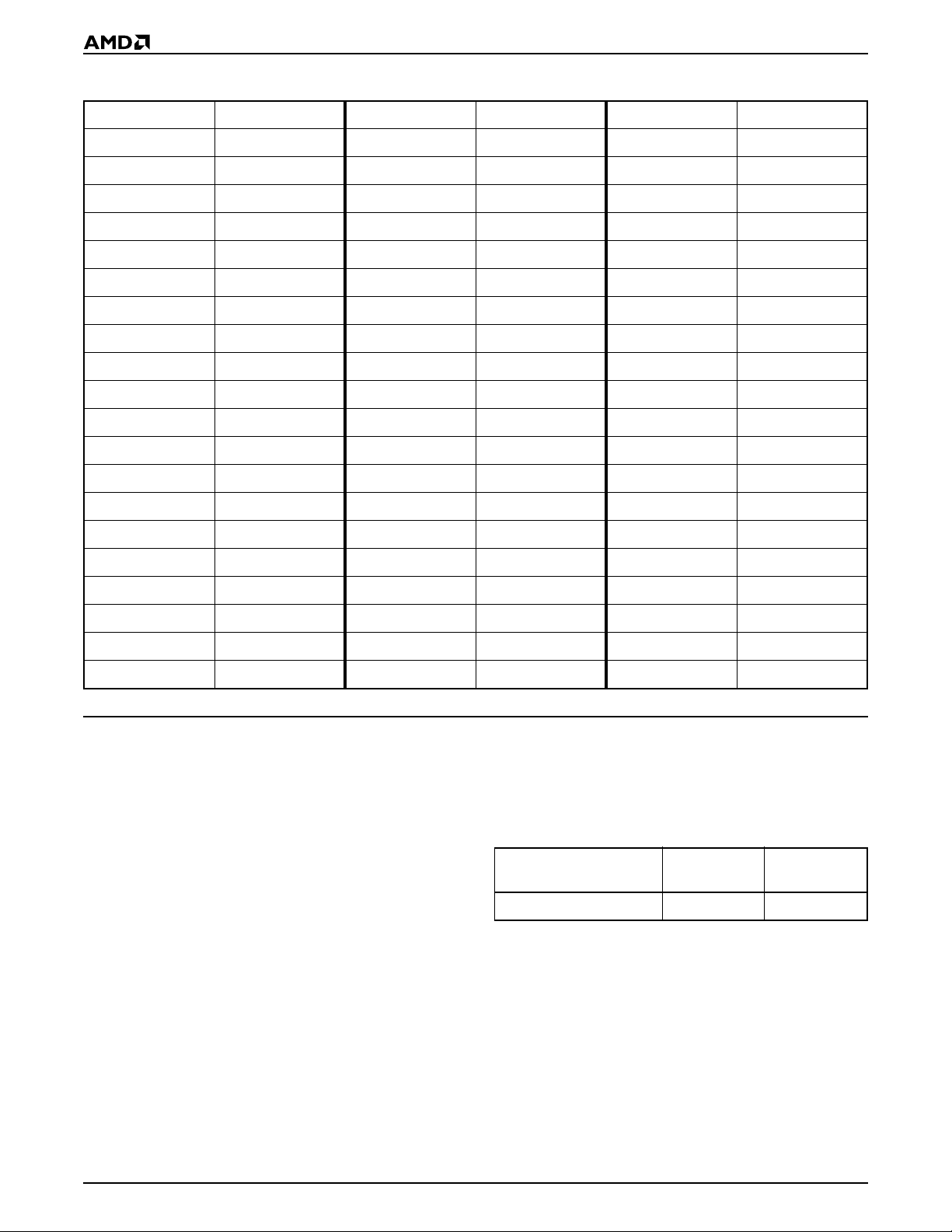

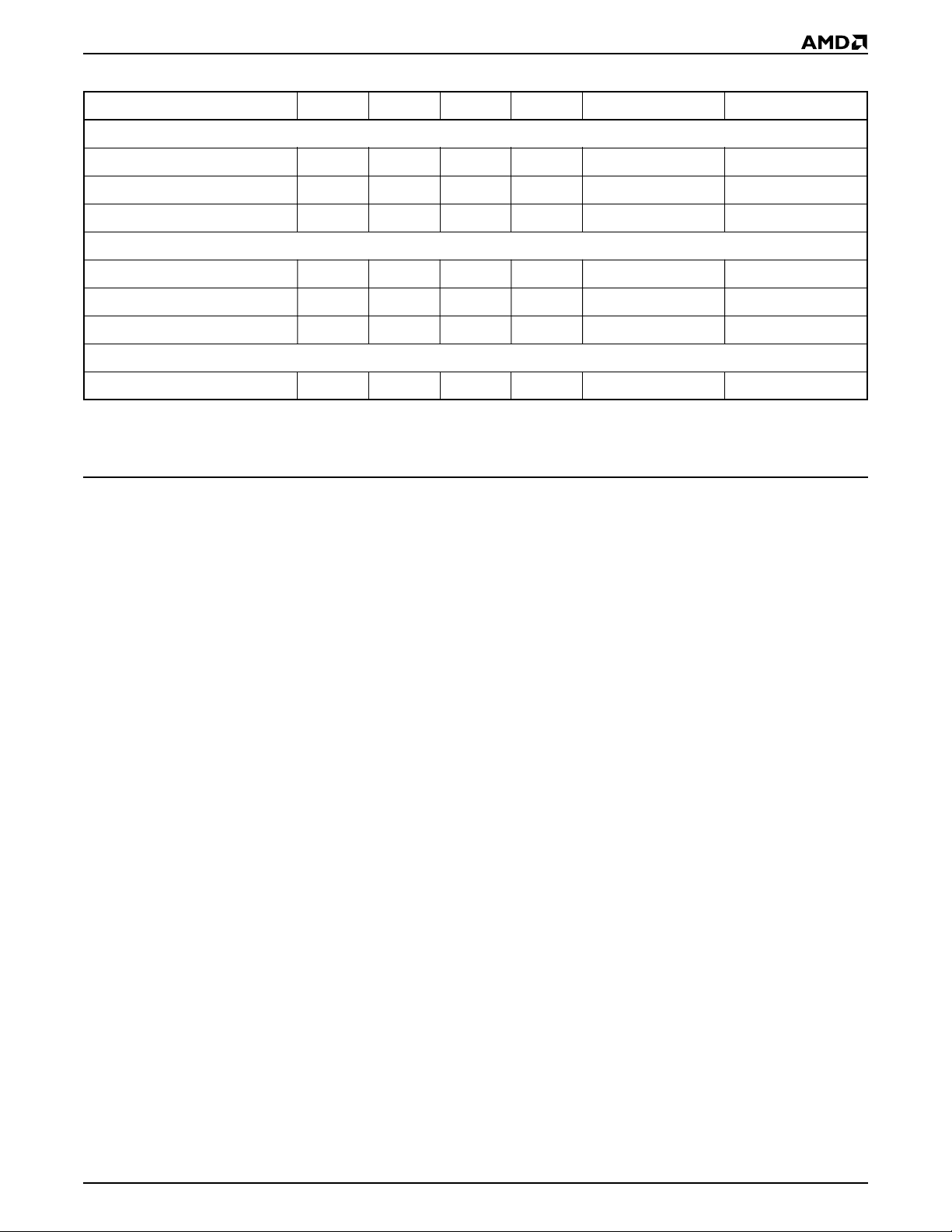

Table 4. Miniature Card Read/Write Modes

Function CEH# CEL# WE# OE# D8–D15 D0–D7

Read Mode

Word Access L L H L High Byte Data Low Byte Data

Low Byte Access H L H L High-Z Low Byte Data

High Byte Access L H H L High Byte Data Hi gh-Z

Write Mode

Word Access L L L H High Byte Data Low Byte Data

Low Byte Access H L L H High-Z Low Byte Data

High Byte Access L H L H High Byte Data Hi gh-Z

Standby Mode

Standby H H X X High-Z High-Z

Notes:

1. Unlisted access combinations are invalid and may return unexpected results.

2. X indicates a don’t care value.

Erase Operations

The AMD Flash Miniature Card is organized as an

array of individual devices. Each Am29LV081 device

contains sixteen 64 KByte sectors, for a total of 1 Mbyte

of memory space per device.

Flash technology allows any logical “1” data bit to be programmed to a log ica l “0 ”. T he on ly wa y t o r ese t bit s t o a

logical “1” is to erase that entire memory sector or

memory device. Once a memory s ector or memory

device is erased, any address location may be programmed. Two or more de vi ces m ay be er ase d co nc urrently when additional I

However, erasing more than two devices concurrently is

not typical in battery-powered applications, but may take

place during procedures such as card testing.

Erase operations can be performed in several ways:

■ Erase a single sector or multiple sectors in a device

■ Erase a sector pair

■ Erase multiple device pairs*

■ Erase the entire card*

* This operation is only feasible in solutions capable of

supplying more than the specified miniature card

supply current requirement (150mA) per system. Each

AMD Flash memory device pair can accept a

maximum of 120mA supply current.

The common memory space data contents are altered

in a similar ma nner to writing to individua l Flash

memory devices. An on-card address decoder activates the appropriate Flash device in the memory

current is supplied to the card.

CC

array. Each device internally latches address and data

during write cycles. Refer to Table 4.

Standby Mode

The AMD flash devices are designed to accommodate

low standby power consumption. In order to achieve

standby mode, the CE# line must be deselected. In

addition, while in the standby mode, data I/O pins

remain in the high impedance state independent of the

voltage level applied to the OE# input. See the DC

Characteristics section for more details on Standby

Modes.

Deselecting CE# (CE# and RE SET# = V

puts the device into the I

standby mode. If the

CC3

device is deselected during an Embedded Algorithm

operation, it continues to draw active power (I

to entering the standby mode, until the operation is

complete. When t he de vice is agai n selec ted (CE # =

), a c t i v e o p e r a t i on s occur in accordance with th e

V

IL

AC timing specifications.

Automatic Sleep Mode

Advanced power management features such as the

automatic sleep mode minimize Flash device energy

consumption. This is extremely important in battery-powered applications. The AMD memory devices

automatically enable the low-power, automatic sleep

mode when addresses remain stable for 300 ns. Automatic sleep mode is independent of the CE#, WE#, and

OE# control signals. Typical sleep mode current draw

from each device is < 1 µA. Standard address access

timings provide new data when addresses are

± 0.3 V)

CC

CC2

) prior

AmMCL00XA 11

Loading...

Loading...