AMD Advanced Micro Devices AMMC008AWP-150, AMMC008AWP-100I, AMMC004AWP-150, AMMC004AWP-100I, AMMC004AWP-100 Datasheet

...

PRELIMINARY

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you ev aluate this product. AMD reserves the right to change or dis continue work on thi s proposed

product without notice.

Publication# 20975 Rev: D Amendment/+1

Issue Date: May 1998

AmMC0XXA

2, 4, or 8 Megabyte 5.0 Volt-only Flash Miniature Card

DISTINCTIVE CHARACTERISTICS

■ 2, 4, or 8 Mbytes of addressable Flash memory

■ 5.0 Volt-only, single power supply operation

— Write and read voltage: 5.0 V ± 10%

— No additional supply current required for V

PP

■ Fast access time

— 100 or 150 ns access time

■ CMOS low power consumption

— Typical active read current:

70 mA (word mode)

— Typical active erase/write current:

100 mA (word mode)

— Typical standby current:

10 µA (8 Mbyte card)

■ High write endurance

— Guaranteed minimum 100,000 write/erase

cycles per card

— More than 1,000,000 cycles per card typical

■ Uniform sector arch itecture

— 64K byte individually useable sectors

— Erase Suspend/Resume increases system lev el

performance

— BUSY# and RESET# signals

■ Zero data retention power

— No power required to retain data

■ Available in industrial temperature grade

(–40°C to +85°C)

■ Miniature Card standard form factor

— True interchangeability

— 60-pad connector

— Supports multiple technologies

— Sonic welded stainless steel case

— PCMCIA Type II adapter available

— Selectable byte- or word-wide configuration

— Small form factor (38 mm x 33 mm x 3.5 mm)

■ 60 connection bus

— 16-bit data bus

— 25-bit address bus

— Easy system integration

— Low cost implementation

— Low cost cards

■ Consumer-friendly mechanicals

— User can easily insert and remove card, upgrade

memory , and add applications

■ Voltage level keying

— Does not allow a 5 V card to plug into a 3 V

system and vice versa

— Single power supply design

— System does not need a separate program

voltage supply; only one is necessary to read

and write

GENERAL DESCRIPTION

The Miniature Card is an expansion card that provides

a high-performance, small form factor solution for data

and file storage to the portable, handheld market,

which includes audio, digital film, wireless, and PDA

(Portable Digital Assistant) applications. The Miniature

Card provides a low cost, low pow er , high perf ormance

interface for memory cards.

Miniature cards can be easily “snapped” into the back

of an electronic system and can be readily removed

and replaced by end users. AMD’s 5 V Flash Miniature

Cards are manufactured using AMD’s industry leading

5.0 volt-only, single-power-supply Am29F080B and

Am29F017B Flash Memory devices, ensuring high reliability and excellent performance. The Miniature Card

is less than 30% of the size of a PCMCIA memory card.

Applications include digital voice recorders, pocket

PCs and intelligent organizers, smar t cellular telephones, voice and data messaging pagers, digital still

cameras and portable instrumentation equipment.

The Miniature Card specification will be defined by

PCMCIA as of October 1997. The participating association member s include maj or Flash mem ory vendors

and leading consumer electronics OEMs. The goal of

the Miniature Card specification is to promote an open,

interoperable small-f orm-f actor memory card standard.

For more information on the Miniature Card specifica-

2AmMC0XXA

PRELIMINARY

tion, visit the PCMCIA web site at http:/ /www.pccard.com.

AMD Flash Miniatur e Cards can be read in either a

byte-wide or word-wide mode, which allows for flexible

integration into v arious system platf orms. Compatibility

is assured at the hardware interface and softw are interchange specification.

Miniature Card is also designed with low-cost and

rugged handling in mind. The card contains virtually

no control logic, which keeps cost and power consumption to a minimum. The Miniature Card is packaged in a sonic welded, stainless steel case that

guarantees durability, provides good ESD protection

and ease of handling.

The Miniature Card has e x tens ive third-party support,

including socket and connector solutions, software

support from the major FTL software vendors, and

PCMCIA adapter solutions and pro g r ammer sup port.

AMD’s Mini ature Fl ash cards can be used f o r both cod e

and data stor age. Si nce f ast ra ndom access is possib le,

code can be directly executed from the card, re ducing

the amount of system RAM required. In addition. AMD’s

Flash technology offers unsurpassed endurance, data

retention and reliability, eliminating the need for

complex er ror co rrect ion and de f ect manag ement ha rdware and software. Each Flash sector provides a

minimum of 100,000 cycles, which translates into a

typical card life of one million or more cycles.

For more information, please contact your local AMD

sales office or visit our Web site at

http://www.amd.com/html/products/nvd/nvd.html.

DEFINITIONS

Table 1 lis ts the terms and definitions t hat ma y be used

in conjunction with Miniature Card specifications.

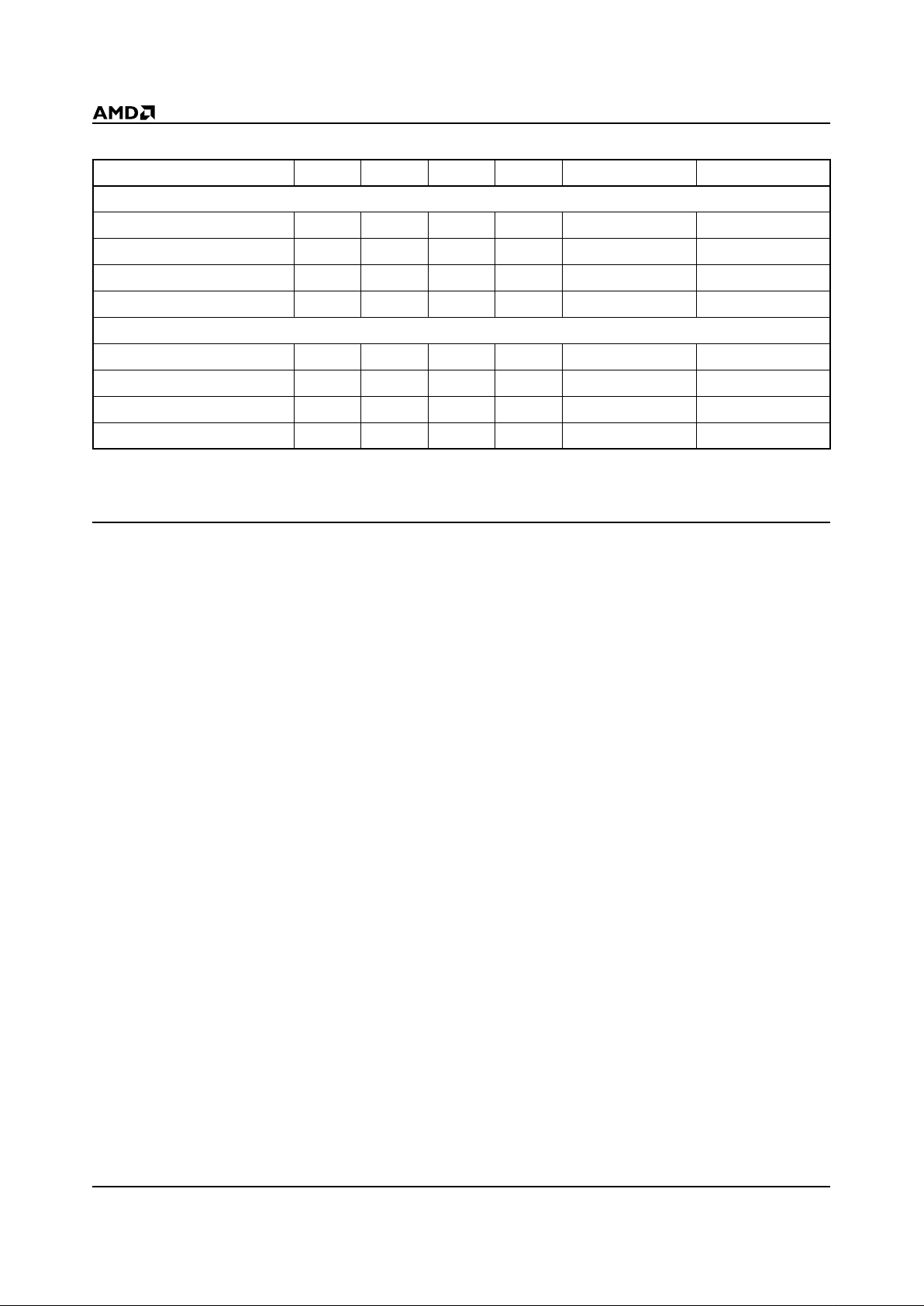

Table 1. Miniature Card Definitions

Term Meaning

AIS

Acronym for Attribute Information Structure. AIS is a Miniature Card specification for storing

Miniature Card attribute information.

ESD Acronym for Electrostatic Discharge. ESD is part of the Miniature Card physical test.

FAT

Acronym for File Allocation Table. Using an F AT is a common method for managing files in a

DOS-based system.

Flash

A type of non-volatile memory that is both readable and writeable, but requires the media to

be erased before it is rewritten.

Host Any system that incorporates a Miniature Card socket.

Insertion, Cold

User Perception:

Insertion of the Miniature Card when the host is off.

Host State:

The host would be either off or in sleep mode, no bus activity is occurring, the

host is non-operational by the user. The user inserts the Miniature Card and then presses a

button to turn the host on before the system is operational.

Insertion, Hot

User Perception:

Insertion of a Miniature Card when the host is running.

Host State:

The host would be in running mode, bus activity is occurring, the host is

operational by the user. The user inserts the card, the host recognizes it, and the host

continues to be operational. Note: Hot insertion may require buffering on the host system for

proper operation.

Insertion, Pseudo Hot

User Perception:

Insertion of a Miniature Card when the host is running.

Host State:

The host would be in running mode, bus activity is occurring, the host is

operational by the user. The user inserts the card, the host immediately powers off before the

Miniature Card makes contact with the host’s internal bus. The user would then need to press

a button to turn the host on for it to become operational.

Interface Signals Miniature Card signals that make connection through the 60-pad connector area.

JEDEC Acronym for Joint Electronic Device Engineering Council.

Miniature Card Backside

The side of the Miniature Card that contains the latching mechanism. The backside is

opposite the frontside.

Miniature Card Bottomside

The side of the Miniature Card that contains the interface signals. The bottomside is opposite

the topside.

AmMC0XXA 3

PRELIMINARY

Miniature Card Frontside

The side of the Miniature Card that contains power, insertion, ground, voltage keys, and

alignment notch. The frontside is opposite the backside.

Miniature Card Topside

The side of the Miniature Card that contains the Miniature Card label. The topside is opposite

the bottomside.

PC Card A memory or I/O card compatible with the PC Card Standard.

PC Card Adapter

The hardware that connects the Miniature Card 60 contact bus to the PC Card 68 pin bus.

This hardware can be mechanically implem ent ed by following the PC Card Type II

specification.

Power/Insertion Signals

The three signals on the frontside of the Miniature Card that provide ground, power and early

detection of insertion.

Pull-Ups Resistors used to ensure that signals do not float when no device is driving them.

Removal, Cold

User Perception:

Removal of a Miniature Card when the host is off.

Host State:

The host would either be off or in sleep mode, no bus activity is occurring, the

host is non-operational by the user. User would turn off the host, then remove the Miniature

Card and then press a button to turn the host on for it to become operational again.

Removal, Hot

User Perception:

Removal of the Miniature Card when the host is running.

Host State:

The host would be in running mode, bus activity is occurring, the host is

operational by the user. User removes the card, the host recognizes the event, and the host

continues to be operational.

Removal, Pseudo Hot

User Perception:

Removal of the Miniature Card when the host is running.

Host State:

The host would be in running mode, bus activity is occurring, the host is

operational by the user. User removes the card, the host recognizes the event, the host

immediately powers off before the Miniature Card removes contact with the host’s internal

bus. The user would then need to press a button to turn the host on for it to be operational

again.

Sector

Usually 64 Kbytes, but depends on device used in the card. In word mode, a sector is 64

KWords.

Tuple

An element of the PC Card Standard CIS that provides card attribute information, and a link

to the next tuple in a string of tuples.

User Insertable

All Miniature Cards should be inserted into the host by the user without the need for any

special tools.

User Removable

This type of Miniature Card can be removed by the user without the need for any special tools.

It contains programs and data that users may want to switch often. The use of this type of

card is similar to a floppy disk.

User Non-Removable

This type of Miniature Card must be removed by the user with a special tool. It contains

memory upgrades or boot program that users switches only when they require an upgrade.

The use of this type of card is similar to a SIMM memory expansion or boot hard disk.

XIP

Acronym for eXecute-In-Place, which refers to code that executes directly from a Miniature

Card.

Table 1. Miniature Card Definitions (Continued)

Term Meaning

4AmMC0XXA

PRELIMINARY

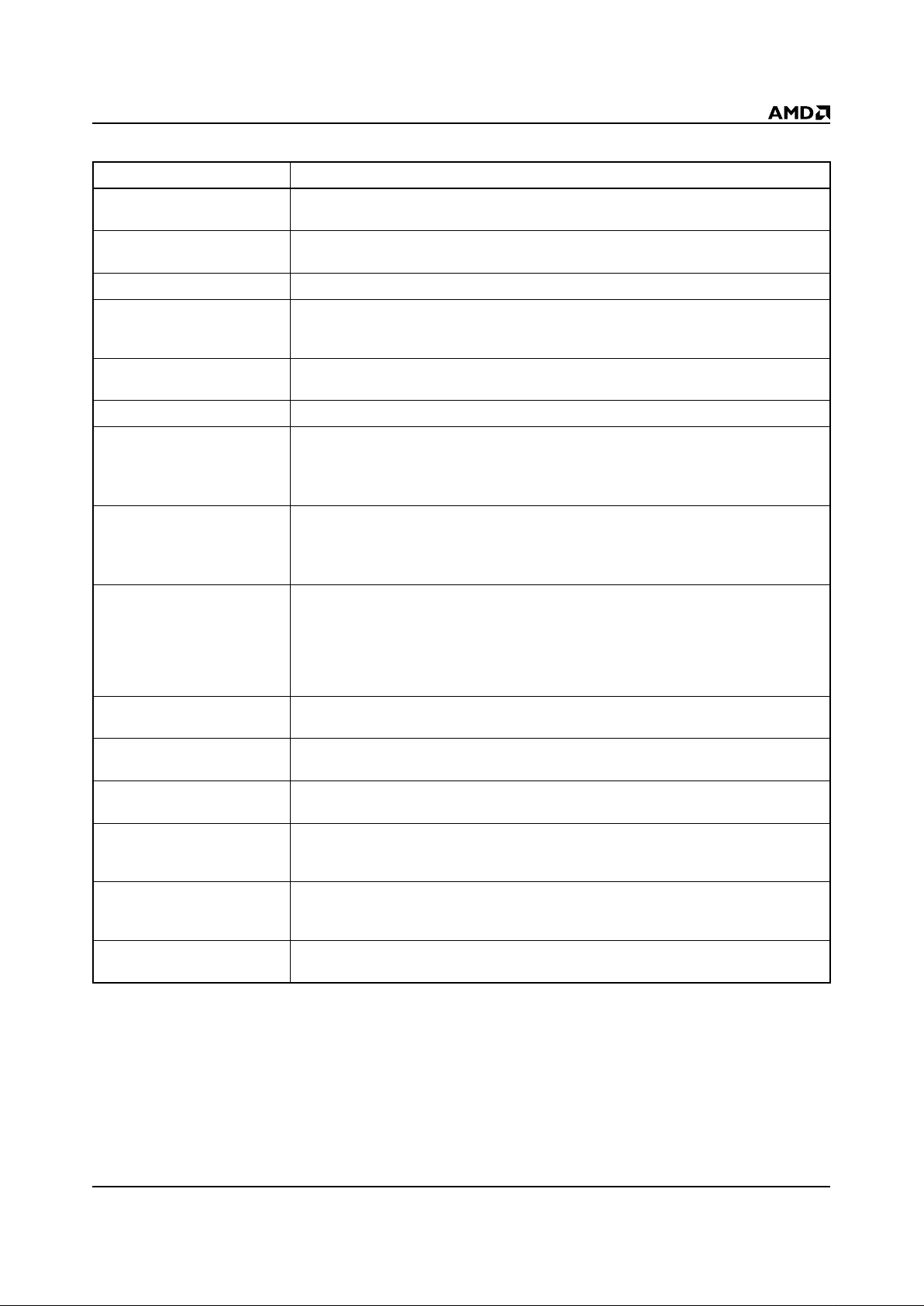

Figure 1. Miniature Card Connector (Card Bottom View)

Note: Refer to the Physical Dimensions section for more information. Also refer to the MCIF specification for detailed mechanical

information, available on the Web at http://www.mcif.org.

Table 2. AMD Flash Miniature Cards and Flash Devices

Family Part Number Density No. of Flash Devices AMD Flash Memory

AmMC002AWP 2 Mbyte 2 Am29F080B

AmMC004AWP 4 Mbyte 2 Am29F017B

AmMC008AWP 8 Mbyte 4 Am29F017B

Write Protect Swit ch (opt i onal)

Pad 60 Pad 31

Pad 30 Pad 1

V

CC

CINS# GND

3V/5V

Key

Alignment

Notch

20975D-1

AmMC0XXA 5

PRELIMINARY

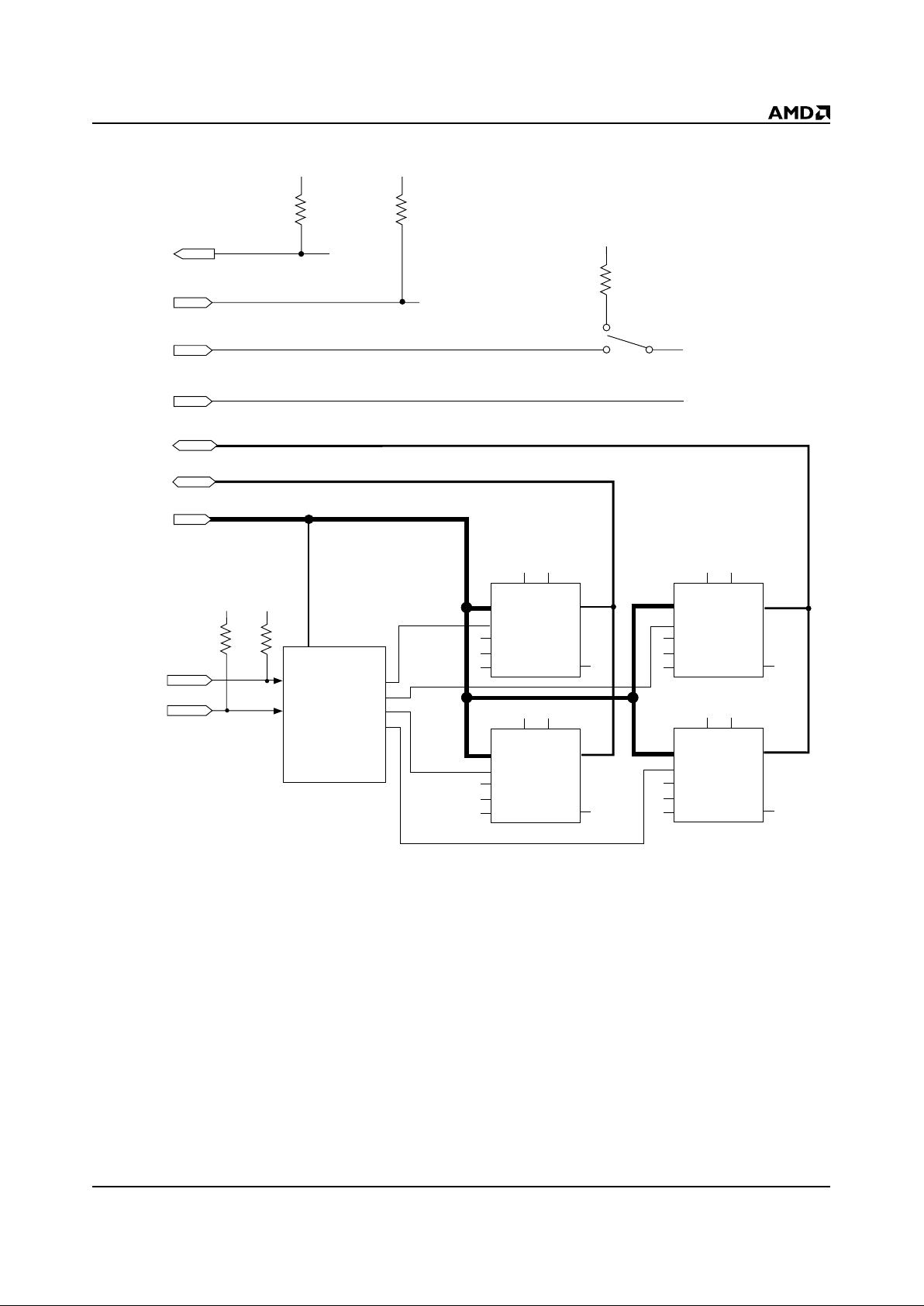

BLOCK DIAGRAM

* Decoder used on 8 Mbyte card only. Not used on 2 and 4 Mbyte cards.

** 2 Mbyte card: Two Am29F080B devices, S0 and S1

4 Mbyte card: Two Am29F017B devices, S0 and S1

8 Mbyte card: Four Am29F017B devices, S0...S3

*** A0–A19 on 2 Mbyte card; A0–A20 on 4 and 8 Mbyte cards.

Note: On the 2 Mbyte card, A20–A24 are not connected. On the 4 Mbyte cards, A21–A24 are not connected. On the 8 Mbyte

cards, A22-A24 are not connected. Connections not shown in this diagram are not connected internally.

OE#

BUSY#

RY/BY#

A0–A24

Decoder*

CEL#

100K

100K

CEH#

WE#

WE# to all Flash devices

Write Protect

Switch

CEL0#

CEH0#

CEL1#

CEH1#

A21

V

CC

10K

V

CCVCC

OE# to all Flash devices

D0–D7

D8–D15

RESET#

RESET# to all Flash devices

A0-A20***

WE#

OE#

D8-D15

V

SSVCC

RESET#

RY/BY#

S1**

A0-A20***

CE#

WE#

OE#

D0-D7

V

SSVCC

RESET#

RY/BY#

S2**

A0-A20***

CE#

WE#

OE#

D8-D15

V

SSVCC

RESET#

RY/BY#

S3**

A0-A20***

CE#

WE#

OE#

D0-D7

V

SSVCC

RESET#

RY/BY#

S0**

V

CC

10K

V

CC

10K

20975D-2

6AmMC0XXA

PRELIMINARY

MINIATURE CARD PAD ASSIGNMENTS

A0–A24

Address A0 to A24 are the address bus lines that can

address up to 32 Mwords (64 Mbytes). The address

lines are word addressed. The Miniature Card specification does not require the Miniature Card to decode

the upper address lines. A 2 Mbyte Miniature Card that

does not decode the upper address lines would repeat

its address space every 2 Mbytes. Address 0h would

access the same physical location as 200000h,

400000h, 600000h, e tc. On the 2 Mbyte cards, A20 –

A24 are not connected. On the 4 Mbyte cards, A21–

A24 are not connected. On the 8 Mbyte cards, A22–

A24 are not connected.

D0–D15

Data lines D0 through D15 constitute the data bus . The

data bus is composed of two bytes; the low byte is D0–

D7 and the high byte is D8–D15. These lines are

tristated when OE# is high.

OE#

OE# indicates to the card that the current bus cycle is

a read cycle. The output enable access time (t

OE

) is the

delay from the falling edge of OE# to valid data at the

output pins (assuming the addresses h a ve been stable

for at least t

ACC

– tOE time).

WE#

WE# indicates to the card that the current bus cycle is a

write cycle. The fall ing edge of WE# latches addr ess in f or mation and the rising edge latches data/command information.

VS1#

Voltage Sense 1 signal. T his signal is left open or

not connected.

VS2#

Voltage Sense 2 signal. T his signal is left open or

not connected.

CEL#

CEL# enables the low byte of t he data b us (D0 –D7) on

the card.

CEH#

CEH# enables the high byte of the data bus (D8–D15)

on the card.

RESET#

RESET# controls card initialization. When RESET#

transitions from a low state to a high state, the Miniature Card resets to the Read state.

BUSY#

BUSY# is a signal generated b y t he card to indic ate the

status of operations w ithin the Miniature Card. When

BUSY# is high, the Miniature Card is ready to accept

the next command from the host. When BUSY# is low,

the Miniature Card is busy and unable to accept most

data operations from the host. In Flash Miniature Cards

the BUSY# signal is tied to th e components’ RY/BY#

signal.

CD#

CD# is a grounded interface signal. After a Miniature

Card has been inserted, CD# will be forced low. The

card detect signal is located in the center of the second

row of interface signals, and should be one of the last

interface signals to connect t o the host . Do not c onfuse

CD# with CINS#.

CINS#

CINS# is a grounded signal on the front of th e Miniature

Card that is used for early detection of a card insertion.

CINS# makes contact on the host when the front of the

card is inserted into the socket, before the interface

signals connect.

BS8#

The BS8# (Bus size 8) signal indicates t o the Mini ature

Card that the host has an 8-bit bus. AMD Flash Miniature Cards ignore this signal. An 8-bit host must

connect its D0–D7 data lines to D8–D15 on the Miniature Card to retrieve the upper (odd) byte.

GND

Ground

V

CC

Vcc is used to supply power to the card.

NC

No connect

RFU

Reserved for future use

AmMC0XXA 7

PRELIMINARY

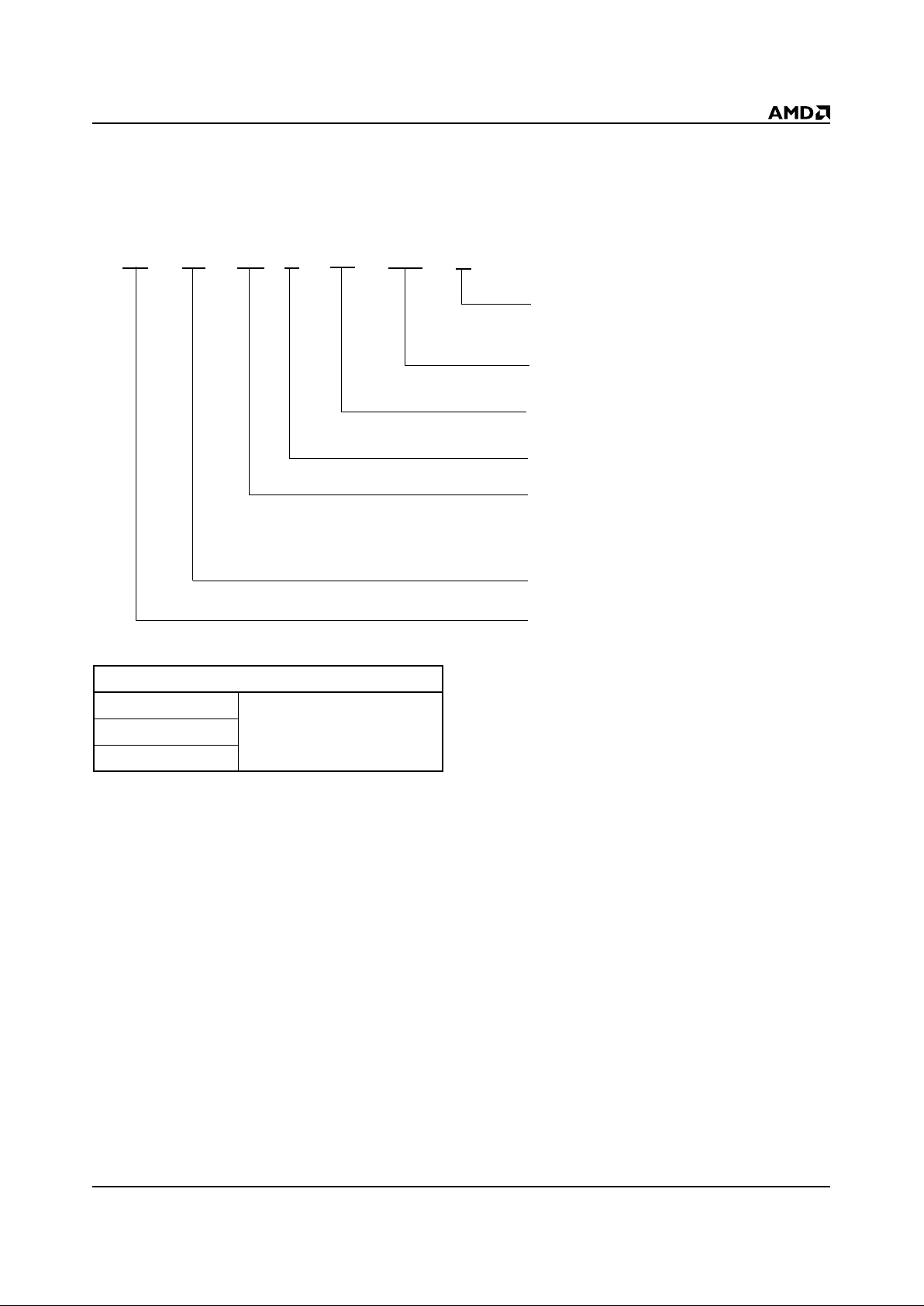

ORDERING INFORMATION

Standard Pr od ucts

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed

by a combination of the following:

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales

office to confirm availability of specific valid combinations and

to check on newly released combinations.

AM MC 008

SPEED OPTION

See Valid Combinations below

MINIATURE CARD

MEMORY CARD DENSITY

002 = 2 Megabyte Card

004 = 4 Megabyte Card

008 = 8 Megabyte Card

AMD

A

REVISION LEVEL

-100 I

TEMPERATURE RANGE

Blank = Commerc ial (0°C to +70°C)

I=Industrial (–40°C to +85°C)

WP

WRITE PROTECT SWITCH OPTION

WP = Switch installed

Valid Combinations

AmMC002AWP

-100, -100I, -150AmMC004AWP

AmMC008AWP

8AmMC0XXA

PRELIMINARY

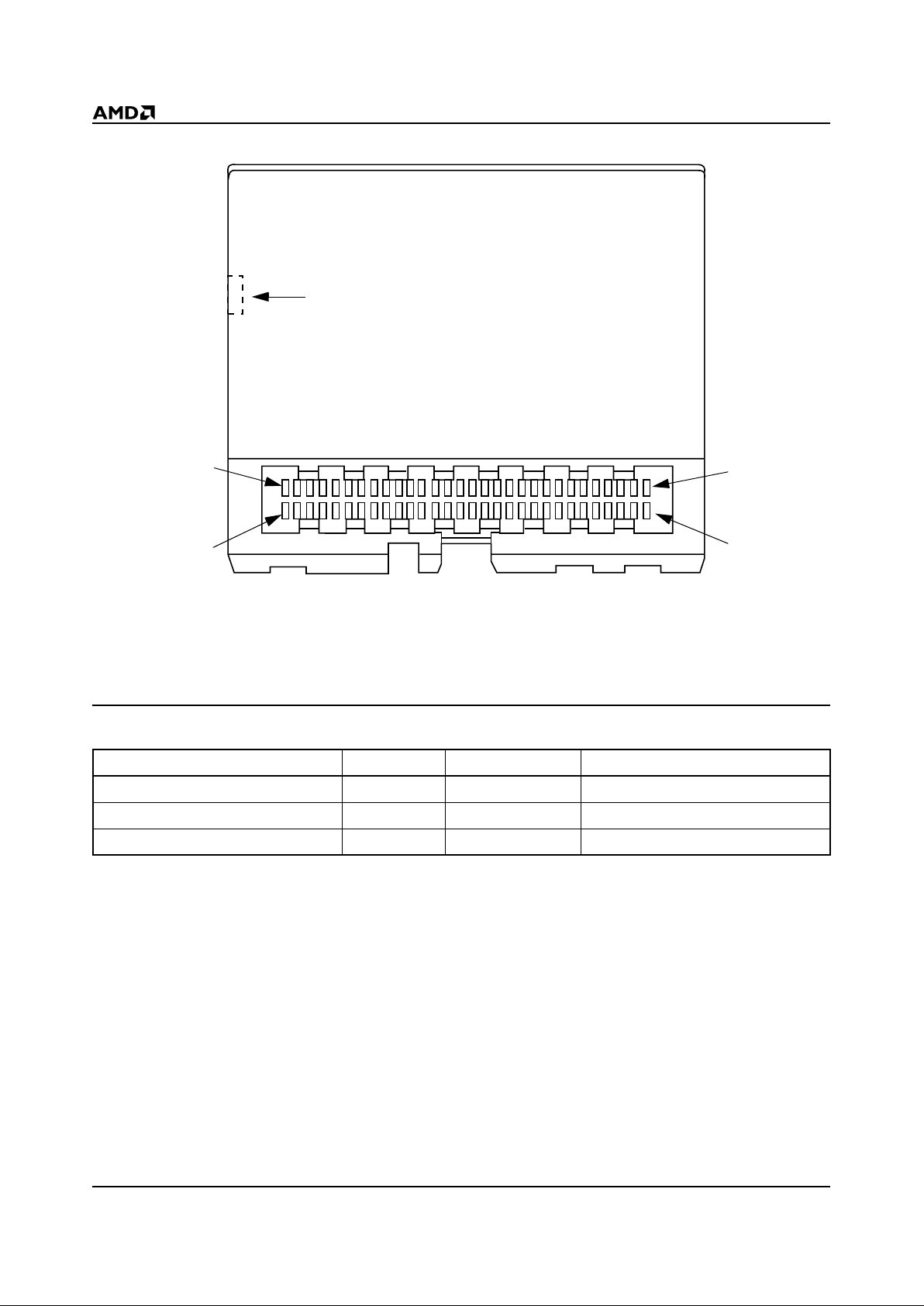

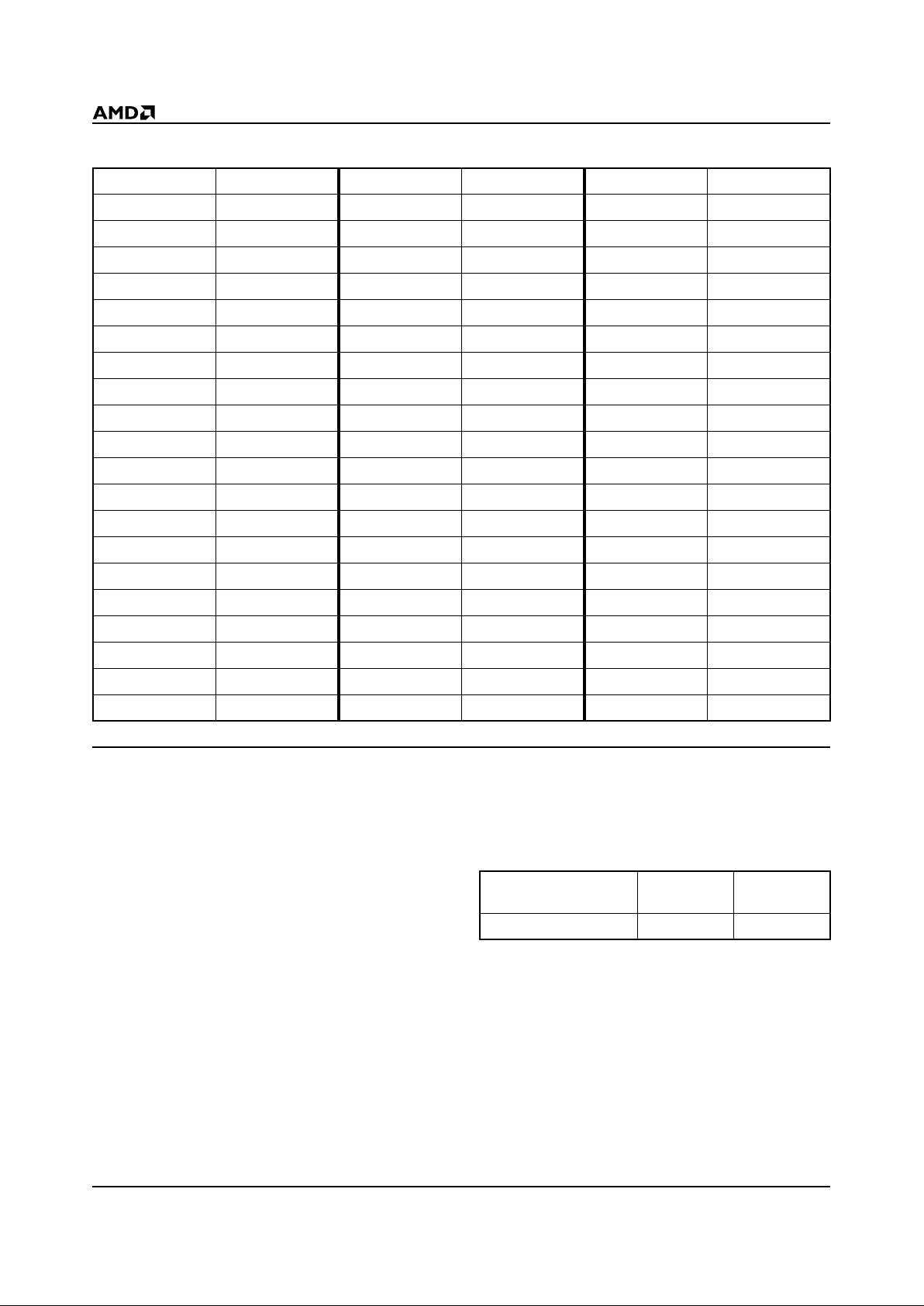

INTERFACE SIGNAL ASSIGNMENTS

Note: NC = No Connect; RFU = Reserved for Future Use.

FLASH MINIATURE CARD OPERATIONS

Voltage Sensing

AMD Miniature Cards provide two voltage sense

signals for hosts that support multiple voltages. The

multivoltage hos t can sense the voltage level of the

Miniature Card and power up th e card at that voltag e.

See Table 3 for a description of the voltage sense

signals.

In addition to the voltage sense pins, there are also

mechanical voltage keys on the Miniature Card that

ensure the card can only be inserted into host systems

that can supply the proper voltage levels to the card.

Refer to Section 4.1.2 in the Miniature Card specification for more information on mechanical keying.

Table 3. Voltage Sense Signals

Pad Number Signal Name Pad Number Signal Name Pad Number Signal Name

1A1821D1241A4

2 A16 22 D10 42 CEL#

3 A14 23 D9 43 A1

4NC24D044NC

5CEH#25 D2 45 NC

6 A11 26 D4 46 CD#

7 A9 27 RFU 47 A21

8 A8 28 D7 48 BUSY#

9A629NC49WE#

10 A5 30 NC 50 D14

11 A3 31 A19 51 RFU

12 A2 32 A17 52 D11

13 A0 33 A15 53 VS2#

14 NC 34 A13 54 D8

15 A24 35 A12 55 D1

16 A23 36 RESET# 56 D3

17 A22 37 A10 57 D5

18 OE# 38 VS1# 58 D6

19 D15 39 A7 59 RFU

20 D13 40 BS8# 60 A20

Miniature Card

Power-Up Voltage VS1# VS2#

5 Volt-only Open Open

AmMC0XXA 9

PRELIMINARY

Data Accesses

The Miniature Card has a 16-bit data bus that can

accommodate word or byte acces ses. By individually

asserting CEL# and CEH#, a host can access either

byte. However, byte swapping (moving the high byte

data to the low byte) is not supported.

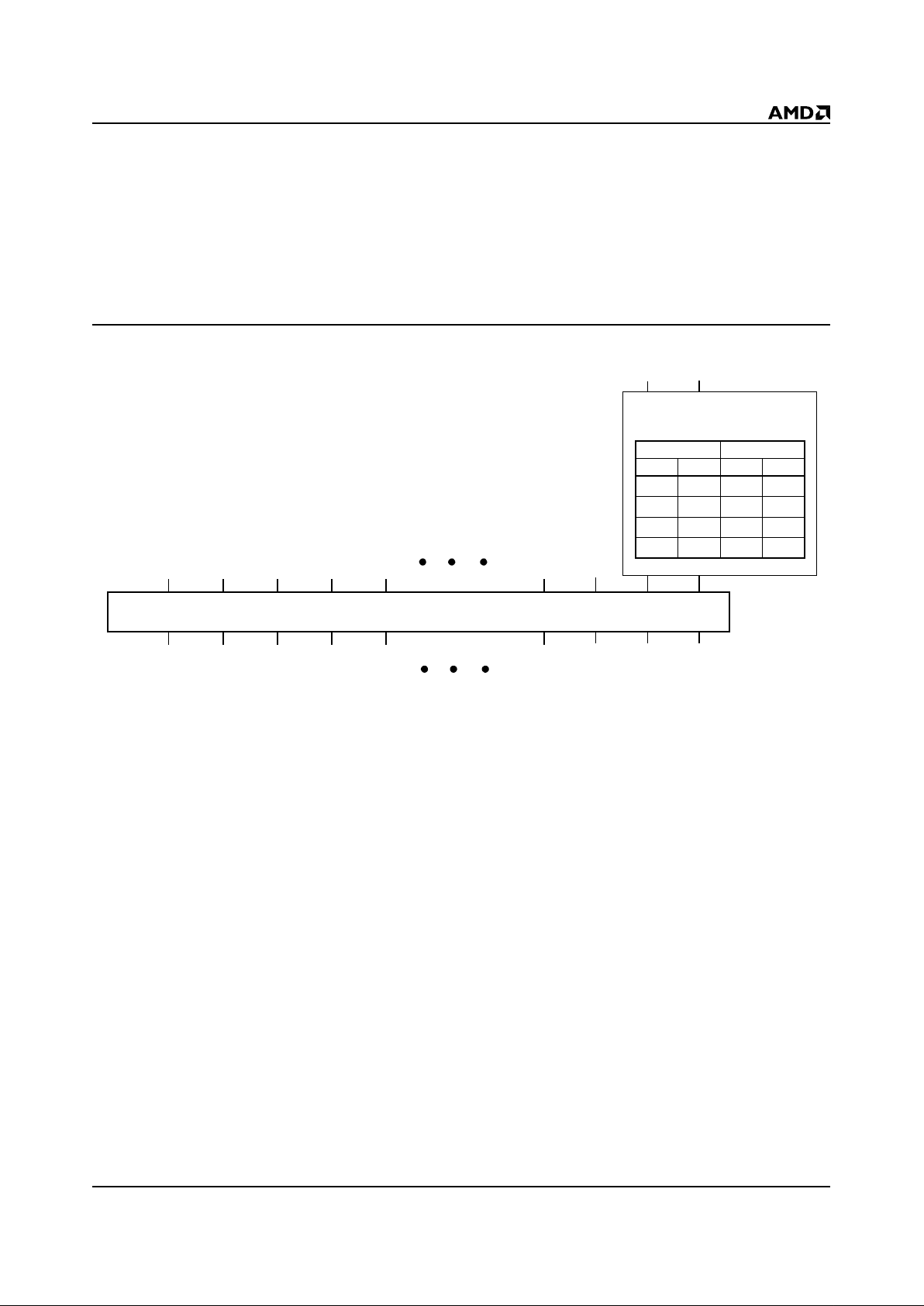

Figure 2 shows the connections between the host and

Miniature Card. The host system address lines range

from A0-A25, whereas the Miniature C ard address

lines range from A0–A24. On the host, A0 and the

byte/word line are sent to a decoder and ou tput to

CEL# and CEH# on the Miniature Card. These two bits

enable a single device for byte accesses and two

devices for word accesses, as shown by the decoder

truth table in Figure 2. Again, the Miniature Card

address lines do not receive input from host addre ss bit

A0. In this document, all address references are

card

addresses

, unless otherwise noted. Table 4 shows the

read/write modes for Miniature Cards.

* Not connected on 2 Mbyte card

** Not connected on 2 and 4 Mbyte card

*** Not connected

Figure 2. Host/Card Address Connections

Host

Byte/Word

A0

A1A25

Card CEH#CEL#A0

A24

A23***A24***

A23

A22***

A22

A21**

60-Pad Connector

A2

A1

Decoder

Decoder Truth Table

Input Output

A0 B/W CEL CEH#

0000

0101

1000

1110

20975D-3

Host Bus

Card Bus

A21

A20*

10 AmMC0XXA

PRELIMINARY

Table 4. Miniature Card Read/Write Modes

Notes:

1. Unlisted access combinations are invalid and may return unexpected results.

2. X indicates a Don’t Care value.

Erase Operations

The AMD Flash Miniature Card is organized as an array

of individual devices. On the 2 Mbyte Miniature Card,

each Am29F080B device contains sixteen 64 Kbyte sectors, for a total of 1 Mbyte of memory space per device.

On 4 and 8 Mbyte Miniature Cards, each Am29F017B

device contains thirty-two 64 Kbyte sectors, for a total of

2 Mbytes of memory space per device.

Flash technology allows any logical “1” data bit to be programmed to a logical “0”. The only way to reset bits to a

logical “1” is to erase that entire memor y sector or

memory device. Once a memory sector or memory

device is erased, any address location may be programmed. Two or more devices may be erased concurrently when additional I

CC

current is supplied to the card.

However, erasing more than two de vices concurrently is

not typical in battery-powered applications, but may take

place during procedures such as card testing.

Since erase commands operate on entire sectors or

devices, the host should track the affected memory

addresses; for example, by determining the sector size

and device size and calculating the corresponding

addresses.

Erase operations can be performed in several ways:

■ Erase a single sector or mult iple sectors in a de v ice

■ Erase a sector pair

■ Erase multiple device pairs *

■ Erase the entire card *

* This operation is only feasible in solutions capable of

supplying more tha n the specified miniature car d

supply current requirement (150 mA) per system. Each

AMD Flash memory device pair will require a

maximum of 120 mA supply current.

The common memory space data contents are altered

in a similar manner as writing to individual Flash memory

devices. An on-card address decoder activates the

appropriate Flash device in the memory array. Each

device internally latches addre ss and data during write

cycles. Refer to Table 4.

Word-Wide Operations

The AMD Miniature Card provide the flexibility to operate

on data in a byte-wide or word-wide format. In word-wide

operations, the low bytes are controlled with CEL#. The

high bytes are controlled with CEH# . Refer to the block

diagram for more information.

Byte-Wide Operations

Byte-wide data is available for read and write operations (CEL# = 0, CEH# = 1). Even and odd bytes are

stored in separate memory devices (for example, S0

and S1) and are accessed by controlling CEL# and

CEH#. The even b yt e is t he lo w order byte and the odd

byte is the high order byte of a 16-bit word.

Each memory sector or device pair must be addressed

separately for erase operations. Refer to the block

diagram for more information.

Card Detection

Each CD# (output) pin should be detected by the host

system to determine if the memory card is adequately

seated in the socket. CD# and CINS# are internally tied

to ground. If both bits are not de tected, the system

should indicate that the card must be re-inserted.

Function CEH# CEL# WE# OE# D8–D15 D0–D7

Read Mode

Standby H H X X High-Z High-Z

Word Access L L H L High Byte Data Low Byte Data

Low Byte Access H L H L High-Z Low Byte Data

High Byte Access L H H L High Byte Data High-Z

Write Mode

Standby H H X X High-Z High-Z

Word Access L L L H High Byte Data Low Byte Data

Low Byte Access H L L H High-Z Low Byte Data

High Byte Access L H L H High Byte Data High-Z

AmMC0XXA 11

PRELIMINARY

Data Protection

An optional mechanical write protect switch provides

user-initiated write protection. When this switch is activated, WE

# is internally forced high. The Flash memory

command register is disabled from accepting any write

commands. This prevents the card from responding to

any commands (for e xample, an Aut oselect command).

See Figure 3.

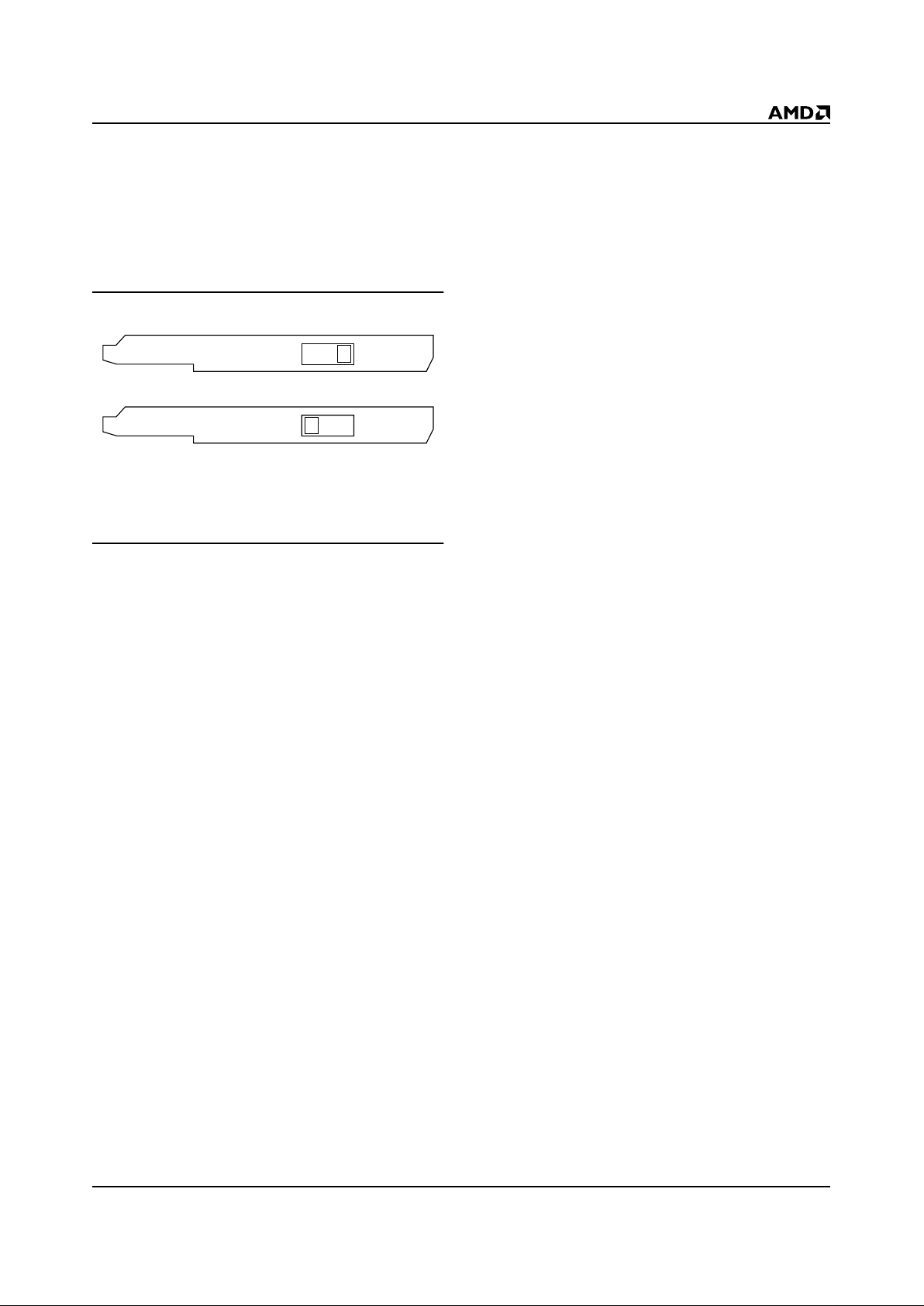

Figure 3. Write Protect Switch

(Card Right Side View)

In addition to card-level data protection, AMD Flash

Miniature Cards offer several device-level data protection features.

Device-Level Data Protection

AMD Flash memory devices offer protection against

accidental erasure or programming caused by spurious

system level signals that may e xist during power tr ansitions. During power up, each device automatically

resets the internal state machine to the read mode. The

control register architecture allows alteration of the

memory contents only occurs after successful completion of specific multi-bus cycle command sequences.

AMD Flash memory devices also incorporate the following features to prevent inadvertent write cycles

resulting from V

CC

power-up and power-down

transitions or system noise.

Low V

CC

Write Inhibit

To avoid initiation of a write cycle during V

CC

powerup and power-down, the AMD memory devices in

the Miniature Card lock out write cycles for V

CC

<

V

LKO

(see “DC Characteristics ” o n page 25 for volt-

ages). When V

CC

< V

LKO

, the command register is

disabled, all internal program/erase circuits are disabled, and the device resets to the read mode.

These memory devices ignore all w r i tes u ntil V

CC

>

V

LKO

. The user must ensure that the control pins

are in the correct logical state wh en V

CC

> V

LKO

to

prevent unintentional writes.

Write Pulse “Glitch” Protection

Noise pulses of less than 5 ns (typical) on OE#, CE#,

or WE# will neither initiate a write cycle nor change the

command registers.

Logical Inhibit

Writing is inhibited by holding any one of OE# = V

IL

,

CE# = V

IH

, or WE# = VIH. To initiate a write cycle CE#

and WE# must be a logical zero while OE# is a logical

one.

Power-Up Write Inhibit

Pow er-up of the devic e with CE# = WE# = V

IL

and OE#

= V

IH

will not accept commands on the rising edge of

WE#. The internal state machine is automatically reset

to the read mode on power-up.

Read Mode

Two Card Enable (CE#) pins are available on the

memory card. Both CE# pins must be active low for

word-wide read accesses. Only one CE# is required for

byte-wide accesses. The CE# pins select and determine when to apply power to the high-byte and lowbyte memory devices. The Output Enable (OE#) controls gating accessed data from the memor y device

outputs.

The Miniature card au tomatically powers up in the

read/reset state. In this case, a command sequence is

not required to r ead data. Standard mic roprocessor

read cycles will retrieve array data. This default value

ensures that no spurio us alteration of the memory

content occurs during the power transition. Ref er to the

AC Read Characteristics and Waveforms for the specific timing parameters.

Output Disable

Data outputs from the card are disabled when OE# is

at a logic-high lev el. Under this condition, outputs are in

the high-impedance state.

Standby Operations

Byte-wide read accesses only require half of the

read/write output buffer (x16) to be active. In addition,

only one memory device is active within either the high

order or low order bank. Activation of the appropriate

half of the output buff er is controll ed by the combination

of both CE# pins. The CE# pins also control power to

the high and low-order banks of memory. Outputs of

the memory bank not selected are plac ed in the high

impedance state. The individual memory device is activated by the address decoders. The other memory

devices operate in standby. An active memory device

continues to draw power until completion of a write or

erase operation if the card is de-selected in t he process

of one of these operations.

Write Enabled

Write Disabled

20975D-4

12 AmMC0XXA

PRELIMINARY

Autoselect Operation

A host system or e xternal card re ader/writer c an determine the on-card manufacturer and device I.D. codes.

Codes are available after writing the 90h command to

the command register of a memory device, as sho wn in

Tables 5 through

10. When the autoselect command is

issued to card address 00000h, the Miniature Card

returns the manufacturer I.D. If the autoselect

command is issued to card address 00001h, the Miniature Card provides the device I.D.

To terminate the Auto Select operation, the

Read/Reset command sequence must be written to the

same device. The Autoselect command operates only

if the card is not write protected.

Sector Group Protection

Sector group protection can be used to permanently

disable program and erase oper ation s in any combination of sector groups on t he Flash memory components

used in AMD Miniature Cards. Each sector group consists of four adjacent sectors within each device. The

pattern begins at SA0: SA0–3, SA4–7, SA8–11, and so

on. This protection must be performed prior to manufacturing the Miniature Cards. None of the sector

groups are protected on the standard Miniature Card

product offerings.

The host system must compensate for these protec ted

sector groups by determining their locations, then

ignoring those locations for reading and writing data. To

determine whether a sector group is protected, the

system would write the first three cycles of the Autoselect command, then on the fourth cycle, read at the

address (SA)02h, where SA is the sector address (see

Tables 11 and 12) within an individual device. A protected sector group produces “01h”, and an unprotected sector group produces “00h”.

Write Operations

Write and erase operations are valid only when VCC is

above 4.5 V. Thi s activates the state machine of a n

addressed memory device. The command register is a

latch which saves address, commands, and data information used by the state machine and memory array.

When Write Ena ble (WE#) and appropriate CE#

signals are at a logi c-level low, and Output Enable

(OE#) is at a logic-high, the comman d register is

enabled for write operations. The falling edge of WE#

latches address information and the rising edge latc hes

data/command information.

Write or erase operations are performed by writing

appropriate data patterns to the com mand register of

accessed Flash memory devices.

The byte-wide commands are defined in Tables 6, 7,

9,

and 10; word-wide commands are defined in Tables 5

and 8. Note that the Erase Suspend (B0h) and Erase

Resume (30h) commands are valid only while the

Sector Erase operation is in progress.

Loading...

Loading...