AMD Advanced Micro Devices AMD-K6-300AFR, AMD-K6-266AFR, AMD-K6-233AFR, AMD-K6-200AFR, AMD-K6-233ANR Datasheet

...

Preliminary Information

AMD-K6

Processor

Data Sheet

®

Preliminary Information

© 1998 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. (“AMD”) reserves the right to make changes in its

products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of

publication, but AMD makes no representations or warranties with respect to the

accuracy or completeness of the contents of this publication or the information

contained herein, and reserves the right to make changes at any time, without notice.

AMD disclaims responsibility for any consequences resulting from the use of the

information included in this publication.

This publication neither states nor implies any representations or warranties of any

kind, including but not limited to, any implied warranty of merchantability or fitness

for a particular purpose. AMD products are not authorized for use as critical

components in life support devices or systems without AMD’s written approval. AMD

assumes no liability whatsoever for claims associated with the sale or use (including

the use of engineering samples) of AMD products, except as provided in AMD’s Terms

and Conditions of Sale for such products.

Trademarks

AMD, the AMD logo, and combinations thereof, K86, AMD-K5, and the AMD-K6 logo are trademarks, and RISC86

and AMD-K6 are registered trademarks of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks, and Windows NT is a trademark of Microsoft Corporation.

Netware is a registered trademark of Novell, Inc.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

The TAP State Diagram is reprinted from IEEE Std 1149.1-1990 “IEEE Standard Test Access Port and Boundary-Scan

Architecture,” Copyright © 1990 by the Institute of Electrical and Electronics Engineers, Inc. The IEEE disclaims

any responsibility or liability resulting from the placement and use in the described manner. Information is reprinted

with the permission of the IEEE.

Other product names used in this publication are for identification purposes only and may be trademarks of their

respective companies.

Contents iii

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xvii

About This Data Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Part One

AMD-K6® Processor Family 3

1 AMD-K6® Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Internal Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2 AMD-K6

®

Processor Microarchitecture Overview . . . . . . . . . 7

Enhanced RISC86

®

Microarchitecture . . . . . . . . . . . . . . . . . . . 8

2.3 Cache, Instruction Prefetch, and Predecode Bits . . . . . . . . . 11

Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Prefetching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Predecode Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.4 Instruction Fetch and Decode . . . . . . . . . . . . . . . . . . . . . . . . . 13

Instruction Fetch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Instruction Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.5 Centralized Scheduler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.6 Execution Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.7 Branch-Prediction Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Branch History Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Branch Target Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Return Address Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Branch Execution Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3 Software Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

General-Purpose Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Integer Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Segment Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Segment Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Instruction Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Floating-Point Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Floating-Point Register Data Types. . . . . . . . . . . . . . . . . . . . . 28

MMX™ Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

EFLAGS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Debug Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Model-Specific Registers (MSR) . . . . . . . . . . . . . . . . . . . . . . . 37

iv Contents

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

Memory Management Registers . . . . . . . . . . . . . . . . . . . . . . .39

Task State Segment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Descriptors and Gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Exceptions and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.2 Instructions Supported by the AMD-K6 Processor . . . . . . . . 49

4 Logic Symbol Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.1 A20M# (Address Bit 20 Mask) . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.2 A[31:3] (Address Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.3 ADS# (Address Strobe) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.4 ADSC# (Address Strobe Copy) . . . . . . . . . . . . . . . . . . . . . . . .81

5.5 AHOLD (Address Hold) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.6 AP (Address Parity) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.7 APCHK# (Address Parity Check) . . . . . . . . . . . . . . . . . . . . . . 84

5.8 BE[7:0]# (Byte Enables) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.9 BF[2:0] (Bus Frequency) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

5.10 BOFF# (Backoff) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.11 BRDY# (Burst Ready) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.12 BRDYC# (Burst Ready Copy) . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.13 BREQ (Bus Request) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.14 CACHE# (Cacheable Access) . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.15 CLK (Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.16 D/C# (Data/Code) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.17 D[63:0] (Data Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.18 DP[7:0] (Data Parity) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.19 EADS# (External Address Strobe) . . . . . . . . . . . . . . . . . . . . . 94

5.20 EWBE# (External Write Buffer Empty) . . . . . . . . . . . . . . . . . 95

5.21 FERR# (Floating-Point Error) . . . . . . . . . . . . . . . . . . . . . . . . 96

5.22 FLUSH# (Cache Flush) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.23 HIT# (Inquire Cycle Hit) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.24 HITM# (Inquire Cycle Hit To Modified Line) . . . . . . . . . . . . 98

5.25 HLDA (Hold Acknowledge) . . . . . . . . . . . . . . . . . . . . . . . . . .99

5.26 HOLD (Bus Hold Request) . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.27 IGNNE# (Ignore Numeric Exception) . . . . . . . . . . . . . . . . . 100

5.28 INIT (Initialization) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.29 INTR (Maskable Interrupt) . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.30 INV (Invalidation Request) . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.31 KEN# (Cache Enable) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.32 LOCK# (Bus Lock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

5.33 M/IO# (Memory or I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.34 NA# (Next Address) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.35 NMI (Non-Maskable Interrupt) . . . . . . . . . . . . . . . . . . . . . . . 106

5.36 PCD (Page Cache Disable) . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.37 PCHK# (Parity Check) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.38 PWT (Page Writethrough) . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Contents v

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

5.39 RESET (Reset) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

5.40 RSVD (Reserved) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

5.41 SCYC (Split Cycle) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

5.42 SMI# (System Management Interrupt) . . . . . . . . . . . . . . . . 111

5.43 SMIACT# (System Management Interrupt Active) . . . . . . 112

5.44 STPCLK# (Stop Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

5.45 TCK (Test Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

5.46 TDI (Test Data Input) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

5.47 TDO (Test Data Output) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

5.48 TMS (Test Mode Select) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

5.49 TRST# (Test Reset) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

5.50 VCC2DET (V

CC2

Detect) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

5.51 W/R# (Write/Read) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

5.52 WB/WT# (Writeback or Writethrough) . . . . . . . . . . . . . . . . 116

6 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

6.1 Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

6.2 Bus State Machine Diagram . . . . . . . . . . . . . . . . . . . . . . . . . 123

Idle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Data-NA# Requested . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Pipeline Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Pipeline Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

6.3 Memory Reads and Writes . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Single-Transfer Memory Read and Write . . . . . . . . . . . . . . . 126

Misaligned Single-Transfer Memory Read and Write . . . . . 128

Burst Reads and Pipelined Burst Reads . . . . . . . . . . . . . . . . 130

Burst Writeback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

6.4 I/O Read and Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Basic I/O Read and Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Misaligned I/O Read and Write . . . . . . . . . . . . . . . . . . . . . . . 135

6.5 Inquire and Bus Arbitration Cycles . . . . . . . . . . . . . . . . . . . 136

Hold and Hold Acknowledge Cycle . . . . . . . . . . . . . . . . . . . . 136

HOLD-Initiated Inquire Hit to Shared or Exclusive

Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

HOLD-Initiated Inquire Hit to Modified Line . . . . . . . . . . . 140

AHOLD-Initiated Inquire Miss. . . . . . . . . . . . . . . . . . . . . . . . 142

AHOLD-Initiated Inquire Hit to Shared or Exclusive

Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

AHOLD-Initiated Inquire Hit to Modified Line. . . . . . . . . . 146

AHOLD Restriction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Bus Backoff (BOFF#) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Locked Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Basic Locked Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Locked Operation with BOFF# Intervention . . . . . . . . . . . . 154

Interrupt Acknowledge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

vi Contents

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

6.6 Special Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Basic Special Bus Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Shutdown Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Stop Grant and Stop Clock States . . . . . . . . . . . . . . . . . . . . . 161

INIT-Initiated Transition from Protected Mode to

Real Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

7 Power-on Configuration and Initialization . . . . . . . . . . . . . . 167

7.1 Signals Sampled During the Falling Transition

of RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

FLUSH# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

BF[2:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

BRDYC# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

7.2 RESET Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

7.3 State of Processor After RESET . . . . . . . . . . . . . . . . . . . . . . 168

Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

7.4 State of Processor After INIT . . . . . . . . . . . . . . . . . . . . . . . . 170

8 Cache Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

8.1 MESI States in the Data Cache . . . . . . . . . . . . . . . . . . . . . . . 172

8.2 Predecode Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

8.3 Cache Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Cache-Related Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

8.4 Cache Disabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

8.5 Cache-Line Fills . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

8.6 Cache-Line Replacements . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

8.7 Write Allocate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Write to a Cacheable Page . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Write to a Sector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Write Allocate Limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Descriptions of the Logic Mechanisms and Conditions. . . . 180

8.8 Prefetching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

8.9 Cache States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

8.10 Cache Coherency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Inquire Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Internal Snooping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

FLUSH# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

WBINVD and INVD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Cache-Line Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Cache Snooping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

8.11 Writethrough vs. Writeback Coherency States . . . . . . . . . . 187

8.12 A20M# Masking of Cache Accesses . . . . . . . . . . . . . . . . . . . 187

9 Floating-Point and Multimedia Execution Units . . . . . . . . . 189

9.1 Floating-Point Execution Unit . . . . . . . . . . . . . . . . . . . . . . . 189

Handling Floating-Point Exceptions . . . . . . . . . . . . . . . . . . . 189

External Logic Support of Floating-Point Exceptions . . . . . 189

Contents vii

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

9.2 Multimedia Execution Unit . . . . . . . . . . . . . . . . . . . . . . . . . . 191

9.3 Floating-Point and MMX Instruction Compatibility . . . . . . 191

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

FERR# and IGNNE# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

10 System Management Mode (SMM) . . . . . . . . . . . . . . . . . . . . 193

10.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

10.2 SMM Operating Mode and Default Register Values . . . . . 193

10.3 SMM State-Save Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

10.4 SMM Revision Identifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

10.5 SMM Base Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

10.6 Halt Restart Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

10.7 I/O Trap Dword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

10.8 I/O Trap Restart Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

10.9 Exceptions, Interrupts, and Debug in SMM . . . . . . . . . . . . 202

11 Test and Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

11.1 Built-In Self-Test (BIST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

11.2 Tri-State Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

11.3 Boundary-Scan Test Access Port (TAP) . . . . . . . . . . . . . . . . 205

Test Access Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

TAP Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

TAP Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

TAP Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

TAP Controller State Machine . . . . . . . . . . . . . . . . . . . . . . . . 212

11.4 L1 Cache Inhibit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Purpose. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

11.5 Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Debug Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Debug Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

12 Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

12.1 Halt State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Enter Halt State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Exit Halt State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

12.2 Stop Grant State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Enter Stop Grant State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Exit Stop Grant State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

12.3 Stop Grant Inquire State . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Enter Stop Grant Inquire State . . . . . . . . . . . . . . . . . . . . . . . 226

Exit Stop Grant Inquire State . . . . . . . . . . . . . . . . . . . . . . . . 226

12.4 Stop Clock State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Enter Stop Clock State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Exit Stop Clock State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

viii Contents

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

13 Power and Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

13.1 Power Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

13.2 Decoupling Recommendations . . . . . . . . . . . . . . . . . . . . . . . 230

13.3 Pin Connection Requirements . . . . . . . . . . . . . . . . . . . . . . . 231

14 Electrical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

14.1 Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

14.2 Absolute Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

14.3 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

14.4 Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

15 I/O Buffer Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

15.1 Selectable Drive Strength . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

15.2 I/O Buffer Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

15.3 I/O Model Application Note . . . . . . . . . . . . . . . . . . . . . . . . . 239

15.4 I/O Buffer AC and DC Characteristics . . . . . . . . . . . . . . . . . 239

16 Signal Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . 241

16.1 CLK Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . 241

16.2 Clock Switching Characteristics for 66-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

16.3 Clock Switching Characteristics for 60-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

16.4 Valid Delay, Float, Setup, and Hold Timings . . . . . . . . . . . 243

16.5 Output Delay Timings for 66-MHz Bus Operation . . . . . . . 244

16.6 Input Setup and Hold Timings for 66-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

16.7 Output Delay Timings for 60-MHz Bus Operation . . . . . . . 248

16.8 Input Setup and Hold Timings for 60-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

16.9 RESET and Test Signal Timing . . . . . . . . . . . . . . . . . . . . . . 252

17 Thermal Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

17.1 Package Thermal Specifications . . . . . . . . . . . . . . . . . . . . . . 259

Heat Dissipation Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Measuring Case Temperature . . . . . . . . . . . . . . . . . . . . . . . . 262

17.2 Layout and Airflow Considerations . . . . . . . . . . . . . . . . . . . 262

Voltage Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Airflow Management in a System Design. . . . . . . . . . . . . . . 264

18 Pin Description Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

19 Pin Designations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

20 Package Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

20.1 321-Pin Staggered CPGA Package Specification . . . . . . . . 271

21 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Contents ix

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Part Two

AMD-K6 Processor Model 7 275

22 AMD-K6 Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

23 Internal Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

24 Software Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

24.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

Model-Specific Registers (MSR) . . . . . . . . . . . . . . . . . . . . . . 281

24.2 Instructions Supported by the AMD-K6 Processor . . . . . . . 283

25 Logic Symbol Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

26 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

26.1 VCC2DET (V

CC2

Detect) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

26.2 VCC2H/L# (V

CC2

High/Low) . . . . . . . . . . . . . . . . . . . . . . . . . 287

27 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

28 Power-on Configuration and Initialization . . . . . . . . . . . . . . 291

28.1 State of Processor After RESET . . . . . . . . . . . . . . . . . . . . . . 291

Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

29 Cache Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

30 Floating-Point and Multimedia Execution Units . . . . . . . . . 295

31 System Management Mode (SMM) . . . . . . . . . . . . . . . . . . . . 297

32 Test and Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

32.1 Tri-State Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

32.2 Boundary-Scan Test Access Port (TAP) . . . . . . . . . . . . . . . . 299

TAP Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

33 Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

34 Power and Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

34.1 Power Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

35 Electrical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

35.1 Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

35.2 Absolute Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

35.3 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

35.4 Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

36 I/O Buffer Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

x Contents

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

37 Signal Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . 311

38 Thermal Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

38.1 Package Thermal Specifications . . . . . . . . . . . . . . . . . . . . . . 313

39 Pin Description Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

40 Pin Designations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

41 Package Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

42 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

List of Figures xi

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

List of Figures

Part One

AMD-K6 Processor Family 3

Figure 1. AMD-K6 Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 2. Cache Sector Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 3. The Instruction Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 4. AMD-K6 Processor Decode Logic . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 5. AMD-K6 Processor Scheduler. . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 6. EAX Register with 16-Bit and 8-Bit Name Components. . . . . . 22

Figure 7. Integer Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 8. Segment Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 9. Segment Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 10. Floating-Point Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 11. FPU Status Word Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 12. FPU Control Word Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 13. FPU Tag Word Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 14. Packed Decimal Data Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 15. Precision Real Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 16. MMX Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 17. MMX Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 18. EFLAGS Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 19. Control Register 4 (CR4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 20. Control Register 3 (CR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 21. Control Register 2 (CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 22. Control Register 1 (CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 23. Control Register 0 (CR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 24. Debug Register DR7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 25. Debug Register DR6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 26. Debug Registers DR5 and DR4. . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 27. Debug Registers DR3, DR2, DR1, and DR0. . . . . . . . . . . . . . . . 36

Figure 28. Machine-Check Address Register (MCAR) . . . . . . . . . . . . . . . . 37

Figure 29. Machine-Check Type Register (MCTR). . . . . . . . . . . . . . . . . . . 38

Figure 30. Test Register 12 (TR12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 31. Time Stamp Counter (TSC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 32. Write Handling Control Register (WHCR) . . . . . . . . . . . . . . . . 39

Figure 33. Memory Management Registers. . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 34. Task State Segment (TSS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

xii List of Figures

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

Figure 35. 4-Kbyte Paging Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Figure 36. 4-Mbyte Paging Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 37. Page Directory Entry 4-Kbyte Page Table (PDE). . . . . . . . . . . 44

Figure 38. Page Directory Entry 4-Mbyte Page Table (PDE) . . . . . . . . . . 44

Figure 39. Page Table Entry (PTE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 40. Application Segment Descriptor . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 41. System Segment Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 42. Gate Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 43. Waveform Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Figure 44. Bus State Machine Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Figure 45. Non-Pipelined Single-Transfer Memory Read/Write and

Write Delayed by EWBE# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 46. Misaligned Single-Transfer Memory Read and Write . . . . . . 129

Figure 47. Burst Reads and Pipelined Burst Reads . . . . . . . . . . . . . . . . . 131

Figure 48. Burst Writeback due to Cache-Line Replacement . . . . . . . . . 133

Figure 49. Basic I/O Read and Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Figure 50. Misaligned I/O Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Figure 51. Basic HOLD/HLDA Operation . . . . . . . . . . . . . . . . . . . . . . . . . 137

Figure 52. HOLD-Initiated Inquire Hit to Shared or Exclusive Line . . . 139

Figure 53. HOLD-Initiated Inquire Hit to Modified Line. . . . . . . . . . . . . 141

Figure 54. AHOLD-Initiated Inquire Miss . . . . . . . . . . . . . . . . . . . . . . . . . 143

Figure 55. AHOLD-Initiated Inquire Hit to Shared or

Exclusive Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Figure 56. AHOLD-Initiated Inquire Hit to Modified Line . . . . . . . . . . . 147

Figure 57. AHOLD Restriction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Figure 58. BOFF# Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Figure 59. Basic Locked Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Figure 60. Locked Operation with BOFF# Intervention. . . . . . . . . . . . . . 155

Figure 61. Interrupt Acknowledge Operation . . . . . . . . . . . . . . . . . . . . . . 157

Figure 62. Basic Special Bus Cycle (Halt Cycle) . . . . . . . . . . . . . . . . . . . . 159

Figure 63. Shutdown Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160

Figure 64. Stop Grant and Stop Clock Modes, Part 1 . . . . . . . . . . . . . . . . 162

Figure 65. Stop Grant and Stop Clock Modes, Part 2 . . . . . . . . . . . . . . . . 163

Figure 66. INIT-Initiated Transition from Protected Mode to

Real Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Figure 67. Cache Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Figure 68. Cache Sector Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Figure 69. Write Handling Control Register (WHCR) . . . . . . . . . . . . . . . 179

Figure 70. Write Allocate Logic Mechanisms and Conditions. . . . . . . . . 180

Figure 71. External Logic for Supporting Floating-Point

Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

List of Figures xiii

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Figure 72. SMM Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Figure 73. TAP State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 74. Debug Register DR7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

Figure 75. Debug Register DR6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Figure 76. Debug Registers DR5 and DR4. . . . . . . . . . . . . . . . . . . . . . . . .218

Figure 77. Debug Registers DR3, DR2, DR1, and DR0. . . . . . . . . . . . . . . 219

Figure 78. Clock Control State Transitions . . . . . . . . . . . . . . . . . . . . . . . . 228

Figure 79. Suggested Component Placement . . . . . . . . . . . . . . . . . . . . . . 230

Figure 80. K6STD Pulldown V/I Curves . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Figure 81. K6STD Pullup V/I Curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Figure 82. CLK Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

Figure 83. Diagrams Key . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Figure 84. Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Figure 85. Maximum Float Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . 255

Figure 86. Input Setup and Hold Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 255

Figure 87. Reset and Configuration Timing . . . . . . . . . . . . . . . . . . . . . . . 256

Figure 88. TCK Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Figure 89. TRST# Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Figure 90. Test Signal Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Figure 91. Thermal Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

Figure 92. Power Consumption vs. Thermal Resistance . . . . . . . . . . . . . 260

Figure 93. Processor Heat Dissipation Path . . . . . . . . . . . . . . . . . . . . . . . 261

Figure 94. Measuring Case Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Figure 95. Voltage Regulator Placement. . . . . . . . . . . . . . . . . . . . . . . . . . 263

Figure 96. Airflow for a Heatsink with Fan . . . . . . . . . . . . . . . . . . . . . . . . 263

Figure 97. Airflow Path in a Dual-fan System . . . . . . . . . . . . . . . . . . . . . . 264

Figure 98. Airflow Path in an ATX Form-Factor System . . . . . . . . . . . . . 265

Figure 99. AMD-K6 Processor Top-Side View . . . . . . . . . . . . . . . . . . . . . . 267

Figure 100. AMD-K6 Processor Pin-Side View . . . . . . . . . . . . . . . . . . . . . . 268

Figure 101. 321-Pin Staggered CPGA Package Specification . . . . . . . . . . 272

Part Two

AMD-K6 Processor Model 7 275

Figure 102. Extended Feature Enable Register (EFER) . . . . . . . . . . . . . . 282

Figure 103. SYSCALL/SYSRET Target Address Register (STAR) . . . . . . 283

Figure 104. AMD-K6 Processor Model 7 Top-Side View. . . . . . . . . . . . . . . 315

Figure 105. AMD-K6 Processor Model 7 Pin-Side View . . . . . . . . . . . . . . . 316

xiv List of Figures

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

List of Tables xv

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

List of Tables

Part One

AMD-K6 Processor Family 3

Table 1. Execution Latency and Throughput of Execution

Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 2. General-Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 3. General-Purpose Register Dword, Word, and Byte

Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 4. Segment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 5. Model-Specific Registers (MSRs) . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 6. Memory Management Registers. . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 7. Application Segment Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 8. System Segment and Gate Types . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 9. Summary of Exceptions and Interrupts. . . . . . . . . . . . . . . . . . .48

Table 10. Integer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 11. Floating-Point Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 12. MMX Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 13. Processor-to-Bus Clock Ratios. . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 14. Input Pin Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 15. Output Pin Float Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 16. Input/Output Pin Float Conditions. . . . . . . . . . . . . . . . . . . . . . 118

Table 17. Test Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 18. Bus Cycle Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 19. Special Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 20. Bus-Cycle Order During Misaligned Transfers . . . . . . . . . . . . 128

Table 21. A[4:3] Address-Generation Sequence During Bursts . . . . . . . 130

Table 22. Bus-Cycle Order During Misaligned I/O Transfers . . . . . . . . . 135

Table 23. Interrupt Acknowledge Operation Definition. . . . . . . . . . . . . 156

Table 24. Encodings For Special Bus Cycles . . . . . . . . . . . . . . . . . . . . . . 158

Table 25. Output Signal State After RESET . . . . . . . . . . . . . . . . . . . . . . 168

Table 26. Register State After RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Table 27. PWT Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 28. PCD Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 29. CACHE# Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 30. Data Cache States for Read and Write Accesses . . . . . . . . . . 182

Table 31. Cache States for Inquiries, Snoops, Invalidation, and

Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Table 32. Snoop Action. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 33. Initial State of Registers in SMM . . . . . . . . . . . . . . . . . . . . . . . 195

Table 34. SMM State-Save Area Map . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

Table 35. SMM Revision Identifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table 36. I/O Trap Dword Configuration . . . . . . . . . . . . . . . . . . . . . . . . . 200

xvi List of Tables

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

Table 37. I/O Trap Restart Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Table 38. Boundary Scan Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 39. Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . .210

Table 40. Supported Tap Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Table 41. DR7 LEN and RW Definitions . . . . . . . . . . . . . . . . . . . . . . . . . 221

Table 42. Operating Ranges. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Table 43. Absolute Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Table 44. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Table 45. Typical and Maximum Power Dissipation . . . . . . . . . . . . . . . . 235

Table 46. A[20:3], ADS#, HITM#, and W/R# Strength Selection . . . . . .237

Table 47. CLK Switching Characteristics for 66-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Table 48. CLK Switching Characteristics for 60-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Table 49. Output Delay Timings for 66-MHz Bus Operation . . . . . . . . . 244

Table 50. Input Setup and Hold Timings for 66-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Table 51. Output Delay Timings for 60-MHz Bus Operation . . . . . . . . . 248

Table 52. Input Setup and Hold Timings for 60-MHz Bus

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Table 53. RESET and Configuration Signals (60-MHz and 66-MHz

Operation) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

Table 54. TCK Waveform and TRST# Timing at 25 MHz . . . . . . . . . . . . 253

Table 55. Test Signal Timing at 25 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . 253

Table 56. Package Thermal Specification . . . . . . . . . . . . . . . . . . . . . . . . 259

Table 57. 321-Pin Staggered CPGA Package Specification . . . . . . . . . . 271

Table 58. Valid Ordering Part Number Combinations . . . . . . . . . . . . . . 273

Part Two

AMD-K6 Processor Model 7 275

Table 59. Model-Specific Registers (MSRs) . . . . . . . . . . . . . . . . . . . . . . . 282

Table 60. Extended Feature Enable Register (EFER) Definition. . . . . 282

Table 61. SYSCALL/SYSRET Target Address Register (STAR)

Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Table 62. Integer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Table 63. Output Pin Float Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Table 64. Output Signal State After RESET . . . . . . . . . . . . . . . . . . . . . . 291

Table 65. Register State After RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

Table 66. Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . .300

Table 67. Operating Ranges. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

Table 68. Absolute Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

Table 69. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

Table 70. Typical and Maximum Power Dissipation . . . . . . . . . . . . . . . . 307

Table 71. Package Thermal Specification . . . . . . . . . . . . . . . . . . . . . . . . 313

Table 72. Valid Ordering Part Number Combinations . . . . . . . . . . . . . . 321

Revision History xvii

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Revision History

Date Rev Description

June 1997 E Replaced overbar with # to identify active-Low signals.

June 1997 E Corrected description in “Write Allocate” on page 177.

June 1997 E

Revised latency and throughput information in Table 1, “Execution Latency and Throughput of

Execution Units,” on page 18.

June 1997 E

Updated Figure 79, “Suggested Component Placement,” on page 230 of Chapter 13, “Power and

Grounding”.

Sept 1997 F Unreleased version.

March 1998 G

Divided book into Part 1 and Part 2. Part 1 provides information about the AMD-K6

®

processor

family (Model 6 and Model 7) and Part 2 provides information specific to the AMD-K6 processor

Model 7 (0.25-micron process technology).

March 1998 G Added Figure 17, “MMX™ Data Types,” on page 30 in Chapter 3, “Software Environment”.

March 1998 G

Qualified conditions under which Write Allocate occurs in the memory area between 640 Kbytes

and 1 Mbyte in “Write Allocate Limit” on page 178 of Chapter 8, “Cache Organization”.

March 1998 G

Changed power dissipation specifications for Stop Grant State and Stop Clock State for 166MHz,

200MHz, and 233MHz components in Table 45, “Typical and Maximum Power Dissipation,” on

page 235, and Table 56, “Package Thermal Specification,” on page 259.

March 1998 G

Removed all references to Write KEN# Control Register (WKCR) from Chapter 3, “Software

Environment”, Chapter 5, “Signal Descriptions”, and Chapter 8, “Cache Organization”.

March 1998 G

Added top-side view pin description diagram. See Figure 99, “AMD-K6

®

Processor Top-Side

View,” on page 267.

March 1998 G Added voltage detection pin to diagram in Chapter 4, “Logic Symbol Diagram”.

March 1998 G

Modified flatness specification (symbol f) in Table 57, “321-Pin Staggered CPGA Package

Specification,” on page 271.

March 1998 G

Corrected Figure 44, “Bus State Machine Diagram,” on page 123 in Chapter 6, “Bus Cycles” to

accurately show the direct transition from the Pipeline Data state to the Data-NA# Requested

state.

March 1998 G

Corrected list of internal resources tested during BIST in Chapter 11, “Test and Debug” on page

203.

March 1998 G

Revised Figure 92, “Power Consumption vs. Thermal Resistance,” on page 260 in Chapter 17,

“Thermal Design”.

March 1998 H Revised signal description of VCC2H/L# on page 287 in Chapter 26, “Signal Descriptions”.

xviii Revision History

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

About This Data Sheet 1

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

About This Data Sheet

The AMD-K6® Processor Data Sheet supports the Model 6 and Model 7 versions of

the AMD-K6 processor family. Model 6 refers to the AMD-K6 manufactured in the

0.35-micron process technology and Model 7 refers to the AMD-K6 manufactured in

the 0.25-micron process technology. The data sheet is divided into two parts. Part One

(chapters 1–21) contains information that pertains to the entire AMD-K6 desktop

family and information specific to the Model 6. Part Two (chapters 22–42) contains

information regarding new specifications and differences that pertain only to Model

7 as compared to Model 6.

2 About This Data Sheet

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Part One AMD-K6® Processor Family 3

Part One

AMD-K6

Processor Family

The AMD-K6® Processor Data Sheet supports the Model 6 and

Model 7 versions of the AMD-K6 processor family. Model 6

refers to the AMD-K6 manufactured with 0.35-micron process

technology and Model 7 refers to the AMD-K6 manufactured

with 0.25-micron process technology. Part One (chapters 1–21)

contains information that pertains to the entire AMD-K6

desktop family and information specific to Model 6.

®

4 AMD-K6® Processor Family Part One

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Chapter 1 AMD-K6® Processor 5

1AMD-K6

®

Processor

■ Advanced 6-Issue RISC86

®

Superscalar Microarchitecture

◆ Seven parallel specialized execution units

◆ Multiple sophisticated x86-to-RISC86 instruction decoders

◆ Advanced two-level branch prediction

◆ Speculative execution

◆ Out-of-order execution

◆ Register renaming and data forwarding

◆ Issues up to six RISC86 instructions per clock

■ Large On-Chip Split 64-Kbyte Level-One (L1) Cache

◆ 32-Kbyte instruction cache with additional predecode cache

◆ 32-Kbyte writeback dual-ported data cache

◆ MESI protocol support

■ High-Performance IEEE 754-Compatible and 854-Compatible Floating-Point Unit

■ High-Performance Industry-Standard MMX™ Instructions

■ 321-Pin Ceramic Pin Grid Array (CPGA) Package (Socket 7 Compatible)

■ Industry-Standard System Management Mode (SMM)

■ IEEE 1149.1 Boundary Scan

■ Full x86 Binary Software Compatibility

As the next generation in the AMD K86™ family of x86 processors, the innovative

AMD-K6 processor brings industry-leading performance to PC systems running the

extensive installed base of x86 software. In addition, its socket 7 compatible, 321-pin

Ceramic Pin Grid Array (CPGA) package enables the AMD-K6 to reduce

time-to-market by leveraging today’s cost-effective infrastructure to deliver a

superior price/performance PC solution.

To provide state-of-the-art performance, the AMD-K6 processor incorporates the

innovative and efficient RISC86 microarchitecture, a large 64-Kbyte level-one cache

(32-Kbyte dual-ported data cache, 32-Kbyte instruction cache with predecode data), a

powerful IEEE 754-compatible and 854-compatible floating-point execution unit, and

a high-performance multimedia execution unit for executing industry-standard MMX

instructions. These features have been combined to deliver industry leadership in

16-bit and 32-bit performance, providing exceptional performance for both Windows

®

95 and Windows NT™ software bases.

6 AMD-K6® Processor Chapter 1

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

The AMD-K6 processor’s RISC86 microarchitecture is a decoupled decode/execution

superscalar design that implements state-of-the-art design techniques to achieve

leading-edge performance. Advanced design techniques implemented in the AMD-K6

include multiple x86 instruction decode, single-clock internal RISC operations, seven

execution units that support superscalar operation, out-of-order execution, data

forwarding, speculative execution, and register renaming. In addition, the processor

supports the industry’s most advanced branch prediction logic by implementing an

8192-entry branch history table, the industry’s only branch target cache, and a return

address stack, which combine to deliver better than a 95% prediction rate. These

design techniques enable the AMD-K6 processor to issue, execute, and retire

multiple x86 instructions per clock, resulting in excellent scaleable performance.

The AMD-K6 processor is fully x86 binary code compatible. AMD’s extensive

experience through four generations of x86 processors has been carefully integrated

into the AMD-K6 to provide complete compatibility with Windows 95, Windows 3.x,

Windows NT, DOS, OS/2, Unix, Solaris, NetWare®, Vines, and other leading x86

operating systems and applications. The AMD-K6 processor is Socket 7 compatible,

allowing the processor to be quickly and easily integrated into a mature and

cost-effective industry-standard infrastructure of motherboards, chipsets, power

supplies, and thermal designs.

AMD has designed, manufactured, and delivered over 50 million Microsoft

®

Windows-compatible processors in the last five years alone. The AMD-K6 processor is

the next generation in this long line of processors. With its combination of

state-of-the-art features, industry-leading performance, high-performance

multimedia engine, full x86 compatibility, and low-cost infrastructure, the AMD-K6 is

the superior choice for mainstream personal computers.

Chapter 2 Internal Architecture 7

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

2 Internal Architecture

2.1 Introduction

The AMD-K6 processor implements advanced design techniques

known as the RISC86 microarchitecture. The RISC86

microarchitecture is a decoupled decode/execution design

approach that yields superior sixth-generation performance for

x86-based software. This chapter describes the techniques used

and the functional elements of the RISC86 microarchitecture.

2.2 AMD-K6® Processor Microarchitecture Overview

When discussing processor design, it is important to understand

the terms architecture, microarchitecture, and design

implementation. The term architecture refers to the instruction

set and features of a processor that are visible to software

programs running on the processor. The architecture

determines what software the processor can run. The

architecture of the AMD-K6 processor is the industry-standard

x86 instruction set.

The term microarchitecture refers to the design techniques used

in the processor to reach the target cost, performance, and

functionality goals. The AMD-K6 is based on a sophisticated

RISC core known as the Enhanced RISC86 microarchitecture.

The Enhanced RISC86 microarchitecture is an advanced,

second-order decoupled decode/execution design approach that

enables industry-leading performance for x86-based software.

The term design implementation refers to the actual logic and

circuit designs from which the processor is created according to

the microarchitecture specifications.

8 Internal Architecture Chapter 2

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

Enhanced RISC86®

Microarchitecture

The Enhanced RISC86 microarchitecture defines the

characteristics of the AMD-K6. The innovative RISC86

microarchitecture approach implements the x86 instruction set

by internally translating x86 instructions into RISC86

operations. These RISC86 operations were specially designed to

include direct support for the x86 instruction set while

observing the RISC performance principles of fixed length

encoding, regularized instruction fields, and a large register

set. The Enhanced RISC86 microarchitecture used in the

AMD-K6 enables higher processor core performance and

promotes straightforward extensibility in future designs.

Instead of directly executing complex x86 instructions, which

have lengths of 1 to 15 bytes, the AMD-K6 processor executes

the simpler and easier fixed-length RISC86 opcodes, while

maintaining the instruction coding efficiencies found in x86

programs.

The AMD-K6 processor contains parallel decoders, a

centralized RISC86 operation scheduler, and seven execution

units that support superscalar operation—multiple decode,

execution, and retirement—of x86 instructions. These elements

are packed into an aggressive and highly efficient six-stage

pipeline.

Decoders. Decoding of the x86 instructions begins when the

on-chip instruction cache is filled. Predecode logic determines

the length of an x86 instruction on a byte-by-byte basis. This

predecode information is stored, along with the x86

instructions, in the instruction cache, to be used later by the

decoders. The decoders translate on-the-fly, with no additional

latency, up to two x86 instructions per clock into RISC86

operations.

Note: In this chapter, “clock” refers to a processor clock.

The AMD-K6 processor categorizes x86 instructions into three

types of decodes—short, long and vector. The decoders process

either two short, one long, or one vector decode at a time. The

three types of decodes have the following characteristics:

■ Short decodes—x86 instructions less than or equal to seven

bytes in length

■ Long decodes—x86 instructions less than or equal to 11

bytes in length

■ Vector decodes—complex x86 instructions

Chapter 2 Internal Architecture 9

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Short and long decodes are processed completely within the

decoders. Vector decodes are started by the decoders and then

completed by fetched sequences from an on-chip ROM. After

decoding, the RISC86 operations are delivered to the scheduler

for dispatching to the executions units.

Scheduler/Instruction Control Unit. The centralized scheduler or

buffer is managed by the Instruction Control Unit (ICU). The

ICU buffers and manages up to 24 RISC86 operations at a time.

This equals from 6 to 12 x86 instructions. This buffer size (24) is

perfectly matched to the processor’s six-stage RISC86 pipeline

and seven parallel execution units. The scheduler accepts as

many as four RISC86 operations at a time from the decoders.

The ICU is capable of simultaneously issuing up to six RISC86

operations at a time to the execution units. This consists of the

following types of operations:

■ Memory load operation

■ Memory store operation

■ Complex integer or MMX register operation

■ Simple integer register operation

■ Floating-point register operation

■ Branch condition evaluation

Registers. The scheduler uses 48 physical registers that are

contained within the RISC86 microarchitecture when managing

the 24 RISC86 operations. The 48 physical registers are located

in a general register file and are grouped as 24 general

registers, plus 24 renaming registers. The 24 general registers

consist of 16 scratch registers and eight registers that

correspond to the x86 general purpose registers—EAX, EBX,

ECX, EDX, EBP, ESP, ESI and EDI.

Branch Logic. The AMD-K6 processor is designed with highly

sophisticated dynamic branch logic consisting of the following:

■ Branch history/Prediction table

■ Branch target cache

■ Return address stack

The AMD-K6 implements a two-level branch prediction scheme

based on an 8192-entry branch history table. The branch history

table stores prediction information that is used for predicting

conditional branches. Because the branch history table does not

10 Internal Architecture Chapter 2

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

store predicted target addresses, special address ALUs

calculate target addresses on-the-fly during instruction decode.

The branch target cache augments predicted branch

performance by avoiding a one clock cache-fetch penalty. This

specialized target cache does this by supplying the first 16 bytes

of target instructions to the decoders when branches are

predicted. The return address stack is a unique device

specifically designed for optimizing CALL and RETURN pairs.

In summary, the AMD-K6 uses dynamic branch logic to

minimize delays due to the branch instructions that are

common in x86 software.

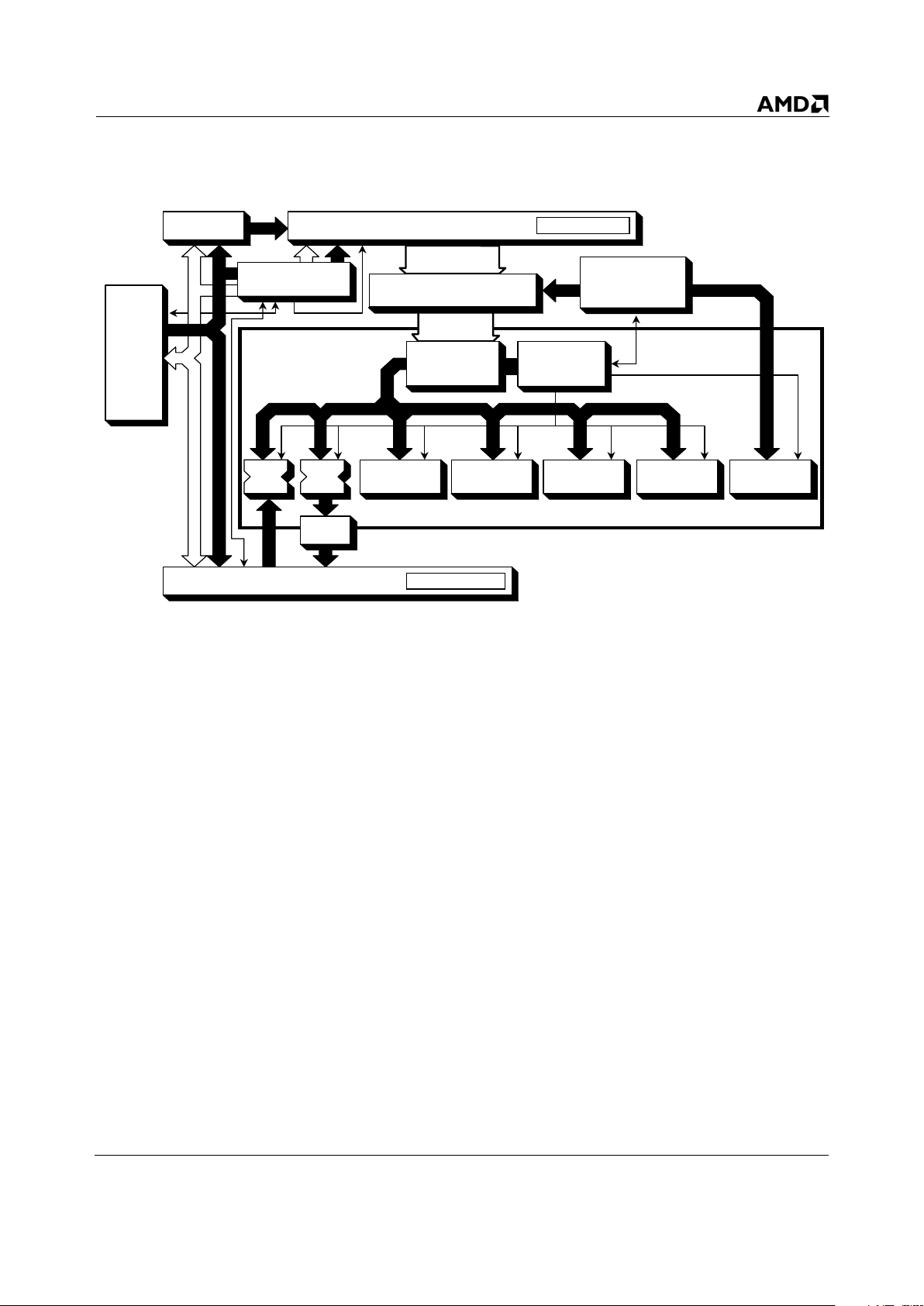

AMD-K6® Processor Block Diagram. As shown in Figure 1 on page 11,

the high-performance, out-of-order execution engine of the

AMD-K6 processor is mated to a split level-one 64-Kbyte

writeback cache with 32 Kbytes of instruction cache and 32

Kbytes of data cache. The instruction cache feeds the decoders

and, in turn, the decoders feed the scheduler. The ICU issues

and retires RISC86 operations contained in the scheduler. The

system bus interface is an industry-standard 64-bit Pentium

®

processor demultiplexed bus.

The AMD-K6 processor combines the latest in processor

microarchitecture to provide the highest x86 performance for

today’s personal computers. The AMD-K6 offers true

sixth-generation performance and full x86 binary software

compatibility.

Chapter 2 Internal Architecture 11

20695H/0—March 1998 AMD-K6

®

Processor Data Sheet

Preliminary Information

Figure 1. AMD-K6® Processor Block Diagram

2.3 Cache, Instruction Prefetch, and Predecode Bits

The writeback level-one cache on the AMD-K6 processor is

organized as a separate 32-Kbyte instruction cache and a

32-Kbyte data cache with two-way set associativity. The cache

line size is 32 bytes and lines are prefetched from main memory

using an efficient pipelined burst transaction. As the

instruction cache is filled, each instruction byte is analyzed for

instruction boundaries using predecoding logic. Predecoding

annotates each instruction byte with information that later

enables the decoders to efficiently decode multiple instructions

simultaneously.

Cache The processor cache design takes advantage of a sectored

organization (see Figure 2 on page 12). Each sector consists of

64 bytes configured as two 32-byte cache lines. The two cache

lines of a sector share a common tag but have separate pairs of

MESI (Modified, Exclusive, Shared, Invalid) bits that track the

state of each cache line.

Integer X

(Register) Unit

Store

Unit

Integer Y

(Register) Unit

Floating-Point

Unit

Branch

(Resolving) Unit

Store

Queue

Instruction

Control Unit

Scheduler

Buffer

(24 RISC86)

Six RISC86

®

Operation Issue

Out-of-Order

Execution Engine

Level-One Dual-Port Data Cache (32 KByte)

128-Entry DTLB

Level-One Instruction Cache

(32 KByte + Predecode)

64-Entry ITLB

Dual Instruction Decoders

x86 to RISC86

Branch Logic

(8192-Entry BHT)

(16-Entry BTC)

(16-Entry RAS)

Load

Unit

Multimedia

Unit

Predecode

Logic

Level-One Cache

Controller

Socket 7

Bus

Interface

16-Byte Fetch

Four RISC86

Decode

12 Internal Architecture Chapter 2

AMD-K6® Processor Data Sheet 20695H/0—March 1998

Preliminary Information

Figure 2. Cache Sector Organization

Two forms of cache misses and associated cache fills can take

place—a sector replacement and a cache line replacement. In

the case of a sector replacement, the miss is due to a tag

mismatch, in which case the required cache line is filled from

external memory, and the cache line within the sector that was

not required is marked as invalid. In the case of a cache line

replacement, the address matches the tag, but the requested

cache line is marked as invalid. The required cache line is filled

from external memory, and the cache line within the sector that

is not required remains in the same cache state.

Prefetching The AMD-K6 processor performs cache prefetching for sector

replacements only—as opposed to cache line replacements.

This cache prefetching results in the filling of the required

cache line first, and a prefetch of the second cache line.

Furthermore, the prefetch of the cache line that is not required

is initiated only in the forward direction—that is, only if the

requested cache line is the first cache line within the sector.

From the perspective of the external bus, the two cache-line

fills typically appear as two 32-byte burst read cycles occurring

back-to-back or, if allowed, as pipelined cycles.

Predecode Bits Decoding x86 instructions is particularly difficult because the

instructions are variable-length and can be from 1 to 15 bytes

long. Predecode logic supplies the predecode bits that are

associated with each instruction byte. The predecode bits

indicate the number of bytes to the start of the next x86

instruction. The predecode bits are stored in an extended

instruction cache alongside each x86 instruction byte as shown

in Figure 2 on page 12. The predecode bits are passed with the

instruction bytes to the decoders where they assist with parallel

x86 instruction decoding.

Tag

Address

Cache Line 1 Byte 31 Predecode Bits Byte 30 Predecode Bits ........ ........ Byte 0 Predecode Bits MESI Bits

Cache Line 2 Byte 31 Predecode Bits Byte 30 Predecode Bits ........ ........ Byte 0 Predecode Bits MESI Bits

Loading...

Loading...