AMD Advanced Micro Devices AM29F010B-90DWI1, AM29F010B-90DWE1, AM29F010B-90DWC1, AM29F010B, AM29F010B-90DTC1 Datasheet

...

SUPPLEMENT

1/13/98 Publication# 21116 Rev: B Amendment/0

Issue Date: January 1998

Am29F010 Known Good Die

1 Megabi t (1 28 K x 8-Bit)

CMOS 5.0 Volt-only, Uniform Sector Fla sh Memory—Die Revision 1

DISTINCTIVE CHARACTERISTICS

■ Single power supply ope ration

— 5.0 V ± 10% for read, erase, and program

operations

— Simplifies system-level power requirements

■ High performance

— 90 or 12 0 n s max im u m acc e ss t ime

■ Low power con sumption

— 30 mA max active read current

— 50 mA max program/erase current

—<25 µA typical standby current

■ Flexible sector architecture

— Eig ht un i for m sec t or s

— Any combination of sectors can be erased

— Supports full chip erase

■ Sector protection

— Hardware-based feature that disables/re-

enables program and erase operations in any

combination of sectors

— Sector protection/unprotecti on can be

implemented using standard PROM

programming equipm e nt

■ Embedded Algorithms

— Embedded E rase algorithm automatically

pre-programs and erases the chi p or any

combination of designated sector

— Embedded Program algorithm automatically

programs and verifies data at specified addres s

■ Minimum 100,000 program/erase cycles

guaranteed

■ Compatible with JEDEC standards

— Pinout and software compatible with

single-power-supply flash

— Superior inadverten t write prote ction

■ Data Po lling and Toggle Bits

— Provides a software method of detecting

program or erase cycle completion

■ T ested to datasheet specific ations at

temperature

■ Quality and reliability levels equivalent to

standard packaged components

2 Am29F010 Known Good Die 1/13/98

SUPPLEMENT

GENERAL DESCRIPTION

The Am29F010 in Known Good Die (KGD) form is a 1

Mbit, 5.0 Volt-only Flash memory . AMD defines KGD as

standard product in die form, tested for functionality

and speed. AMD KGD products have the same reliability and quality as AMD products in packaged form.

Am29F010 Features

The Am29F010 device is organized as eight uniform

sectors of 16 K byt es ea ch for fl e xibl e e ras e c ap ab i lit y.

This de vice is desig ned to b e prog ramme d in- system

with the standard syst em 5.0 Volt V

CC

supp ly. A power

supply providing 12.0 Volt V

PP

is not required for

program or erase operations.

The Am29F010 in KGD form offers access times of 90

ns and 120 ns, allowing high speed microprocessors to

operat e witho ut wait s tates. To eli min ate bus con tention the device has separate c hip enable (CE#), write

enable (WE#) and output enable (OE) controls.

The device requires only a single 5.0 volt power sup-

ply for both re ad an d w rite fu nc t ion s. In te rn all y g en er ated and r egulated voltages a re provided for th e

program and erase operations.

The device is entirely command set compatible with the

JEDEC single- power-s upply F lash st andar d. Commands ar e w ri tt en to th e c omm and re gi st er us ing st a ndard micr opro cess or wr ite timi ngs. R egi ster c ont ents

serve a s i nput t o an in ternal st ate ma chi ne that c ont rols

the erase and programming circuitry. Write cycles also

intern ally latch add re s se s an d d at a ne ed ed for t he pr ogramming and erase operations. Reading data out of

the device i s similar to r eading from other Flash o r

EPROM devices.

Device programming occurs by executing the program

command sequence. Thi s invokes the Embedded

Program algorithm—an internal algorit hm that automatica lly time s the pr ogram pulse widths and ver ifies

proper cell margin.

Device erasure occurs by executing the erase command sequence. This invokes the Embedded Erase

algori thm —an i nte rnal a lgo rith m th at a uto matic all y pr eprograms the array (if it is not already programmed) before executing the erase operation. During erase, the

device au tom a ticall y tim es th e e ra se pu ls e wid ths and

verifies proper cell margin.

The host system can detect whether a program or

erase operation is complete by reading the DQ7 (Data#

Polling) and DQ6 (toggle) status bits. After a program

or erase cycle has been completed, the device is ready

to read array data or accept another command.

The sector erase architecture allows memo ry sec tors

to be er ased and reprog rammed withou t affecting the

data contents of other sectors. The device is erased

when shipped from the factory.

The har dware data protection measures include a

low V

CC

detector automatically inhibits write operations

during power transitions . The hardware sector pro-

tection feature disables both program and erase operations in any combination of the sectors of memory,

and is imp lemen ted usi ng sta ndar d EPR OM pro gram mers.

The system can place the device into the standby mode.

Power cons u mpt io n i s gr eat l y r edu ce d in th i s mo de.

ELECTRICAL SPECIFICATIONS

Refer to the Am29F010 data sheet, publication number

16736, for full electrical specifications for the

Am29F0 10 in KGD form.

1/13/98 Am29F010 Known Good Die 3

SUPPLEMENT

PRODUCT SELECTOR GUIDE

DIE PHOTOGRAPH

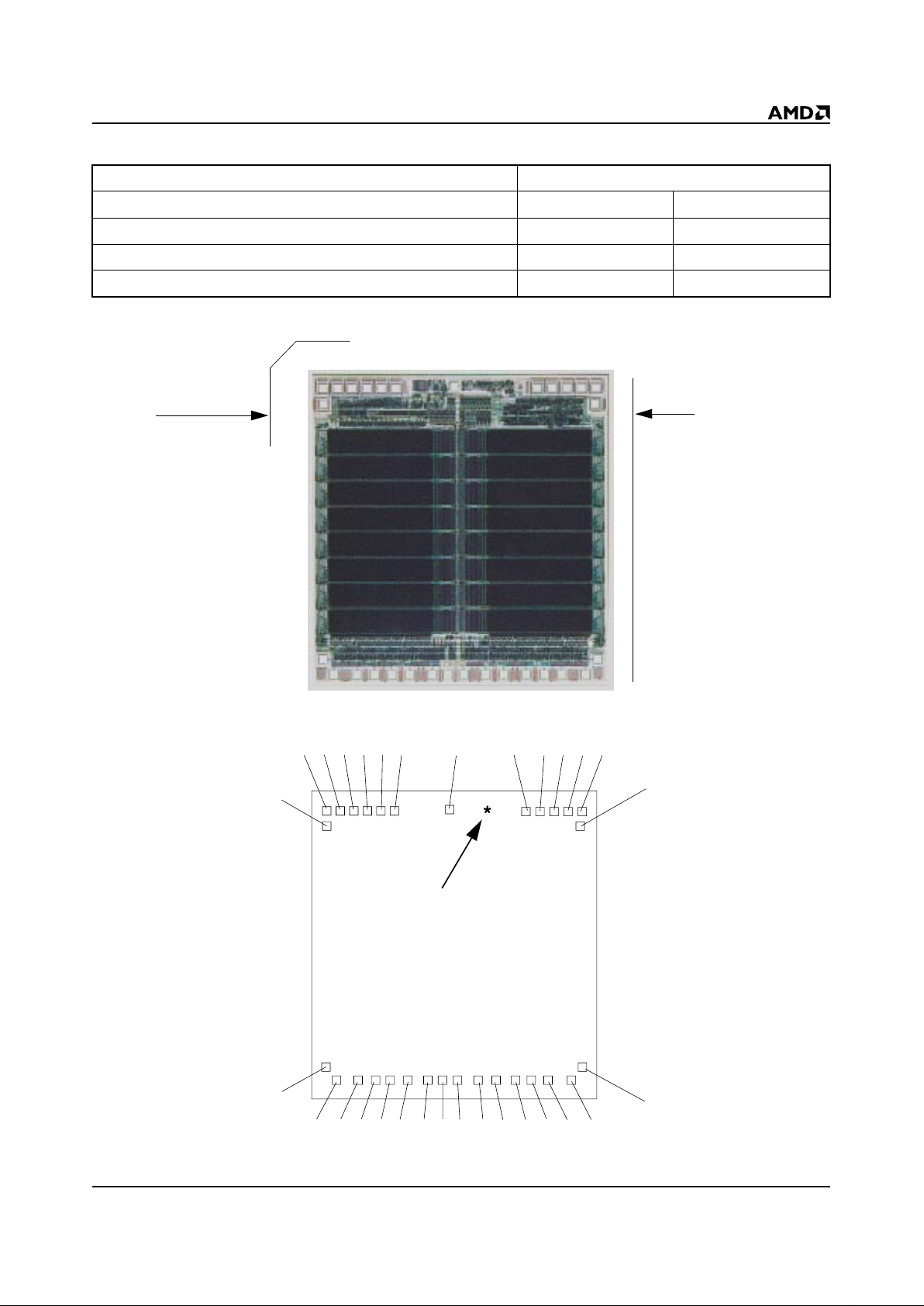

DIE PAD LOCATIONS

Family Part Number Am29F010 KGD

Speed Option (V

CC

= 5.0 V ± 10%) -90 -120

Max Access Time, t

ACC

(ns) 90 120

Max CE# Access, t

CE

(ns) 90 120

Max OE# Access, t

OE

(ns) 35 50

Orientation relative to

top left corner of

Gel-Pak

Orientation relative to

leading edge of tape

and reel

1234567

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23

24

25

2627282930

AMD logo location

Loading...

Loading...