Page 1

查询Am29F010-120DGC1供应商

SUPPLEMENT

Am29F010 Known Good Die

1 Megabi t (128 K x 8-Bit)

CMOS 5.0 Volt-only, Uniform Sector Fla sh Memory—Die Revision 1

DISTINCTIVE CHARACTERISTICS

■ Single power supply operation

— 5.0 V ± 10% for read, erase, and program

operations

— Simplifies system-level power requirements

■ High performance

— 90 or 120 ns maximu m access time

■ Low power consumptio n

— 30 mA max active read current

— 50 mA max program/erase current

—<25 µA typical standby current

■ Flexible sector architecture

— Eig ht un i for m sec t or s

— Any combination of sectors can be erased

— Supports full chip erase

■ Sector protection

— Hardware-based feature that disables/re-

enables program and erase operations in any

combination of sectors

— Sector protection/unprotection can be

implemented using standard PROM

progr am min g eq ui pm e nt

■ Embedded Algorithms

— Embedded Erase a lgorithm automatically

pre-programs and erases the chi p or any

combination of designated sector

— Embedded Program algorithm automatically

programs and v erifies data at specified address

■ Minimum 100,000 program/erase cycles

guaranteed

■ Compatible with JEDEC standards

— Pinout and software compatible with

single-power-supply flash

— Superior inadvertent write protection

■ Data P olling and T oggle Bits

— Provides a software method of detecting

program or erase cycle completion

■ T ested to datasheet specifications at

temperature

■ Quality and reliability levels equivalent to

standard packaged components

1/13/98 Publication# 21116 Rev: B Amendment/0

Issu e Date: January 1998

Page 2

SUPPLEMENT

GENERAL DESCRIPTION

The Am29F010 in Known Good Die (KGD) form is a 1

Mbit, 5.0 Volt-only Flash memory . AMD defines KGD as

standard product in die form, tested for functionality

and speed. AMD KGD products have the same reliability and quality as AMD products in packaged form.

Am29F010 Features

The Am29F010 device is organized as eight uniform

sectors of 16 Kbytes ea ch for fle x ible erase cap ab ilit y.

This de vice is desig ned t o be pr ogram med in- system

with the st andard system 5.0 V olt V

supply providing 12.0 Volt V

program or erase operations.

The Am29F010 in KGD form offers access times of 90

ns and 120 ns, allowing high speed microprocessors to

operat e witho ut wait s tates. To el imin ate bus con ten tion the device has separate chip enable (CE#), write

enable (WE#) and output enable (OE) controls.

The device requires only a single 5.0 volt power sup-

ply for both re ad an d write functions. Inte rn al ly g en er ated and r egulated voltages a re provided for th e

program and erase operations.

The device is entirely command set compatible with the

JEDEC single- power -supply F lash st andar d. Commands ar e w ri tt en to th e c om ma nd re gi s ter us i ng st a ndard micr opro cess or wr ite timi ngs. R egi ster c ont ents

serve a s i nput t o an in tern al st ate ma chi ne that c ont rols

the erase and programming circuitry. Write cycles also

intern ally latch a ddr es se s an d d at a ne ed ed for t he pr ogramming and erase operations. Readi ng data out of

the devic e is similar to r eading from other Flas h or

EPROM devices .

Device programming occurs by executing the program

command sequence. Thi s invokes the Embedded

supp ly. A power

CC

is not required for

PP

Program algorithm—an internal algorit hm that automatica lly time s the pr ogram pulse widths and ver ifies

proper cell margin.

Device erasure occurs by executing the erase command sequence. This invokes the Embedded Erase

algori thm —an i nte rnal a lgo ri thm th at a uto matic all y pr eprograms the array (if it is not already programmed) before executing the erase operation. During erase, the

device au tom a ticall y tim es th e e ra se pu ls e wi d ths an d

verifies proper cell margin.

The host system can detect whether a program or

erase operation is complete by reading the DQ7 (Data#

Polling) and DQ6 (toggle) status bits. After a program

or erase cycle has been completed, the device is ready

to read array data or accept another command.

The sector erase architecture allows me mory sect ors

to be er ased and reprog rammed withou t affecting the

data contents of other sectors. The device is erased

when shipped from the factory.

The har dware data protection measures include a

low V

detector automatically inhibits write operations

CC

during power transitions . The hardware sector protection feature disables both program and erase oper-

ations in any combination of the sectors of memory,

and is imp lemen ted usi ng sta ndar d EPR OM pro gram mers.

The system can place the device into the standby mode.

Power co nsu mpt i on i s gr ea tl y re duce d in thi s mo de.

ELECTRICAL SPECIFICATIONS

Refer to the Am29F010 data sheet, publication number

16736, for full electrical specifications for the

Am29F0 10 in KGD form.

2 Am29F010 Known Good Die 1/13/98

Page 3

SUPPLEMENT

PRODUCT SELECTOR GUIDE

Family Part Number Am29F010 KGD

Speed Option (V

Max Access Time, t

Max CE# Access, t

Max OE# Access, t

= 5.0 V ± 10%) -90 -120

CC

(ns) 90 120

ACC

(ns) 90 120

CE

(ns) 35 50

OE

DIE PHOTOGRAPH

Orientation relative to

top left corner of

Gel-Pak

Orientation relative to

leading edge of tape

and reel

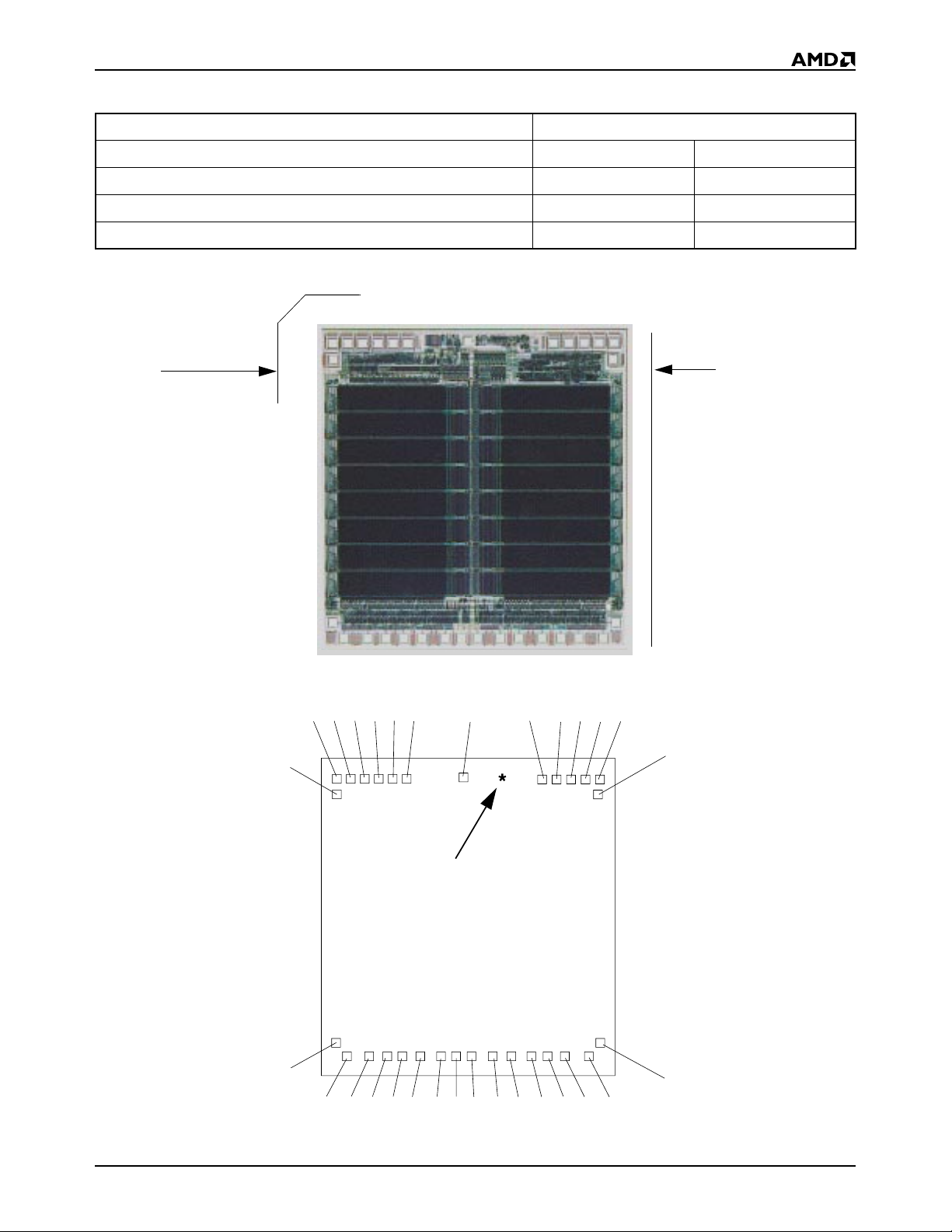

DIE PAD LOCATIONS

1234567

8

AMD logo location

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23

2627282930

25

24

1/13/98 Am29F010 Known Good Die 3

Page 4

PAD DESCRIPTION

SUPPLEMENT

Pad Signal

1V

2 A16 –33.20 –1.30 –0.84 –0.03

3 A15 –41.60 –1.30 –1.06 –0.03

4 A12 –49.90 –1.30 –1.27 –0.03

5 A7 –58.30 –1.30 –1.48 –0.03

6 A6 –66.60 –1.30 –1.69 –0.03

7 A5 –75.00 –1.30 –1.91 –0.03

8 A4 –74.40 –10.50 –1.89 –0.27

9 A3 –75.60 –158.20 –1.92 –4.02

10 A2 –69.40 –166.80 –1.76 –4.24

11 A1 –56.10 –166.80 –1.42 –4.24

12 A0 –46.10 –166.80 –1.17 –4.24

13 D0 –36.30 –166.90 –0.92 –4.24

14 D1 –25.90 –166.90 –0.66 –4.24

15 D2 –13.30 –166.90 –0.34 –4.24

CC

Pad Center (mils) Pad Center (millimeters)

XYXY

0.00 0.00 0.00 0.00

16 V

17 D3 4.70 –166.90 0.12 –4.24

18 D4 17.30 –166.90 0.44 –4.24

19 D5 27.60 –166.90 0.70 –4.24

20 D6 40.20 –166.90 1.02 –4.24

21 D7 50.60 –166.90 1.29 –4.24

22 CE# 60.60 –166.80 1.54 –4.24

23 A10 74.00 –166.80 1.88 –4.24

24 OE# 81.40 –158.20 2.07 –4.02

25 A11 80.20 –10.40 2.04 –0.26

26 A9 80.80 –1.30 2.05 –0.03

27 A8 72.40 –1.30 1.84 –0.03

28 A13 64.10 –1.30 1.63 –0.03

29 A14 55.70 –1.30 1.41 –0.03

30 WE# 47.40 –1.30 1.20 –0.03

SS

–4.30 –166.90 –0.11 –4.24

Note: The coordinates above are relative to the center of pad 1 and can be used to operate wire bonding equipment.

4 Am29F010 Known Good Die 1/13/98

Page 5

SUPPLEMENT

ORDERING INFORMATION

Standard Products

AMD KGD produ cts ar e avai lable i n seve ral pa ckages and operat ing ran ges. T he or der nu mber (Valid Combin ation) is form ed

by a combination of the following:

Am29F010

-90

DP

C

1

DIE REVISION

This number refers to the specific AMD manufacturing

process and product technology reflected in this

document. It is entered in the revision field of AMD

standard product nomenclature.

TEMPERATURE RANGE

C = Commercial (0°C to +70°C)

I=Industrial (–40°C to +85°C)

E = Extended (–55°C to +125°C)

PACKAGE TYPE AND MINIMUM ORDER QUANTITY

DP = Waffle Pack

245 die per 5 tray stack

DG = Gel-Pak

486 die per 6 tray stack

DT = Surftape™ (Tape and Reel)

2500 per 7-inch reel

DW = Gel-Pak

Call AMD sales office for minimum order quantity

SPEED OPTION

See Valid Combinations

®

Die Tray

®

Wafer Tray (sawn wafer on frame)

Valid Combinations

Am29F010-90 DPC 1, DPI 1, DPE 1,

DGC 1, DGI 1, DGE 1,

Am29F010-120

DTC 1, DTI 1, DTE 1,

DWC 1, DWI 1, DWE 1

DEVICE NUMBER/DESCRIPTION

Am29F010 Known Good Die

1 Megabit (128 K x 8-Bit) CMOS Flash Memory—Die Revision 1

5.0 Volt-only Program and Erase

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales

office to confirm availability of specific valid combinations and

to check on newly released combinations.

1/13/98 Am29F010 Known Good Die 5

Page 6

SUPPLEMENT

PRODUCT TEST FLOW

Figure 1 pr ovi d es an overview of A MD’s Kn ow n G ood

Die test flow. For more detailed information, refer to the

Am29F010 product qualification database supplement

for KGD. AMD implements quality assurance procedures th roug hout t he pro duct t est flow. In addi tion, an

Wafer So rt 1

Bake

24 hours at 250°C

Wafer Sort 2

off-line quality monitoring program (QMP) further guarantees AMD quality standards are met on Known Good

Die products. These QA procedures also allow AMD to

produce KGD products without requiring or implementing burn-in.

DC Parameters

Functionality

Programmability

Erasability

Data Retention

DC Parameters

Functionality

Programmability

Erasability

Wafer So rt 3

High Temperature

Packaging for Shipment

Shipment

Figure 1. AMD KGD Product Test Flow

DC Parameters

Functionality

Programmability

Erasability

Speed

Incoming Inspection

Wafer Saw

Die Separation

100% Visual Inspection

Die Pack

6 Am29F010 Known Good Die 1/13/98

Page 7

SUPPLEMENT

PHYSICAL SPECIFICATIONS

Die dimensions . . . . . . . . . . . . . . 174 mils x 189 mils

4.42 mm x 4.80 mm

Die Thickness . . . . . . . . . . . . . ~20 mils or ~0.51 mm

Bond Pad Size . . . . . . . . . . . . . . 4.47 mils x 4.47 mils

113.48 µm x 11 3.48 µm

Pad Area Free of Passivation . . . . . . . . . .19.98 mils

12,878 µm

Pads Per Die . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Bond Pad Metalization. . . . . . . . . . . . . . . . . . Al/Si/Cu

Die Backside . . . . . . . . . . . . . . . . . . . . . . . . No metal,

may be grounded (optional)

Passivation. . . . . . . . . . . . . . . . . . Nitride/SOG/Nitride

DC OPERATING CONDITIONS

VCC (Supply Voltage) . . . . . . . . . . . . . . .4.5 V to 5.5 V

Junction Temperature Under Bias . .T

For Read-only . . . . . . . . . . .T

Operating Temperature . . . Commercial 0°C to +70°C

Industrial –40°C to +85°C

Extended –5 5 ° C to +125°C

(max) = 130°C

J

(max) = 140°C

J

MANUFACTURING INFORMATION

Manufacturing and Test. . . . . . . . . Fab 14, Austin, TX

Manufacturing ID. . . . . . . . . . . . . . . . . . . . . .98108AK

Preparation for Shipment . . . . . . . .Penang, Malaysia

Fabrication Process . . . . . . . . . . . . . . . . . CS19AFDS

Die Revision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2

2

SPECIAL HANDLING INSTRUCTIONS

Processing

Do not expose KGD products to ultraviolet light or

proce ss them at temperat ures greater tha n 250°C.

Failure to adher e to these handling i nstructions will

result in irreparable damage to the devices. For best

yiel d, AMD recom mends assem bly in a Clas s 10K

clean room with 30% to 60% relative humidity.

Storage

Store at a maximum temperature of 30°C in a nitrogenpurged cabinet or vacuum-sealed bag. Observe all

standard ESD handling procedures.

1/13/98 Am29F010 Known Good Die 7

Page 8

SUPPLEMENT

TERMS AND CONDITIONS OF SALE FOR

AMD NON-VOLATILE MEMORY DIE

All transactions relating to AMD Products under this

agreement shall be subject to AMD’s standard terms

and co nd iti on s o f s ale , o r an y r evisions t her eo f, w hic h

revisio ns AMD res erves the rig ht to mak e at any time

and fro m tim e t o tim e . In th e e ve nt o f conflict bet w ee n

the provisions of AMD’s standard terms and conditions

of sale and this agreement, the terms of this agreement

shall be controlling.

AMD warrants artic les of its manufacture against

defective materials or workmanship for a period of

ninety (9 0) da ys fr om d ate of ship ment. Thi s warr anty

does not extend beyond AMD’s customer, and does

not extend to die which has been affixed onto a board

or substrate of any kind. The liability of AMD under this

warranty is limited, at AMD’s option, solely to repair or

to repla cemen t wit h equiv ale nt artic les, or to m ake a n

appropriate credit adjustment not to exceed the original

sales price, f or articles returned to AMD, provided th at:

(a) The Buyer promptly notifies AMD in writing of each

and every defect or nonco nformity in any article for

which Buy er wishe s to mak e a wa rran ty claim again st

AMD; (b) Buyer obtains authoriza tion from AMD to

return the ar ticle; (c) the artic le is returned to AMD,

trans por tati on c har ges paid by AMD, F.O.B . AMD ’s fa ctory; and (d) AMD’s examination of such article discloses to its satisfaction that such alleged d efect or

nonconformity actually ex ists and w as not caused by

negligence, misuse, improper installation, accident or

unauthorized repair or alteration by an entity other than

AMD. The afore mentioned provisions do not extend

the original warranty period of any article whi ch has

either been repaired or replaced by AMD.

THIS WARRANTY IS EXPRESSED IN LIEU OF ALL

OTHER WARR ANTIES, E XPRESSED OR IMPLIED ,

INCLUDING THE IMPLIED WARRANTY OF FI TNESS

FOR A PARTICULAR PURPOSE, THE IMPLI ED

WARRANTY OF MERCHANTABILITY AND OF ALL

OTHER OBLIGATIONS OR LIABILITIES ON AMD’S

PART, AND IT NEITHER ASSUMES NOR AUTHORIZES ANY OTHER PERSON TO ASSUME FOR

AMD ANY OTHER LIABILITIES. THE FOR EGOING

CONSTITUTES THE BUYERS SOLE AND EXCLUSIVE REMEDY FOR THE FURNISHING OF DEFECTIVE OR NON CONFORMING ARTICLES AND AMD

SHALL NOT IN ANY EVENT BE LIABLE FOR

DAMAGES BY REASON OF FAILURE OF ANY

PRODUCT TO FUNCTION PROPERLY OR FOR ANY

SPECIAL, INDIRECT, CONSEQUENTIAL, INCIDENTAL OR EXEMPLARY DAMAGES, INCLUDING

BUT NOT LIMITED TO, LOSS OF PROFITS, LOSS

OF USE OR COST OF LABOR BY REASON OF THE

FACT T HAT SUCH ARTICLES SHALL HAVE BEEN

DEFECTIVE OR NON CONFORMING.

Buyer agrees that it will make no warranty representations to its customer s which exceed those g iven by

AMD to Buyer unless and until Buyer shall agree to

indemnify AMD in wr iting fo r any claims w hich excee d

AMD’s warranty. Buyer assumes all responsibility for

success ful die pr ep, di e attach and wire b ondin g processes. Due to the unprotecte d nature o f the AMD

Products which are the subject hereof, AMD assumes

no responsibility for environmental effects on die.

AMD produ cts are n ot designed or author ized for us e

as components in life support appliances, devices or

systems where malfunction of a product can reasonably be expected to res ult in a personal injury. Buyer’s

use of A MD pro duct s f or use i n li fe s uppor t app li cati ons

is at Buyer’s own risk and Buyer agrees to fully indemnify AMD for an y damages resu lting in such use o r

sale.

REVISION SUMMARY FOR AM29F010

KNOWN GOOD DIE

Formatted to match current template. Updated Distinctive Characteristics and General Description sections

using the current main data sheet.

Trademarks

Copyright © 1998 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD logo, and combinations thereof are registered trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

8 Am29F010 Known Good Die 1/13/98

Loading...

Loading...