Page 1

Am186ER and Am188ER

Microcontrollers

User’s Manual

FT

RA

D

Page 2

© 1997 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. (“AM D”) reserves the right to make changes in

its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with

respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make

changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this

publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied w arranty of

merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or

systems without AMD’s written approval. AMD assumes no liability whatsoever for claims assoc iated with the sale or use (including the use of

engineering samples) of AMD products except as provided in AMD’s Terms and Conditions of Sale for such products.

Trademarks

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am386 and Am486 are registered trademarks of Advanced Micro Devices, Inc.

Am186, Am188, E86, AMD Facts-On-Demand, and K86 are trademarks of Advanced Micro Devices, Inc.

FusionE86 is a service mark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Page 3

IF YOU HAVE QUESTIONS, WE’RE HERE TO HELP YOU.

Customer Ser v ic e

The AMD customer service network includes U.S. offices, international offices, and a

customer training center. Expert t echnical assista nce is available from the worl dwide staff

of AMD field application engineers and factory support staff to answer E86™ family

hardware and software development questions.

Hotline and World Wide W eb Support

For answers to technical questions, AMD provides a toll-fr ee n umb er for direct access to

our corporate applications hotli ne. Also available is the AMD World Wide Web home page

and FTP site, which provides the la test E86 family product i nformation, including t echnical

information and data on upcoming product releases.

For technical support question s on all E86 products, send E-mail to lpd.support@amd.com.

Corporate A p plications Hotline

800-222-9323 toll-free for U.S. and Canada

44-(0) 1276-803-299 U.K. and Europe hotline

World Wide Web Home Page and FTP Site

To access the AMD home page go to http://www.amd.com.

To download documents and software, ftp to ftp.amd.com and log on as anonymous using

your E-mail address as a password. Or via your web browser, go to ftp://ft p .amd.com.

Questions, requests, and input concer ning AMD’s WWW pages c an be se nt via E-mail t o

webmaster@amd.com.

Documentation an d Literature

Free E86 family infor mation such as data books, user’ s manuals , data shee ts, ap plicatio n

notes, the FusionE86SM Partner Solu tions Catalog, and othe r literature is avail able with a

simple phone call. Internationally, contact your local AMD sales office for complete E86

family literature.

Literature Ordering

800-222-9323 toll-free for U.S. and Canada

512-602-5651 direct dial worldwide

512-602-7639 fax

800-222-9323 AMD Facts-On-Demand™ faxback service

toll-free for U.S. and Canada

iii

Page 4

iv

Page 5

TABLE OF CONTENTS

PREFACE INTRODUCTION AND OVERVIEW

Design Philosophy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

Purpose of this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

User’s Manual Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

AMD Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

E86™ Microcontroller Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

CHAPTER 1 FEATURES AND PERFORMANCE

1.1 Key Features and Benefits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.2 Distinctive Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.3 Application Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

1.3.1 Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

1.3.2 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.3.3 Serial Communications Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-7

1.4 Third-Party Development Support Products . . . . . . . . . . . . . . . . . . . . . . .1-8

CHAPTER 2 PROGRAMMING

2.1 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.1.1 Processor Status Flags Register . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.2 Memory Organization and Address Generation . . . . . . . . . . . . . . . . . . . . 2-3

2.3 I/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.4 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.5 Segments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.6 Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.7 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

CHAPTER 3 SYSTEM OVERVIEW

3.1 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.1.1 Pins That Are Used by Emulators . . . . . . . . . . . . . . . . . . . . . . .3-17

3.2 Bus Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

3.3 Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.3.1 Nonmultiplexed Address Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

3.3.2 Byte Write Enables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.3.3 Pseudo Static RAM (PSRAM) Support . . . . . . . . . . . . . . . . . . . . 3-21

3.4 Clock and Power Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.4.1 Phase-Locked Loop (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.4.2 Crystal-Driven Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.4.3 External Source Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

3.4.4 System Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-25

3.4.5 Power-Save Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

CHAPTER 4 PERIPHERAL CONTROL BLOCK

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4.1.1 Peripheral Control Block Relocation Register

(RELREG, Offset FEh) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.1.2 Reset Configuration Register (RESCON, Offset F6h). . . . . . . . . .4-5

4.1.3 Processor Release Level Register (PRL, Offset F4h). . . . . . . . . .4-6

4.1.4 Power-Save Control Register (PDCON, Offset F0h). . . . . . . . . . . 4-7

4.2 Initialization and Processor Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

Table of Contents

v

Page 6

CHAPTER 5 CHIP SELECT UNIT

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5.2 Chip Select Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

5.3 Ready and Wait-State Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

5.4 Chip Select Overlap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

5.5 Chip Select Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

5.5.1 Upper Memory Chip Select Register (UMCS, Offset A0h) . . . . . . 5-4

5.5.2 Low Memory Chip Select Register (LMCS, Offset A2h) . . . . . . . .5-6

5.5.3 Midrange Memory Chip Select Register (MMCS, Offset A6h) . . .5-8

5.5.4 PCS

5.5.5 Peripheral Chip Select Register (PACS, Offset A4h) . . . . . . . . . 5-12

CHAPTER 6 INTERNAL MEMORY

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

6.2 Interaction with External RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

6.3 Emulator and Debug Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.1 Internal Memory Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.2 Show Read Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

6.4 Internal Memory Chip Select Register (IMCS, Offset ACh) . . . . . . . . . . .6-3

CHAPTER 7 REFRESH CONTROL UNIT

7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7.1.1 Memory Partition Register (MDRAM, Offset E0h) . . . . . . . . . . . .7-1

7.1.2 Clock Prescaler Register (CDRAM, Offset E2h) . . . . . . . . . . . . . .7-2

7.1.3 Enable RCU Register (EDRAM, Offset E4h) . . . . . . . . . . . . . . . .7-2

CHAPTER 8 INTERRUPT CONTROL UNIT

8.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.1.1 Definitions of Interrupt Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.1.2 Interrupt Conditions and Sequence. . . . . . . . . . . . . . . . . . . . . . . .8-4

8.1.3 Interrupt Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-5

8.1.4 Software Exceptions, Traps, and NMI. . . . . . . . . . . . . . . . . . . . . .8-6

8.1.5 Interrupt Acknowledge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-8

8.1.6 Interrupt Controller Reset Conditions . . . . . . . . . . . . . . . . . . . . . .8-9

and MCS Auxiliary Register (MPCS, Offset A8h) . . . . . . . .5-10

8.1.1.1 Interrupt Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1.1.2 Interrupt Vector Table . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.1.1.3 Maskable and Nonmaskable Interrupts. . . . . . . . . . . . . .8-2

8.1.1.4 Interrupt Enable Flag (IF) . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.1.1.5 Interrupt Mask Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.1.1.6 Interrupt Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.1.1.7 Software Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.1.1.8 Software Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.1.2.1 Nonmaskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . .8-4

8.1.2.2 Maskable Hardware Interrupts . . . . . . . . . . . . . . . . . . . .8-4

8.1.2.3 The Interrupt Request . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.1.2.4 Interrupt Servicing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-4

8.1.2.5 Returning from the Interrupt . . . . . . . . . . . . . . . . . . . . . .8-4

8.1.3.1 Nonmaskable Interrupts and Software

Interrupt Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.1.3.2 Maskable Hardware Interrupt Priority . . . . . . . . . . . . . . . 8-5

8.1.4.1 Divide Error Exception (Interrupt Type 00h) . . . . . . . . . .8-6

8.1.4.2 Trace Interrupt (Interrupt Type 01h) . . . . . . . . . . . . . . . . 8-6

8.1.4.3 Nonmaskable Interrupt—NMI (Interrupt Type 02h). . . . .8-6

8.1.4.4 Breakpoint Interrupt (Interrupt Type 03h) . . . . . . . . . . . .8-7

8.1.4.5 INTO Detected Overflow Exception

(Interrupt Type 04h) . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-7

8.1.4.6 Array BOUNDS Exception (Interrupt Type 05h) . . . . . . .8-7

8.1.4.7 Unused Opcode Exception (Interrupt Type 06h). . . . . . .8-7

8.1.4.8 ESC Opcode Exception (Interrupt Type 07h) . . . . . . . . . 8-7

vi

Table of Contents

Page 7

8.2 Master Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.2.1 Fully Nested Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.2.2 Cascade Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.2.3 Special Fully Nested Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

8.2.4 Operation in a Polled Environment . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.2.5 End-of-Interrupt Write to the EOI Register . . . . . . . . . . . . . . . . .8-12

8.3 Master Mode Interrupt Controller Registers . . . . . . . . . . . . . . . . . . . . . . 8-13

8.3.1 INT0 and INT1 Control Registers

(I0CON, Offset 38h, I1CON, Offset 3Ah). . . . . . . . . . . . . . . . . . .8-14

8.3.2 INT2 and INT3 Control Registers

(I2CON, Offset 3Ch, I3CON, Offset 3Eh) . . . . . . . . . . . . . . . . . .8-16

8.3.3 INT4 Control Register (I4CON, Offset 40h). . . . . . . . . . . . . . . . .8-17

8.3.4 Timer and DMA Interrupt Control Registers

(TCUCON, Offset 32h, DMA0CON, Offset 34h, DMA1CON,

Offset 36h). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-18

8.3.5 Watchdog Timer Interrupt Control Register

(WDCON, Offset 42h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-19

8.3.6 Serial Port Interrupt Control Register (SPICON, Offset 44h). . . .8-20

8.3.7 Interrupt Status Register (INTSTS, Offset 30h). . . . . . . . . . . . . .8-21

8.3.8 Interrupt Request Register (REQST, Offset 2Eh) . . . . . . . . . . . .8-22

8.3.9 In-Service Register (INSERV, Offset 2Ch) . . . . . . . . . . . . . . . . . 8-23

8.3.10 Priority Mask Register (PRIMSK, Offset 2Ah) . . . . . . . . . . . . . . . 8-24

8.3.11 Interrupt Mask Register (IMASK, Offset 28h) . . . . . . . . . . . . . . .8-25

8.3.12 Poll Status Register (POLLST, Offset 26h). . . . . . . . . . . . . . . . . 8-26

8.3.13 Poll Register (POLL, Offset 24h). . . . . . . . . . . . . . . . . . . . . . . . .8-27

8.3.14 End-of-Interrupt Register (EOI, Offset 22h). . . . . . . . . . . . . . . . .8-28

8.4 Slave Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

8.4.1 Slave Mode Interrupt Nesting . . . . . . . . . . . . . . . . . . . . . . . . . . .8-29

8.4.2 Slave Mode Interrupt Controller Registers . . . . . . . . . . . . . . . . .8-29

8.4.3 Timer and DMA Interrupt Control Registers

(T0INTCON, Offset 32h, T1INTCON, Offset 38h, T2INTCON,

Offset 3Ah, DMA0CON, Offset 34h, DMA1CON, Offset 36h). . . 8-30

8.4.4 Interrupt Status Register (INTSTS, Offset 30h). . . . . . . . . . . . . .8-31

8.4.5 Interrupt Request Register (REQST, Offset 2Eh) . . . . . . . . . . . .8-32

8.4.6 In-Service Register (INSERV, Offset 2Ch) . . . . . . . . . . . . . . . . . 8-33

8.4.7 Priority Mask Register (PRIMSK, Offset 2Ah) . . . . . . . . . . . . . . . 8-34

8.4.8 Interrupt Mask Register (IMASK, Offset 28h) . . . . . . . . . . . . . . .8-35

8.4.9 Specific End-of-Interrupt Register (EOI, Offset 22h) . . . . . . . . . . 8-36

8.4.10 Interrupt Vector Register (INTVEC, Offset 20h) . . . . . . . . . . . . .8-37

CHAPTER 9 TIMER CONTROL UNIT

9.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9.2 Programmable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2.1 Timer Operating Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.2.2 Timer 0 and Timer 1 Mode and Control Registers (T0CON,

Offset 56h, T1CON, Offset 5Eh) . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.2.3 Timer 2 Mode and Control Register (T2CON, Offset 66h) . . . . . .9-5

9.2.4 Timer Count Registers (T0CNT, Offset 50h, T1CNT,

Offset 58h, T2CNT, Offset 60h). . . . . . . . . . . . . . . . . . . . . . . . . . .9-6

9.2.5 Timer Maxcount Compare Registers (T0CMPA, Offset 52h,

T0CMPB, Offset 54h, T1CMPA, Offset 5Ah, T1CMPB,

Offset 5Ch, T2CMPA, Offset 62h). . . . . . . . . . . . . . . . . . . . . . . . .9-7

Table of Contents

vii

Page 8

CHAPTER 10 DMA CONTROLLER

10.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.2 DMA Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.3 Programmable DMA Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

10.3.1 DMA Control Registers

(D0CON, Offset CAh, D1CON, Offset DAh) . . . . . . . . . . . . . . . .10-3

10.3.2 DMA Transfer Count Registers

(D0TC, Offset C8h, D1TC, Offset D8h). . . . . . . . . . . . . . . . . . . . 10-5

10.3.3 DMA Destination Address High Register (High Order Bits)

(D0DSTH, Offset C6h, D1DSTH, Offset D6h). . . . . . . . . . . . . . . 10-6

10.3.4 DMA Destination Address Low Register (Low Order Bits)

(D0DSTL, Offset C4h, D1DSTL, Offset D4h) . . . . . . . . . . . . . . . 10-7

10.3.5 DMA Source Address High Register (High Order Bits)

(D0SRCH, Offset C2h, D1SRCH, Offset D2h) . . . . . . . . . . . . . .10-8

10.3.6 DMA Source Address Low Register (Low Order Bits)

(D0SRCL, Offset C0h, D1SRCL, Offset D0h) . . . . . . . . . . . . . . .10-9

10.4 DMA Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

10.4.1 Synchronization Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-11

10.4.2 DMA Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

10.4.3 DMA Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

10.4.4 DMA Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-12

10.4.5 DMA Channels on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-13

CHAPTER 11 ASYNCHRONOUS SERIAL PORT

11.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.2 Programmable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.2.1 Serial Port Control Register (SPCT, Offset 80h). . . . . . . . . . . . .11-2

11.2.2 Serial Port Status Register (SPSTS, Offset 82h) . . . . . . . . . . . .11-4

11.2.3 Serial Port Transmit Data Register (SPTD, Offset 84h) . . . . . . . 11-5

11.2.4 Serial Port Receive Data Register (SPRD, Offset 86h). . . . . . . .11-6

11.2.5 Serial Port Baud Rate Divisor Register (SPBAUD, Offset 88h). .11-7

CHAPTER 12 SYNCHRONOUS SERIAL INTERFACE

12.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

12.1.1 Four-Pin Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.2 Programmable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

12.2.1 Synchronous Serial Status Register (SSS, Offset 10h). . . . . . . .12-3

12.2.2 Synchronous Serial Control Register (SSC, Offset 12h). . . . . . . 12-4

12.2.3 Synchronous Serial Transmit 1 Register (SSD1, Offset 14h)

Synchronous Serial Transmit 0 Register (SSD0, Offset 16h) . . . 12-5

12.2.4 Synchronous Serial Receive Register (SSR, Offset 18h) . . . . . .12-6

12.3 SSI Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-7

CHAPTER 13 PROGRAMMABLE I/O PINS

13.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

13.2 PIO Mode Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-3

13.2.1 PIO Mode 1 Register (PIOMODE1, Offset 76h) . . . . . . . . . . . . .13-3

13.2.2 PIO Mode 0 Register (PIOMODE0, Offset 70h) . . . . . . . . . . . . .13-3

13.3 PIO Direction Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-4

13.3.1 PIO Direction 1 Register (PDIR1, Offset 78h) . . . . . . . . . . . . . . 13-4

13.3.2 PIO Direction 0 Register (PDIR0, Offset 72h) . . . . . . . . . . . . . . 13-4

13.4 PIO Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-5

13.4.1 PIO Data Register 1 (PDATA1, Offset 7Ah) . . . . . . . . . . . . . . . .13-5

13.4.2 PIO Data Register 0 (PDATA0, Offset 74h) . . . . . . . . . . . . . . . . 13-5

13.5 Open-Drain Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-5

APPENDIX A REGISTER SUMMARY

viii

Table of Contents

Page 9

LIST OF FIGURES

Figure 1-1 Am186ER Microcontroller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 1-2 Am188ER Microcontroller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Figure 1-3 Basic Functional System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Figure 2-1 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

Figure 2-2 Processor Status Flags Register (FLAGS) . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

Figure 2-3 Physical Address Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-4 Memory and I/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-5 Supported Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 3-1 Am186ER Micr ocontr ol le r Ad dres s Bus —Normal Read

Figure 3-2 Am186ER Microcontroller—Read and Write with Address Bus Disable

Figure 3-3 Am188ER Microcontroller Address Bus—Normal Read and Write Operation.3-20

Figure 3-4 Am188ER Microcontroller—Read and Write with Address Bus Disable

Figure 3-5 Oscillator Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

Figure 3-6 Clock Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

Figure 4-1 Peripheral Control Block Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

Figure 4-2 Peripheral Control Block Relocation Register (RELREG, offset FEh) . . . . . . . . 4-4

Figure 4-3 Reset Configuration Register (RESCON, offset F6h) . . . . . . . . . . . . . . . . . . . . 4-5

Figure 4-4 Processor Release Level Register (PRL, offset F4h). . . . . . . . . . . . . . . . . . . . .4-6

Figure 4-5 Power-Save Control Register (PDCON, offset F0h) . . . . . . . . . . . . . . . . . . . . .4-7

Figure 5-1 Upper Memory Chip Select Register (UMCS, offset A0h) . . . . . . . . . . . . . . . . . 5-4

Figure 5-2 Low Memory Chip Select Register (LMCS, offset A2h) . . . . . . . . . . . . . . . . . . . 5-6

Figure 5-3 Midrange Memory Chip Select Register (MMCS, offset A6h) . . . . . . . . . . . . . .5-8

Figure 5-4 PCS

Figure 5-5 Peripheral Chip Select Register (PACS, offset A4h) . . . . . . . . . . . . . . . . . . . . 5-12

Figure 6-1 Internal Memory Chip Select Register (IMCS, offset ACh) . . . . . . . . . . . . . . . . 6-3

Figure 7-1 Memory Partition Register (MDRAM, offset E0h). . . . . . . . . . . . . . . . . . . . . . . .7-1

Figure 7-2 Clock Prescaler Register (CDRAM, offset E2h). . . . . . . . . . . . . . . . . . . . . . . . .7-2

Figure 7-3 Enable RCU Register (EDRAM, offset E4h) . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Figure 8-1 External Interrupt Acknowledge Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

Figure 8-2 Fully Nested (Direct) Mode Interrupt Controller Connections . . . . . . . . . . . . .8-10

Figure 8-3 Cascade Mode Interrupt Controller Connections . . . . . . . . . . . . . . . . . . . . . . . 8-11

Figure 8-4 INT0 and INT1 Control Registers (I0CON, I1CON, offsets 38h and 3Ah) . . . . 8-14

Figure 8-5 INT2 and INT3 Control Registers (I2CON, I3CON, offsets 3Ch and 3Eh). . . .8-16

Figure 8-6 INT4 Control Register (I4CON, offset 40h) . . . . . . . . . . . . . . . . . . . . . . . . . . .8-17

Figure 8-7 Timer/DMA Interrupt Control Registers

Figure 8-8 Watchdog Timer Interrupt Control Register (WDCON, offset 42h). . . . . . . . . . 8-19

Figure 8-9 Serial Port Interrupt Control Register (SPICON, offset 44h) . . . . . . . . . . . . . . 8-20

Figure 8-10 Interrupt Status Register (INTSTS, offset 30h) . . . . . . . . . . . . . . . . . . . . . . . . 8-21

Figure 8-11 Interrupt Request Register (REQST, offset 2Eh) . . . . . . . . . . . . . . . . . . . . . . . 8-22

Figure 8-12 In-Service Register (INSERV, offset 2Ch) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-23

Figure 8-13 Priority Mask Register (PRIMSK, offset 2Ah). . . . . . . . . . . . . . . . . . . . . . . . . . 8-24

Figure 8-14 Interrupt Mask Register (IMASK, offset 28h) . . . . . . . . . . . . . . . . . . . . . . . . . . 8-25

Figure 8-15 Poll Status Register (POLLST, offset 26h). . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-26

Figure 8-16 Poll Register (POLL, offset 24h). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

Figure 8-17 Example EOI Assembly Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

Figure 8-18 End-of-Interrupt Register (EOI, offset 22h) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

Figure 8-19 Timer and DMA Interrupt Control Registers (T0INTCON, T1INTCON,

Figure 8-20 Interrupt Status Register (INTSTS, offset 30h) . . . . . . . . . . . . . . . . . . . . . . . . 8-31

Figure 8-21 Interrupt Request Register (REQST, offset 2Eh) . . . . . . . . . . . . . . . . . . . . . . . 8-32

Figure 8-22 In-Service Register (INSERV, offset 2Ch) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-33

Figure 8-23 Priority Mask Register (PRIMSK, offset 2Ah). . . . . . . . . . . . . . . . . . . . . . . . . . 8-34

Figure 8-24 Interrupt Mask Register (IMASK, offset 28h) . . . . . . . . . . . . . . . . . . . . . . . . . . 8-35

and Write Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

In Effect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

In Effect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-20

and MCS Auxiliary Register (MPCS, offset A8h). . . . . . . . . . . . . . . . . . .5-10

(TCUCON, DMA0CON, DMA1CON, offsets 32h, 34h, and 36h). . . . . . . . . . .8-18

T2INTCON, DMA0CON, DMA1CON, offsets 32h, 38h, 3Ah, 34h, and 36h). . 8-30

Table of Contents

ix

Page 10

Figure 8-25 Specific End-of-Interrupt Register (EOI, offset 22h). . . . . . . . . . . . . . . . . . . . . 8-36

Figure 8-26 Interrupt Vector Register (INTVEC, offset 20h) . . . . . . . . . . . . . . . . . . . . . . . . 8-37

Figure 9-1 Timer 0 and Timer 1 Mode and Control Registers (T0CON, T1CON,

offsets 56h and 5Eh) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-3

Figure 9-2 Timer 2 Mode and Control Register (T2CON, offset 66h) . . . . . . . . . . . . . . . . .9-5

Figure 9-3 Timer Count Registers (T0CNT, T1CNT, T2CNT, offsets 50h, 58h, and 60h) . .9-6

Figure 9-4 Timer Maxcount Compare Registers (T0CMPA, T0CMPB, T1CMPA,

Figure 10-1 DMA Unit Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

Figure 10-2 DMA Control Registers (D0CON, D1CON, offsets CAh and DAh) . . . . . . . . .10-3

Figure 10-3 DMA Transfer Count Registers (D0TC, D1TC, offsets C8h and D8h) . . . . . . . 10-5

Figure 10-4 DMA Destination Address High Register

Figure 10-5 DMA Destination Address Low Register

Figure 10-6 DMA Source Address High Register

Figure 10-7 DMA Source Address Low Register

Figure 10-8 Source-Synchronized DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-11

Figure 10-9 Destination Synchronized DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

Figure 11-1 Serial Port Control Register (SPCT, offset 80h). . . . . . . . . . . . . . . . . . . . . . . . 11-2

Figure 11-2 Serial Port Status Register (SPSTS, offset 82h) . . . . . . . . . . . . . . . . . . . . . . . 11-4

Figure 11-3 Serial Port Transmit Data Register (SPTD, offset 84h) . . . . . . . . . . . . . . . . . . 11-5

Figure 11-4 Serial Port Receive Data Register (SPRD, offset 86h) . . . . . . . . . . . . . . . . . . 11-6

Figure 11-5 Serial Port Baud Rate Divisor Register (SPBAUD, offset 88h) . . . . . . . . . . . . 11-7

Figure 12-1 Synchronous Serial Status Register (SSS, offset 10h) . . . . . . . . . . . . . . . . . .12-3

Figure 12-2 Synchronous Serial Control Register (SSC, offset 12h). . . . . . . . . . . . . . . . . . 12-4

Figure 12-3 Synchronous Serial Transmit Register (SSD1, SSD0, offsets 14h and 16h) . .12-5

Figure 12-4 Synchronous Serial Receive Register (SSR, offset 18h) . . . . . . . . . . . . . . . . . 12-6

Figure 12-5 Synchronous Serial Interface Multiple Write . . . . . . . . . . . . . . . . . . . . . . . . . . 12-8

Figure 12-6 Synchronous Serial Interface Multiple Read . . . . . . . . . . . . . . . . . . . . . . . . . .12-8

Figure 13-1 Programmable I/O Pin Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

Figure 13-2 PIO Mode 1 Register (PIOMODE1, offset 76h) . . . . . . . . . . . . . . . . . . . . . . . . 13-3

Figure 13-3 PIO Mode 0 Register (PIOMODE0, offset 70h) . . . . . . . . . . . . . . . . . . . . . . . . 13-3

Figure 13-4 PIO Direction 1 Register (PDIR1, offset 78h). . . . . . . . . . . . . . . . . . . . . . . . . . 13-4

Figure 13-5 PIO Direction 0 Register (PDIR0, offset 72h). . . . . . . . . . . . . . . . . . . . . . . . . . 13-4

Figure 13-6 PIO Data 1 Register (PDATA1, offset 7Ah) . . . . . . . . . . . . . . . . . . . . . . . . . . .13-5

Figure 13-7 PIO Data 0 Register (PDATA0, offset 74h) . . . . . . . . . . . . . . . . . . . . . . . . . . .13-5

Figure A-1 Internal Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-4

T1CMPB, T2CMPA, offsets 52h, 54h, 5Ah, 5Ch, and 62h) . . . . . . . . . . . . . . . . 9-7

(D0DSTH, D1DSTH, offsets C6h and D6h) . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

(D0DSTL, D1DSTL, offsets C4h and D4h). . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

(D0SRCH, D1SRCH, offsets C2h and D2h). . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

(D0SRCL, D1SRCL, offsets C0h and D0h) . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

x

Table of Contents

Page 11

LIST OF TABLES

Table 2-1 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

Table 2-2 Segment Register Selection Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Table 2-3 Memory Addressing Mode Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Table 3-1 PIO Pin Assignments—Numeric Listing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Table 3-2 PIO Pin Assignments—Alphabetic Listing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Table 3-3 Bus Cycle Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

Table 3-4 Clocking Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Table 3-5 Maximum and Minimum Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

Table 4-1 Processor Release Level (PRL) Register High-Order Byte Values . . . . . . . . . . 4-6

Table 4-2 Initial Register State After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

Table 5-1 Chip Select Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

Table 5-2 UMCS Block Size Programming V alues. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

Table 5-3 LMCS Block Size Programming Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-6

Table 5-4 MCS

Table 5-5 PCS

Table 5-6 PCS

Table 8-1 Am186ER and Am188ER Microcontroller Interrupt Types. . . . . . . . . . . . . . . . .8-3

Table 8-2 Interrupt Controller Registers in Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . 8-13

Table 8-3 Priority Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

Table 8-4 Priority Field Mask (Master Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-24

Table 8-5 Interrupt Controller Registers in Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

Table 8-6 Priority Field Mask (Slave Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-34

Table 9-1 Timer Control Unit Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

Table 10-1 DMA Controller Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

Table 10-2 Synchronization Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

Table 10-3 Maximum DMA Transfer Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-10

Table 11-1 Asynchronous Serial Port Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

Table 11-2 Parity Mode Bit Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

Table 11-3 Serial Port Baud Rate Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

Table 12-1 Synchronous Serial Interface Register Summary . . . . . . . . . . . . . . . . . . . . . .12-1

Table 12-2 SCLK Divider Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-4

Table 13-1 PIO Pin Assignments and Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-2

Table 13-2 PIO Mode and PIO Direction Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-3

Table A-1 Internal Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-2

Block Size Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

Address Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

3–PCS0 Wait-State Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Table of Contents

xi

Page 12

xii

Table of Contents

Page 13

PREFACE

INTRODUCTION AND OVERVIEW

DESIGN PHILOSOPHY

AMD’s Am186™ and Am188Q™ family of microcontrol lers is base d on the archite cture of

the original 8086 and 8088 microcontr olle rs, and cu rr ently i ncludes t he 80C18 6, 80C188 ,

80L186, 80L188, Am186ER, Am188ER, Am186EMLV, Am188EMLV, Am186ES,

Am188ES, Am186ESLV, Am188ESLV, Am186EM, Am188EM, Am186ED, and

Am186EDLV microcontrollers. The Am186ER and Am188ER microcontroll e rs provide a

natural migration path for 80C186/188 designs that need performance and system cost

enhancements.

The Am186ER an d A m1 8 8E R m ic r oc o n t ro l l er s p r o v id e a lo w -c o st , h ig h - pe r f o rm a nc e s ol u ti o n

for embedded sy ste m designe rs wh o want to use th e x86 a rchit ectur e. By i nteg rati ng multi ple

fun c t i onal b l o c k s a n d 3 2 K b y t e o f i n t e r n a l R A M w i t h t h e C P U , the Am186ER and Am188ER

microcontrollers eliminate the need for off-chip system-interface logic. It is possible to

implement a fully functio nal system wit h ROM and RAM, serial int erfaces, and custom I / O

capability without additional system-interface logic.

The Am186ER and Am188ER microcontrollers can opera te at f requenci es up t o 40 MHz.

The microcontrollers in clude an on-boar d PLL so that the clock input frequency can b e as

little as one fourth the processor operating frequency. The Am186ER and Am188ER

microcontrollers are available in versions operating at 20, 25, 33, and 40 MHz.

PURPOSE OF THIS MANUAL

This manual describes the technical features and programming inte rface of the Am186ER

and Am188ER microcontrollers. The complete inst ruction set is documented in the

and Am188 Family Instruction Set Manual,

order #21267.

Am186

INTENDED AUDIENCE

This manual is intended for computer hardware and software engineers and system

architects who are designing or are considering designi ng systems based on the Am186ER

and Am188ER microcontrollers.

USER’S MANUAL OVERVIEW

This manual contains information on the Am186ER and Am188ER mic rocontrollers and is

essential for system architects and design engineers . Additional information is avail able in

the form of data sheets, application notes, and othe r documentation that is provided with

software products and hardware-development tools.

The information in this manual is organized into 12 chapters and 1 appendix.

n Chapter 1 introduces the features and performance aspects of the Am186ER and

Am188ER microcontrollers.

n Chapter 2 describes the programmer’s model of the Am186 and Am188 family

microcontrollers, including an instruction set overview and register model.

n Chapter 3 provides an overview of the system interfaces, along with clocking

features.

Introduction and Overview

xiii

Page 14

n Chapter 4 provides a description of the peripheral control block al ong wit h power

management and reset configuration.

n Chapter 5 provides a description of the chip select unit.

n Chapter 6 provides a description of the internal memory.

n Chapter 7 provides a description of the refresh control unit.

n Chapter 8 provides a description of the on-chip interrupt controller.

n Chapter 9 describes the timer control unit.

n Chapter 10 describes the DMA controller.

n Chapter 11 describes the asynchronous serial port.

n Chapter 12 describes the synchronous serial interface.

n Chapter 13 describes the programmable I/O pins.

n Appendix A includes a complete summary of peripheral registers and fields.

For complete information on the Am186ER and Am188ER microcontroller pi n lists, timing,

thermal characteristics, and physical dimensions, please refer to the

Am188ER Microcontrollers Data Sheet

, order #20732.

Am186ER and

AMD DOCUMENTATION

E86™ Microcontroller Family

ORDER NO. DOCUMENT TITLE

20732 Am186ER and Am188ER Microcon troller s Dat a Sheet

Hardware docume ntati on: pin desc ript ions, funct ion al desc ript ions, absol ute

maximum ratings, operating ranges, switching characteristics and waveforms,

connection diagr ams an d pinout s, and package p hysic al dime nsions .

21267 Am186 and Am188 Family Instr uctio n Set Manua l

Provides a detail ed description and examples for eac h instruction included in the

Am186 and Am188 Famil y Ins tructi on Set.

SM

19255 FusionE86

Catalog

Provides info rmat ion on t ool s that s peed a n E86 fami ly em bedde d produc t to

market. Include s products fr om expert suppl iers of emb edded develo pment solutions.

20071 E86 Family Support Tools Bri ef

Lists avail able E86 family sof tware and hard ware developme nt tools, as well a s

contact information for suppliers.

21058 FusionE86 Development Too ls Refe rence CD

Provides a sing le-so urce multim edia to ol for cus tomer eva luatio n of AMD pr oducts, as well as Fu sion partner tools and techno logies that support the E86 family

of microcontrollers and microprocessors. T echnical documentation for the E86

family is included on the CD in PDF format.

To order literature, contact the neares t AMD sales office or call 800-222-9323, opt ion 3 (in

the U.S. and Canada ) or dir ect di al from any locat ion 512 -602 -5651.

xiv

Literature is also available in postscript and PDF formats on the AMD web site. To access the

AMD home page, go to http://www.amd.com. To download documents and software, ftp t o

ftp.amd.com and log on as anonymous using your E-mail address as a password. Or via

your web browser, go to ftp://ftp.amd.com.

Introduction and Overview

Page 15

CHAPTER

1

FEATURES AND PERFORMANCE

Compared to the 80C186/188 microcontrollers, the Am186™ER and Am188™ER

microcontroller s enable designers to increase perf ormance and functionality , while reducing

the cost, s ize, and power consumption of embedded systems. The Am186ER and Am188ER

microcontrollers are cost-effective, enhanced versions of the AMD 80C186/188 devices.

The Am186ER and Am188ER microcontrollers deliver 80C186/188 compatibility plus

32 Kbyte of integrated memory, increased performance, reduced power consumption,

serial communications, and a glueless bus interface. Developed exclusively for the

embedded marketplace, the Am186ER and Am188ER microcontrollers increase the

performance of existing 80C186/188 systems while decreasing their cost.

Because the Am186ER and Am188ER microcontrollers integrate memory, on-chip

peripherals, and system logic and offer up to twice the performance of an 80C186/188,

they are ideal solutions for customer s who need to enhance and cost-reduce their pres ent

x86 designs.

1.1 KEY FEATURES AND BENEFITS

The Am186ER and Am188ER microcontrollers extend the AMD family of microcontroller s

based on the industry-standard x86 archit ecture. Upgrading to the Am186ER or Am188ER

microcontrollers is attractive for the following reasons:

n Minimized total system co st—The new on-chip RAM, peripherals , and system-int erface

logic nearly eliminate the need f or external devices, reducing t he overal l system cos t of new

or existing 80C186/188 designs.

n Integrated RAM—32 Kbyte of internal RAM ensures a low-cost supply of memor y and

also a smaller form fa ctor and lower power consumption for syst em designs. The internal

memory provides the same performance as external zero-wait-state RAM devices.

n Enhanced performance—The Am186ER and Am188ER microcontrollers offer up to

40-MHz operation, which requires only a 10-MHz input clock. The nonmultiplexed

address bus offers faster, unbuffered access to memory.

n Zero-wait-state operation—Enhanced bus timing permits zero -wait-state op e rati on at

40 MHz with internal RAM or inexpensive 70-ns memories.

n 3.3-V supply voltage with 5-V-tolerant I/O—The Am186ER and Am188ER

microcontrollers use a 3.3-V supply over the ent ire range of operating frequencies,

increasing the performance of on e-sup ply 3.3- V systems whi le preser ving much l ower

power consumption when compared to 5-V operation. The 5-V-tolerant I/O

accommodates existing 5-V designs.

n Enhanced functionality—The new and enhanced on-chip peripherals include an

asynchronous serial port, a virtual watchdog timer, an additional interrupt pin, a highspeed synchronous serial interface, a PSRAM controller, a 16-bit Reset Configuration

Register, enhanced chip-select functionality, and 32 programmable I/Os.

n x86 software compatibility—The Am186ER and Am188ER microcontrollers are

80C186/188-compatible and upward-compatible with the AMD E86 family.

Features and Performance

1-1

Page 16

The Am186ER and Am188ER microcontrollers are part of the AMD E86 family of embedded

microcontroll ers and microproc essors based on th e x86 architectu re. The 16-bit me mbers of the

E86 family, ref erred to t hrough out t his man ual as t he Am186 and Am188 f amily , includ e the

80C186, 80C188, 80L186, 80L188, Am186ER, Am188ER, Am186EM, Am188EM,

Am186EMLV, Am188EMLV, Am186ES, Am188ES, Am186ESLV, Am188ESLV,

Am186ED and Am186EDLV microcontrollers.

The Am186ER and Am188ER microcontrollers are designed to meet the most common

requirements of embedded products developed for t he offi ce automation, mass storage,

communications, and general embedded markets. Applications include disk drive

controllers, hand-held an d desktop terminals, fax machines, printers, phot ocopiers, feature

phones, cellular phones, PBXs, multiplexers, modems, and industrial control.

1.2 DISTINCTIVE CHARACTERISTICS

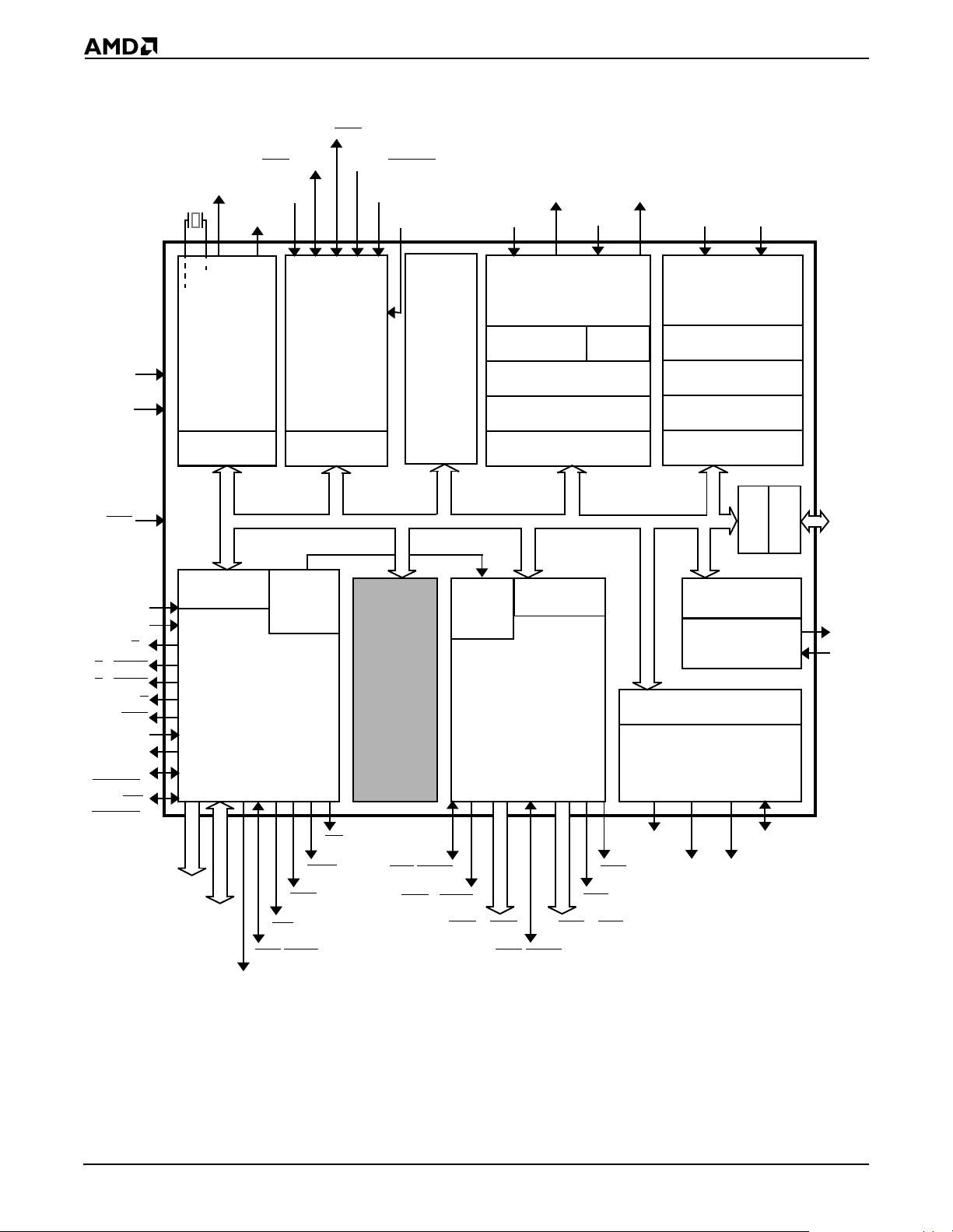

A block diagram of each microcontroller is shown in Figure 1-1 and Figure 1-2. The

Am186ER microcontroller uses a 16-bit external bus, while the Am188ER microcontr oller

has an 8-bit external bus.

The Am186ER and Am188ER microcontrollers provide the following features:

n Memory Integration:

– 32 Kbyte of internal RAM with an internal chip sel ect register

– Internal RAM provides same performance as zero-wait-state external memory

n Reduced power consumption:

– 3.3-V ± 0.3-V operation at all operating frequencies

– I/O drivers tolerate 5-V signal s

n High performance:

– 20-, 25-, 33-, and 40-MHz operating frequencies

– Support for zero-wait-state operation at 40 MHz with 70-ns memory

– 1-Mbyte memory address space and 64-Kbyte I/O space

n New features remove the requirement for a 2x clock i nput and provi de faster access to

memory:

– Phase-locked loop (PLL) allows processor to operate at up to four times the clock

input frequency

– Nonmultiplexed address bus

n New integrated peripherals increase functionalit y wh ile reducing system cost:

– 32 programmable I/O (PIO) pins

– Asynchronous serial port allows full-duplex, 7-bit or 8-bit data transfers

– Synchronous serial interface allows high-speed, half-duplex, bidirectional data

transfer to and from application-specific integrated circuits (ASICs)

1-2

– Controller for external pseudo-static RAM (PSRAM) with auto refresh capability

– Reset Configuration Register

– Additional external and internal interrupts

– Timer 1 can be configured to provide a watchdog timer interrupt

Features and Performance

Page 17

n Familiar 80C186 peripherals:

– Two independent DMA channels

– Programmable interrupt controller with six external interrupts

– Three programmable 16-bit timers

– Programmable memory and peripheral chip-s elect logic

– Programmable wait-state gen erator

– Power-save clock divider

n Software-compatible with the 80C186/188 microcontroller

n Widely available native development tools, applications, and system software

n Available for commercial or industrial temperature range

n Available in the following packages:

– 100-pin, thin quad flat pack (TQFP)

– 100-pin, plastic quad flat pack (PQFP)

Features and Performance

1-3

Page 18

Figure 1-1 Am186ER Microcontroller Block Diagram

V

CC

GND

RES

ARDY

SRDY

S1/IMDIS

S0/SREN

DT/R

DEN

HOLD

HLDA

S6/

CLKSEL

UZI

CLKSEL

S2

1

/

2

INT3/INTA

CLKOUTA

CLKOUTB

X2

X1

Clock and

Power

Management

Unit

Control

Registers

Control

Registers

Interface

Bus

Unit

INT2/INTA

1/IRQ

INT4

Interrupt

Control Unit

Control

Registers

Refresh

Control

Unit

INT1/SELECT

RD

0

INT0

NMI

Execution

32 Kbyte

RAM

(16K x 16)

Unit

TMROUT0 TMROUT1

TMRIN0 TMRIN1

DRQ0 DRQ1

Timer Control

Unit

01 (WDT)2 0 1

Max Count B

20-Bit Source

Registers

Max Count A

20-Bit Destination

Registers

16-Bit Coun t

16-Bit Count

Registers

Control

Registers

PSRAM

Control

Unit

Control

Registers

Chip-Select

Unit

Asynchronous

Control

Registers

Synchronous Serial

Interface

SCLK

DMA

Unit

Pointers

Pointers

Registers

Control

Registers

Control

Control

Registers

Serial Port

SDATA

Unit

Registers

PIO

PIO31–

1

PIO0

TXD

RXD

1-4

A19–A0

AD15–AD0

ALE

BHE

WR

/ADEN

WLB

WHB

LCS/ONCE0

MCS3/RFSH

MCS

2–MCS0

UCS/ONCE1

PCS

PCS

5/A1

PCS

3–PCS0

6/A2

SDEN0 SDEN1

Notes:

1. All PIO signals are shared wi th other physic al pins. See the pin des criptions in Chapter 3 and

Table 3-1 on page 3-10 for information on shared functions.

Features and Performance

Page 19

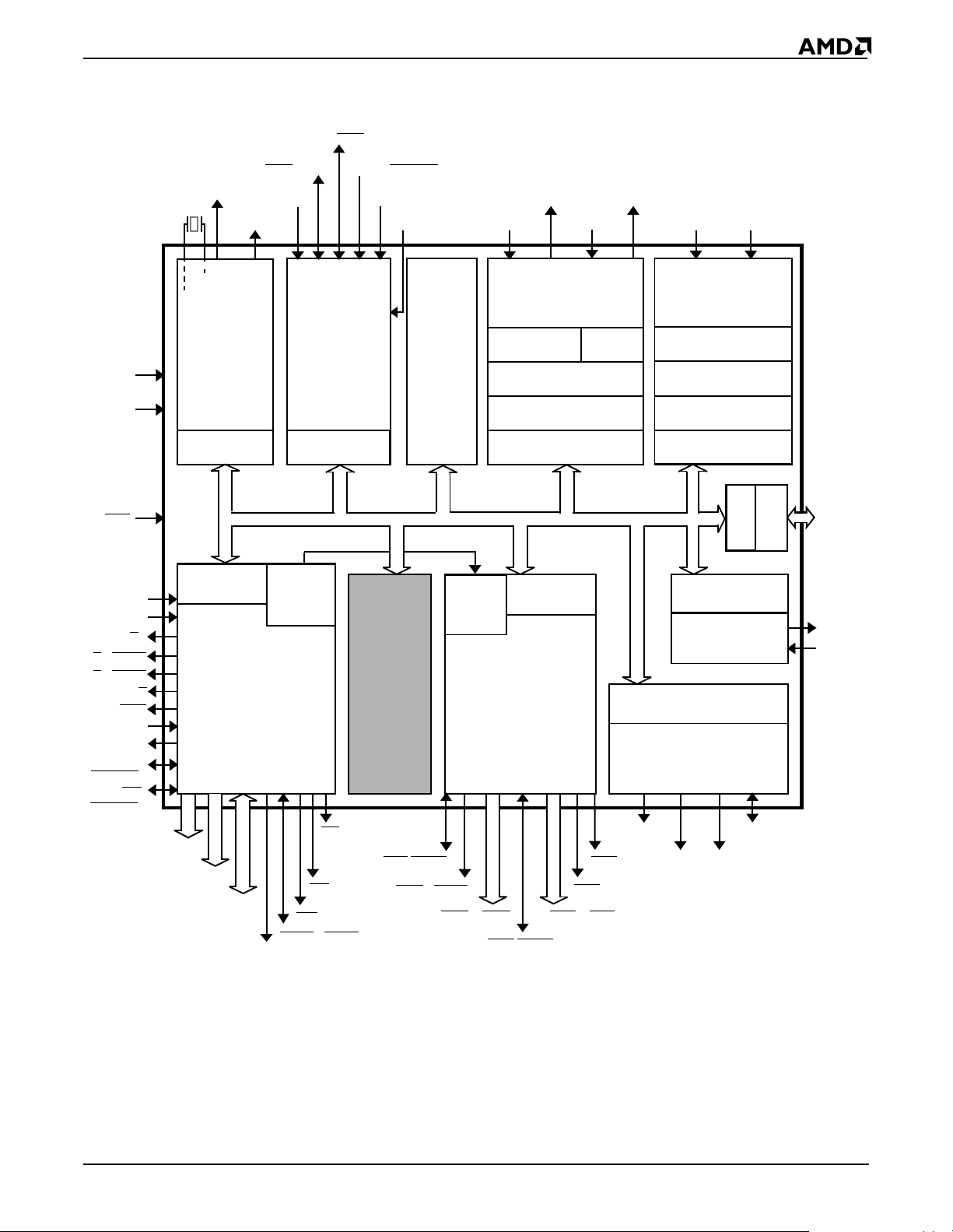

Figure 1-2 Am188ER Microcontroller Block Diagram

INT2/INTA0

V

CC

GND

RES

ARDY

SRDY

S1/IMDIS

S0/SREN

DT/R

DEN

HOLD

HLDA

S6/

CLKSEL

UZI

CLKSEL

S2

1

/

2

A19–A0

CLKOUTA

X2

X1

Clock and

Power

Management

Unit

Control

Registers

Control

Registers

AO15–AO8

AD7–AD0

INT3/INTA

CLKOUTB

Bus

Interface

Unit

ALE

1/IRQ

INT4

Interrupt

Control Unit

Control

Registers

Refresh

Control

Unit

RD

WB

WR

RFSH2/ADEN

INT1/SELECT

INT0

NMI

Execution

32 Kbyte

RAM

(32K x 8)

LCS/ONCE0

MCS3/RFSH

Unit

MCS

TMROUT0 TMROUT1

TMRIN0 TMRIN1

Timer Control

01 (WDT)2 0 1

Max Count B

Registers

Max Count A

16-Bit Count

PSRAM

Control

Registers

Unit

Chip-Select

Unit

2–MCS0

UCS

/ONCE1

Unit

Registers

Registers

Control

Registers

Control

PCS

PCS

PCS

5/A1

3–PCS0

DRQ0 DRQ1

DMA

Unit

20-Bit Source

Pointers

20-Bit Destination

Pointers

16-Bit Count

Registers

Control

Registers

Control

Registers

Asynchronous

Serial Port

Control

Registers

Synchronous Serial

Interface

SCLK

SDEN0 SDEN1

6/A2

Control

Registers

SDATA

PIO

Unit

PIO31–

1

PIO0

TXD

RXD

Notes:

1. All PIO signals are shared wi th other physic al pins. See the pin des criptions in Chapter 3 and

Table 3-1 on page 3-10 for information on shared functions.

Features and Performance

1-5

Page 20

1.3 APPLICATION CONSIDERATIONS

The integration enhancements of the Am186ER and Am188ER microc ontrollers provide a

high-performance, low-syst em-cost solution for 16-bit embedded microcontrolle r designs.

The internal 32-Kbyte RAM allows t he manufacture of a complete embedded sy stem using

only one external ROM device and a low-cost crystal, plus any voltage conversion or current

drivers required for I/O. Internal RAM is enabled and configured by using the Internal

Memory Chip Select (IMCS) Register described in Chapter 6, “Internal Memory.”

The nonmultiplexed address bus (A19–A0) eliminates system-interface logic for external

memory, while the multi plexed address /data bus maint ains the value of existin g customerspecific peripherals and circuits within the upgraded design.

The nonmultiplexed address bus is available in additi on to the 80C186 and 80C188

microcontrollers’ multiplexed addres s/d ata bus (AD15–AD0). The two buses can operate

simultaneously, or the AD15–AD0 bus can be configured to operate only during the data

phase of a bus cycle. See the BHE

and see section 5 .5.1 an d sectio n 5.5.2 for a dditio nal in form ation regard ing the AD15 –AD0

address enabling and di sablin g.

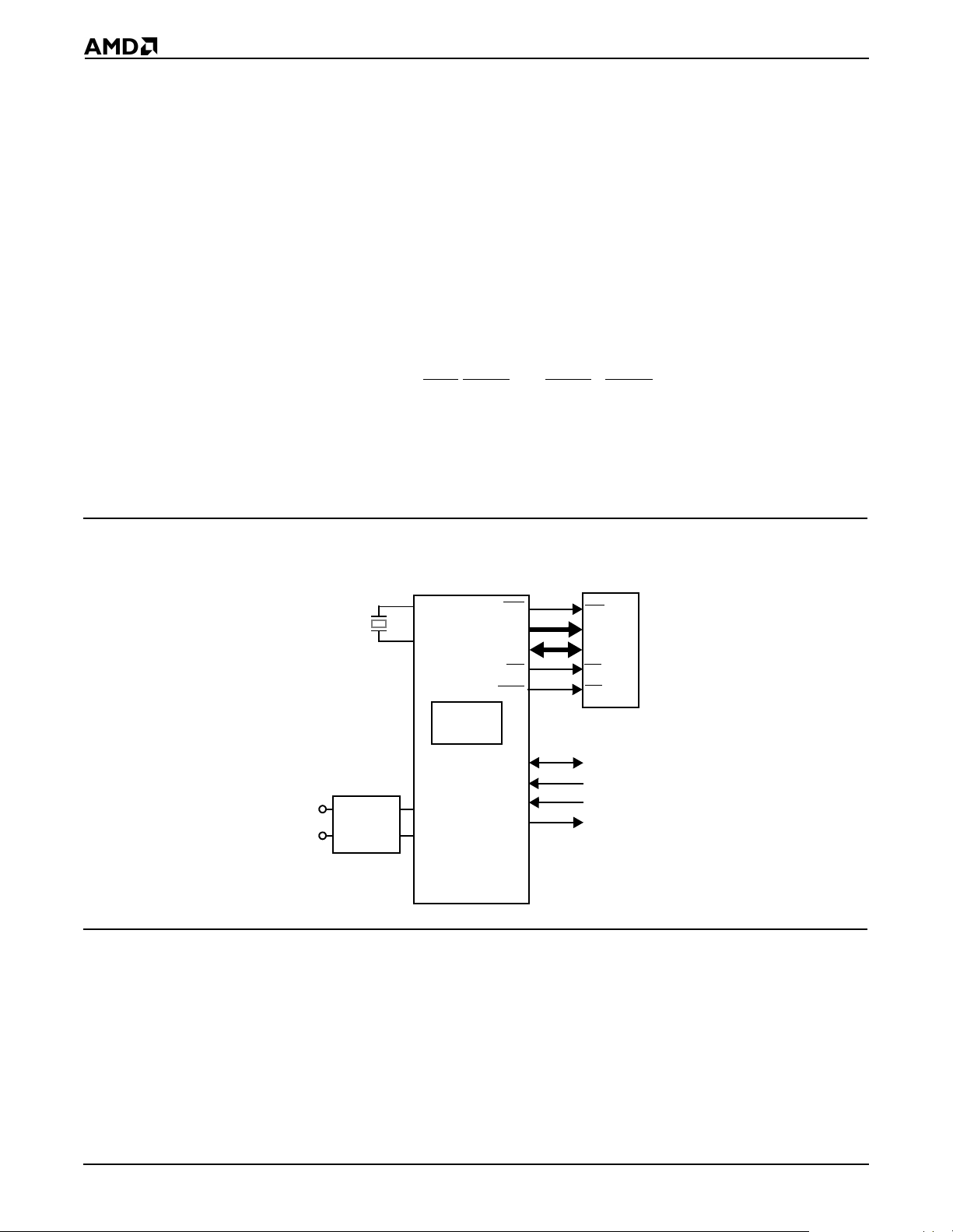

Figure 1-3 illustrates a functi onal sy stem de sig n tha t uses t he integ rat ed peri pheral se t t o

achieve high performance with reduced system cost.

/ADEN and RFSH2/ ADEN pin desc ription s in Chapt er 3,

Figure 1-3 Basic Functional System Design

Am186ER

Microcontroller

10-MHz

Crystal

Serial Port

RS-232

Level

Converter

X2

X1

32 Kbyte

RAM

TXD

RXD

1.3.1 Clock Generation

The integrated PLL clock-generation circuitry of the Am186ER and Am188ER

microcontrollers allows operation at one times or four times t he crystal frequency, in addition

to the one-half frequency operat ion required by 80C186 and 80C188 microc ontrollers. The

design in Figure 1-3 achieves 40-MHz CPU operation with a 10-MHz cryst al.

WR

A19–A0

AD15–AD0

RD

UCS

Timer 0–2

INT4–INT0

DMA 0–1

CLKOUTA

Am29F400

Flash

WE

Address

Data

OE

CS

40 MHz

1-6

The integrated PLL lowers system cost by reducing the cost of the crystal and reduces

electromagnetic interference (EMI ) in the system.

Features and Performance

Page 21

1.3.2 Memory Interface

The integrated memory controller logic of t he Am186ER and Am188ER microcontrollers

provides a direct address bus interface to memory devices. The use of an external address

latch controlled by the address latch enable (ALE) signal is not required.

Individual byte write-enable signals are provided to eliminate the need for external high/

low-byte, write-enable circuitr y. The maximum bank size programmable for the memory

chip-select signals is increased to 512 Kbyte to facil itate the use of high-density memory

devices.

Improved memory timing specifications enable the use of zero-wait-state memories with

70-ns access times at 40-MHz CPU operation. This reduces overall system cost

significantly by allowing the use of commonly available memory devices. The integrated

32-Kbyte RAM operates at the same speed as zero-wait-state external memory.

Figure 1-3 illustrates an Am186ER microcontroller-based configurati on with 512 Kbyte of

external Flash EPROM in addition to the internal 32-Kbyte memory. Addit ional external

RAM can also be added. The external memory interface requires the following:

n The processor A19–A0 bus connects to the memory address inputs.

n The AD bus connects directly to the data inputs/outputs.

n The UCS chip select connects to the memory chip-select input.

External read operations require that the RD

) input pin. External write operati ons require that the byte write enables con nect to the SRAM

(OE

Write Enable (WE

The example design shown in Figure 1-3 uses a 4-Mbit (256-K x 16) external Flash EPROM

for application memory, mapped into the upper region of the microcontroller’s 1-Mbyte

address space at 80000h–FFFFFh. After a valid reset, the Am186ER or Am188ER

microcontroller will fetch the first instruction from address FFFF0h. The user application

can then enable and configure the location of the integrated 32-Kbyte RAM within the

remaining address space ; in this example, it would be at address 00000h to accommodate

the interrupt vector table.

) input pin.

1.3.3 Seri al Communications Port

The integrated universal asynchronous receiver/transmitter (UART) controller in the

Am186ER and Am188ER microcontrollers eliminates the need for external logic to

implement a communications interface. The integrated UART generates the serial clock

from the CPU clock so that no external time-base oscillato r is r equir ed.

Figure 1-3 shows a minimal implementation of an RS-232 console or modem

communications port. The RS-232 to CMOS voltage-level converter is required for the

proper electrical interface with the external device.

The Am186ER and Am188ER microcontrollers al so include a synchronous serial interface.

For more information, see Chapter 11.

output connect s to t he SRAM Out put E nable

Features and Performance

1-7

Page 22

1.4 THIRD-PARTY DEVELOPMENT SUPPORT PRODUCTS

The FusionE86 Program of Partne rships for Applica tion Solut ions p rovid es the cus tomer w ith

an array of prod ucts design ed to meet cri tic al time- to-m arket needs . Produc ts a nd solut ions

available fro m the AMD Fusi onE86 pa rtn ers incl ude emu lators , hardw are and s oftwar e

debuggers, board-level products, and software development tools.

In addition, mature development tools and applications for the x86 platform are widely

available in the general marketplace.

1-8

Features and Performance

Page 23

CHAPTER

PROGRAMMING

2

All members of the Am186 and Am188 family of microcontr ollers, includi ng the Am186ER

and Am188ER, contain the same basic set of registers, instructions, and addressing modes,

and are compatible with the original industry-standard 186/188 parts.

2.1 REGISTER SET

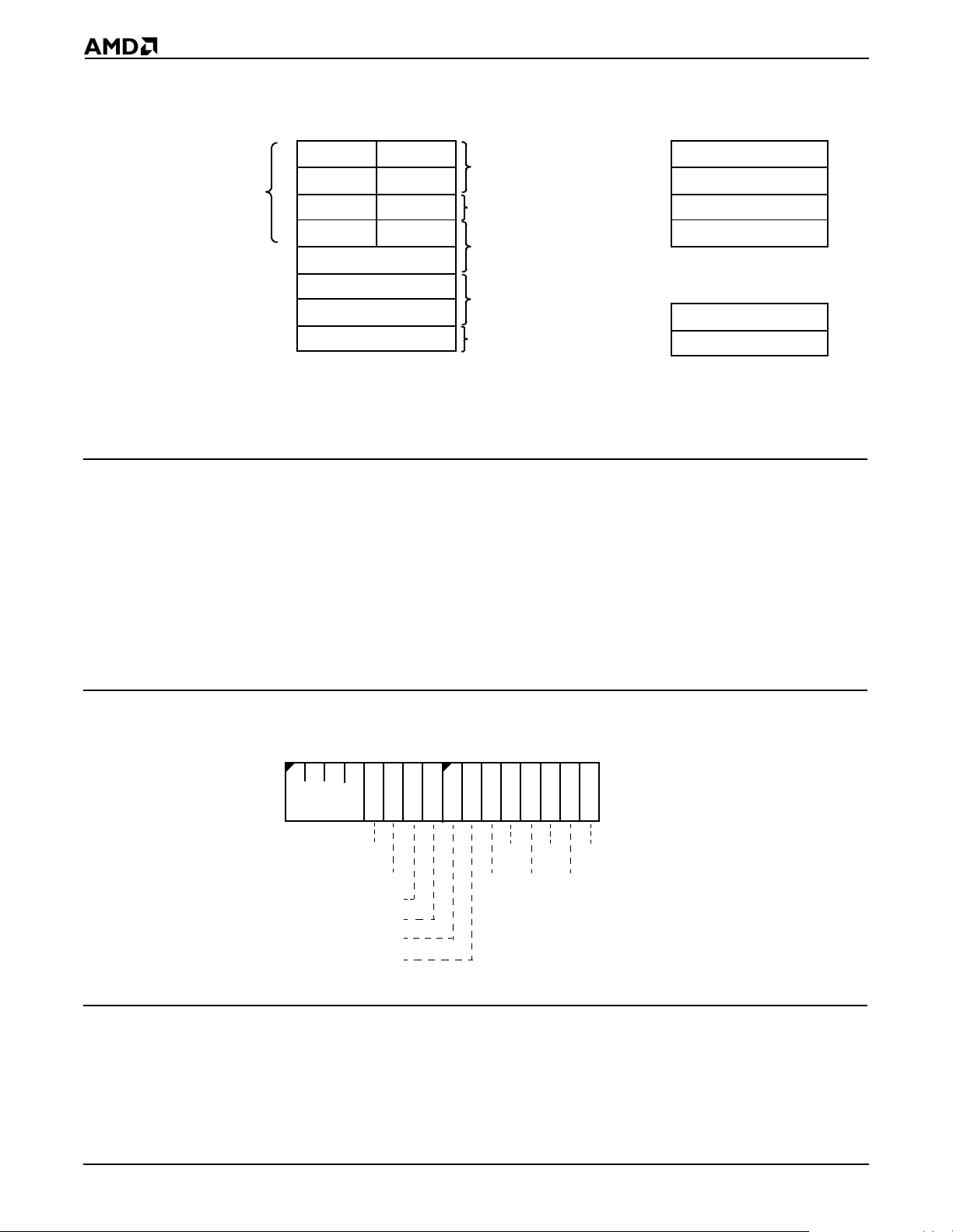

The base architecture of the Am186ER and Am188ER microcontrollers has 14 registers,

as shown in Figure 2-1. These registers are grouped into the following categories:

n General Registers—Eight 16-bit general purpose registers ca n be used for arit hmetic

and logical operands. Four of these ( AX, BX, CX, and DX) can be used as 16-bit registers

or split into pairs of se parate 8-bit register s (AH, AL, BH, BL, CH, CL, DH, an d DL). The

Destination Index (DI) and Source Index (SI) general-purpose registers are used for

data movement and string instructions. The Base Point er (BP) and St ack Pointer (SP)

general-purpose register s are used for the stack segment and poi nt to the bottom and

top of the stack, respectively.

– Base and Index Registers—Four of the general-purpose registers (BP, BX, DI, and

SI) can also be used to determine offset addresses of operands in memory. These

registers can contain base addresses or indexes to part icular locations within a

segment. The addressing mode sel ects the specific registers for operand and addre ss

calculations.

– Stack Pointer Register—All stack operatio ns (POP, POPA, POPF, PUSH, PUSHA,

PUSHF) utilize the stack pointer. The Stack Pointer Register is always offset from the

Stack Segment (SS) Register, and no segment override is allowed.

n Segment Registers—Four 16-bit special-purpose registers (CS, DS, ES, and SS)

select, at any given time, the segments of memory that are immediately addressable

for code (CS), data (DS and ES), and stack (SS) memory. (For usage, refer to sectio n

2.2.)

n Status and Control Registers—Two 16-bit speci al-purpose registers record or alter certain

aspects of the processor state—the Instruction Pointer (IP) Register contains the offset

address of the ne xt s equenti al instru cti on to be ex ecut ed and th e Proc esso r Stat us Flags

(FLAGS) Register contains status and control flag bits (see Figure 2-1 and Figure 2-2).

Note that the Am186ER and Am188ER microcon trollers have additional on-chip per ipheral

registers, which are exter nal to the proc essor. These exter nal register s are not accessibl e

by the instruction set. However, because the processor t reat s these peripheral registers

like memory, instructions that have operands that access memory can also access

peripheral registers. The above processor registers, as well as the additional on-chip

peripheral registers, are described in the chapters that follow.

Programming

2-1

Page 24

Figure 2-1 Register Set

16-Bit

Register Name

Byte

Addressable

(8-Bit

Register

Names

Shown)

7 0 7 0

AX

DX

CX

BX

BP

SI

DI

SP

AH

DH

CH

BH

Base Pointer

Source Index

Destination Index

15 0

General

Registers

AL

DL

CL

BL

Special Register

Functions

Multiply/Divide

I/O Instructions

Loop/Shift/Repeat/Count

Base Registers

Index Registers

Stack Pointer

2.1.1 Processor Status Flags Register

The 16-bit processor Status Flags Register ( Figure 2-2) reco rds specific c haracteristics of

the result of logical and arithmetic instructions (bits 0, 2, 4, 6, 7, and 11) and controls the

operation of the microcontroller within a given operating mode (bits 8, 9, and 10).

16-Bit

Register Name

FLAGS

15 0

CS

DS

SS

ES

Segment Registers

15 0

Processor Status Flags

IP

Instruction Pointer

Status and Control

Code Segment

Data Segment

Stack Segment

Extra Segment

Registers

After an instruction is ex ecuted, the va lue of the f lags may be set ( to 1), cl eared/reset (set

to 0), unchanged, or undefined. The term

execution of the instruction is not preserved, and the value of the flag after the instruction is

executed cannot be predi cted.

Figure 2-2 Processor Statu s Flags Registe r (FLAGS)

15

Reserved

OF

DF

IF

TF

SF

ZF

70

AF

Res

Bits 15–12—Reserved

undefined

PF

Res

Res

means that the fl ag va lue pri or to the

CF

2-2

Bit 11: Overflow Flag (OF)—Set if the signed result cannot be expressed within the number

of bits in the destination operand; cleared o ther wise.

Bit 10: Direction Flag (DF)—Causes string instructions to auto-decrement the appropriate

index registers when set. Clearing DF causes auto-increment.

Programming

Page 25

Bit 9: Interrupt-Enable Flag (IF)—When set, enables maskable interrupts to cause the

CPU to transfer control to a location specified by an interrupt vector .

Bit 8: Trace Flag (TF)—When set, a trace interrupt occurs after instructions execute. TF

is cleared by the t race interr upt after t he processor st atus flags are pushed onto t he stack.

The trace service routine can continue t racing by poppi ng the fl ags back with an int errupt

return (IRET) instruct ion.

Bit 7: Sign Flag (SF)—Set equal to h igh-order bit of r esult (0 if 0 or positive, 1 if negative).

Bit 6: Zero Flag (ZF)—Set if result is 0; clear ed otherwise.

Bit 5: Reserved

Bit 4: Auxiliary Carry (AF)—Set on carry f rom or borrow to the low-or der 4 bits of the AL

general-purpose register; cleared otherwise.

Bit 3: Reserved

Bit 2: Parity Flag (PF)—Set if low-order 8 bi ts of resul t contain an ev en number of 1 bits;

cleared otherwise.

Bit 1: Reserved

Bit 0: Carry Flag (CF)—Set on high-order bit carry or borrow; cleared otherwise.

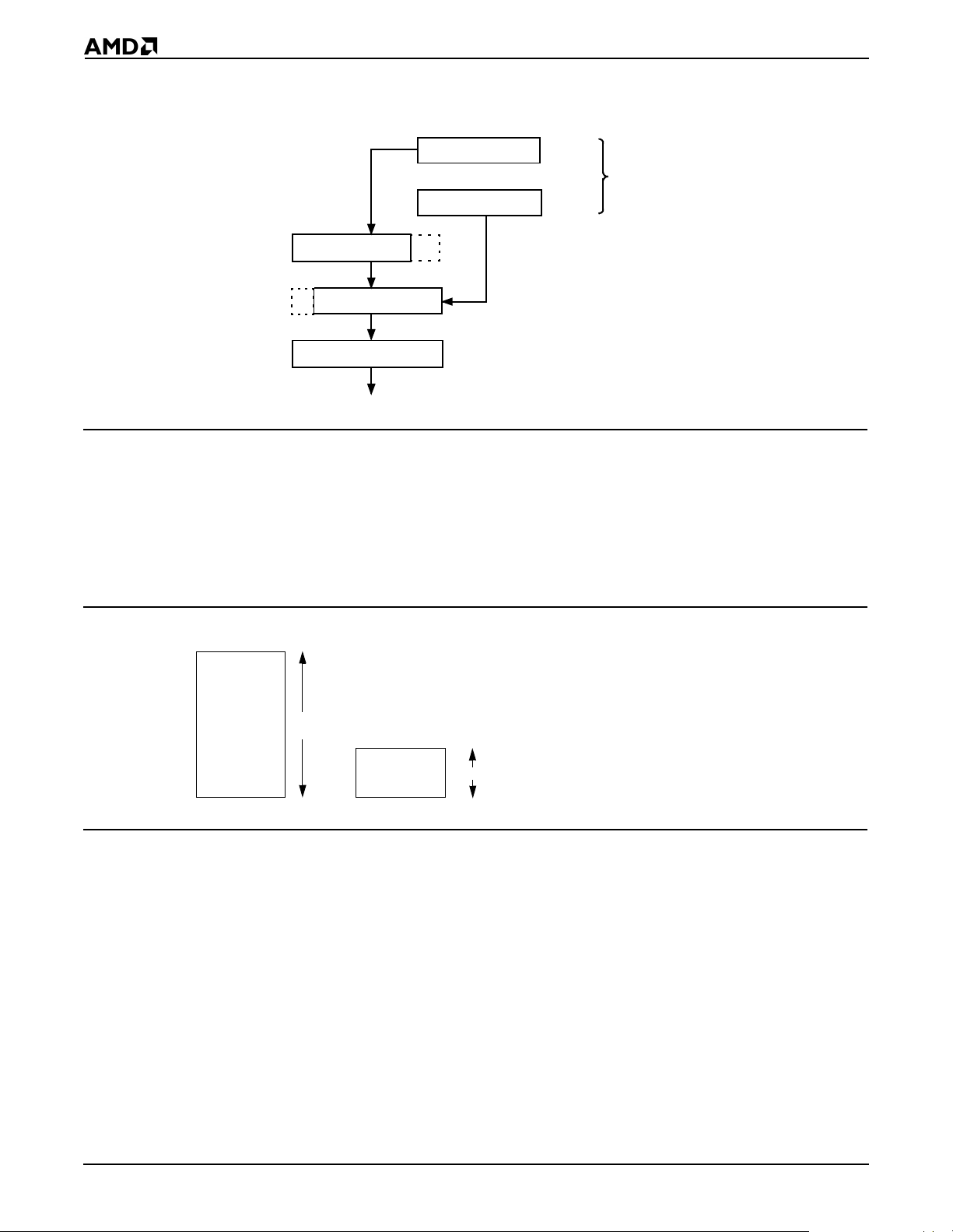

2.2 MEMORY ORGANIZATION AND ADDRESS GENERATION

Memory is organized in sets of segments. Each segment is a linear contiguous sequence

of 64K (2

of a 16-bit segment value and a 16-bit offset. The offset is the number of bytes from the

beginning of the segment (the segment address) to the data or instruction that is being

accessed.

16

) 8-bit bytes. Memory is addressed using a two-component address that consists

The processor forms the physical address of the target location by taking the segment

address, shifting it to the left 4 bits (multi plying by 16), and adding this to the 16-b it offset.

The result is the 20-bit address of the target data or instruction. This allows for a 1-Mbyte

physical address size.

For example, if the segment register is loaded with 12A4h and the offset i s 0022h, the

resultant address is 12A62h (see Figure 2-3). To find the result:

1. The segment register contains 12A4h.

2. The segment register is shifted left 4 places and is now 12A40h.

3. The offset is 0022h.

4. The shifted segment address (12A40h) is added to the offset (00022h) to get 12A62h.

5. This address is placed on the pins of the controller.

All instructions that address operands in memory must specify (implicitly or explicitly) a

16-bit segment value and a 16-bit of fset value. The 16-bit segment values a re con tained i n

one of four int er na l s eg me nt r egi st e rs ( C S, DS , ES , an d SS) . See “Add ress ing Modes” on

page 2-10 for more information on calculating the offset value. See “Segments” on page

2-8 for more information on CS, DS, ES, and SS.

In addition to memory space, all Am186 and Am188 family microcontrollers provide 64K

of I/O space (see Figure 2-4).

Programming

2-3

Page 26

Figure 2-3 Physical Address Generatio n

Shift

Left

4 Bits

1 2 A 4 0

19 0

0 0 0 2 2

15 0

1 2 A 4

15 0

15

0 0 2 2

Segment

Base

Offset

0

Logical

Address

1 2 A 6 2

19 0

To Memory

2.3 I/O SPACE

The I/O space consists of 64K 8-bit or 32K 16-bit port s. The IN and OUT instructions address

the I/O space with either an 8-bit port addr ess specified in the instruction, or a 16-bit port

address in the DX Register. Eight-bit port addresses are zero-extended so that A15–A8

are Low. I/O port addresses 00F8h through 00FFh are reserved. The Am186ER and

Am188ER microcontrollers provide specific instructions for addressing I/O space.

Figure 2-4 Memory an d I/O Space

Memory

Space

1M

I/O

Space

Physical Address

64K

2.4 INSTRUCTION SET

The Am186ER and Am188ER microcontrollers use the same instruction set as the 80C186

microcontroller. An instruct ion can reference from zero to several operands. An operand

can reside in a register , in the inst ruction itself, or in memory. Specif ic operand addressi ng

modes are discussed on page 2-10.

Table 2-1 lists the instructions for the Am1 86ER and Am188ER microcont rollers in

alphabetical order.

#21267, provides detailed information on the format and function of the following

instructions.

2-4

The Am186™ and Am188™ Family Instruction Set Manual

, order

Programming

Page 27

Table 2-1 Instruction Set

Mnemonic Instruction Name

AAA ASCII adjust for addition

AAD ASCII adjust for division

AAM ASCII adjust for multiplication

AAS ASCII adjust for subtraction

ADC Add byte or word with carry

ADD Add byte or word

AND Logical AND byte or word

BOUND Detects values outside prescribed range

CALL Call procedure

CBW Convert byte to word

CLC Clear carry flag

CLD Clear direction flag

CLI Clear interrupt-enable flag

CMC Complement carry flag

CMP Compare byte or word

CMPS Compare byte or word string

CWD Convert word to doubleword

DAA Decimal adjust for addition

DAS Decimal adjust for subtraction

DEC Decrement byte or word by 1

DIV Divide byte or word unsigned

ENTER Format stack for procedure entry

ESC Escape to extension processor

HLT Halt until interrupt or reset

IDIV Integer divide byte or word

IMUL Integer multiply byte or word

IN Input byte or word

INC Increment byte or word by 1

INS Input bytes or word string

INT Interrupt

INTO Interrupt if overflow

IRET Interrupt return

JA/JNBE Jump if above/not below or equal

JAE/JNB Jump if above or equal/not below

Programming

2-5

Page 28

Mnemonic Instruction Name

JB/JNAE Jump if below/not above or equal

JBE/JNA Jump if below or equal/not above

JC Jump if carry

JCXZ Jump if register CX = 0

JE/JZ Jump if equal/zero

JG/JNLE Jump if greater/not less or equal

JGE/JNL Jump if greater or equal/not less

JL/JNGE Jump if less/not greater or equal

JLE/JNG Jump if less or equal/not greater

JMP Jump

JNC Jump if not carry

JNE/JNZ Jump if not equal/not zero

JNO Jump if not overflow

JNP/JPO Jump if not parity/parity odd

JNS Jump if not sign

JO Jump if overflow

JP/JPE Jump if parity/parity even

JS Jump if sign

LAHF Load AH register from flags

LDS Load pointer using DS

LEA Load effective address

LEAVE Restore stack for procedure exit

LES Load pointer using ES

LOCK Lock bus during next instruction

LODS Load byte or word string

LOOP Loop

LOOPE/

LOOPZ

LOOPNE/

LOOPNZ

MOV Move byte or word

Loop if equal/zero

Loop if not equal/not zero

2-6

MOVS Move byte or word string

MUL Multiply byte or word unsigned

NEG Negate byte or word

NOP No operation

NOT Logical NOT byte or word

Programming

Page 29

Mnemonic Instruction Name

OR Logical inclusive OR byte or word

OUT Output byte or word

POP Pop word off stack

POPA Pop all general register off stack

POPF Pop flags off stack

PUSH Push word onto stack

PUSHA Push all general registers onto stack

PUSHF Push flags onto stack

RCL Rotate left through carry byte or word

RCR Rotate right through carry byte or word

REP Repeat

REPE/REPZ Repeat while equal/zero

REPNE/

REPNZ

RET0 Return from procedure

ROL Rotate left byte or word

ROR Rotate right byte or word

SAHF Store AH register in flags SF, ZF, AF, PF, and CF

SAL Shift left arithmetic byte or word

SAR Shift right arithmetic byte or word

SBB Subtract byte or word with borrow

SCAS Scan byte or word string

SHL Shift left logical byte or word

SHR Shift right logical byte or word

STC Set carry flag

STD Set direction flag

STI Set interrupt-enable flag

STOS Store byte or word string

Repeat while not equal/not zero

SUB Subtract byte or word

TEST Test (logical AND, flags only set) byte or word

XCHG Exchange byte or word

XLAT Translate byte

XOR Logical exclusive OR byte or word

Programming

2-7

Page 30

2.5 SEGMENTS

The Am186ER and Am188ER microcontrollers use four segment registers:

1. Data Segment (DS): The processor assumes that all accesses to the program’s

variables are from the 64K space pointed to by the DS Register. The data segment holds

data, operands, etc.

2. Code Segment (CS): This 64K space is the default locati on for all instruct ions. All code

must be executed from the code segment.

3. Stack Segment (SS): The processor uses the SS Register to perform operations that

involve the stack, such as pushes and pops. The st ack segment i s used for t emporar y

space.

4. Extra Segment (ES): Usually this segment is used for large string operati ons and for

large data structures. Certain str ing i n structions assume the extra segment as the

segment portion of the address. The extra segment is also used (by using segment

override) as a spare data segment.

When a segment is not defined for a data movement instruc tion, it’s assumed to be a data

segment. An instruction prefix can be used to override the segment register. For speed

and compact instruction encoding, the segment register used for physical address

generation is implied by the addressing mode used (see Table 2-2).

Table 2-2 Segment Regist er Selection Rules

Memory Reference

Needed

Local Data Data (DS) All data references

Instructions Code (CS) Instructions (including immedi ate data)

Stack Stack (SS) All stack pushes and pops

External Data (Global) Extra (ES) All string instruc tion references that use the DI Regi s-

Segment Register

Used

2.6 DATA TYPES

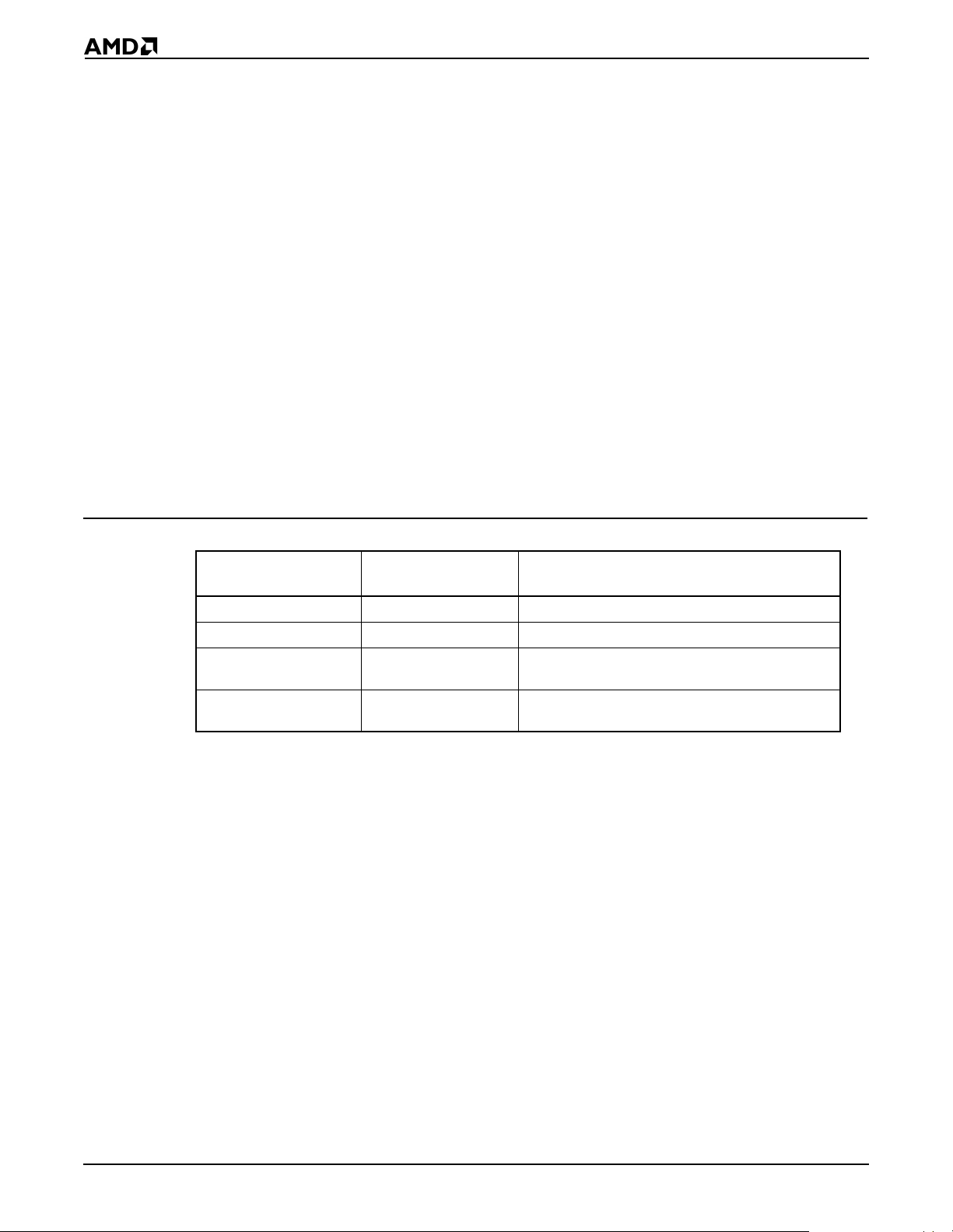

The Am186ER and Am188ER microcontrollers directly support the following data types:

n Integer—A signed binary numeric value contained in an 8-bit byte or a 16-bit word. All

operations assume a two’s complement representation.

n Ordinal—An unsigned binary numeric value contained in an 8-bit byt e or a 16-bit wor d.

n Double Word—A signed binary numeric value contained in two sequential 16-bit

addresses, or in a DX::AX register pair.

n Quad Word—A signed binary numeric value contained in four sequential 16-bit

addresses.

Implicit Segment Selection Rule

Any memory references that use the BP Reg ister

ter as an index

2-8

n Binary-Coded Decimal (BCD)—An unpacked byte representation of the decimal

digits 0–9.

n ASCII—A byte representation of alphanumeric and c ontr ol char acters usi ng the ASCII

standard of character representation.

n Packed BCD—A packed byte representation of two decimal digits (0–9). One digit is

stored in each nibble (4 bits) of the byte.

Programming

Page 31

n String—A contiguous sequence of bytes or words. A string can contain fr om 1 byte up

to 64 Kbyte.

n Pointer—A 16-bit or 32-bit quantity, composed of a 16-bi t offset component or a 16-bi t

segment base component plus a 16-bit offset component.

In general, individual data elements must fit within defined segment limits. Figure 2-5

graphically represents the data types supported by the Am186ER and Am188ER

microcontrollers.

Figure 2-5 Supported Data Types

Signed

Byte

Sign Bit

Unsigned

Byte

Signed

Word

Sign Bit

Signed

Double

Word

Sign Bit

Signed

Quad

Word

Sign Bit

Unsigned

Word

7 0

Magnitude

7 0

MSB

Magnitude

+1 0

1514 8 7 0

MSB

Magnitude

+3

31 1615 0

+2

+1 0

MSB

Magnitude

63 48 47 32 31 1615 0

+3 +2 +1+6 +5 +4 +0+7

MSB

Magnitude

+1 0

015

MSB

Magnitude

Binary

Coded

Decimal

(BCD)

ASCII

Packed

BCD

String

Pointer

+N +1 0

7 0 7 0 7 0

BCD

Digit N

7 0 7 0 7 0

. . .

BCD

Digit 1

+N +1 0

BCD

Digit 0

. . .

ASCII

Character

7 0 7 0 7 0

N

+N +1 0

ASCII

Character

ASCII

Character

1

0

. . .

Most Significant

Digit

+N

70

. . .

Significant Digit

+1 0

7 0 7 0

Least

Byte/WordN Byte/Word1 Byte/Word0

+3 +2 +1 0

Segment Base Offset

Programming

2-9

Page 32

2.7 ADDRESSING MODES

The Am186ER and Am188ER microcontrollers u se eight categori es of addressing modes

to specify operands. Two addressing modes are provided for i nstruct ions that operate o n

register or immediate operands; six modes are provided to specify the location of an

operand in a memory segment.

Register and Immediate Operands

n Register Operand Mode—The operand is located in one of the 8- or 16-bit registers.

n Immediate Operand Mode—The operand is included in the instruction.

Memory Operands

A memory-operand address consists of two 16-bit components: a segment value and an

offset. The segment value is supplied by a 16-bit segme nt register either i mplicitly chosen