Page 1

SDI II IP Core User Guide

Last updated for Altera Complete Design Suite: 15.0

Subscribe

Send Feedback

UG-01125

2015.05.04

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Contents

SDI II IP Core Quick Reference..........................................................................1-1

SDI II IP Core Overview......................................................................................2-1

SDI II IP Core Getting Started............................................................................3-1

General Description.....................................................................................................................................2-1

SMPTE372 Dual Link Support.......................................................................................................2-2

SMPTE RP168 Switching Support.................................................................................................2-6

SD 20-Bit Interface for Dual/Triple Standard..............................................................................2-6

Dynamic TX Clock Switching........................................................................................................2-7

Resource Utilization.................................................................................................................................... 2-9

Installation and Licensing...........................................................................................................................3-1

Design Walkthrough................................................................................................................................... 3-1

Creating a New Quartus II Project................................................................................................3-2

Launching IP Catalog......................................................................................................................3-2

Parameterizing the IP Core............................................................................................................ 3-3

Generating a Design Example and Simulation Testbench.........................................................3-3

Simulating the SDI II IP Core Design...........................................................................................3-3

Compiling the SDI II IP Core Design.......................................................................................................3-4

Programming an FPGA Device................................................................................................................. 3-5

Design Reference..........................................................................................................................................3-5

SDI II IP Core Parameters..............................................................................................................3-6

SDI II IP Core Component Files....................................................................................................3-9

Design Examples..............................................................................................................................3-9

Video Pattern Generator Signals................................................................................................. 3-22

Transceiver Reconfiguration Controller Signals.......................................................................3-23

Reconfiguration Management Parameters.................................................................................3-26

Reconfiguration Router Signals...................................................................................................3-27

SDI II IP Core Functional Description...............................................................4-1

Altera Corporation

Protocol......................................................................................................................................................... 4-2

Transmitter.......................................................................................................................................4-2

Receiver............................................................................................................................................. 4-6

Transceiver..................................................................................................................................................4-12

Submodules.................................................................................................................................................4-14

Insert Line.......................................................................................................................................4-14

Insert/Check CRC..........................................................................................................................4-15

Insert Payload ID........................................................................................................................... 4-15

Match TRS...................................................................................................................................... 4-17

Scrambler........................................................................................................................................ 4-17

Page 3

TOC-3

TX Sample.......................................................................................................................................4-18

Clock Enable Generator................................................................................................................4-18

RX Sample.......................................................................................................................................4-19

Detect Video Standard..................................................................................................................4-21

Detect 1 and 1/1.001 Rates............................................................................................................4-21

Transceiver Controller..................................................................................................................4-21

Descrambler....................................................................................................................................4-22

TRS Aligner.....................................................................................................................................4-23

3Gb Demux.....................................................................................................................................4-24

Extract Line.....................................................................................................................................4-24

Extract Payload ID.........................................................................................................................4-24

Detect Format.................................................................................................................................4-24

Sync Streams...................................................................................................................................4-25

Convert SD Bits..............................................................................................................................4-26

Insert Sync Bits...............................................................................................................................4-26

Clocking Scheme........................................................................................................................................4-27

SDI II IP Core Signals................................................................................................................................4-27

Additional Information......................................................................................A-1

Document Revision History......................................................................................................................A-1

Altera Corporation

Page 4

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI II IP Core Quick Reference

1

UG-01125

Subscribe

Send Feedback

The Altera® Serial Digital Interface (SDI) II MegaCore® function is the next generation SDI intellectual

property (IP).

The SDI II IP core is part of the MegaCore IP Library, which is distributed with the Quartus® II software

and downloadable from the Altera website at www.altera.com.

Note:

For system requirements and installation instructions, refer to Altera Software Installation &

Licensing.

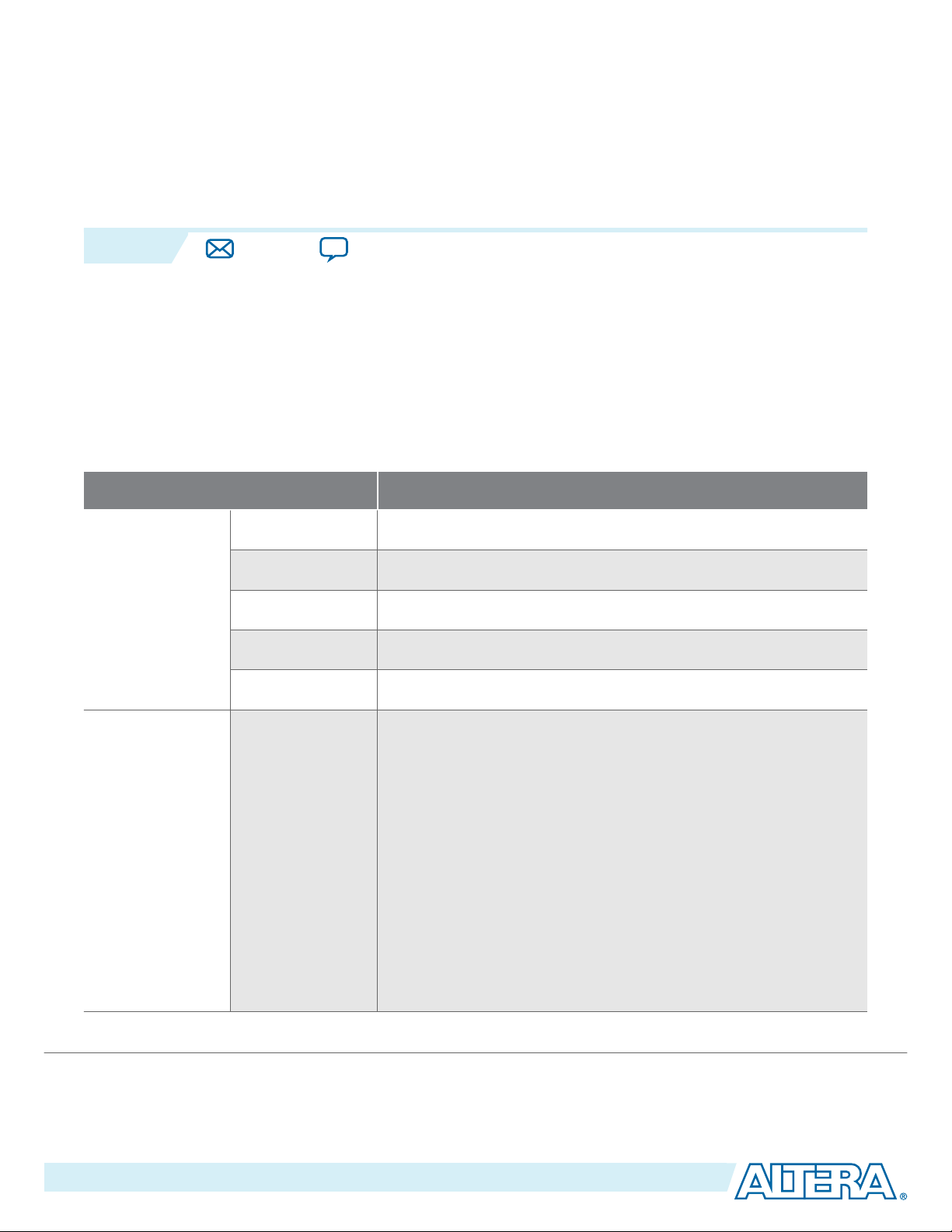

Table 1-1: Brief Information About the SDI II IP Core

Item Description

Version 15.0

Release Date May 2015

Release

Information

Ordering Code IP-SDI-II

Product ID(s) 0111

Vendor ID 6AF7

SDI Data Rate

Support

• 270-Mbps SD-SDI, as defined by SMPTE259M specification

• 1.485-Gbps or 1.4835-Gbps HD-SDI, as defined by

SMPTE292M specification

• 2.97-Gbps or 2.967-Gbps 3G-SDI, as defined by SMPTE424M

specification

• 5.94-Gbps or 5.934-Gbps 6G-SDI, as defined by SMPTEST2081

IP Core

Information

specification

• 11.88-Gbps or 11.868-Gbps 12G-SDI, as defined by

SMPTEST2082 specification

• Dual link HD-SDI, as defined by SMPTE372M specification

• Dual standard support for SD-SDI and HD-SDI

• Triple standard support for SD-SDI, HD-SDI, and 3G-SDI

• Multi standard support for SD-SDI, HD-SDI, 3G-SDI, 6G-SDI,

and 12G-SDI

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 5

1-2

SDI II IP Core Quick Reference

Item Description

Features • 20-bit interface support for SD-SDI

UG-01125

2015.05.04

• Multiple SDI standards and video formats

• Payload identification packet insertion and extraction

• Clock enable generator

• Video rate detection

• Cyclical redundancy check (CRC) encoding and decoding

(except SD)

• Line number (LN) insertion and extraction (except SD)

• Word scrambling and descrambling

• Word alignment

• Framing and extraction of video timing signals

• Dual link data stream synchronization (except SD)

• Transceiver dynamic reconfiguration

• RP168 support for synchronous video switching

• Dynamic TX clock switching

• OpenCore Plus evaluation

• SMPTE425M level A support (direct source image formatting)

• SMPTE425M level B support (dual link mapping)

Application • Digital video equipment

• Mixing and recording equipment

Device Family

Support

Arria® 10 (preliminary), Arria V GX, Arria V GZ, Cyclone® V,

and Stratix® V FPGA device families.

Refer to the device support table and What’s New in Altera page of

the Altera website for detailed information.

Design Tools • IP Catalog in the Quartus II software for design creation and

compilation

• ModelSim®-Altera, Riviera-Pro, and VCS/VCS MX software

for design simulation or synthesis

Related Information

• Altera Software Installation and Licensing

• What's New in Altera IP

Altera Corporation

SDI II IP Core Quick Reference

Send Feedback

Page 6

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI II IP Core Overview

2

UG-01125

Subscribe

Send Feedback

The SDI II IP core implements a transmitter, receiver, or full-duplex SDI at standard definition (SD), high

definition (HD), or 3 gigabits per second (3G) to 12G rate as defined by the Society of Motion Picture and

Television Engineers (SMPTE). The SDI II IP core supports dual standard (SD-SDI and HD-SDI), triple

standard (SD-SDI, HD-SDI, and 3G-SDI) and multi standard (SD-SDI, HD-SDI, 3G-SDI, 6G-SDI, and

12G-SDI). These modes provide automatic receiver rate detection and transceiver dynamic reconfigura‐

tion.

The SDI II IP core highlights the following new features:

• Supports 28 nm devices and beyond.

• Arria V GX and Stratix V from Quartus II version 12.1 onwards

• Arria V GZ and Cyclone V from Quartus II version 13.0 onwards

• Arria 10 from Quartus II version 14.0A10 onwards

• Improved integration with Altera tools (hw.tcl).

• IEEE encryption for functional simulation.

• Dynamic generation of user simulation testbench that matches the IP configuration.

• Dynamic generation of design example that serves as common entity for simulation and hardware

verification.

General Description

The SMPTE defines a SDI standard that is widely used as an interconnect between equipment in video

production facilities. The SDI II IP core can handle the following SDI data rates:

• 270 megabits per second (Mbps) SD-SDI, as defined by SMPTE259M-1997 10-Bit 4:2:2 Component

Serial Digital Interface

• 1.485 gigabits per second (Gbps) or 1.4835-Gbps HD-SDI, as defined by SMPTE292M-1998 Bit-Serial

Digital Interface for High Definition Television Systems

• 2.97-Gbps or 2.967-Gbps 3G SDI, as defined by SMPTE424M

• 5.94-Gbps or 5.934-Gbps 6G-SDI, as defined by SMPTEST2081

• 11.88-Gbps or 11.868-Gbps 12G-SDI, as defined by SMPTEST2082

• Dual link HD-SDI, as defined by SMPTE372M-Dual Link 1.5Gb/s Digital Interface for 1920×1080 and

2048×1080 Picture Formats

• Dual standard support for SD-SDI and HD-SDI

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 7

2-2

SMPTE372 Dual Link Support

• Triple standard support for SD-SDI, HD-SDI, and 3G-SDI

• Multi standard support for SD-SDI, HD-SDI, 3G-SDI, 6G-SDI, and 12G-SDI

• SMPTE425M level A support (direct source image formatting)

• SMPTE425M level B support (dual link mapping)

• SMPTE RP168 switching support

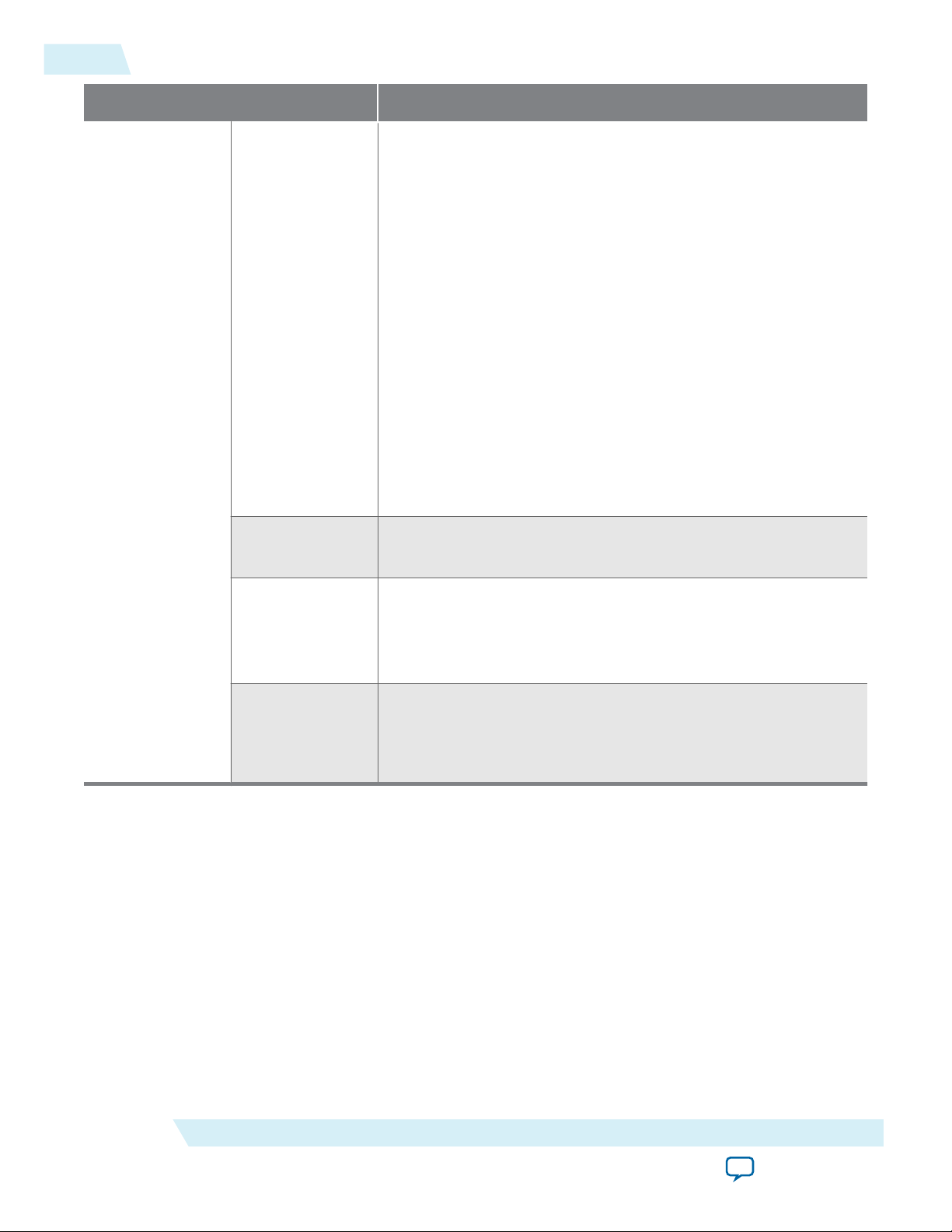

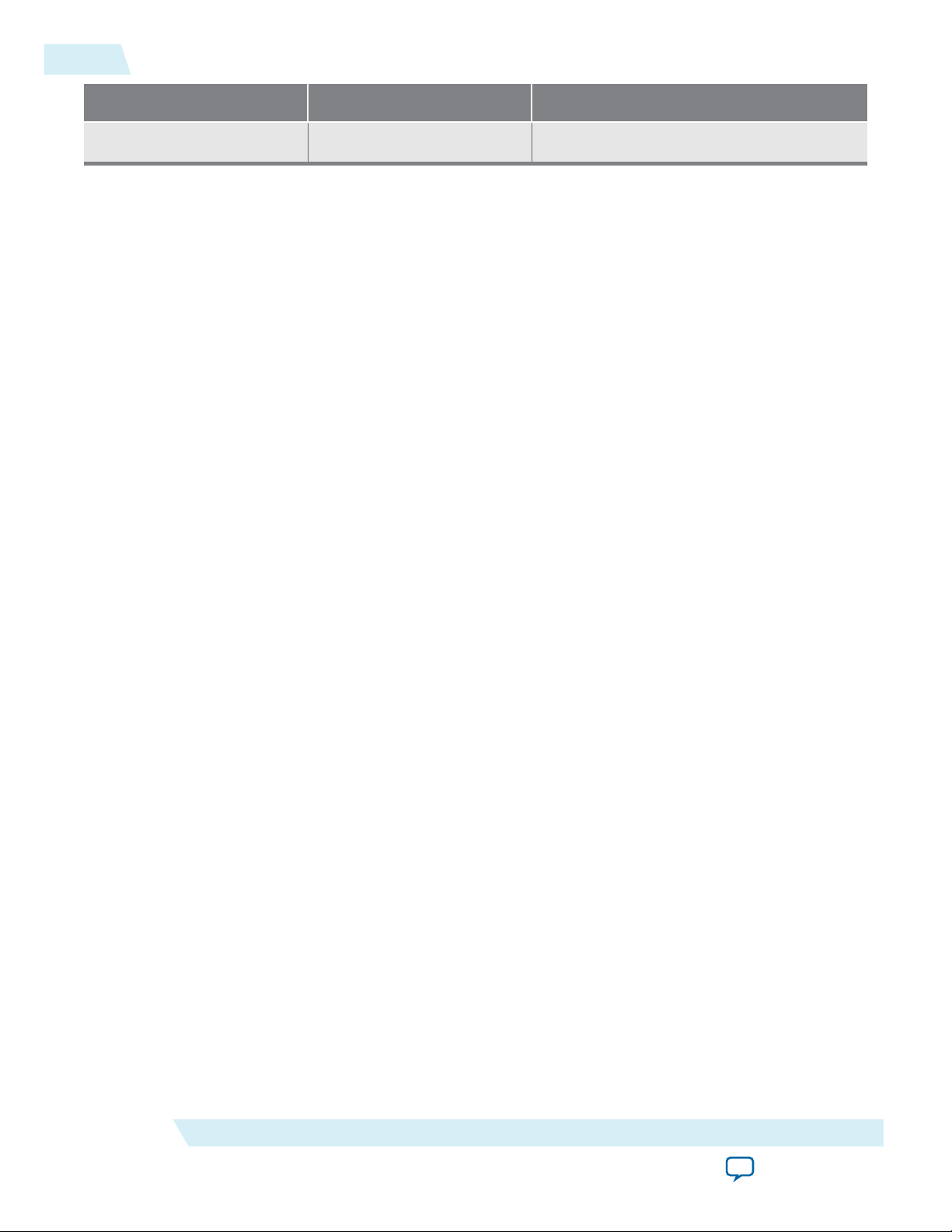

Table 2-1: SDI Standard Support

Table below lists the SDI standard support for various FPGA devices.

SDI Standard

Single Standard Multiple Standards

Device Family

SD-SDI HD-SDI 3G-SDI Dual Link

HD-SDI

Dual

Standard

(up to HD)

Triple

Standard

(up to 3G)

UG-01125

2015.05.04

Multi Standard

(up to 12G)

Arria V

Yes Yes Yes Yes Yes Yes No

GX

Arria V

Yes Yes Yes Yes Yes Yes No

GZ

Stratix V Yes Yes Yes Yes Yes Yes No

Cyclone V Yes Yes Yes Yes Yes Yes No

Arria 10 No Yes Yes Yes No Yes Yes

SMPTE372 Dual Link Support

Recording studios support HD 1080p format by using a dual-link connection (SMPTE372) from cameras

to the mixing and recording equipment. The SMPTE 372 specification defines a way of interconnecting

digital video equipment with a dual link HD-SDI, based upon the SMPTE292 specification data structure.

The total data rate of the dual link connection is 2.97 Gbps or 2.97/1.001 Gbps.

HD-SDI Dual Link to 3G-SDI (Level B) Conversion

To interface between a HD-SDI dual link receiver and 3G-SDI single link transmitter equipment, perform

a HD-SDI dual link to 3G-SDI (level B) conversion. Level B is defined as 2× SMPTE292 HD-SDI

mapping, including SMPTE372 dual link mapping.

This conversion takes either two 1.485 Gbps dual link signals or two separate co-timed HD signals and

combines them into a single 3G-SDI stream.

Altera Corporation

SDI II IP Core Overview

Send Feedback

Page 8

3FFh(C1)

3FFh(Y1)

000h(C1)

000h(Y1)

XYZ(C1)

XYZ(Y1)

LN0(C1)

LN0(Y1)

LN1(C1)

LN1(Y1)

3FFh(C2)

3FFh(Y2)

000h(C2)

000h(Y2)

XYZ(C2)

XYZ(Y2)

LN0(C2)

LN0(Y2)

LN1(C2)

LN1(Y2)

000h(C1)

000h(Y1)

000h(C2)

000h(Y2)

Multiplexing

Data Stream 1

Data Stream 2

3G-SDI Level B

Interleaved Stream

3FFh(C2)

3FFh(C1)

3FFh(Y2)

3FFh(Y1)

000h(C2)

000h(C1)

000h(Y2)

000h(Y1)

XYZ(C2)

XYZ(C1)

XYZ(Y2)

XYZ(Y1)

LN0(C2)

LN0(C1)

LN0(Y2)

LN0(Y1)

LN1(C2)

LN1(C1)

LN1(Y2)

LN1(Y1)

UG-01125

2015.05.04

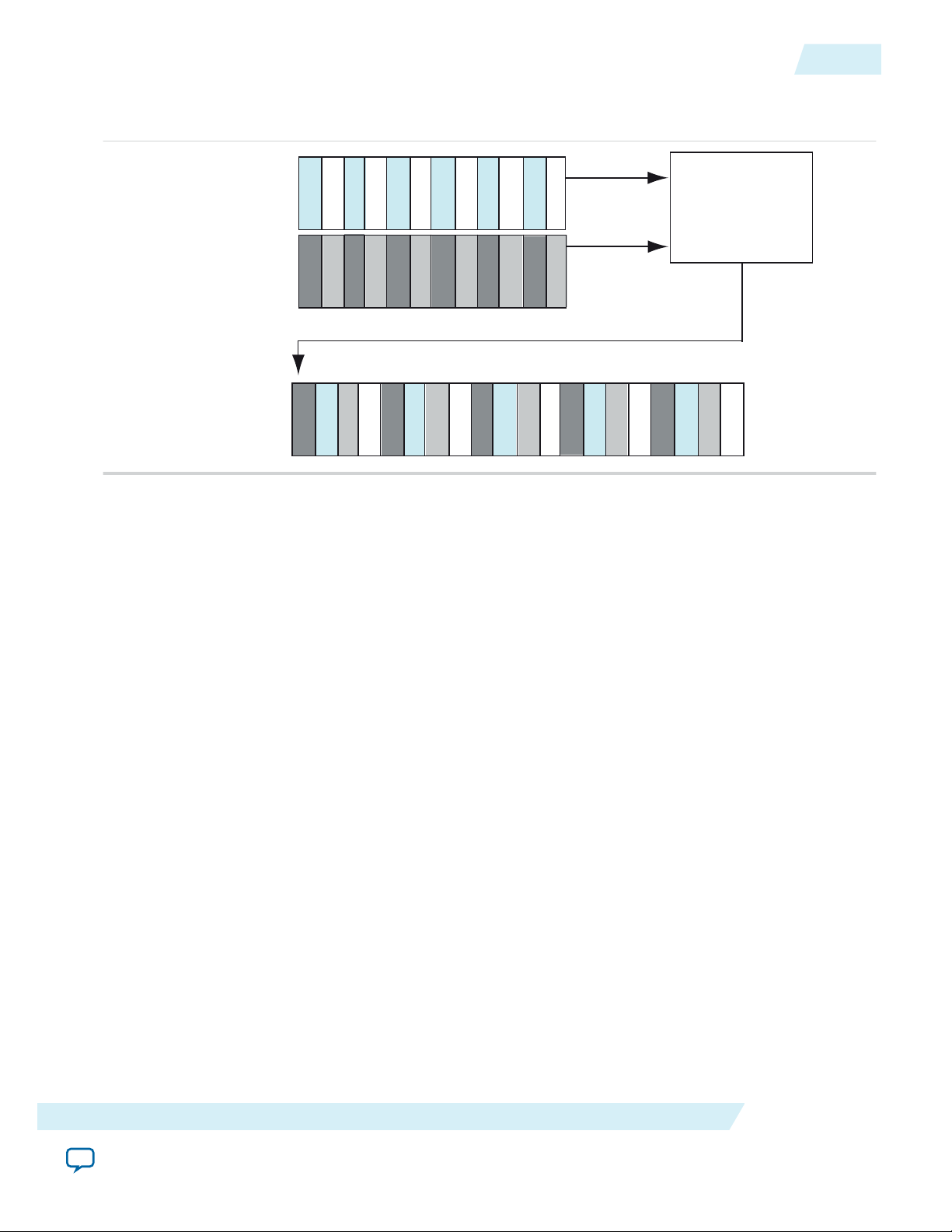

HD-SDI Dual Link to 3G-SDI (Level B) Conversion

Figure 2-1: Example of HD-SDI Dual Link to 3G-SDI (Level B) Conversion

The figure shows the conversion of two HD-SDI data streams to 3G-SDI (level B) data streams.

2-3

SDI II IP Core Overview

Send Feedback

Altera Corporation

Page 9

Transceiver

HD Link A

Protocol FIFO

rxdataA rxdataA rdreq

Transceiver

HD Link B

Protocol FIFO

rxdataB rxdataB

rdreq

Divide

Clock

rx_clkin_smpte372

(148.5 MHz or 148.35 MHz)

rx_dataout[19:0]

rdclk_3gb_div2 =

1H1L1H1L

xcvr_refclk (74.25 MHz or 74.175 MHz)

rx_clkout

(74.25 MHz or 74.175 MHz)

rx_clkout_b

(74.25 MHz or 74.175 MHz)

Sync Stream

HD Dual-Link Receiver

Y1 Y1 Y1 Y1

C1 C1 C1 C1

Y2 Y2 Y2 Y2

C2 C2 C2 C2

rx_clkout

rxdataA[19:10]

rxdataA[9:0]

rx_clkout_b

rxdataB[19:10]

rxdataB[9:0]

rx_clkin_smpte372

rdclk_3gb_div2

rx_dataout[19:10]

rx_dataout[9:0]

C1 C1 C1 C1Y1 Y1 Y1 Y1

C2 C2 C2 C2Y2 Y2 Y2 Y2

2-4

3G-SDI (Level B) to HD-SDI Dual Link Conversion

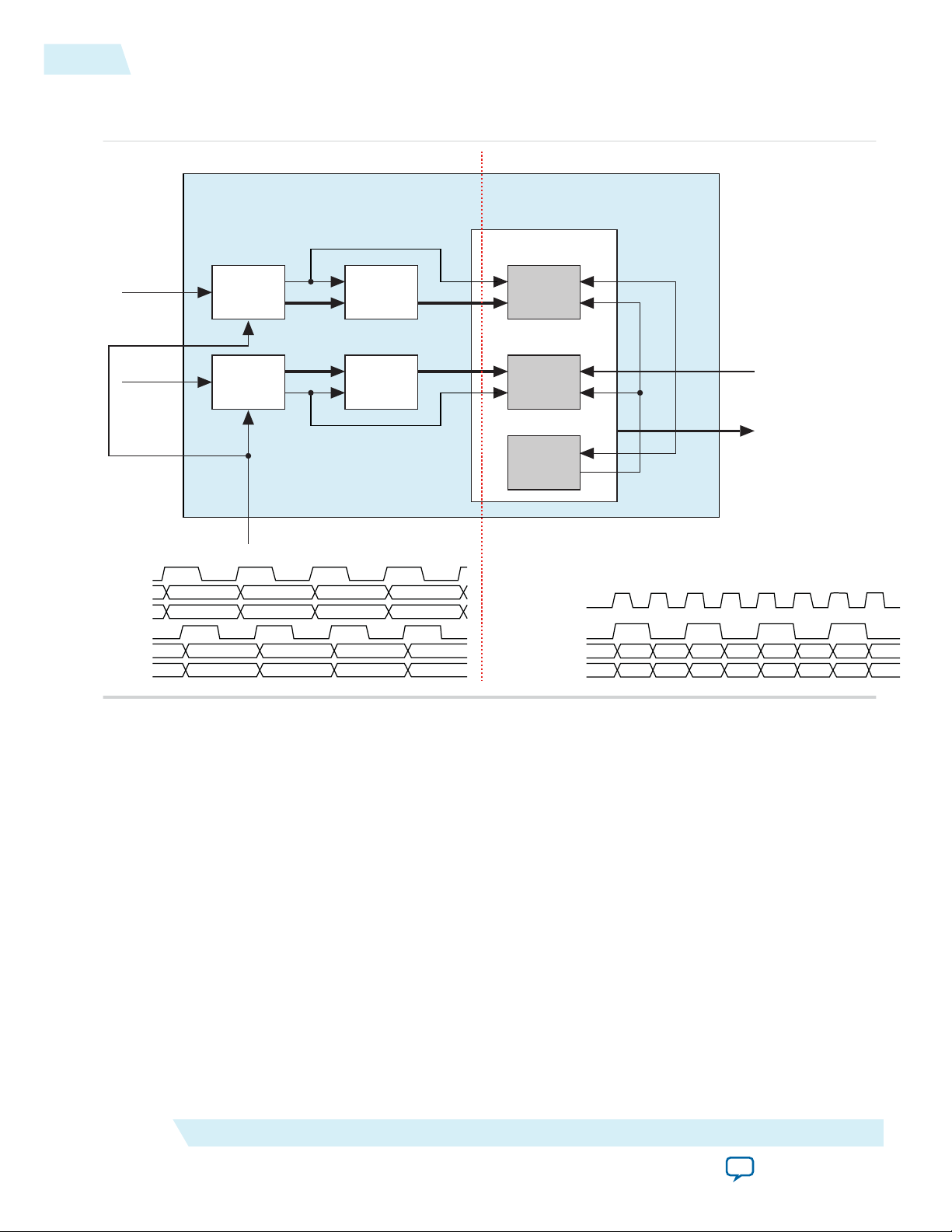

Figure 2-2: Implementation of HD-SDI Dual Link to 3G-SDI (Level B) Conversion

The figure shows a block diagram of HD-SDI dual link to 3G-SDI (level B) conversion.

UG-01125

2015.05.04

Altera Corporation

3G-SDI (Level B) to HD-SDI Dual Link Conversion

To interface between 3-Gbps single link receiver and HD-SDI dual link transmitter equipment, perform a

3G-SDI (level B) to HD-SDI dual link conversion. This conversion takes a single 3G-SDI signal and

separates the signal into two 1.485 Gbps signals, which can either be a dual link 1080p signal or two

separate co-timed HD data streams.

SDI II IP Core Overview

Send Feedback

Page 10

3FFh(C2)

Demux

3FFh(C1)

3FFh(Y2)

3FFh(Y1)

000h(C2)

000h(C1)

000h(Y2)

000h(Y1)

XYZ(C2)

XYZ(C1)

XYZ(Y2)

XYZ(Y1)

LN0(C2)

LN0(C1)

LN0(Y2)

LN0(Y1)

LN1(C2)

LN1(C1)

LN1(Y2)

LN1(Y1)

3FFh(C1)

3FFh(Y1)

000h(C1)

000h(Y1)

XYZ(C1)

XYZ(Y1)

LN0(C1)

LN0(Y1)

LN1(C1)

LN1(Y1)

3FFh(C2)

3FFh(Y2)

000h(C2)

000h(Y2)

XYZ(C2)

XYZ(Y2)

LN0(C2)

LN0(Y2)

LN1(C2)

LN1(Y2)

000h(C1)

000h(Y1)

000h(C2)

000h(Y2)

3G-SDI Level B Interleaved Stream

Data Stream 1

HD-SDI Link A (10-bit)

HD-SDI Link B (10-bit)

Data Stream 2

Transceiver

3-GB Signal

Protocol

3-GB

Demux

rxdata

rx_clkin_smpte372

(74.25 MHz or 74.175 MHz)

rx_dataout[19:0]

rdclk_3gb_div2 =

1H1L1H1L

xcvr_refclk (148.5 MHz or 148.35 MHz)

rx_clkout

(148.5 MHz or 148.35 MHz)

FIFO

rx_dataout_b[19:0]

rx_dataout[19:0]

rx_dataout_b[19:0]

wrreq

rxdata[19:0]

rx_trs

3-GB Receiver

rx_clkout

rx_trs

rxdata[19:10]

rxdata[9:0]

C1 C1 C1 C1Y1 Y1 Y1 Y1

C2 C2 C2 C2Y2 Y2 Y2 Y2

Y1 Y1 Y1 Y1

C1 C1 C1 C1

Y2 Y2 Y2 Y2

C2 C2 C2 C2

rx_clkin_smpte372

rx_dataout[19:10]

rx_dataout[9:0]

rx_clkdiv2

rx_dataout_b[19:10]

rx_dataout_b[9:0]

rx_clkout

rx_trs

UG-01125

2015.05.04

3G-SDI (Level B) to HD-SDI Dual Link Conversion

Figure 2-3: Example of 3G-SDI (Level B) to HD-SDI Dual Link Conversion

The figure shows the conversion of 3G-SDI (level B) data to two HD-SDI data streams.

Figure 2-4: Implementation of 3G-SDI (Level B) to HD-SDI Dual Link Conversion

2-5

The figure shows a block diagram of 3G-SDI (level B) to HD-SDI dual link conversion.

SDI II IP Core Overview

Send Feedback

Altera Corporation

Page 11

rx_clkout(148.5 MHz)

rx_dataout[19:10]

rx_dataout[9:0]

rx_dataout_valid

Don’t Care

Cb Y Cr Y Cb

rx_clkout(148.5 MHz)

rx_dataout[19:10]

rx_dataout[9:0]

rx_dataout_valid

Cb

Y

Cr

Y Y

Cb

2-6

SMPTE RP168 Switching Support

SMPTE RP168 Switching Support

The SMPTE RP168 standard defines the requirements for synchronous switching between two video

sources to take place with minimal interference to the receiver. The RP168 standard has restrictions for

which lines the source switching can occur.

The SDI II IP core has flexibility and does not restrict you to switch at only a particular line defined in the

RP168 standard. You can perform switching at any time between different video sources as long as the

source has similar standard and format. After switching, all the status output signals, including the

rx_trs_locked, rx_frame_locked, and rx_align_locked signals, remain unchanged. You should

should not see any interrupts at downstream.

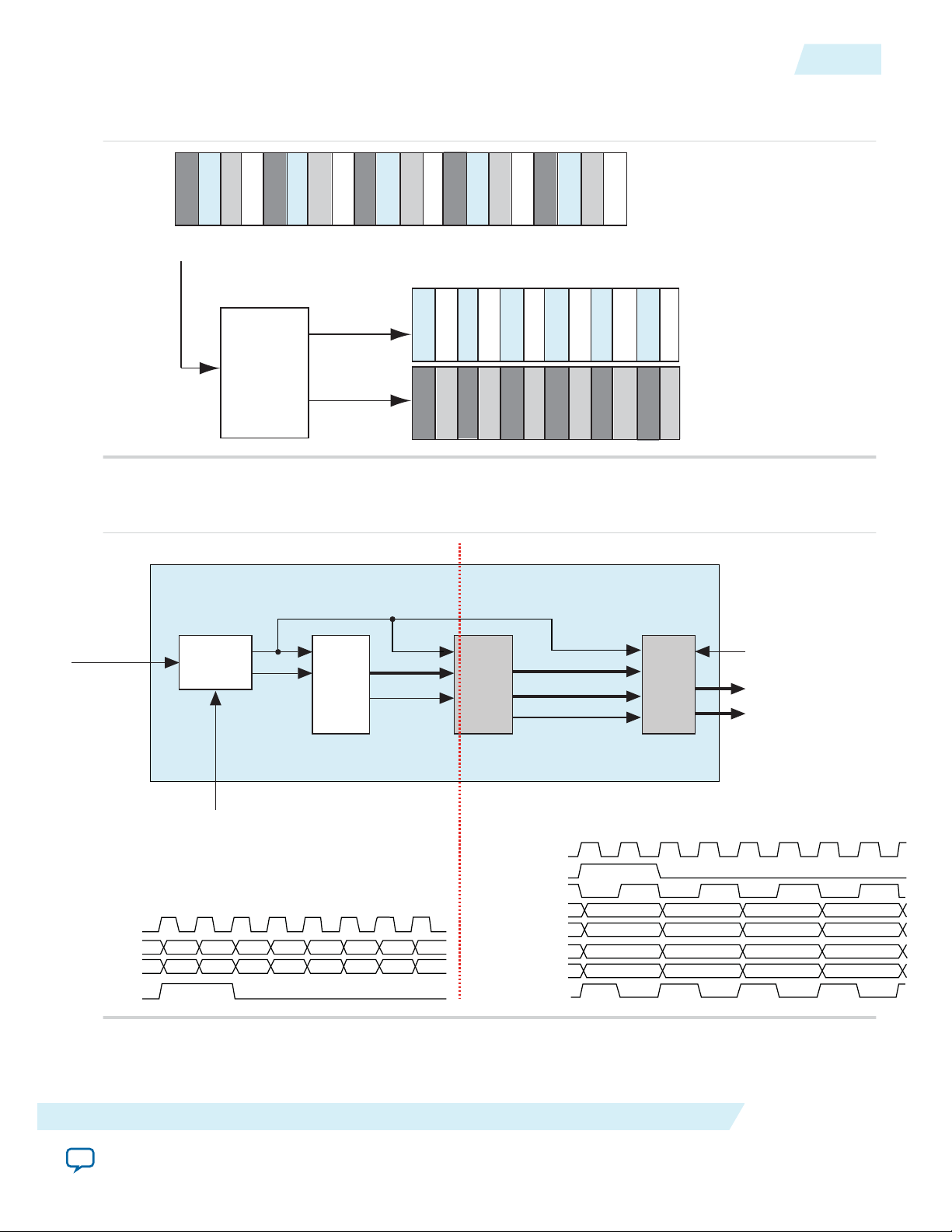

SD 20-Bit Interface for Dual/Triple Standard

For a common SD interface, the serial data format is 10 bits wide, whereas for HD or 3G, the data format

is 20 bits wide, divided into two parallel 10-bit datastreams (known as Y and C).

To make the interface bit width common for all standards in the dual standard or triple standard SDI

mode:

• The receiver can extract the data and align them in 20-bit width

• The transmitter can accept SD data in 20-bit width and retransmit them successfully

UG-01125

2015.05.04

The timing diagrams below show a comparison of data arrangement between 10-bit and 20-bit interface.

Figure 2-5: SD 10-Bit Interface

• The upper 10 bits of rx_dataout are insignificant data.

• The lower 10 bits of rx_dataout are Luma (Y) and chroma (Cb, Cr) channels (interleaved).

• The 1H 4L 1H 5L cadence of rx_dataout_valid repeats indefinitely (ideal).

Figure 2-6: SD 20-Bit Interface

Altera Corporation

• The upper 10 bits of rx_dataout are Luma (Y) channel and the lower 10 bits are Chroma (Cb, Cr)

channel.

• The 1H 10L cadence of rx_dataout_valid repeats indefinitely (ideal).

SDI II IP Core Overview

Send Feedback

Page 12

UG-01125

2015.05.04

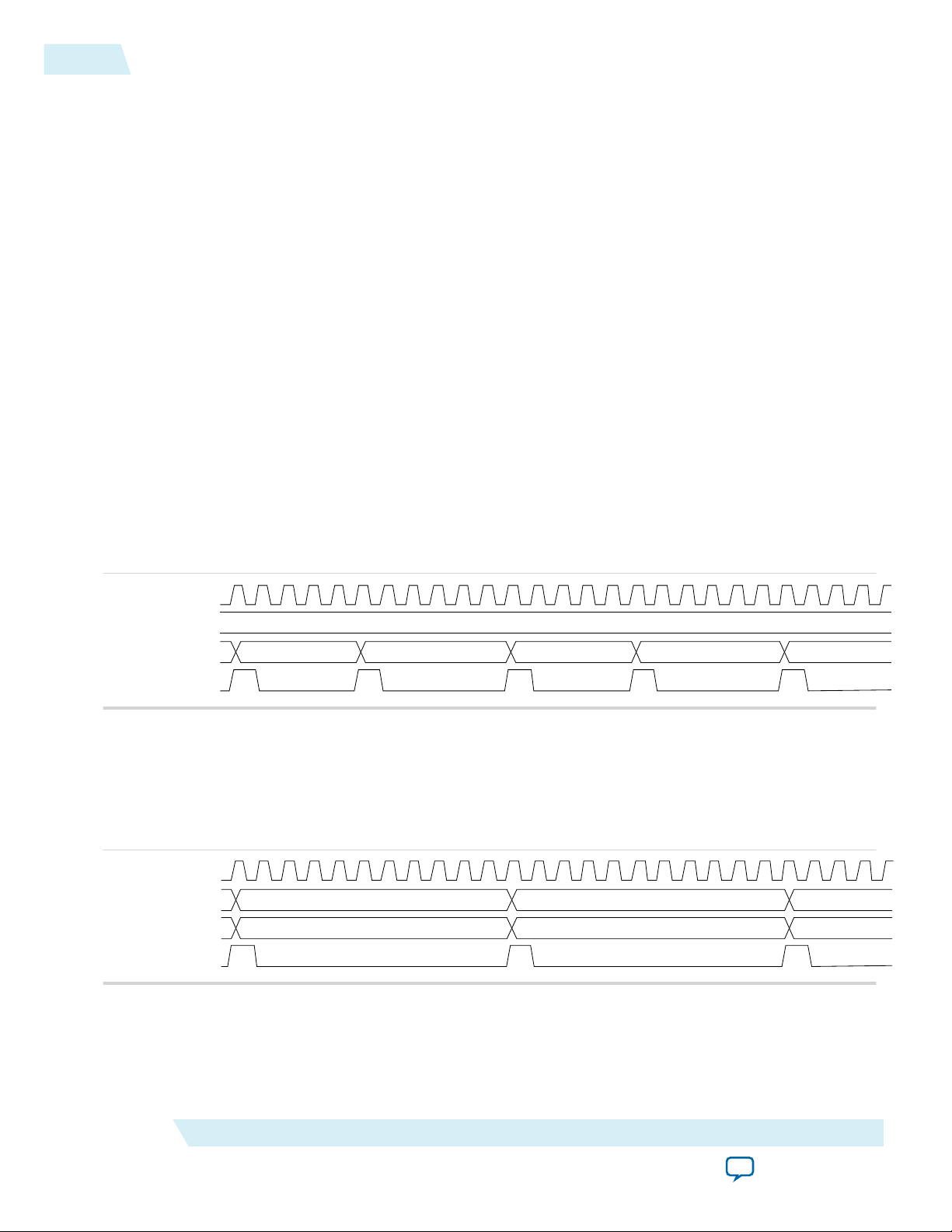

Dynamic TX Clock Switching

The dynamic TX clock switching feature allows you to dynamically switch between NTSC and PAL

transceiver data rates for all video standards except SD-SDI. The dynamic TX clock switching enables an

SDI video equipment to operate on NTSC or PAL.

You can choose to switch the TX clocks through one of these two methods:

• Instantiate an alternate TX PLL and supply two different clocks to the two PLLs. Switch between the

primary PLL and the alternate PLL for transmission.

• Use the primary PLL with two reference input clocks. The PLL switches between these two clocks for

transmission.

To implement this feature, you are required to provide two reference clocks (xcvr_refclk and

xcvr_refclk_alt) to the SDI II IP core. The frequency of the reference clocks must be assigned to 148.5

MHz and 148.35 MHz in any assignment order.

The TX PLL select signal (ch1_{tx/du}_tx_pll_sel) is an input control signal that you provide to the

core and the transceiver reconfiguration controller to select the desired clock input for the hard

transceiver.

• Set ch1_{tx/du}_tx_pll_sel to 0 to select xcvr_refclk

• Set ch1_{tx/du}_tx_pll_sel to 1 to select xcvr_refclk_alt

Dynamic TX Clock Switching

2-7

To dynamically switch between the two reference clocks, you need to implement a simple handshaking

mechanism. The handshake is initiated when the reconfiguration request signal (ch1_{tx/

du}_tx_start_reconfig) is asserted high. This signal must remain asserted until the reconfiguration

process completes. The reconfiguration process completes when the reconfiguration done signal

(ch1_{tx/du}_tx_reconfig_done) is asserted high. The TX PLL select signal (ch1_{tx/

du}_tx_pll_sel) needs to be stable throughout the reconfiguration process.

To complete the handshaking process, you must deassert the reconfiguration request signal (ch1_{tx/

du}_tx_start_reconfig) upon assertion of the reconfiguration done signal (ch1_{tx/

du}_tx_reconfig_done). The dynamic TX clock switching only takes effect after the tx_rst is asserted

high and deasserted low accordingly.

SDI II IP Core Overview

Send Feedback

Altera Corporation

Page 13

TX Protocol

TX PHY

Management

PHY Adapter

Transceiver

PHY Reset

Controller

Transceiver

Reconfiguration

Controller

Reconfiguration

Management

Reconfiguration

Router

TX Transceiver

Channel

TX PLL0 TX PLL1

Parallel Video In

(tx_datain and

tx_datain_b for

HD-SDI Dual Link)

Primary Reference Clock (xcvr_refclk)

Alternative Reference Clock (xcvr_refclk_alt)

Reset

(tx_rst)

Tx PLL Switching

Handshaking

Signals

Reconfiguration Acknowledge

(ch1_{tx/du}_tx_reconfig_done)

Reconfiguration Request

(ch1_{tx/du}_tx_start_reconfig)

TX PLL Select (ch1_{tx/du}_tx_pll_sel)

Avalon-MM

Control Interface

TX Clock Out (tx_clkout)

(148.5 or 148.35 MHz)

SDI Out

(sdi_tx and sdi_tx_b for

HD-SDI Dual Link)

Altera Transceiver

Analog Reset

Digital Reset

PLL Powerdown

PLL Locked

Cal Busy

TX PLL Select

SDI TX (All Video Standard Modes except SD-SDI)

Altera PHY

IP Core

Data

Control/Status

Clock

Reset

Legend

148.5 MHz

148.35 MHz

148.5 MHz

Case 1 Case 2 Case 3

148.35 MHz 148.5 MHz 148.35 MHz

xcvr_refclk

xcvr_refclk_alt

tx_rst

ch1_{tx/du}_tx_pll_sel

ch1_{tx/du}_tx_start_reconfig

ch1_{tx/du}_tx_reconfig_done

tx_clkout

2-8

Dynamic TX Clock Switching

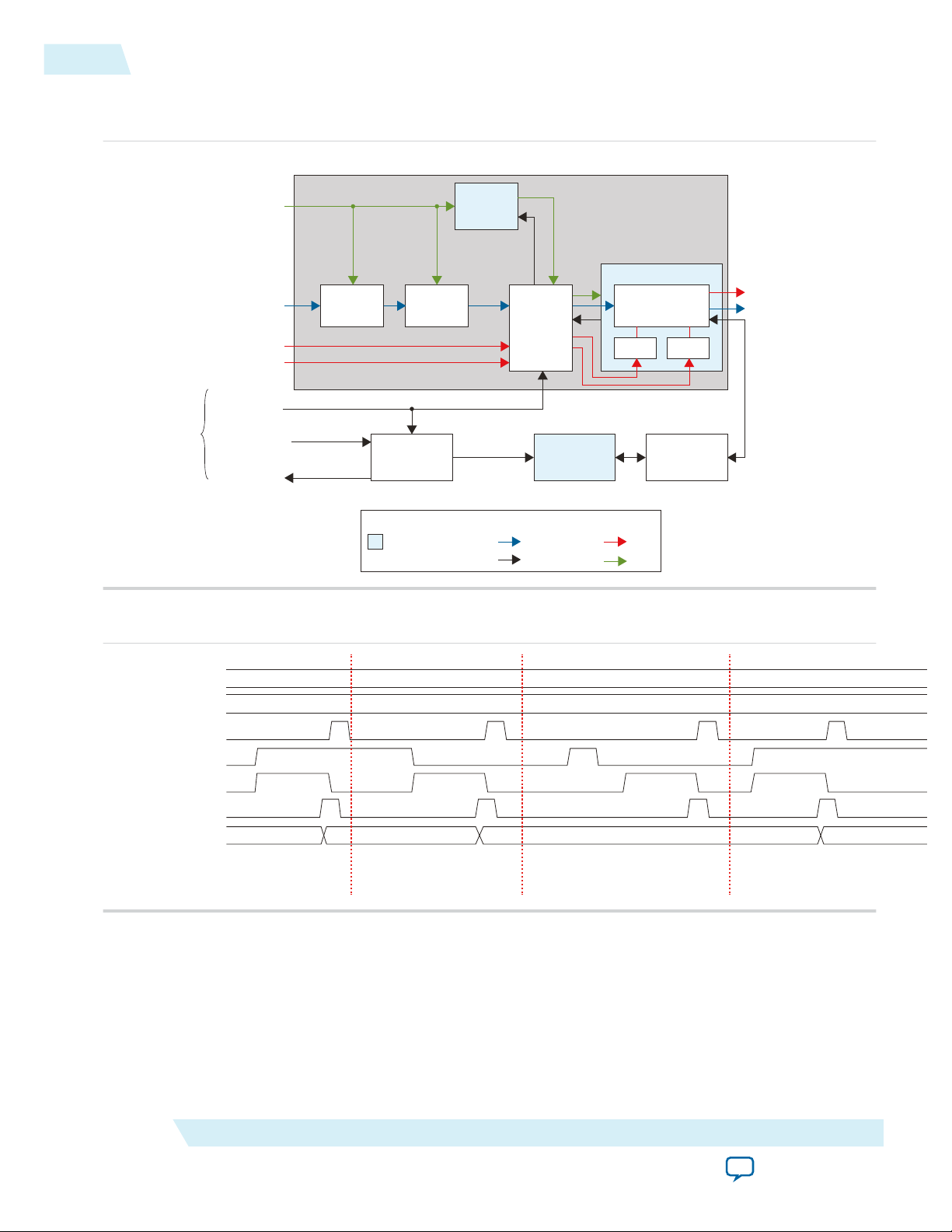

Figure 2-7: Hardware Implementation of the Dynamic TX Clock Switching Feature

The figure shows the TX clock switching feature with two TX PLLs.

UG-01125

2015.05.04

Figure 2-8: Dynamic TX Clock Switching Timing Diagram

The table below describes the behavior of the dynamic switching feature when you initiate a handshaking

process (with reference to the timing diagram).

Altera Corporation

SDI II IP Core Overview

Send Feedback

Page 14

UG-01125

2015.05.04

Table 2-2: Dynamic Switching Behavior During a Handshaking Process

Case Description

1 The handshaking process attempts to switch to select xcvr_refclk_alt. tx_clkout success‐

fully locks to xcvr_refclk_alt (148.35 MHz).

2 The handshaking process attempts to switch to select xcvr_refclk. tx_clkout successfully

locks to xcvr_refclk (148.5 MHz).

3 The handshaking process attempts to switch to select xcvr_refclk_alt. The switching fails

because ch1_{tx/du}_tx_pll_sel changes from 1 to 0 prior to the assertion of ch1_{tx/

du}_tx_start_reconfig. Therefore tx_clkout is still locked to xcvr_refclk (148.5MHz).

Resource Utilization

The tables below list the typical resource utilization for the SDI II IP core with the Quartus II software,

version 15.0.

Note:

The resource utilization data was obtained by using the most common configurations for each

video standard and from one specific family device.

Resource Utilization

2-9

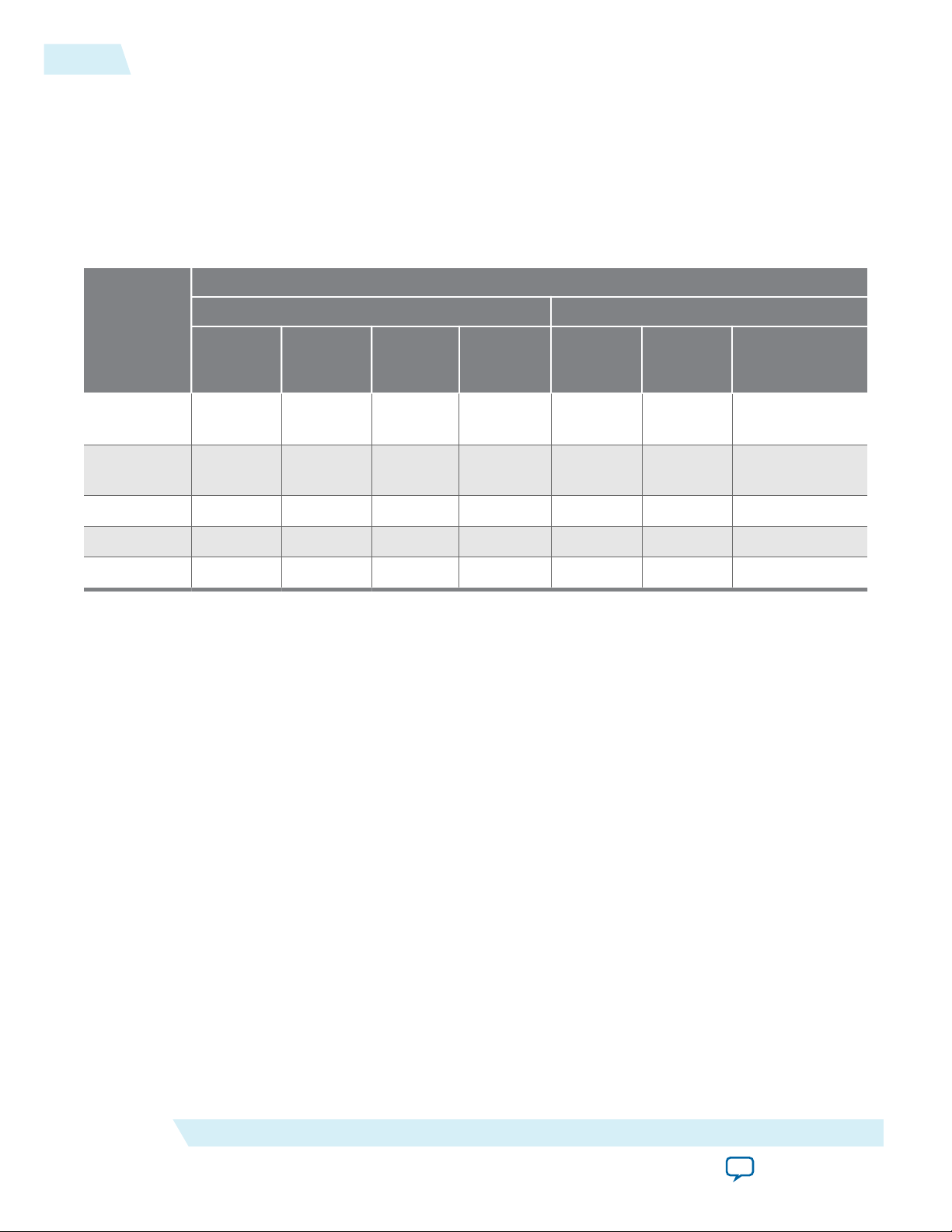

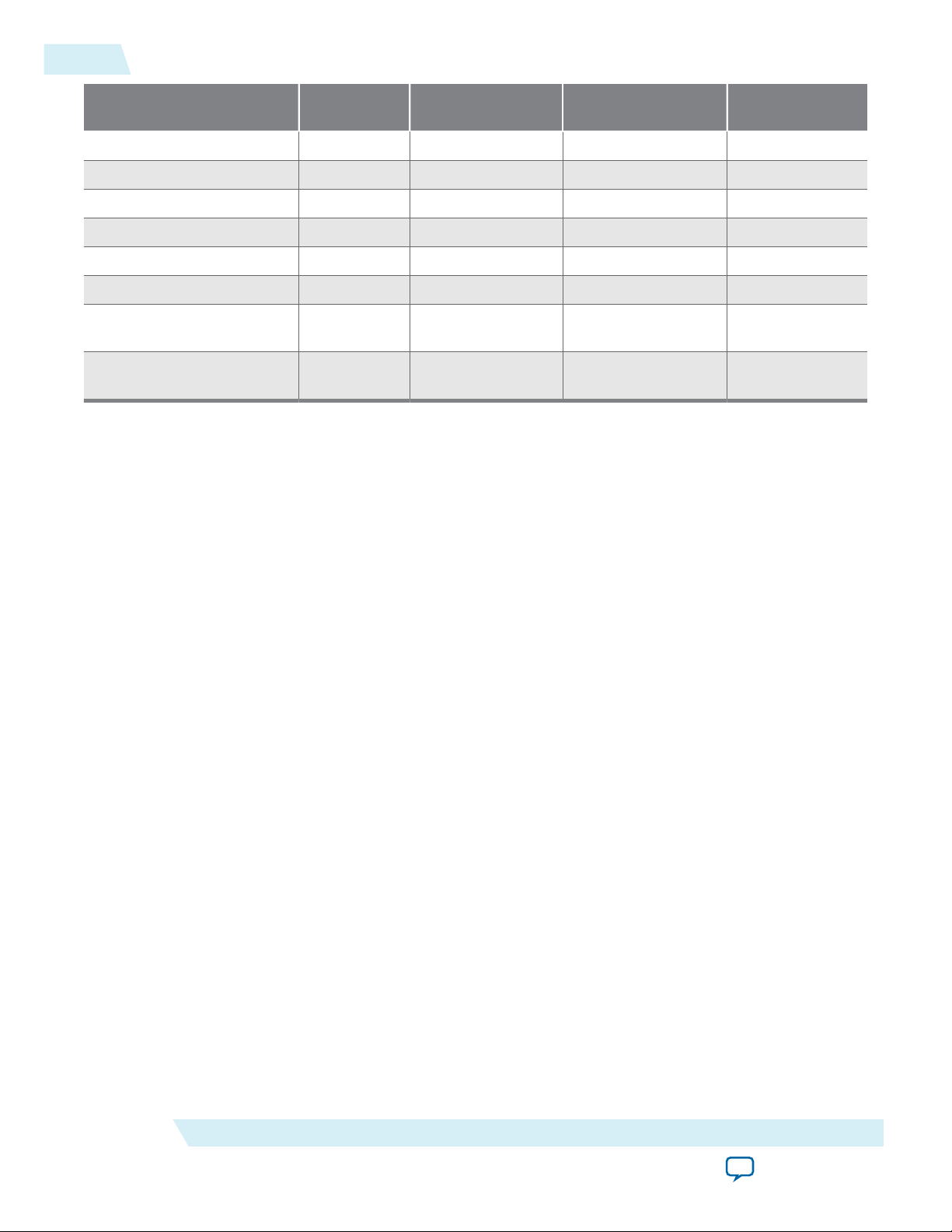

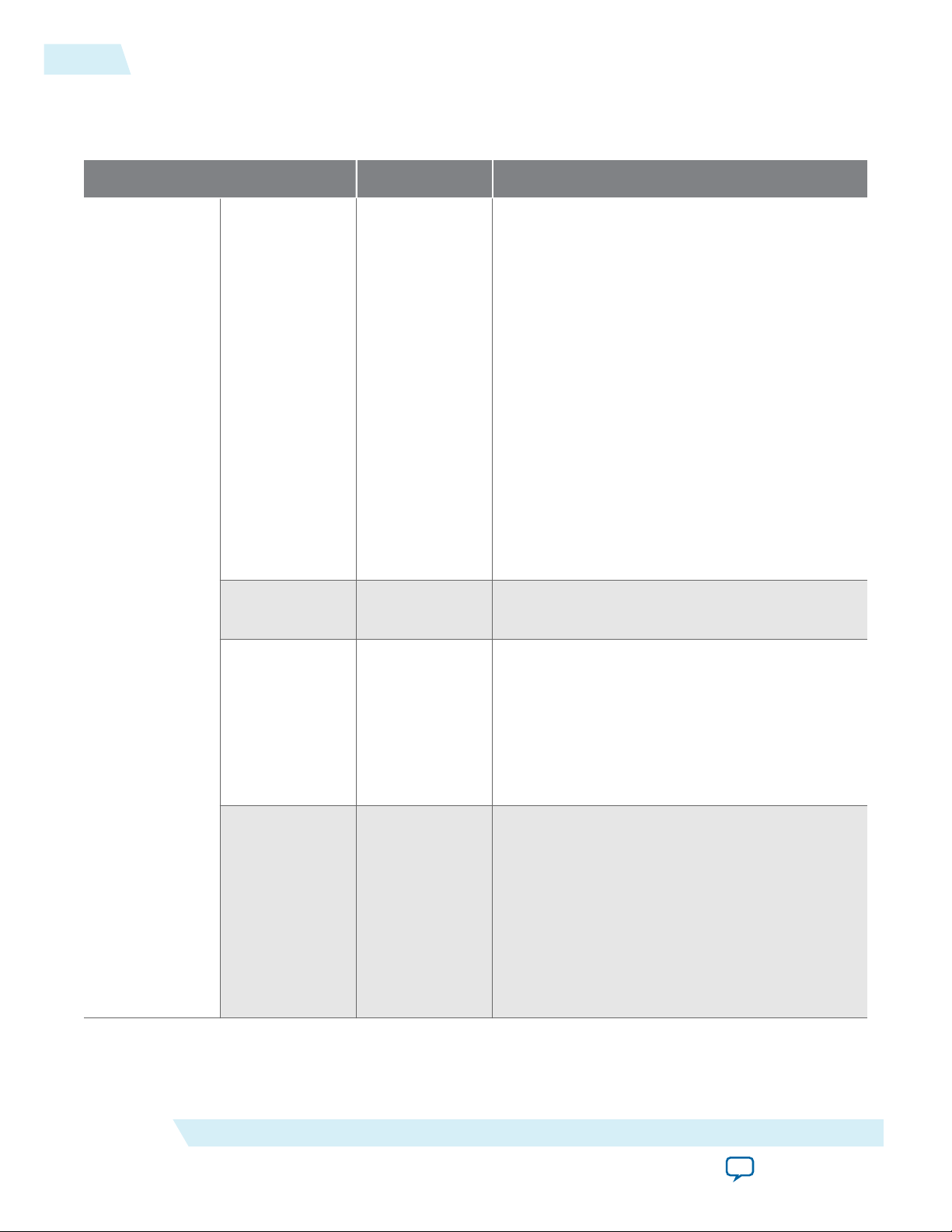

Table 2-3: Resource Utilization for Each Video Standard (Arria V, Cyclone V, and Stratix V Devices)

Standard ALM Needed Primary Logic

Registers

Secondary Logic

Registers

Block Memory Bits

SD-SDI TX 95 126 10 0

SD-SDI RX 528 641 48 60

HD-SDI TX 141 159 10 0

HD-SDI RX 557 821 60 0

HD Dual Link TX 447 478 43 0

HD Dual Link RX 1,305 1,897 155 4,608

3G-SDI TX 444 414 12 0

3G-SDI RX 826 1307 125 0

Dual Rate TX 242 237 4 0

Dual Rate RX 924 1,209 84 0

Triple Rate TX 496 528 8 0

Triple Rate RX 1,064 1,583 98 0

Table 2-4: Resource Utilization for Each Video Standard (Arria 10 Devices)

Standard ALM Needed Primary Logic

HD-SDI TX 106 124 23 0

HD-SDI RX 523 765 66 0

SDI II IP Core Overview

Send Feedback

Registers

Secondary Logic

Registers

Block Memory Bits

Altera Corporation

Page 15

2-10

Resource Utilization

UG-01125

2015.05.04

Standard ALM Needed Primary Logic

Registers

Secondary Logic

Registers

Block Memory Bits

HD Dual Link TX 367 410 60 0

HD Dual Link RX 1,239 1,780 177 4,608

3G-SDI TX 407 380 13 0

3G-SDI RX 808 1,261 93 0

Triple Rate TX 475 492 9 0

Triple Rate RX 1024 1,535 86 0

Multi Rate (Up to 12G-

1,807 1,742 24 0

SDI) TX

Multi Rate (Up to 12G-

3,581 4,734 270 0

SDI) RX

Altera Corporation

SDI II IP Core Overview

Send Feedback

Page 16

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI II IP Core Getting Started

3

UG-01125

Subscribe

Installation and Licensing

To evaluate the SDI II IP core using the OpenCore Plus feature, follow these steps in your design flow:

1. Install the SDI II IP core.

2. Create a custom variation of the SDI II IP core.

3. Implement the rest of your design using the design entry method of your choice.

4. Use the IP functional simulation model to verify the operation of your design.

5. Compile your design in the Quartus II software. You can also generate an OpenCore Plus time-limited

programming file, which you can use to verify the operation of your design in hardware.

For more information on IP functional simulation models, refer to the Simulating Altera Designs

Note:

chapter in volume 3 of the Quartus II Handbook.

The default installation directory for the SDI II IP core on Windows is c:\altera\<version>; on Linux, it is /

opt/ altera<version>.

You can obtain a license for the IP core only when you are completely satisfied with its functionality and

performance, and want to take your design to production. After you purchase a license for the SDI II IP

core, follow these steps:

1. Set up licensing.

2. Generate a programming file for the Altera device or devices on your board.

3. Program the Altera device or devices with the completed design.

Send Feedback

Related Information

Simulating Altera Designs

Design Walkthrough

This walkthrough explains how to create an SDI II IP core design using the Quartus II software and IP

Catalog. After you generate a custom variation of the SDI II IP core, you can incorporate it into your

overall project.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 17

3-2

Creating a New Quartus II Project

This walkthrough includes the following steps:

1. Creating a New Quartus II Project on page 3-2

2. Launching IP Catalog on page 3-2

3. Parameterizing the IP Core on page 3-3

4. Generating a Design Example and Simulation Testbench on page 3-3

5. Simulating the SDI II IP Core Design on page 3-3

Creating a New Quartus II Project

Before you begin

You need to create a new Quartus II project with the New Project Wizard, which specifies the working

directory for the project, assigns the project name, and designates the name of the top-level design entity.

To create a new project, perform the following the steps.

1. From the Windows Start menu, select Programs > Altera > Quartus II <version> to run the Quartus

II software. Alternatively, you can use the Quartus II Web Edition software.

2. On the File menu, click New Project Wizard.

3. In the New Project Wizard: Directory, Name, Top-Level Entity page, specify the working directory,

project name, and top-level design entity name. Click Next.

4. In the New Project Wizard: Add Files page, select the existing design files (if any) you want to include

in the project.

5. In the New Project Wizard: Family & Device Settings page, select the device family and specific

device you want to target for compilation. Click Next.

6. In the EDA Tool Settings page, select the EDA tools you want to use with the Quartus II software to

develop your project.

7. The last page in the New Project Wizard window shows the summary of your chosen settings. Click

Finish to complete the Quartus II project creation.

(1)

Click Next.

UG-01125

2015.05.04

Launching IP Catalog

To launch the IP Catalog in the Quartus II software, follow these steps:

1. On the Tools menu, click IP Catalog.

2. Expand the Interface Protocols> Audio & Video folder and double-click SDI II to launch the

parameter editor.

The parameter editor prompts you to specify your IP variation name, optional ports, architecture

features, and output file generation options. The parameter editor generates a top-level .qsys or .qip

file representing the IP core in your project.

3. Click OK to display the SDI II IP core parameter editor.

(1)

To include existing files, you must specify the directory path to where you installed the SDI II IP core. You

must also add the user libraries if you installed the MegaCore IP Library in a different directory from where

you installed the Quartus II software.

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 18

UG-01125

2015.05.04

Parameterizing the IP Core

To parameterize your IP core, follow these steps:

1. Select the video standard.

2. Select Bidirectional, Transmitter, or Receiver interface direction.

3. Select Combined Transceiver and Protocol, Separate Transceiver or Separate Protocol, (for Arria V,

Cyclone V, and Stratix V devices only).

4. Turn on the necessary transceiver options, (for Arria V, Cyclone V, and Stratix V devices only).

5. Turn on the necessary receiver options.

Some options may be grayed out, because they are not supported in the currently selected configura‐

tion.

6. Turn on the necessary transmitter options.

Some options may be grayed out, because they are not supported in the currently selected configura‐

tion.

7. Select the example design options, (if you are generating the design example for Arria 10 devices).

8. Click Finish.

Related Information

SDI II IP Core Parameters on page 3-6

Parameterizing the IP Core

3-3

Generating a Design Example and Simulation Testbench

After you have parameterized the IP core, click Generate Example Design to create the following entities:

• design example— serves as a common entity for simulation and hardware verification.

• simulation testbench—consists of the design example entity and other non-synthesizable components.

The example testbench and the automated script are located in the <variation name>_example/

simulation/verilog or <variation name>_example/simulation/vhdl directory.

Note:

Generating a design example can increase processing time.

You can now integrate your custom IP core variation into your design, simulate, and compile.

Simulating the SDI II IP Core Design

After design generation, the files located in the <variation name>_example/simulation/verilog or

<variation name>_example/simulation/vhdl directory are available for you to simulate your design.

The SDI II IP core supports the following EDA simulators listed in the table below.

Table 3-1: Supported EDA Simulators

Simulator Supported Platform Supported Language

ModelSim-SE Windows/Linux VHDL and Verilog HDL

ModelSim-Altera Windows/Linux Verilog

VCS/VCS MX Windows/Linux Verilog

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 19

3-4

Timing Violation

Simulator Supported Platform Supported Language

Aldec Riviera-PRO Linux Verilog

To simulate the design using the ModelSim-SE or ModelSim-Altera simulator, follow these steps:

1. Start the simulator.

2. On the File menu, click Change Directory > Select <variation name>_example_design/simulation/

verilog/mentor (for Verilog HDL language) or _example_design/simulation/vhdl/mentor (for

VHDL language).

3. Run the provided run_sim.tcl script. This file compiles the design and runs the simulation automati‐

cally. It provides a pass/fail indication on completion.

To simulate the design using the VCS/VCS MX simulator (in Linux), follow these steps:

1. Start the VCS/VCS MX simulator.

2. On the File menu, click Change Directory > Select <variation name>_example_design/sdi_ii/

simulation/verilog/synopsys.

3. Run the provided run_vcs.sh (in VCS) or run_vcsmx.sh (in VCSMX) script. This file compiles the design

and runs the simulation automatically. It provides a pass/fail indication on completion.

To simulate the design using the Aldec Riviera-PRO simulator, follow these steps:

UG-01125

2015.05.04

1. Start the Aldec Riviera-PRO simulator.

2. On the File menu, click Change Directory > Select <variation name>_example_design/sdi_ii/

simulation/verilog/aldec.

3. Run the provided run_riviera.tcl script. This file compiles the design and runs the simulation automati‐

cally. It provides a pass/fail indication on completion.

Timing Violation

After you create a new project, the Quartus II software generates a Quartus II Settings File (.qsf). Add the

following assignments to .qsf to avoid timing violation from the synchronizers.

set_instance_assignment -name GLOBAL_SIGNAL OFF -to *|altera_reset_synchronizer:alt_rst_sync_uq1|altera_reset_synchronizer_int_chain_out

Compiling the SDI II IP Core Design

To compile your design, click Start Compilation on the Processing menu in the Quartus II software. You

can use the generated .qip file to include relevant files into your project.

You can find the design examples of the SDI II IP core in the <variation name>_example_design/

example_design/<variation name>_example_design directory. For the design example illustrations, refer

to the Design Examples section.

To create a new project using the generated design example, follow the steps in the Creating a New

Note:

Quartus II Project section and add the design example .qip file in step 4.

Related Information

• Creating a New Quartus II Project on page 3-2

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 20

UG-01125

2015.05.04

• Design Examples on page 3-9

Each design example provided with the SDI II IP core is synthesizable.

• Quartus II Help

More information about compilation in Quartus II software.

Programming an FPGA Device

After successfully compiling your design, program the targeted Altera device with the Quartus II

Programmer and verify the design in hardware.

For instructions on programming the FPGA device, refer to the Device Programming section in volume 3

of the Quartus II Handbook.

Related Information

Device Programming

Design Reference

This section describes the SDI II IP core parameters, signals, and files to help you configure your design.

This section includes detailed description about the SDI II IP core design examples.

Programming an FPGA Device

3-5

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 21

3-6

SDI II IP Core Parameters

SDI II IP Core Parameters

Table 3-2: SDI II IP Core Parameters

Parameter Value Description

UG-01125

2015.05.04

Configuration

Options

Video standard

SD-SDI, HD-SDI,

3G-SDI, HD-SDI

dual link, Dual

rate (up to HDSDI), Triple rate

(up to 3G-SDI),

Multi rate (up to

12G-SDI)

SD interface bit

10, 20 Selects the SD interface bit width. Only applicable

width

Direction Birectional,

Receiver,

Transmitter

Sets the video standard.

• SD-SDI—disables option for line insertion

and extraction, and CRC generation and

extraction

• HD-SDI—enables option for in line insertion

and extraction and CRC generation and

extraction

• Dual, triple or multi rate SDI—includes the

processing blocks for both SD-SDI and HDSDI standards. Logics for bypass paths and to

automatically switch between the input

standards are included.

Note:

SD-SDI and Dual rate (up to HDSDI) options are not available for

Arria 10 devices. Multi rate (up to

12G-SDI) option is not available for

Arria V, Cyclone V, and Stratix V

devices.

for dual standard and triple standard.

Sets the port direction. The selection enables or

disables the receiver and transmitter supporting

logic appropriately.

Altera Corporation

Transceiver and/

or Protocol

Combined,

Transceiver,

Protocol

• Bidirectional—instantiates both the SDI

transmitter and receiver.

• Receiver—instantiates the SDI receiver

• Transmitter—instantiates the SDI transmitter.

Selects the components.

• Transceiver—includes tx/rx_phy_mgmt/phy_

adapter and hard transceiver. This option is

useful if you want to use the same transceiver

component to support both SDI and ASI IP

cores.

• Protocol.

Note: This option is available only for Arria

V, Cyclone V, and Stratix V devices.

SDI II IP Core Getting Started

Send Feedback

Page 22

UG-01125

2015.05.04

SDI II IP Core Parameters

Parameter Value Description

3-7

Transceiver

Options

(2)

Dynamic Tx clock

switching

Transceiver

reference clock

frequency

TX PLL type

Off, Tx PLLs

switching, Tx PLL

reference clocks

switching

• Off: Disable dynamic switching

• Tx PLLs switching: Instantiates two PLLs,

each with a reference input clock

• Tx PLL reference clocks switching: Instanti‐

ates a PLL with two reference input clocks.

Note: This option is not available if you

select ATX PLL.

Turn on this option to allow dynamic switching

between 1 and 1/1.001 data rates.

Note: This option is only available for TX or

bidirectional ports, and all video

standards except SD-SDI.

148.5/148.35

MHz,

74.25/74.175

MHz,

Selects the transceiver reference clock frequency.

The 74.25/74.175 MHz option is available only

for HD-SDI and HD-SDI dual link video

standards, and if you select CMU as the TX PLL.

CMU, ATX Selects the transmitter PLL for TX or bidirec‐

tional ports.

ATX PLL is useful for bidirectional channels—

you can use the ATX PLL as the transmitter PLL

instead of the CMU PLL from another channel.

ATX PLL is only available in the Stratix V and

Arria V GZ families

Increase error

tolerance level

On, Off • On: Error tolerance level = 15

• Off: Error tolerance level = 4

Turn on this option to increase the error

tolerance level for consecutive missed end of

Receiver

Options

active videos (EAVs), start of active videos

(SAVs), or erroneous frames.

CRC error output On, Off • On: CRC monitoring (Not applicable for SD-

SDI mode)

• Off: No CRC monitoring (saves logic)

(2)

These options are available only for Arria V, Cyclone V, and Stratix V devices.

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 23

3-8

SDI II IP Core Parameters

Parameter Value Description

UG-01125

2015.05.04

Transmitter

Options

Extract Payload

ID (SMPTE

352M)

Convert HD-SDI

dual link to 3GSDI (level B)

Convert 3G-SDI

(level B) to HDSDI dual link

Insert payload ID

(SMPTE 352M)

On, Off • On: Extract payload ID

• Off: No payload ID extraction (saves logic)

It is compulsory to turn on this option for 3GSDI, HD SDI dual link, and triple standard

modes. The extracted payload ID is required for

consistent detection of the 1080p format.

On, Off • On: Converts to level B (2 × SMPTE 292M

HD-SDI mapping, including SMPTE 372M

dual link mapping) for HD-SDI dual link

receiver output.

• Off: No conversion

This option is only available for HD-SDI dual

link receiver.

On, Off • On: Converts to HD-SDI dual link (direct

image format mapping) for 3G-SDI receiver

output.

• Off: No conversion

This option is only available for 3G-SDI receiver.

On, Off • On: Insert payload ID

• Off: No payload ID insertion (saves logic)

TX PLL type CMU, ATX Sets the transmitter PLL type for transmit and

Example

Design

Dynamic Tx

clocks switching

Options

(3)

(3)

These options are available only for Arria 10 devices.

Off, Tx PLLs

switching, Tx PLL

reference clocks

switching

bidirectional ports.

ATX PLL is useful for bidirectional channels—

you can use the ATX PLL as the transmitter PLL

instead of the CMU PLL from another channel.

• Off: Disable dynamic switching

• Tx PLLs switching: Instantiates two PLLs,

each with a reference input clock

• Tx PLL reference clocks switching: Instanti‐

ates a PLL with two reference input clocks.

Turn on this option to allow dynamic switching

between 1 and 1/1.001 data rates.

Note: This option is only available for TX or

bidirectional ports, and all video

standards except SD-SDI.

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 24

UG-01125

2015.05.04

SDI II IP Core Component Files

SDI II IP Core Component Files

Table 3-3: Generated Files

Table below describes the generated files and other files that might be in your project directory. The names and

types of files vary depending on whether you create your design with VHDL or Verilog HDL.

Extension Description

<variation name>.v or .sv An IP core variation file, which defines a Verilog HDL description of the

custom IP core. Instantiate the entity defined by this file inside your design.

Include this file when compiling your design in the Quartus II software.

<variation name>.sdc Contains timing constraints for your SDI variation.

<variation name>.qip Contains Quartus II project information for your IP core variations.

<variation name>.tcl Tcl script file to run in Quartus II software.

Design Examples

Each design example provided with the SDI II IP core is synthesizable.

3-9

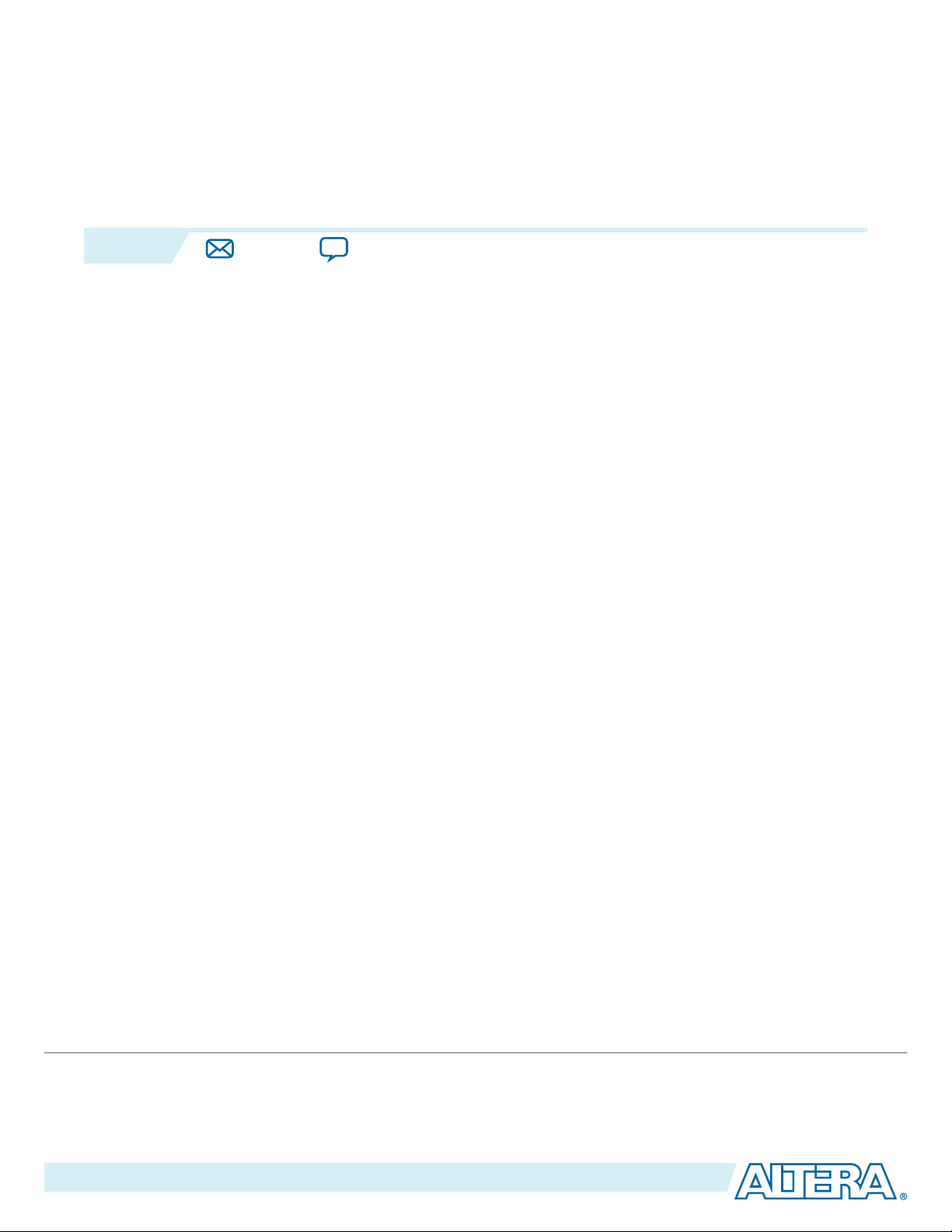

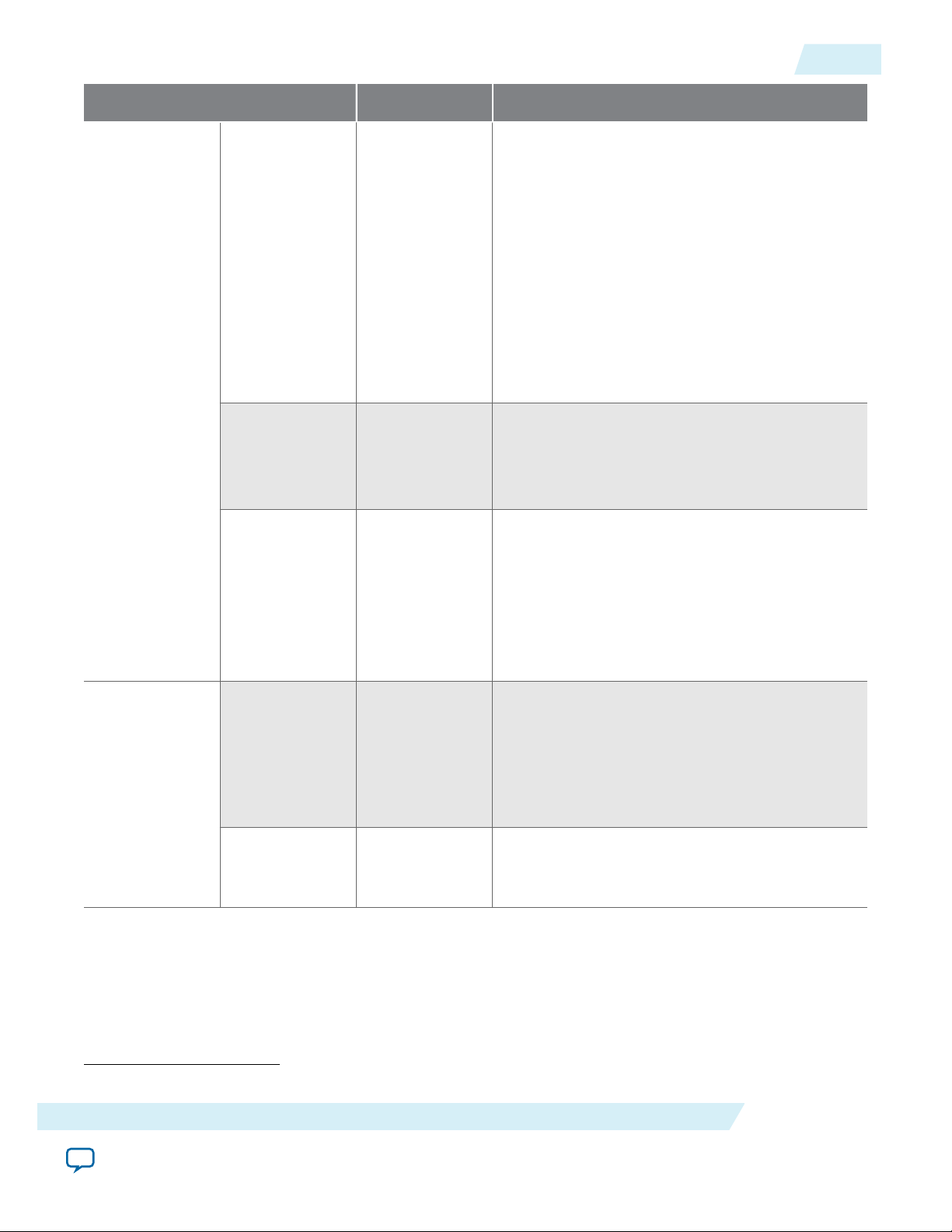

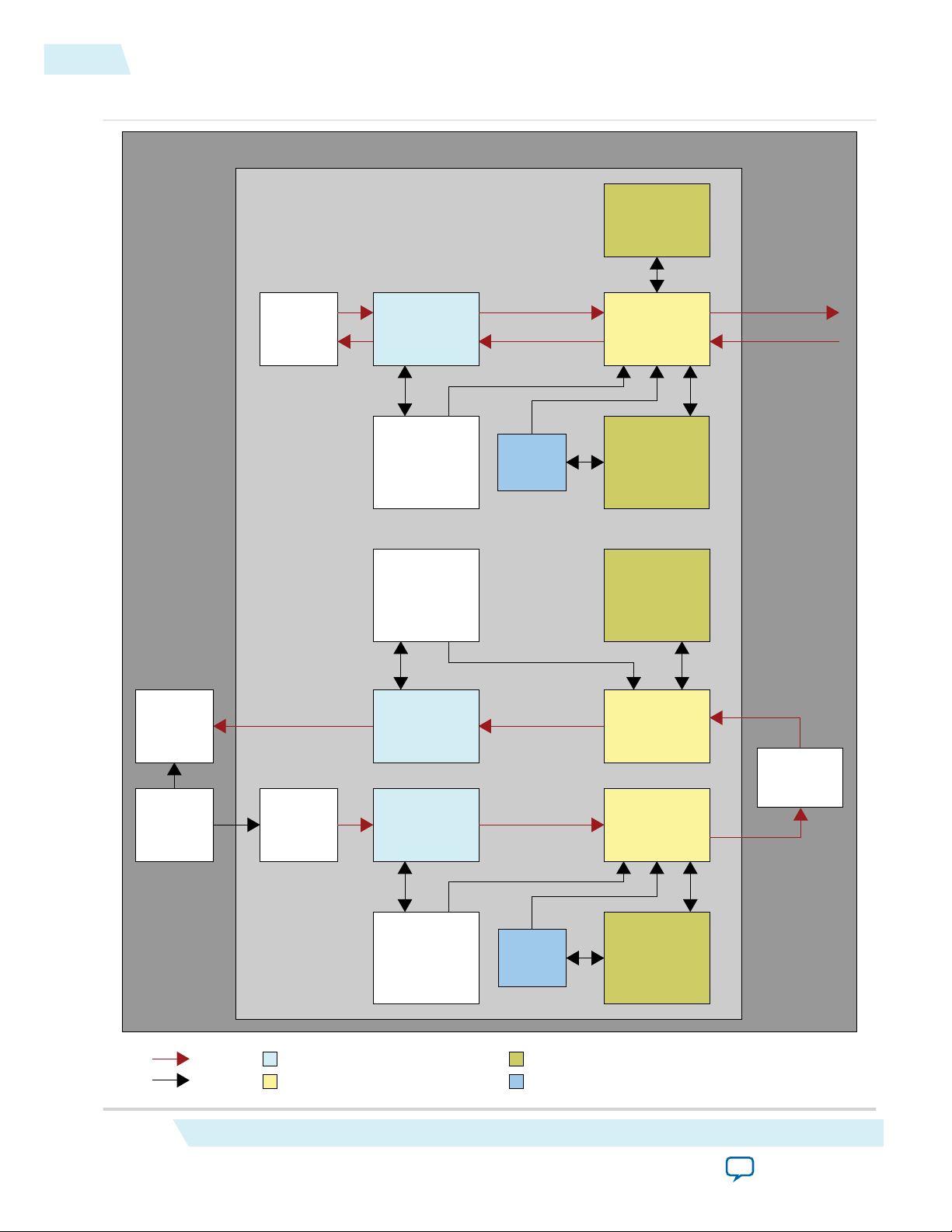

Design Examples for Arria 10 Devices

The figure below illustrates the generated design example entity and simulation testbench for Arria 10

devices. This design example consists of two SDI channels, a video pattern generator, a reconfiguration

controller, and a loopback path.

The IP core configures the device under test (DUT) block according to your parameterization. For

example, if you choose to generate an SDI RX, the software instantiates an SDI TX block to serve as a

video source.

The loopback block (SDI duplex) is always instantiated in the design example for parallel loopback

demonstrations.

The PHY adapter in the generated example design is not included in the figure below so that you can

observe how the signals are physically connected without the adapter. You may bypass the adapter in your

own design to make the design simpler.

For Arria 10 devices, the transceiver is no longer wrapped inside the IP core, and the TX PLL is no longer

wrapped inside the Transceiver PHY. You must generate these blocks separately in the example design.

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 25

Loopback

Path

Ch0 Loopback

(SDI TX + RX)

Arria 10 Native

PHY (Duplex)

Ch0 RX

Transceiver

Reset Controller

Pattern

Generator

Ch1 DUT

(SDI TX)

Arria 10 Native

PHY (TX)

Ch1 RX

Transceiver

Reset Controller

Ch0 TX

Transceiver

Reset Controller

Ch1 TX

Transceiver

Reconfiguration

Controller

Ch0 TX

PLL

Ch1 Test

(SDI RX)

Arria 10 Native

PHY (RX)

Ch0 TX

Transceiver

Reset Controller

Ch0 Duplex

Transceiver

Reconfiguration

Controller

Ch0 TX

PLL

Ch1 RX

Transceiver

Reconfiguration

Controller

TX Checker

RX

Checker

Test

Control

Testbench

Example Design

Data

Control

SDI II IP Core

Arria 10 Native PHY IP Core

Transceiver PHY Reset Controller IP Core

Arria 10 Transceiver CMU/ATX PLL IP Core

3-10

Design Examples for Arria 10 Devices

Figure 3-1: Design Example Entity and Simulation Testbench for Arria 10 Devices

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 26

UG-01125

2015.05.04

This design generates two transceiver PHY reset controllers—one for TX and one for RX. These reset

controllers are connected to the transceiver to control the reset sequence. The PHY adapter controls the

rx_manual and rx_is_lockedtodata input signals of the reset controller. If you want to bypass the PHY

adapter, you must copy the assignment of these input signals in the sdi_ii_phy_adapter.v file to your design.

The table below describes how you should connect the input signals.

Table 3-4: Connecting Input Signals

Input Signal Connection

rx_manual Connect this signal to the rx_ready port of the PHY reset controller to

rx_is_lockedtodata Connect this signal to an output from a multiplexer between rx_is_

Note: The Transceiver Reconfiguration Controller that was used in the design examples for Arria V,

Cyclone V, and Stratix V devices are not applicable for Arria 10 devices. The reconfiguration

interface is now integrated into the transceiver. Each transceiver should pair with a reconfiguration

controller if it requires reconfiguration.

Design Examples for Arria V, Cyclone V, and Stratix V Devices

avoid any disturbance from short interference after the receiver is

locked.

lockedtoref and rx_is_lockedtodata ports from the transceiver,

with the rx_set_locktoref acting as the selector. The receiver operates

in locktoref mode when it receives SD video data. rx_is_lockedto-

data is not stable in this mode.

3-11

Design Examples for Arria V, Cyclone V, and Stratix V Devices

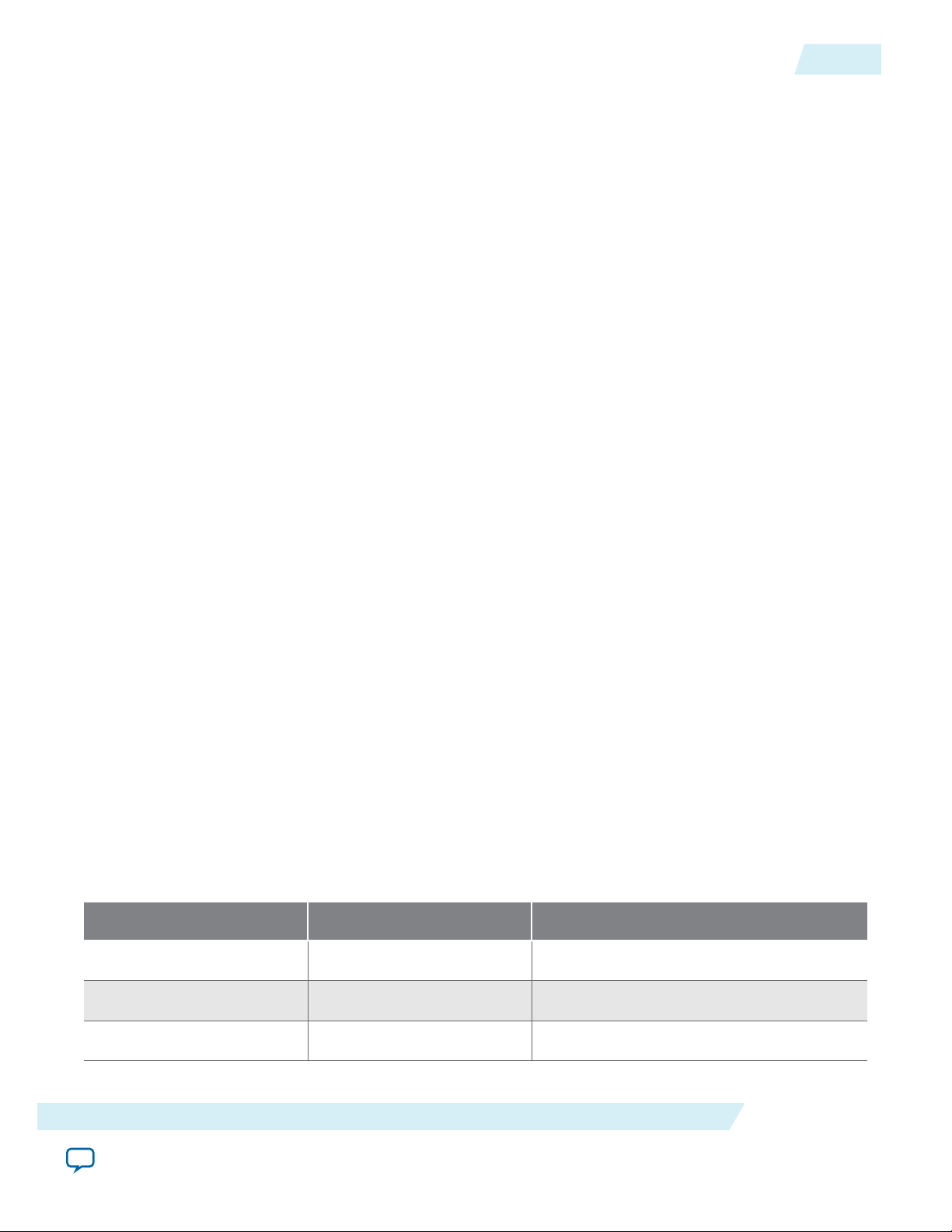

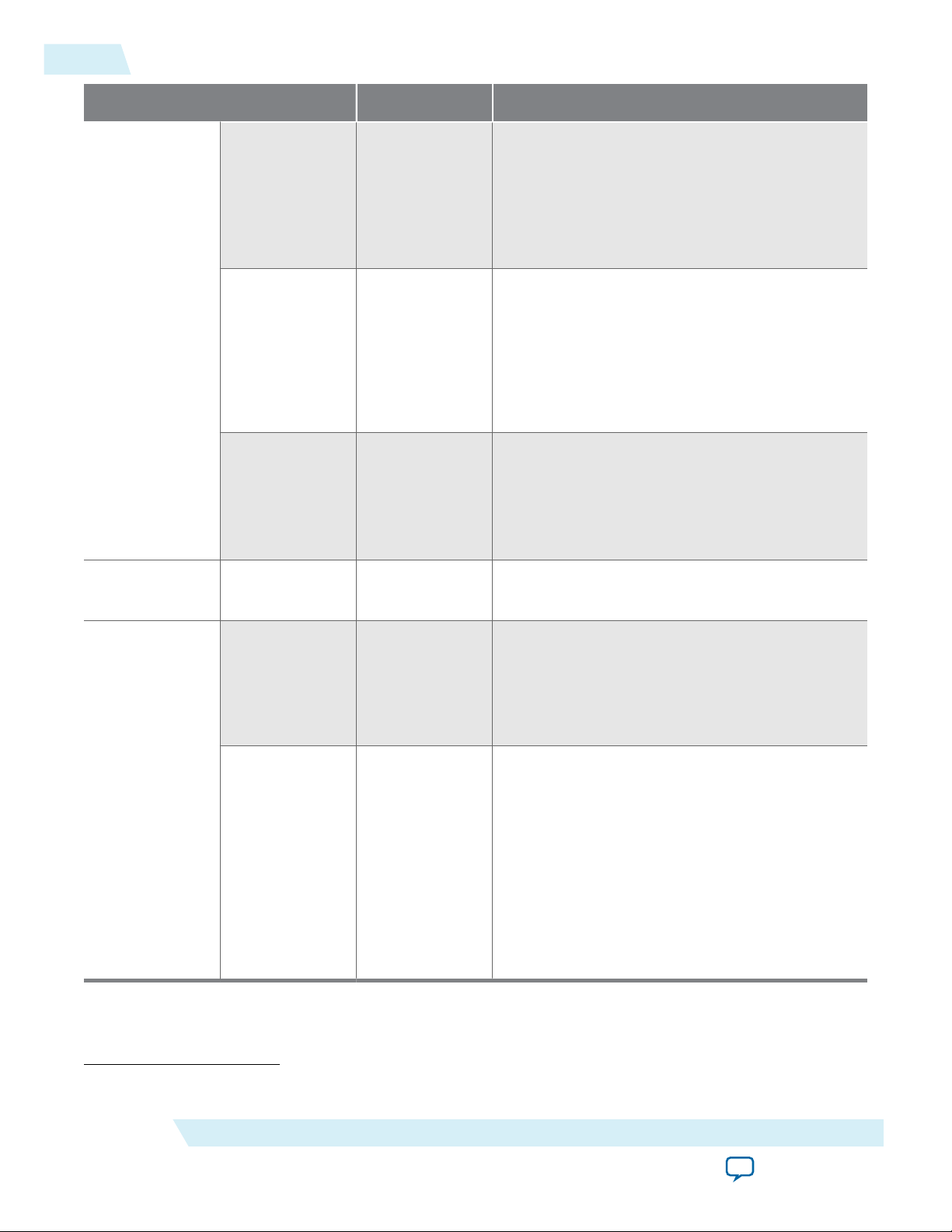

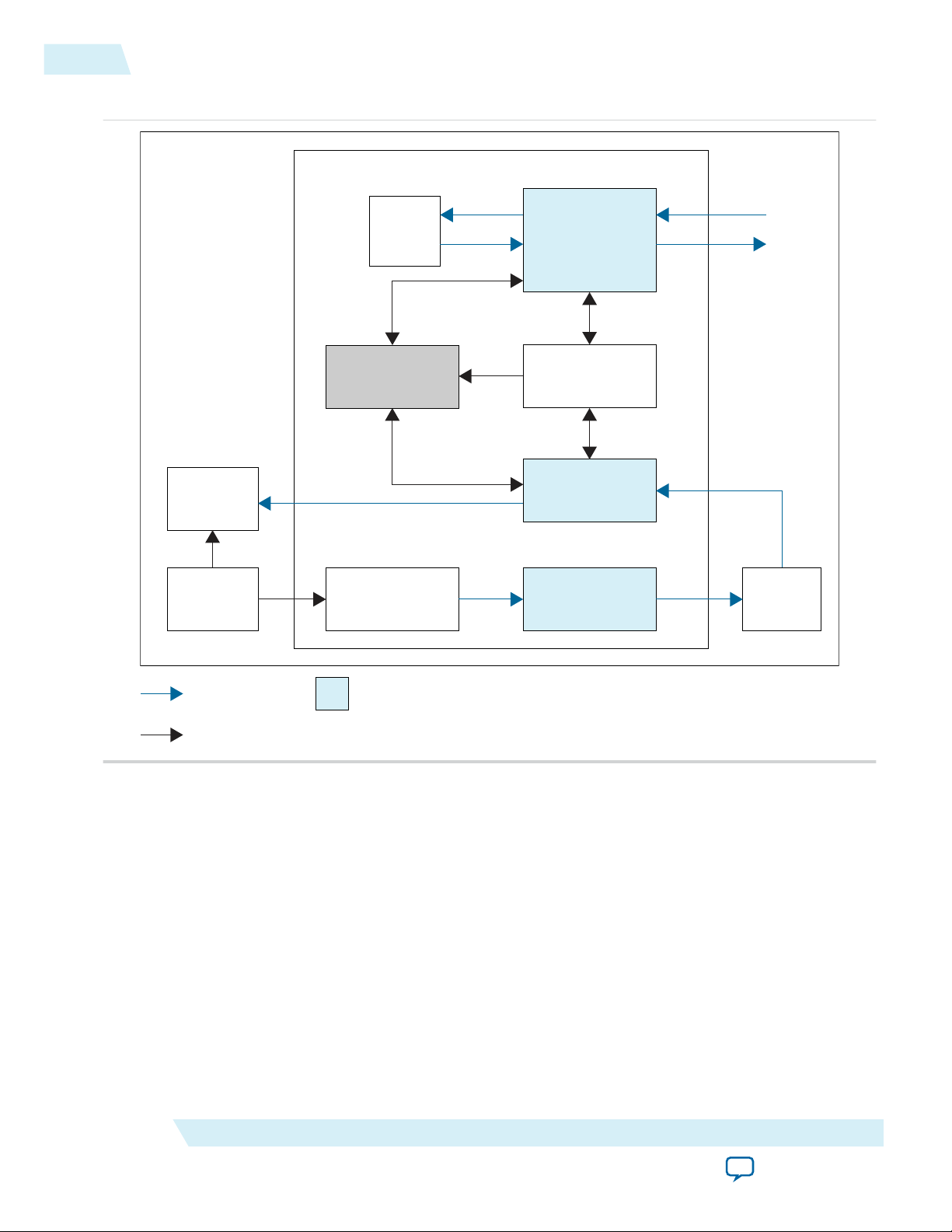

Figure below illustrates the generated design example entity and simulation testbench for Arria V,

Cyclone V, and Stratix V devices. This design example consists of a video pattern generator, transceiver

reconfiguration controller, reconfiguration management, loopback path, and various SDI blocks

occupying two transceiver channels.

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 27

Loopback

Path

Ch0

Loopback

(SDI Duplex)

Reconfiguration

Management/Router

Ch1 Test

(SDI RX)

Ch1 DUT

(SDI TX)

Transceiver

Reconfiguration

Controller

Video Pattern

Generator

TX

Checker

RX

Checker

Test

Control

Data

Control

SDI II IP Core

Design Example

Testbench

3-12

Design Examples for Arria V, Cyclone V, and Stratix V Devices

Figure 3-2: Design Example Entity and Simulation Testbench

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 28

Loopback

Path

Ch0

Loopback

(SDI Duplex)

Reconfiguration

Management/Router

Ch1 Test

(HD DL SDI TX)

Ch1 DUT

(HD DL SDI RX)

A to B

Video Pattern

Generator

Test

Control

Ch2 Test

(3-Gb SDI TX)

Ch2 Test

(3-Gb SDI RX)

TX

Checker

RX

Checker

Loopback

Path

Data

Control

SDI II IP Core

Design Example

Testbench

Transceiver

Reconfiguration

Controller

UG-01125

2015.05.04

Design Examples for Arria V, Cyclone V, and Stratix V Devices

Figure 3-3: Design Example Entity and Simulation Testbench for HD-SDI Dual Link to 3G-SDI (Level B)

Conversion

The figure below illustrates the generated design example entity and simulation testbench when you

generate HD-SDI dual link receiver with Convert HD-SDI dual link to 3G-SDI (level B) option enabled.

3-13

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 29

Loopback

Path

Ch0

Loopback

(SDI Duplex)

Reconfiguration

Management/Router

Ch1 Test

(3-Gb SDI TX)

Ch1 DUT

(3-Gb SDI RX)

B to A

Video Pattern

Generator

Test

Control

Ch2 Test

(HD DL SDI TX)

Ch2 Test

(HD DL SDI RX)

TX

Checker

RX

Checker

Loopback

Path

Data

Control

SDI II IP Core

Design Example

Testbench

Transceiver

Reconfiguration

Controller

3-14

Design Example Components

Figure 3-4: Design Example Entity and Simulation Testbench for 3G-SDI (Level B) to HD-SDI Dual Link

Conversion

The figure below illustrates the generated design example entity and simulation testbench when you

generate 3G-SDI or triple rate SDI receiver with Convert 3G-SDI (level B) to HD-SDI dual link option

enabled.

UG-01125

2015.05.04

Design Example Components

The Arria V, Cyclone V, and Stratix V design examples for the SDI II IP core consist of the following

components:

• Video pattern generator

• Transceiver reconfiguration controller

• Reconfiguration management

• Reconfiguration router

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 30

UG-01125

2015.05.04

Video Pattern Generator

The Arria 10 design example for the SDI II IP core consists of the following components:

• Video pattern generator

• Transceiver reconfiguration controller

Video Pattern Generator

The video pattern generator generates a colorbar or pathological pattern. The colorbar is preferable for

image generation while the pathological pattern can stress the PLL and cable equalizer of the attached

video equipment. You can configure the video pattern generator to generate various video formats.

Table 3-5: Configuring the Video Pattern Generator to Generate Different Video Formats

Table below lists the examples of how to configure the video pattern generator signals to generate a video format

that you desire.

Example

Video

Format

Interface

pattgen_tx_std pattgen_tx_format pattgen_dl_mapping

Signal

3-15

Example 1:

Generate

1080i video

format

1080i60 HD-SDI 2'b01 4'b0100 1'b0

1080i60x2

HD-SDI

dual link

2'b01 4'b0100 1'b0

3Gb 2'b10 4'b0100 1'b0

1080p30 HD-SDI 2'b01 4'b1100 1'b0

Example 2:

Generate

1080p

video

format

1080p30x2 HD-SDI

dual link

HD-SDI

dual link

1080p60

3Ga 2'b11 4'b1100 1'b0

2'b01 4'b1100 1'b0

2'b01 4'b1100 1'b1

3Gb 2'b10 4'b1100 1'b1

Related Information

Video Pattern Generator Signals on page 3-22

Transceiver Reconfiguration Controller

The transceiver reconfiguration controller reconfigures the transceivers. The transceiver reconfiguration

controller in the Arria V, Cyclone V, and Stratix V design examples and the Arria 10 design example is

used differently.

Related Information

• Transceiver Reconfiguration Controller Signals on page 3-23

• Modifying the Transceiver Reconfiguration Controller on page 3-19

Transceiver Reconfiguration Controller for Arria 10

For Arria 10 design examples, the reconfiguration interface is integrated into the Arria 10 Native PHY

instance and TX PLL. Each transceiver and PLL contains an Avalon-MM reconfiguration interface that

must be connected to this reconfiguration controller user logic.

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 31

3-16

Transceiver Reconfiguration Controller for Arria V, Cyclone V, and...

Transceiver Reconfiguration Controller for Arria V, Cyclone V, and Stratix V

For Arria V, Cyclone V, and Stratix V design examples, the transceiver reconfiguration controller allows

you to change the device transceiver settings at any time. Any portion of the transceiver can be selectively

reconfigured. Each portion of the reconfiguration requires a read-modify-write operation (read first, then

write), in such a way by modifying only the appropriate bits in a register and not changing other bits.

Prior to this operation, you must define the logical channel number and the streamer module mode.

You can perform a transceiver dynamic reconfiguration in these two modes:

• streamer module mode 1 (manual mode)—execute a series of Avalon® Memory-Mapped (AvalonMM) write operation to change the transceiver settings. In this mode, you can execute a write

operation directly from the reconfiguration management/router interface to the device transceiver

registers.

• streamer module mode 0—use the .mif files to change the transceiver settings.

For read operation, after defining the logical channel number and the streamer module mode, the

following sequence of events occur:

1. Define the transceiver register offset in the offset register.

2. Read the data register. Toggle the read process by setting bit 1 of the control and status register (CSR)

to logic 1.

3. Once the busy bit in the CSR is cleared to logic 0, it indicates that the read operation is complete and

the required data should be available for reading.

UG-01125

2015.05.04

For write operation, after setting the logical channel number and the streamer module mode, the

following sequence of events occur:

1. Define the transceiver register offset (in which the data will be written to) in the offset register.

2. Write the data to the data register. Toggle the write process by setting bit 0 of the CSR to logic 1.

3. Once the busy bit in the CSR is cleared to logic 0, it indicates that the transceiver register offset

modification is successful.

For more information about the transceiver reconfiguration controller streamer module, refer to the

Transceiver Reconfiguration Controller IP Core Overview chapter of the Altera Transceiver PHY IP Core

User Guide.

Related Information

Altera Transceiver PHY IP Core User Guide

More information about the transceiver reconfiguration controller streamer module.

Reconfiguration Management

The reconfiguration management block (sdi_ii_ed_reconfig_mgmt.v and sdi_ii_reconfig_logic.v) contains the

reconfiguration user logic (a finite state machine) to determine the bits that needs to be modified, and

selects the correct data to be written to the appropriate transceiver register through streamer module

mode 1. It also provides handshaking between the SDI receiver and the transceiver reconfiguration

controller. In this design, each reconfiguration block must interface with only one transceiver reconfigu‐

ration controller.

During the reconfiguration process, the logic first reads the data from the transceiver register that needs

to be reconfigured and stores the data temporarily in a local register. Then, the logic overwrites only the

appropriate bits of the data with predefined values and write the modified data to the transceiver register.

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 32

UG-01125

2015.05.04

Since only one transceiver register can be accessed at a time, the whole process repeats when reconfi‐

guring other registers.

For multiple SDI channels reconfiguration, the logical channel number needs to be set appropriately for

each channel and reconfiguration interface. For example, in the design example and simulation testbench

figure, there are one SDI duplex, one SDI RX, and one SDI TX block. The number of reconfiguration

interface for SDI duplex is 2 (one for channel and one for TX PLL), for SDI RX is 1 (for channel), for SDI

TX is 2 (one for channel and one for TX PLL). The total number of reconfiguration interface required in

the transceiver reconfiguration controller is 5.

The table below lists the channel and transceiver reconfiguration controller interface numbers.

The logical channel number for the receiver in SDI duplex is 0 and the logical channel number for SDI RX

is 2. The generated example design entity demonstrates this interface connection.

Table 3-6: Channel Numbers Setting for Multiple SDI Channels Reconfiguration

SDI Block SDI Channel Number Transceiver Reconfiguration Controller Interface Number

SDI Duplex 0 0 and 1

SDI RX 1 2

SDI TX 1 3 and 4

Reconfiguration Router

3-17

For more information about the logical channel number, refer to the Transceiver Reconfiguration

Controller IP Core Overview chapter of the Altera Transceiver PHY IP Core User Guide.

Related Information

• Reconfiguration Management Parameters on page 3-26

Table below lists the parameters for reconfiguration management.

• Modifying the Reconfiguration Management on page 3-20

• Altera Transceiver PHY IP Core User Guide

For more information about the logical channel number.

Reconfiguration Router

The reconfiguration router (sdi_ii_ed_reconfig_router.v) connects multiple SDI instances to the reconfigu‐

ration management and transceiver reconfiguration controller blocks. The reconfiguration router receives

all the interface signals between the transceiver reconfiguration controller and reconfiguration

management, as well as SDI instances, and transmits the signals to their respective destinations.

The reconfiguration router converts reconfiguration related interface signals of multiple SDI instances

and user interface to a single-wide data bus for the reconfiguration management and transceiver reconfi‐

guration controller blocks. You can bypass this component if you want to implement designs that expands

to more channels. The details are described in the Expanding to Multiple Channels section.

Related Information

• Reconfiguration Router Signals on page 3-27

Table below lists the signals for the reconfiguration router.

• Modifying the Reconfiguration Router on page 3-21

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 33

3-18

Avalon-MM Translators

Avalon-MM Translators

The Avalon-MM Master Translator and Avalon-MM Slave Translator are Avalon-MM interface blocks

that access the Transceiver Reconfiguration Controller registers. The translators are not SDI-specific and

are automatically instantiated when the core interfaces with an Avalon-MM master or slave component.

If you want to bypass the Avalon MM translator in your design, connect reconfig_mgmt_address[8:2]

from the reconfiguration management block to reconfig_mgmt_address from the Transceiver Reconfi‐

guration Controller.

You can connect the other signals from the reconfiguration management block directly to the Transceiver

Reconfiguration Controller.

• reconfig_mgmt_waitrequest

• reconfig_mgmt_read

• reconfig_mgmt_readdata

• reconfig_mgmt_write

• reconfig_mgmt_writedata

For more information about the Avalon-MM Translator functions, refer to the Qsys Interconnect chapter

in volume 1 of the Quartus II Handbook.

Related Information

UG-01125

2015.05.04

• Qsys Interconnect

More information about the Avalon-MM Translator functions.

• Avalon Interface Specifications

Transceiver Dynamic Reconfiguration

The dual and triple standard SDI receivers (or receivers of duplex SDIs) require the transceiver dynamic

reconfiguration feature to perform auto detection and locking to different SDI video rates. Transceiver

dynamic reconfiguration reconfigures the transceivers to support the three SDI video standards (SD, HD

and 3G).

You need to perform transceiver dynamic reconfiguration on the SDI transmitter (or transmitters

Note:

of duplex SDIs) if you want to use the dynamic TX clock switching feature.

The dual and triple standard SDI use 11 times oversampling for receiving SD-SDI standard. As the rates

for 3G-SDI and SD-SDI are the same, transceiver reconfiguration is not required when the video standard

changes from 3G-SDI to SD-SDI and vice versa. Transceiver reconfiguration is only required when the

video standard changes from 3G-SDI or SD-SDI to HD-SDI, and vice versa.

To perform transceiver dynamic reconfiguration, you need the transceiver reconfiguration controller and

reconfiguration management/router blocks.

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 34

UG-01125

2015.05.04

The following sequence of events occur when there is a change in the SDI receiver video standard:

1. The SDI receiver locks to 3G-SDI standard and detects the incoming video standard has changed from

3G-SDI to HD-SDI. The transceiver controller requests a reconfiguration.

2. The transceiver reconfiguration controller determines the appropriate settings to write based on the

information from the transceiver controller. Then, it performs the read-modify-write operation to

reconfigure the device transceiver.

3. Once the reconfiguration completes, the transceiver reconfiguration controller indicates to the SDI

receiver that reconfiguration is complete.

4. The SDI receiver begin the process of locking to the incoming data.

Expanding to Multiple Channels

The generated design example consists of two SDI channels, where the SDI duplex instance always occupy

Channel 0 (Ch0), while the SDI instance at Channel 1 (Ch1) depends on your selection from the

parameter editor. To expand and accommodate more channels, you must perform some modifications to

the source files.

For example, when Ch0 is duplex, Ch1 is RX and TX, if you want to instantiate an additional SDI duplex

instance at Channel 2 (Ch2), you need to make some modifications to the following components.

Note: This is only applicable for Arria V, Cyclone V, and Stratix V design examples. For Arria 10 design

example, just duplicate another transceiver reconfiguration controller generated from the example

design for the additional channel.

Expanding to Multiple Channels

3-19

Modifying the Transceiver Reconfiguration Controller

Perform the following changes to modify the transceiver reconfiguration controller:

• Edit the Number_of_reconfig_interfaces parameter. This parameter specifies the total number of

reconfiguration interfaces that connect to this block.

• Each channel or TX PLL needs one reconfiguration interface. Therefore, an SDI duplex or SDI TX

mode requires two interfaces while an SDI RX mode requires only one interface. If you enable the

dynamic TX clock switching feature, , the SDI duplex or SDI TX mode requires three interfaces. The

additional interface is for the additional TX PLL. For simplicity, assume this option is disabled.

• Determine the total number of reconfiguration interfaces required in your design and assign the

parameter value accordingly. In this design example, the total number of reconfiguration interfaces is 7

(Ch0=2, Ch1=3 and Ch2=2).

• Link the reconfig_to_xcvr and reconfig_from_xcvr signals from the additional SDI duplex

instance at Ch2. You must link the signals in the order of the logical channel number (rx_log_ch_num

and tx_log_ch_num) in the reconfiguration logic source file (sdi_ii_reconfig_logic.v).

• In the design example that instantiates the transceiver reconfiguration controller, add the wire

connection between the additional SDI duplex instance at Ch2 and the transceiver reconfiguration

controller as shown below:

wire [ 139:0] reconfig_to_xcvr_du_ch2;

wire [ 91:0] reconfig_from_xcvr_du_ch2;

wire [ 139:0] reconfig_to_xcvr_tx_ch1;

wire [ 69:0] reconfig_to_xcvr_rx_ch1;

wire [ 91:0] reconfig_from_xcvr_tx_ch1;

wire [ 45:0] reconfig_from_xcvr_rx_ch1;

wire [ 139:0] reconfig_to_xcvr_du_ch0;

wire [ 91:0] reconfig_from_xcvr_du_ch0;

alt_xcvr_reconfig #(

SDI II IP Core Getting Started

Send Feedback

Altera Corporation

Page 35

3-20

Modifying the Reconfiguration Management

.number_of_reconfig_interfaces (7),

….

) u_reconfig (

.reconfig_to_xcvr ({reconfig_to_xcvr_du_ch2,

reconfig_to_xcvr_tx_ch1,

reconfig_to_xcvr_rx_ch1,

reconfig_to_xcvr_du_ch0}),

.reconfig_from_xcvr ({reconfig_from_xcvr_du_ch2,

reconfig_from_xcvr_tx_ch1,

reconfig_from_xcvr_rx_ch1,

reconfig_from_xcvr_du_ch0}),

);

Modifying the Reconfiguration Management

Perform the following changes to modify the reconfiguration management:

• Edit the Number_of_channels parameter in sdi_ii_ed_reconfig_mgmt.v. This parameter value should be

the total number of the SDI RX channels declared in the design. In this example, the NUM_CHS is 3.

• Link the interface signals—sdi_rx_start_reconfig, sdi_rx_reconfig_done, and sdi_rx_std—

between multiple SDI instances and reconfiguration management block. Link the interface signals—

sdi_tx_start_reconfig, sdi_tx_reconfig_done, and sdi_tx_pll_sel—between user and reconfi‐

guration management block. You must link the signals in the order of the logical channel number

(rx_log_ch_num and tx_log_ch_num) in the reconfiguration logic source file (sdi_ii_reconfig_logic.v).

For example:

UG-01125

2015.05.04

wire tx_start_reconfig_ch2,tx_start_reconfig_ch1,tx_start_reconfig_ch0;

wire tx_pll_sel_ch2,tx_pll_sel_ch1,tx_pll_sel_ch0;

wire tx_reconfig_done_ch2,tx_reconfig_done _ch1,tx_reconfig_done_ch0;

wire rx_start_reconfig_ch2,rx_start_reconfig_ch1,rx_start_reconfig_ch0;

wire [1:0] rx_std_ch2, rx_std_ch1,rx_std_ch0;

wire rx_reconfig_done_ch2,rx_reconfig_done _ch1,rx_reconfig_done_ch0;

sdi_ii_ed_reconfig_mgmt #(

. NUM_CHS (3),

) u_reconfig_mgmt (

.sdi_tx_start_reconfig (tx_start_reconfig_ch2,

tx_start_reconfig_ch1,tx_start_reconfig_ch0),

.sdi_tx_pll_sel (tx_pll_sel_ch2,tx_pll_sel_ch1,tx_pll_sel_ch0),

.sdi_tx_reconfig_done (tx_reconfig_done_ch2,

tx_reconfig_done_ch1,tx_reconfig_done_ch0),

.sdi_rx_start_reconfig (rx_start_reconfig_ch2,

rx_start_reconfig_ch1,rx_start_reconfig_ch0),

.sdi_rx_std (rx_std_ch2,rx_std_ch1,rx_std_ch0),

.sdi_rx_reconfig_done (rx_reconfig_done_ch2,

rx_reconfig_done_ch1,rx_reconfig_done_ch0)

)

• In the reconfiguration logic source file, the default setting for the wire rx_log_ch_num is 0 and 2 for

channel 0 and channel 1, respectively. The default setting for the wire tx_log_ch_num is 0 and 2

(duplex) or 3 (TX) for channel 0 and channel 1, respectively. These numbers are referring to the

Number_of_channels parameter value that was set in transceiver reconfiguration controller. Hence,

the logical channel number for each SDI channel is as listed in the table below.

Altera Corporation

SDI II IP Core Getting Started

Send Feedback

Page 36

UG-01125

2015.05.04

Table 3-7: Logical Channel Number For Each SDI Channel

Modifying the Reconfiguration Router

3-21

SDI Channel Direction Number of Reconfiguration

Logical Channel Number

Interfaces

0 Duplex 2 • 0: RX/TX channel

• 1: Tx PLL

1 RX and TX 3 (1 for RX and 2 for TX) • 2: RX channel

• 3: TX channel

• 4: TX PLL

2 Duplex 2 • 5: RX/TX channel

• 6: TX PLL

• Edit the reconfiguration logic source file to assign the logical channel number for the additional SDI

duplex instance, which occupies the SDI Ch2. The logical channel number specified in the source file is

the reconfiguration interface that is intended for dynamic reconfiguration. For example, if TX channel

is intended for dynamic reconfiguration, tx_log_ch_num[2] should be 5.

wire [7:0] rx_log_ch_num [0:NUM_CHS-1];

assign rx_log_ch_num[0] = 8'd0; // Duplex Rx channel share same