Page 1

SDI Audio IP Cores User Guide

Last updated for Altera Complete Design Suite: 14.0

Subscribe

Send Feedback

UG-SDI-AUD

2014.06.30

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

SDI Audio IP Cores User Guide

Contents

SDI Audio IP Overview.......................................................................................1-1

SDI Audio IP Getting Started.............................................................................2-1

SDI Audio IP Functional Description................................................................3-1

Installing and Licensing IP Cores..............................................................................................................2-1

OpenCore Plus IP Evaluation........................................................................................................2-1

IP Catalog and Parameter Editor...............................................................................................................2-2

Specifying IP Core Parameters and Options................................................................................2-3

Simulating Altera IP Cores in other EDA Tools.....................................................................................2-4

SDI Audio Embed IP Core.........................................................................................................................3-1

SDI Audio Embed Parameters.......................................................................................................3-2

SDI Audio Extract IP Core.........................................................................................................................3-4

SDI Audio Extract Parameters.......................................................................................................3-5

SDI Clocked Audio Input IP Core.............................................................................................................3-6

SDI Audio Clocked Audio Input Parameters..............................................................................3-6

SDI Clocked Audio Output IP Core..........................................................................................................3-7

SDI Audio Clocked Audio Output Parameters...........................................................................3-7

AES Format...................................................................................................................................................3-7

Avalon-ST Audio Interface.........................................................................................................................3-8

Instantiating the SDI Audio IP Cores.....................................................................................................3-10

Simulating the Testbench.........................................................................................................................3-10

Guidelines.......................................................................................................................................3-11

SDI Audio IP Interface Signals...........................................................................4-1

SDI Audio IP Registers........................................................................................5-1

Altera Corporation

SDI Audio Embed Signals...........................................................................................................................4-1

SDI Audio Extract Signals...........................................................................................................................4-5

SDI Audio Clocked Input Signals..............................................................................................................4-8

SDI Audio Clocked Output Signals...........................................................................................................4-9

SDI Audio IP Register Interface Signals.................................................................................................4-10

Page 3

SDI Audio IP Cores User Guide

SDI Audio Embed Registers.......................................................................................................................5-1

SDI Audio Extract Registers.......................................................................................................................5-4

SDI Clocked Audio Input Registers..........................................................................................................5-8

SDI Clocked Audio Output Registers.......................................................................................................5-9

TOC-3

SDI Audio IP Design Example............................................................................6-1

Components of Design Example...............................................................................................................6-1

SDI Transmitter P0..........................................................................................................................6-2

SDI Duplex........................................................................................................................................6-2

Audio Extract....................................................................................................................................6-2

AES Input Module...........................................................................................................................6-2

AES Output Module........................................................................................................................6-2

Audio Embed P0/P1........................................................................................................................6-2

Video Pattern Generator P0/P1.....................................................................................................6-2

Audio Pattern Generator................................................................................................................6-2

Ancillary Data Insertion P0/P1......................................................................................................6-2

Transceiver Dynamic Reconfiguration Control Logic...............................................................6-3

Hardware and Software Requirements.....................................................................................................6-3

Running the Design Example.....................................................................................................................6-4

Transmit SD-SDI with Embedding of Audio Group 1...............................................................6-5

Transmit HD-SDI with Embedding of Audio Group 1 and 2...................................................6-5

Transmit 3G-SDI Level A with Embedding of Audio Group 1, 2 and 3..................................6-6

Transmit 3G-SDI Level B with Embedding of Audio Group 1, 2, 3 and 4..............................6-6

Additional Information......................................................................................7-1

Document Revision History.......................................................................................................................7-1

How to Contact Altera................................................................................................................................7-1

Altera Corporation

Page 4

2014.06.30

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI Audio IP Overview

1

UG-SDI-AUD

Subscribe

Send Feedback

The Altera®SDI Audio MegaCore®functions ease the development of video and image processing designs.

For some instances, you combine the audio and video into one digital signal, and at other times you process

the audio and video signals separately.

The SDI Audio IP cores are part of the MegaCore IP Library, which is distributed with the Quartus®II

software and downloadable from the Altera website at www.altera.com.

You can use the following cores to embed, extract or convert audio:

• Audio Embed IP core

• Audio Extract IP core

• Clocked Audio Input IP core

• Clocked Audio Output IP core

You can instantiate the SDI Audio IP cores with the SDI and SDI II IP cores, and configure each Audio IP

core at run time using an Avalon-MM slave interface.

Table 1-1: Brief Information About the SDI Audio IP Cores

14.0Version

DescriptionItem

June 2014Release Date

Release

Informa-

IP-SDIOrdering Code

tion

00E6Product ID(s)

6AF7Vendor ID

Device FamilyIP Core

Information

Arria®II GX, Arria V, Cyclone®IV GX, Cyclone V, and Stratix®IV

GX, and Stratix V FPGA device families.

Refer to the What’s New in Altera IP page of the Altera website for

detailed information.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 5

1-2

SDI Audio IP Overview

Related Information

• Serial Digital Interface (SDI) IP Core User Guide

For information about SDI IP core.

• SDI II IP Core User Guide

For information about SDI II IP core.

UG-SDI-AUD

2014.06.30

Altera Corporation

SDI Audio IP Overview

Send Feedback

Page 6

2014.06.30

acds

quartus - Contains the Quartus II software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

<IP core name> - Contains the IP core source files

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI Audio IP Getting Started

2

UG-SDI-AUD

Subscribe

Send Feedback

Installing and Licensing IP Cores

The Quartus II software includes the Altera IP Library. The library provides many useful IP core functions

for production use without additional license. You can fully evaluate any licensed Altera IP core in simulation

and in hardware until you are satisfied with its functionality and performance. Some Altera IP cores, such

as MegaCore®functions, require that you purchase a separate license for production use. After you purchase

a license, visit the Self Service Licensing Center to obtain a license number for any Altera product.

Figure 2-1: IP Core Installation Path

Note:

The default IP installation directory on Windows is <drive>:\altera\<version number>; on Linux it

is <home directory>/altera/ <version number>.

Related Information

• Altera Licensing Site

• Altera Software Installation and Licensing Manual

OpenCore Plus IP Evaluation

Altera's free OpenCore Plus feature allows you to evaluate licensed MegaCore IP cores in simulation and

hardware before purchase. You need only purchase a license for MegaCore IP cores if you decide to take

your design to production. OpenCore Plus supports the following evaluations:

• Simulate the behavior of a licensed IP core in your system.

• Verify the functionality, size, and speed of the IP core quickly and easily.

• Generate time-limited device programming files for designs that include IP cores.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 7

2-2

IP Catalog and Parameter Editor

• Program a device with your IP core and verify your design in hardware

OpenCore Plus evaluation supports the following two operation modes:

• Untethered—run the design containing the licensed IP for a limited time.

• Tethered—run the design containing the licensed IP for a longer time or indefinitely. This requires a

connection between your board and the host computer.

All IP cores using OpenCore Plus in a design time out simultaneously when any IP core times out.Note:

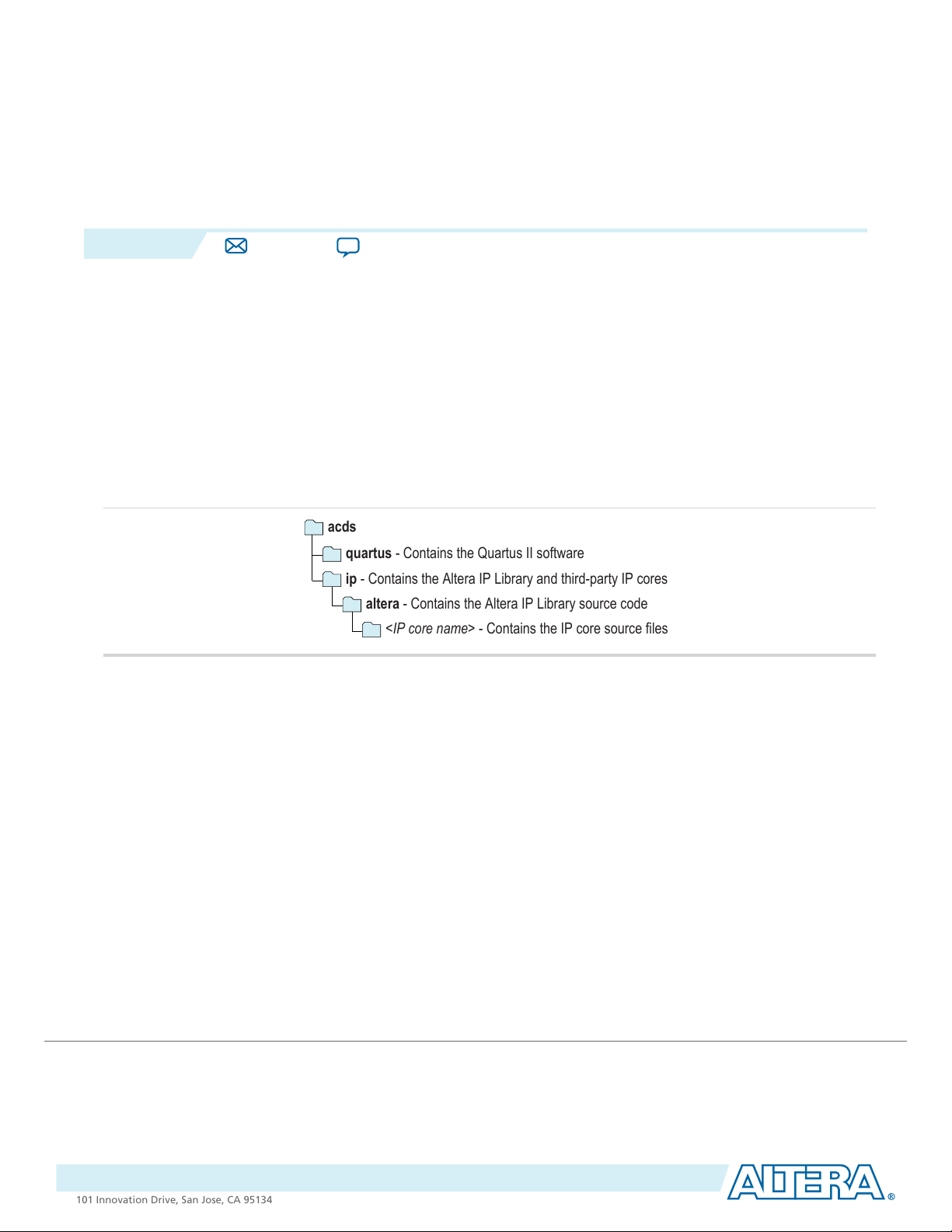

IP Catalog and Parameter Editor

The Quartus II IP Catalog (Tools > IP Catalog) and parameter editor help you easily customize and integrate

IP cores into your project. You can use the IP Catalog and parameter editor to select, customize, and generate

files representing your custom IP variation.

The IP Catalog automatically displays the IP cores available for your target device. Double-click any IP core

name to launch the parameter editor and generate files representing your IP variation. The parameter editor

prompts you to specify your IP variation name, optional ports, architecture features, and output file generation

options. The parameter editor generates a top-level .qsys or .qip file representing the IP core in your project.

Alternatively, you can define an IP variation without an open Quartus II project. When no project is open,

select the Device Family directly in IP Catalog to filter IP cores by device.

UG-SDI-AUD

2014.06.30

Note:

The IP Catalog is also available in Qsys (View > IP Catalog). The Qsys IP Catalog includes exclusive

system interconnect, video and image processing, and other system-level IP that are not available in

the Quartus II IP Catalog.

Use the following features to help you quickly locate and select an IP core:

• Filter IP Catalog to Show IP for active device family or Show IP for all device families.

• Search to locate any full or partial IP core name in IP Catalog. Click Search for Partner IP, to access

partner IP information on the Altera website.

• Right-click an IP core name in IP Catalog to display details about supported devices, installation location,

and links to documentation.

Altera Corporation

SDI Audio IP Getting Started

Send Feedback

Page 8

Search and filter IP for your target device

Double-click to customize, right-click for information

UG-SDI-AUD

2014.06.30

Figure 2-2: Quartus II IP Catalog

Specifying IP Core Parameters and Options

2-3

Note:

The IP Catalog and parameter editor replace the MegaWizard™Plug-In Manager in the Quartus II

software. The Quartus II software may generate messages that refer to the MegaWizard Plug-In

Manager. Substitute "IP Catalog and parameter editor" for "MegaWizard Plug-In Manager" in these

messages.

Specifying IP Core Parameters and Options

Follow these steps to specify IP core parameters and options.

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize.

The parameter editor appears.

2. Specify a top-level name for your custom IP variation. This name identifies the IP core variation files in

your project. If prompted, also specify the target Altera device family and output file HDL preference.

Click OK.

3. Specify parameters and options for your IP variation:

• Optionally select preset parameter values. Presets specify all initial parameter values for specific

applications (where provided).

• Specify parameters defining the IP core functionality, port configurations, and device-specific features.

• Specify options for generation of a timing netlist, simulation model, testbench, or example design

(where applicable).

SDI Audio IP Getting Started

Send Feedback

Altera Corporation

Page 9

2-4

Simulating Altera IP Cores in other EDA Tools

• Specify options for processing the IP core files in other EDA tools.

4. Click Finish or Generate to generate synthesis and other optional files matching your IP variation

specifications. The parameter editor generates the top-level .qip or .qsys IP variation file and HDL files

for synthesis and simulation. Some IP cores also simultaneously generate a testbench or example design

for hardware testing.

5. To generate a simulation testbench, click Generate > Generate Testbench System. Generate Testbench

System is not available for some IP cores that do not provide a simulation testbench.

6. To generate a top-level HDL example for hardware verification, click Generate > HDL Example.

Generate > HDL Example is not available for some IP cores.

The top-level IP variation is added to the current Quartus II project. Click Project > Add/Remove Files in

Project to manually add a .qip or .qsys file to a project. Make appropriate pin assignments to connect ports.

Simulating Altera IP Cores in other EDA Tools

The Quartus II software supports RTL- and gate-level design simulation of Altera IP cores in supported

EDA simulators. Simulation involves setting up your simulator working environment, compiling simulation

model libraries, and running your simulation.

You can use the functional simulation model and the testbench or example design generated with your IP

core for simulation. The functional simulation model and testbench files are generated in a project

subdirectory. This directory may also include scripts to compile and run the testbench. For a complete list

of models or libraries required to simulate your IP core, refer to the scripts generated with the testbench.

You can use the Quartus II NativeLink feature to automatically generate simulation files and scripts.

NativeLink launches your preferred simulator from within the Quartus II software.

UG-SDI-AUD

2014.06.30

Figure 2-3: Simulation in Quartus II Design Flow

Note:

Altera IP supports a variety of simulation models, including simulation-specific IP functional

simulation models and encrypted RTL models, and plain text RTL models. These are all cycle-accurate

models. The models support fast functional simulation of your IP core instance using industrystandard VHDL or Verilog HDL simulators. For some cores, only the plain text RTL model is

generated, and you can simulate that model. Use the simulation models only for simulation and not

for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

Related Information

Simulating Altera Designs

Altera Corporation

SDI Audio IP Getting Started

Send Feedback

Page 10

2014.06.30

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI Audio IP Functional Description

3

UG-SDI-AUD

Subscribe

The following sections describe the block diagrams and components for the SDI Audio IP cores.

• Audio Embed IP core

• Audio Extract IP core

• Clocked Audio Input IP core

• Clocked Audio Output IP core

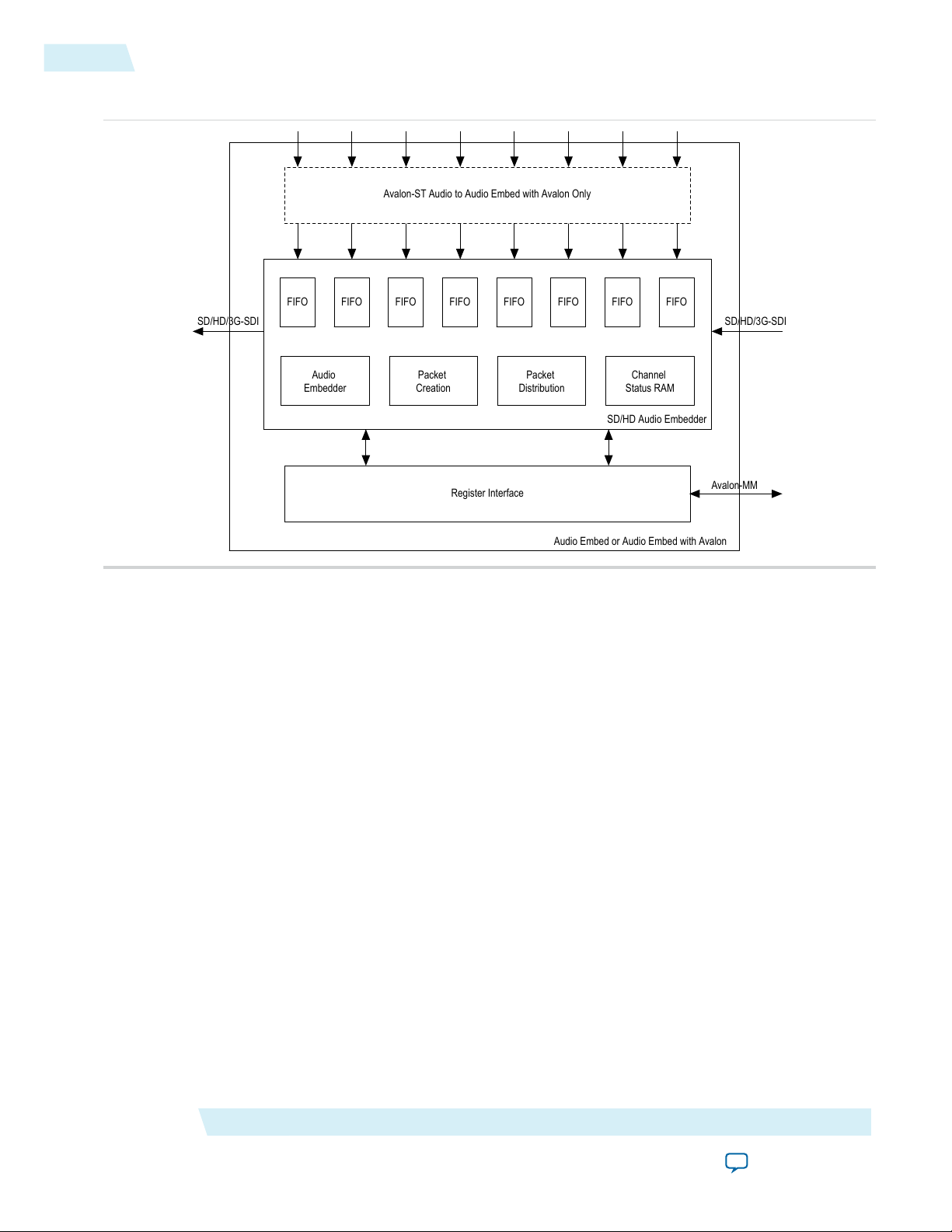

SDI Audio Embed IP Core

The SDI Audio Embed Audio IP core embeds audio into the SD-, HD-, and 3G-SDI video standards.

The format of the embedded audio is in accordance with the following standards:

• SMPTE272M-ABCD standard for SD-SDI

• SMPTE299M standard for HD-SDI

• SMPTE299M standard for 3G-SDI (provisional)

This IP core supports AES audio format for 48-kHz sampling rate

This figure shows a block diagram of the SDI Audio Embed IP core.

Send Feedback

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 11

Avalon-ST Audio to Audio Embed with Avalon Only

FIFO FIFO FIFO FIFO FIFO FIFO FIFO FIFO

Audio

Embedder

SD/HD/3G-SDI SD/HD/3G-SDI

Avalon-MM

Audio Embed or Audio Embed with Avalon

SD/HD Audio Embedder

Packet

Creation

Packet

Distribution

Channel

Status RAM

Register Interface

3-2

SDI Audio Embed Parameters

Figure 3-1: SDI Audio Embed IP Core Block Diagram

UG-SDI-AUD

2014.06.30

The SDI Audio Embed IP core embeds up to 16 channels or 8 channel pairs. The input audio can be any of

the sample rates permitted by the SMPTE272M-ABCD and SMPTE299M standards; synchronous to the

video. If you want to embed audio pairs together in a sample audio group, the audio pairs must be synchronous

with each other.

The SDI Audio Embed IP core consists of the following components:

• An encrypted audio embedder core

• A register interface block that provides support for an Avalon-MM control bus

The audio embedder accepts the audio in AES format, and stores each channel pair in an input FIFO buffer.

As the embedder places the audio sample in the FIFO buffer, it also records and stores the video clock phase

information.

When accepting the audio in AES format, the SDI Audio Embed IP core does one of the following operations:

• maintains the channel-status details

• replaces the channel-status details with the default or the RAM versions

SDI Audio Embed Parameters

The following table lists the parameters for the SDI Audio Embed IP core.

Altera Corporation

SDI Audio IP Functional Description

Send Feedback

Page 12

UG-SDI-AUD

2014.06.30

Table 3-1: SDI Audio Embed Parameters

SDI Audio Embed Parameters

DescriptionValueParameter

3-3

supported audio

groups

Interface

Frequency of fix_

clk

24-bit support

existing audio

1, 2, 3, 4Number of

On or OffAsync Audio

0, 24.576, 25, 50, 100,

200

On or OffInclude SD-SDI

0,1, 2Cleanly remove

Specifies the maximum number of audio groups supported.

Each audio group consists of 4 audio channels (2 channel pairs)

. You must specify all the four channels to the same sample

frequencies.

Turn on to enable the Asynchronous input.

In this mode, the audio clock provides higher than 64* sample

rate.

Sets the expected frequency of the fix_clk input; used as

frequency reference when detecting the difference between video

rate of 1/1.000 or 1/1.001.

Setting this parameter to 0 drives fix_clk low.

Enables the embedding of SD-SDI Extended Data Packets (EDP)

for each audio group.

Enables the removal of existing embedded audio data.

When set to 1, the system requires extra storage to delay the video

and remove any existing audio from SD-SDI, HD-SDI, or 3GSDI Level A standard.

When set to 2, the system includes extra storage to remove the

existing audio from 3G-SDI Level B standard.

RAM

wave generator

ST interface

Select 0 to turn off this parameter.

0,1, 2Channel status

Enables storage of the custom channel status data.

Select 1 to generate a single channel status RAM, or 2 to generate

separate RAMs for each input audio pair.

Select 0 to turn off this parameter.

On or OffFrequency sine

Turn on to enable a four-frequency sine wave generator.

You can use the four-frequency sine wave generator as a test

source for the audio embedder.

On or OffInclude clock

Turn on to enable a 48-kHz pulse generator synchronous to the

video clock. You can use the 48-kHz pulse generator to request

data from a sample rate convertor.

When you turn on the Frequency Sine Wave Generator

parameter, the core automatically includes this pulse generator.

On or OffInclude Avalon-

Turn on to include the SDI Clocked Audio Output IP core.

When you turn on this parameter, the Avalon-ST interface signals

appear at the top level. Otherwise, the audio input signals appear

at the top level.

SDI Audio IP Functional Description

Send Feedback

Altera Corporation

Page 13

Sample FIFO

Clock Recovery

Audio Extract or Audio Extract with Avalon

Avalon-MM

48 KHz Clock

Core

Error Detection

Packet Find

and

Extract

AES

to

Avalon-ST Audio

(Audio Extract

with Avalon Only)

Channel

Status RAM

Register Interface

aud_clk

internal AES

Avalon-ST

Audio

vid_clk

SD/HD/3G-SDI

3-4

SDI Audio Extract IP Core

UG-SDI-AUD

2014.06.30

DescriptionValueParameter

On or OffInclude AvalonMM control

interface

Related Information

SDI Audio Embed Signals on page 4-1

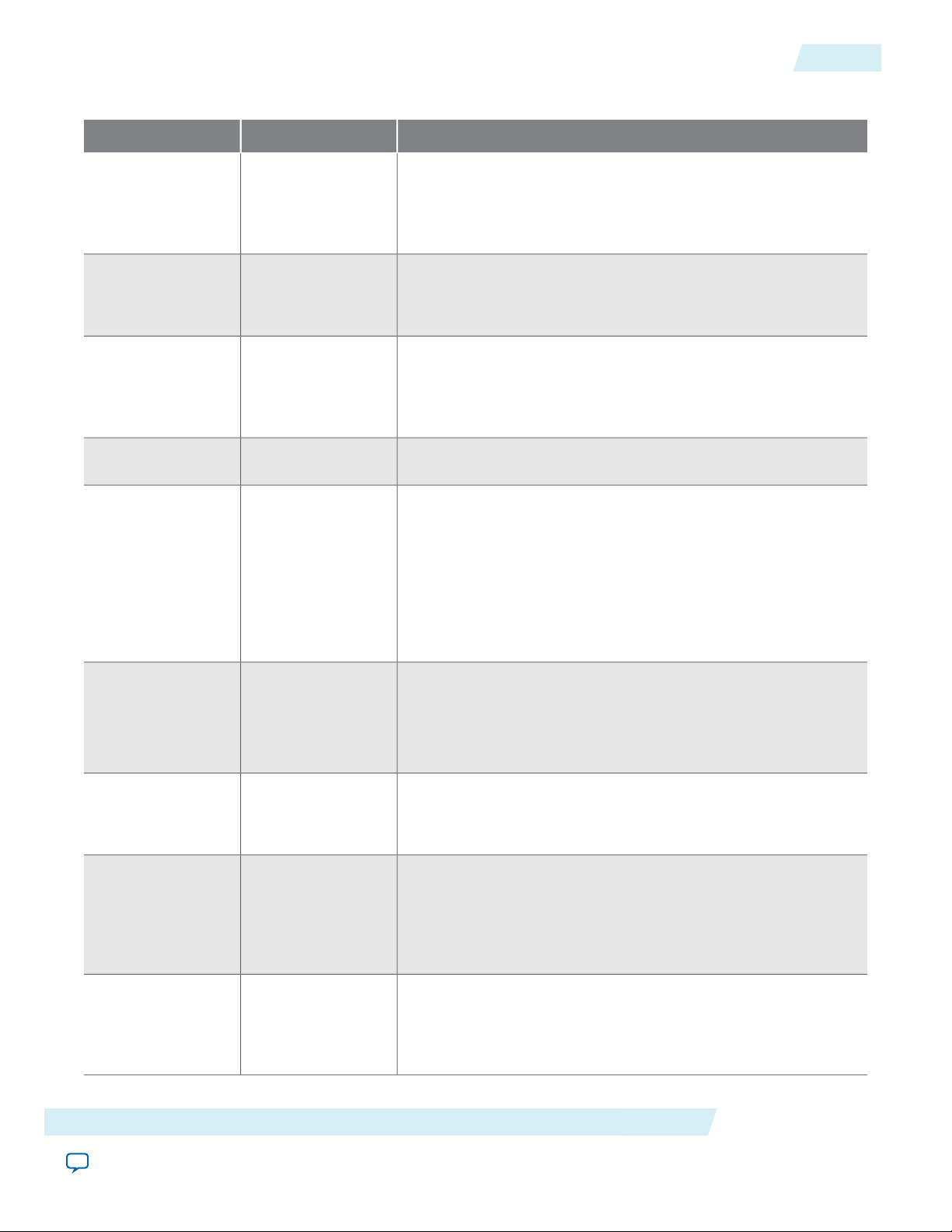

SDI Audio Extract IP Core

The SDI Audio Extract IP core accepts the SD-, HD-, and 3G-SDI from the SDI IP cores and extracts one

channel pair of embedded audio.

The format of the embedded audio is in accordance with the following standards:

• SMPTE272M-ABCD standard for SD-SDI

• SMPTE299M standard for HD-SDI

• SMPTE299M standard for 3G-SDI (provisional)

If you are extracting more than one channel pair, you must use multiple instances of the component. This

IP core supports AES audio format for 48-kHz sampling rate.

This figure shows a block diagram of the SDI Audio Extract IP core.

Turn on to include the Avalon-MM control interface.

When you turn on this parameter, the register interface signals

appear at the top level. Otherwise, the direct control interface

signals appear at the top level.

Figure 3-2: SDI Audio Extract IP Core Block Diagram

The SDI Audio Extract IP core consists of the following components:

• An audio extraction core

Altera Corporation

SDI Audio IP Functional Description

Send Feedback

Page 14

Programmable

Divide

Digital

PLL

Clock Phase

Recovery

vid_clk

Video standard

3.072 MHz Output

24 KHz

200 MHz

Extracted

audio data

/128

SD

HD

UG-SDI-AUD

2014.06.30

SDI Audio Extract Parameters

• A register interface block that provides support for an Avalon-MM control bus

The clock recovery block recreates a 64 × sample rate clock, which you can use to clock the audio output

logic. As the component recreates this clock from a 200-MHz reference clock, the created clock may have a

higher jitter than is desirable.

A digital PLL synchronizes this created clock to a 24-kHz reference source.

For the HD-SDI embedded audio, the 24-kHz reference source is the embedded clock phase information.

For the SD-SDI embedded audio, where the embedded clock phase data is not present, you can create the

24-kHz reference signal directly from the video clock.

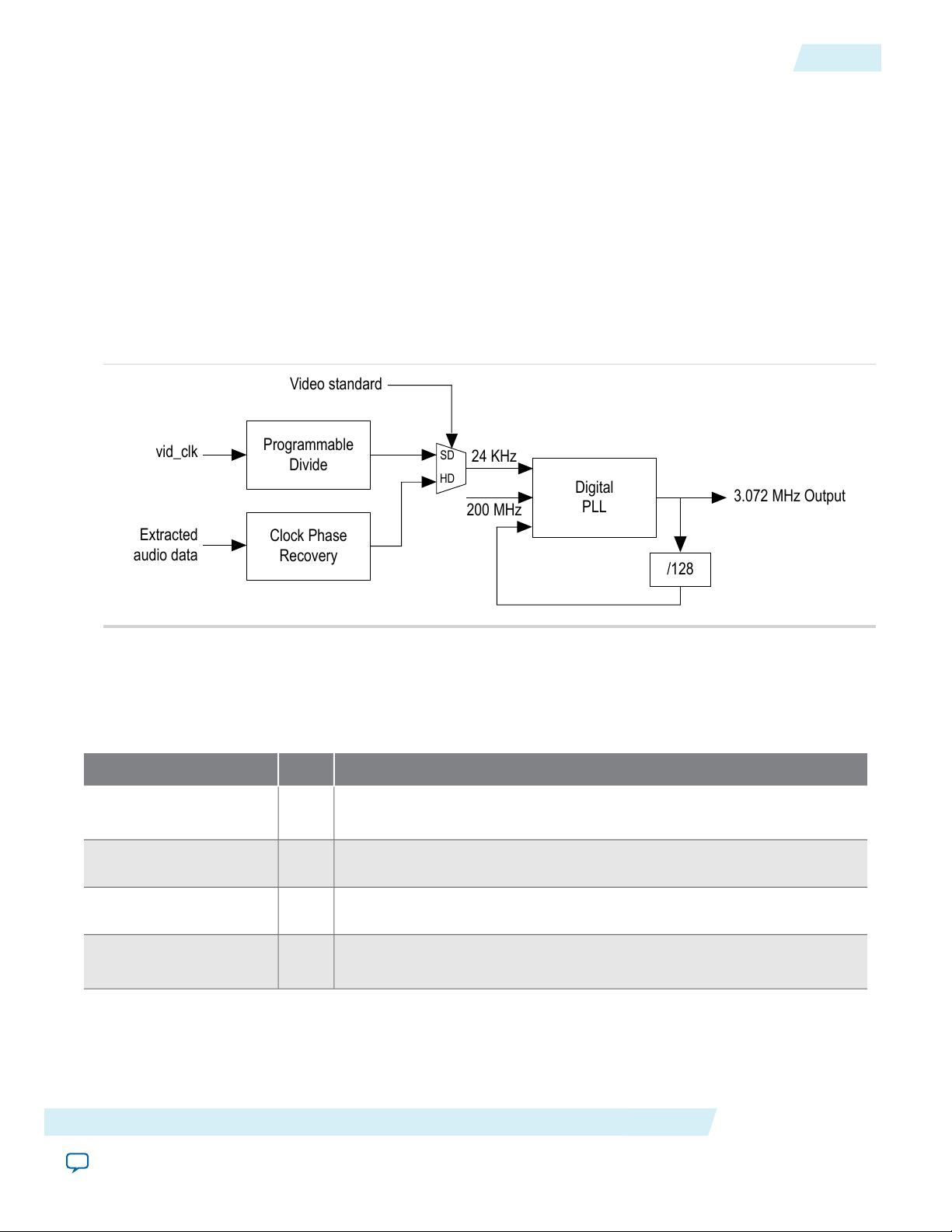

This figure shows the clock recovery block diagram.

Figure 3-3: Clock Recovery Block Diagram

3-5

SDI Audio Extract Parameters

The following table lists the parameters for the SDI Audio Extract IP core.

Table 3-2: SDI Audio Extract Parameters

Include SD-SDI 24-bit

support

Channel status RAM

Include error checking

Include status register

SDI Audio IP Functional Description

Send Feedback

On or

Off

Off

Off

On or

Off

DescriptionValueParameter

Enables the extra logic to recover the EDP ancillary packets from SD-SDI

inputs.

Turn on to store the received channel status data.On or

Turn on to enable extra error-checking logic to use the error status register.On or

Turn on to enable extra logic to report the audio FIFO status on the fifo_

status port or register.

Altera Corporation

Page 15

3-6

SDI Clocked Audio Input IP Core

UG-SDI-AUD

2014.06.30

DescriptionValueParameter

Include clock

On or

Off

Turn on to enable the logic to recover both a sample rate clock and a 64 ×

sample rate clock.

With HD-SDI inputs, the core generates the output by using the embedded

clock phase information.

With SD-SDI inputs, the core generates this output by using the counters

running on the 27-MHz video clock. This generation limits the SD-SDI

embedded audio to being synchronous to the video.

Include Avalon-ST

interface

On or

Off

Turn on to include the SDI Clocked Audio Input IP core.

When you turn on this parameter, the Avalon-ST interface signals appear

at the top level. Otherwise, the audio input signals appear at the top level.

Include Avalon-MM

control interface

On or

Off

Turn on to include the Avalon-MM control interface.

When you turn on this parameter, the register interface signals appear at

the top level. Otherwise, the direct control interface signals appear at the

top level.

Related Information

SDI Audio Extract Signals on page 4-5

SDI Clocked Audio Input IP Core

The Clocked Audio Input IP core converts clocked audio in AES formats to Avalon-ST audio.

For a typical AES input, for each channel, the clocked audio input function does the following operations:

• Creates a 192-bit validity word, user word and channel status word

• Presents the words as a control packet after the audio data packet

SDI Audio Clocked Audio Input Parameters

The following table lists the parameters for the SDI Clocked Audio Input IP cores.

Table 3-3: SDI Clocked Audio Input Parameters

Defines the internal FIFO depth.

For example, a value of 3 means 2³ = 8.

Turn on to include the Avalon-MM control interface.

When you turn on this parameter, the register interface signals appear at

the top level. Otherwise, the direct control interface signals appear at the

top level.

Include Avalon-MM

control interface

3–10FIFO size

On or

Off

DescriptionValueParameter

Altera Corporation

SDI Audio IP Functional Description

Send Feedback

Page 16

clock

aud_de

aud_ws

aud_data

Channel

Status

Parity

Y Preamble

LSB = 1

Z/X Preamble

1/0

Word n - Left Channel 32 bits

Z/X Preamble

LSB = 0

UG-SDI-AUD

2014.06.30

SDI Clocked Audio Output IP Core

The SDI Clocked Audio Output IP core accepts clocked Avalon-ST audio and converts to audio in modified

AES formats.

SDI Audio Clocked Audio Output Parameters

The following table lists the parameters for the SDI Clocked Audio Output IP cores.

Table 3-4: SDI Clocked Audio Output Parameters

SDI Clocked Audio Output IP Core

DescriptionValueParameter

3-7

3–10FIFO size

Defines the internal FIFO depth.

For example, a value of 3 means 2³ = 8.

Include Avalon-MM

control interface

On or

Off

Turn on to include the Avalon-MM control interface.

When you turn on this parameter, the register interface signals appear at

the top level. Otherwise, the direct control interface signals appear at the

top level.

AES Format

The SDI cores use the AES standard. The Audio Engineering Society (AES), together with the European

Broadcasting Union (EBU), created a digital audio transmission standard known as the AES/EBU standard.

The AES standard is a digital audio standard for transporting digital audio signals serially between devices.

Using the AES format requires the entire 64-bit AES frame to be sent serially. As the AES defines the preambles

as biphase mark codes, which cannot be directly decoded to 4 bits, you must replace the preambles with X

= 0000b, Y = 0001b, and Z = 0010b. This internal AES format serializes the bit-parallel data words by sending

the least significant bits (LSB) first, with the audio sample (up to 24 bits).

This figure shows the timing diagram of the internal AES format.

Figure 3-4: Internal AES Format Timing Diagram

SDI Audio IP Functional Description

Send Feedback

Altera Corporation

Page 17

PPreamble 4 bit U CV

AUX data

or

Audio data 4 bit

AES channel pair 1, sub-frame 2 (CH2)

Audio data 20 bit

D0 D192

...

V0 V7

... ...

MSB

Audio Data Packet

Audio Control Packet

LSB

MSB LSB

AUX data (4 bits) Audio data (20 bits) AUX data (4 bits) Audio data (20 bits)

MSB LSB MSB LSB

1st frame

of V bit

24th frame

of V bit

192nd frame

of V bit

3-8

Avalon-ST Audio Interface

Avalon-ST Audio Interface

To allow the standard components inside Qsys to interconnect, you must define the Avalon-ST audio

interface. The Avalon-ST audio interface must carry audio to and from physical AES3 interfaces; which

means to support the AES3 outputs, the interface must transport the extra V, U, and C bits. You may create

the P bit.

Each audio block consists of 192 frames, and each frame has channels 1 and 2. Each frame has a combination

of the bits shown in the following figure.

Figure 3-5: AES Format

UG-SDI-AUD

2014.06.30

The Avalon-ST is a packet-based interface, which carries audio information as a sequence of data packets.

The functions define the types of packets as audio data packets and audio control packets.

This figure shows the audio data and audio control packets for Avalon-ST audio interface.

Figure 3-6: Audio Data and Audio Control Packets for Avalon-ST Audio Interface

The sequence of audio control packets begins with V bit, U bit, and finally C bit. The audio control packets

for U and C bits are similar to V bits.

The Avalon-ST audio protocol separates the audio data from the control or status data to facilitate audio

data processing. The protocol defines that the data is packed LSB first, which matches the AES3 data. The

Altera Corporation

SDI Audio IP Functional Description

Send Feedback

Page 18

sop

Audio data

header identifier

Single channel audio data

(Channel = 1)

Audio data control packet

header identifier (LSB 4 bits)

eop

data [23:0]

channel

A D0

D1

D2

D3

D4

D5

D6

D7

D8

D190 D191

E

V0 V1 V2 V3 V4 V5 V6 V7

U0

C4C5C6

C7

1 1

Audio sample data

Audio control data

UG-SDI-AUD

2014.06.30

audio data size is configurable at compile time and matches the audio data sample size. Including the aux,

the audio data word would be 24 bits.

In Avalon-ST audio, the data is packed as 24 bit symbols, typically with 1 symbol per beat [23:0]. The core

transmits the audio control data as a packet after the audio data to meet the latency requirements.

The packet type identifier defines the packet type. The packet type identifier is the first value of any packet,

when the start of packet signal is high. The audio data packet identifier is 0×A and the audio control data

packet identifier is 0×E.

The table below lists the packet types.

Table 3-5: Avalon-ST Packet Types

Avalon-ST Audio Interface

3-9

DescriptionType Identifier

Video data packet0

User packet types1–8

Audio data packet10

Audio control data packet14

Video control data packet15

Reserved9–15

The preamble data, XYZ from AES, describes whether the data is at the start of a block and which channel

the audio refers to. In Avalon-ST audio protocol, you are not required to transport the preamble data because

the information stored in the data is described by the start of packet, end of packet, and channel signals.

The start of packet, end of packet, and channel signals indicate the start of the audio sample data and the

associated audio channel.

For a single audio channel, the channel signal indicates channel 1 for all valid samples. This figure shows an

example of a single audio channel.

Figure 3-7: Single Audio Channel

For multiple channels, the Avalon-ST interface standard allows the packets to interleave across the channels.

By interleaving, the interface allows multiple audio sources to be multiplexed and demultiplexed.

SDI Audio IP Functional Description

Send Feedback

Altera Corporation

Page 19

sop

eop

data

channel

A D0 A D1

D188 D189

D2 D3

D190D4D191 D188 D189 D190 D191

E E

1 2 1 1 2 1 2 2 21 1

Start of packet for audio

sample data channel 1

End of packet for audio

sample data channel 1

End of packet for audio

sample data channel 2

Channel signal indicates

audio channel number

Control dataControl data

Start of packet for audio

sample data channel 1

3-10

Instantiating the SDI Audio IP Cores

This figure shows an example of two audio channels, where the channel signal indicates either channel 1 or

channel 2. Each channel has a start of packet and an end of packet signal, which allows the channel interleaving

and de-interleaving.

Figure 3-8: Multiple Audio Channels

Instantiating the SDI Audio IP Cores

UG-SDI-AUD

2014.06.30

You can instantiate the SDI Audio Embed and Audio Extract IP cores in the following ways:

• Instantiate within Qsys with the audio inputs exposed outside Qsys.

• Instantiate within Qsys with the audio inputs exposed as Avalon-ST Audio within Qsy.

As the SDI Audio Embed and Extract IP cores use an Avalon-MM slave interface to access the control

registers, the most convenient way for you to instantiate the components are within Qsys. You are provided

with the component declaration TCL files to support either the ordinary AES audio inputs or the AvalonST audio interface.

• Instantiate directly in RTL with a CPU register interface.

You can instantiate the SDI Audio Embed and Audio Extract IP cores directly in your RTL and drive the

direct control interface signals directly without the accompanying Avalon-MM register interface

• Instantiate the encrypted core directly on RTL with control ports.

Simulating the Testbench

Altera provides a fixed testbench as an example to simulate the SDI Audio cores. Use this testbench to

simulate the SDI Audio Embed and the associated SDI Audio Extract IP cores, and the SDI Clocked Audio

Input and the associated SDI Clocked Audio Output IP cores.

You can obtain the testbench from ip/altera/audio_ip/simulation directory.

To use the testbench with the ModelSim simulator, follow these steps:

1. Open the Quartus II software.

2. On the File menu, click the New Project Wizard.

3. Specify the working directory to ip/altera/audio_ip/simulation/megacore_build, and give a sensible

Altera Corporation

name for your project and top-level entity.

4. Click Next, and select Stratix IV for the device family.

SDI Audio IP Functional Description

Send Feedback

Page 20

UG-SDI-AUD

2014.06.30

Guidelines

Guidelines

3-11

5. Click Finish.

6. In the IP Catalog (Tools > IP Catalog), locate and double-click the variant audio_embed_avalon_top.v

file.

The SDI Audio Embed parameter editor appears.

7. In the SDI Audio Embed parameter editor, click Finish to regenerate the variant

audio_embed_avalon_top.v file and produce the simulation model.

8. Repeat steps 6 to 9 for the remaining variant files in the megacore_build directory.

9. In a text editor, open the simulation script, simulation/run.tcl. Edit the script to point to your installation

of the Quartus II software.

For example, set quartusdir /tools/acds/14.0/157/linux32/quartus/eda/sim_lib/

10. Start the ModelSim simulator.

11. Run run.tcl in the simulation directory. This file compiles the design.

A selection of signals appears on the waveform viewer. The simulation runs automatically, providing a

pass or fail indication upon completion.

When you use the testbench to simulate the IP cores, consider the following guidelines:

• Select the video standard for the video test source through the generic G_TEST_STD of the testbench entity.

Set 0, 1, 2 or 3 to select SD-SDI, HD-SDI, 3G-SDI Level A, or 3G-SDI Level B.

• The audio test source uses the 48-kHz clock output from the SDI Audio Embed IP core. The audio test

sample comprises an increasing count which allows the testbench to check the extracted audio at the far

end of the processing chain.

• The SDI Audio Embed IP core accepts these video and audio test sources to create a video stream with

embedded audio. The SDI Audio Extract IP core then receives the resulting stream to recover the embedded

audio. Examine this audio sequence to ensure that the count pattern that was created is preserved.

• The synchronisation requirements of the receive FIFO buffer in the SDI Audio Extract IP core allows

you to repeat the occasional sample from the SDI Audio Extract IP core. Synchronisation may take up

to a field period of typically 16.7 ms to complete.

• Select G_INCLUDE_AVALON_ST = 1, if you want to instantiate another SDI Audio Embed IP core with

Avalon-ST interface (with embedded clocked audio output component) and the associated SDI Audio

Extract IP core with Avalon-ST interface (with embedded clocked audio input component) in this

testbench.

SDI Audio IP Functional Description

Send Feedback

Altera Corporation

Page 21

2014.06.30

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI Audio IP Interface Signals

4

UG-SDI-AUD

Subscribe

Send Feedback

SDI Audio Embed Signals

The following tables list the signals for the SDI Audio Embed IP cores.

This table lists the general input and output signals.

Table 4-1: SDI Audio Embed General Input and Output Signals

This signal resets the system.Input[0:0]reset

Input[0:0]fix_clk

This signal provides the frequency reference used when detecting

the difference between video standards using 1 and 1/1.001 clock

rates. If its frequency is 0, the signal only detects either one of the

clock rates.

The core limits the possible frequencies for this signal to 24.576

MHz, 25 MHz, 50 MHz, 100 MHz, and 200 MHz. Set the required

frequency using the Frequency of fix_clk parameter.

DescriptionDirectionWidthSignal

Input[0:0]vid_std_rate

If you set the Frequency of fix_clk parameter to 0, you must drive

this signal high to detect a video frame rate of 1/1.001 and low to

detect a video frame rate of 1. For other settings of the Frequency

of fix_clk parameter, the core automatically detects these frame

rates and drives this signal low.

Output[0:0]vid_clk48

The 48 kHz output clock that is synchronous to the video. This

clock signal is only available when you turn on the Frequency Sine

Wave Generator or Include Clock parameter.

This table lists the video input and output signals.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 22

4-2

SDI Audio Embed Signals

Table 4-2: SDI Audio Embed Video Input and Output Signals

UG-SDI-AUD

2014.06.30

DescriptionDirectionWidthSignal

Input[0:0]vid_clk

The video clock that is typically 27 MHz for SD-SDI, 74.25 MHz

or 74.17 MHz for HD-SDI, or 148.5 MHz or 148.35 MHz for 3GSDI standards. You can use higher clock rates with the vid_

datavalid signal.

Set exclusive clock group to aud_clk and vid_clk to prevent

unstable or flickering image.

Input[1:0]vid_std

Indicates the received video standard. Applicable for 3G-SDI, dual

standard, and triple standard modes only.

Set this signal to indicate the following formats:

• [00] for10-bit SD-SDI

• [01] for 20-bit HD-SDI

• [10] for 3G-SDI Level B

• [11] for 3G-SDI Level A

Assert this signal when the video data is valid.Input[0:0]vid_datavalid

Input[19:0]vid_data

Receiver protocol reset signal. This signal must be driven by the

rx_rst_proto_out reset signal from the transceiver block.

This signal carries luma and chroma information.

SD-SDI:

• [19:10] Unused

• [9:0] Cb,Y, Cr, Y multiplex

HD-SDI and 3G-SDI Level A:

• [19:10] Y

• [9:0] C

3G-SDI Level B:

• [19:10] Cb,Y, Cr, Y multiplex (link A)

• [9:0] Cb,Y, Cr, Y multiplex (link B)

Output[0:0]vid_out_datavalid

The core drives this signal high during valid output video clock

cycles.

Output[0:0]vid_out_trs

The core drives this signal high during the first 3FF clock cycle of

a video timing reference signal; the first two 3FF cycles for 3G-SDI

Level B. This signal provides easy connection to the SDI IP cores.

Output[10:0]vid_out_ln

The video line signal that provides for easy connection to the SDI

IP cores. To observe the correct video out line number, allow twoframe duration for the audio embed IP to correctly embed and

show the line number.

The video output signal.Output[19:0]vid_out_data

Altera Corporation

SDI Audio IP Interface Signals

Send Feedback

Page 23

UG-SDI-AUD

2014.06.30

This table lists the audio input signals.

Table 4-3: SDI Audio Embed Audio Input Signals

N is the number of audio group.

SDI Audio Embed Signals

DescriptionDirectionWidthSignal

4-3

Input[2N–1:0]aud_clk

Set this clock to 3.072 MHz that is synchronous to the extracted

audio. In asynchronous mode, set this to any frequency above 3.072

MHz. Altera recommends that you set this clock to 50 MHz.

For SD-SDI inputs, this mode of operation limits the core to

embedding audio that is synchronous to the video. For HD-SDI

inputs, this clock must either be generated from the optional 48

Hz output or the audio must be synchronous to the video.

Set exclusive clock group to aud_clk and vid_clk to prevent

unstable or flickering image.

Input[2N–1:0]aud_de

Assert this data enable signal to indicate valid information on the

aud_ws and aud_data signals.

In synchronous mode, the core ignores this signal.

Input[2N–1:0]aud_ws

Assert this word select signal to provide framing for deserialization

and to indicate left or right sample of channel pair.

Internal AES data signal from the AES input module.Input[2N–1:0]aud_data

This table lists the Avalon-ST audio signals when you instantiate the SDI Audio Embed IP core in Qsys.

Table 4-4: SDI Audio Embed Avalon-ST Audio Signals

n is the number of audio channels, the value starts from from 0 to n-1.

Input[0:0]aud(n)_clk

Clocked audio clock. All the audio input signals are synchronous

to this clock.

Output[0:0]aud(n)_ready

Avalon-ST ready signal. Assert this signal when the device is able

to receive data.

Input[0:0]aud(n)_valid

Avalon-ST valid signal. The core asserts this signal when it receives

data.

Input[0:0]aud(n)_sop

Avalon-ST start of packet signal. The core asserts this signal when

it is starting a new frame.

Input[0:0]aud(n)_eop

Avalon-ST end of packet signal. The core asserts this signal when

it is ending a frame.

Avalon-ST select signal. Use this signal to select a specific channel.Input[7:0]aud(n)_channel

Avalon-ST data bus. This bus transfers data.Input[23:0]aud(n)_data

This table lists the register interface signals. The register interface is a standard 8-bit wide Avalon-MM slave.

SDI Audio IP Interface Signals

DescriptionDirectionWidthSignal

Altera Corporation

Send Feedback

Page 24

4-4

SDI Audio Embed Signals

Table 4-5: SDI Audio Embed Register Interface Signals

Clock for the Avalon-MM register interface.Input[0:0]reg_clk

Reset for the Avalon-MM register interface.Input[0:0]reg_reset

Reset for the Avalon-MM register interface.Input[5:0]reg_base_addr

Transfer size in bytes.Input[5:0]reg_burst_count

Wait request.Output[0:0]reg_waitrequest

Write request.Input[7:0]reg_write

Data to be written to target.Input[0:0]reg_writedata

Read request.Input[0:0]reg_read

Requested read data valid after read latency.Output[0:0]reg_readdatavalid

Data read from target.Output[7:0]reg_readdata

UG-SDI-AUD

2014.06.30

DescriptionDirectionWidthSignal

This table lists the direct control interface signals. These signals are exposed as ports if you turn off the

Include Avalon-MM Control Interface parameter.

Table 4-6: SDI Audio Embed Direct Control Interface Signals

Clock for the direct control interface.Input[0:0]reg_clk

Input[7:0]audio_control

Assert this 8-bit signal to enable the audio channels. Each bit

controls one audio channel.

This signal does the same function as the extended control register.Input[7:0]extended_control

This signal does the same function as the video status register.Output[7:0]video_status

This signal does the same function as the SD EDP control register.Output[7:0]sd_edp_control

This signal does the same function as the audio status register.Output[7:0]audio_status

Input[15:0]cs_control

This signal does the same function as the channel status control

register.

This signal does the same function as the strip control register.Input[7:0]strip_control

This signal does the same function as the strip status register.Output[7:0]strip_status

DescriptionDirectionWidthSignal

Altera Corporation

Input[7:0]sine_freq_ch1

This signal does the same function as the sine channel 1 frequency

register.

Input[7:0]sine_freq_ch2

This signal does the same function as the sine channel 2 frequency

register.

Input[7:0]sine_freq_ch3

This signal does the same function as the sine channel 3 frequency

register.

SDI Audio IP Interface Signals

Send Feedback

Page 25

UG-SDI-AUD

2014.06.30

SDI Audio Extract Signals

DescriptionDirectionWidthSignal

4-5

Input[7:0]sine_freq_ch4

Input[0:0]csram_we

Input[7:0]csram_data

Related Information

• SDI Audio Embed Registers on page 5-1

• SDI Audio IP Register Interface Signals on page 4-10

All SDI Audio IP cores use the same register interface signals.

SDI Audio Extract Signals

The following tables list the signals for the SDI Audio Extract IP core.

This signal does the same function as the sine channel 4 frequency

register.

Channel status RAM address.Input[5:0]csram_addr

Drive this signal high for a single cycle of reg_clk signal to load

the value of the csram_data port into the channel status RAM at

the address on the csram_addr port.

If each input audio pair gets separate channel status RAMs, this

signal addresses the RAM selected by the extended_control port.

Channel status data. This signal does the same function as the

channel status RAM register in Table 4–9.

This table lists the clock recovery input and output signals.

Table 4-7: SDI Audio Extract Recovery Input and Output Signals

This signal resets the system.Input[0:0]reset

Input[0:0]fix_clk

Assert this 200 MHz reference clock when you turn on the Include

Clock parameter.

If you do not turn on the Include Clock parameter, tie this signal

low.

Output[0:0]aud_clk_out

The core asserts this 64 × sample rate clock (3.072 MHz audio

clock) when you turn on the Include Clock parameter. You use

this clock to clock the audio interface in synchronous mode.

As the core creates this clock digitally, it is prone to higher levels

of jitter.

Output[0:0]aud_clk48_out

The core asserts this sample rate clock when you turn on the

Include Clock parameter.

This table lists the video input signals.

DescriptionDirectionWidthSignal

SDI Audio IP Interface Signals

Send Feedback

Altera Corporation

Page 26

4-6

SDI Audio Extract Signals

Table 4-8: SDI Audio Extract Video Input Signals

UG-SDI-AUD

2014.06.30

DescriptionDirectionWidthSignal

Input[0:0]vid_clk

The video clock that is typically 27 MHz for SD-SDI, 74.25 MHz

or 74.17 MHz for HD-SDI, or 148.5 MHz or 148.35 MHz for 3GSDI standards. You can use higher clock rates with the vid_

datavalid signal.

Input[1:0]vid_std

Indicates the received video standard. Applicable for 3G-SDI, dual

standard, and triple standard modes only.

Set this signal to indicate the following formats:

• 00b for10-bit SD-SDI

• 01b for 20-bit HD-SDI

• 11b for 3G-SDI Level B

• 10b for 3G-SDI Level A

Assert this signal when the video data is valid.Input[0:0]vid_datavalid

Input[19:0]vid_data

This signal carries luma and chroma information.

SD-SDI:

• [19:10] Unused

• [9:0] Cb,Y, Cr, Y multiplex

HD-SDI and 3G-SDI Level A:

• [19:10] Y

• [9:0] C

3G-SDI Level B:

• [19:10] Cb,Y, Cr, Y multiplex (link A)

• [9:0] Cb,Y, Cr, Y multiplex (link B)

Assert this signal when the video is locked.Input[0:0]vid_locked

This table lists the audio input and output signals.

Table 4-9: SDI Audio Extract Audio Input and Output Signals

Input[0:0]aud_clk

Set this clock to 3.072 MHz that is synchronous to the extracted

audio.

For SD-SDI inputs, this mode of operation limits the core to

extracting audio that is synchronous to the video. For HD-SDI

inputs, you must generate this clock from the optional 48 kHz

output or the audio must be synchronous to the video.

DescriptionDirectionWidthSignal

Altera Corporation

SDI Audio IP Interface Signals

Send Feedback

Page 27

UG-SDI-AUD

2014.06.30

SDI Audio Extract Signals

DescriptionDirectionWidthSignal

4-7

Input[0:0]aud_ws_in

Some audio receivers provide a word select output to align the

serial outputs of several audio extract cores. In these circumstances,

assert this signal to control the output timing of the audio extract

externally, otherwise set it to 0. This signal must be a repeating

cycle of high for 32 aud_clk cycles followed by low for 32 aud_clk

cycles.

Output[0:0]aud_de

Assert this data enable signal to indicate valid information on the

aud_ws and aud_data signals.

In synchronous mode, the core ignores this signal.

The core asserts this data enable signal to indicate valid information

on the aud_ws and aud_data signals.

In synchronous mode, the core drives this signal high.

Output[0:0]aud_ws

The core asserts this word select signal to provide framing for

deserialization and to indicate left or right sample of channel pair.

Output[0:0]aud_data

The core asserts this signal to extract the internal AES audio signal

from the AES output module.

This table lists the Avalon-ST audio signals when you instantiate the SDI Audio Extract IP core in Qsys.

Table 4-10: SDI Audio Extract Avalon-ST Audio Signals

n is the number of audio channels, the value starts from from 0 to n-1.

Input[0:0]aud(n)_clk

Clocked audio clock. All the audio input signals are synchronous

to this clock.

Output[0:0]aud(n)_ready

Avalon-ST ready signal. Assert this signal when the device is able

to receive data.

Input[0:0]aud(n)_valid

Avalon-ST valid signal. The core asserts this signal when it receives

data.

Input[0:0]aud(n)_sop

Avalon-ST start of packet signal. The core asserts this signal when

it is starting a new frame.

Input[0:0]aud(n)_eop

Avalon-ST end of packet signal. The core asserts this signal when

it is ending a frame.

Avalon-ST select signal. Use this signal to select a specific channel.Input[7:0]aud(n)_channel

Avalon-ST data bus. This bus transfers data.Input[23:0]aud(n)_data

This table lists the direct control interface signals. The direct control interface is internal to the SDI Audio

Extract IP core.

DescriptionDirectionWidthSignal

SDI Audio IP Interface Signals

Send Feedback

Altera Corporation

Page 28

4-8

SDI Audio Clocked Input Signals

Table 4-11: SDI Audio Extract Direct Control Interface Signals

Clock for the direct control interface.Input[0:0]reg_clk

This signal does the same function as the audio control register.Input[7:0]audio_control

This signal does the same function as the audio presence register.Input[7:0]audio_presence

This signal does the same function as the audio status register.Output[7:0]audio_status

This signal does the same function as the SD EDP presence register.Output[7:0]sd_edp_presence

This signal does the same function as the error status register.Output[7:0]error_status

UG-SDI-AUD

2014.06.30

DescriptionDirectionWidthSignal

Input[15:0]error_reset

Set any bit of this port high for a single cycle of reg_clk to clear

the corresponding bit of the error_status signal.

Setting any of bits [3:0] high for a clock cycle resets the entire 4-bit

error counter.

This signal does the same function as the FIFO status register.Input[7:0]fifo_status

Input[7:0]fifo_reset

Set high for a single cycle of reg_clk to clear the underflow or

overflow field of the fifo_status signal.

This signal does the same function as the clock status register.Input[7:0]clock_status

Input[5:0]csram_addr

Channel status RAM address. The contents of the selected address

will be valid on the csram_data signal after one cycle of reg_clk.

Input[7:0]csram_data

Channel status data. This signal does the same function as the

channel status RAM.

Related Information

• SDI Audio Extract Registers on page 5-4

• SDI Audio IP Register Interface Signals on page 4-10

All SDI Audio IP cores use the same register interface signals.

SDI Audio Clocked Input Signals

The following tables list the signals for the SDI Audio Clocked Input IP cores.

This table lists the input and output signals.

Table 4-12: SDI Audio Clocked Input Input and Output Signals

Audio input clock.Input[0:0]aes_clk

Audio data enable.Input[0:0]aes_de

Altera Corporation

DescriptionDirectionWidthSignal

SDI Audio IP Interface Signals

Send Feedback

Page 29

UG-SDI-AUD

2014.06.30

Audio word select.Input[0:0]aes_ws

Audio data input in internal AES format.Input[0:0]aes_data

This table lists the Avalon-ST audio signals when you instantiate the SDI Audio Clocked Input IP core in

Qsys.

Table 4-13: SDI Audio Clocked Input Avalon-ST Audio Signals

SDI Audio Clocked Output Signals

DescriptionDirectionWidthSignal

DescriptionDirectionWidthSignal

4-9

Input[0:0]aud_clk

Clocked audio clock. All the audio input signals are synchronous

to this clock.

Input[0:0]aud_ready

Avalon-ST ready signal. Assert this signal when the device is able

to receive data.

Output[0:0]aud_valid

Avalon-ST valid signal. The core asserts this signal when it produces

data.

Output[0:0]aud_sop

Avalon-ST start of packet signal. The core asserts this signal when

it is starting a new frame.

Output[0:0]aud_eop

Avalon-ST end of packet signal. The core asserts this signal when

it is ending a frame.

Avalon-ST data bus. The core asserts this signal to transfer data.Output[23:0]aud_data

This table lists the direct control interface signals. The direct control interface is internal to the audio extract

component.

Table 4-14: SDI Audio Clocked Input Direct Control Interface Signals

Indicates the channel number of audio channel 1.Input[7:0]channel0

Indicates the channel number of audio channel 2.Input[7:0]channel1

DescriptionDirectionWidthSignal

Output[0:0]fifo_reset

Related Information

SDI Audio IP Register Interface Signals on page 4-10

All SDI Audio IP cores use the same register interface signals.

SDI Audio Clocked Output Signals

The following tables list the signals for the SDI Audio Clocked Output IP cores.

SDI Audio IP Interface Signals

Send Feedback

Drive bit 7 high to reset the clocked audio input FIFO buffer.Input[7:0]fifo_status

Assert this signal when the clocked audio input FIFO buffer

overflows.

Altera Corporation

Page 30

4-10

SDI Audio IP Register Interface Signals

This table lists the input and output signals.

Table 4-15: SDI Audio Clocked Output Input and Output Signals

Audio input clock.Input[0:0]aes_clk

Audio data enable.Output[0:0]aes_de

Audio word select.Output[0:0]aes_ws

Audio data input in internal AES format.Output[0:0]aes_data

This table lists the Avalon-ST audio signals when you instantiate the SDI Audio Clocked Output IP core in

Qsys.

Table 4-16: SDI Audio Clocked Output Avalon-ST Audio Signals

UG-SDI-AUD

2014.06.30

DescriptionDirectionWidthSignal

DescriptionDirectionWidthSignal

Input[0:0]aud_clk

Clocked audio clock. All the audio input signals are synchronous

to this clock.

Output[0:0]aud_ready

Avalon-ST ready signal. Assert this signal when the device is able

to receive data.

Input[0:0]aud_valid

Avalon-ST valid signal. The core asserts this signal when it receives

data.

Input[0:0]aud_sop

Avalon-ST start of packet signal. The core asserts this signal when

it is starting a new frame.

Input[0:0]aud_eop

Avalon-ST end of packet signal. The core asserts this signal when

it is ending a frame.

Avalon-ST data bus. This bus transfers data.Input[23:0]aud_data

Related Information

SDI Audio IP Register Interface Signals on page 4-10

All SDI Audio IP cores use the same register interface signals.

SDI Audio IP Register Interface Signals

All SDI Audio IP cores use the same register interface signals.

The register interface is a standard 8-bit wide Avalon-MM slave.

Table 4-17: SDI Audio IP Register Interface Signals

Clock for the Avalon-MM register interface.Input[0:0]reg_clk

Reset for the Avalon-MM register interface.Input[0:0]reg_reset

Altera Corporation

DescriptionDirectionWidthSignal

SDI Audio IP Interface Signals

Send Feedback

Page 31

UG-SDI-AUD

2014.06.30

SDI Audio IP Register Interface Signals

4-11

DescriptionDirectionWidthSignal

Reset for the Avalon-MM register interface.Input[5:0]reg_base_addr

Transfer size in bytes.Input[5:0]reg_burst_count

Wait request.Output[0:0]reg_waitrequest

Write request.Input[7:0]reg_write

Data to be written to target.Input[0:0]reg_writedata

Read request.Input[0:0]reg_read

Requested read data valid after read latency.Output[0:0]reg_readdatavalid

Data read from target.Output[7:0]reg_readdata

SDI Audio IP Interface Signals

Send Feedback

Altera Corporation

Page 32

2014.06.30

www.altera.com

101 Innovation Drive, San Jose, CA 95134

SDI Audio IP Registers

5

UG-SDI-AUD

Subscribe

Send Feedback

SDI Audio Embed Registers

The following tables list the registers for the SDI Audio Embed IP core.

Table 5-1: SDI Audio Embed Register Map

Audio Control Register00h

Extended Control Register01h

Video Status Register02h

SD EDP Control Register03h

Channel Status Control Registers (3:0)04h

Channel Status Control Registers (7:4)05h

Strip Control Register06h

NameBytes Offset

Strip Status Register07h

Sine Channel 1 Frequency08h

Sine Channel 2 Frequency09h

Sine Channel 3 Frequency0Ah

Sine Channel 4 Frequency0Bh

Audio Status Register0Ch

Reserved0Dh-0Fh

Channel Status RAM (0×00), (0×01), ... (0×2F)10h-3Fh

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 33

5-2

SDI Audio Embed Registers

Table 5-2: SDI Audio Embed Registers

UG-SDI-AUD

2014.06.30

DescriptionAccessNameBit

Audio Control Register

RWAudio group enable7:0

Enables the embedding of each audio group. When working

with HD-SDI or 3G-SDI video, this register also enables

the embedding of the audio control packet when one or

more audio groups are enabled.

The following bits correspond to the number of audio

groups you specify:

• Bit [1:0] = Audio group 1

• Bit [3:2] = Audio group 2

• Bit [5:4] = Audio group 3

• Bit [7:6] = Audio group 4

Extended Control Register

RWChannel status RAM select2:0

When you specify the Channel Status RAM parameter

to 2, this field selects the channel pair for the RAM

written to by registers 10h to 3Fh. If you specify the

Channel Status RAM parameter to 0 or 1, ignore this

signal.

Reserved for future use.—Unused3

RWTest sine generator enable4

When set to 1b, this bit ignores the audio inputs and

uses the output of the sine generator as the data for each

audio group.

Altera Corporation

RWLink AB Control6:5

This register applies only for 3G-SDI Level B standard.

Controls which link the ancillary data is embedded in.

• 00b = No data is embedded

• 01b = Data is embedded only in Link B.

• 10b = Data is embedded only in Link A (default

value).

• 11b = Data is embedded in Link A and Link B at the

same time.

When set to 11b, the IP core inserts new packets after

any existing ancillary data on Link A and in the identical

location on Link B.

If the packet distribution of existing ancillary data on

Link B differs, existing packets may be corrupted. In

these circumstances, Altera recommends you use two

separate instances of the ancillary embedder.

Reserved for future use.—Unused7

SDI Audio IP Registers

Send Feedback

Page 34

UG-SDI-AUD

2014.06.30

Video Status Register

SDI Audio Embed Registers

5-3

ROActive channel7:0

Reports the detected video input standard.

• Bits[7:5] = Picture structure code. Defined values for

picture structure code are:

• 001b = 486 or 576 line SD-SDI

• 100b = 720 line HD-SDI

• 101b = 1080 line HD-SDI

• 010b = 1080 line 3G-SDI

• 011b = 1080 line 3GA-SDI

• 110b = 720 line 3GA-SDI

• 111b = 720 line 3GB-SDI

• Bit[4] = 0b—Interlace or segmented frame,

1b—Progressive.

• Bits[3:0] = Frame rate code. Defined values for frame

rate code (in Hz) are:

• 0010b = 23.97

• 0011b = 24

• 0101b = 25

• 0110b = 29.97

• 0111b = 30

• 1001b = 50

• 1010b = 59.94

• 1011b = 60

SD EDP Control Register

RWEnable SD EDP3:0

Enables the embedding of SD-SDI Extended Data

Packets (EDP) for each audio group.

RWEnable SD ACP7:4

Enables the embedding of SD-SDI Audio Control

Packets (ACP) for each audio group.

Channel Status Control Register

RWCS mode select7:0

When set to 00b, the core keeps the existing channel

status data.

When set to 01b, the core replaces the channel status

data with default values.

When set to 10b, the core replaces the data with the

contents of the appropriate channel status RAM.

The following bits correspond to the number of audio

groups you specify:

• Bit [1:0] = Audio group 1

• Bit [3:2] = Audio group 2

• Bit [5:4] = Audio group 3

• Bit [7:6] = Audio group 4

SDI Audio IP Registers

Send Feedback

Altera Corporation

Page 35

5-4

SDI Audio Extract Registers

UG-SDI-AUD

2014.06.30

Strip Control Register

RWStrip enable3:0

Enables the removal of both ACP and ADP (and any

SD-SDI EDP) for each of the four audio groups.

Reserved for future use.—Unused7:4

Strip Status Register

Data packet present3:0

RO

3:0

Reports which audio data groups are detected in the SDI

stream.

When in 3G-SDI Level B mode, this register reports the

presence of audio on Link A (Link B should be a

duplicate).

ROControl packet present7:4

Reports which audio control groups are detected in the

SDI stream.

When in 3G-SDI Level B mode, this register reports the

presence of audio on Link A (Link B should be a

duplicate).

Sine ChannelnFrequency

Defines the frequency of the generated audio.RWSine channel frequency7:0

Audio Status Register

Related Information

SDI Audio Embed Signals on page 4-1

SDI Audio Extract Registers

The following tables list the registers for the SDI Audio Extract IP core.

ROAudio group presence3:0

Reports which audio groups are detected in the SDI

stream.

ROFrame lock4

Reports whether the video frame with the embedded

audio is locked.

Channel Status RAM

WOChannel status data7:0

Write accesses within the address range 10h to 3Fh to

the channel status RAM. This field returns the 24 bytes

of channel status for X channels starting at address 10h

to 27h, and the 24 bytes of channel status for Y channels

starting at address 28h to 3Fh.

Altera Corporation

SDI Audio IP Registers

Send Feedback

Page 36

UG-SDI-AUD

2014.06.30

Table 5-3: SDI Audio Extract Register Map

SDI Audio Extract Registers

NameBytes Offset

5-5

Audio Control Register00h

Audio Presence Register01h

Audio Status Register02h

SD EDP Presence Register03h

Error Status Register04h

Reserved05h

FIFO Status Register06h

Clock Status Register07h

Reserved08h-09h

Channel Status RAM (0×00), (0×01), ... (0×2F)10h-3Fh

Table 5-4: SDI Audio Extract Registers

Audio Control Register

RWEnable0

Enables the audio extraction component and internal AES

output.

RWExtract pair3:1

Defines the audio pair that the component extracts. For

example:

• [000] = Extract the first channel pair of audio signal

• [111] = Extract the eighth channel pair of audio signal

RWExtract pair MSB4

For 3G-SDI Level A standard, this field extends the extract

pair field to allow for future implementations with 32

embedded audio channels.

For 3G-SDI Level B standard, this field selects the active

video half of the 3G multiplex.

Drive this register high to mute the audio output.RWMute5

Reserved for future use.—Unused7:6

DescriptionAccessNameBit

SDI Audio IP Registers

Send Feedback

Altera Corporation

Page 37

5-6

SDI Audio Extract Registers

UG-SDI-AUD

2014.06.30

Audio Presence Register

RWData packet present3:0

When you specify the Channel Status RAM parameter to

2, this field selects the channel pair for the RAM written to

by registers 10h to 3Fh. If you specify the Channel Status

RAM parameter to 0 or 1, ignore this signal.

Reports which audio data groups are detected in the SDI

stream.

The following bits correspond to the number of audio

groups detected:

• Bit [0] = Audio group 1

• Bit [1] = Audio group 2

• Bit [2] = Audio group 3

• Bit [3] = Audio group 4

ROControl packet present7:4

Reports which audio control packets are detected in the

SDI stream.

Audio Status Register

ROActive channel3:0

Reports the detected video input standard.

• Bits[7:5] = Picture structure code. Defined values for

picture structure code are:

• 001b = 486 or 576 line SD-SDI

• 100b = 720 line HD-SDI

• 101b = 1080 line HD-SDI

• 010b = 1080 line 3G-SDI

• Bit[4] = 0b—Interlace or segmented frame,

1b—Progressive.

• Bits[3:0] = Frame rate code. Defined values for frame

rate code (in Hz) are:

• 0010b = 23.97

• 0011b = 24

• 0101b = 25

• 0110b = 29.97

• 0111b = 30

• 1001b = 50

• 1010b = 59.94

• 1011b = 60

RWAsynchronous4

Reflects the asx bit of the RATE (sampling rate) field of the

audio control packet.