Page 1

SDC and TimeQuest API Reference Manual

101 Innovation Drive

San Jose, CA 95134

www.altera.com

MNL-SDCTMQ-5.0

Page 2

Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other

words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other

countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty,

but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of

any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders for products or services

.

MNL-SDCTMQ-5.0

Page 3

Contents

About this Reference Manual

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1–vii

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1–vii

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–viii

Chapter 1. Introduction to the SDC and TimeQuest API Reference Manual

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

What's Inside the SDC and TimeQuest API Reference Manual? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

TimeQuest Timing Analyzer Scripting Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Related Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Chapter 2. SDC and TimeQuest API Package and Commands

sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

all_clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

all_inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

all_outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

all_registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

create_clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

create_generated_clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

derive_clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

get_cells . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

get_clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

get_nets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

get_pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

get_ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

remove_clock_groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

remove_clock_latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–19

remove_clock_uncertainty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

remove_disable_timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

remove_input_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

remove_output_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–23

reset_design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–24

set_clock_groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–25

set_clock_latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–26

set_clock_uncertainty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–28

set_disable_timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–29

set_false_path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–30

set_input_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–32

set_input_transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–34

set_max_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–35

set_min_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–37

set_multicycle_path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39

set_output_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–41

sdc_ext . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–43

derive_clock_uncertainty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–44

derive_pll_clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–45

get_assignment_groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–46

get_fanins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–47

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 4

iv Contents

get_fanouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–48

get_keepers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–49

get_nodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–50

get_partitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–51

get_registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–52

remove_annotated_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–53

remove_clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–54

reset_timing_derate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–55

set_active_clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–56

set_annotated_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–57

set_max_skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–58

set_net_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–60

set_scc_mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–61

set_time_format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–62

set_timing_derate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–63

sta . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–64

add_to_collection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–67

check_timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–68

create_report_histogram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–70

create_slack_histogram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–72

create_timing_netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–74

create_timing_summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–76

delete_timing_netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–77

enable_ccpp_removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–78

enable_sdc_extension_collections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–79

get_available_operating_conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–80

get_cell_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–81

get_clock_domain_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–82

get_clock_fmax_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–83

get_clock_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–84

get_datasheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–86

get_default_sdc_file_names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–88

get_edge_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–89

get_edge_slacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–90

get_min_pulse_width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–91

get_net_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–92

get_node_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–93

get_object_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–94

get_operating_conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–95

get_operating_conditions_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–96

get_partition_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–97

get_path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–98

get_path_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–100

get_pin_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–103

get_point_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–104

get_port_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–107

get_register_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–108

get_timing_paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–109

locate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–112

query_collection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–114

read_sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . 2–115

remove_from_collection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–116

report_advanced_io_timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–117

report_bottleneck . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–118

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 5

Contents v

report_clock_fmax_summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–120

report_clock_transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–121

report_clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–122

report_datasheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–123

report_ddr . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–124

report_exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–125

report_max_skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–129

report_metastability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–132

report_min_pulse_width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–135

report_net_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–137

report_net_timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–138

report_partitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–139

report_path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–140

report_rskm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–142

report_sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–143

report_skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–144

report_tccs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–147

report_timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–148

report_ucp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–152

set_operating_conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–153

timing_netlist_exist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–154

update_timing_netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–155

use_timequest_style_escaping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–156

write_sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–157

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 6

vi Contents

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 7

This manual provides comprehensive information about SDC and TimeQuest API

operations.

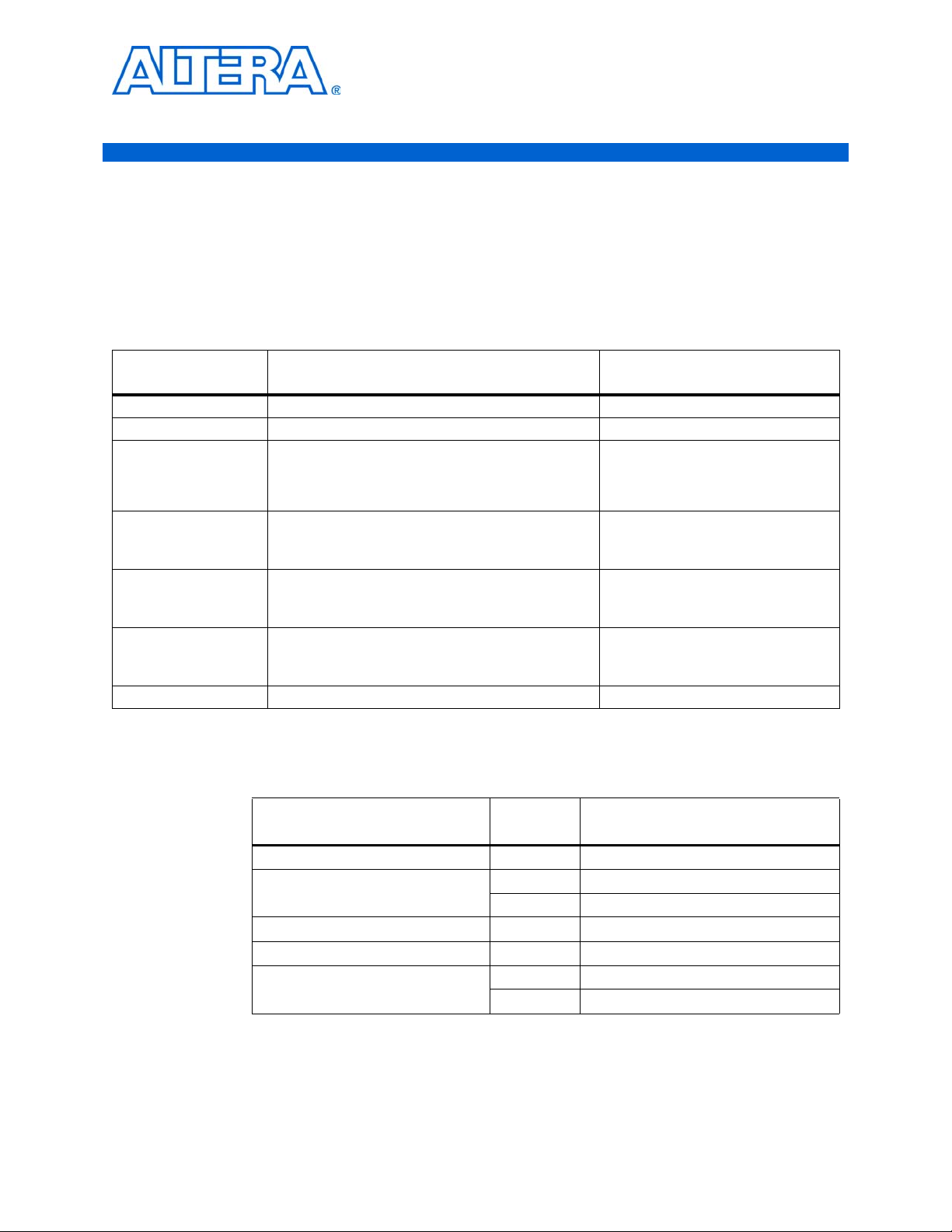

Revision History

The following table shows the revision history for this manual.

About this Reference Manual

Date and

Document Version

December 2009, v5.0

March 2009, v4.0

November 2008, v3.1

July 2008, v3.0

December 2007, v2.0

March 2007, v1.1

May 2006, v1.0

■ Updated for Quartus II version 9.1 —

■ Updated for Quartus II version 9.0 —

■ Updated for Quartus II version 8.1

■ Added Revision History to this reference manual

■ Updated new document template

■ Updated for Quartus II version 8.0

■ Updated for Quartus II version 7.2

■ Updates to sdc, sdc_ext, and sta API operations.

■ Added Revision History to this reference manual.

■ Initial release. —

How to Contact Altera

For the most up-to-date information about Altera® products, see the following table.

Contact (Note 1)

Technical support Website www.altera.com/support

Technical training

Product Literature Website www.altera.com/literature

Altera literature services Email literature@altera.com

Non-technical support (General) Email nacomp@altera.com

(Software Licensing) Email authorization@altera.com

Note:

(1) You can also contact your local Altera sales office or sales representative.

Changes Made Summary of Changes

—

Updated the sdc and TimeQuest API

operations based on the latest

Quartus II software release.

Updated the sdc and TimeQuest API

operations based on the latest

Quartus II software release.

Updated the sdc and TimeQuest API

operations based on the latest

Quartus II software release.

Contact

Method

Address

Website www.altera.com/training

Email custrain@altera.com

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 8

viii

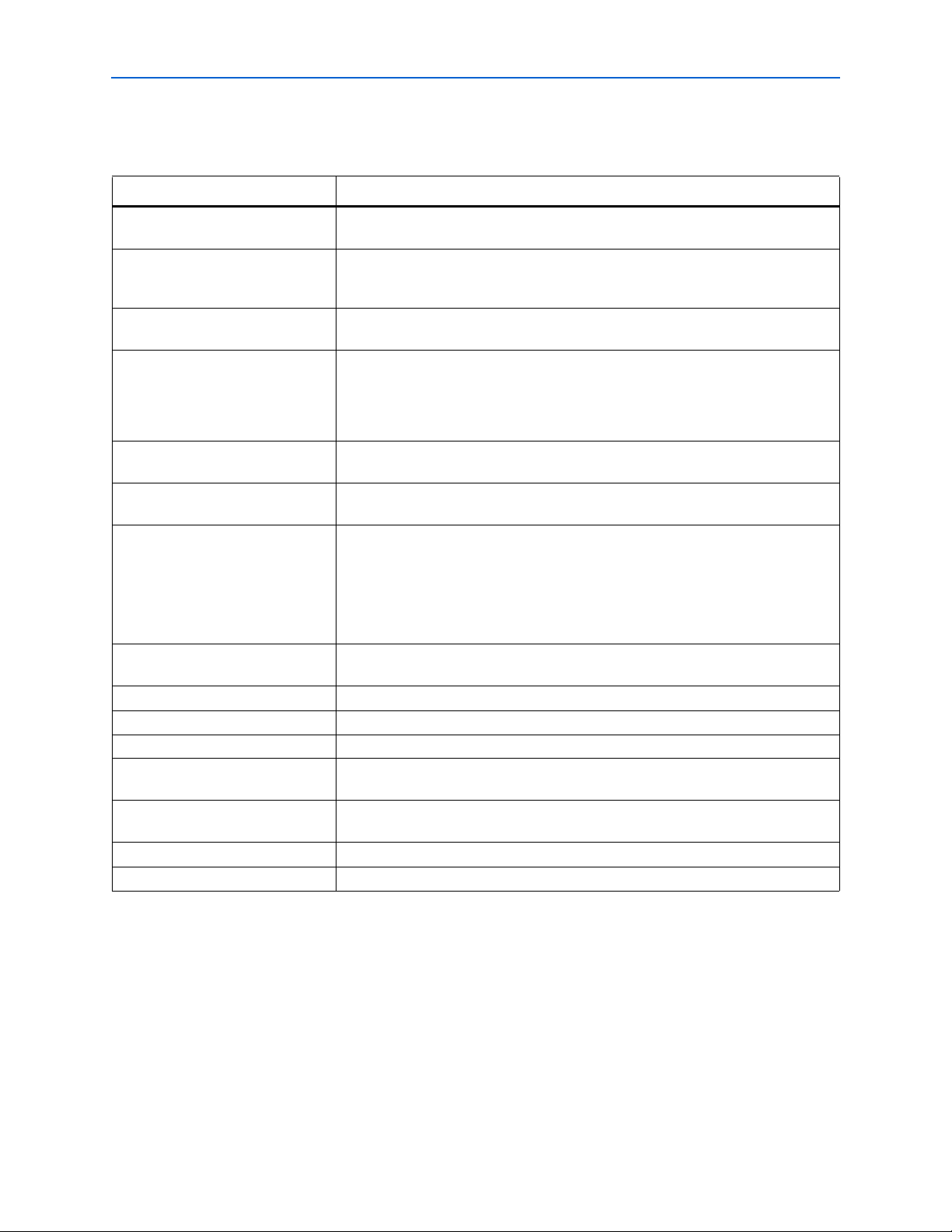

Typographic Conventions

Typographic Conventions

The following table shows the typographic conventions that this document uses.

Visual Cue Meaning

Bold Type with Initial Capital

Letters

bold type

Italic Type with Initial Capital Letters

Italic type

Initial Capital Letters

“Subheading Title”

Courier type

1., 2., 3., and

a., b., c., etc.

■ ■ Bullets are used in a list of items when the sequence of the items is not important.

v The checkmark indicates a procedure that consists of one step only.

1 The hand points to information that requires special attention.

c

w

r The angled arrow indicates you should press the Enter key.

f The feet direct you to more information on a particular topic.

Command names, dialog box titles, checkbox options, and dialog box options are

shown in bold, initial capital letters. Example: Save As dialog box.

External timing parameters, directory names, project names, disk drive names, file

names, file name extensions, and software utility names are shown in bold type.

Examples: f

, \qdesigns directory, d: drive, chiptrip.gdf file.

MAX

Document titles are shown in italic type with initial capital letters. Example: AN 75:

High-Speed Board Design.

Internal timing parameters and variables are shown in italic type.

Examples: t

PIA

, n + 1.

Variable names are enclosed in angle brackets (< >) and shown in italic type.

Example: <file name>, <project name>.pof file.

Keyboard keys and menu names are shown with initial capital letters. Examples:

Delete key, the Options menu.

References to sections within a document and titles of on-line help topics are shown

in quotation marks. Example: “Typographic Conventions.”

Signal and port names are shown in lowercase Courier type. Examples:

input. Active-low signals are denoted by suffix n, e.g., resetn.

data1, tdi,

Anything that must be typed exactly as it appears is shown in Courier type. For example:

c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file,

such as a Report File, references to parts of files (e.g., the AHDL keyword

SIGN

), as well as logic function names (e.g., TRI) are shown in Courier.

SUBDE-

Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.

A caution calls attention to a condition or possible situation that can damage or

destroy the product or the user’s work.

A warning calls attention to a condition or possible situation that can cause injury to

the user.

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 9

Introduction to the SDC and TimeQuest

API Reference Manual

Introduction

The TimeQuest timing analyzer is a powerful ASIC-style timing analysis tool that

validates the timing performance of all logic in a design using industry standard

constraint, analysis, and reporting methodology.

The TimeQuest timing analyzer includes support for Synopsis Design Constraints

(SDC). Additionally, the TimeQuest timing analyzer includes an extensive tool

command language (Tcl) scripting API. This reference manual includes the supported

SDC constraints and commands, and the TimeQuest Tcl API commands.

This overview covers the TimeQuest timing analyzer support for scripted operation.

At the end of this overview is a table of additional documentation and resources.

What's Inside the SDC and TimeQuest API Reference Manual?

The Quartus II SDC and TimeQuest API Reference Manual is your reference guide to

TimeQuest timing analyzer constraints and commands, including command details,

usage, and examples.

All the information included in the Quartus II SDC and TimeQuest API Reference

Manual, as well as the most up-to-date list of commands, can also be found in the

Quartus II software Tcl API and command-line executable online help reference,

Qhelp. To access this information within Quartus II design software, type the

following command at the command prompt:

quartus_sh --qhelpr

TimeQuest Timing Analyzer Scripting Support

The sdc and sta packages are supported in the quartus_sta command-line executable.

The sdc package contains the Synopsys Design Constraints (SDC) functions used to

specify constraints and exceptions to the TimeQuest timing analyzer.

The sta package contains the set of Tcl functions for obtaining advanced information

from the TimeQuest timing analyzer.

The quartus_sta command-line executable validates the timing performance of all

logic in a design using industry standard constraint, analysis, and reporting

methodology. You can use the TimeQuest analyzer's graphical user interface (GUI) or

command-line interface to constrain, run, and view results for all timing paths in your

design.

f For information about other command-line executables and Tcl packages, refer to the

Quartus II Scripting Reference Manual.

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 10

1-2 Introduction to the SDC and TimeQuest API Reference Manual

Related Documentation

Related Documentation

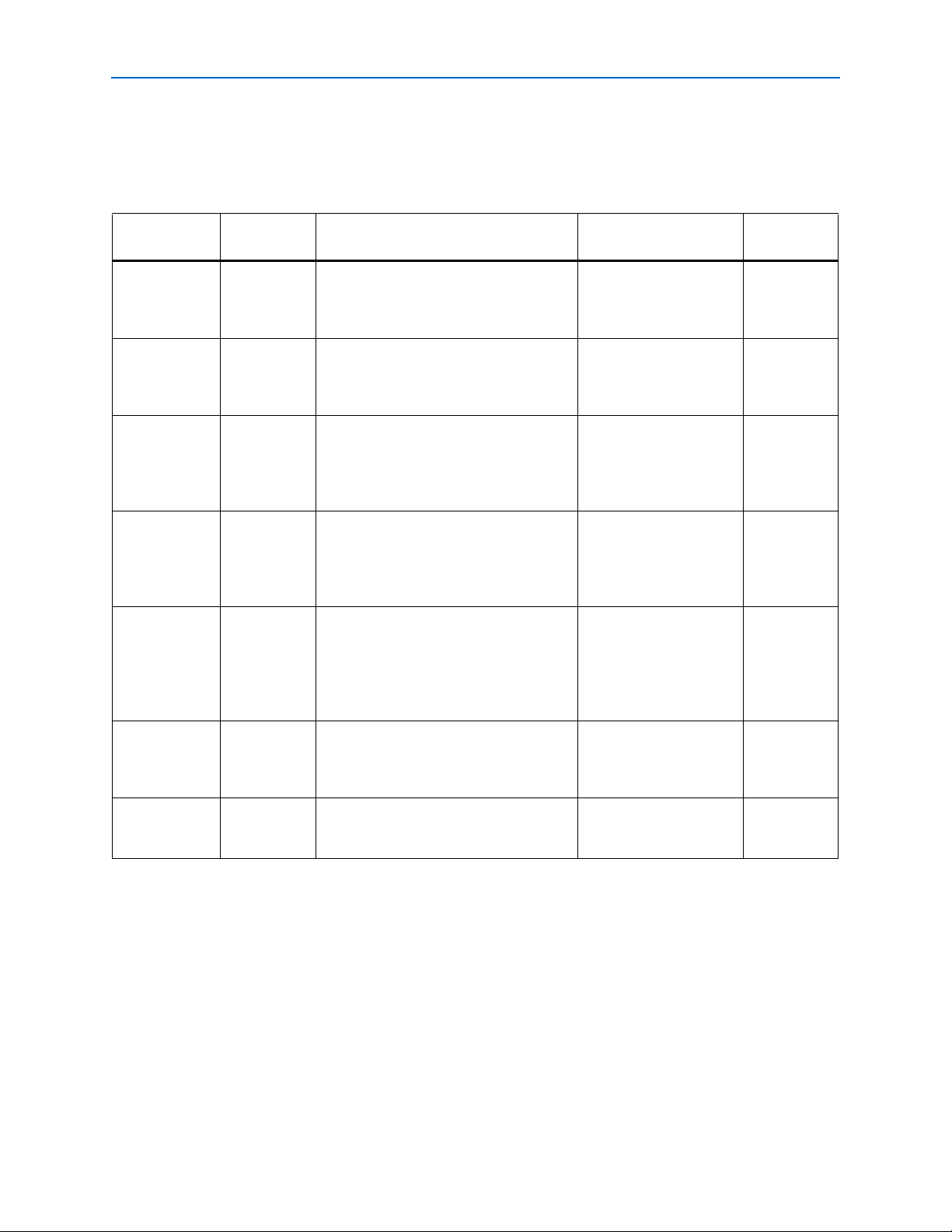

Tab le 1 presents additional resources and documentation for the Quartus II

development software.

Table 1. Quartus II Software Resources and Documentation

Resource Name

Quartus II

Online

Demonstration

Introduction to

Quartus II

Manual

Scripting and

Constraint Entry

section of the

Quartus II

Handbook

Qhelp

Enhance Your

FPGA Design

Flow With

Command-Line

and Tcl

Scripting

Design

Examples

Online Training

Resource

Type

Videos www.altera.com/quartusdemos

PDF

PDF www.altera.com/literature/lit-qts.jsp

Quartus II

software

online help

Net Seminar

(one hour)

html

PowerPoint

(PPT) and

audio

www.altera.com/literature/manual/intro_to

_quartus2.pdf

quartus_sh --qhelp from the

Run

command line

www.altera.com/education/net_seminars/p

ast/ns-tcl.html

www.altera.com/support/examples/quartu

s/quartus.html

www.altera.com/training

Access Description User Level

Demonstration of the

Quartus II software

command-line operation

and scripting features.

An overview of the

capabilities of Quartus II

software in programmable

logic design.

Detailed instruction for

command-line operation

and Tcl scripting in

Quartus II software.

Detailed listing of all

command-line

executables and Tcl

commands including

usage examples.

Overview of Quartus II

command-line operation

and scripting support.

Instructions for

implementing various

functions using Quartus II

design software.

Detailed instruction

examples.

Beginning to

Advanced

Beginning to

Intermediate

Beginning to

Advanced

Beginning to

Advanced

Beginning to

Intermediate

Beginning to

Advanced

Beginning to

Advanced

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 11

2. SDC and TimeQuest API Package and Commands

sdc

Synopsys Design Constraint (SDC) format is used to specify the design intent, including the timing and

area constraints of the design. The TimeQuest Timing Analyzer only implements the set of SDC

commands required to specify the timing constraints of the design. For area constraints, the QSF file

should be used.

This package implements the SDC Spec Version 1.5 (June 2005).

Any command in this package can be specified in a TimeQuest SDC file.

This package is loaded by default in the following executable:

■ quartus_sta

This package is available for loading in the following executable:

■ quartus_map

This package includes the following commands:

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 12

2–2 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

Command Page

all_clocks ................................................................................................................................................... 2–3

all_inputs................................................................................................................................................... 2–4

all_outputs ................................................................................................................................................ 2–5

all_registers ............................................................................................................................................... 2–6

create_clock............................................................................................................................................... 2–7

create_generated_clock ........................................................................................................................... 2–8

derive_clocks .......................................................................................................................................... 2–10

get_cells ................................................................................................................................................... 2–11

get_clocks ................................................................................................................................................ 2–13

get_nets.................................................................................................................................................... 2–14

get_pins ................................................................................................................................................... 2–15

get_ports.................................................................................................................................................. 2–17

remove_clock_groups ........................................................................................................................... 2–18

remove_clock_latency ........................................................................................................................... 2–19

remove_clock_uncertainty.................................................................................................................... 2–20

remove_disable_timing......................................................................................................................... 2–21

remove_input_delay.............................................................................................................................. 2–22

remove_output_delay ........................................................................................................................... 2–23

reset_design ............................................................................................................................................ 2–24

set_clock_groups.................................................................................................................................... 2–25

set_clock_latency.................................................................................................................................... 2–26

set_clock_uncertainty ............................................................................................................................ 2–28

set_disable_timing ................................................................................................................................. 2–29

set_false_path ......................................................................................................................................... 2–30

set_input_delay ...................................................................................................................................... 2–32

set_input_transition............................................................................................................................... 2–34

set_max_delay ........................................................................................................................................ 2–35

set_min_delay......................................................................................................................................... 2–37

set_multicycle_path ............................................................................................................................... 2–39

set_output_delay.................................................................................................................................... 2–41

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 13

Chapter 2: SDC and TimeQuest API Package and Commands 2–3

sdc

all_clocks

Usage

all_clocks

Options

None

Description

Returns a collection of all clocks in the design.

Example

project_open chiptrip

create_timing_netlist

foreach_in_collection clk [all_clocks] {

puts [get_clock_info -name $clk]

}

delete_timing_netlist

project_close

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 14

2–4 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

all_inputs

Usage

all_inputs

Options

None

Description

Returns a collection of all input ports in the design.

Example

project_open chiptrip

create_timing_netlist

foreach_in_collection in [all_inputs] {

puts [get_port_info -name $in]

}

set_input_delay -clock clock1 2.0 [all_inputs]

delete_timing_netlist

project_close

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 15

Chapter 2: SDC and TimeQuest API Package and Commands 2–5

sdc

all_outputs

Usage

all_outputs

Options

None

Description

Returns a collection of all output ports in the design.

Example

project_open chiptrip

create_timing_netlist

foreach_in_collection out [all_outputs] {

puts [get_port_info -name $out]

}

set_output_delay -clock clock1 2.0 [all_outputs]

delete_timing_netlist

project_close

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 16

2–6 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

all_registers

Usage

all_registers

Options

None

Description

Returns a collection of all regisers in the design.

Example

project_open chiptrip

create_timing_netlist

foreach_in_collection reg [all_registers] {

puts [get_register_info -name $reg]

}

report_timig -from [all_regisers] -to [all_registers]

delete_timing_netlist

project_close

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 17

Chapter 2: SDC and TimeQuest API Package and Commands 2–7

sdc

create_clock

Usage

create_clock [-add] [-name <clock_name>] -period <value> [-waveform <edge_list>]

<targets>

Options

-add: Adds clock to a node with an existing clock

-name <clock_name>: Clock name of the created clock

-period <value>: Speed of the clock in terms of clock period

-waveform <edge_list>: List of edge values

<targets>: List or collection of targets

Description

Defines a clock. If the -name option is not used, the clock name is the same as the first target in the list or

collection. The clock name is used to refer to the clock in other commands.

The -period option specifies the clock period. It is also possible to use this option to specify a frequency to

define the clock period. This can be done by using -period option followed by either <frequency>MHz or

"<frequency> MHz". However, this is a TimeQuest-only extension and makes the SDC syntax

non-standard.

The -waveform option specifies the rising and falling edges (duty cycle) of the clock, and is specified as a

list of two time values: the first rising edge and the next falling edge. The rising edge must be within the

range [0, period]. The falling edge must be within one clock period of the rising edge. The waveform

defaults to (0, period/2).

If a clock with the same name is already assigned to a given target, the create_clock command will

overwrite the existing clock. If a clock with a different name exists on the given target, the create_clock

command will be ignored unless the -add option is used. The -add option can be used to assign multiple

clocks to a pin or port.

If the target of the clock is internal (i.e. not an input port), the source latency is zero by default.

If a clock is on a path after another clock, then it blocks or overwrites the previous clock from that point

forward.

The value of the targets is either a collection or a Tcl list of wildcards used to create a collection of the

appropriate type. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See the help for use_timequest_style_escaping for details.

Example

# Create a simple 10ns with clock with a 60% duty cycle

create_clock -period 10 -waveform {0 6} -name clk [get_ports clk]

# Create a clock with a falling edge at 2ns, rising edge at 8ns,

# falling at 12ns, etc.

create_clock -period 10 -waveform {8 12} -name clk [get_ports clk]

# Assign two clocks to an input port that are switched externally

create_clock -period 10 -name clk100Mhz [get_ports clk]

create_clock -period 6.667 -name clk150Mhz -add [get_ports clk]

# Two ways to use MHz to define clock period (TimeQuest only)

create_clock -period 250MHz -name clk250MHz [get_ports clk]

create_clock -period "250 MHz" -name clk250MHz [get_ports clk]

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 18

2–8 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

create_generated_clock

Usage

create_generated_clock [-add] [-divide_by <factor>] [-duty_cycle <percent>]

[-edge_shift <shift_list>] [-edges <edge_list>] [-invert] [-master_clock <clock>]

[-multiply_by <factor>] [-name <clock_name>] [-offset <time>] [-phase <degrees>]

-source <clock_source> <targets>

Options

-add: Add clock to existing clock node

-divide_by <factor>: Division factor

-duty_cycle <percent>: Specifies the duty cycle as a percentage of the clock

period--accepts floating point values

-edge_shift <shift_list>: List of edge shifts

-edges <edge_list>: List of edge values

-invert: Invert the clock waveform

-master_clock <clock>: Specifies clock of the source node

-multiply_by <factor>: Multiplication factor

-name <clock_name>: Name of generated clock

-offset <time>: Specifies the offset as an absolute time shift

-phase <degrees>: Specifies the phase shift in degrees

-source <clock_source>: Source node for the generated clock

<targets>: List or collection of targets

Description

Defines an internally generated clock. If -name is not specified, the clock name is the same as the first

target in the list or collection. The clock name is used to refer to the clock in other commands.

If a clock with the same name is already assigned to a given target, the create_generated_clock command

will overwrite the existing clock. If a clock with a different name exists on the given target, the

create_generated_clockcommand will be ignored unless the -add option is used. The -add option can be

used to assign multiple clocks to a pin or port, and is recommended be used with -master_clock option.

The source of the generated clock, specified by -source, is a port, pin, register, or net in the design. All

waveform modifications are relative to this point. If more than one clock feeds the source node, the

-master_clock option must be used to specify which clock to modify.

The source latency of the generated clock is based on the clock network of the generated clock, and not the

clock network of the node specified using -source. This latency is added to any source latency of the

master clock.

The -divide_by, -multiply_by, -invert, -duty_cycle, -edges, and -edge_shift options modify the waveform

relative to the waveform at the source node.

Clock division and multiplication, using -divide_by and -multiply_by, is performed relative to the first

rising edge. Clock division is based on edges in the master clock waveform, and scaled if the division is an

odd number. Use the -duty_cycle option to specify the new duty cycle for clock multiplication. Use the

-phase option to specify any phase shift relative to the new clock period. Use the -offset option to specify

an arbitrary offset or time shift. Use the -invert option to invert the waveform.

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 19

Chapter 2: SDC and TimeQuest API Package and Commands 2–9

sdc

Clock generation can also be specified with the -edges and -edge_shift options. The -edges option accepts a

list of three numbers specifying the master clock edges to use for the first rising edge, the next falling edge,

and next rising edge. Edges of the master clock are labeled according to the first rising edge (1), next falling

edge (2), next rising edge (3), etc. For example, a basic clock divider can be specified equivalently with

-divide_by 2 or -edges {1 3 5}. The -edge_shift option accepts a list of three time values, the amount to shift

each of the three edges.

The value of the targets is either a collection or a Tcl list of wildcards used to create a collection of the

appropriate type. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See the help for use_timequest_style_escaping for details.

Example

# Create a clock and a divide-by-2 generated clock

create_clock -period 10 [get_ports clk]

create_generated_clock -divide_by 2 -source [get_ports clk] -name clkdiv \

[get_registers clkdiv]

# An equivalent generated clock

create_generated_clock -edges {1 3 5} -source [get_ports clk] -name \

clkdiv [get_registers clkdiv]

# Specify a clock multipler with a 60% duty cycle

create_generated_clock -multiply_by 2 -duty_cycle 60 \

[get_pins clkmult|combout]

# Specify an inverted divide-by-2 clock relative to the output of the

# source clock

create_generated_clock -divide_by 2 -invert -source [get_ports clk] -name \

nclkdiv [get_registers clkdiv]

# Specify a divide-by-2 clock with a 90-degree phase shift

create_generated_clock -divide_by 2 -phase 90 -source [get_ports clk] \

-name clkdiv [get_registers clkdiv]

# Assign two clocks to an input port that are switched externally,

# along with an internal clock divider.

create_clock -period 10 -name clk100Mhz [get_ports clk]

create_clock -period 6.667 -name clk150Mhz -add [get_ports clk]

create_generated_clock -divide_by 2 -name clk50Mhz -source [get_ports \

clk] -master_clock clk100Mhz -add [get_registers clkdiv]

create_generated_clock -divide_by 2 -name clk75Mhz -source [get_ports \

clk] -master_clock clk150Mhz -add [get_registers clkdiv]

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 20

2–10 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

derive_clocks

Usage

derive_clocks -period <period_value> [-waveform <edge_list>]

Options

-period <period_value>: Speed of the default clock in terms of clock period

-waveform <edge_list>: List of edge values

Description

Creates a clock on sources of clock pins in the design that do not already have at least one clock sourcing

the clock pin. This command is equivalent to calling create_clock on each clock source in the design that

does not already have a clock assigned to it.

See the help for create_clock for more information.

Altera does not recommend using this command during final sign-off analysis of a design. derive_clocks

should only be used early in the design phase when the clocks are not completely known. When possible,

create_clock and create_generated_clock should be used instead.

Example

# Automatically create a 10ns, 60% duty cycle clock on all

# unconstrained clock sources

derive_clocks -period 10 -waveform {0 6}

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 21

Chapter 2: SDC and TimeQuest API Package and Commands 2–11

sdc

get_cells

Usage

get_cells [-compatibility_mode] [-hierarchical] [-no_duplicates] [-nocase] [-nowarn]

<filter>

Options

-compatibility_mode: Use simple Tcl matching (Classic Timing Analyzer style)

-hierarchical: Specifies use of a hierarchical searching method

-no_duplicates: Do not match duplicated cell names

-nocase: Specifies case insensitive node name matching

-nowarn: Do not issue warnings messages about unmatched patterns

<filter>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Returns a collection of cells in the design. All cell names in the collection match the specified pattern.

Wildcards can be used to select multiple cells at once.

There are three Tcl string matching schemes available with this command: the default method, the

-hierarchical option, and the -compatibility_mode option.

When you use the default matching scheme, use pipe characters to separate one hierarchy level from the

next. They are treated as special characters and are taken into account when string matching with

wildcards is performed. When this matching scheme is enabled, the specified pattern is matched against

absolute cell names: the names that include the entire hierarchical path. A full cell name can contain

multiple pipe characters in it to reflect the hierarchy. All hierarchy levels in the pattern are matched level

by level. Any included wildcards refer to only one hierarchical level. For example, "*" and "*|*" produce

different collections since they refer to the highest hierarchical level and second highest hierarchical level

respectively.

When using the -hierarchical matching scheme, pipe characters are treated as special characters and are

taken into account when string matching with wildcards is performed. This matching scheme forces the

search to proceed recursively down the hierarchy. The specified pattern is matched against the relative cell

names: the immediate names that do not include any of the hierarchy information. Note that a short cell

name cannot contain pipe characters in it. Any included wildcards are expanded to match the relative pin

names.

The -compatibility_mode matching scheme mimics the string matching behavior of the Classic Timing

Analyzer. The simple Tcl string matching on full, absolute cell names is used. Pipe characters are not

treated as special characters when used with wildcards.

The default matching scheme returns cells whose names match the specified filter and also cells

automatically generated by the Quartus II software from these cells). Use -no_duplicates option to not

include duplicated cells.

The filter for the collection is a Tcl list of wildcards, and must follow standard Tcl or TimeQuest-extension

substitution rules. See help for the use_timequest_style_escaping command for details.

Example

# Find a cell called "reg" using case insensitive search

get_cells -nocase reg

# Create a collection of all cells whose names start with "reg"

get_cells reg*

# Create a collection of all cells on the highest hierarachical level

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 22

2–12 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

set mycollection [get_cells *]

# Create a collection of all cells in the design

# Output cell names.

foreach_in_collection cell $mycollection {

puts [get_cell_info -name $cell]

}

set fullcollection [get_cells -hierarchical *]

# Output cell IDs and names.

foreach_in_collection cell $fullcollection {

puts -nonewline $cell

puts -nonewline ": "

puts [get_cell_info -name $cell]

}

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 23

Chapter 2: SDC and TimeQuest API Package and Commands 2–13

sdc

get_clocks

Usage

get_clocks [-nocase] [-nowarn] <filter>

Options

-nocase: Specifies the matching of node names to be case-insensitive

-nowarn: Do not issue warnings messages about unmatched patterns

<filter>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Returns a collection of clocks in the design. When used as an argument to another command, such as the

-from or -to options of set_multicycle_path, each node in the clock represents all nodes driven by the

clocks in the collection.

# The following multicycle constraint applies to all paths ending at registers

# driven by clk

set_multicycle_path -to [get_clocks clk] 2

The filter for the collection is a Tcl list of wildcards, and must follow standard Tcl or TimeQuest-extension

substitution rules. See the help for use_timequest_style_escaping for details.

Example

project_open chiptrip

create_timing_netlist

read_sdc

update_timing_netlist

set clocks [get_clocks c* -nocase]

foreach_in_collection clk $clocks {

set name [get_clock_info -name $clk]

set period [get_clock_info -period $clk]

puts "$name: $period"

}

delete_timing_netlist

project_close

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 24

2–14 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

get_nets

Usage

get_nets [-no_duplicates] [-nocase] [-nowarn] <filter>

Options

-no_duplicates: Do not match duplicated net names

-nocase: Specifies case-insensitive node name matching

-nowarn: Do not issue warnings messages about unmatched patterns

<filter>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Returns a collection of nets in the design. All net names in the collection match the specified pattern.

Wildcards can be used to select multiple nets at once.

The default matching scheme returns nets whose names match the specified filter and nets that are

automatically generated by the Quartus II software from these nets. Use the -no_duplicates option to

exclude duplicated nets.

The filter for the collection is a Tcl list of wildcards, and must follow standard Tcl or TimeQuest-extension

substitution rules. See help for the use_timequest_style_escaping command for details.

Example

# Find a net called "reg" using case insensitive search

get_nets -nocase reg

# Create a collection of all nets whose names start with "reg"

get_nets reg*

# Create a collection of all nets in the design

set mycollection [get_nets *]

# Output net names.

foreach_in_collection net $mycollection {

puts [get_net_info -name $net]

}

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 25

Chapter 2: SDC and TimeQuest API Package and Commands 2–15

sdc

get_pins

Usage

get_pins [-compatibility_mode] [-hierarchical] [-no_duplicates] [-nocase] [-nowarn]

<filter>

Options

-compatibility_mode: Use simple Tcl matching (Classic Timing Analyzer style)

-hierarchical: Specifies use of a hierarchical searching method

-no_duplicates: Do not match duplicated pin names

-nocase: Specifies case-insensitive node name matching

-nowarn: Do not issue warnings messages about unmatched patterns

<filter>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Returns a collection of pins in the design. All pin names in the collection match the specified pattern.

Wildcards can be used to select multiple pins at once.

There are three Tcl string matching schemes available with this command: the default method, the

-hierarchical option, and the -compatibility_mode option.

By default, pipe characters are used to separate one hierarchy level from the next. They are treated as

special characters and are taken into account when string matching with wildcards is performed. When

the default matching scheme is enabled, the specified pattern is matched against absolute pin names: the

names that include the entire hierarchical path. All hierarchy levels in the pattern are matched level by

level. Pin names of the form <absolute full cell name>|<pin suffix> are used for matching. Note that a full

cell name can contain multiple pipe characters in it to reflect the hierarchy. Any included wildcards refer to

only one hierarchical level. For example, "*|*" and "*|*|*" produce different collections since they refer to

the highest hierarchical level and second highest hierarchical level respectively.

When uisng the -hierarchical matching scheme, pipe characters are treated as special characters and are

taken into account when string matching with wildcards is performed. This matching scheme forces the

search to proceed recursively through the hierarchy. The specified pattern is matched against the relative

pin names: the immediate names that do not include any of the hierarchy information. Pin names of the

form <relative short cell name>|<pin suffix> are used for matching. Note that a short cell name cannot

contain pipe characters. Any included wildcards are expanded to match the relative pin names. For

example, "*" and "*|*" match exactly the same pins since the former is expanded into the latter.

The -compatibility_mode matching scheme mimics the string matching behavior of the Classic timing

analyzer for full, absolute pin names. Pipe characters are not treated as special characters when used with

wildcards.

The default matching scheme returns not only pins whose names match the specified filter, but also pins

duplicated from these pins (refers to pins are automatically generated by Quartus from the pins). Use

-no_duplicates option to not include duplicated pins.

The filter for the collection is a Tcl list of wildcards, and must follow standard Tcl or TimeQuest-extension

substitution rules. See help for the use_timequest_style_escaping command for details.

Example

# Get regout pin of "reg" cell

get_pins -nocase reg|regout

# Create a collection of all pins of "reg" cell

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 26

2–16 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

get_pins reg|*

# Create a collection of all pins on the highest hierarachical level

set mycollection [get_pins *]

# Output pin names.

foreach_in_collection pin $mycollection {

puts [get_pin_info -name $pin]

}

# Create a collection of all pins in the design

set fullcollection [get_pins -hierarchical *]

# Output pin IDs and names.

foreach_in_collection pin $fullcollection {

puts -nonewline $pin

puts -nonewline ": "

puts [get_pin_info -name $pin]

}

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 27

Chapter 2: SDC and TimeQuest API Package and Commands 2–17

sdc

get_ports

Usage

get_ports [-nocase] [-nowarn] <filter>

Options

-nocase: Specifies case-insensitive node name matching

-nowarn: Do not issue warnings messages about unmatched patterns

<filter>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Returns a collection of ports (design inputs and outputs) in the design.

The filter for the collection is a Tcl list of wildcards, and must follow standard Tcl or TimeQuest-extension

substitution rules. See help for the use_timequest_style_escaping command for details.

Example

project_open chiptrip

create_timing_netlist

# Get all ports starting with "In".

set ports [get_ports In*]

foreach_in_collection port $ports {

puts [get_port_info -name $port]

}

delete_timing_netlist

project_close

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 28

2–18 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

remove_clock_groups

Usage

remove_clock_groups -all

Options

-all: Specify remove all clock group settings

Description

Remove all clock group assignments. This command removes any clock groups that have been previously

set. There is no way to remove specific groups.

Example

project_open top

create_timing_netlist

create_clock -period 10.000 -name clkA [get_ports sysclk[0]]

create_clock -period 10.000 -name clkB [get_ports sysclk[1]]

# Set clkA and clkB to be mutually exclusive clocks.

set_clock_groups -exclusive -group {clkA} -group {clkB}

set_clock_groups -exclusive -group {clkC} -group {clkD}

# Remove clock groups A, B, C, and D. Result is that there

# are no longer any mutually exclusive clocks.

remove_clock_groups -all

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 29

Chapter 2: SDC and TimeQuest API Package and Commands 2–19

sdc

remove_clock_latency

Usage

remove_clock_latency -source <targets>

Options

-source: Specifies the source clock latency

<targets>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Removes clock latency for a given clock or clock target.

There are two types of latency: network and source. Network latency is the clock network delay between

the clock and register clock pins. Source latency is the clock network delay between the clock and its

source (e.g., a system clock or a base clock of a generated clock).

The TimeQuest Timing Analyzer automatically computes network latencies for all register and generated

clocks. Overriding clock network latencies is not supported by the TimeQuest analyzer. Therefore, the

-source option must always be specified. Remove_clock_latency requires this option as well.

You can apply clock latency to a clock, which affects all targets of the clock, or to a specific clock target.

Therefore, you can remove clock latency from a collection of clocks, or from a collection of target nodes.

remove_clock_latency removes all latencies from a clock or node, so removing a node's clock latency with

respect to a particular clock, or removing only latencies with particular conditions is not supported.

The value of the targets is either a collection or a Tcl list of wildcards used to create a collection of the

appropriate type. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See the help for use_timequest_style_escaping for details.

Example

create_clock -name SYSCLK -period 10.000 [get_ports inclk]

create_generated_clock -name OUTCLK -divide_by 1 -source [get_ports \

inclk] [get_ports outclk]

create_generated_clock -name FDBKCLK -divide_by 1 -source \

[get_ports outclk] [get_ports fdbkclk]

# Apply a simple 2.000 ns source latency to the system clock.

set_clock_latency -source 2.000 [get_clocks SYSCLK]

# Specify feedback clock latencies between output port outclk

# and the output port fdbkclk.

set_clock_latency -source -late -rise 0.800 [get_clocks FDBKCLK]

set_clock_latency -source -late -fall 0.750 [get_clocks FDBKCLK]

set_clock_latency -source -early -rise 0.500 [get_clocks FDBKCLK]

set_clock_latency -source -early -fall 0.460 [get_clocks FDBKCLK]

# Remove all clock latency from FDBKCLK

remove_clock_latency -source [get_clocks FDBKCLK]

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 30

2–20 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

remove_clock_uncertainty

Usage

remove_clock_uncertainty -from <from_clock> -to <to_clock>

Options

-from <from_clock>: Valid destinations (string patterns are matched using Tcl string

matching)

-to <to_clock>: Valid destinations (string patterns are matched using Tcl string

matching)

Description

Removes clock uncertainty from a collection of clocks to a collection of clocks. The source and destination

clocks can be any arbitrary collection of clocks. This command removes all uncertainty between two

clocks. If there does not exist uncertainty between two clocks specified in remove_clock_uncertainty, the

command does nothing for those two clocks but continues to attempt to remove uncertainty between other

clocks specified.

The values of the -from and -to options are either collections or a Tcl list of wildcards used to create

collections of appropriate types. The values used must follow standard Tcl or TimeQuest-extension

substitution rules. See the help for use_timequest_style_escaping for details.

Example

set_clock_uncertainty -setup -rise_from {clk1 clk2} -fall_to {clk3 clk4} \

200ps

set_clock_uncertainty -from {clk5 clk6} -to {clk7 clk8} 300ps

remove_clock_uncertainty -from {clk3 clk5} -to {clk4 clk7}

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 31

Chapter 2: SDC and TimeQuest API Package and Commands 2–21

sdc

remove_disable_timing

Usage

remove_disable_timing [-from <name>] [-to <name>] <cells>

Options

-from <name>: Valid source pin suffix

-to <name>: Valid destination pin suffix

<cells>: List of cells

Description

Adds a previously disabled edge (arc) back to a given cell(s). If no -from/-to value is specified, the missing

value is substituted by a "*".

The values of the -from and -to are either collections or a Tcl list of wildcards used to create collections of

appropriate types. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See the help for use_timequest_style_escaping for details.

Example

remove_disable_timing -from datain -to combout A|B

remove_disable_timing -from carryin *

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 32

2–22 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

remove_input_delay

Usage

remove_input_delay <targets>

Options

<targets>: Collection or list of input ports

Description

Removes input delay from a port. For each input port specified, removes all input delays for that port. This

means that rise, fall, max, and min delays for each clock and reference pin on the input port are all

removed.

The value of the targets is either a collection or a Tcl list of wildcards used to create a collection of the

appropriate type. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See help for the use_timequest_style_escaping command for details.

Example

# Simple input delay with the same value for min/max and rise/fall

set_input_delay -clock clk 1.5 [get_ports {in1 in2}]

set_input_delay -clock clk2 1.5 [get_ports {in1 in2}]

set_input_delay -clock clk 1.6 [get_ports {in3 in4}]

# Remove input delay on ports in1 and in4,

# for all flags and reference ports and flags

remove_input_delay [get_ports {in1 in4}]

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 33

Chapter 2: SDC and TimeQuest API Package and Commands 2–23

sdc

remove_output_delay

Usage

remove_output_delay <targets>

Options

<targets>: Collection or list of output ports

Description

Removes output delay from a port. For each output port specified, removes all output delays for that port.

Rise, fall, max, and min delays for each clock and reference pin on the output port are all removed.

The value of the targets is either a collection or a Tcl list of wildcards used to create a collection of the

appropriate type. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See help for the use_timequest_style_escaping command for details.

Example

# Simple output delay with the same value for min/max and rise/fall

set_output_delay -clock clk 1.5 [get_ports {out1 out2}]

set_output_delay -clock clk2 1.5 [get_ports {out1 out2}]

set_output_delay -clock clk 1.6 [get_ports {out3 out4}]

# Remove input delay on ports out1 and out4,

# for all flags and reference ports and flags

remove_output_delay [get_ports {out1 out4}]

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 34

2–24 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

reset_design

Usage

reset_design

Options

None

Description

Removes all assignments from the design. This includes clocks, generated clocks, derived clocks, input

delays, output delays, clock latency, clock uncertainty, clock groups, false paths, multicycle paths, min

delays, and max delays. After reset_design is called, the design should be in the same state as it would be

if create_timing_netlist was just called.

Example

# Constrain design

create_clock -name clk -period 4.000 -waveform { 0.000 2.000 } \

[get_ports clk]

set_input_delay -clock clk2 1.5 [get_ports in*]

set_output_delay -clock clk 1.6 [get_ports out*]

set_false_path -from [get_keepers in] -through [get_nets r1] -to \

[get_keepers out]

# Reset the design to the state that it was in before any constraints

# were entered

reset_design

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 35

Chapter 2: SDC and TimeQuest API Package and Commands 2–25

sdc

set_clock_groups

Usage

set_clock_groups [-asynchronous] [-exclusive] -group <names>

Options

-asynchronous: Specify mutually exclusive clocks (same as the -exclusive option).

Exists for compatibility.

-exclusive: Specify mutually exclusive clocks

-group <names>: Valid destinations (string patterns are matched using Tcl string

matching)

Description

Clock groups provide a quick and convenient way to specify which clocks are not related. Asynchronous

clocks are those that are completely unrelated (e.g., have different ideal clock sources). Exclusive clocks are

those that are not active at the same time (e.g., multiplexed clocks). TimeQuest treats both options,

"-exclusive" and "-asynchronous", as if they were the same.

The result of set_clock_groups is that all clocks in any group are cut from all clocks in every other group.

This command is equivalent to calling set_false_path from each clock in every group to each clock in every

other group and vice versa, making set_clock_groups easier to specify for cutting clock domains. The use

of a single -group option tells TimeQuest to cut this group of clocks from all other clocks in the design,

including clocks that are created in the future.

Example

project_open top

create_timing_netlist

create_clock -period 10.000 -name clkA [get_ports sysclk[0]]

create_clock -period 10.000 -name clkB [get_ports sysclk[1]]

# Set clkA and clkB to be mutually exclusive clocks.

set_clock_groups -exclusive -group {clkA} -group {clkB}

# The previous line is equivalent to the following two commands.

set_false_path -from [get_clocks clkA] -to [get_clocks clkB]

set_false_path -from [get_clocks clkB] -to [get_clocks clkA]

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 36

2–26 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

set_clock_latency

Usage

set_clock_latency [-clock <clock_list>] [-early] [-fall] [-late] [-rise] -source

<delay> <targets>

Options

-clock <clock_list>: Valid clock destinations (string patterns are matched using Tcl

string matching)

-early: Specifies the early clock latency

-fall: Specifies the falling transition clock latency

-late: Specifies the late clock latency

-rise: Specifies the rising transition clock latency

-source: Specifies the source clock latency

<delay>: Latency delay value

<targets>: Valid destinations (string patterns are matched using Tcl string matching)

Description

Specifies clock latency for a given clock or clock target.

There are two types of latency: network and source. Network latency is the clock network delay between

the clock and register clock pins. Source latency is the clock network delay between the clock and its

source (e.g., the system clock or base clock of a generated clock).

The TimeQuest Timing Analyzer automatically computes network latencies for all register and generated

clocks. Overriding clock network latencies is not supported by the TimeQuest analyzer. Therefore, the

-source option must always be specified.

You can apply clock latency to a clock, which affects all targets of the clock, or to a specific clock target. If

you specify a specific clock target that is driven by more than one clock, use the -clock option to specify

which clock to use. Latencies assigned to a clock target override any latencies assigned to a clock.

Different clock latencies can be specified for early (-early) and late (-late) latencies, as well as for rising

edges (-rise) and falling edges (-fall). If only some combinations are specified, the other combinations are

used by default. For example, if only a -rise -early latency and a -fall -early latency are specified, then the

-rise -late latency is assumed to be the same as the -rise -early latency and the -fall -late latency is assumed

to be the same as the -fall -early latency. If neither -rise nor -fall are used or neither -early nor -fall are used,

then the latency applies to both conditions.

Source latency can also be assigned to generated clocks. This may be useful for specifying board level

delays from a clock output port to a clock input port when the clock input port is acting as a feedback

clock.

The value of the targets is either a collection or a Tcl list of wildcards used to create a collection of the

appropriate type. The values used must follow standard Tcl or TimeQuest-extension substitution rules.

See help for the use_timequest_style_escaping command for details.

Example

create_clock -name SYSCLK -period 10.000 [get_ports inclk]

create_generated_clock -name OUTCLK -divide_by 1 -source [get_ports \

inclk] [get_ports outclk]

create_generated_clock -name FDBKCLK -divide_by 1 -source \

[get_ports outclk] [get_ports fdbkclk]

SDC and TimeQuest API Reference Manual © December 2009 Altera Corporation

Page 37

Chapter 2: SDC and TimeQuest API Package and Commands 2–27

sdc

# Apply a simple 2.000 ns source latency to the system clock.

set_clock_latency -source 2.000 [get_clocks SYSCLK]

# Specify feedback clock latencies between output port outclk

# and the output port fdbkclk.

set_clock_latency -source -late -rise 0.800 [get_clocks FDBKCLK]

set_clock_latency -source -late -fall 0.750 [get_clocks FDBKCLK]

set_clock_latency -source -early -rise 0.500 [get_clocks FDBKCLK]

set_clock_latency -source -early -fall 0.460 [get_clocks FDBKCLK]

© December 2009 Altera Corporation SDC and TimeQuest API Reference Manual

Page 38

2–28 Chapter 2: SDC and TimeQuest API Package and Commands

sdc

set_clock_uncertainty

Usage

set_clock_uncertainty [-add] [-fall_from <fall_from_clock>] [-fall_to <fall_to_clock>]

[-from <from_clock>] [-hold] [-rise_from <rise_from_clock>] [-rise_to <rise_to_clock>]

[-setup] [-to <to_clock>] <uncertainty>

Options

-add: Specifies that this assignment is an addition to the clock uncertainty derived by

derive_clock_uncertainty call

-fall_from <fall_from_clock>: Valid destinations (string patterns are matched using Tcl

string matching)

-fall_to <fall_to_clock>: Valid destinations (string patterns are matched using Tcl

string matching)

-from <from_clock>: Valid destinations (string patterns are matched using Tcl string

matching)

-hold: Specifies the uncertainty value (applies to clock hold or removal checks)

-rise_from <rise_from_clock>: Valid destinations (string patterns are matched using Tcl

string matching)

-rise_to <rise_to_clock>: Valid destinations (string patterns are matched using Tcl

string matching)

-setup: Specifies the uncertainty value (applies to clock setup or recovery checks)

(default)

-to <to_clock>: Valid destinations (string patterns are matched using Tcl string

matching)

<uncertainty>: Uncertainty

Description