Page 1

SERVICE MANUAL

MULTIPLE OUTPUT LINEAR SYSTEM

DC POWER SUPPLY

AGILENT MODELS 6625A, 6626A,

6628A, and 6629A

Agilent Part No 06626-90003

Agilent Model 6625A, Serial 3738A-01389 through 01408

US37380101 and up

Agilent Model 6626A, Serial 3737A-02259 through 02328

US37370101 and up

Agilent Model 6628A, Serial 3738A-00683 through 00727

US37380101 and up

Agilent Model 6629A, Serial 3738A-00968 through 00997

US37380101 and up

* For instruments with higher Serial Numbers, a change page may be included.

5

Microfiche Part No. 06626-90004 Printed in Malaysia: September, 2001

Page 2

CERTIFICATION

Agilent Technologies certifies that this product met its published specifications at time of shipment from the factory. Agilent

Technologies further certifies that its calibration measurements are traceable to the United States National Bureau of

Standards, to the extent allowed by the Bureau’s calibration facility, and to the calibration facilities of other International

Standards Organization members.

WARRANTY

This Agilent Technologies hardware product is warranted against defects in material and workmanship for a period of three

years from date of delivery. Agilent software and firmware products, which are designated by Agilent for use with a

hardware product and when properly installed on that hardware product, are warranted not to fail to execute their

programming instructions due to defects in material and workmanship for a period of 90 days from date of delivery. During

the warranty period Agilent Technologies will, at its option, either repair or replace products which prove to be defective.

Agilent does not warrant that the operation of the software, firmware, or hardware shall be uninterrupted or error free.

For warranty service, with the exception of warranty optio ns, this product must be returned to a service facility designated

by Agilent. Customer shall prepay shipping charges by (and shall pay all duty and taxes) for products returned to Agilent

for warranty service. Except for products returned to Customer from another country, Agilent shall pay for return of

products to Customer.

Warranty services outside the country of initial purchase are included in Agilent’s prod uct pr ice, only if Customer pays

Agilent international prices (defined as destination local currency price, or U.S. or Geneva Export price).

If Agilent is unable, within a reasonable time to repair or replace any product to condition as warranted, the Customer shall

be entitled to a refund of the purchase price upon retur n of t he pr oduct to Agilent.

LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Customer,

Customer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental

specifications for the product, or improper site preparation and maintenance. NO OTHER WARRANTY IS EXPRESSED

OR IMPLIED. Agilent SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCH ANTABILITY AND

FITNESS FOR A PARTICULAR PURPOSE.

EXCLUSIVE REMEDIES

THE REMEDIES PROVIDED HEREIN ARE THE CUSTOMER’S SOLE AND EXCLUSIVE REMEDIES. Agilent

SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL

DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

ASSISTANCE

The above statements apply only to the standard product warranty. Warranty options, extended support contracts, product

maintenance agreements and customer assistance agreements are also available. Contact your nearest Agilent

Technologies Sales and Service office for further information on Agilent’s full line of Support Programs.

Page 3

SAFETY SUMMARY

The following general safety precautions must be observed during all phases of operation, service, and repair of this

instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety

standards of design, manufacture, and intended use of the instrument. Agilent Technologies assumes no liability for the

customer’s failure to comply with these requirements.

BEFORE APPLYING POWER.

Verify that the product is set to match the available line voltage and the correct fuse is installed.

GROUND THE INSTRUMENT.

This product is a Safety Class 1 inst rument (provided with a protective earth terminal). To minimize shock hazard, the instrument chassis

and cabinet must be connected to an electrical ground. The instrument must be connected to the ac power supply mains through a threeconductor power cable, with the third wire firmly connected to an electrical ground (safety ground) at the power outlet. For instruments

designed to be hard-wired to th e ac power lines (supply mains), conn ect the protective earth terminal to a protective conductor before any

other connection is made. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will

cause a potential shock h azard that could result in personal inju ry. If the instrument is to be energized via an external autotransformer for

voltage reduction, be certain that the autotransfo r mer common terminal is connected to the neutral (earthed pole) of the ac power lines

(supply mains).

FUSES.

Only fuses with the required rated current, voltage, and specified type (normal blow, time delay, etc.) should be used. Do not use repaired

fuses or short circuited fuseholders. To do so could cause a shock o r fire h azard.

DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the instrument in the presence of flammable gases or fumes.

KEEP AWAY FROM LIVE CIRCUITS.

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made by qualified

service personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even

with the power cable removed. To avoid injuries, always disconnect power, discharge circuits and remove external voltage sources before

touching components.

DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

DO NOT EXCEED INPUT RATINGS.

This instrument may be equipped with a line filter to reduce electromagnetic interference and must be connected to a properly grounded

receptacle to minimize electric shock hazard. Operation at line voltages or frequ encies in excess of those stated on the data plate may

cause leakage currents in excess of 5.0 mA peak.

SAFETY SYMBOLS.

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the

instruction manual (refer to Table of Contents) .

Indicates hazardous vo ltages.

Indicate earth (ground) terminal.

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly

performed or adhered to, could result in personal inj ury. Do not proceed beyond a WARNING sign until the

indicated conditions are fully understood and met.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, or th e like, which, if not correctly

performed or adhered to, coul d result in damage to or destruction of part or all of the product. Do not proceed

beyond a CAUTION sign until the indicated conditions are fully understood and met.

DO NOT SUBSTITUTE PARTS OR MODIFY INSTRUMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unau thorized modification to the

instrument. Return the instrument to an Agilent Technologies Sales and Service Office for service and repair to ensure that safety features

are maintained.

Instruments which appear damaged or defective should be made inoperative and secured against unintended operation until they can be

repaired by qualified service personnel

Page 4

SAFETY SUMMARY (continued)

GENERAL

Any LEDs used in this product are Class 1 LEDs as per IEC 825-1.

ENVIRONMENTAL CONDITIONS

This instrument is intended for indoor use in an installation category II, pollution degree 2 environment. It is designed to

operate at a maximum relative humidity of 95% and at altitudes of up to 2000 meters. Refer to the specifications tables for the

ac mains voltage requirements and ambient operating temperature range.

SAFETY SYMBOL DEFINITIONS

Symbol Description Symbol Description

Direct current Terminal for Line conductor on permanently

installed equipment

Alternating current Caution, risk of electric shock

Both direct and alternating current Caution, hot surface

Three-phase alternating current Caution (refer to accompanying documents)

Earth (ground) terminal In position of a bi-stable push control

Protective earth (ground) terminal Out position of a bi-stable push control

Frame or chassis terminal On (supply)

Terminal for Neutral conductor on

permanently installed equipment

Terminal is at earth potential

(Used for measurement and control

circuits designed to be operated with

one terminal at earth potential.)

Herstellerbescheinigung

Diese Information steht im Zusammenhang mit den Anforderungen der

Maschinenläminformationsverordnung vom 18 Januar 1991.

* Schalldruckpegel Lp <70 dB(A) * Am Arbeitsplatz * Normaler Betrieb

* Nach EN 27779 (Typprüfung).

Manufacturer’s Declaration

This statement is provided to comply with the requirements of the German Sound Emission Directive,

from 18 January 1991.

* Sound Pressure Lp <70 dB(A) * At Operator Position * Normal Operation

* According to EN 27779 (Type Test).

Off (supply)

Standby (supply)

Units with this symbol are not completely

disconnected from ac mains when t his switch is

off. To completely disconnect the unit from ac

mains, either disconnect the power cord or have

a qualified electrician install an external switch.

Edition 2 September, 2001

© Copyright 2001 Agilent Technologies, Inc.

Page 5

CONTENTS

Section I

INTRODUCTION

1-1 SCOPE ……………………………………………………1-1

1-2 SAFETY CONSIDERATIONS…………………………..1-1

1-3 INSTRUMENT AND MANUAL

IDENTIFICATION……………………………………….1-1

1-4 FIRMWARE REVISIONS ……………………………….1-1

Section II

PRINCIPLES OF OPERATION

2-1 INTRODUCTION ………………………………………..2-1

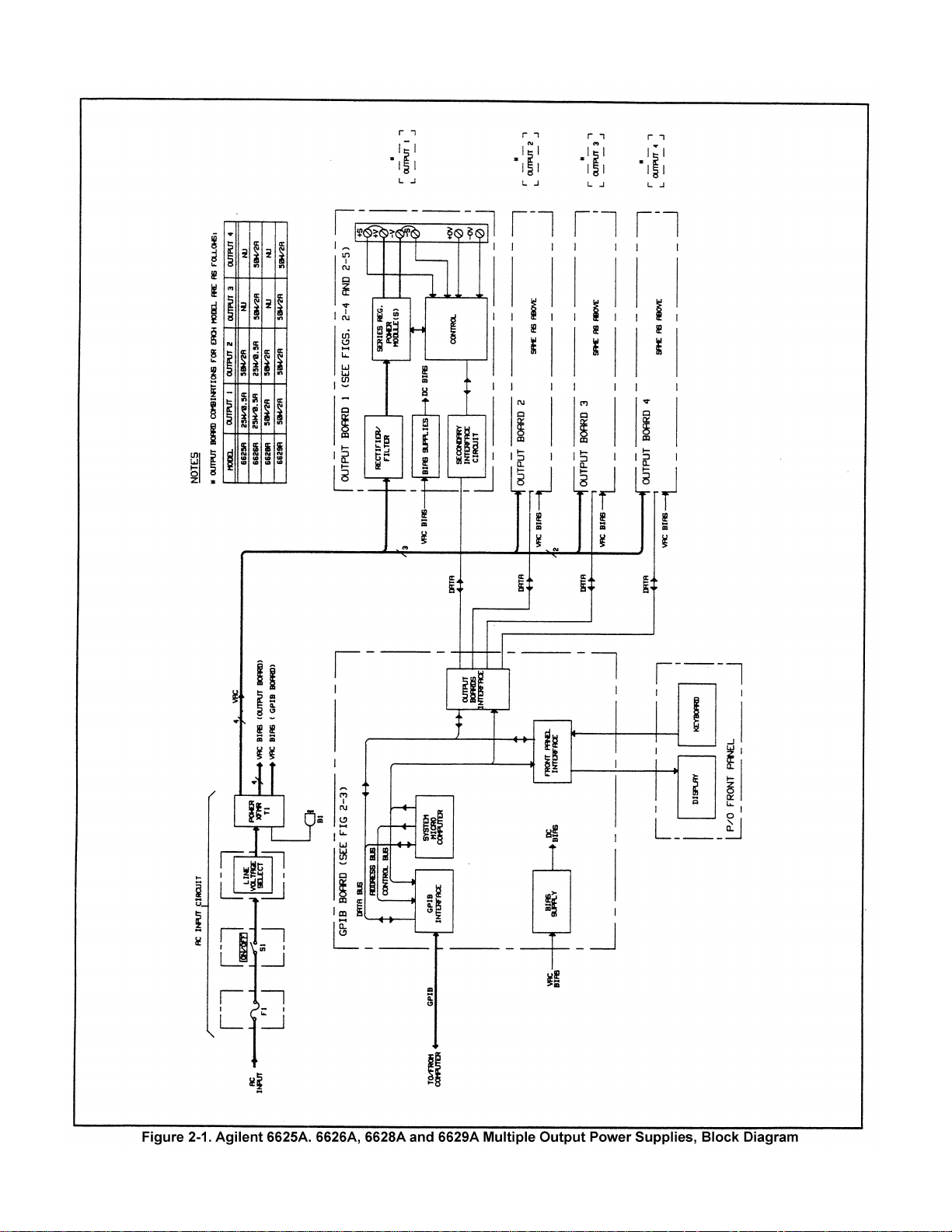

2-2 OVERALL BLOCK DIAGRAM DESCRIPTION

(Figure 2-1) ………………………………………………..2-1

2-3 AC Input Circuits ………………………………………..2-1

2-4 GPIB Board .……………………………………………... 2-1

2-5 Front Panel ……………………………………………….2-1

2-6 Output Boards …………………………………………2-1

2-7 GPIB BOARD (Figure 2-3) ……………………………... 2-3

2-8 GPIB Interface …………………………………………... 2-3

2-9 System MicroComputer…………………………………2-4

2-16 Output Boards Interface ………………………………...2-4

2-20 Front Panel Interface …………………………………...2-5

2-23 Bias Supply and Start Up ……………………………….2-5

2-24 OUTPUT BOARD ……………………………………… 2-7

2-25 Secondary Interface Circuits

(Figure 2-4) ……………………………………………… 2-7

2-37 Power mesh and Control Circuits

(Figure 2-5) …………………………………………… 2-10

Section III

VERIFICATION

3-1 INTRODUCTION ………………………………………..3-1

3-2 TEST EQUIPMENT REQUIRED ………………………3-1

3-3 OPERATION VERIFICATION TESTS ………………. 3-1

3-4 PERFORMANCE TESTS ………………………………..3-1

3-5 Introduction………………………………………………3-1

3-6 Measurement Techniques ………………………………3-1

3-10 Constant Voltage (CV) Tests ……………………………3-4

3-19 Constant Current (CC) Tests…………………………..3-10

3-27 EXTENDTED TESTS …………………………………...3-13

3-28 Output Drift Tests ……………………………………...3-13

Section IV

TROUBLESHOOTING

4-1 INTRODUCTION ………………………………………..4-1

4-2 ELECTROSTATIC PROTECTION ……………………..4-1

4-3 REMOVAL AND REPLACEMENT …………………...4-2

4-4 Top Cover Removal …………………………………….4-2

4-5 Gaining Access to Assemblies in the Supply …………4-2

4-6 GPIB Board Removal ..………………………………….4-2

4-8 DUSTCOVERS …………………………………………..4-4

4-9 Replacing the Power Module U338 ……………………4-4

4-10 Front Panel Removal …………………………………….4-4

4-11 Chassis Mounted Components ………………………...4-5

4-12 TEST EQUIPMENT REQUIRED ……………………….4-5

4-13 FUSE REPLACEMENT………………………………….4-5

4-14 INITIAL TROUBLESHOOTING AND BOARD

ISOLATION PROCEDURES ..…………………………4-8

4-15 Power-On Self Test ………………………………………4-8

4-16 Connector P201 Jumper Positions ……………………...4-9

4-17 ERROR Codes and Messages…………………………...4-9

4-18 GPIB BOARD AND FRONT PANEL

TROUBLESHOOTING PROCEDURES ……………...4-13

4-19 Test Setup ……………………………………………….4-13

4-20 Post Repair Calibration………………………………...4-13

4-21 Setting the Model Number

(MODEL Command) …………………………………...4-13

4-22 Signature Analysis Testing …………………………4-14

4-23 Test Setup for S.A. ……………………………………...4-14

4-24 Firmware Revisions (ROM? Command)……………..4-14

4-25 OUTPUT BOARD TROUBLESHOOTING

PROCEDURES ………………………………………….4-30

4-26 Test Setup ……………………………………………….4-30

4-27 Post Repair Calibration ………………………………..4-30

4-28 Self Exercise Routine on the Output Board ………….4-30

4-29 Troubleshooting Analog Multiplexer U323 and

Readback Using VMUX? Command …………………4-49

4-30 Understanding and Troubleshooting the Signal

Processor (U327)………………………………………...4-50

4-33 Power Module Signals …………………………………4-54

4-34 Miscellaneous Trouble Symptoms and Remedies ….4-54

Section V

REPLACEABLE PARTS

5-1 INTRODUCTION ………………………………………..5-1

5-2 HOW TO ORDER PARTS ………………………………5-1

i

Page 6

CONTENTS (Cont. )

Section VI

CIRCUIT DIAGRAMS

6-1 INTRODUCTION ………………………………………..6-1

6-2 FUNCTIONAL SCHEMATIC DIAGRAMS …………..6-1

6-3 COMPONENT LOCATION ILLUSTRATIONS ……...6-1

Appendix A

LOGIC SYMBOLOGY

ii

Page 7

LIST OF FIGURES

Figure Page

2-1 Agilent 6625A, 6826A, 6628A and 6629A Multiple Output Power Supplies, Block Diagram ……………………………...2-2

2-2 Output Operating Ranges for Agilent Models 6625A, 6626A, 6628A and 6629A …………………………………………2-3

2-2 HP-IB Board, Block Diagram ……………………………………………………………………………………………………..2-6

2-4 Output Board, Secondary Interface Circuits, Block Diagram ………………………………………………………………….2-9

2-5 Output Board, Power Mesh and Control Circuits, Block …………………………………………………………………….2-12

2-6 Voltage and Current Control Circuits, Simplified Schematic ………………………………………………………………..2-13

2-7 Typical Output Range Characteristics ………………………………………………………………………………………….2-14

2-8 Typical Downprogramming Characteristics Below 2.0 V …………………………………………………………………….2-16

2-9 Overvoltage Protection Circuits, Block Diagram ……………………………………………………………………………...2-17

3-1 Operating Ranges Available in Models 6625A, 6626A, 6820A and 6629A …………………………………………………..3-3

3-2 Current Monitoring Resistor Setup ………………………………………………………………………………………………3-4

3-3 Basic Test Setup …………………………………………………………………………………………………………………….3-5

3-4 Transient Recovery Time Test Setup …………………………………………………………………………………………….3-6

3-5 Transient Response Waveform. …………………………………………………………………………………………………..3-7

3-6 Negative Current Limit (- CC) Readback Accuracy ……………………………………………………………………………3-9

3-7 Down Programming Speed Test Setup ………………………………………………………………………………………3-12

3-8 CV Down Programming Speed Test Waveform ………………………………………………………………………………3-13

3-9 CV Up Programming Speed Test Setup ………………………………………………………………………………………..3-13

3-10 CV Up Programming Test Waveform ………………………………………………………………………………………….3-14

3-11 Fixed OV Protection Test Setup …………………………………………………………………………………………………3-14

3-I2 OV External Trip Test Connection ……………………………………………………………………………………………3-14

4-1 Agilent 6625A, 6626A, 6628A and 6629A Multiple Output Supplies, Assembly Locations ……………………………….4-3

4-2 HP-IB, Board, Fuse and Test Point Locations …………………………………………………………………………………...4-6

4-3 Output Board 1 and 2 Fuse and Test Point Locations ………………………………………………………………………….4-7

4-4 Output Board 3 and 4 Fuse and Test Point Locations ………………………………………………………………………….4-9

4-5 Initial Troubleshooting and Board Isolation …………………………………………………………………………………..4-13

4-6 HP-IB Board and Front Panel Troubleshooting ……………………………………………………………………………….4-15

4-7 Signature Analysis Test Setup ………………………………………………………………………………………………….4-17

4-8 Output Board Troubleshooting …………………………………………………………………………………………………4-29

4-9 Output Board Waveform During Self Exercise Routine ……………………………………………………………………4-35

4-10 DAC/Amplifier Circuit Troubleshooting ……………………………………………………………………………………...4-36

4-11 Overvoltage Troubleshooting …………………………………………………………………………………………………4-37

4-12 Output Held Low Troubleshooting ……………………………………………………………………………………………..4-39

4-13 Output Held High Troubleshooting …………………………………………………………………………………………….4-42

4-14 OV Circuit Will Not Trip Troubleshooting ……………………………………………………………………………………..4-43

4-15 Signal Processor U327, Overvoltage Circuit, Simplified Schematic …………………………………………………………4-46

4-16 Signal processor U327, Power-On/Start-Up Circuit, Simplified Schematic ………………………………………………4-46

4-17 Signal processor U327, Status Monitor Circuit, Simplified Schematic ………………………………………………………4-52

4-18 Status Problems Troubleshooting ……………………………………………………………………………………………….4-53

6-1 Power Distribution Schematic ….…………………………………………………………………………………………………6-3

6-2 GPIB Board, Component Location ……………………………………………………………………………………………….6-5

6-2 GPIB Board, Schematic Diagram ...……………………………………………………………………………………………….6-6

6-3 Output 1 & 2 Board, Component Location ..…………………………………………………………………………………..…6-7

6-3 Output 1 & 2 Board, Schematic Diagram .....…………………………………………………………………………………..…6-8

6-4 Output 3 & 4 Board, Component Location ..……………………………………….…………………………………………..6-13

6-4 Output 3 & 4 Board, Schematic Diagram .………………………………………….…………………………………………..6-14

iii

Page 8

LIST OF TABLES

Table Page

3-1 Test Equipment Required for Verification ………………………………………………………………………………………… 3-2

3-2 Low Range Voltage and Current Values …………………………………………………………………………………………… 3-4

3-3 Performance Test Record for Agilent 6625A and 6628A ...………………………………………………………………………. 3-15

3-4 Performance Test Record for Agilent 6626A and 6629A ………………………………………………………………………… 3-16

4-1 Test Equipment Required for Troubleshooting …………………………………………………………………………………… 4-5

4-2 Fuses …………………………………………………………………………………………………………………………………….4-6

4-3 Tests Performed at Power-On ..……………………………………………………………………………………………………… 4-8

4-4 Power-On Self Test Error Message ………………………………………………………………………………………………….. 4-9

4-5 ERROR Codes and Messages.………………………………………………………………………………………………………. 4-10

4-6

GPIB Board S.A. Test No. 1 ………………………………………………………………………………………………………… 4-18

4-7 GPIB Board S.A. Test No. 2 ………………………………………………………………………………………………………… 4-19

4-8 GPIB Board S.A. Test No. 3 ………………………………………………………………………………………………………… 4-20

4-9 GPIB Board S.A. Test No. 4 ………………………………………………………………………………………………………… 4-21

4-10 GPIB Board S.A. Test No. 5 ………………………………………………………………………………………………………… 4-22

4-11 GPIB Board S.A. Test No. 6 ………………………………………………………………………………………………………… 4-23

4-12 GPIB Board S.A. Test No. 7 ………………………………………………………………………………………………………… 4-24

4-13 GPIB Board S.A. Test No. 8 ………………………………………………………………………………………………………… 4-25

4-14 Keyboard Signal Paths ………………………………………………………………………………………………………………. 4-27

4-15 Microcomputer (U312) Signal Measurements During the Self Exercise Routine …………………………………………… 4-44

4-16 U368 Signal Levels …………………………………………………………………………………………………………………… 4-45

4-17 Signal Processor (U327) Signal Levels …………………………………………………………………………………………….. 4-47

4-18 Typical Power Module Voltage Levels ……………………………………………………………………………………………. 4-49

4-19 Miscellaneous Trouble Symptoms …………………………………………………………………………………………………. 4-50

5-1 Output Board Configurations ……………………………………………………………………………………………………….. 5-1

5-2 Reference Designators ………………………………………………………………………………………………………………… 5-1

5-3 Abbreviations …………………………………………………………………………………………………………………………...5-2

5-4 Federal Manufacturer Codes ………………………………………………………………………………………………………… 5-3

5-5 Chassis Parts …………………………………………………………………………………………………………………………… 5-4

5-6 Output Board Replacement Part List …………………………………………………………………………………………………5-7

5-7 25W/.5A Replacement Parts List ……………………………………………………………………………………………………. 5-9

5-8 50W/2A Replacement Parts List …………………………………………………………………………………………………… 5-18

iv

Page 9

Section I

INTRODUCTION

1-1 SCOPE

This manual contains principles of operation, verification,

and troubleshooting information for the power supply.

Replaceable parts lists and circuit diagrams are also

provided. Installation, operation, programming, and

calibration procedures as well as detailed specifications are

given in a separate Operating Manual, Agilent Part No.

06626-90001.

Wherever applicable, the service instructions given in this

manual refer to pertinent information provided in the

Operating Manual. The information in each manual covers

model 6625A, 6626A, 6628A, and 6629A. The main

differences between the models are the number and type of

outputs each model contains. These differences are specified

in each of the manuals.

The following is a listing of the information contained in this

manual with a brief description concerning its scope and

purpose.

Principles of Operation: Section II provides block diagram

level descriptions of the supply’s circuits. The GPIB

interface (digital circuits), the power control (analog and

digital circuits), and power output (analog circuits) are

described. These descriptions are intended as an aid in

troubleshooting.

Verification: Section III contains test procedures that check

the operation of the supply to ensure that it meets the

specifications given in Section I of the Operating manual.

Troubleshooting: Section IV contains board level

troubleshooting procedures to isolate a malfunction to a

defective board (GPIB or output board) or assembly (front

panel, power transformer, or cable assembly). Additional

troubleshooting procedures are provided to isolate the fault

to a defective component on the board. Board and assembly

level removal and replacement procedures are also given in

this section.

NOTE

Calibration is generally required after a repair is made.

Software calibration procedures are given in Appendix A

of the Operating Manual. After calibration is completed,

perform the applicable test(s) given in Section III of this

manual to ensure that the supply meets all specifications.

Replaceable Parts:

replaceable parts for all electronic components and

mechanical assemblies.

Section V provides a listing of

Circuit Diagrams:

and component location diagrams . The names that appear

on the functional schematics also appear on the block

diagrams in Section II. Thus, the descriptions in Section II

can be correlated with both the block diagrams and the

schematics.

Section VI contains functional schematics

Logic Symbology:

the logic symbols used on the functional schematics.

Fault Indicator (FLT) and Remote Inhibit (INH): A fault

indicator and remote inhibit circuit, which provide

additional shutdown protection should either the GPIB

and/or controller fail, are available optionally. See a

separate document entitled, "Appendix E Option 750

Operating Instructions" for the Multiple Output Linear

System DC Power Supply Agilent Models 662xA (Agilent

P/N 5957-6372).

Appendix A gives a brief description of

1-2 SAFETY CONSIDERATIONS

This product is a Safety Class 1 instrument, which means

that it is provided with a protective earth terminal. The

instrument and this manual should be reviewed for safety

markings and instructions before operation. Refer to the

Safety Summary page at the beginning of this manual for a

summary of general safety information. Safety information

for specific procedures is located at appropriate places in the

manual.

1-3 INSTRUMENT AND MANUAL

IDENTIFICATION

Agilent Techonologies instruments are identified by a twopart Serial number, i.e. 2601A-00101. The first part of the

serial number (the prefix) is a number/letter combination

that denotes either the date of manufacture or the date of a

significant design change. It also indicates the country of

manufacture. The first two digits indicate the year (25 =

1985, 26 = 1986, etc), the second two digits indicate the week,

and “A” designates the U.S.A. The second part of the serial

number is a different sequential number assigned to each

instrument.

1-1

Page 10

If the serial number prefix on your power supply differs

from that shown on the title page of this manual, a yellow

Manual Change sheet that is supplied with the manual

add/or manual backdating changes in Appendix A of this

manual define the differences between your supply and the

supply described in this manual. The yellow change sheet

may also contain information for correcting errors in the

manual.

The serial number prefixes listed on the front of this manual

indicate the versions of the supplies that were available

when the manual was issued. If the serial prefix of your

supply is not listed in this manual, the manual may include

a yellow “Manual Changes” sheet. That sheet updates this

manual by defining any differences between the version of

your supply and the versions included here, and may also

include information for correcting any manual errors. Note

that because not all changes to the product require changes

to the manual, there may be no update information required

for your version of the supply.

1-4 FIRMWARE REVISIONS

The Read Only Memory (ROM) chip inside of your supply is

identified with a label that specifies the revision of the

supply’s firmware, see paragraph 4-24

1-2

Page 11

Section II

PRINCIPLES OF OPERATION

2-1 INTRODUCTION

The following paragraphs provide block diagram level

descriptions of the power supplies. Differences between the

models are given as required. The descriptions provide a

basic understanding of circuit operation and are intended as

an aid in troubleshooting . It is assumed in the following

discussions that you are familiar with the operating and

programming instructions presented in the Operating

Manual (Agilent Part No. 06626-90001).

2-2 OVERALL BLOCK DIAGRAM DESCRIPTION

(FIGURE 2-1)

Figure 2-1 is a block diagram that illustrates the major

assemblies contained within the power supply. As shown in

the figure, each supply includes ac input circuits, an GPIB

board, front panel display and keyboard, and two or more

output boards.

2-3 AC Input Circuit

The ac input circuit consists of a line module on the rear

panel of supply, front panel ON/OFF switch S1, power

transformer (T1), located in the front of the chassis, and a

cooling fan located in the rear of the chassis. The line module

contains a voltage selector card that selects the applicable ac

input voltage: 100 Vac, 120 Vac, 220 Vac, or 240 Vac. The

voltage card selection must match the nominal line voltage

that is connected to the unit. The line module also contains

the main fuse F1. An 8 A fuse (normal blow) must be

installed for a 100/120 VAC input; a4 fuse (normal blow)

must be installed for a 220/240 VAC input. The ac input is

applied to the power transformer when S1 is ON.

Depending on the line module setting, the 120 Vac cooling

fan either runs directly from the line module setting, the 120

VAC cooling fan either runs directly from the line or from

the appropriate transformer tap. The power transformer

provides the main ac inputs to the output boards and also

provides the ac inputs for the bias voltage supplies located

on the GPIB board and each output board. Ac power

distribution is shown in detail in Figure 6-1 in the rear of this

manual.

2-4 GPIB Board

The GPIB board contains the GPIB interface, system

microcomputer, output boards interface, and front panel

interface. These circuits provide the interface between the

user and the multiple outputs of the power supply. Each

output board is actually an output channel that can be

individually selected and controlled over the GPIB or from

the supply’s front panel. The GPIB board inter prets

commands from the GPIB or from the front panel to

control the selected output. The GPIB board also processes

measurement and status data received from the output

boards. This data may be read back to the controller over

the GPIB and/or displayed on the supply’s front panel.

Also, each output board can be individually calibrated over

the GPIB using calibration commands (See Appendix A in

Operating Manual). Correction factors are calculated during

calibration and stored in non-volatile memory on the GPIB

board. The GPIB board is described in greater detail in

paragraph 2-7.

2-5 Front Panel

Most of the remote operations that can be performed via the

GPIB can also be performed from the supply’s front panel.

In addition to the ON/OFF switch already mentioned, the

front panel contains an LCD display and a keypad. The LCD

display consists of an alphanumeric display and status

annunciators. The LCD normally displays the measured

output voltage and current of the selected output. When

programming an output from the front panel keypad, the

selected output channel, the function being programmed,

and the present value will be displayed. The annunciators

indicate which output channel has been selected and give

GPIB and power supply status information. The keypad

allows control of the supply’s system functions as well as

individual control of each output channel. Detailed

instructions on using the front panel’s display and keypad

are given in the Operating Manual.

2-6 Output Boards

The Agilent 6625A and 6628A contain two output boards

and the Agilent 6626A and 6629A contain four output

boards. The output combinations that correspond to each

model are shown in Figure 2-1. Each isolated output can

supply power in two ranges as shown in Figure 2-2. This

flexibility allows you to use the same output to power loads

with different voltage and current requirements. The output

ranges and operating characteristics of each output are

described in greater detail in Section IV of the Operating

Manual.

As shown in Figure 2-1, each output board contains a

rectifier/filter, power module, control circuit, secondary

interface circuit, and bias supplies.

The ac input to each output board is rectified, filtered, and

applied to the power module regulator. Each output board

employs series regulation techniques. The regulator element

is connected in series with the load and operates in the linear

region (between saturation and cutoff) of the transistor

characteristic curve. Regulation is achieved by varying the

conduction of the series element in response to changes in

the line voltage or the load. The constant voltage CV control

circuit compares the voltage at the output with a reference

voltage and generates a control signal which varies the

conduction of the series regulator to raise or lower the

output voltage as required. The constant current CC control

2-1

Page 12

2-2

Page 13

Circuit compares the voltage at the current monitor resistor

with a reference and likewise varies the conduction of the

series regulator.

The interface circuit on the output board receives digital

signals from the GPIB board and converts them to analog

signals (reference voltages) which are sent to the control

circuit to program the output voltage and current.

The output boards can be commanded to send measurement

and status data back to the GPIB controller and/or to the

display on the front panel. The data is sent back via the

secondary interface circuit and the appropriate circuits on

the GPIB board.

The output board is able to sink current as well as source

current. Current sink limits are fixed at values slightly

higher than the maximum current source limit for the

particular output voltage operating point. See Figure 2-7 for

typical current source and sink characteristics. The output

board circuits are described in greater in paragraph 2-24.

2-7 GPIB BOARD (FIGURE 2-3)

Figure 2-3 illustrates the major circuits and signal flow on

the GPIB board. Complete circuit details are shown on the

functional schematic in the rear of this manual.

The functional names on the block diagram correspond with

those on the schematic so that the diagrams can be

correlated. As shown in Figure 2-3, the major circuits consist

of the GPIB interface, the system micro-computer, the

output boards interface, and the front panel interface circuit.

2-8 GPIB Interface

These circuits consist of the GPIB bus connector (J201),

transceivers (U203) for the 8 data lines and 8 control lines,

and the GPIB talker/listener chip (U202). All GPIB (IEEE-

488) functions are implemented by the GPIB chip which

handles data transfer between the microprocessor and the

GPIB, handshake protocol, and talker/listener addressing

procedures. The GPIB talker/listener chip is connected to

the data bus and appears as memory locations to the

microprocessor.

The eight data lines (DIO1-DIO8) of the GPIB are reserved

for the transfer of data and other messages in a byte serial,

bit parallel manner. Data and message transfer is

asynchronous, coordinated by the three handshake lines

(DAV, NRFD, and NDAC). The power supply can be a talker

or a listener on the GPIB. The controller dictates the role of

an GPIB device by setting the ATN (attention) line true and

sending talk or listen addresses on the data lines (DIO1DIO8). The power supply’s GPIB address is stored in the

EEPROM (electrically erasable programmable memory) chip

along with other system variables. You can find out your

supply’s GPIB address by using the front panel ADDR key

as described in the operating manual. As shipped from the

factory, the power supply’s address is set to 5. Any address

from 0 through 30 is a valid address.

There are five GPIB control lines: ATN, IFC, REN, SRQ, and

EOI (IEEE-488). When the controller sets the ATN line true,

all devices on the bus must “listen” to the addresses and

universal commands placed on the bus. When ATN is false,

only devices that are addressed will actively send or receive

data. All unaddressed devices will ignore the data lines

when ATN is false.

2-3

Page 14

2-9 System Micro-Computer

The system micro-computer decodes and executes all

instructions, and controls all data transfers. It consists of a

microprocessor, an address decoder, RAM and ROM

memories, data buffers/latches, and a real time clock as

shown in Figure 2-3.

2-10 Microprocessor and Clock Circuits. These circuits

contain a high performance 8-bit microprocessor(U201) and

associated clock circuits. The microprocessor operates on a 1

MHz cycle, which it derives from a 4 MHz ceramic resonator

oscillator(Y201). The 1 MHz Q signal is generated by the

microprocessor for use by other circuit.

A 4 millisecond (approximately) clock signal, applied to the

microprocessor interrupt input, enables the microprocessor

to keep track of real time. This allows the microprocessor to

form necessary tasks on a regular basis. The real time clock

signal is also used to keep track of the time that has elapsed

since the output was last changed. This enables

microprocessor to determine if a CV/CC mode change

occurred before the selected time delay (see Reprogramming

Delay discussion in Section V of the Operating Manual). The

microprocessor inhibits the OCP function until the delay is

over.

The microprocessor also uses the 4 millisecond clock to

determine when to refresh the front panel display and to

perform other regularly scheduled jobs.

The R/W (read/write) output from the microprocessor

indicates the direction of flow on the data bus, either to or

from the microprocessor. A low level R/W signal indicates

that the microprocessor is writing data onto the data bus. A

high level R/W signal indicates that the microprocessor is

reading data that was placed on the bus by the addressed

circuit. The microprocessor uses the address decoder circuit

and the address bus to specify the data transfer locations.

Addresses are valid on the rising edge of the Q signal.

2-11 Data Bus latches (U217) and Buffers (U216). The

timing sequence of the microprocessor is such that the

circuits providing data for the microprocessor are deselected (address disappears) before the microprocessor can

read the data. The data bus latches (U217) latch the data to

be read by the microprocessor. The data is updated on every

falling Q pulse. Data put on the data bus by the

microprocessor goes around the latches though buffers

(U216).

2-12 Free-Run and Signature Analysis Jumpers. The data

bus is connected to the microprocessor through a jumper

pack (W202). For some signature analysis tests of the

microprocessor kernel (microprocessor, RAM, ROM), the

data bus is broken by moving W202 from the NORMAL

position to the NOP position (see paragraph 4-23). This

connects a NOP (no operation) code (free run) to the

microprocessor data inputs. The NOP code does not contain

an address for the next instruction so the microprocessor

goes to the next highest address. Therefore, the address bus

looks like a 16-bit counter that continuously rolls over and

_

_

_

_

_

_

_

starts at zero. The contents of each address appear

sequentially on the data bus (other side of the break) In

addition, for all signature analysis tests, jumper W201

must be moved from the NORM RUN position to the SIG

ANALYSIS position (see paragraph 4-23).

2-13 Address Bus and Address Decoder. The

microprocessor has 16 address lines (A0-A15) allowing it to

address 65,536 locations. The address decoder (U208) allows

each addressable circuit to look at a shorter address. The

chip select signals (CS0-CS8) are decoded from the higher

order address lines (A12-A15). When a data buffer’s CS is

decoded, it places its data on the data bus lines. When a data

latch’s CS is decoded, the output of each latch will be set to

the logic state that is present on the associated data bus line.

If the chip select for the RAM (random access memory),

ROM (read only memory), or talker/listener chip is

decoded, the selected circuit will decode the lower order

address bits supplied to it on the address bus.

2-14 Memory (ROM and RAM). The system microcomputer

contains both ROM (U206) and RAM (U207) devices. The

32KK non-volatile ROM contains the operating program and

parameters. The 2 K static RAM stores variables voltage to

be programmed, output current readback, etc. A third

memory chip, shown in the output board interface block of

Figure 2-3, is the EEPROM (electrically erasable

programmable memory). The EEPROM (U230) stores all of

the system constants including calibration constants, the

supply’s GPIB address, and model number (see paragraph

2-19).

2-15 Real Time Clock. The real time clock (U209) consists

of a 14-stage ripple counter that divides the 1 MHz Q clock

signal from the microprocessor to produce a pulse every 4

milliseconds. The real-time clock is used by the

microprocessor to schedule regular jobs as described

previously. The TIMER ENABLE signal resets the counter to

zero.

___________

__

_

__

_

2-16 Output Boards Interface

This circuit provides the interface between the system

microcomputer and each of the output boards (up to 4) in

the power supply. Data is transferred serially one bit at a

time between latches/buffers on the GPIB board and

optoisolators on the output boards. As shown in Figure 2-3,

the latches/buffers use data bus lines D0-D3 to send/receive

data from the applicable output. Data line D0 is used for

output board 1, D1 for output board 2, D2 for output board

3 (if present), and D3 for output board 4 (if present). A

controlled and regulated 5 volt line is also generated on the

GPIB board to operate art of the opto-isolators on the

output boards. In addition to interfacing with the output

boards, the latches/buffers interface with the 4 K bit serial

EEPROM in which system constants are stored.

2-17 Data Buffers. These 3-state buffers (U212) place the

serial data from each output board and the EEPROM on the

supply’s system microcomputer data bus lines when chip

__

select CS3 is decoded. Serial data from output boards 1-4

appears on data bus lines D0-D3, respectively, and EEPROM

_

2-4

Page 15

serial output data appears on data bus line D7. Logic 0’s will

always appear on data bus lines D4-D6 when CS3 is

decoded because these buffer inputs are connected to

COMMON. All buffer output are held in the high

impedance state when CS3 is not decoded.

2-18 Data Latches. These stages (U213) are edge-triggered

D-type flip-flops. On the rising edge of the CS2 chip select,

the output of each stage will be set to the logic state that is

present on the associated data bus line. Data bus line D0-D3

are the serial data input lines for output boards 1-4,

respectively. Data bus line D4 controls the TIMER ENABLE

signal line to the real time clock circuit; D5 is the chip select

line for the EEPROM; D6 is the clock signal for the

EEPROM; and D7 is the data input line for the EEPROM.

The data that is transferred between the GPIB board and

the output boards (up to 4) passes through optical isolators

located on each output board.

2-19 EEPROM. This 4 K bit serial EEPROM (electrically

erasable programmable memory) stores the power supply’s

GPIB address and model number as well as the constants

used in calibrating the supply. The EEPROM (U230) is

nonvolatile allowing it to retain the stored information after

power is cycled off and on.

Because the RAM operates faster than the EEPROM, at

power on, the stored data is read into RAM in the system

microcomputer via data bus line D7.

The EEPROM’s 4096 bits of read/write memory are divided

into 2 pages of 8 X 256 each. Each register can be serially

read from or written to using data bus line D7. Input data is

received via a data latch and output data is sent via a data

buffer.

Data written to the EEPROM is stored in a location until it is

updated by a write cycle. The CHIP SELECT and CLOCK

signals are use by the microprocessor to control the

EEPROM’s programming modes. AT power on, the

EEPROM signal holds the EEPROM’s CLOCK signal off to

protect against accidental data writes when power is initially

applied.

__

_

__

___________

__

_

_

2-20 Front Panel Interface

These circuits provide the interface between the supply’s

system microcomputer and the front panes (keyboard and

LCD display). The microprocessor uses the data latches

(U210 ) and data buffers (U214) to transfer data between the

supply’s system microcomputer and the front panel.

2-21 Data Latches. On the rising edge of the CS5 chip select

these D-type flip-flops will be set to the logic states that are

present on the data bus lines.

Data bus lines D2-D7 are fed directly to the front panel

display to indicate power supply conditions The LCD

display may indicate the output voltage and current for a

selected output board, the present function being

programmed, a programmed message, or an error message.

__

_

The annunciators provide operating and status information.

The microprocessor uses the real time clock to determine

when update/refresh the display.

Data bus line D0-D2 are fed to the 3 to 8 line keyboard

decoder (U211). The microprocessor successively drives

each of the eight open collector outputs of the decoder and

monitors the four readback lines from the keyboard to

determine which key was pressed. The readback lines are

held high until a depressed key pulls the line low.

2-22 Data Buffers. These 3-state buffers place the keyboard

readback data on data bus lines D4-D7 when chip select CS4

is decoded. As stated above, the microprocessor will use this

information to determine which key was pressed. In

addition buffers provide the following data on bus lines D0D3 when CS4 is decoded:

or

a logic 0 (Jumper W201 is installed in the Skip

D1 - A logic 1 (Jumper W201 is not installed in the

or

a logic 0 (Jumper W201 is installed in the Cal

D2 - A logic 0 indicates Remote Inhibit is true

D3 - A logic 1 indicates OPTION 750 is installed in

All buffer outputs are held in the high impedance state

disconnecting it from the data bus when CS4

__

_

D0 - A logic 1 (Jumper W201 is not installed in the

Skip Self Test position) – tells the

microprocessor to perform the self test at

power on;

Self Test position) – tells the microprocessor

not to perform self test at power on.

Cal Lockout position) – tells the

microprocessor to respond to calibration

commands;

Lockout position ) – tells the microprocessor

to ignore calibration commands. This jumper

provides security against unauthorized

calibration.

(OPTION 750).

power supply.

__

_

is not decoded.

2-23 Bias Supply and Start-Up Circuit

The bias supply (U218) provides + 5 V bias power to operate

the circuits on the GPIB board. The start-up circuit (U220,

U222) generates the OPTO PON signal (delayed +5 V) which

is used to power the optical-isolators on the output boards.

The OPTO PON signal is initially held low for

approximately 100 ms to prevent the erroneous transfer of

data at power on. The start-up circuit also generates PCLR

(power clear) and EEPON (EEPROM power on) signals

when power is turned on. The PCLR signal is held low at

power on to initialize the talker/listener and microprocessor

chips. The EEPON signal is held low at power onto disable

the EEPROM clock. Thus, the start up circuit delays turning

on the microprocessor and optoisolators until the bias

voltages have stabilized. If the line voltage drops after the

unit has been turned on, the start-up circuit will again

generate the low level signals to disable the interface and

remove power from the supply’s outputs.

2-5

_____

_

__

_____

_

_

Page 16

2-6

Page 17

2-24 OUTPUT BOARD

The following paragraphs provide block diagram level

descriptions of the output board. The descriptions cover the

two output board types. Differences between the board

types are given as required. Figure 2-1 shows which output

board types are used in the power supplies.

The descriptions that follow are divided into two main block

diagram discussions: Secondary Interface Circuits and

Control Circuits. The block diagrams illustrate the major

circuits and signal flow on an output board. Complete

circuit details are shown on the output board functional

schematic Figure 6-3 in the rear of the manual. The

functional names on the block diagrams correspond with

those on the functional schematic.

2-25 Secondary Interface Circuits (Figure 2-4)

These circuits receive digital signals from the GPIB board

and convert them to analog signals (voltages) which are sent

to the power mesh and control circuits to program the

output voltage, output current, and overvoltage.

Measurement and status signals are sent back to the

secondary interface circuits from the power mesh and

control circuits to be processed before they are sent on to the

GPIB board and then to the GPIB controller and/or the

front panel. The following paragraphs describe the interface

circuits shown in Figure 2-4.

2-26 Microcomputer. This 8-bit microcomputer (U312)

contains a CPU, ROM, and RAM. These internal circuits

process all data that is transferred between the GPIB board

and the power mesh and control circuits on the output

board. GPIB board data is transferred serially via optical

isolators which connect incoming data to an input port on

the microcomputer and outgoing data to an output port on

the microcomputer.

On the output board side, the microcomputer uses an 8-bit

parallel bi-directional data bus to program DACs which

control the output voltage, output current, overvoltage

setting, and sets the readback DAC. Various status and

operating conditions are read back on the data bus. The

microcomputer also generates address and control signals

which are used by other interface circuits. The interrupt

input to the microcomputer is used in conjunction with

readback monitor switches (U365, U366, and U368) analog

multiplexer (U323) and DAC (U321) to perform a successive

approximation A/D conversion in order to readback output

voltage and current values as well as various test point

voltages.

2-27 Address Decoder. This circuit (U320) decodes

addresses sent by the microcomputer and generates the

appropriate chip select signal (CS0 – CS6) to select which

circuit sends or receives data. CS0 selects the status monitor

(part of U327) to send status data back to the microcomputer

on data bus lines D0-D5. CS1-CS4 determine which DAC

will receive data. CS1 selects the 14-bit CV (Constant

Voltage) DAC, CS2 selects the 14-bit CC (Constant Current)

DAC, CS3 selects the 14-bit Readback DAC and CS4 selects

__

_

__

_

__

_

__

_

__

_____

_

__

_

_

_

__

_

the 8-bit OV (Over Voltage) DAC. C55 selects the

programming latches (U367), and CS6 selects the readback

monitor switches (U365, U366, and U368). The digital inputs

(D0 – D7) to the DAC’s are derived from the GPIB

controller or from the front panel depending upon whether

the supply is in the remote or local mode.

2-28 CV DAC. The 14-bit CV DAC (U313) and amplifier

(U360) convert the digital input signal from D0 –D7

supplied through latches (U369) into an analog signal (CV

PROG) in the range of 0 to – 10 Volts. This output signal is

used as a reference voltage and is send to the voltage control

circuits (see paragraph 2-46) to set the output voltage to the

programmed value.

The most significant bits (MSB’s) are loaded into the input

register of U313 from the data bus when: address line A3

goes high, address line A4 goes low, and CS1 goes low. The

least significant bits (LSB’s) are loaded into the input register

of U313 from the data bus when: address line A3 goes low,

address line A4 goes high, and CS1 goes low. The data in the

input register in transferred to the DAC of U313 when:

address line A3 is high, address line A34 is high, and CS1 is

low.

CV PROG is also sent to the analog multiplexer so that it can

be measured during power on self test.

U369 and U370 provide isolation between the 8-bit data bus

and the CV/CC DAC’s. This isolation assures that signals on

the data bus will not be capacitively coupled through the CV

and CC DAC’s as noise.

2-29 CC DAC. The 14-bit CC DAC (U314) and amplifier

(U361) convert the digital input signals in a similar manner

as the CV DAC into a analog signal (CC PROG) in the range

of 0 to - 10 Volts. This signal is used as a reference voltage

and is sent to the current control circuits (see paragraph 2-

47) to set output current to the programmed value.

The most significant bits (MSB’s) are loaded into the input

register of U313 from the data bus when: address line A3

goes high, address line A4 goes low, and CS1 goes low. The

least significant bits (LSB’s) are loaded into the input register

of U313 from the data bus when: address line A3 goes low,

address line A4 goes high, and CS2 goes low.

This data in the input register is transferred to the DAC of

U314 when: address line A3 is high, address line A4 is high

_

__

and CS2 is low. CC PROG signal is also sent to the analog

multiplexer (U323) seo that it can be measured during

power on self test.

2-30 OV DAC. The 8-bit OV DAC (U363) and amplifier

(U319) convert the digital input into an analog signal (OV

DAC) in the range of 0 to – 10 Volts. This signal is compared

with the output voltage exceeds the programmed OV

setpoint (see paragraph 2-44).

__

__

_

__

_

_

__

__

_

__

_

2-7

Page 18

The OV signals is also sent to the analog multiplexer so that

it can be measured during power on self test.

2-31 Readback Amplifier and Analog Multiplexer. The

analog multiplexer (U323) selects one of eight inputs (value

of these inputs are from 0 to 10 Volts) to be applied to the

readback signal comparator (U324) for the A-to-D converter.

The selected signal is determined by address lines (A0-A2)

which are received from the microcomputer. The analog

inputs to the multiplexer indicate the following:

COM - hardwired to common to reduce noise when no

signals are being sampled.

FUSE - output board’s return fuse status (read back

during power-on self test)

VFS - Readback amp output (U315A)

V/I MUX - Range amp output (U315C)

CV DAC - voltage DAC output

CC DAC - current DAC output

OV DAC - overvoltage DAC output

U315C can be configured as an inverting or non-inverting

amplifier. Swiches (U365) determine it’s configuration as

well as the input to amplify. U366 is use to determine the

gain of the amplifier.

U315B is used as a buffer. For current readback, inputs from

the 4 terminal shunt resistor R408 are select via U365. For

voltage readback low range, U366 (D) is used as the input to

U315C.

2-32 Readback DAC and Signal Comparator. The

readback DAC (U321), amplifier (U362), readback signal

comparator (U324), and analog multiplexer (U323) along

with the microcomputer (U312) form an analog-to-digital

converter (ADC) which monitors the output board signals

sent to the analog multiplexer.

The readback DAC (U321) and amplifier U362 convert the

digital input signal from the microcomputer to an analog

signal in the range of 0 to – 10 volts. The DAC internally

formulates the 14-bit DAC data from the 8-bit (DB0-DB7)

data bus (same as the CV DAC described above).

The output of the DAC and the output of the analog

multiplexer are applied to the signal comarator U324. The

readback DAC, under the control of the microcomputer,

successively approximates the value of the multiplexer’s

output to a 14-bit resolution,. Starting from the most

significant bit, each bit is successively compare to the

multiplexer’s output and is kept or discarded depending on

whether its value is less than (kept) or greater than

(discarded) the multiplexer’s output.

Each comparison (successive approximation) is evaluated by

the microprocessor via its INT input. The microcomputer

maintains a running total of the approximations (sum of the

kept bits) which, when complete, represents the value of the

analog multiplexer’s output.

2-33 CV and CC Programming Range Switching. U367,

U364, and resistor pack U381 determine the attenuation

factor for the CV and CC signals. Programming range

latchU367 receives information via the data bus (DO0 and

DO1), which determines if the power supply will operate in

the low or high voltage and current ranges. Using this

information, U367 sets analog switches U364 for the proper

divider tap for the desired range (full DAC output O to – 10

V for high range, or a portion of the 10 V for the low range).

2-34 Readback Range Switching. U365, U366, and U368

provide readback of the output of the power supply to the

analog multiplexer (U323), except for the 50 V range (VFS).

Readback latch U368 receives information via data lines

DO0 and DO1 which set up monitor switches U365 and gain

select switches U366 to readback the output parameters.

2-35 Signal Processor. This special purpose IC (U327)

processes both analog and digital signals to interface the

microcomputer with the power mesh and control circuits.

The circuits can be functionally divided into status monitor,

overvoltage detector and driver, and power-on/start-up

circuits.

Status Monitor

the control loops, logic to decode these input line, and flipflops to catch and hold changes. The inputs to the status

comparators are the CV LOOP, + CL LOOP, and – CL LOOP

signals from the power control circuits (see Figure 2-5). The

outputs of the comparators are combined in logic circuits

which then go into the set inputs of flip-flops which hold the

status of CVO, + CLO, - CLO, and UNREG outputs. UNREG

is decoded if the output is not regulated by a CV or CL

control loop.

The flip-flops are set by any transition into a decoded state.

This generates a record of whether any of the conditions

(CV, + CL, - CL, UNREG) existed since the last time the flipflops were reset. The STATUS RESET input line from the

microcomputer resets the flip-flops.

The status monitor circuit also receives OV SENSE and

_____

THERM inputs. The THERM signal is received from the

power module(s) in the power mesh (see Figure 2-5) and

indicates when an overtemperature condition exists. Note

that when the microcomputer senses the overtemperature

(OT) condition via data bus line D4, it shuts down the

output. This circuit resets automatically and restores the

output approximately 30 seconds after the temperature

drops sufficiently for safe operation.

________

The OV SENSE input signal indicates when the output’s

overvoltage detector circuit has been tripped and the output

has been shut-down (see overvoltage detector description

below). The THERM and OV SENSE inputs control the OT

and OV outputs of the status monitor. Note that the OT and

OV status are not held in flip-flops. All of status monitor’s

outputs (CVO, CLO, - CLO, OV, OT, and UNREG are

returned to the microcomputer via data bus lines D0-D5

when chip select CS0 is decoded.

– this circuit consists of comparators to monitor

________

__

_____

_

__

_

__

_

________

_____

_

_

________

_

__

_____

_____

_____

__

_____

2-8

Page 19

2-9

Page 20

Overvoltage Detector

signal which shorts the output by firing the SCR crowbar

(within the power module) on the output if any of the

following conditions are present:

1. The output at the + V terminal exceeds the

programmed OV trip point (OV PROG). Note that the

+I READBACK signal provides an offset to

compensate for the voltage drop across the current

monitor resistor. The POV DISABLE signal inhibits

the programmable OV function from affecting the OV

DRIVE signal.

2. The voltage from the + V output terminal to the +S

terminal or from the –S terminal to the –V output

terminal exceeds 10 V (applies to remote sensing

only).

3. A trip signal is received on the output’s OV terminal.

4. The output’s fixed overvoltage circuit is activated.

Power-On/Start-Up

comparator circuit (BIAS TRIP input signal to U327) is

initially low which holds the PCLR and ON/OFF signals

low. With PCLR low, the microcomputer is held in the reset

state.

off preventing any power from reaching the output

terminals.

The turn-on comparator circuit (part of U325) monitors the

unregulated bias supply to determine if it is high enough to

guarantee regulation by the three-pin regulators. The

medium rail voltage is also monitored to ensure that it is

above the minimum level required for proper operation of

the power module. When these two conditions are met, the

BIAS TRIP line is allowed to go high (approximately 0.7 V).

Then, after a delay of approximately 0.3 seconds (provided

by an external delay capacitor, C346), the PCLR signal goes

high allowing the microcomputer to complete its

initialization routine and set the OUTPUT ENABLE line

low. This allows the ON/OFF signal to go high (+ 2.4 V)

enabling the control circuit and current sources which allow

power to reach the output terminals. Note that whenever the

_____________

OUTPUT ENABLE signal is high, the ON/OFF signal is low

and turns off the control circuit thus preventing power from

reaching the output terminals.

If the line voltage drops below a minimum level, the

comparator described above will shut-down the output

(remove power from the output terminals) until normal line

voltage is restored. This resets the microcomputer and sets

the output to the turn-on state.

2-36 Bias Supplies and Precision Reference Voltage. The

bias supplies (U300-U303) generate the voltages required to

operate the circuits on the output board. The precision

reference voltage circuit (U318, U319A/B/C) operates from

the + 15 V bias and generates the VREF outputs (10 V ±

0.5%) which are used by the DAC’s and the control circuit.

____

With ON/OFF low, the power control circuits are held

– This circuit generates the OV DRIVE

– At power-on, the output of the turn-on

________

____ ___

____

_____________

___

2-37 Power Mesh and Control Circuits (Figure 2-5)

The power mesh circuit in the upper half of Figure 2-5

converts the AC from the power transformer to regulated

DC output power. The primary power control element is the

power module hybrid (U338). The power mesh circuit

generates a constant voltage or constant current output

under control of the control circuits shown in the lower half

of Figure 2-5. In addition to controlling the power mesh

circuit, the control circuits send measurement and status

data back to the GPIB controller and/or front panel via the

interface circuits on the output board and the GPIB board.

2-38 Rectifier and Filter. These circuits consist of two full

wave bridge rectifier circuits with filter capacitors connected

across the rectifier outputs. The proper ac voltage levels are

applied to the rectifiers via secondary windings of chassis

power transformer T1 (see Figure 2-1). The rectifiers provide

raw dc o the power module at three different levels (high,

medium, and low power rails). The return line for the

rectifier circuits is fuse protected. If this fuse opens, the

power supply will fail self test, all outputs will be disabled,

and the error message “FUSE CH <n>” will be displayed

(where n specifies the particular output board, 1-4).

2-39 Power-On Circuit and Current Sources. The poweron circuit (Q318 and Q319) is used to turn on the current

source transistors and the bleed circuit (see paragraph 2-43)

which is connected across the output of the supply. The

power –on circuit is activated when it receives the ON/OFF

signal (2.4 V level) from the signal processor (U327).

The current sources U336) are a series of transistors

connected to the high rail. When activated by the power-on

circuit, the current sources supply a few milliamps to the +

BASE DRIVE, in conjunction with the – DRIVE signal (see

BASE DRIVE CIRCUIT description below), control the

conduction of the series pass elements and shunt ( - CL) in

the power module.

2-40 Power Module Reference Voltage. When the current

sources have been turned on, this circuit (P/O U340 and

U337) provides a reference voltage (about 2 V above + V) to

the power module REF input. The REF input is used by an

internal control circuit that allows switching between the

low, medium, and high rails. The reference circuit includes a

transistor (P/O U340) that turns on when the current

sources apply power, a programmable reference (U337)

which provides the reference voltage, and bypass capacitors

C366 and C367.

2-41 Power Module. The power module hybrid U338

receives three unregulated DC voltage levels on its high,

medium, and low voltage input rails. The power module

contains series regulator stages, an SCR overvoltage circuit,

a down programmer, a built-in overtemperature thermistor,

and a reverse output voltage protection diode.

2-10

Page 21

Series Regulators –

pass transistors which regulate the voltage received from the

selected power rail. The power module automatically selects

the proper input rail depending upon the output voltage

required. For example, if the low rail is supplying current

and the output voltage exceeds the low rail minus about 2.5

V, the medium rail begins to raise the voltage on the

BYPASS input and supply current. Finally, if the output

voltage exceeds the medium rail minus about 2.5 V, the high

rail will begin to supply current.

As stated previously, the conduction of the series pass

transistors is controlled by the + BASE DRIVE and – DRIVE

inputs. Normally there is about a diode drop between these

two input pins. The current sources drive the series

regulator into conduction via the + BASE DRIVE input. The

– DRIVE input from the base drive circuit (see paragraph 2-

42) controls the amount of + BASE DRIVE current that

drives the series regulators in order to maintain a regulated

output. Any + BASE DRIVE current from the current source

that is not required by the series pass transistor to regulate

the output is drawn away by the control circuit through the

– DRIVE input via Q335. A level of current through Q335

that exceeds the + BASE DRIVE current can turn on the

power module current sink transistors to sink output

current up to the negative current limit value.

SCR Overvoltage Circuit –

SCR whose gate input is capacitively coupled to the OV

GATE pin. The OV GATE signal can fire the SCR for a

number of reasons which are described later under the

“Overvoltage Protection Circuit” paragraph. In addition to

shorting the output, the fired SCR will cause the OV SENSE

signal to go low signaling the microcomputer to program

the output to zero. The output will remain shorted and

programmed to zero until the circuit is reset. The SCR circuit

is reset when the POV DISABLE signal (OVRST command)

is received by the OV reset circuit (Q320). The condition that

caused the overvoltage must be removed in order for the

circuit to remain reset. If the condition is not removed, the

OV GATE signal will again fire the SCR and disable the

output. Note that in addition to resetting the SCR, the

OVRST command will program the output to the settings

that existed before the OV occurred.

Down Programmer

are used to sink output current and are capable of rapidly

down programming the output voltage to about 2 V. An

external FET down programmer circuit (see paragraph 2-49),

is connected across the output to continue down

programming the output voltage below 2 V.

Overtemperature Protection

overtemperature circuit that consists of a negative

temperature coefficient thermistor that senses the power

module's temperature. When the power module's

temperature rises enough to reduce the THERM input

resistance to about 8 K ohms, the thermistor drops below 2.5

V (approximately) notifying the signal processor that an

overtemperature (OT) condition has occurred. The signal

The series regulator stages consist of series

The power module has an internal

_______

- Separate transistors in the power module

- The power module also contains an

_____

processor then relays this information to the microprocessor

which will shutdown the particular output with the

overtemperature condition. The output will be restored 30

seconds after a safe operating temperature is reached.

Reverse Output Voltage Protection Diode

contains a diode with its cathode connected to the

COLLECTOR output and its anode connected to the power

module COMMON. This diode is essentially connected

across the power supply's output terminals to protect the

output from having reverse voltages applied.

2-42 Peak Current Limit. This circuit Q321, Q322, R407, P/0

U340, quickly limits the amount of current through the

series regulator elements in the power module. It is

activated when the output current exceeds the full scale

value + about 75% in either the sourcing or the sinking

direction.

The series pass regulator in power module U338 is

connected in series with an external resistor (R407). When

the voltage across R407 exceeds a diode drop in either

direction, the peak current limit circuit is activated and

limits the conduction of the series pass transistor element or

current sink transistor. This circuit reacts much faster than

the + or--current control circuits (see paragraph 2-47).

When the peak current limit circuit is activated in the

current source direction, not only will the conduction of the

series regulator be limited, but the current control circuit

(U376) will be quickly activated through P/O U340, CR341,

U376 and R405 to take control of the current limiting action.

2-43 Bleed Circuit. This circuit (Q341, R456, etc.), connected

from + V to - 7 V, provides a fixed current of about 15 mA

through the series pass elements in the power module so

that they are never completely turned off. The bleed circuit

is activated via the power-on circuit when the ON/OFF

signal is high. The bleed circuit maintains stability with

large output capacitors under light loading conditions and

helps to keep the output impedance constant.

2-44 Sense Protect Circuit. This circuit (P/O U375 and

P/O U351) monitors the voltage from + V to + S and from S to - V. If either of these voltages exceeds 1.0 V, the sense

protect circuit will generate a signal which will fire the

overvoltage protection circuits and shut down the output

(see paragraph 2-50). This circuit prevents the output

voltage from being regulated at a value higher than the

maximum value for which it was designed.

2-45 Base Drive Circuit. When activated (ON/ OFF is at

approximately 2.4 volts), this circuit (Q335 and U348)

provides the - DRIVE input to the series regulator and

current sink transistors in the power module. The - DRIVE

input determines how much drive current (+ BASE DRIVE)

the power module will receive. The -DRIVE input is

controlled by either the voltage control (CV), current control

( + CL), or negative current limit circuits ( - CL).

- The power module

2-11

Page 22

2-12

Page 23

The CV or + CL signal controls the base drive circuit via OR

gate diodes CR351 or CR348 to generate the – DRIVE signal

in order to control the conduction of the series regulators in

the power module and provide a regulated output. If the

output is less than the programmed value, the – DRIVE

signal will allow more + BASE DRIVE current causing the

series regulators to conduct more and raise the output. If the

output exceeds the programmed value, the – DRIVE signal

will divert current through Q335 and U348 of the base drive

circuit and away from the + BASE DRIVE power module

input causing the series regulators to conduct less thereby

reducing the output The voltage control (VV) circuit and the

current control (+CL) circuit is described in paragraphs 2-46

and 2-47, respectively.

When the output is operating in negative current limit, the –

CL signal controls the base drive circuit via diode CR354 so

that the – DRIVE signal controls the conduction of the

current sink transistors in the power module. The negative

current limit circuit which generates the – CL signal is

described in paragraph 2-48. The maximum – Base Drive is

reached when the drop across R428 reaches. 6 volts, turning

on part of U348 which limits the base drive to Q335.

2-46 Voltage Control Circuit. When the output is operating

in the constant voltage mode, this circuit generates the CV

control and CV LOOP signals. The CV control signal is

applied through OR gate diode CR351 to control the base

drive circuit in order to regulate the output voltage. The CV

2-13

Page 24

LOOP signal is sent back to the secondary interface circuit to

indicate that the output is in the constant voltage mode of

operation. The voltage control circuit compares the output

voltage to the programmable reference voltage CV PROG to

produce the CV signal. As shown in the simplified

schematic of Figure 2-6, the major components in the voltage

control circuit are: unity gain buffer (U378 and inverter

amplifier U372), output sence buffer U373 (who used for – 5

guard), inverting differential amplifier U352A, and CV error

amplifier U347. The reference voltage (CV PROG, 0 to –10 V)

is applied to U372 which produces a 0 to + 10 V signal

feeding into the summing junction S1 (U347-2). The output

voltage is monitored by U352A which produces a 0 to - 10 V

signal that represents the output voltage magnitude which is

also fed into S1. The 0 to –10 V signal is also sent back (V

READBACK) to the secondary interface to indicate the

magnitude of the output voltage.

If the output voltage exceeds the programmed voltage, the

summing junction goes negative, causing U347/U377 to

produce a positive going CV control signal. For this

condition, the base drive circuits will conduct more and pull

current away from the power module’s + BASE DRIVE

input via the – DRIVE input line. This will cause the power

module’s series regulators to conduct less and thus reduce

the output voltage.

2-14

Page 25

If the output voltage is less than the programmed voltage

,the junction goes positive causing U347/377 to produce a

negative going CV control signal . For this condition ,the

base drive circuit will conduct less allowing more current to

flow into the +BASE DRIVE input. This will cause the power

module’ s series regulator to conduct more and thus increase

the output voltage.

2-47 Current Control Circuit. When the output is operating