AGERE OR3C55-5BA352, OR3C55-5PS208I, OR3C55-5PS240I, OR3C80-4BA352I, OR3C80-4BC432I Datasheet

...

Data Sheet

June 1999

ORCA® Series 3C and 3T

Field-Programmable Gate Arrays

Features

■High-performance, cost-effective, 0.35 µm (OR3C) and

0.3µm (OR3T) 4-level metal technology, (4- or 5-input look-up table delay of 1.1 ns with -7 speed grade in

0.3µm).

■Same basic architecture as lower-voltage, advanced process technology Series 3 architectures. (See ORCA Series 3L FPGA documentation.)

■Up to 186,000 usable gates.

■Up to 452 user I/Os. (OR3Txxx I/Os are 5 V tolerant to allow interconnection to both 3.3 V and 5 V devices, selectable on a per-pin basis.)

■Pin selectable I/O clamping diodes provide 5 V or 3.3 V PCI compliance and 5 V tolerance on OR3Txxx devices.

■Twin-quad programmable function unit (PFU) architecture with eight 16-bit look-up tables (LUTs) per PFU, organized in two nibbles for use in nibbleor byte-wide functions. Allows for mixed arithmetic and logic functions in a single PFU.

■Nine user registers per PFU, one following each LUT, plus one extra. All have programmable clock enable and local set/reset, plus a global set/reset that can be disabled per PFU.

■Flexible input structure (FINS) of the PFUs provides a routability enhancement for LUTs with shared inputs and the logic flexibility of LUTs with independent inputs.

■Fast-carry logic and routing to adjacent PFUs for nibble-, byte-wide, or longer arithmetic functions, with the option to register the PFU carry-out.

■Softwired LUTs (SWL) allow fast cascading of up to three levels of LUT logic in a single PFU for up to 40% speed improvement.

■Supplemental logic and interconnect cell (SLIC) provides 3-statable buffers, up to 10-bit decoder, and PAL*-like AND-OR with optional INVERT in each programmable

Table 1. ORCA Series 3 (3C and 3T) FPGAs

logic cell (PLC), with over 50% speed improvement typical.

■Abundant hierarchical routing resources based on routing two data nibbles and two control lines per set provide for faster place and route implementations and less routing delay.

■TTL or CMOS input levels programmable per pin for the OR3Cxx (5.0 V) devices.

■Individually programmable drive capability:

12 mA sink/6 mA source or 6 mA sink/3 mA source.

■Built-in boundary scan (IEEE †1149.1 JTAG) and TS_ALL testability function to 3-state all I/O pins.

■Enhanced system clock routing for low skew, high-speed clocks originating on-chip or at any I/O.

■Up to four ExpressCLK inputs allow extremely fast clocking of signals onand off-chip plus access to internal general clock routing.

■StopCLK feature to glitchlessly stop/start ExpressCLKs independently by user command.

■Programmable I/O (PIO) has:

—Fast-capture input latch and input flip-flop (FF) latch for reduced input setup time and zero hold time.

—Capability to (de)multiplex I/O signals.

—Fast access to SLIC for decodes and PAL-like functions.

—Output FF and two-signal function generator to reduce CLK to output propagation delay.

—Fast open-drain dive capability

—Capability to register 3-state enable signal.

■Baseline FPGA family used in Series 3+ FPSCs (field programmable system chips) which combine FPGA logic and standard cell logic on one device.

* PAL is a trademark of Advanced Micro Devices, Inc.

†IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

Device |

System |

LUTs |

Registers |

Max User RAM |

User I/Os |

Array Size |

Process |

|

Gates‡ |

Technology |

|||||||

|

|

|

|

|

|

|||

OR3T20 |

36K |

1152 |

1872 |

18K |

196 |

12 x 12 |

0.3 µm/4 LM |

|

|

|

|

|

|

|

|

|

|

OR3T30 |

48K |

1568 |

2436 |

25K |

228 |

14 x 14 |

0.3 µm/4 LM |

|

|

|

|

|

|

|

|

|

|

OR3C/3T55 |

80K |

2592 |

3780 |

42K |

292 |

18 x 18 |

0.3 µm/4 LM |

|

|

|

|

|

|

|

|

|

|

OR3C/3T80 |

116K |

3872 |

5412 |

62K |

356 |

22 x 22 |

0.3 µm/4 LM |

|

|

|

|

|

|

|

|

|

|

OR3T125 |

186K |

6272 |

8400 |

100K |

452 |

28 x 28 |

0.3 µm/4 LM |

|

|

|

|

|

|

|

|

|

‡The system gate counts range from a logic-only gate count to a gate count assuming 30% of the PFUs/SLICs being used as RAMs. The logic-only gate count includes each PFU/SLIC (counted as 108 gates per PFU/SLIC), including 12 gates per LUT/FF pair (eight per PFU), and 12 gates per SLIC/FF pair (one per PFU). Each of the four PIOs per PIC is counted as 16 gates (two FFs, fast-capture latch, output logic, CLK drivers, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32 x 4 RAM (or 512 gates) per PFU.

ORCA Series 3C and 3T FPGAs |

Data Sheet |

June 1999 |

|

|

|

Table of Contents

Contents Page Contents Page

Features ...................................................................... |

1 |

System-Level Features................................................ |

6 |

Description................................................................... |

7 |

FPGA Overview ........................................................ |

7 |

PLC Logic .................................................................. |

7 |

PIC Logic ................................................................... |

8 |

System Features ....................................................... |

8 |

Routing ...................................................................... |

8 |

Configuration ............................................................. |

8 |

ORCA Foundry Development System ...................... |

9 |

Architecture ................................................................. |

9 |

Programmable Logic Cells ........................................ |

11 |

Programmable Function Unit .................................. |

11 |

Look-Up Table Operating Modes ............................ |

13 |

Supplemental Logic and Interconnect Cell (SLIC) .. |

21 |

PLC Latches/Flip-Flops ........................................... |

25 |

PLC Routing Resources .......................................... |

27 |

PLC Architectural Description ................................. |

34 |

Programmable Input/Output Cells ............................. |

36 |

5 V Tolerant I/O ....................................................... |

37 |

PCI Compliant I/O ................................................... |

37 |

Inputs ...................................................................... |

38 |

Outputs .................................................................... |

41 |

PIC Routing Resources ........................................... |

44 |

PIC Architectural Description .................................. |

45 |

High-Level Routing Resources.................................. |

47 |

Interquad Routing .................................................... |

47 |

Programmable Corner Cell Routing ........................ |

48 |

PIC Interquad (MID) Routing ................................... |

49 |

Clock Distribution Network ........................................ |

50 |

PFU Clock Sources ................................................. |

50 |

Clock Distribution in the PLC Array ......................... |

51 |

Clock Sources to the PLC Array ............................. |

52 |

Clocks in the PICs ................................................... |

52 |

ExpressCLK Inputs ................................................. |

53 |

Selecting Clock Input Pins ...................................... |

53 |

Special Function Blocks ............................................ |

54 |

Single Function Blocks ............................................ |

54 |

Boundary Scan ........................................................ |

57 |

Microprocessor Interface (MPI) ................................. |

64 |

PowerPC System .................................................... |

65 |

i960 System ............................................................ |

66 |

MPI Interface to FPGA ............................................ |

67 |

MPI Setup and Control ............................................ |

68 |

Programmable Clock Manager (PCM) ...................... |

72 |

PCM Registers ........................................................ |

73 |

Delay-Locked Loop (DLL) Mode ............................. |

75 |

Phase-Locked Loop (PLL) Mode ............................ |

76 |

PCM/FPGA Internal Interface ................................. |

79 |

PCM Operation ....................................................... |

79 |

PCM Detailed Programming ................................... |

80 |

PCM Applications .................................................... |

83 |

2 |

|

PCM Cautions ........................................................ |

84 |

FPGA States of Operation........................................ |

85 |

Initialization ............................................................. |

85 |

Configuration .......................................................... |

86 |

Start-Up .................................................................. |

87 |

Reconfiguration ...................................................... |

88 |

Partial Reconfiguration ........................................... |

88 |

Other Configuration Options ................................... |

88 |

Configuration Data Format ...................................... |

89 |

Using ORCA Foundry to Generate |

|

Configuration RAM Data ....................................... |

89 |

Configuration Data Frame ...................................... |

89 |

Bit Stream Error Checking ...................................... |

91 |

FPGA Configuration Modes...................................... |

92 |

Master Parallel Mode ............................................. |

92 |

Master Serial Mode ................................................ |

93 |

Asynchronous Peripheral Mode ............................. |

94 |

Microprocessor Interface (MPI) Mode .................... |

94 |

Slave Serial Mode .................................................. |

97 |

Slave Parallel Mode ............................................... |

97 |

Daisy-Chaining ....................................................... |

98 |

Daisy-Chaining with Boundary Scan ...................... |

99 |

Absolute Maximum Ratings.................................... |

100 |

Recommended Operating Conditions .................. |

100 |

Electrical Characteristics ........................................ |

101 |

Timing Characteristics ............................................ |

103 |

Description ........................................................... |

103 |

PFU Timing ......................................................... |

104 |

PLC Timing ........................................................... |

111 |

SLIC Timing .......................................................... |

111 |

PIO Timing ........................................................... |

112 |

Special Function Blocks Timing ........................... |

115 |

Clock Timing ......................................................... |

123 |

Configuration Timing ............................................ |

133 |

Readback Timing ................................................. |

142 |

Input/Output Buffer Measurement Conditions ........ |

143 |

Output Buffer Characteristics ................................. |

144 |

OR3Cxx ................................................................ |

144 |

OR3Txxx .............................................................. |

145 |

Estimating Power Dissipation ................................. |

146 |

OR3Cxx ................................................................ |

146 |

OR3Txxx (Preliminary Information) ...................... |

147 |

Pin Information ....................................................... |

149 |

Pin Descriptions ................................................... |

149 |

Package Compatibility .......................................... |

153 |

Compatibility with OR2C/TxxA Series .................. |

154 |

Package Thermal Characteristics........................... |

194 |

ΘJA ....................................................................... |

194 |

ψJC ...................................................................... |

194 |

ΘJC ...................................................................... |

194 |

ΘJB ...................................................................... |

194 |

FPGA Maximum Junction Temperature ............... |

195 |

Lucent Technologies Inc. |

|

Data Sheet |

|

June 1999 |

ORCA Series 3C and 3T FPGAs |

Table of Contents

Contents |

Page |

|

Package Coplanarity ............................................... |

|

196 |

Package Parasitics .................................................. |

|

196 |

Package Outline Diagrams...................................... |

|

197 |

Terms and Definitions ........................................... |

|

197 |

208-Pin SQFP ....................................................... |

|

198 |

208-Pin SQFP2 ..................................................... |

|

199 |

240-Pin SQFP ....................................................... |

|

200 |

240-Pin SQFP2 ..................................................... |

|

201 |

256-Pin PBGA ....................................................... |

|

202 |

352-Pin PBGA ....................................................... |

|

203 |

432-Pin EBGA ....................................................... |

|

204 |

600-Pin EBGA ....................................................... |

|

205 |

Ordering Information................................................ |

|

206 |

Index........................................................................ |

|

207 |

Tables |

|

|

Table 1. ORCA Series 3 (3C and 3T) FPGAs ............ |

|

2 |

Table 2. ORCA Series 3 System Performance .......... |

|

6 |

Table 3. Look-Up Table Operating Modes ............... |

|

13 |

Table 4. Control Input Functionality .......................... |

|

14 |

Table 5. Ripple Mode Equality Comparator |

|

|

Functions and Outputs ............................................ |

|

18 |

Table 6. SLIC Modes ................................................ |

|

21 |

Table 7. Configuration RAM Controlled |

|

|

Latch/Flip-Flop Operation ........................................ |

|

25 |

Table 8. Inter-PLC Routing Resources ..................... |

|

31 |

Table 9. PIO Options ................................................ |

|

37 |

Table 10. PIO Logic Options .................................... |

|

43 |

Table 11. PIO Register Control Signals .................... |

|

43 |

Table 12. Readback Options .................................... |

|

54 |

Table 13. Boundary-Scan Instructions ..................... |

|

58 |

Table 14. Boundary-Scan ID Code ........................... |

|

59 |

Table 15. TAP Controller Input/Outputs ................... |

|

61 |

Table 16. PowerPC/MPI Configuration ..................... |

|

65 |

Table 17. i960/MPI Configuration ............................. |

|

66 |

Table 18. MPI Internal Interface Signals .................. |

|

67 |

Table 19. MPI Setup and Control Registers ............. |

|

68 |

Table 20. MPI Setup and Control Registers |

|

|

Description ............................................................... |

|

68 |

Table 21. MPI Control Register 2 ............................. |

|

69 |

Table 22. Status Register ......................................... |

|

70 |

Table 23. Device ID Code ........................................ |

|

71 |

Table 24. Series 3 Family and Device ID Values |

..... |

71 |

Table 25. ORCA Series 3 Device ID Descriptions .... |

71 |

|

Table 26. PCM Registers ......................................... |

|

73 |

Table 27. DLL Mode Delay/1x Duty Cycle |

|

|

Programming Values ............................................... |

|

75 |

Table 28. DLL Mode Delay/2x Duty Cycle |

|

|

Programming Values ............................................... |

|

76 |

Table 29. PCM Oscillator Frequency Range 3Txxx .78 |

||

Table 30. PCM Oscillator Frequency Range 3Cxx ... |

78 |

|

Table 31. PCM Control Registers ............................. |

|

80 |

Contents |

Page |

|

Table 32. Configuration Frame Format and |

|

|

Contents .................................................................. |

|

90 |

Table 33. Configuration Frame Size ......................... |

|

91 |

Table 34. Configuration Modes ................................ |

|

92 |

Table 35. Absolute Maximum Ratings .................... |

|

100 |

Table 36. Recommended Operating Conditions ....100 |

||

Table 37. Electrical Characteristics ........................ |

|

101 |

Table 38. Derating for Commercial Devices |

|

|

(OR3Cxx) .............................................................. |

|

103 |

Table 39. Derating for Industrial Devices (OR3Cxx) 103 |

||

Table 40. Derating for Commercial/Industrial |

|

|

Devices (OR3Txxx) ............................................... |

|

103 |

Table 41. Combinatorial PFU Timing |

|

|

Characteristics ....................................................... |

|

104 |

Table 42. Sequential PFU Timing Characteristics |

..106 |

|

Table 43. Ripple Mode PFU Timing |

|

|

Characteristics ....................................................... |

|

107 |

Table 44. Synchronous Memory Write |

|

|

Characteristics ....................................................... |

|

109 |

Table 45. Synchronous Memory Read |

|

|

Characteristics ....................................................... |

|

110 |

Table 46. PFU Output MUX and Direct Routing |

|

|

Timing Characteristics ........................................... |

|

111 |

Table 47. Supplemental Logic and Interconnect |

|

|

Cell (SLIC) Timing Characteristics ........................ |

|

111 |

Table 48. Programmable I/O (PIO) Timing |

|

|

Characteristics ....................................................... |

|

112 |

Table 49. Microprocessor Interface (MPI) Timing |

|

|

Characteristics ....................................................... |

|

115 |

Table 50. Programmable Clock Manager (PCM) |

|

|

Timing Characteristics (Preliminary Information) |

..121 |

|

Table 51. Boundary-Scan Timing Characteristics .. |

122 |

|

Table 52. ExpressCLK (ECLK) and Fast Clock |

|

|

(FCLK) Timing Characteristics .............................. |

|

123 |

Table 53. General-Purpose Clock Timing |

|

|

Characteristics (Internally Generated Clock) ......... |

|

124 |

Table 54. OR3Cxx ExpressCLK to Output Delay |

|

|

(Pin-to-Pin) ............................................................ |

|

125 |

Table 55. OR3Cxx Fast Clock (FCLK) to Output |

|

|

Delay (Pin-to-Pin) .................................................. |

|

126 |

Table 56. OR3Cxx General System Clock (SCLK) |

|

|

to Output Delay (Pin-to-Pin) .................................. |

|

127 |

Table 57. OR3C/Txxx Input to ExpressCLK (ECLK) |

||

Fast-Capture Setup/Hold Time (Pin-to-Pin) .......... |

|

128 |

Table 58. OR3C/Txxx Input to Fast Clock |

|

|

Setup/Hold Time (Pin-to-Pin) ................................ |

|

130 |

Table 59. OR3C/Txxx Input to General System |

|

|

Clock (SCLK) Setup/Hold Time (Pin-to-Pin) .......... |

|

132 |

Table 60. General Configuration Mode Timing |

|

|

Characteristics ....................................................... |

|

133 |

Table 61. Master Serial Configuration Mode Timing |

||

Lucent Technologies Inc. |

3 |

ORCA Series 3C and 3T FPGAs |

Data Sheet |

June 1999 |

|

|

|

Table of Contents

Contents Page Contents Page

Characteristics ...................................................... |

136 |

Table 62. Master Parallel Configuration Mode Timing |

|

Characteristics ...................................................... |

137 |

Table 63. Asynchronous Peripheral Configuration Mode |

|

Timing Characteristics ........................................... |

138 |

Table 64. Slave Serial Configuration Mode Timing |

|

Characteristics ...................................................... |

139 |

Table 65. Slave Parallel Configuration Mode |

|

Timing Characteristics ........................................... |

140 |

Table 66. Readback Timing Characteristics ........... |

142 |

Table 67. Pin Descriptions ...................................... |

149 |

Table 68. ORCA I/Os Summary ............................. |

153 |

Table 69. Series 3 ExpressCLK Pins ..................... |

154 |

Table 70. OR3T20, OR3T30, OR3C/T55, |

|

OR3C/T80, and OR3T125 208-Pin |

|

SQFP/SQFP2 Pinout ............................................ |

155 |

Table 71. OR3T20, OR3T30, OR3C/T55, |

|

OR3C/T80, and OR3T125 240-Pin |

|

SQFP/SQFP2 Pinout ............................................ |

161 |

Table 72. OR3T20, OR3T30, and OR3C/T55 |

|

256-Pin PBGA Pinout ............................................ |

168 |

Table 73. OR3T20, OR3T30, OR3C/T55, |

|

OR3C/T80, and OR3T125 352-Pin PBGA Pinout . 172 |

|

Table 74. OR3C/T80 and OR3T125 432-Pin |

|

EBGA Pinout ......................................................... |

182 |

Table 75. OR3T125 600-Pin EBGA Pinout ............ |

187 |

Table 76. Plastic Package Thermal |

|

Characteristics for the ORCA Series ..................... |

195 |

Table 77. Package Coplanarity .............................. |

196 |

Table 78. Package Parasitics ................................. |

196 |

Table 79. Voltage Options ...................................... |

206 |

Table 80. Temperature Options ............................. |

206 |

Table 81. Package Options .................................... |

206 |

Table 82. ORCA Series 3 Package Matrix ............. |

206 |

Table 83. Speed Grade Options ............................. |

206 |

Figures |

|

Figure 1. OR3C/T55 Array ........................................ |

10 |

Figure 2. PFU Ports .................................................. |

11 |

Figure 3. Simplified PFU Diagram ............................ |

12 |

Figure 4. Simplified F4 and F5 Logic Modes ............ |

14 |

Figure 5. Softwired LUT Topology Examples ........... |

15 |

Figure 6. Ripple Mode .............................................. |

16 |

Figure 7. Counter Submode ..................................... |

17 |

Figure 8. Multiplier Submode .................................... |

18 |

Figure 9. Memory Mode ........................................... |

19 |

Figure 10. Memory Mode Expansion Example— |

|

128 x 8 RAM ........................................................... |

20 |

Figure 11. SLIC All Modes Diagram ......................... |

22 |

Figure 12. Buffer Mode ............................................. |

22 |

Figure 13. Buffer-Buffer-Decoder Mode ................... |

23 |

Figure 14. Buffer-Decoder-Buffer Mode ................... |

23 |

Figure 15. Buffer-Decoder-Decoder Mode ............... |

24 |

Figure 16. Decoder Mode ......................................... |

24 |

Figure 17. Latch/FF Set/Reset Configurations ......... |

26 |

Figure 18. Configurable Interconnect Point .............. |

27 |

Figure 19. Single PLC View of Inter-PLC Route |

|

Segments ................................................................ |

28 |

Figure 20. Multiple PLC View of Inter-PLC Routing |

.32 |

Figure 21. PLC Architecture ..................................... |

35 |

Figure 22. OR3C/Txxx Programmable Input/Output |

|

(PIO) Image from ORCA Foundry ........................... |

36 |

Figure 23. Fast-Capture Latch and Timing ............... |

39 |

Figure 24. PIO Input Demultiplexing ......................... |

40 |

Figure 25. Output Multiplexing (OUT1OUT2 Mode) .42 |

|

Figure 26. Output Multiplexing |

|

(OUT2OUTREG Mode) ........................................... |

42 |

Figure 27. PIC Architecture ...................................... |

46 |

Figure 28. Interquad Routing .................................... |

47 |

Figure 29. hIQ Block Detail ....................................... |

48 |

Figure 30. Top (TMID) Routing ................................. |

49 |

Figure 31. PFU Clock Sources ................................. |

50 |

Figure 32. ORCA Series 3 System Clock |

|

Distribution Overview .............................................. |

51 |

Figure 33. PIC System Clock Spine Generation ...... |

52 |

Figure 34. ExpressCLK and Fast Clock Distribution |

53 |

Figure 35. Top CLKCNTRL Function Block .............. |

56 |

Figure 36. Printed-Circuit Board with Boundary- |

|

Scan Circuitry .......................................................... |

57 |

Figure 37. Boundary-Scan Interface ......................... |

58 |

Figure 38. ORCA Series Boundary-Scan Circuitry |

|

Functional Diagram ................................................. |

60 |

Figure 39. TAP Controller State Transition Diagram |

61 |

Figure 40. Boundary-Scan Cell ................................ |

62 |

Figure 41. Instruction Register Scan Timing |

|

Diagram ................................................................... |

63 |

Figure 42. MPI Block Diagram .................................. |

64 |

Figure 43. PowerPC/MPI .......................................... |

65 |

Figure 44. i960/MPI .................................................. |

66 |

Figure 45. PCM Block Diagram ................................ |

72 |

Figure 46. PCM Functional Block Diagram .............. |

74 |

Figure 47. ExpressCLK Delay Minimization Using |

|

the PCM .................................................................. |

76 |

Figure 48. Clock Phase Adjustment Using the PCM 83 |

|

Figure 49. FPGA States of Operation ....................... |

85 |

Figure 50. Initialization/Configuration/Start-Up |

|

Waveforms .............................................................. |

86 |

Figure 51. Start-Up Waveforms ................................ |

88 |

Figure 52. Serial Configuration Data Format— |

|

Autoincrement Mode ............................................... |

90 |

Figure 53. Serial Configuration Data Format— |

|

4 |

Lucent Technologies Inc. |

Data Sheet |

|

June 1999 |

ORCA Series 3C and 3T FPGAs |

Table of Contents

Contents |

Page |

|

Explicit Mode ........................................................... |

|

90 |

Figure 54. Master Parallel Configuration Schematic |

92 |

|

Figure 55. Master Serial Configuration Schematic ... |

93 |

|

Figure 56. Asynchronous Peripheral Configuration .. |

94 |

|

Figure 57. PowerPC/MPI Configuration Schematic .. |

95 |

|

Figure 58. i960/MPI Configuration Schematic .......... |

|

95 |

Figure 59. Configuration Through MPI ..................... |

|

95 |

Figure 60. Readback Through MPI .......................... |

|

96 |

Figure 61. Slave Serial Configuration Schematic ..... |

97 |

|

Figure 62. Slave Parallel Configuration Schematic .. |

97 |

|

Figure 63. Daisy-Chain Configuration Schematic ..... |

98 |

|

Figure 64. Combinatorial PFU Timing .................... |

|

105 |

Figure 65. Synchronous Memory Write |

|

|

Characteristics ...................................................... |

|

109 |

Figure 66. Synchronous Memory Read Cycle ........ |

|

110 |

Figure 67. MPI PowerPC User Space Read Timing 117 |

||

Figure 68. MPI PowerPC User Space Write Timing 117 |

||

Figure 69. MPI PowerPC Internal Read Timing |

..... 118 |

|

Figure 70. MPI PowerPC Internal Write Timing ...... |

|

118 |

Figure 71. MPI i960 User Space Read Timing ....... |

|

119 |

Figure 72. MPI i960 User Space Write Timing ....... |

|

119 |

Figure 73. MPI i960 Internal Read Timing .............. |

|

120 |

Figure 74. MPI i960 Internal Write Timing .............. |

|

120 |

Figure 75. Boundary-Scan Timing Diagram ........... |

|

122 |

Figure 76. ExpressCLK to Output Delay ................ |

|

125 |

Figure 77. Fast Clock to Output Delay ................... |

|

126 |

Figure 78. System Clock to Output Delay .............. |

|

127 |

Figure 79. Input to ExpressCLK Setup/Hold Time .. |

129 |

|

Figure 80. Input to Fast Clock Setup/Hold Time |

..... |

131 |

Figure 81. Input to System Clock Setup/Hold Time 132 |

||

Contents |

Page |

Figure 82. General Configuration Mode Timing |

|

Diagram ................................................................. |

135 |

Figure 83. Master Serial Configuration Mode |

|

Timing Diagram ..................................................... |

136 |

Figure 84. Master Parallel Configuration Mode |

|

Timing Diagram ..................................................... |

137 |

Figure 85. Asynchronous Peripheral Configuration |

|

Mode Timing Diagram ........................................... |

138 |

Figure 86. Slave Serial Configuration Mode |

|

Timing Diagram ..................................................... |

139 |

Figure 87. Slave Parallel Configuration Mode |

|

Timing Diagram ..................................................... |

140 |

Figure 88. Readback Timing Diagram .................... |

142 |

Figure 89. ac Test Loads ........................................ |

143 |

Figure 90. Output Buffer Delays ............................. |

143 |

Figure 91. Input Buffer Delays ................................ |

143 |

Figure 92. Sinklim (TJ = 25 °C, V DD = 5.0 V) .......... |

144 |

Figure 93. Slewlim (TJ = 25 °C, V DD = 5.0 V) ......... |

144 |

Figure 94. Fast (TJ °C, V DD = 5.0 V) ...................... |

144 |

Figure 95. Sinklim (TJ = 125 °C, V DD = 4.5 V) ........ |

144 |

Figure 96. Slewlim (TJ = 125 °C, V DD = 4.5 V) ....... |

144 |

Figure 97. Fast (TJ = 125 °C, V DD = 4.5 V) ............ |

144 |

Figure 98. Sinklim (TJ = 25 °C, V DD = 3.3 V) .......... |

145 |

Figure 99. Slewlim (TJ = 25 °C, V DD = 3.3 V) ......... |

145 |

Figure 100. Fast (TJ = 25 °C, V DD = 3.3 V) ............ |

145 |

Figure 101. Sinklim (TJ = 125 °C, V DD = 3.0 V) ...... |

145 |

Figure 102. Slewlim (TJ = 125 °C, V DD = 3.0 V) ..... |

145 |

Figure 103. Fast (TJ = 125 °C, V DD = 3.0 V) .......... |

145 |

Figure 104. Package Parasitics .............................. |

196 |

Lucent Technologies Inc. |

5 |

ORCA Series 3C and 3T FPGAs |

Data Sheet |

June 1999 |

|

|

|

System-Level Features

System-level features reduce glue logic requirements and make a system on a chip possible. These features in the ORCA Series 3 include:

■Full PCI local bus compliance.

■Dual-use microprocessor interface (MPI) can be used for configuration, readback, device control, and device status, as well as for a general-purpose interface to the FPGA. Glueless interface to i960* and PowerPC† processors with user-configurable address space provided.

■Parallel readback of configuration data capability with the built-in microprocessor interface.

■Programmable clock manager (PCM) adjusts clock

Table 2. ORCA Series 3 System Performance

phase and duty cycle for input clock rates from

5 MHz to 120 MHz. The PCM may be combined with FPGA logic to create complex functions, such as digital phase-locked loops (DPLL), frequency counters, and frequency synthesizers or clock doublers. Two PCMs are provided per device.

■True, internal, 3-state, bidirectional buses with simple control provided by the SLIC.

■32 x 4 RAM per PFU, configurable as singleor dualport at >176 MHz. Create large, fast RAM/ROM blocks (128 x 8 in only eight PFUs) using the SLIC decoders as bank drivers.

* i960 is a registered trademark of Intel Corporation.

†PowerPC is a registered trademark of International Business Machines Corporation.

Parameter |

# PFUs |

|

Speed |

|

Unit |

||

-4 |

-5 |

-6 |

-7 |

||||

|

|

|

|||||

16-bit Loadable Up/Down Counter |

2 |

78 |

102 |

131 |

168 |

MHz |

|

16-bit Accumulator |

2 |

78 |

102 |

131 |

168 |

MHz |

|

8 x 8 Parallel Multiplier: |

|

|

|

|

|

|

|

Multiplier Mode, Unpipelined1 |

11.5 |

19 |

25 |

30 |

38 |

MHz |

|

ROM Mode, Unpipelined2 |

8 |

51 |

66 |

80 |

102 |

MHz |

|

Multiplier Mode, Pipelined3 |

15 |

76 |

104 |

127 |

166 |

MHz |

|

32 x 16 RAM (synchronous): |

|

|

|

|

|

|

|

Single-port, 3-state Bus4 |

4 |

97 |

127 |

151 |

192 |

MHz |

|

Dual-port5 |

4 |

127 |

166 |

203 |

253 |

MHz |

|

128 x 8 RAM (synchronous): |

|

|

|

|

|

|

|

Single-port, 3-state Bus4 |

8 |

88 |

116 |

139 |

176 |

MHz |

|

Dual-port5 |

8 |

88 |

116 |

139 |

176 |

MHz |

|

8-bit Address Decode (internal): |

|

|

|

|

|

|

|

Using Softwired LUTs |

0.25 |

4.87 |

3.66 |

2.58 |

2.03 |

ns |

|

Using SLICs6 |

0 |

2.35 |

1.82 |

1.23 |

0.99 |

ns |

|

32-bit Address Decode (internal): |

|

|

|

|

|

|

|

Using Softwired LUTs |

2 |

16.06 |

12.07 |

9.01 |

7.03 |

ns |

|

Using SLICs7 |

0 |

6.91 |

5.41 |

4.21 |

3.37 |

ns |

|

36-bit Parity Check (internal) |

2 |

16.06 |

12.07 |

9.01 |

7.03 |

ns |

|

1.Implemented using 8 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

2.Implemented using two 32 x 12 ROMs and one 12-bit adder, one 8-bit input, one fixed operand, one 16-bit output.

3.Implemented using 8 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (7 of 15 PFUs contain only pipelining registers).

4.Implemented using 32 x 4 RAM mode with read data on 3-state buffer to bidirectional read/write bus.

5.Implemented using 32 x 4 dual-port RAM mode.

6.Implemented in one partially occupied SLIC with decoded output set up to CE in same PLC.

7.Implemented in five partially occupied SLICs.

6 |

Lucent Technologies Inc. |

Data Sheet |

ORCA Series 3C and 3T FPGAs |

June 1999 |

Description

FPGA Overview

The ORCA Series 3 FPGAs are a new generation of SRAM-based FPGAs built on the successful OR2C/ TxxA FPGA Series from Lucent Technologies Microelectronics Group, with enhancements and innovations geared toward today’s high-speed designs and tomorrow’s systems on a single chip. Designed from the start to be synthesis friendly and to reduce place and route times while maintaining the complete routability of the ORCA 2C/2T devices, Series 3 more than doubles the logic available in each logic block and incorporates sys- tem-level features that can further reduce logic requirements and increase system speed. ORCA Series 3 devices contain many new patented enhancements and are offered in a variety of packages, speed grades, and temperature ranges.

The ORCA Series 3 FPGAs consist of three basic elements: programmable logic cells (PLCs), programmable input/output cells (PICs), and system-level features. An array of PLCs is surrounded by PICs. Each PLC contains a programmable function unit (PFU), a supplemental logic and interconnect cell (SLIC), local routing resources, and configuration RAM. Most of the FPGA logic is performed in the PFU, but decoders, PAL-like functions, and 3-state buffering can be performed in the SLIC. The PICs provide device inputs and outputs and can be used to register signals and to perform input demultiplexing, output multiplexing, and other functions on two output signals. Some of the sys- tem-level functions include the new microprocessor interface (MPI) and the programmable clock manager (PCM).

PLC Logic

Each PFU within a PLC contains eight 4-input (16-bit) look-up tables (LUTs), eight latches/flip-flops (FFs), and one additional flip-flop that may be used independently or with arithmetic functions.

The PFU is organized in a twin-quad fashion: two sets of four LUTs and FFs that can be controlled independently. LUTs may also be combined for use in arithmetic functions using fast-carry chain logic in either 4-bit or 8-bit modes. The carry-out of either mode may be registered in the ninth FF for pipelining. Each PFU may also be configured as a synchronous 32 x 4 single- or dual-port RAM or ROM. The FFs (or latches) may obtain input from LUT outputs or directly from invertible PFU inputs, or they can be tied high or tied low. The FFs also have programmable clock polarity, clock enables, and local set/reset.

The SLIC is connected to PLC routing resources and to the outputs of the PFU. It contains 3-state, bidirectional buffers and logic to perform up to a 10-bit AND function for decoding, or an AND-OR with optional INVERT (AOI) to perform PAL-like functions. The 3-state drivers in the SLIC and their direct connections to the PFU outputs make fast, true 3-state buses possible within the FPGA, reducing required routing and allowing for realworld system performance.

Lucent Technologies Inc. |

7 |

ORCA Series 3C and 3T FPGAs |

Data Sheet |

June 1999 |

|

|

|

Description (continued)

PIC Logic

Series 3 PIC addresses the demand for ever-increas- ing system clock speeds. Each PIC contains four programmable inputs/outputs (PIOs) and routing resources. On the input side, each PIO contains a fastcapture latch that is clocked by an ExpressCLK. This latch is followed by a latch/FF that is clocked by a system clock from the internal general clock routing. The combination provides for very low setup requirements and zero hold times for signals coming on-chip. It may also be used to demultiplex an input signal, such as a multiplexed address/data signal, and register the signals without explicitly building a demultiplexer. Two input signals are available to the PLC array from each PIO, and the ORCA 2C/2T capability to use any input pin as a clock or other global input is maintained.

On the output side of each PIO, two outputs from the PLC array can be routed to each output flip-flop, and logic can be associated with each I/O pad. The output logic associated with each pad allows for multiplexing of output signals and other functions of two output signals.

The output FF in combination with output signal multiplexing, is particularly useful for registering address signals to be multiplexed with data, allowing a full clock cycle for the data to propagate to the output. The I/O buffer associated with each pad is very similar to the ORCA 2C/2T Series buffer with a new, fast, open-drain option for ease of use on system buses.

System Features

Series 3 also provides system-level functionality by means of its dual-use microprocessor interface and its

innovative programmable clock manager. These functional blocks allow for easy glueless system interfacing and the capability to adjust to varying conditions in today’s high-speed systems.

Routing

The abundant routing resources of the ORCA Series 3 FPGAs are organized to route signals individually or as buses with related control signals. Clocks are routed on a low-skew, high-speed distribution network and may be sourced from PLC logic, externally from any I/O pad, or from the very fast ExpressCLK pins. ExpressCLKs may be glitchlessly and independently enabled and disabled with a programmable control signal using the new StopCLK feature. The improved PIC routing resources are now similar to the patented intra-PLC routing resources and provide great flexibility in moving signals to and from the PIOs. This flexibility translates into an improved capability to route designs at the required speeds when the I/O signals have been locked to specific pins.

Configuration

The FPGA’s functionality is determined by internal configuration RAM. The FPGA’s internal initialization/ configuration circuitry loads the configuration data at powerup or under system control. The RAM is loaded by using one of several configuration modes. The configuration data resides externally in an EEPROM or any other storage media. Serial EEPROMs provide a simple, low pin count method for configuring FPGAs. A new, easy method for configuring the devices is through the microprocessor interface.

8 |

Lucent Technologies Inc. |

Data Sheet |

ORCA Series 3C and 3T FPGAs |

June 1999 |

Description (continued)

ORCA Foundry Development System

The ORCA Foundry Development System is used to process a design from a netlist to a configured FPGA. This system is used to map a design onto the ORCA architecture and then place and route it using ORCA Foundry’s timing-driven tools. The development system also includes interfaces to, and libraries for, other popular CAE tools for design entry, synthesis, simulation, and timing analysis.

The ORCA Foundry Development System interfaces to front-end design entry tools and provides the tools to produce a configured FPGA. In the design flow, the user defines the functionality of the FPGA at two points in the design flow: at design entry and at the bit stream generation stage.

Following design entry, the development system’s map, place, and route tools translate the netlist into a routed FPGA. A static timing analysis tool is provided to determine device speed and a back-annotated netlist can be created to allow simulation. Timing and simulation output files from ORCA Foundry are also compatible with many third-party analysis tools. Its bit stream generator is then used to generate the configuration data which is loaded into the FPGA’s internal configuration RAM. When using the bit stream generator, the user selects options that affect the functionality of the FPGA. Combined with the front-end tools, ORCA Foundry produces configuration data that implements the various logic and routing options discussed in this data sheet.

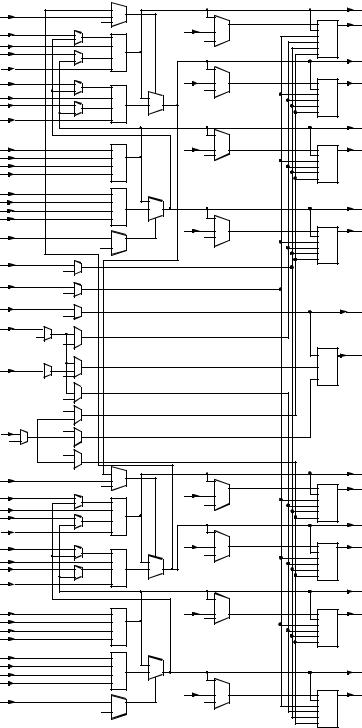

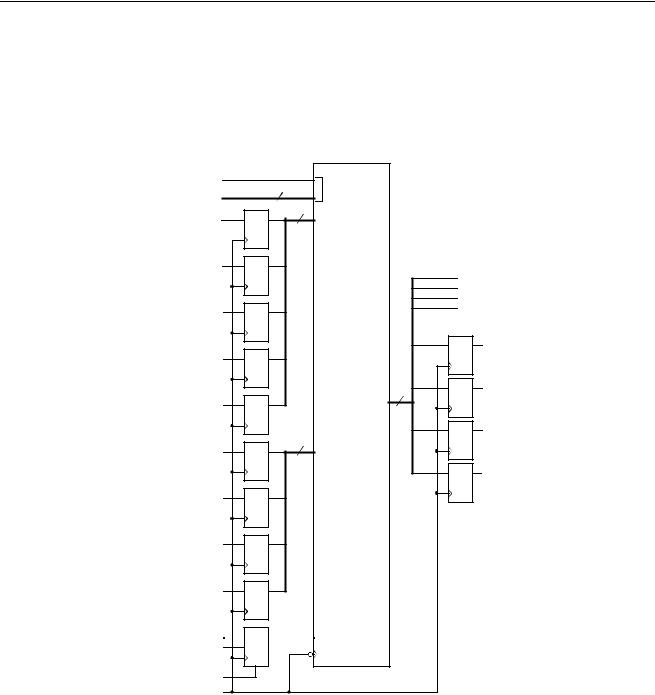

Architecture

The ORCA Series 3 FPGA comprises three basic elements: PLCs, PICs, and system-level functions. Figure 1 shows an array of programmable logic cells (PLCs) surrounded by programmable input/output cells (PICs). Also shown are the interquad routing blocks (hIQ, vIQ) present in Series 3. System-level functions (located in the corners of the array) and the routing resources and configuration RAM are not shown in Figure 1.

The OR3C/T55 array in Figure 1 has PLCs arranged in an array of 18 rows and 18 columns. The location of a PLC is indicated by its row and column so that a PLC in the second row and the third column is R2C3. PICs are located on all four sides of the FPGA between the PLCs and the device edge. PICs are indicated using PT and PB to designate PICs on the top and bottom sides of the array, respectively, and PL and PR to designate PICs along the left and right sides of the array, respectively. The position of a PIC on an edge of the array is indicated by a number, counting from left to right for PT and PB and top to bottom for PL and PR PICs.

Each PIC contains routing resources and four programmable I/Os (PIOs). Each PIO contains the necessary I/O buffers to interface to bond pads. PIOs in Series 3 FPGAs also contain input and output FFs, fast opendrain capability on output buffers, special output logic functions, and signal multiplexing/demultiplexing capabilities.

PLCs comprise a programmable function unit (PFU), a supplemental logic and interconnect cell (SLIC), and routing resources. The PFU is the main logic element of the PLC, containing elements for both combinatorial and sequential logic. Combinatorial logic is done in look-up tables (LUTs) located in the PFU. The PFU can be used in different modes to meet different logic requirements. The LUT’s twin-quad architecture provides a configurable medium-/large-grain architecture that can be used to implement from one to eight independent combinatorial logic functions or a large number of complex logic functions using multiple LUTs. The flexibility of the LUT to handle wide input functions, as well as multiple smaller input functions, maximizes the gate count per PFU while increasing system speed.

The LUTs can be programmed to operate in one of three modes: combinatorial, ripple, or memory. In combinatorial mode, the LUTs can realize any 4- or 5-input logic function and many multilevel logic functions using ORCA’s softwired LUT (SWL) connections. In ripple mode, the high-speed carry logic is used for arithmetic functions, comparator functions, or enhanced data path functions. In memory mode, the LUTs can be used as a 32 x 4 synchronous read/write or read-only memory, in either singleor dual-port mode.

Lucent Technologies Inc. |

9 |

ORCA Series 3C and 3T FPGAs |

Data Sheet |

June 1999 |

|

|

|

Architecture (continued)

VI

PL18 PL17 PL16 PL15 PL14 PL13 PL12 PL11 PL10 LMID PL9 PL8 PL7 PL6 PL5 PL4 PL3 PL2 PL1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PT1 |

|

PT2 |

|

PT3 |

|

PT4 |

|

PT5 |

|

PT6 |

|

PT7 |

|

PT8 |

|

PT9 |

|

TMID |

|

PT10 |

|

PT11 |

|

PT12 |

|

PT13 |

|

PT14 |

|

PT15 |

|

PT16 |

|

PT17 |

|

PT18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

R1C1 |

|

R1C2 |

|

R1C3 |

|

R1C4 |

|

R1C5 |

|

R1C6 |

|

R1C7 |

|

R1C8 |

|

R1C9 |

|

|

R1C10 |

R1C11 |

|

R1C12 |

|

R1C13 |

|

R1C14 |

|

R1C15 |

|

R1C16 |

|

R1C17 |

|

R1C18 |

PR1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R2C1 |

|

R2C2 |

|

R2C3 |

|

R2C4 |

|

R2C5 |

|

R2C6 |

|

R2C7 |

|

R2C8 |

|

R2C9 |

|

vIQ |

R2C10 |

R2C11 |

|

R2C12 |

|

R2C13 |

|

R2C14 |

|

R2C15 |

|

R2C16 |

|

R2C17 |

|

R2C18 |

PR2 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R3C1 |

|

R3C2 |

|

R3C3 |

|

R3C4 |

|

R3C5 |

|

R3C6 |

|

R3C7 |

|

R3C8 |

|

R3C9 |

|

|

R3C10 |

R3C11 |

|

R3C12 |

|

R3C13 |

|

R3C14 |

|

R3C15 |

|

R13C16 |

|

R3C17 |

|

R3C18 |

PR3 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R4C1 |

|

R4C2 |

|

R4C3 |

|

R4C4 |

|

R4C5 |

|

R4C6 |

|

R4C7 |

|

R4C8 |

|

R4C9 |

|

|

R4C10 |

R4C11 |

|

R4C12 |

|

R4C13 |

|

R4C14 |

|

R4C15 |

|

R4C16 |

|

R4C17 |

|

R4C18 |

PR4 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R5C1 |

|

R5C2 |

|

R5C3 |

|

R5C4 |

|

R5C5 |

|

R5C6 |

|

R5C7 |

|

R5C8 |

|

R5C9 |

|

|

R5C10 |

R5C11 |

|

R5C12 |

|

R5C13 |

|

R5C14 |

|

R5C15 |

|

R5C16 |

|

R5C17 |

|

R5C18 |

PR5 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R6C1 |

|

R6C2 |

|

R6C3 |

|

R6C4 |

|

R6C5 |

|

R6C6 |

|

R6C7 |

|

R6C8 |

|

R6C9 |

|

|

R6C10 |

R6C11 |

|

R6C12 |

|

R6C13 |

|

R6C14 |

|

R6C15 |

|

R6C16 |

|

R6C17 |

|

R6C18 |

PR6 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R7C1 |

|

R7C2 |

|

R7C3 |

|

R7C4 |

|

R7C5 |

|

R7C6 |

|

R7C7 |

|

R7C8 |

|

R7C9 |

|

|

R7C10 |

R7C11 |

|

R7C12 |

|

R7C13 |

|

R7C14 |

|

R7C15 |

|

R7C16 |

|

R7C17 |

|

R7C18 |

PR7 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R8C1 |

|

R8C2 |

|

R8C3 |

|

R8C4 |

|

R8C5 |

|

R8C6 |

|

R8C7 |

|

R8C8 |

|

R8C9 |

|

|

R8C10 |

R8C11 |

|

R8C12 |

|

R8C13 |

|

R8C14 |

|

R8C15 |

|

R8C16 |

|

R8C17 |

|

R8C18 |

PR8 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R9C1 |

|

R9C2 |

|

R9C3 |

|

R9C4 |

|

R9C5 |

|

R9C6 |

|

R9C7 |

|

R9C8 |

|

R9C9 |

|

|

R9C10 |

R9C11 |

|

R9C12 |

|

R9C13 |

|

R9C14 |

|

R9C15 |

|

R9C16 |

|

R9C17 |

|

R9C18 |

PR9 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

hIQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PR10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R10C1 |

|

R10C2 |

|

R10C3 |

|

R10C4 |

|

R10C5 |

|

R10C6 |

|

R10C7 |

|

R10C8 |

|

R10C9 |

R10C10 R10C11 R10C12 R10C13 R10C14 R10C15 R10C16 R10C17 R10C18 |

RMID |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R11C1 |

|

R11C2 |

|

R11C3 |

|

R11C4 |

|

R11C5 |

|

R11C6 |

|

R11C7 |

|

R11C8 |

|

R11C9 |

R11C10 R11C11 R11C12 R11C13 R11C14 R11C15 R11C16 R11C17 R11C18 |

PR11 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R12C1 |

|

R12C2 |

|

R12C3 |

|

R12C4 |

|

R12C5 |

|

R12C6 |

|

R12C7 |

|

R12C8 |

|

R12C9 |

R12C10 R12C11 R12C12 R12C13 R12C14 R12C15 R12C16 R12C17 R12C18 |

PR12 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R13C1 |

|

R13C2 |

|

R13C3 |

|

R13C4 |

|

R13C5 |

|

R13C6 |

|

R13C7 |

|

R13C8 |

|

R13C9 |

R13C10 R13C11 R13C12 R13C13 R13C14 R13C15 R13C16 R13C17 R13C18 |

PR13 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R14C1 |

|

R14C2 |

|

R14C3 |

|

R14C4 |

|

R14C5 |

|

R14C6 |

|

R14C7 |

|

R14C8 |

|

R14C9 |

R14C10 R14C11 R14C12 R14C13 R14C14 R14C15 R14C16 R14C17 R14C18 |

PR14 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R15C1 |

|

R15C2 |

|

R15C3 |

|

R15C4 |

|

R15C5 |

|

R15C6 |

|

R15C7 |

|

R15C8 |

|

R15C9 |

R15C10 R15C11 R15C12 R15C13 R15C14 R15C15 R15C16 R15C17 R15C18 |

PR15 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R16C1 |

|

R16C2 |

|

R16C3 |

|

R16C4 |

|

R16C5 |

|

R16C6 |

|

R16C7 |

|

R16C8 |

|

R16C9 |

R16C10 R16C11 R16C12 R16C13 R16C14 R16C15 R16C16 R16C17 R16C18 |

PR16 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R17C1 |

|

R17C2 |

|

R17C3 |

|

R17C4 |

|

R17C5 |

|

R17C6 |

|

R17C7 |

|

R17C8 |

|

R17C9 |

R17C10 R17C11 R17C12 R17C13 R17C14 R17C15 R17C16 R17C17 R17C18 |

PR17 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R18C1 |

|

R18C2 |

|

R18C3 |

|

R18C4 |

|

R18C5 |

|

R18C6 |

|

R18C7 |

|

R18C8 |

|

R18C9 |

R18C10 R18C11 R18C12 R18C13 R18C14 R18C15 R18C16 R18C17 R18C18 |

PR18 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PB1 |

PB2 |

PB3 |

PB4 |

PB5 PB6 |

PB7 |

PB8 |

PB9 PB10 BMID PB11 PB12 PB13 PB14 PB15 PB16 PB17 PB18 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5-4489(F)

Figure 1. OR3C/T55 Array

10 |

Lucent Technologies Inc. |

Data Sheet |

ORCA Series 3C and 3T FPGAs |

June 1999 |

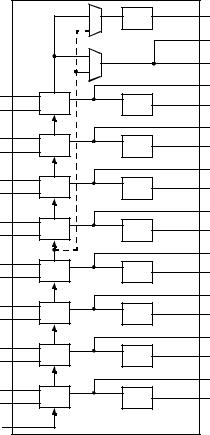

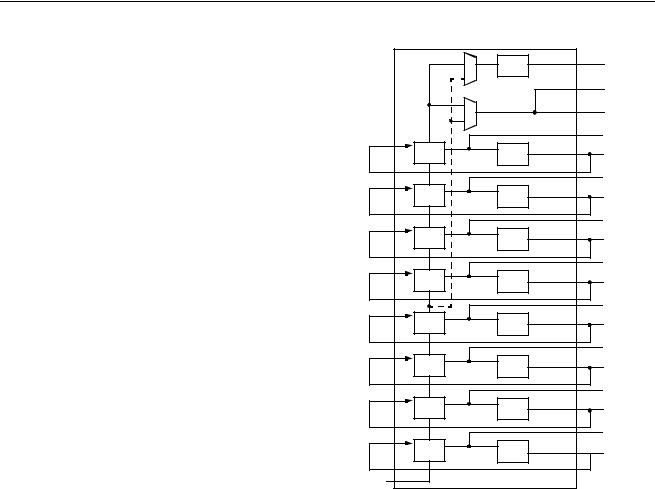

Programmable Logic Cells

The programmable logic cell (PLC) consists of a programmable function unit (PFU), a supplemental logic and interconnect cell (SLIC), and routing resources. All PLCs in the array are functionally identical with only minor differences in routing connectivity for improved routability. The PFU, which contains eight 4-input LUTs, eight latches/FFs, and one FF for logic implementation, is discussed in the next section, followed by discussions of the SLIC and PLC routing resources.

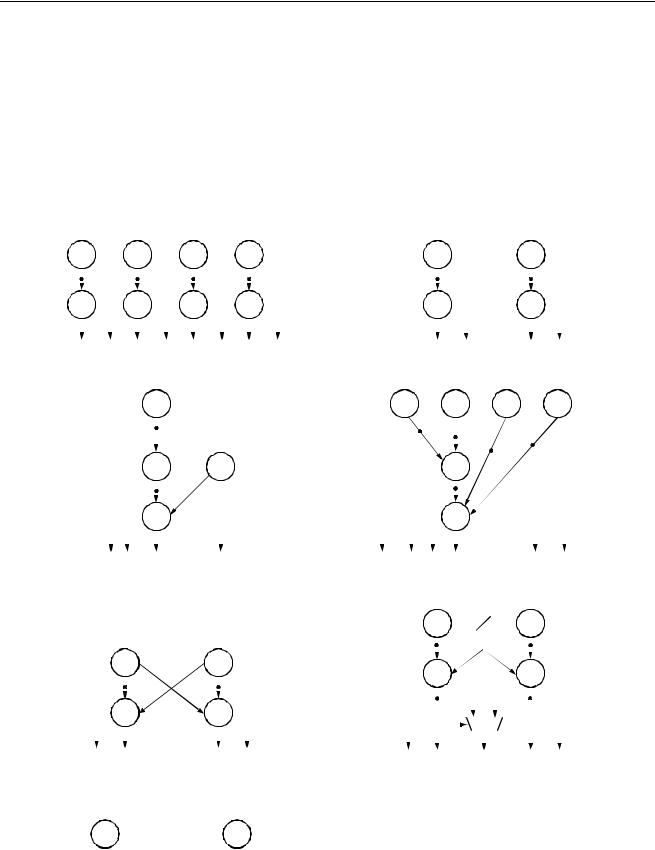

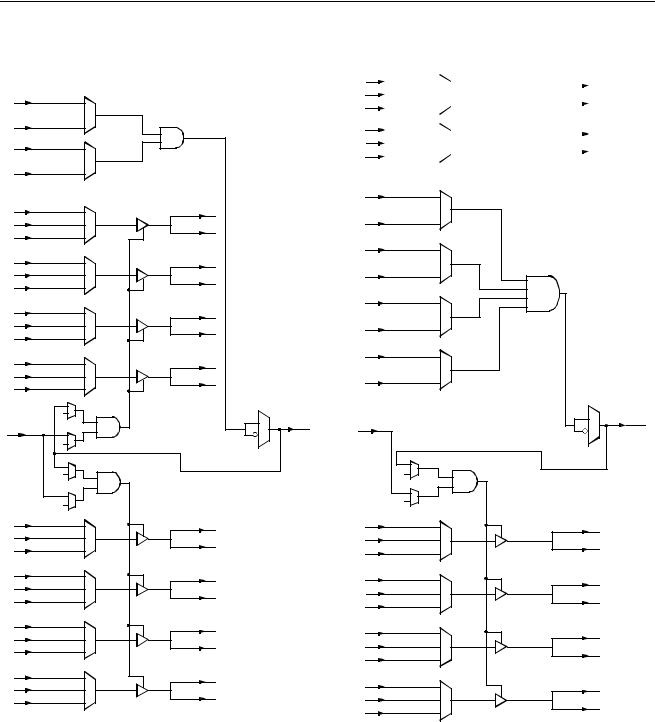

Programmable Function Unit

The PFUs are used for logic. Each PFU has 50 external inputs and 18 outputs and can operate in several modes. The functionality of the inputs and outputs depends on the operating mode.

The PFU uses 36 data input lines for the LUTs, eight data input lines for the latches/FFs, five control inputs (ASWE, CLK, CE, LSR, SEL), and a carry input (CIN) for fast arithmetic functions and general-purpose data input for the ninth FF. There are eight combinatorial data outputs (one from each LUT), eight latched/registered outputs (one from each latch/FF), a carry-out (COUT), and a registered carry-out (REGCOUT) that comes from the ninth FF. The carry-out signals are used principally for fast arithmetic functions.

Figure 2 and Figure 3 show high-level and detailed views of the ports in the PFU, respectively. The eight sets of LUT inputs are labeled as K0 through K7 with each of the four inputs to each LUT having a suffix of _x, where x is a number from 0 to 3. There are four F5 inputs labeled A through D. These inputs are used for a fifth LUT input for 5-input LUTs or as a selector for multiplexing two 4-input LUTs. The eight direct data inputs to the latches/FFs are labeled as DIN[7:0]. Registered LUT outputs are shown as Q[7:0], and combinatorial LUT outputs are labeled as F[7:0].

The PFU implements combinatorial logic in the LUTs and sequential logic in the latches/FFs. The LUTs are static random access memory (SRAM) and can be used for read/write or read-only memory.

Each latch/FF can accept data from its associated LUT. Alternatively, the latches/FFs can accept direct data from DIN[7:0], eliminating the LUT delay if no combinatorial function is needed. Additionally, the CIN input can be used as a direct data source for the ninth FF. The LUT outputs can bypass the latches/FFs, which reduces the delay out of the PFU. It is possible to use the LUTs and latches/FFs more or less independently, allowing, for instance, a comparator function in the LUTs simultaneously with a shift register in the FFs.

Lucent Technologies Inc.

F5D

K7_0

K7_1

K7_2

K7_3

K6_0

K6_1

K6_2

K6_3

K5_0

K5_1

K5_2

K5_3

K4_0

K4_1

K4_2

K4_3

F5C

DIN7

DIN6

DIN5

DIN4

DIN3

DIN2

DIN1

DIN0

CIN

F5B

K3_0

K3_1

K3_2

K3_3

K2_0

K2_1

K2_2

K2_3

K1_0

K1_1

K1_2

K1_3

K0_0

K0_1

K0_2

K0_3

F5A

LSR

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

PROGRAMMABLE

FUNCTION UNIT

(PFU) COUT REGCOUT

F7

F6

F5

F4

F3

F2

F1

F0

CLK CE SEL ASWE

5-5752(F)

5-5752(F)

Figure 2. PFU Ports

The PFU can be configured to operate in four modes: logic mode, half-logic mode, ripple mode, and memory (RAM/ROM) mode. In addition, ripple mode has four submodes and RAM mode can be used in either a singleor dual-port memory fashion. These submodes of operation are discussed in the following sections.

11

ORCA Series 3C and 3T FPGAs |

Data Sheet |

June 1999 |

|

|

|

Programmable Logic Cells (continued)

F5D |

|

|

|

F7 |

|

|

|

REG7 |

Q7 |

||

|

0 |

|

|||

|

DIN7 |

D0 |

|||

K7_0 |

K7 |

D1 |

|

||

|

A |

0 |

DSEL |

|

|

K7_1 |

CE |

|

|||

B |

|

||||

K7_2 |

|

CK |

|

||

|

|

S/R |

|

||

|

C |

|

F6 |

||

K7_3 |

|

|

|||

D |

|

|

|

||

K6_0 |

K6 |

DIN6 |

REG6 |

Q6 |

|

D0 |

|||||

|

|

|

|||

K6_1 |

A |

0 |

D1 |

|

|

B |

1 |

DSEL |

|

||

K6_2 |

CE |

|

|||

|

C |

0 |

CK |

|

|

K6_3 |

D |

|

S/R |

|

|

F5MODE67 |

|

|

|||

|

|

F5 |

|||

|

|

|

|||

|

|

|

|

||

K5_0 |

K5 |

DIN5 |

REG5 |

Q5 |

|

A |

D0 |

||||

K5_1 |

0 |

|

|||

B |

D1 |

|

|||

K5_2 |

|

DSEL |

|

||

C |

|

|

|||

K5_3 |

|

CE |

|

||

D |

|

CK |

|

||

|

|

|

|||

|

|

S/R |

|

||

|

K4 |

|

|

||

K4_0 |

|

|

|

||

A |

|

|

|

||

K4_1 |

|

|

|

||

B |

1 |

|

F4 |

||

K4_2 |

|

||||

C |

|

||||

K4_3 |

0 |

|

|

||

D |

REG4 |

|

|||

|

DIN4 |

Q4 |

|||

|

|

D0 |

|||

F5C |

|

|

|

||

|

0 |

D1 |

|

||

|

0 |

F5MODE45 |

DSEL |

|

|

|

|

CE |

|

||

|

|

|

CK |

|

|

CLK |

|

|

S/R |

|

|

|

0 |

|

|

|

|

SEL |

|

|

|

|

|

|

0 |

|

|

|

|

CIN |

|

|

|

COUT |

|

CE |

0 |

|

|

|

|

|

|

|

|

||

1 |

1 |

|

FF8 |

|

|

|

|

REGCOUT |

|||

|

|

|

D |

||

|

|

|

|

||

ASWE |

|

|

CE |

|

|

|

1 |

|

CK |

|

|

|

|

S/R |

|

||

|

|

|

|

||

|

1 |

|

|

|

|

|

0 |

|

|

|

|

LSR |

0 |

|

|

|

|

|

|

|

|

||

0 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

F3 |

|

F5B |

|

|

REG3 |

|

|

|

0 |

|

Q3 |

||

K3_0 |

DIN3 |

D0 |

|||

K3 |

D1 |

|

|||

K3_1 |

A |

0 |

DSEL |

|

|

CE |

|

||||

B |

|

||||

K3_2 |

|

CK |

|

||

C |

|

S/R |

|

||

|

|

F2 |

|||

K3_3 |

|

|

|||

D |

|

|

|

||

|

|

|

|

||

K2_0 |

K2 |

DIN2 |

REG2 |

Q2 |

|

D0 |

|||||

K2_1 |

A |

0 |

D1 |

|

|

B |

1 |

DSEL |

|

||

K2_2 |

CE |

|

|||

C |

0 |

|

|||

|

CK |

|

|||

K2_3 |

D |

F5MODE23 |

S/R |

|

|

|

|

||||

|

|

F1 |

|||

|

|

|

|

||

K1_0 |

K1 |

DIN1 |

REG1 |

Q1 |

|

A |

D0 |

||||

K1_1 |

0 |

|

|||

B |

D1 |

|

|||

K1_2 |

|

DSEL |

|

||

C |

|

|

|||

K1_3 |

|

CE |

|

||

D |

|

CK |

|

||

|

|

|

|||

|

K0 |

|

S/R |

|

|

K0_0 |

|

|

|

||

A |

|

|

|

||

K0_1 |

1 |

|

|

||

B |

|

F0 |

|||

K0_2 |

0 |

|

|||

C |

|

||||

K0_3 |

|

|

|||

|

|

|

|||

D |

|

REG0 |

|

||

|

DIN0 |

Q0 |

|||