Page 1

PXI-9527

24-Bit High Resolution Dynamic

Signal Acquisition and Generation Module

User’s Manual

Manual Rev.: 2.00

Revision Date: Nov, 17, 2011

Part No: 50-17036-1000

Advance Technologies; Automate the World.

Page 2

Revision History

Revision Release Date Description of Change(s)

2.00 2011/11/17 Initial Release

ii

Page 3

PXI-9527

Preface

Copyright 2011 ADLINK Technology, Inc.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form

without prior written permission of the manufacturer.

Disclaimer

The information in this document is subject to change without prior

notice in order to improve reliability, design, and function and does

not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect,

special, incidental, or consequential damages arising out of the

use or inability to use the product or documentation, even if

advised of the possibility of such damages.

Environmental Responsibility

ADLINK is committed to fulfill its social responsibility to global

environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE)

directive. Environmental protection is a top priority for ADLINK.

We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little

impact on the environment as possible. When products are at their

end of life, our customers are encouraged to dispose of them in

accordance with the product disposal and/or recovery programs

prescribed by their nation or company.

Trademarks

PC, PS/2, and VGA are registered trademarks of International

Business Machines Corp. Borland®, Borland® C, C++ Builder®,

and Delphi® are registered trademarks of the Borland Software

Corporation. LabVIEW™ is a trademark of National Instruments

Corporation. Microsoft®, Visual Basic®, Visual C++®, Windows

Preface iii

®

Page 4

98, Windows® NT, Windows® 2000, Windows® XP, and Windows

Vista® are registered trademarks of Microsoft® Corporation.

PCI™, is a registered trademark of the Peripheral Component

Interconnect Special Interest Group (PCI-SIG).

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks

of their respective companies.

Conventions

Take note of the following conventions used throughout this

manual to make sure that users perform certain tasks and

instructions properly.

Additional information, aids, and tips that help users perform tasks.

NOTE:

NOTE:

Information to prevent minor physical injury, component

damage, data loss, and/or program corruption when try-

CAUTION:

ing to complete a task.

®

Information to prevent serious physical injury, component damage, data loss, and/or program corruption

when trying to complete a specific task.

iv Preface

Page 5

PXI-9527

Table of Contents

Preface .................................................................................... iii

List of Figures ....................................................................... vii

List of Tables.......................................................................... ix

1 Introduction ........................................................................ 1

1.1 Features............................................................................... 2

1.2 Applications ......................................................................... 2

1.3 Specifications....................................................................... 3

1.3.1 Analog Input ............................................................... 3

1.3.2 Analog Output............................................................. 7

1.3.3 Triggers, Timebase..................................................... 9

1.3.4 General Specifications.............................................. 10

1.4 Software Support ............................................................... 11

1.4.1 SDK .......................................................................... 11

1.4.2 DSA-DASK ............................................................... 11

1.4.3 Application Software................................................. 12

2 Getting Started ................................................................. 15

2.1 Installation Environment .................................................... 15

2.2 Package Contents ............................................................. 16

2.3 Device Layout and IO Array............................................... 17

2.4 Installing the module.......................................................... 18

2.5 Signal Connection.............................................................. 19

2.5.1 BNC Connector Polarity ........................................... 19

2.5.2 Analog Input Connection .......................................... 19

2.5.3 Analog Output Connection ....................................... 20

3 Operations ........................................................................ 21

3.1 Functional Block Diagram.................................................. 21

Table of Contents v

Page 6

3.2 Analog Input Channel ........................................................ 22

3.2.1 Analog Input Front-End Configuration ......................22

3.2.2 Input Range and Data Format ..................................23

3.2.3 ADC and Analog Input Filter..................................... 25

3.2.4 FIFO and DMA Transfer For Analog Input................ 25

3.3 Analog Output Channel...................................................... 27

3.3.1 Analog Output Front-End Configuration ...................28

3.3.2 Output Range and Data Format ...............................28

3.3.3 DAC and Analog Output Filter ..................................29

3.3.4 FIFO and DMA Transfer For Analog Output............. 29

3.4 Trigger Source and Trigger Mode...................................... 30

3.4.1 Trigger Sources ........................................................30

3.4.2 Trigger Mode ............................................................33

3.5 ADC and DAC Timing Control ........................................... 34

3.5.1 Timebase Architecture.............................................. 34

3.5.2 DDS Timing VS ADC/DAC Relationship................... 35

3.5.3 Timing Constraints.................................................... 35

3.5.4 Filter Delay in ADC and DAC.................................... 35

4 Calibration ........................................................................ 37

4.1 Calibration Constant .......................................................... 37

4.2 Auto-Calibration ................................................................. 38

4.3 Offset Error Compensation During

AI Sampling Rate Change ....................................... 38

Important Safety Instructions.............................................. 41

Getting Service ..................................................................... 43

vi Table of Contents

Page 7

PXI-9527

List of Figures

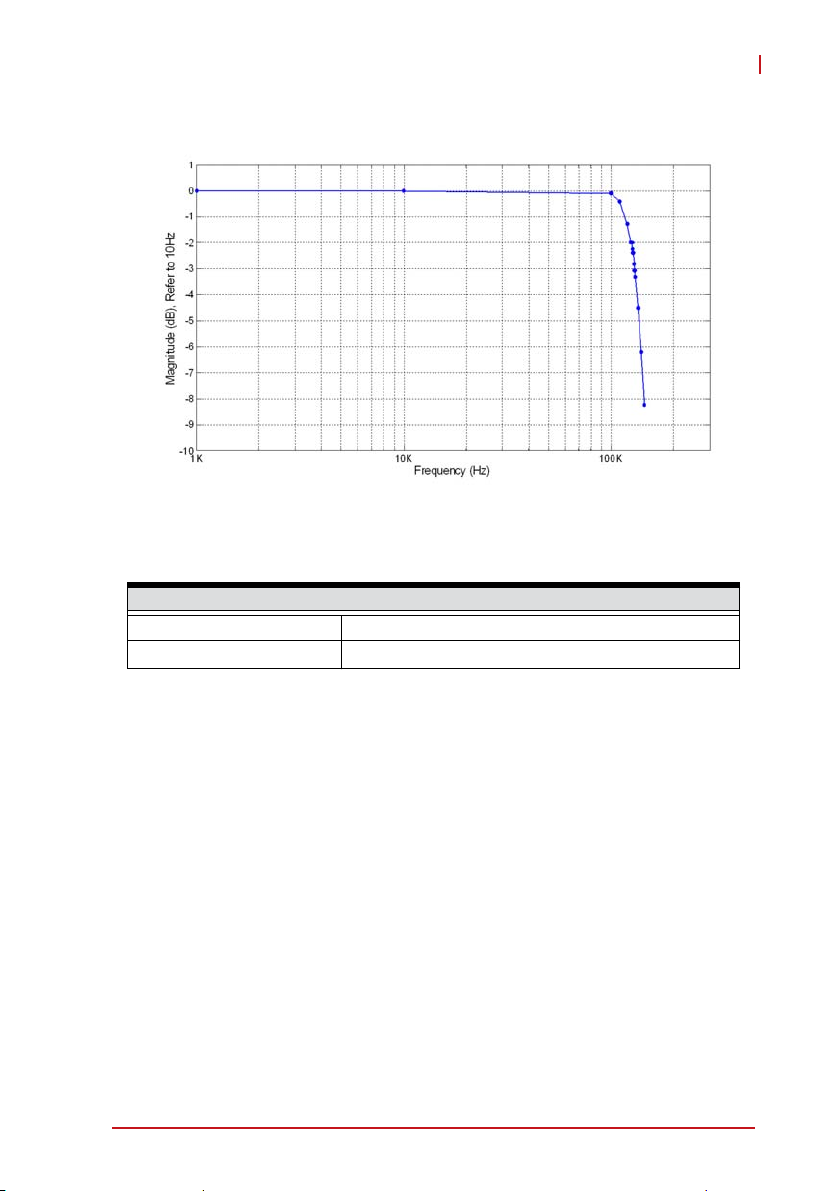

Figure 1-1: Analog Input Channel Bandwidth, ±10 V Input Range5

Figure 1-2: Magnitude Response of AC Couple of Input Channel 6

Figure 1-3: DSA Device Setting Interface ................................... 12

Figure 1-4: DSA Input Interface .................................................. 13

Figure 1-5: DSA Output Interface ............................................... 14

Figure 2-1: PXI-9527 Side View.................................................. 17

Figure 2-2: PXI-9527 I/O array.................................................... 18

Figure 3-1: Analog Input Architecture of the PXI-9527 ............... 22

Figure 3-2: Linked List of PCI Address DMA Descriptors ........... 27

Figure 3-3: Analog Output Architecture of the PXI-9527 ............ 27

Figure 3-4: Trigger Architecture of the PXI-9527 ........................ 30

Figure 3-5: External Digital Trigger ............................................. 31

Figure 3-6: Analog Trigger Conditions ........................................ 32

Figure 3-7: Post-trigger Acquisition / Waveform Generation ...... 34

Figure 3-8: Delay Trigger Mode

Acquisition / Waveform Generation .......................... 34

Figure 3-9: PXI-9527 Timebase Architecture.............................. 34

List of Figures vii

Page 8

This page intentionally left blank.

viii List of Figures

Page 9

PXI-9527

List of Tables

Table 1-1: Channel Characteristics................................................... 3

Table 1-2: Crosstalk.......................................................................... 4

Table 1-3: Transfer Characteristics................................................... 4

Table 1-4: Analog Input Channel Bandwidth ....................................4

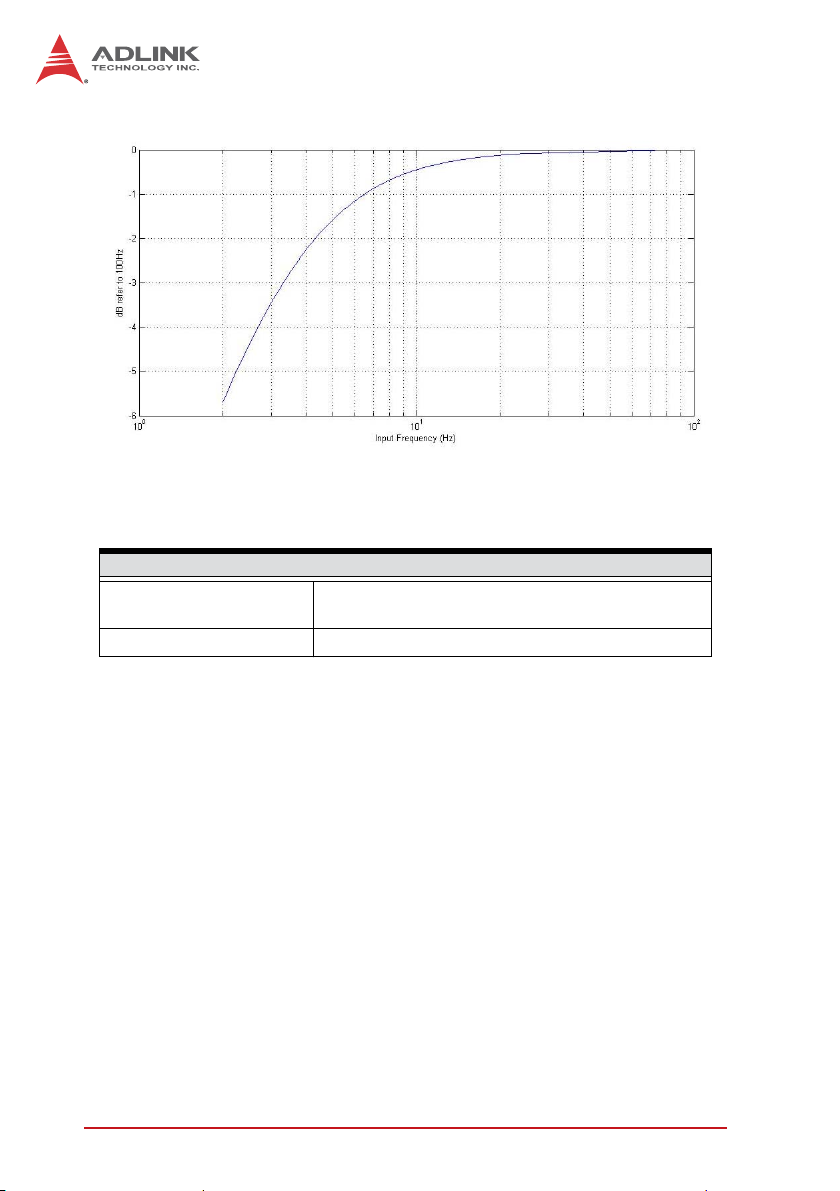

Table 1-5: AC Coupling..................................................................... 5

Table 1-6: Integrated Electronic Piezoelectric (IEPE)....................... 6

Table 1-7: Channel Characteristics................................................... 7

Table 1-8: AO DC Accuracy.............................................................. 7

Table 1-9: Output Impedance ...........................................................8

Table 1-10: AO Dynamic Characteristics ............................................ 8

Table 1-11: Triggers............................................................................ 9

Table 1-12: Analog Trigger .................................................................9

Table 1-13: Digital Trigger .................................................................. 9

Table 1-14: Timebase ......................................................................... 9

Table 2-1: Analog Input Connection ...............................................19

Table 2-2: Analog Output Connection............................................. 20

Table 3-1: Input Configurations....................................................... 22

Table 3-2: Input Range and Data Format .......................................24

Table 3-3: Input Range Midscale Values........................................ 24

Table 3-4: ADC Sample Rates VS DSS Output Clock.................... 25

Table 3-5: Output Configuration...................................................... 28

Table 3-6: Digital Input Code and Analog Output Range................ 28

Table 3-7: DAC (Digital-to-Analog Converter) ................................29

Table 3-8: Timing Relationship of the ADC, DAC and DDS Clock .35

Table 3-9: ADC Filter Delay ............................................................ 36

Table 3-10: DAC Filter Delay ............................................................ 36

Table 4-1: Offset Compensation Time Required

for Various Sampling Rates ........................................... 39

List of Tables ix

Page 10

This page intentionally left blank.

x List of Tables

Page 11

1 Introduction

The PXI-9527 is a high-performance 2-CH analog input and output

dynamic signal acquisition module, specifically suited for use in

audio testing, acoustic measurement, and vibration analysis applications.

The PXI-9527 features two 24-bit simultaneous sampling analog

input channels. A 24-bit sigma-delta ADC provides a sampling rate

up to 432 kS/s at high resolutions, suitable for higher bandwidth

dynamic signal measurements. The sampling rate can be adjusted

by setting the onboard DDS clock source to an appropriate frequency. All channels are sampled simultaneously and accept an

input range from ±40 V to ±0.316 V. The PXI-9527 analog input

supports software selectable AC or DC coupling and 4 mA bias

current for integrated electronic piezoelectric (IEPE) sensors.

The PXI-9527 also provides two channels of 24-bit resolution, high

fidelity analog output. The outputs occur simultaneously at software programmable rates up to 216 kS/s. A software programmable output range of 0.1 V, 1 V, and 10 V is available on the output

channels.

PXI-9527

Introduction 1

Page 12

1.1 Features

X PXI specification Rev. 2.2 compliant

X 24-Bit Sigma-Delta ADC and DAC

X 2-CH simultaneous sampling analog inputs

X 2-CH simultaneous updated analog outputs

X 432 kS/s maximum ADC sampling rate with software pro-

grammable rate

X 216 kS/s maximum DAC update rate with software pro-

grammable rate

X Programmable input range: ±40 V, ±10 V, ±3.16 V, ±1 V,

±0.316 V

X Programmable output range: ±0.1 V, ±1 V, ±10 V

X AC or DC input coupling, software selectable

X Trigger I/O connector for external digital trigger signal

X Support for IEPE output on each analog input, software-

configurable

1.2 Applications

X Audio signal testing

X Acoustic measurement

X Environmental noise testing

X Vibration testing

X Machine condition monitoring

2 Introduction

Page 13

PXI-9527

1.3 Specifications

1.3.1 Analog Input

Channel Characteristics

Channels 2

Input configurations Differential or pseudo-differential

Input coupling AC or DC, software selectable

ADC resolution 24 bit

ADC type Delta-sigma

Sample rates (fs) 432 kS/s maximum, 2 kS/s to 432 kS/s in 454.7

uS/s increments, maximum

FIFO buffer size Total 4096 samples shared for AI channels

Data transfers Direct memory access (DMA)

Input signal range ±40 V

±10 V

±3.16 V

±1 V

±0.316 V

Input Common Mode

Range

Overvoltage protection Differential input: ±40 Vpk

Input impedance Differential configuration

Table 1-1: Channel Characteristics

±10 V for both differential and pseudo-differential

configuration

Pseudo-differential

X Positive terminal: ±40 Vpk

X Negative terminal: ±10 Vpk

X Between (+) and GND: 1 MΩ

X Between (-) and GND: 1 MΩ

Pseudo-differential configuration

X Between (+) and GND: 1 MΩ

X Between (-) and GND: 50 Ω

Introduction 3

Page 14

Crosstalk

Crosstalk

Adjacent channel < -100 dB

Measured with +/-10V input

Input signal is 18 Vpp @ 1kHz sine wave

Table 1-2: Crosstalk

Transfer Characteristics

Input range Offset (±mV) @ Tcal ± 5°C

AI offset

error

AI gain error ±10 V, ±3.16 V, ±1 V, ±0.316 V ±0.2%

Table 1-3: Transfer Characteristics

±40 V 0.5

±10 V 0.2

±3.16 V 0.1

±1 V 0.05

±0.316 V 0.05

±40 V ±0.5%

Analog Input Channel Bandwidth

Input range Bandwidth (-3dB)

±40 V, ±10 V, ±3.16 V, ±1 V, and

±0.316 V

Table 1-4: Analog Input Channel Bandwidth

4 Introduction

130 kHz

Page 15

Figure 1-1: Analog Input Channel Bandwidth, ±10 V Input Range

AC Coupling

-3 dB cutoff frequency 3.5 Hz

-0.1 dB cutoff frequency 26 Hz

Table 1-5: AC Coupling

PXI-9527

Introduction 5

Page 16

Figure 1-2: Magnitude Response of AC Couple of Input Channel

Integrated Electronic Piezoelectric (IEPE)

Current 4 mA, each channel independently software

selectable

Compliance 24 V

Table 1-6: Integrated Electronic Piezoelectric (IEPE)

6 Introduction

Page 17

PXI-9527

1.3.2 Analog Output

Channel Characteristics

Channels 2

Output configurations Differential or pseudo-differential (50 Ω to chas-

sis ground), balance output, each channel independently software selectable

Output coupling DC

DAC resolution 24 bit

DAC type Delta-sigma

Update rates (fs) 1 kS/s to 216 kS/s in 227.3 uS/s increments,

maximum

Minimum working load 600 Ω

Short circuit protection Indefinite protection between positive and nega-

tive

Onboard FIFO buffer size 2048 samples for each AO channel

Data transfers Direct memory access (DMA)

Output signal range ±10 V

±1 V

±0.1 V

Table 1-7: Channel Characteristics

AO DC Accuracy

Output Range

±10 V 1

AO Offset ±mV

AO Gain Error

±%

Introduction 7

±1 V 0.25

±0.1 V 0.05

±10 V 0.4

±1 V 0.4

±0.1 V 0.4

Table 1-8: AO DC Accuracy

Page 18

Output Impedance

Differential

configuration

Between positive output and

chassis ground

Between negative output and

chassis ground

Between positive and

negative outputs

Table 1-9: Output Impedance

AO Dynamic Characteristics

Bandwidth (-3dB) 110 kHz

AO THD + N 100 Hz - 20 kHz, 200 kS/s

±0.1V -89 dB

±1 V -101 dB

±10V -101 dB

Table 1-10: AO Dynamic Characteristics

50 KΩ 10 KΩ

50 KΩ 50 Ω

10 KΩ 10 KΩ

Pseudo-differential

configuration

8 Introduction

Page 19

PXI-9527

1.3.3 Triggers, Timebase

Triggers

Trigger source Software command, analog input, external digital

trigger, PXI star trigger, and PXI trigger bus [0..7]

Trigger mode Post trigger, delay trigger

Table 1-11: Triggers

Analog Trigger

Source AI0 - AI1

Level ± Full-scale, programmable

Trigger conditions Positive or negative

Trigger resolution 24 bit

Table 1-12: Analog Trigger

Digital Trigger

Sources Front panel SMB connector

Compatibility 5V TTL

Trigger polarity Rising or falling edge

Pulse width 65 ns minimum

Table 1-13: Digital Trigger

Timebase

Frequency 80 MHz

Internal Timebase Accuracy ±20 ppm, over operating tempera-

ture range

Table 1-14: Timebase

Introduction 9

Page 20

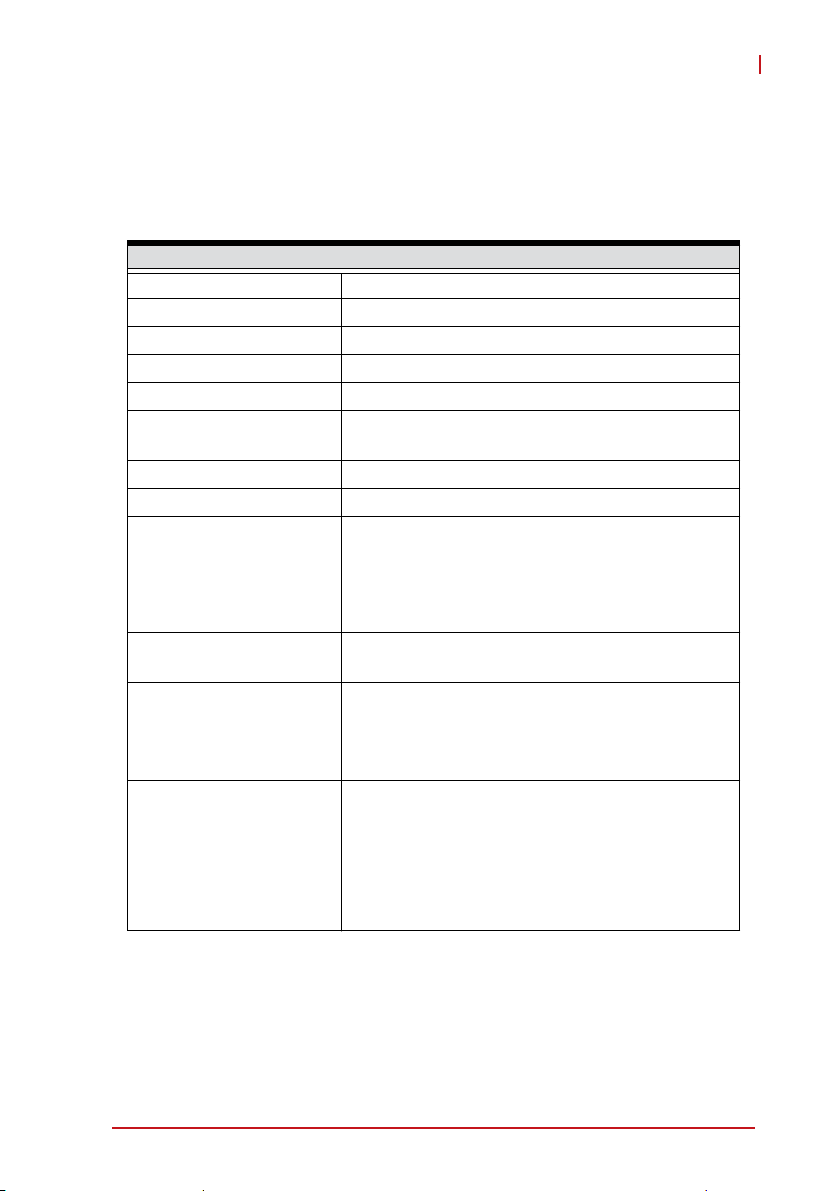

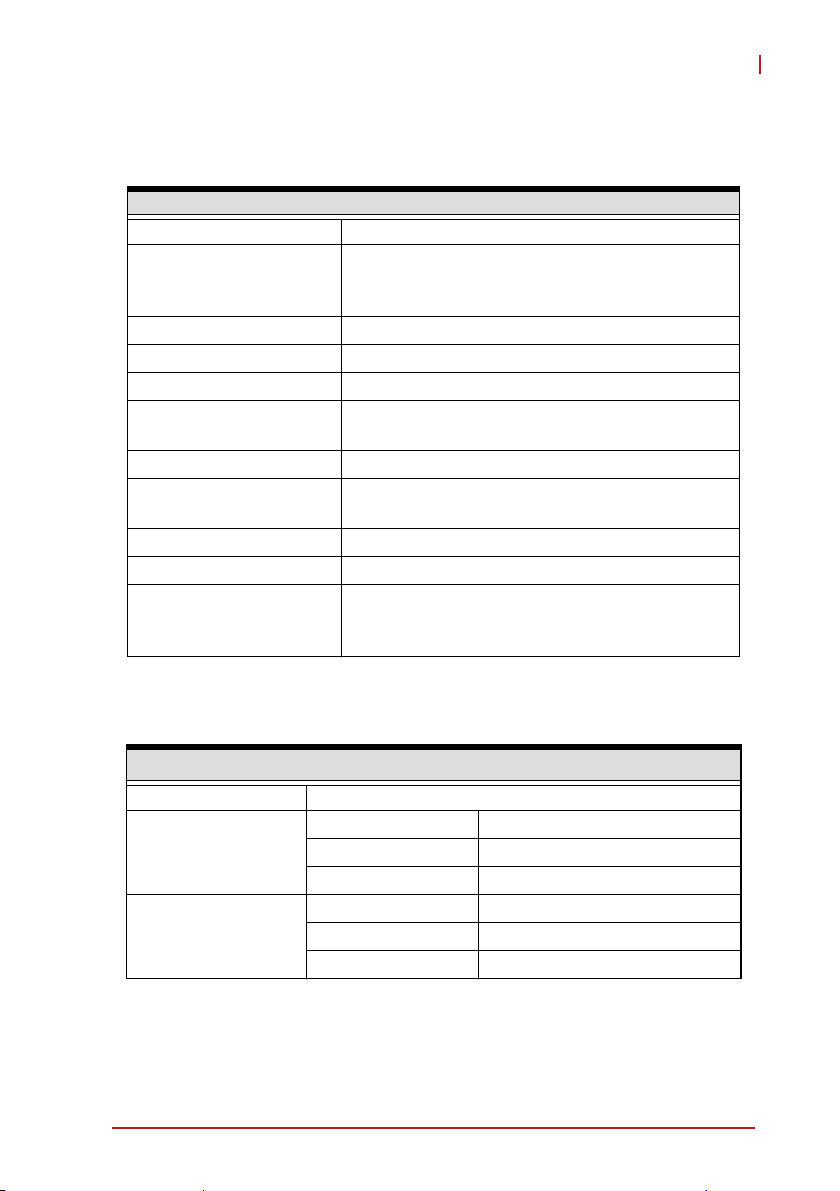

1.3.4 General Specifications

Bus and Physical

Bus interface PCI, 32 bit/ 33MHz

PCI Bus Signaling Universal PCI, support 3.3 V and 5 V PCI

signals

Physical dimensions 160 W x 100 H mm (6.3 x 3.94 in.)

Environment Requirements

Operating environment Temperature:0°C - 50°C

Relative humidity: 5% - 95%, non-condensing

Storage Environment Temperature: -20°C - +80°C

Relative humidity: 5% - 95%, non-condensing

Calibration

Onboard reference +5 V

Temperature coefficient ≤ ±5 ppm/°C

Self-calibration On software command, the PXI-9527 corrects

offset and gain error relative to internal high

stability, high precision reference

External calibration

interval

Warm-up time 15 minutes

1 year

Power Consumption

Power Rail Standby Current (mA) Full Load (mA)

+5 V 930 2330

+12 V 310 350

10 Introduction

Page 21

PXI-9527

1.4 Software Support

ADLINK provides versatile software drivers and packages to suit

various user approaches to building a system. Aside from programming libraries, such as DLLs, for most Windows-based systems, ADLINK also provides drivers for other application

environments such as LabVIEW®.

All software options are included in the ADLINK All-in-One CD.

Commercial software drivers are protected with licensing codes.

Without the code, you may install and run the demo version for

trial/demonstration purposes for only up to two hours. Contact

your ADLINK dealer to purchase the software license.

1.4.1 SDK

For customers who want to write their own programs, ADLINK provides the following software development kits.

Z DAQPilot for Windows, compatible with various applica-

tion environments, such as VB.NET, VC.NET, VB/VC++,

BCB, and Delphi

Z DAQPilot for LabVIEW

Z Toolbox adapter for MATLAB

1.4.2 DSA-DASK

DSA-DASK includes device drivers and DLL for Windows 2000/

XP/Vista/7. DLL is binary compatible across Windows 2000/XP/

Vista/7. This means all applications developed with DSA-DASK

are compatible with these Windows operating systems. The development environment may be VB.NET, VC.NET, VB/VC++, BCB,

and Delphi, or any Windows programming language that allows

calls to a DLL. The DSA-DASK user and function reference manuals are on the ADLINK All-in-One CD.

Introduction 11

Page 22

1.4.3 Application Software

ADLINK’s Dynamic Signal Assistant is a ready-to-run software utility designed for dynamic signal acquisition modules, such as the

PXI-9527. This software provides a windows-based configuration

interface for setting parameters, in addition to a real-time visualized data display on the screen. An instrument-like user interface

is also provided for basic waveform generation. The Dynamic Signal Assistant can also log data acquired from hardware modules.

With the Dynamic Signal Assistant, signal acquisition and generation can be performed in just a few minutes with no programming

required. A brief overview of the application’s operations follows.

The Device Setting window allows selection of a virtual device or

any installed ADLINK DSA devices. Selecting an Operation Mode

allows separate or simultaneous AI and AO operation.

Figure 1-3: DSA Device Setting Interface

12 Introduction

Page 23

The Input window provides operation of AI channels, such as:

X Channel configuration: change AI channels settings and

start/stop acquisition

X Time domain chart: displays acquired data with time domain

mode

X Freq domain chart: calculates acquired data frequency

response and displays the result

X Zoom, copy, save, and print operations for chart images are

all provided by buttons above the displayed charts

PXI-9527

Figure 1-4: DSA Input Interface

Introduction 13

Page 24

The Output window provides operation of AI channels, such as:

X Output of offset, amplitude, frequency, and phase can be

set by, first, settings at the left

X Input of the desired number is enabled via the center key-

pad

X Channels can be enabled/disabled and preferred output

patterns chosen by the bottom buttons

X The top “OUTPUT” button executes AO channel output

Figure 1-5: DSA Output Interface

14 Introduction

Page 25

2 Getting Started

This chapter describes proper installation environment, installation

procedures, package contents and basic information users should

be aware of regarding the PXI-9527.

Diagrams and illustrated equipment are for reference only.

Actual system configuration and specifications may vary.

NOTE:

NOTE:

2.1 Installation Environment

When unpacking and preparing to install, please refer to Important

Safety Instructions.

Only install equipment in well-lit areas on flat, sturdy surfaces with

access to basic tools such as flat- and cross-head screwdrivers,

preferably with magnetic heads as screws and standoffs are small

and easily misplaced.

Recommended Installation Tools

X Phillips (cross-head) screwdriver

X Flat-head screwdriver

X Anti-static wrist strap

X Antistatic mat

ADLINK PXI-9527 DAQ modules are electrostatically sensitive

and can be easily damaged by static electricity. The module must

be handled on a grounded anti-static mat. The operator must wear

an anti-static wristband, grounded at the same point as the antistatic mat.

PXI-9527

Getting Started 15

Page 26

Inspect the carton and packaging for damage. Shipping and handling could cause damage to the equipment inside. Make sure that

the equipment and its associated components have no damage

before installation.

The equipment must be protected from static discharge and

physical shock. Never remove any of the socketed parts

CAUTION:

except at a static-free workstation. Use the anti-static bag

shipped with the product to handle the equipment and wear a

grounded wrist strap when servicing.

2.2 Package Contents

Before continuing, check the package contents for any damage

and ensure that the following items are included:

X PXI-9527 dynamic signal acquisition and generation mod-

ule

X ADLINK All-in-one compact disc

X PXI-9527 User’s Manual

If any of these items are missing or damaged, contact the dealer

from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the

future.

Do not install or apply power to equipment that is damaged or

missing components. Retain the shipping carton and packing

materials for inspection. Please contact your ADLINK dealer/

vendor immediately for assistance and obtain authorization

before returning any product.

16 Getting Started

Page 27

2.3 Device Layout and IO Array

All dimensions are in mm

NOTE:

NOTE:

165.04

162.54

PXI-9527

100

210.03

Figure 2-1: PXI-9527 Side View

Getting Started 17

Page 28

The PXI-9527 I/O array is labeled to indicate connectivity, as

shown.

Figure 2-2: PXI-9527 I/O array

2.4 Installing the module

1. Turn off the PXI system/chassis and disconnect the

power cable from the power source.

2. Align the module’s edge with the module guide in the

PXI chassis.

3. Slide the module into the chassis until resistance is felt

from the PXI connector.

4. Push the ejector upwards and fully insert the module into

the chassis.

18 Getting Started

Page 29

5. Once the module is fully seated, a “click” can be heard

from the ejector latch.

6. Tighten the screw on the front panel.

7. Connect the power plug to a power source and turn on

the PXI system/chassis.

2.5 Signal Connection

2.5.1 BNC Connector Polarity

BNC connector polarity is as shown.

Positive (+)

Negative (-)

PXI-9527

2.5.2 Analog Input Connection

The PXI-9527 input channels can be configured as differential for

ground-reference signal sources, and for floating signal sources,

as pseudo-differential, to provide a reference. In pseudo-differential configuration, the (-) port is grounded through a 50 Ω resistor.

Signal Source Type AI Channel Configuration

Floating Pseudo differential

Ground-Reference Differential

Table 2-1: Analog Input Connection

Getting Started 19

Page 30

2.5.3 Analog Output Connection

If the DUT inputs are ground-referenced, differential output mode

can eliminate measurement errors caused by ground loops.

If the DUT inputs are in a floating system, such as a floating earphone, pseudo-differential output mode provides a reference

ground connected to the positive output of the BNC through a

50 Ω resistor.

DUT Input Reference Type AO Channel Configuration

Floating Pseudo differential

Ground-Reference Differential

Table 2-2: Analog Output Connection

20 Getting Started

Page 31

3 Operations

This chapter contains information regarding analog input, analog

output, triggering and timing for the PXI-9527.

3.1 Functional Block Diagram

AI Channel 0

Front End

Circuit

PXI-9527

Reference Src

AO Channel 0

AO Channel 1

AI Channel 1

Front End

Circuit

Calibration

Mux and

Front End

Circuit

Front End

Circuit

ADC

Interface

DAC

Interface

Offset/Gain

Correction

Local

FIFO

Offset/Gain

Correction

FIFO

FIFO

FP

PF

PCI Interface

Timing Control

and Trigger In

DDS

3&,%XV

Operations 21

Page 32

3.2 Analog Input Channel

3.2.1 Analog Input Front-End Configuration

Figure 3-1: Analog Input Architecture of the PXI-9527

Differential and Pseudo-Differential Input Configuration

The PXC-9527 provides both differential and psuedo-differential input configurations. The differential input mode provides

voltage to the anode and cathode inputs of the BNC connector

according to signal voltage difference between them. If the signal source is ground-referenced, the differential input mode

can be used for common-mode noise rejection.

If the signal source is a floating signal, pseudo-differential input

mode will provide a reference ground connected to the cathode

input of the BNC through a 50 Ω resistor. This will prevent the

floating source from drifting over the input common-mode

range.

The recommended configurations for the signal sources are as

follows..

Signal Source Type Card Configuration

Floating Pseudo differential

Ground-Reference Differential

Table 3-1: Input Configurations

22 Operations

Page 33

PXI-9527

AC and DC Input Coupling

AC and DC coupling are available. With DC coupling, DC offset

present in the input signal is passed to ADC. DC coupling is

indicated if the signal source has a small level of offset voltage

or if DC content of the signal is important.

In AC coupling, the DC offset present in the input signal is

erased. AC coupling is indicated if the DC content of the input

signals is to be rejected. AC coupling enables a high pass R-C

filter through the input signal path. The corner frequency (-3dB)

is about 3Hz.

Input for IEPE

For applications that require sensors such as accelerometers

or microphones, PXI-9527 provides an excitation current

source.

The common excitation current is usually about 4mA for these

IEPE sensors. A DC voltage offset is generated due to the

excitation current and sensor impedance. When IEPE current

sources are enabled, the PXI-9527 automatically sets input

configuration to AC coupling.

3.2.2 Input Range and Data Format

When using an A/D converter, properties of the signal to be measured should be considered prior to selecting channel and signal

connection to the module. Please refer to Section 2.5: Signal Connection.

A/D acquisition is initiated by a trigger source, which must be predetermined. Data acquisition will commence once the trigger condition is established. Following completion of A/D conversion, A/D

data is buffered in a Data FIFO, and can then be transferred to PC

memory for further processing.

Operations 23

Page 34

Transfer characteristics of various input ranges of the PXI-9527

are as follows. Data format of the PXI-9527 is 2’s complement.

Description

Bipolar

Analog

Input

Digital

Code

Description

Bipolar

Analog

Input

Digital

Code

Full-scale

range

±40 V 4.76 uV 39.99999952 V -40 V

±10 V 1.19 uV 9.99999881 V -10 V

±3.1622776V 0.37uV 3.1622773 V -3.1622776 V

±1V 0.119 uV 0.999999881V -1 V

±0.316227 V 0.037uV 0.31622773 V

N/A N/A 7FFFFF 800000

Table 3-2: Input Range and Data Format

Midscale

+1LSB

4.76 uV 0 V -4.76 uV

1.19 V 0 V -1.19 V

0.37uV 0 V -0.37uV

0.119 uV 0 V -0.119 uV

0.037 uV 0 V -0.037 uV

000001 000000 -FFFFFF

Least

significant

bit

Midscale

FSR-1LSB -FSR

-0.31622776

V

Midscale

–1LSB

Table 3-3: Input Range Midscale Values

24 Operations

Page 35

3.2.3 ADC and Analog Input Filter

ADC (Analog-to-Digital Converter)

The PXI-9527 provides sigma-delta analog-to-digital converters, suitable for vibration, audio, and acoustic measurement.

The analog side of the sigma-delta ADC is 1-bit, and the digital

side performs oversampling, noise shaping and digital filtering.

For example, if a desired sampling rate is 108kS/s, each ADC

samples input signals at 6.912MS/s, 64 times the sampling

rate. The 1-bit 6.912MS/s data streams from 1-bit ADC to its

internal digital filter circuit to produce 24-bit data at 108kS/s.

The noise shaping removes quantization noise from low frequency to high frequency. With the digital filter at the last stage,

the digital filter improves the ADC resolution and removes high

frequency quantization noise.

The relationship between ADC sample rate and DDS output

clock is as follows

PXI-9527

Sampling

Rate

DDS CLK

2 K - 54 kHz

512 K -

13.824 MHz

Table 3-4: ADC Sample Rates VS DSS Output Clock

54 K - 108

kHz

6.912 M-

13.824 MHz

108 K-216

kHz

6.912 M-

13.824 MHz

216 K - 432

13.824 M -

27.648 MHz

Filter

Each channel has a two-pole low pass filter. The filters limit the

bandwidth of the signal path and reject band noise.

3.2.4 FIFO and DMA Transfer For Analog Input

FIFO

One FIFO is implemented on the PXI-9527 for analog input

data storage. FIFO depth is 4096 samples, shared between

both AI channels. When only one AI channel is enabled, the

4096-sample-FIFO is used for one-channel data storage.

When both are enabled, the 4096-sample-FIFO is shared

between both channels.

kHz

Operations 25

Page 36

Bus-Mastering Dma Data Transfer

PCI bus-mastering DMA is essential for continuous data

streaming, as it helps to achieve full potential PCI bus bandwidth and improve bus efficiency. The bus-mastering controller

controls the PCI bus, with the host CPU unburdened, since

data is directly transferred to the host memory without intervention. Once analog input begins, the DMA returns control of the

program. During DMA transfer, the hardware temporarily stores

acquired data in the onboard AD Data FIFO, and then transfers

the data to a user-defined DMA buffer in the computer.

Using a high-level programming library for high speed DMA

data acquisition, the sampling period and number of conversions need only be assigned to their specified counters. After

the AD trigger condition is met, data is transferred to the system memory by the bus-mastering DMA.

In a multi-user or multi-tasking OS, such as Microsoft Windows, Linux, or other, it can be difficult to allocate a large continuous memory block. Therefore, the PCI controller provides

DMA transfer with scatter-gather function to link non-continuous memory blocks into a linked list allowing transfer of large

amounts of data without being limited by memory limitations. In

non-scatter-gather mode, the maximum DMA data transfer size

is 2 MB double words (8 MB bytes); in scatter-gather mode,

there is no limitation on DMA data transfer size beyond physical storage capacity of the system. Users can also link descriptor nodes circularly to achieve a multi-buffered DMA. As

shown, in a linked list comprising three DMA descriptors, each

containing a PCI address, PCI dual address, transfer size, and

the pointer to the next descriptor, PCI address and PCI dual

address support 64-bit addresses which can be mapped into

more than 4 GB of address space.

26 Operations

Page 37

First PCI Address PCI Address PCI Address

r

r

r

First Dual Address Dual Address

Transfer Size

Next Descripto

Transfer Size

Next Descripto

Next Descripto

PCI Bus

Local Memory

(FIFO)

Figure 3-2: Linked List of PCI Address DMA Descriptors

3.3 Analog Output Channel

PXI-9527

Dual Address

Transfer Size

Attenuator

x1

x0.1

x0.01

IV

Converter

DAC

CH0

IV

Converter

DAC

CH1

Differential

Driver

Differential

Driver

XLR

Switch

AO GND

AO CH0+

AO CH0- / AOGND

AO CH1+/ AO CH0-

AO CH1- / AOGND

Figure 3-3: Analog Output Architecture of the PXI-9527

Operations 27

CHASSIS

GND

Page 38

3.3.1 Analog Output Front-End Configuration

Differential and Pseudo-Differential Output Configuration

Differential output provides voltage to the anode and cathode

outputs of the BNC connector according to DAC output voltage

difference between the two. If the DUT inputs are ground-referenced, the differential output mode can be used for the elimination of measurement errors caused by ground loops.

If the DUT inputs are in a floating system, such as a floating

earphone, pseudo-differential output mode provides a reference ground connected to the cathode output of the BNC

through a 50 Ω resistor. This prevents the floating system from

drifting beyond its input common-mode range.

The recommended configurations for DUT input reference

types are as follows.

DUT Input Reference Type Card Configuration

Floating Pseudo-differential

Ground-reference Differential

Table 3-5: Output Configuration

3.3.2 Output Range and Data Format

Ideal PXI-9527 transfer characteristics for various input codes versus output voltages are as follows. The PXI-9527 data format is

2’s-complement.

Description

Full-scale

range

Least

significant bit

FSR-1LSB 7FFFFF 9.99999881 V 0.999999881 V 0.099999988 V

Midscale

+1LSB

Midscale 000000 0 V 0 V 0 V

Table 3-6: Digital Input Code and Analog Output Range

28 Operations

Digital

Input Code

N/A ±10 V ±1 V ±0.1 V

N/A 1.19uV 0.119uV 0.012uV

000001 1.19 uV 0.119 uV 0.012 uV

Bipolar Analog Output

Page 39

PXI-9527

Description

Midscale

–1LSB

-FSR 800000 -10 V -1 V -0.1 V

Table 3-6: Digital Input Code and Analog Output Range

Digital

Input Code

FFFFFF -1.19 uV -0.119 uV -0.012 uV

Bipolar Analog Output

3.3.3 DAC and Analog Output Filter

DAC (Digital-to-Analog Converter)

The PXI-9527 provides two 24-bit delta-sigma DACs, separating sample rates into four regions between 1kS/s and 216kS/s,

as shown in Table 3-7, “DAC (Digital-to-Analog Converter)”.

Different bandwidths of internal digital filter for each region optimize DA dynamic performance over all sample rate regions.

For example, lower sample rates correspond to a lowered digital filter bandwidth. SNR of the output current is improved and

the requirement for external analog low pass filtering is eliminated.

The relationship between DAC sample rate and DDS output

clock is as follows

Update

Rate

DDS CLK

Analog Front-End Filter

Each channel has a 3-pole low pass filter. The cutoff frequency

is set at 110 kHz to limit the bandwidth of the signal path and

eliminate most out-of-band images and noise.

1K-27kHz 27K-54kHz 54K-108kHz 108K-216kHz

512 K-13.824

MHz

Table 3-7: DAC (Digital-to-Analog Converter)

6.912 M-

13.824 MHz

6.912 M-

13.824 MHz

27.648 MHz

13.824 M-

3.3.4 FIFO and DMA Transfer For Analog Output

FIFO

The PXI-9527 implements two FIFOs for analog output, each

having a depth of 2048 samples.

Operations 29

Page 40

Bus-mastering DMA Data Transfer

For analog output, data is transferred from host PC memory to

onboard FIFO by DMA transfer. Please see Section 3.2.4:

FIFO and DMA Transfer For Analog Input for a detailed

description.

3.4 Trigger Source and Trigger Mode

This section details PXI-9527 triggering operations. Since AI and

AO share the same trigger source, when their operations are

simultaneously enabled, the trigger signal is valid only when both

are ready to receive the trigger signal. For more details of programming the PXI-9527, please refer to the software operation

manual.

3.4.1 Trigger Sources

TRG Input

SMB Connector

PXI Interface

Software Trigger

Digital Trigger Input

AI CH0 Analog

Trigger

AI CH1 Analog

Trigger

PXI_STAR

PXI Trigger Bus

[0..7]

To Internal

Trigger

Decision

Trigger Source Mux

FPGA Circuit

Digital Trigger Output

Trigger Output Mux

TRG I/O

SMB Connector

e

ac

PXI Interf

Figure 3-4: Trigger Architecture of the PXI-9527

The PXI-9527 requires a trigger to implement acquisition of data.

Configuration of triggers requires identification of trigger source.

The PXI-9527 supports internal software trigger, external digital

trigger, PXI_STAR trigger, PXI Trigger Bus [0.7], and SSI bus as

well as analog trigger.

30 Operations

Page 41

PXI-9527

Software Trigger

The software trigger, generated by software command, is

asserted immediately following execution of specified function

calls to begin the operation.

External Digital Trigger

An external digital trigger is generated when a TTL rising edge

or a falling edge is detected at the SMB connector on the front

panel. As shown, trigger polarity can be selected by software.

Note that the signal level of the external digital trigger signal

should be TTL compatible, and the minimum pulse width is 65

ns.

Pulse Width > 65ns Pulse Width > 65ns

Rising edge trigger

event

Falling edge trigger

event

Figure 3-5: External Digital Trigger

PXI STAR Trigger

When PXI STAR is selected as the trigger source, the PXI9527 accepts a TTL-compatible digital signal as a trigger signal. The trigger occurs when a rising edge or falling edge is

detected at PXI STAR, with trigger polarity configurable by software. The minimum pulse width requirement of this digital trigger signal is 65 ns.

PXI Trigger Bus

The PXI-9527 utilizes PXI Trigger Bus Numbers 0 through 7 to

act as a System Synchronization Interface (SSI). With the inter-

Operations 31

Page 42

connected bus provided by PXI Trigger Bus, multiple modules

are easily synched. When configured as input, the PXI-9527

serves as a slave module and can accept trigger signals from

one of buses 0 through 7. When configured as output, the PXI9527 serves as a master module and can output trigger signals

to the PXI Trigger Bus Numbers 0 through 7.

Analog Trigger

The PXI-9527 analog trigger circuitry can be configured to

monitor one analog input channel from which data is acquired.

Selection of an analog input channel as the analog trigger

channel does not influence the input channel acquisition operation. The analog trigger circuit generates an internal digital trigger signal based on the condition between the analog signal

and the defined trigger level.

Analog trigger conditions are as follows:

Z Positive-slope trigger: The trigger event occurs when the

analog input signal changes from a voltage lower than

the specified trigger level to a voltage exceeding the

specified trigger level.

Z Negative-slope trigger: The trigger event occurs when

the analog input signal changes from a voltage exceeding the specified trigger level to a voltage lower than the

specified trigger level.

Figure 3-6: Analog Trigger Conditions

32 Operations

Page 43

PXI-9527

Trigger Export

The PCI/PXI-9527 can export trigger signals to the SMB TRG

IO on the front panel, and PXI Trigger Bus Numbers 0 through

7. The TRG IO on the front panel can also be programmed to

output the trigger signal when the trigger source is generated

by software, PXI STAR, or PXI Trigger Bus Numbers 0 through

7. The PXI-9527 utilizes PXI Trigger Bus Numbers 0 through 7

to act as the System Synchronization Interface. When configured as the output, the PXI-9527 serves as a master module

and can output trigger signals to synchronize the slave modules. The trigger signal can be routed to any of the seven PXI

Trigger Bus Numbers via software.

3.4.2 Trigger Mode

Two trigger modes applied to trigger sources initiate different data

acquisition timings when a trigger event occurs. The following trigger mode descriptions are applied to analog input and analog output functions.

Post Trigger Mode

If post trigger mode is configured, activity commences once the

following trigger conditions are met:

Z The analog input channel acquires a programmed num-

ber of samples at a specified sampling rate

Z The analog output channel outputs pre-defined voltage

at a specified output rate

Operations 33

Page 44

Figure 3-7: Post-trigger Acquisition / Waveform Generation

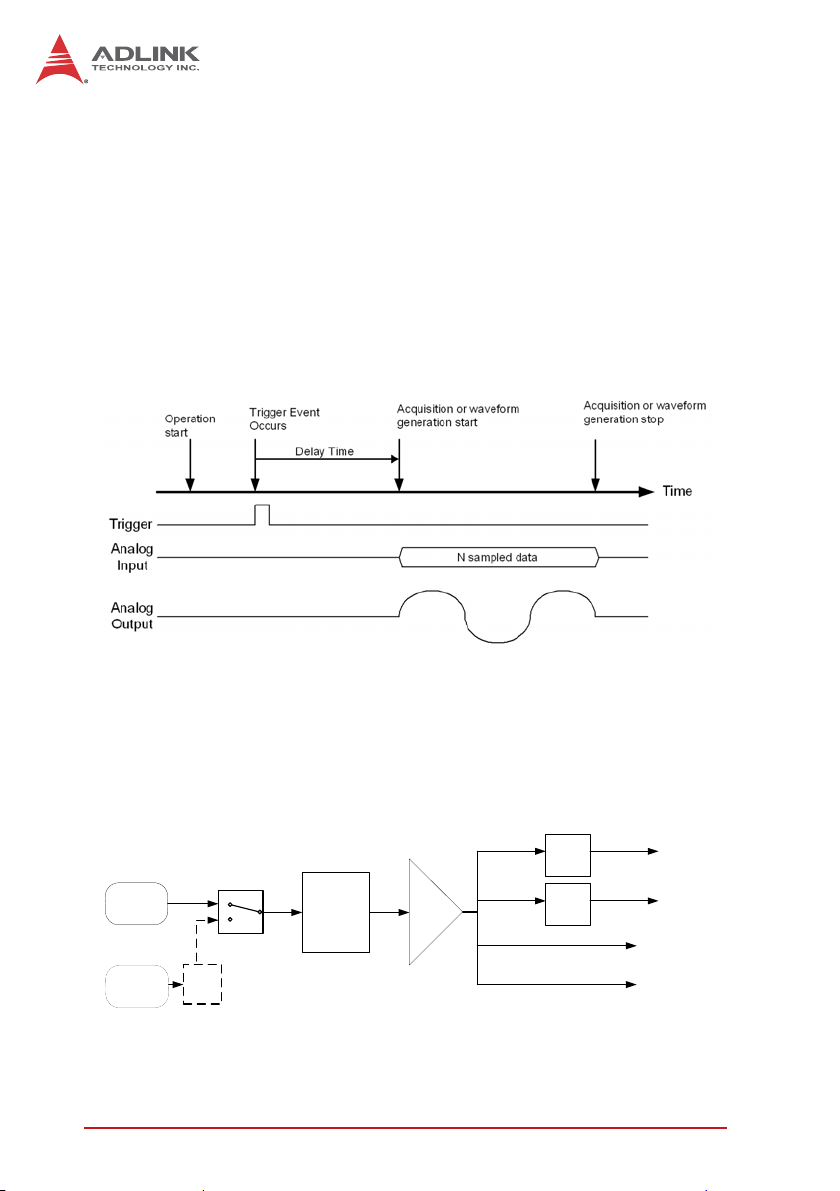

Delay Trigger Mode

If delay trigger mode is configured, delay time from when the

trigger event asserts to the beginning of the acquisition and

waveform generation can be specified, as shown. Delay time is

specified by a 32-bit counter value with the counter clocking

based on the PCI clock. Accordingly, maximum delay time is

the period of PCI_CLK X (232 - 1) and minimum is the period of

PCI_CLK.

Figure 3-8: Delay Trigger Mode Acquisition / Waveform Generation

3.5 ADC and DAC Timing Control

3.5.1 Timebase Architecture

1/2

Divider

Onboard

125MHz

Oscillator

External

PXI

10MHz

PLL

125MHz

DDS

Resolution equal to

125MHz/2^32 =0.029Hz

Buff er

1-to-4 Clock

1/2

Divider

Figure 3-9: PXI-9527 Timebase Architecture

34 Operations

DAC CH0

DAC CH1

ADC CH0

ADC CH1

Page 45

PXI-9527

To drive the sigma-delta ADC and DAC, an onboard timebase

clock is applied. The timebase clock frequency exceeds the sample rate and is produced by a DDS chip. The output frequency of

DDS chip is programmable with excellent resolution. The PXI9527 accepts the external 10MHz clock from the PXI backplane

for better synchronization between modules.

3.5.2 DDS Timing VS ADC/DAC Relationship

Sampling

Rate

Update

Rate

DDS CLK

Table 3-8: Timing Relationship of the ADC, DAC and DDS Clock

2 K - 54 kHz 54 K - 108 kHz

1K-27 kHz 27K-54 kHz 54K-108 kHz 108K-216 kHz

512 K-13.824

MHz

6.912 M-

13.824 MHz

108 K - 216

kHz

6.912 M-

13.824 MHz

216 K - 432 kHz

13.824 M-

27.648 MHz

3.5.3 Timing Constraints

As described in Section 3.5.1, the ADC and DAC share a single

timebase source, that is, the output of the DDS clock. When simultaneous operation of ADC and DAC is implemented, it should be

considered that:

X When sampling rate of the ADC is set to before configuring

DAC, the update rate of the DAC is limited and fixed correspondingly, and when update rate of the DAC is set before

configuring ADC, the sampling rate of DAC is limited and

fixed correspondingly, as shown

X Because the ADC and DAC share the same trigger source,

both AI and AO operations require coordination prior to trigger event, that is, the trigger event cannot occur before AI &

AO configuration is complete

3.5.4 Filter Delay in ADC and DAC

The filter delay indicates the time required for data to propagate

through a converter. Both AI and AO channels experience filter

delay due to the filter circuitry and the architecture of the converter, as shown.

Operations 35

Page 46

ADC Filter Delay

Update Rate (kS/s) Filter Delay (Samples)

2 K - 54 kS/s 12

54 K-108 kS/s 7

108 K-216 kS/s 5

216 K-432 kS/s 5

DAC Filter Delay

Update Rate (kS/s) Filter Delay (Samples)

2 K - 54 kS/s 43.4

54 K-108 kS/s 87.5

108 K-216 kS/s 176.8

Table 3-9: ADC Filter Delay

Table 3-10: DAC Filter Delay

36 Operations

Page 47

4 Calibration

This chapter introduces the calibration process to minimize analog

input measurement errors and analog output errors.

4.1 Calibration Constant

The PXI-9527 is factory calibrated before shipment, with associated calibration constants written to the onboard EEPROM. At

system boot, the PXI-9527 driver loads these calibration constants, such that analog input path and analog output circuit errors

are minimized. ADLINK provides a software API for calibrating the

PXI-9527.

The onboard EEPROM provides three banks for calibration constant storage. Bank 0, the default bank, records the factory calibrated constants, providing written protection preventing

erroneous auto-calibration. Banks 1 and 2, user-defined space,

are provided for storage of self-calibration constants. Upon execution of auto-calibration, the calibration constants are recorded to

bank 1 or 2 based on user assignment.

When PXI-9527 boots, the driver accesses the calibration constants and is automatically set to hardware. In the absence of user

assignment, the driver loads constants stored in bank 0. If constants from bank 1 or 2 are to be loaded, the preferred bank can

be designated as boot bank by software. Following re-assignment

of the bank, the driver will load the desired constants on system

re-boot. This setting is recorded to EEPROM and is retained until

re-configuration.

PXI-9527

Calibration 37

Page 48

4.2 Auto-Calibration

Because errors in measurement and outputs will vary with time

and temperature, re-calibration is recommended when the module

is installed. Auto-calibration can measure and minimize errors

without external signal connections, reference voltages, or measurement devices.

The PXI-9527 has an on-board calibration reference to ensure the

accuracy of auto-calibration. The reference voltage is measured

on the production line and recorded in the on-board EEPROM.

Before initializing auto-calibration, it is recommended to warm up

the PXI-9527 for at least 20 minutes and remove connected

cables.

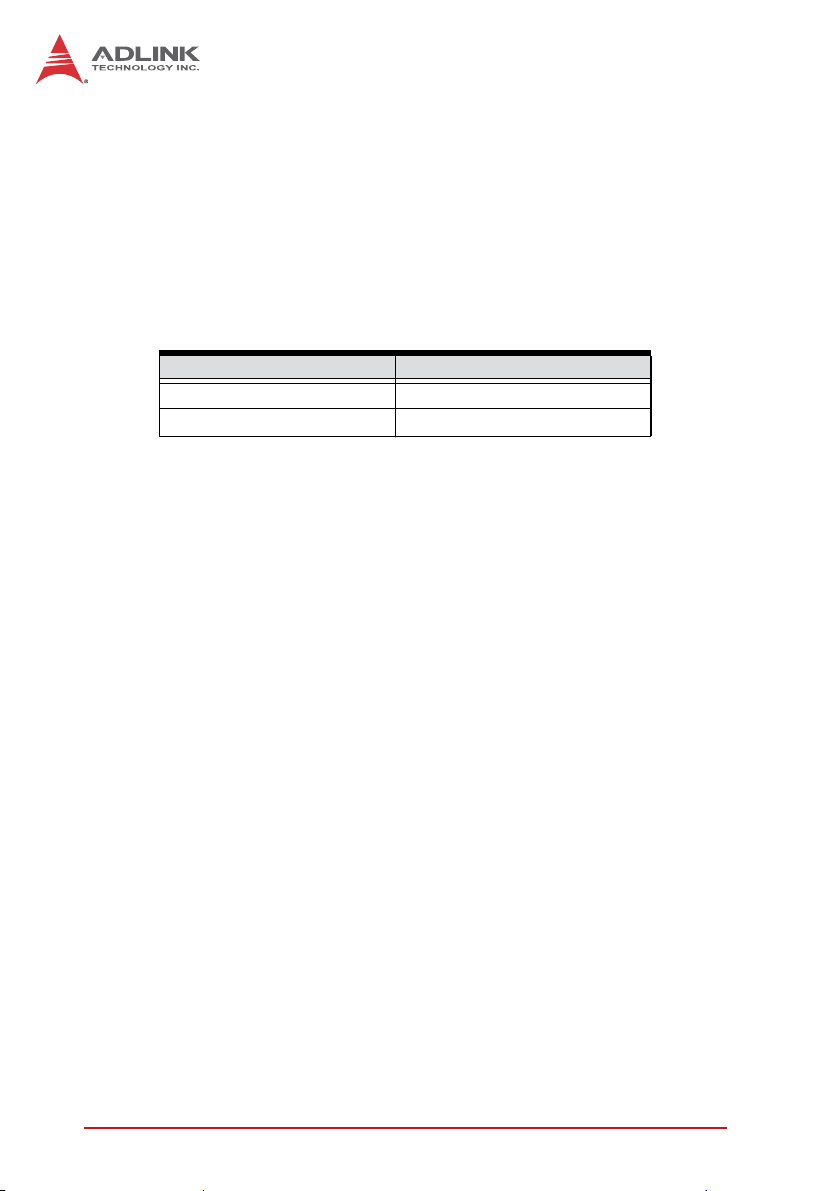

4.3 Offset Error Compensation During AI Sampling Rate Change

For optimal measurement results, the PXI-9527 is equipped with

an internal offset error compensation mechanism to respond to

changes in the AI sampling rate. Compensation times required for

various sampling rates are shown. For example, when sampling

rate is changed from 432 kS/s to 2 kS/s, 6.2 sec is required for offset compensation. When the sampling rate is next set between 2

kS/s and 53.999 kS/s, it is not necessary to have 6.2 sec for the

offset compensation. Only a sampling rate set to different ranges

will generate a compensation time.

It is not necessary to manually factor delay into applications, as the PXI-9527 driver automatically adds the

NOTE:

NOTE:

38 Calibration

compensation time.

Page 49

PXI-9527

Sampling Rate

Offset

Compensation

Time

Table 4-1: Offset Compensation Time Required for Various Sampling Rates

2 kS/s -

53.999 kS/s

6.2 sec 2.6 sec 1.3 sec 0.65 sec

54 kS/s -

107.999 kS/

s

108 K/s -

215.999 kS/

s

216 kS/s -

432 kS/s

Calibration 39

Page 50

This page intentionally left blank.

40 Calibration

Page 51

PXI-9527

Important Safety Instructions

For user safety, please read and follow all instructions,

WARNINGS, CAUTIONS, and NOTES marked in this manual and

on the associated equipment before handling/operating the

equipment.

X Read these safety instructions carefully.

X Keep this user’s manual for future reference.

X Read the specifications section of this manual for detailed

information on the operating environment of this equipment.

X When installing/mounting or uninstalling/removing

equipment:

Z Turn off power and unplug any power cords/cables.

X To avoid electrical shock and/or damage to equipment:

Z Keep equipment away from water or liquid sources;

Z Keep equipment away from high heat or high humidity;

Z Keep equipment properly ventilated (do not block or

cover ventilation openings);

Z Make sure to use recommended voltage and power

source settings;

Z Always install and operate equipment near an easily

accessible electrical socket-outlet;

Z Secure the power cord (do not place any object on/over

the power cord);

Z Only install/attach and operate equipment on stable

surfaces and/or recommended mountings; and,

Z If the equipment will not be used for long periods of time,

turn off and unplug the equipment from its power source.

Important Safety Instructions 41

Page 52

X Never attempt to fix the equipment. Equipment should only

be serviced by qualified personnel.

X A Lithium-type battery may be provided for uninterrupted,

backup or emergency power.

Risk of explosion if battery is replaced with an incorrect type;

please dispose of used batteries appropriately.

X Equipment must be serviced by authorized technicians

when:

Z The power cord or plug is damaged;

Z Liquid has penetrated the equipment;

Z It has been exposed to high humidity/moisture;

Z It is not functioning or does not function according to the

user’s manual;

Z It has been dropped and/or damaged; and/or,

Z It has an obvious sign of breakage.

42 Important Safety Instructions

Page 53

PXI-9527

Getting Service

Contact us should you require any service or assistance.

ADLINK Technology, Inc.

Address: 9F, No.166 Jian Yi Road, Zhonghe District

New Taipei City 235, Taiwan

ᄅקؑխࡉ৬ԫሁ 166 ᇆ 9 ᑔ

Tel: +886-2-8226-5877

Fax: +886-2-8226-5717

Email: service@adlinktech.com

Ampro ADLINK Technology, Inc.

Address: 5215 Hellyer Avenue, #110, San Jose, CA 95138, USA

Tel: +1-408-360-0200

Toll Free: +1-800-966-5200 (USA only)

Fax: +1-408-360-0222

Email: info@adlinktech.com

ADLINK Technology (China) Co., Ltd.

Address: Ϟ⍋Ꮦ⌺ϰᮄᓴ∳催⾥ᡔು㢇䏃 300 ো(201203)

300 Fang Chun Rd., Zhangjiang Hi-Tech Park,

Tel: +86-21-5132-8988

Fax: +86-21-5132-3588

Email: market@adlinktech.com

ADLINK Technology Beijing

Address: ࣫ҀᏖ⍋⎔Ϟഄϰ䏃 1 োⲜ߯ࡼ E ᑻ 801 ᅸ(100085)

Tel: +86-10-5885-8666

Fax: +86-10-5885-8625

Email: market@adlinktech.com

ADLINK Technology Shenzhen

Address: ⏅ഇᏖቅ⾥ᡔು催ᮄϗ䘧᭄ᄫᡔᴃು

Tel: +86-755-2643-4858

Fax: +86-755-2664-6353

Email: market@adlinktech.com

Pudong New Area, Shanghai, 201203 China

Rm. 801, Power Creative E, No. 1, B/D

Shang Di East Rd., Beijing, 100085 China

A1 2 ὐ C (518057)

2F, C Block, Bldg. A1, Cyber-Tech Zone, Gao Xin Ave. Sec. 7,

High-Tech Industrial Park S., Shenzhen, 518054 China

Getting Service 43

Page 54

ADLINK Technology (Europe) GmbH

Address: Nord Carree 3, 40477 Duesseldorf, Germany

Tel: +49-211-495-5552

Fax: +49-211-495-5557

Email: emea@adlinktech.com

ADLINK Technology, Inc. (French Liaison Office)

Address: 15 rue Emile Baudot, 91300 Massy CEDEX, France

Tel: +33 (0) 1 60 12 35 66

Fax: +33 (0) 1 60 12 35 66

Email: france@adlinktech.com

ADLINK Technology Japan Corporation

Address: ͱ101-0045 ᵅҀ䛑ҷ⬄⼲⬄䤯ފ⬎ 3-7-4

⼲⬄ 374 ɛɳ 4F

KANDA374 Bldg. 4F, 3-7-4 Kanda Kajicho,

Chiyoda-ku, Tokyo 101-0045, Japan

Tel: +81-3-4455-3722

Fax: +81-3-5209-6013

Email: japan@adlinktech.com

ADLINK Technology, Inc. (Korean Liaison Office)

Address: 昢殾柢 昢爎割 昢爎壟 1675-12 微汾瘶捒娯 8猻

8F Mointer B/D,1675-12, Seocho-Dong, Seocho-Gu,

Seoul 137-070, Korea

Tel: +82-2-2057-0565

Fax: +82-2-2057-0563

Email: korea@adlinktech.com

ADLINK Technology Singapore Pte. Ltd.

Address: 84 Genting Lane #07-02A, Cityneon Design Centre,

Singapore 349584

Tel: +65-6844-2261

Fax: +65-6844-2263

Email: singapore@adlinktech.com

ADLINK Technology Singapore Pte. Ltd. (Indian Liaison Office)

Address: 1st Floor, #50-56 (Between 16th/17th Cross) Margosa Plaza,

Margosa Main Road, Malleswaram, Bangalore-560055, India

Tel: +91-80-65605817, +91-80-42246107

Fax: +91-80- 23464606

Email: india@adlinktech.com

44 Getting Service

Loading...

Loading...