Page 1

PCIe-7360

100 MHz 32-CH High-Speed Digital I/O Card

User’s Manual

Manual Rev.: 2.00

Revision Date: Aug. 2, 2013

Part No: 50-11042-1000

Advance Technologies; Automate the World.

Page 2

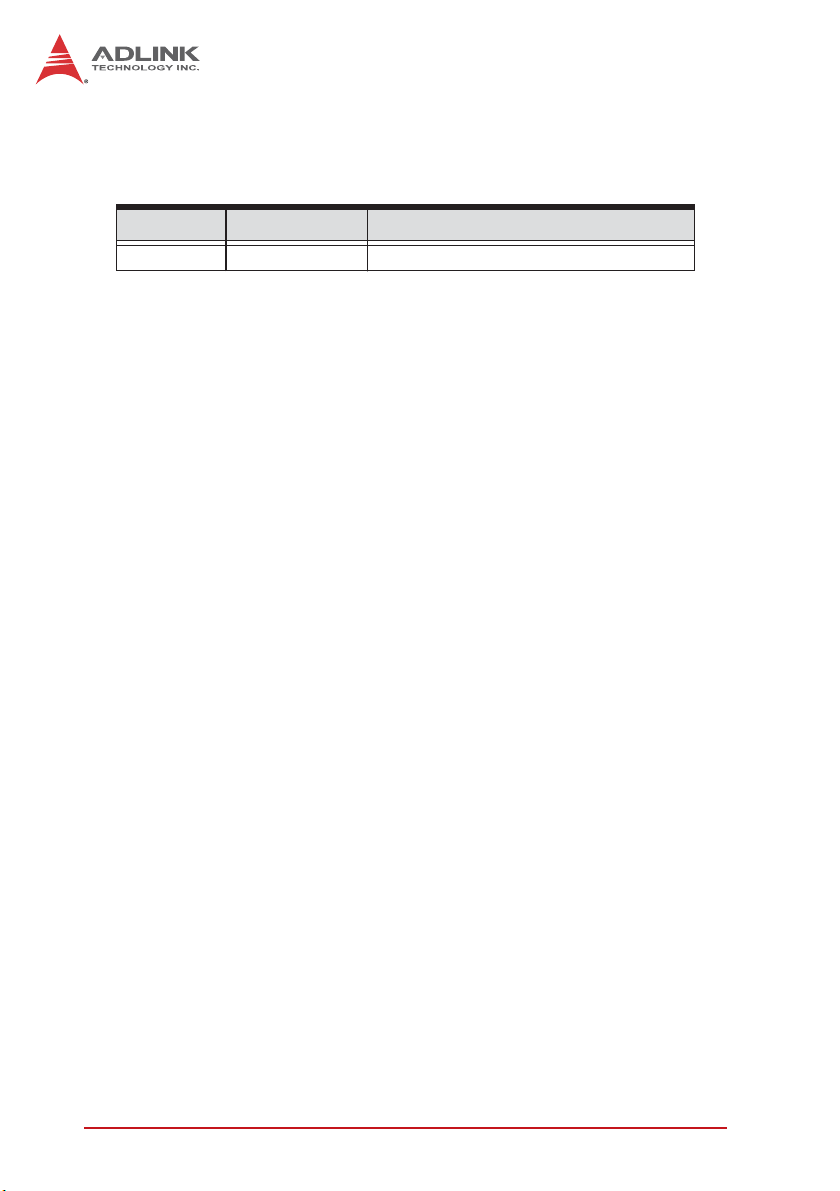

Revision History

Revision Release Date Description of Change(s)

2.00 Aug. 2, 2013 Initial release

ii

Page 3

PCIe-7360

Preface

Copyright ©2013 ADLINK Technology, Inc.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form

without prior written permission of the manufacturer.

Disclaimer

The information in this document is subject to change without prior

notice in order to improve reliability, design, and function and does

not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or

inability to use the product or documentation, even if advised of

the possibility of such damages.

Environmental Responsibility

ADLINK is committed to fulfill its social responsibility to global

environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE)

directive. Environmental protection is a top priority for ADLINK.

We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little

impact on the environment as possible. When products are at their

end of life, our customers are encouraged to dispose of them in

accordance with the product disposal and/or recovery programs

prescribed by their nation or company.

Trademarks

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks

of their respective companies.

Preface iii

Page 4

Conventions

Take note of the following conventions used throughout this

manual to make sure that users perform certain tasks and

instructions properly.

Additional information, aids, and tips that help users perform

tasks.

NOTE:

NOTE:

Information to prevent minor physical injury, component damage, data loss, and/or program corruption when trying to com-

CAUTION:

WARNING:

plete a task.

Information to prevent serious physical injury, component

damage, data loss, and/or program corruption when trying to

complete a specific task.

iv Preface

Page 5

PCIe-7360

Table of Contents

Revision History...................................................................... ii

Preface .................................................................................... iii

List of Figures ....................................................................... vii

List of Tables.......................................................................... ix

1 Introduction ........................................................................ 1

1.1 Features............................................................................... 1

1.2 Applications ......................................................................... 1

1.3 Specifications....................................................................... 2

1.4 Software Support ............................................................ 11

DAQPilot ....................................................................... 11

PCIS-DASK .................................................................. 11

1.5 Schematics, I/O and Indicators.......................................... 12

1.6 Connectors ........................................................................ 12

1.7 LED indicator ..................................................................... 17

2 Getting Started ................................................................. 19

2.1 Unpacking Checklist .......................................................... 19

2.2 Installing the Card.............................................................. 19

2.3 Selecting Cables and Termination Board .......................... 20

3 Operations ........................................................................ 21

3.1 Block Diagram ................................................................... 21

3.2 Programmable Logic Level ................................................ 22

3.3 Digital I/O Configuration..................................................... 23

DI Raw Data Mapping ................................................... 24

3.4 Sample Clock Phase Shift ................................................. 27

3.5 Bus-mastering DMA Data Transfer.................................... 29

Table of Contents v

Page 6

3.6 Sample Clock..................................................................... 31

Digital Input (DI) Sample Clock ..................................... 31

Digital Output (DO) Sample Clock ................................ 33

3.7 Operating Modes ............................................................... 35

Polling Mode (Single Read/Write) ................................. 35

DI DMA in Continuous Mode ........................................ 35

DO DMA in Continuous Mode ......................................38

DI DMA in Handshake Mode ........................................ 41

DO DMA in Handshake Mode ......................................44

DI DMA in Burst Handshake Mode ...............................47

DO DMA in Burst Handshake Mode ............................. 50

DO DMA in Burst Handshake Mode 2 .......................... 53

3.8 Trigger Source and Trigger Mode...................................... 54

3.9 Application Function I/O..................................................... 57

I2C Master .................................................................... 62

SPI Master .................................................................... 64

External Digital Trigger ................................................. 67

Trigger Out .................................................................... 68

Event Out ......................................................................69

Handshake .................................................................... 70

Sample Clock In/Out .....................................................71

3.10 Pattern Match..................................................................... 72

3.11 COS (Change of State) Event............................................ 74

3.12 Termination........................................................................ 75

AppendixA ADLINK DIN-68H .......................................... 77

Important Safety Instructions.............................................. 81

Getting Service ..................................................................... 83

vi Table of Contents

Page 7

PCIe-7360

List of Figures

Figure 1-1: Acquisition Timing Diagram ............................................. 7

Figure 1-2: Generation Timing Diagram............................................. 8

Figure 1-3: PCIe-7360 Schematic Diagram ..................................... 12

Figure 1-4: PCIe-7360 Connectors .................................................. 13

Figure 3-1: PCIe-7360 Block Diagram ............................................. 22

Figure 3-2: DI Raw Data Mapping for 8-Bit Data Width ................... 25

Figure 3-3: DI raw data Mapping for 16-Bit Data Width ................... 26

Figure 3-4: DI raw data Mapping for 24-Bit Data Width ................... 27

Figure 3-5: DI raw data Mapping for 32-Bit Data Width ................... 27

Figure 3-6: Phase Shift of Sample Clock ......................................... 28

Figure 3-7: Maximum Data Throughput ........................................... 29

Figure 3-8: Scatter-Gather DMA for Data Transfer .......................... 31

Figure 3-9: DI/DO Sample Clock Architecture ................................. 34

Figure 3-10: DI Continuous Mode Architecture.................................. 37

Figure 3-11: DI Timing Diagram......................................................... 38

Figure 3-12: DO Continuous Mode Architecture ................................ 40

Figure 3-13: DO Timing Diagram ....................................................... 41

Figure 3-14: DI Handshake Mode Architecture.................................. 43

Figure 3-15: DI Handshake Timing Diagram...................................... 44

Figure 3-16: DO Handshake Mode Architecture ................................ 46

Figure 3-17: DO Handshake Timing Diagram.................................... 47

Figure 3-18: DI Burst Handshake Mode Architecture ........................49

Figure 3-19: DI Burst Handshake Timing Diagram ............................ 50

Figure 3-20: DO Burst Handshake Mode Architecture....................... 52

Figure 3-21: DO Burst Handshake Timing Diagram ..........................53

Figure 3-22: DO Burst Handshake 2 Timing Diagram .......................53

Figure 3-23: DI Post Trigger............................................................... 54

Figure 3-24: DO Post Trigger............................................................. 55

Figure 3-25: DI Post Trigger with Re-trigger ...................................... 55

Figure 3-26: DO Post Trigger with Re-Trigger ................................... 56

Figure 3-27: DI Gated Trigger ............................................................ 56

Figure 3-28: DO Gated Trigger .......................................................... 57

Figure 3-29: I2C Master of PCIe-7360 ............................................... 62

Figure 3-30: Data Transfer on the I2C Bus ........................................ 63

Figure 3-31: I2C Data Format ............................................................ 64

Figure 3-32: SPI Master of PCIe-7360............................................... 65

Figure 3-33: Data Transfer on SPI Bus.............................................. 66

Figure 3-34: Clock Mode of SCK .......................................................66

List of Figures vii

Page 8

Figure 3-35: External Digital Trigger Input Configuration...................67

Figure 3-36: Configured AFI as Internal Software Trigger Output .....68

Figure 3-37: Pattern Match and COS Event Configuration ................ 69

Figure 3-38: Configured AFI as Handshake Interface........................ 70

Figure 3-39: Configured AFI7 as DI Sampled Clock In/Out ............... 71

Figure 3-40: Configured AFI6 as DO Sampled Clock In/Out .............72

Figure 3-41: Example of Pattern Matching......................................... 74

Figure 3-42: Example of Pattern Match .............................................75

Figure A-1: DIN-68H Layout ............................................................ 77

Figure A-2: Resistor Termination Schematic....................................78

Figure A-3: DIN-68H Layout (Back Side) .........................................79

viii List of Figures

Page 9

PCIe-7360

List of Tables

Table 1-1: PCIe-7360 SCSI-VHDCI 68-pin Assignment ................. 15

Table 1-2: Signal Descriptions for SCSI-VHDCI

and SMB Connectors..................................................... 16

Table 1-3: SMB Jack Connector Signal Description ....................... 17

Table 1-4: LED indicator ................................................................. 17

Table 3-1: Logic Levels................................................................... 23

Table 3-2: DI/DO Sample Clock Configuration ............................... 35

Table A-1: DIN-68H Pin Assignment ............................................... 77

Table A-2: Pad Position of User-Defined Resistor Termination ......79

List of Tables ix

Page 10

This page intentionally left blank.

x List of Tables

Page 11

1 Introduction

ADLINK’s PCIe-7360 is a high-speed digital I/O board with

32-channel bi-directional parallel I/O lines. Data rate up to 400

MB/s is available through the x4 PCI Express® interfaces, with

clock rate up to 100 MHz internal clock or 200 MHz external clock,

ideally suited for high-speed and large scale digital data acquisition or exchange applications, such as digital image capture, video

playback, and IC testing.

1.1 Features

X x4 lane PCI Express

X 8/16/24/32-CH @ up to 100MHz for DI or DO and 8/16-CH

@ up to 200MHz for DI in external clock mode

X 400 MB/s maximum throughput

X Software selectable 1.8 V, 2.5 V, or 3.3 V (5 V compatible)

voltage levels

X 80-step phase shift in external clock mode

X Per group (8-bit) input/output direction selectable

X Supports I2C and SPI programmable serial interfaces for

external device communication

X Scatter-gather DMA support

X Flexible handshake and external digital trigger modes

X 8-channel auxiliary programmable I/O support

®

interface

PCIe-7360

1.2 Applications

X High-speed digital data exchange

X Digital pattern generation and acquisition

X IC testing

X Interface to external high-speed A/D and D/A converter

X ATE

Introduction 1

Page 12

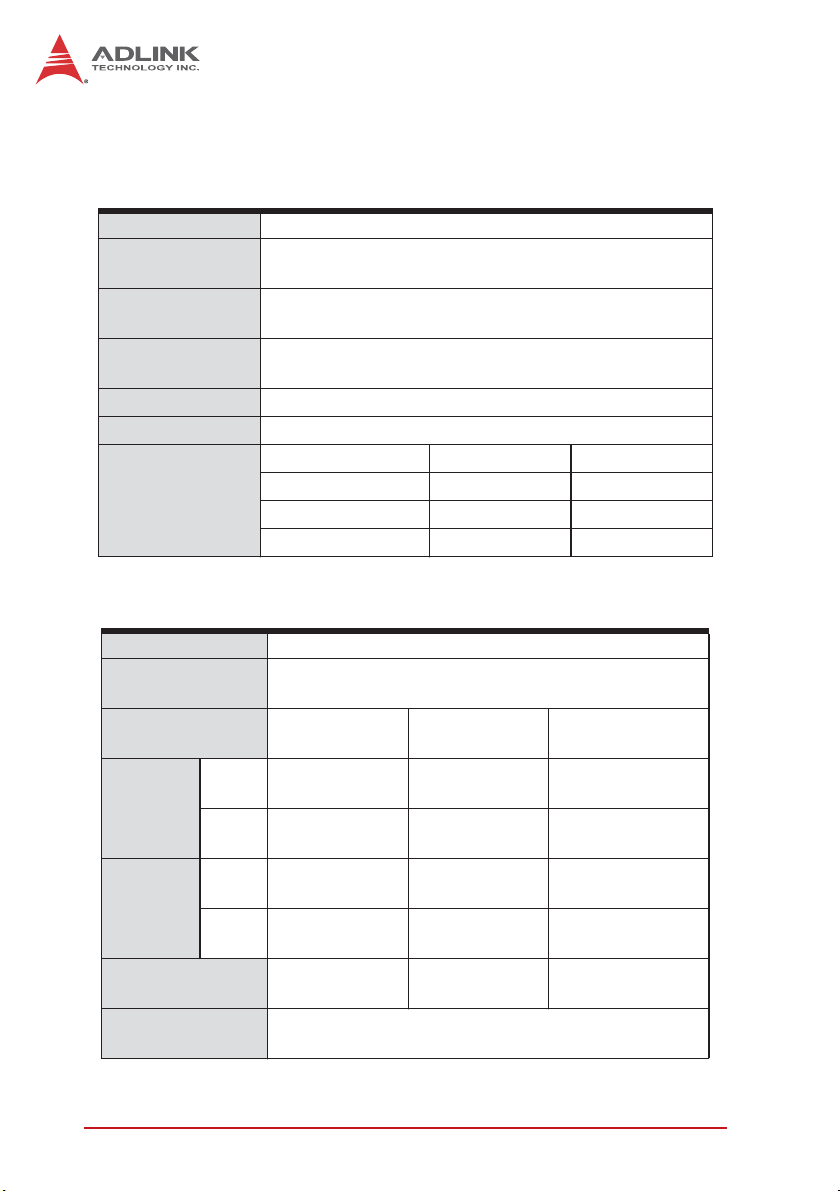

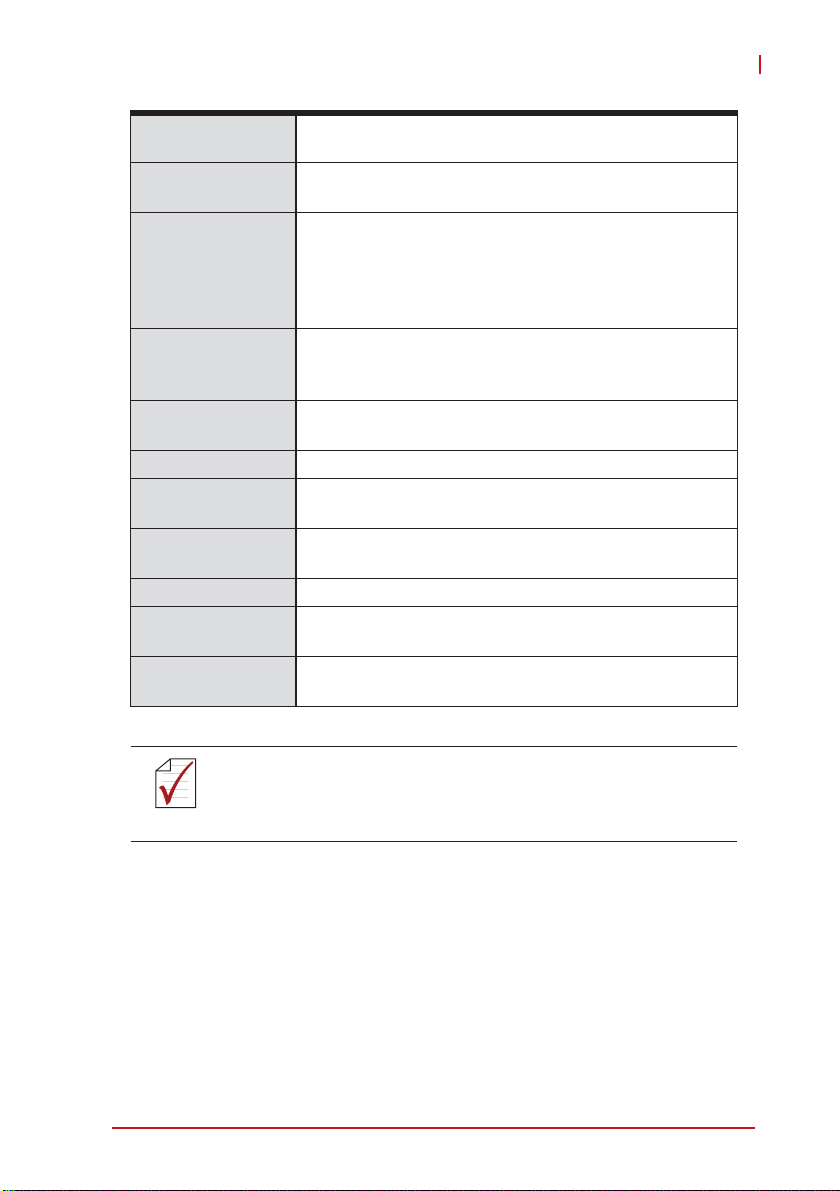

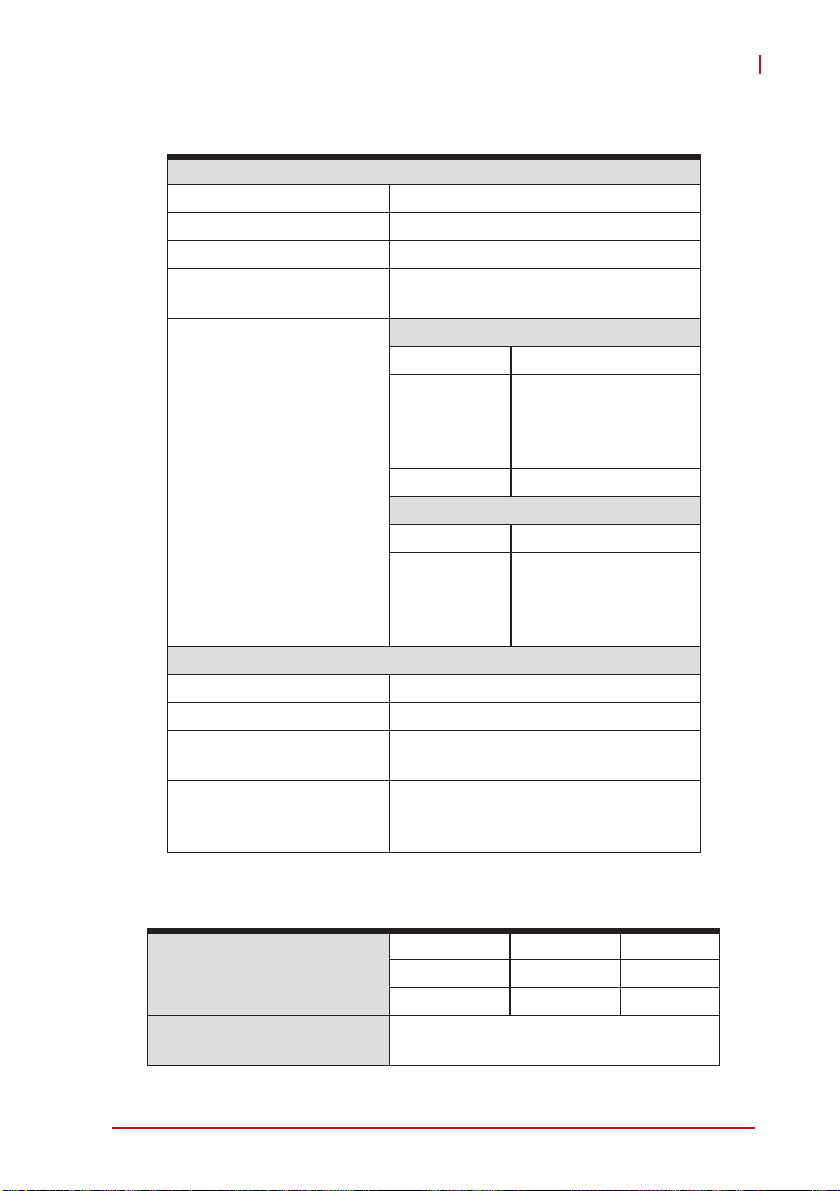

1.3 Specifications

1.3.1 General

Interface x4 PCI Express interface

Connectors

Operating

Temperature

Storage

Temperature

Humidity 5 - 95%, non-condensing

Dimensions 168 mm (L) x 112 mm (H), not including connectors

Power

Consumption

1.3.2 Digital I/O

Channels 32

Direction

(programmable)

Logic level

(programmable)

Min.

Input

voltage

Output

voltage

Driving capacity

(min.)

Max. throughput

V

Max.

V

Min.

V

Max.

V

SMB Jack Connector x2 (CLK IN & OUT)

68-pin SCSI-VHDCI x1 (32-bit Data Lines & 8-CH AFI)

0°C - 55°C

-20°C - 70°C

Typical Maximum

+3.3 VDC 860 mA 950 mA

+12V VDC 270 mA 550 mA

Total Power 6.1 W 9.8 W

Input or output, per group (8 channel) basis

1.8 V 2.5 V

1.2 V 1.6 V 2 V

IH

0.63 V 0.7 V 0.8 V

IL

1.6 V 2.3 V 3.1 V

OH

0.2 V 0.2 V 0.2 V

OL

3.3 V

(5 V compatible)

±8 mA ±16 mA ±32 mA

Digital input: 400M Byte/s

Digital output: 400M Byte/s

2 Introduction

Page 13

PCIe-7360

Buffer size

Data transfer

Digital input: 8k samples

Digital output: 20k samples

Software polling

Bus-mastering DMA with scatter-gather

Internal clock: up to 100 MHz

External clock: 200 MHz for DI, 100MHz for DO (see

Clock modes

Note)

Handshake

Burst handshake

Software

Trigger source

External digital signal

Pattern match

Trigger modes

Post trigger with re-trigger

Gate trigger

Input impedance 10 k

Input protection

range

Input protection

range

-1 to 6 V

-1 to 6 V

Output impedance 50

Power-up initial

state

Output protection

range

Tri-state/All digital inputs

-0.5 V to 3.8 V

External clock rate, which can be up to 200 MHz, only supports

8 or 16-bit data width

NOTE:

NOTE:

Introduction 3

Page 14

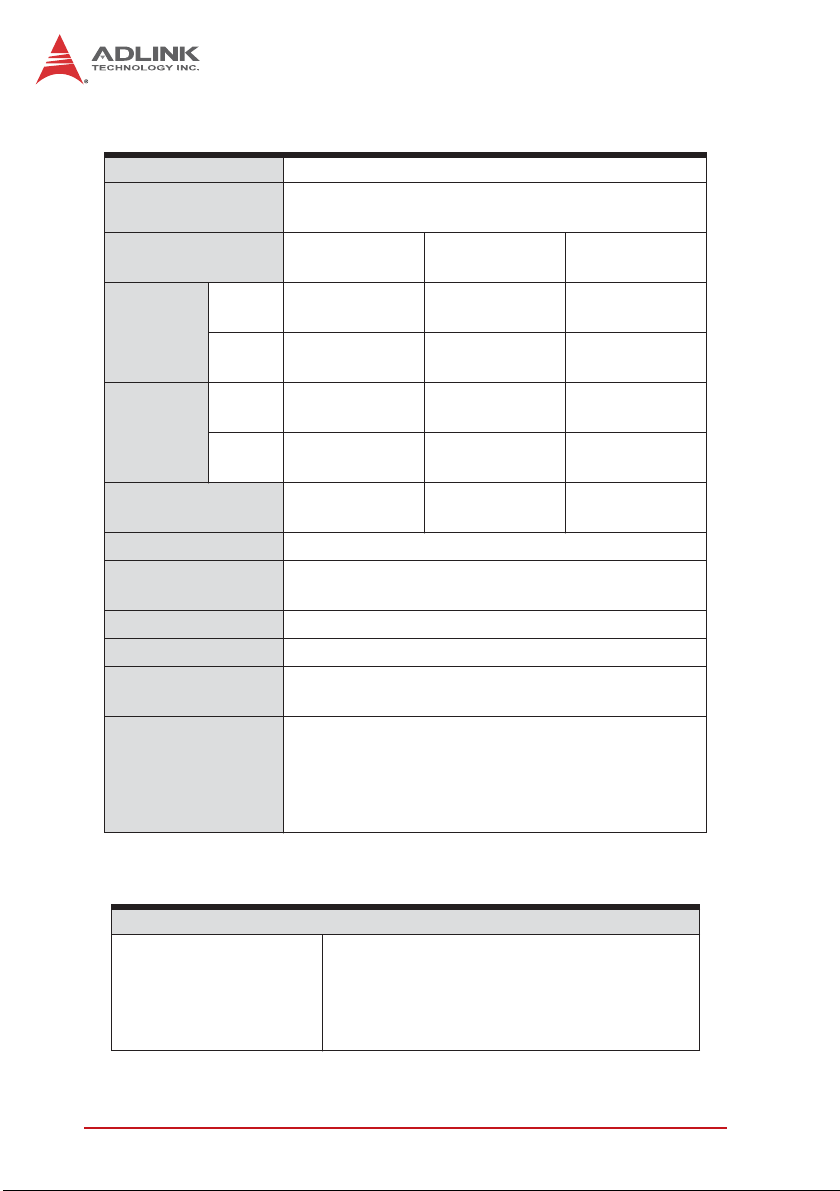

1.3.3 Application Function I/O (AFI)

Channels 8

Direction

(programmable)

Logic levels

(programmable)

Min.

Input

voltage

V

IH

Max.

V

IL

Min.

Output

voltage

V

OH

Max.

V

OL

Driving capacity

(max.)

Input impedance 10 k

Input protection

range

Output impedance 50

Power-up initial state Tri-state/All digital inputs

Output protection

range

Supported Modes

(programmable)

Input or output, per channel basis

1.8 V 2.5 V

1.2 V 1.6 V 2 V

0.63 V 0.7 V 0.8 V

1.6 V 2.3 V 3.1 V

0.2 V 0.2 V 0.2 V

±8 mA ±16 mA ±32 mA

-1 to 6 V

-0.5V to 3.8V

2

I

C master

SPI master

Handshake

External trigger in/out

DI/DO sample clock in/out

3.3 V (5 V

compatible)

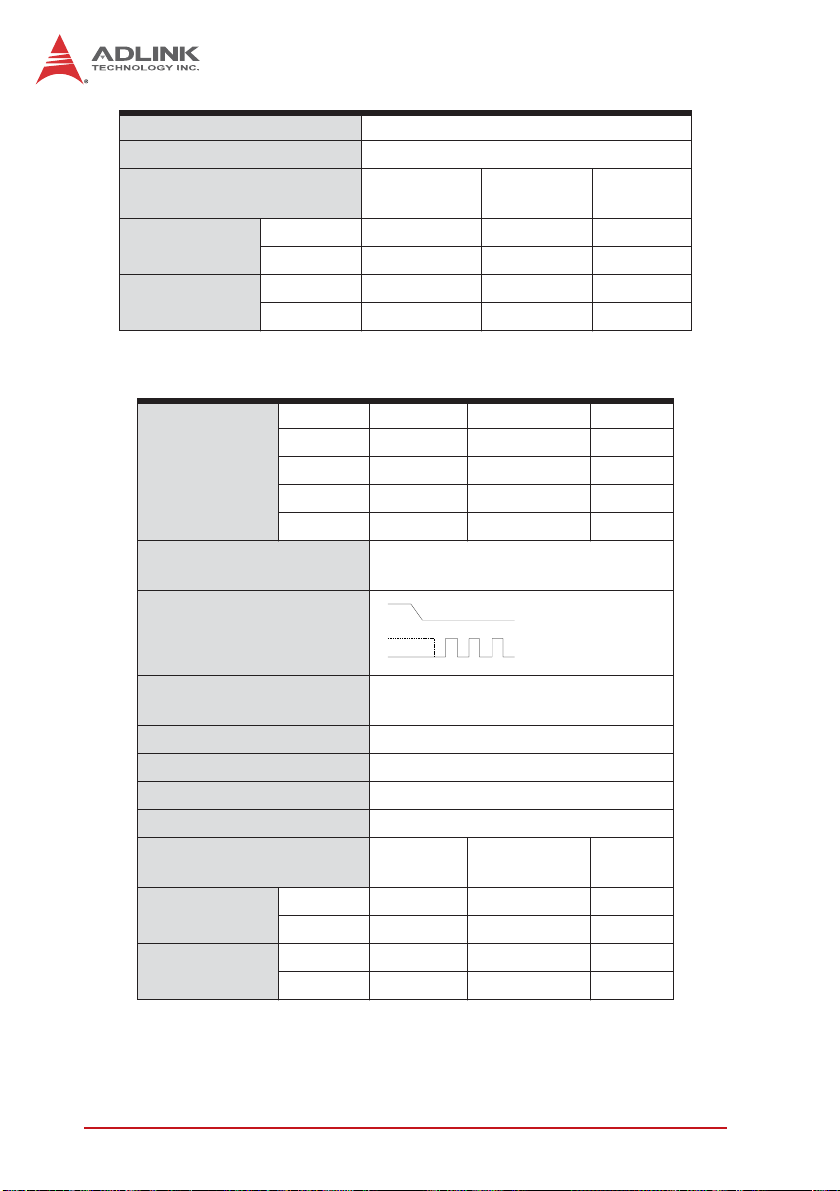

1.3.4 Timing Specifications

Sample Clock

Internal clock: onboard 100MHz with 16-bit

divider

Clock sources

4 Introduction

External clock: AFI6 (for DO)

AFI7 (for DI)

SMB CLK in

Page 15

PCIe-7360

Internal clock rate

(programmable)

1526 Hz – 100 MHz (100 MHz/ N;

1N65,535)

Phase shift disabled: 0-200 MHz

Ext. frequency range

Phase shift enabled: 20MHz - 100MHz (see

Note)

Phase shift

Internal clock: N/A

External clock: 80 steps; 1 step = 4.5°

Sample Clock Exporting

AFI6 (for DO)

Destination

AFI7 (for DI)

SMB CLK out

Phase shift disabled: 0-100 MHz

Frequency range

Phase shift enabled: 20MHz - 100MHz (see

Note)

Clock jitter Period jitter: 300 ps

Clock duty cycle 50%

Phase shift resolution

1/80 of external sampled clock period (80

steps; 1 step = 4.5°)

When phase shift is enabled, the clock must be continuous and

free-running

NOTE:

NOTE:

Introduction 5

Page 16

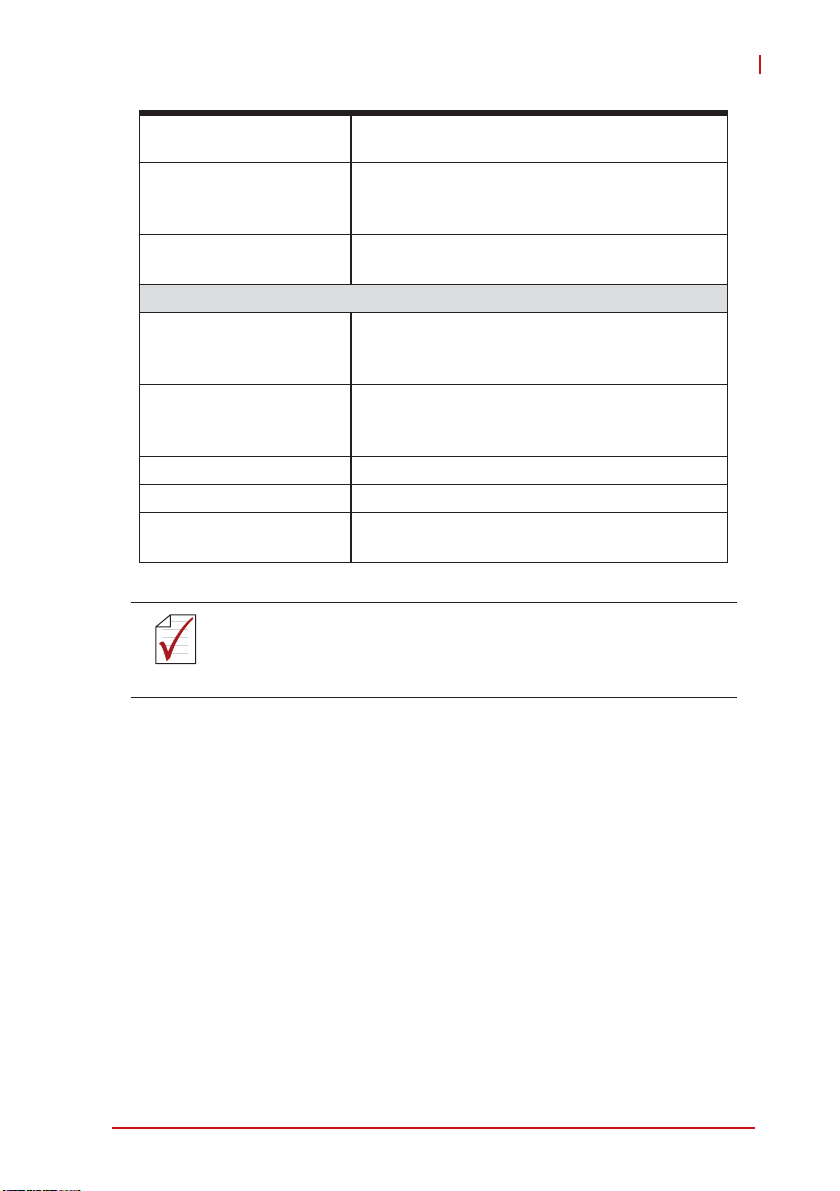

1.3.5 Timing Accuracy

Acquisition Timing

Channel-to-Cannel skew ±1.08 ns

Setup time to sampled clock (t

Hold time to sampled clock (t

Time delay of external sampled clock from AFI7 to

internal (t

AF7D

)

Time delay of external sampled clock from SMB CLK

in to internal (t

SMBID

)

Time delay of DI data from VHDCI connector to

internal (t

DID

)

Generation Timing

Exported clock skew AFI6 -to- SMB CLK out

ECskew

)

(t

Exported clock (AFI6) -to- DO data delay (t

) 2 ns

SU

) 2 ns

H

) 600 ps - 5 ns

AF62D

6.3 ns

9.1 ns

3.26 ns - 4.34 ns

2 ns

6 Introduction

Page 17

DI Sampled Clock

(AFI7)

PCIe-7360

DI Data

(connector)

DI Sampled Clock

(into FPGA)

DI Data

(into FPGA)

t

= Time delay of external sampled clock from AFI7 to internal

AF7D

t

= Time delay of DI data from VHDCI connector to internal

DID

Figure 1-1: Acquisition Timing Diagram

D0 D1 D2 D3

tSUt

H

Trace & component delay

t

AF7D

D0 D1 D2 D3

t

DID

Introduction 7

Page 18

DO Sampled Clock

(internal)

Exported DO Sampled Clock

(SMB CLK out/ non-inverted)

Generation Start

Trace & component delay

Exported DO Sampled Clock

(AFI6/ non-inverted)

Exported DO Sampled Clock

(AFI6/ inverted)

Exported DO Sampled Clock

(AFI6/ phase delay)

DO Data

t

= Time delay from sampled clock (internal) to exported sampled clock (AFI6)

SC2AF6

t

= Time delay from exported clock (AFI6) to exported clock (SMB CLK out)

ECskew

= Time delay from exported sampled clock (AFI6) to do data

t

AF62D

Figure 1-2: Generation Timing Diagram

t

SC2AF6

Phase delay (0° ~ 360°)

t

AF62D

D0

D1 D2

Write data to

external device

t

ECskew

8 Introduction

Page 19

1.3.6 External Clock I/O Specification

CLK IN (SMB Jack Connector)

Destination DI or DO sample clock

Input coupling AC

Input Impedance 50

Minimum detectable pulse

width

External sampled clock

range

CLK OUT (SMB Jack Connector)

Sources DI or DO internal sample clock

Source impedance 50

Logic Levels

(programmable)

Driving Capacity (Max.)

8 ns

Square Wave

Voltage 0.2 Vpp to 5 Vpp

Phase shift disabled:

Frequency

Duty cycle 40% - 60%

Sine Wave

Voltage 0.2 Vpp to 5 Vpp

Frequency

The same logic level of AFI I/O (1.8 V,

2.5 V, or 3.3 V)

±8 mA at 1.8 V

±16 mA at 2.5 V

±32 mA at 3.3 V

0-200 MHz

Phase shift enabled:

20MHz - 100MHz

Phase shift disabled:

0-200 MHz

Phase shift enabled:

20MHz - 100MHz

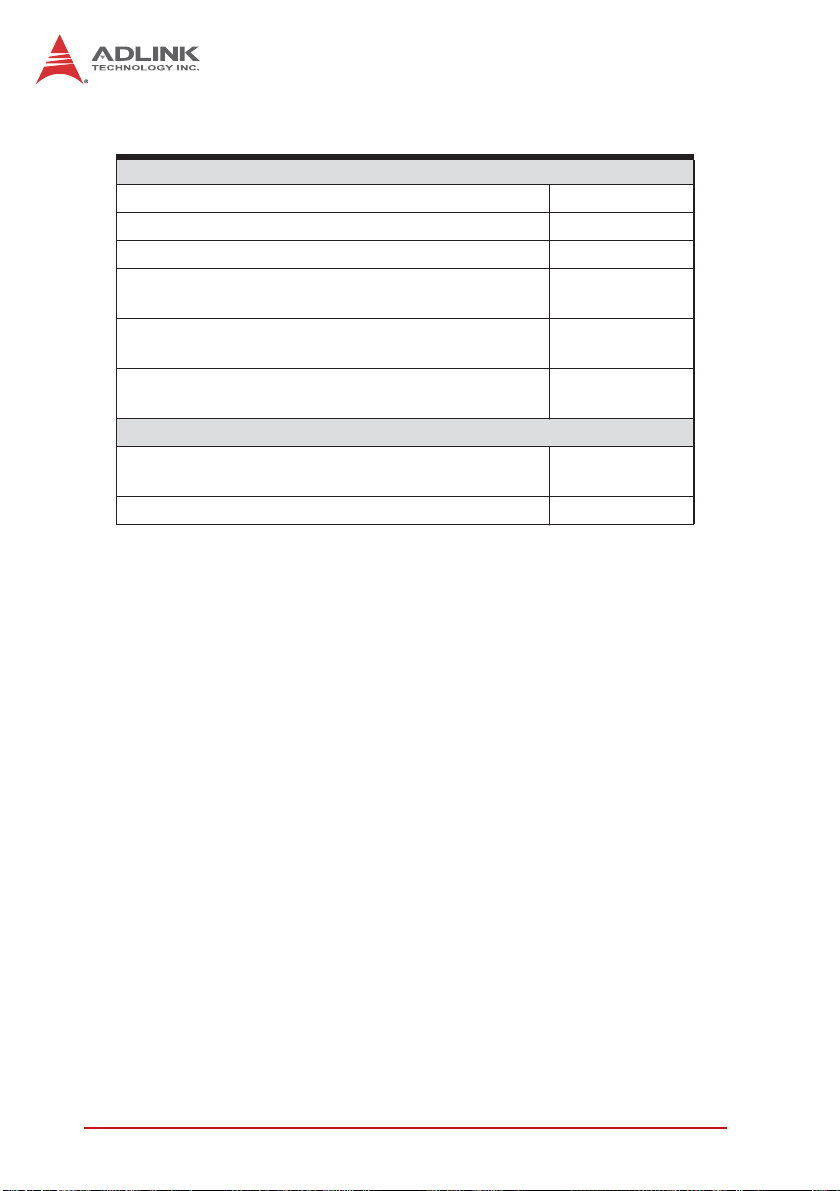

PCIe-7360

2

1.3.7 I

Signal

Supported clock rate

(programmable)

Introduction 9

C Master Specification

Direction Pin

SCL O AFI0

SDA I/O AFI1

1.9 kHz -244.14 kHz;

488.28125 kHz / (n + 1); 1 n 255

Page 20

Transfer size of Data 0 - 4 Bytes

Transfer size of Cmd/ Addr 0 - 4 Bytes

Logic families

(programmable)

Input Voltage

Output Voltage

Min. V

Max. V

Min. V

Max. V

1.8 V 2.5 V 3.3 V

1.2 V 1.6 V 2.0 V

IH

0.63 V 0.7 V 0.8 V

IL

1.6 V 2.3 V 3.1 V

OH

0.2 V 0.2 V 0.2 V

OL

1.3.8 SPI Master Specification

SCK O AFI0

Signal

Supported clock rate

(programmable)

SDO O AFI1

SDI I AFI2

CS_0 O AFI3

244.14 kHz -62.5 MHz,

62.5 MHz / (n + 1); 0 n 255

Direction Pin

Clock mode

The first bit be transferred

Mode =1

Mode =0

MSB/ LSB

(Default: MSB)

Transfer size of Data 0 - 32 bits

Transfer size of Cmd/ Addr 0 - 32 bits

Dummy size 0 - 15 bits

SPI Slave selection CS_0

Logic families

(programmable)

Input Voltage

Output Voltage

Min. V

Max. V

Min. V

Max. V

1.8 V 2.5 V 3.3 V

1.2 V 1.6 V 2 V

IH

0.63 V 0.7 V 0.8 V

IL

1.6 V 2.3 V 3.1 V

OH

0.2 V 0.2 V 0.2 V

OL

10 Introduction

Page 21

PCIe-7360

1.4 Software Support

ADLINK provides versatile software drivers and packages for

users’ different approach to building up a system. ADLINK not only

provides programming libraries such as DLL for most Windows

based systems, but also provide drivers for other software packages such as LabVIEW®.

All software options are included in the ADLINK CD. Non-free software drivers are protected with licensing codes. Without the software code, you can install and run the demo version for two hours

for trial/demonstration purposes. Please contact ADLINK dealers

to purchase the formal license.

DAQPilot

DAQPilot is ADLINK’s proprietary task-oriented software development kit (SDK), supporting ActiveX Controls/.NET Assembly,

Express VI and Polymorphic VI for LabVIEW and DAQ Toolbox for

MATLAB.

You can download and install DAQPilot at:

http://www.adlinktech.com/TM/DAQPilot.html

Please note that only DAQPilot versions 2.6.1.0705 and later support the PCIe-7360.

PCIS-DASK

PCIS-DASK comprises advanced 32/64-bit kernel drivers for customized DAQ application development, enabling detailed operations and superior performance and reliability from the data

acquisition system. DASK kernel drivers now support Windows

8/7/XP OS.

Please note that only PCIS-DASK versions 5.10 and later support

the PCIe-7360 module.

Introduction 11

Page 22

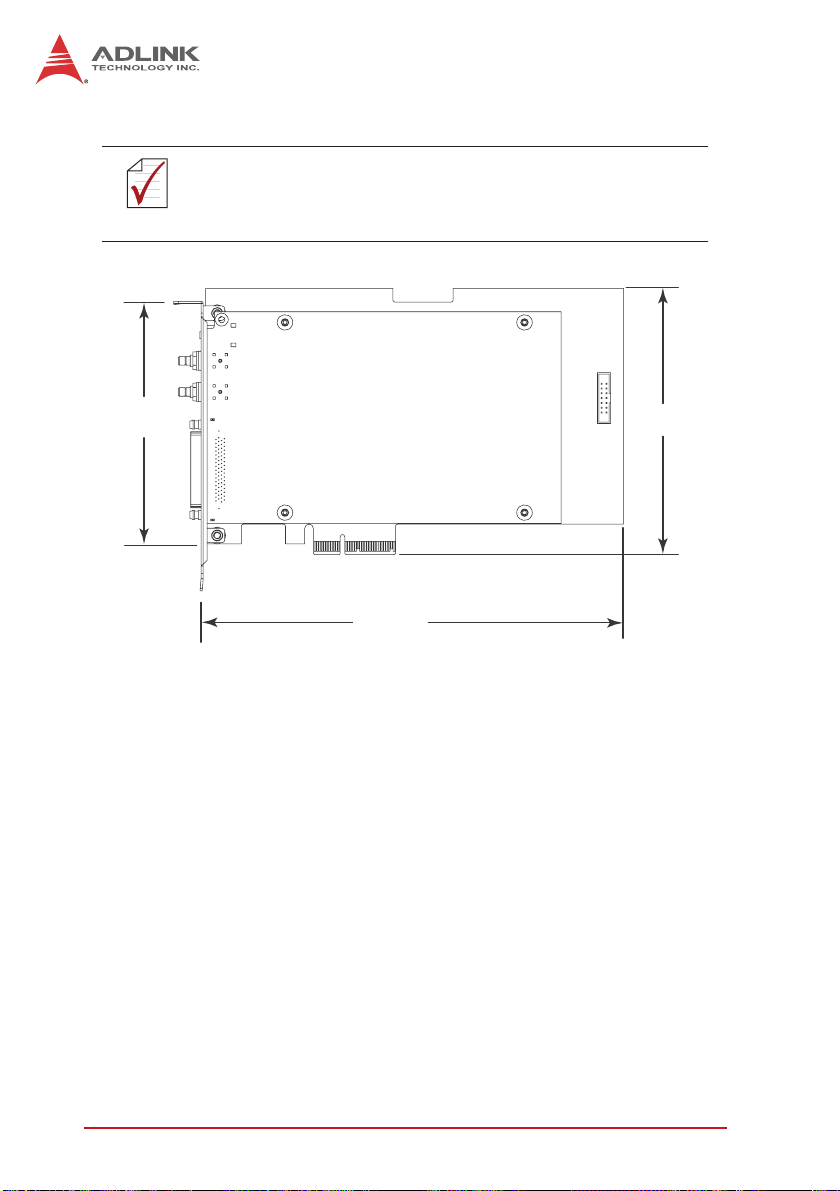

1.5 Schematics, I/O and Indicators

All dimensions shown are in mm

NOTE:

NOTE:

.

100.36

176.42

Figure 1-3: PCIe-7360 Schematic Diagram

111.15

1.6 Connectors

The PCIe-7360 card is equipped with one 68-pin SCSI-VHDCI

connector for high-speed digital I/O and programmable function

12 Introduction

Page 23

PCIe-7360

I/O, and two SMB connectors for sample clock input and output,

as labeled on the faceplate.

Figure 1-4: PCIe-7360 Connectors

Introduction 13

Page 24

ID Pin Pin ID

GND 68 34 GND

(DI CLK) AFI7 67 33 AFI6 (DO CLK)

GND 66 32 GND

D0 65 31 D1

AFI5 64 30 AFI4

D2 63 29 D3

GND 62 28 GND

D4 61 27 D5

AFI3 60 26 AFI2

D6 59 25 D7

GND 58 24 GND

D8 57 23 D9

GND 56 22 GND

D10 55 21 D11

GND 54 20 GND

D12 53 19 D13

AFI1 52 18 GND

D14 51 17 D15

GND 50 16 GND

D16 49 15 D17

GND 48 14 GND

D18 47 13 D19

GND 46 12 GND

D20 45 11 D21

GND 44 10 GND

D22 43 9 D23

GND 42 8 AFI0

D24 41 7 D25

GND 40 6 GND

D26 39 5 D27

GND 38 4 GND

14 Introduction

Page 25

ID Pin Pin ID

D28 37 3 D29

GND 36 2 GND

D30 35 1 D31

Table 1-1: PCIe-7360 SCSI-VHDCI 68-pin Assignment

PCIe-7360

Pin Signal

25, 27,

29, 31,

59, 61,

D0 – D7 Data I/O

63, 65

17, 19,

21, 23,

51, 53,

D8 – D15 Data I/O

55, 57

9, 11, 13,

15, 43,

45, 47,

D16 – D23 Data I/O

49

1, 3, 5,

7, 35, 37,

D24 – D31 Data I/O

39, 41

8, 26, 30,

52, 60, 64AFI0 – AFI5

Signal

Type

Control

/Data

Direction Description

Port_A bi-directional digital

data lines

Port_B bi-directional digital

data lines

Port_C bi-directional digital

data lines

Port_D bi-directional digital

data lines

Application Function I/O,

can be configured as:

2

X I

C/ SPI

I/O

X Handshake sig-

nal

X External trigger

in/out

X Event out

Introduction 15

Page 26

Pin Signal

Signal

Type

Direction Description

Application Function I/O,

can be configured as:

X Handshake sig-

nal

33 AFI6

Control

/Data

I/O

X External trigger

in/out

X Event out

X DO sampled

clock in/out

Application Function I/O,

can be configured as:

X Handshake sig-

nal

67 AFI7

Control

/Data

I/O

X External trigger

in/out

X Event out

X DI sampled clock

in/out

2, 4,6,

10, 12,

14, 16,

18,20,

22, 24,

28, 32,

34, 36,

38, 40,

GND Ground N/A

Ground reference for Data

I/O and AFI I/O

42, 44,

46, 48,

50, 54,

56, 58,

62, 66,

68

Table 1-2: Signal Descriptions for SCSI-VHDCI and SMB Connectors

16 Introduction

Page 27

PCIe-7360

Signal

CLK IN Clock I

CLK OUT Clock O

Signal

Type

Table 1-3: SMB Jack Connector Signal Description

Direction Description

External clock input for DI/DO sampled

clock from external device to the

PCIe-7360

DI/DO sampled clock exporting from the

PCIe-7360 to an external device

1.7 LED indicator

The LED on the faceplate indicates I2C & SPI communication and

digital I/O status of the PCIe-7360.

LED Color Mode

ACC

(Access)

Red DI DMA operation

Green DO DMA operation

Amber DI & DO DMA operation

Table 1-4: LED indicator

Introduction 17

Page 28

This page intentionally left blank.

18 Introduction

Page 29

2 Getting Started

2.1 Unpacking Checklist

Before unpacking, check the shipping carton for any damage. If

the shipping carton and/or contents are damaged, inform your

dealer immediately. Retain the shipping carton and packing materials for inspection. Obtain authorization from your dealer before

returning any product to ADLINK. Check if the following items are

included in the package.

X PCIe-7360 high-speed DIO card

X ADLINK All-in-One CD

X Quick Start Guide

If any of the items is damaged or missing, contact your dealer

immediately.

The card must be protected from static discharge and physical

shock. Never remove any of the socketed parts except at a

CAUTION:

static-free workstation. Use the anti-static bag shipped with the

product to handle the card. Wear a grounded wrist strap when

servicing.

PCIe-7360

2.2 Installing the Card

Install the card driver before you install the card into your computer system. See “Software Support” on page 11. for driver support information.

To install the card:

1. Turn off the system/chassis and disconnect the power

plug from the power source.

2. Remove the system/chassis cover.

3. Select the PCI Express slot that you intend to use, then

remove the bracket opposite the slot, if any.

4. Align the card connectors (golden fingers) with the slot,

then press the card firmly until the card is completely

seated on the slot.

Getting Started 19

Page 30

5. Secure the card to the chassis with a screw.

6. Replace the system/chassis cover.

7. Connect the power plug to a power source, then turn on

the system.

Configuration

All PCI/PCI Express cards on your system are configured individually. Because configuration is controlled by the system and the

software, no jumper setting is required for base address, DMA,

and interrupt IRQ. Configuration is subject to change with every

boot of the system as new PCI/PCI Express® cards are added or

removed.

Troubleshooting

If your system fails to boot or if you experience erratic operation

with your PCI/PCI Express card in place, an interrupt conflict may

have been generated (such as when the BIOS Setup is incorrectly

configured). Refer to the system’s BIOS documentation for details.

2.3 Selecting Cables and Termination Board

Since the PCIe-7360 is a high-speed digital I/O card, impedance

matching is important in eliminating signal reflection generated by

cabling or PCB trace. The following recommended cables and termination board can improve signal quality during high-speed signal transfer.

DIN-68H – Termination board with one 68-pin SCSI-VHDCI connector and user selectable impedance. See “ADLINK DIN-68H” on

page 77. for more information.

ACL-10279 – 68-pin SCSI-VHDCI cable with 50 impedance

SMB-SMB-1M – SMB to SMB cable, 1 M, for sample clock in/out

SMB-BNC-1M – SMB to BNC cable, 1 M, for sample clock in/out

20 Getting Started

Page 31

3 Operations

The PCIe-7360 provides functions including high-speed digital

pattern acquisition, digital pattern generation, application function

I/O, and others.

3.1 Block Diagram

The PCIe-7360 provides 32-channel bi-directional high-speed digital I/O lines, 8-channel AFI (Application Function I/O) lines, and

two sample clock input/output channels. All 32-channel

high-speed digital I/O lines are connected to the level shifter and

can be programmed as 1.8 V, 2.5 V, or 3.3 V (5 V compatible)

logic levels. These channels can also be programmed as input

channels for digital pattern acquisition or output channels for digital pattern generation.

8-channel application function I/O lines are also connected to the

level shifter. These application function I/Os can be programmed

as I2C or SPI serial interface, handshake interface, external digital

trigger input, event output and external clock input/output with 1.8

V or 2.5 V or 3.3 V (5 compatible) logic levels by direction and

logic level control of level shifter and by AFI controller implemented in FPGA.

The digital pattern acquisition/generation and corresponding flexible sample timing are controlled by ADLINK’s Smart Control

Engine implemented by FPGA, as shown

PCIe-7360

Operations 21

Page 32

.

SMB IN

SMB OUT

DIO[7..0]

DIO[15..8]

DIO[23..16]

Ext. CLK in

Ext. CLK out

1.8/2.5/3.3V

Logic Level Selectable

Level Shifter

Level Shifter

Level Shifter

100MHz OSC

80-Step Phase

Shift Control

Ext. CLK in/out

DI DATA

Int. Timebase

Acquisition/ Generation

DI Latch

Control

Logic Level

Pattern

Timing Control

8K FIFO

ADLINK

Smart

Control

Engine

DI DMADO DMA

PCIe

INTERFACE

INTERFACE

PCI Express x4

DIO[31..24]

INTERFACE

VHDCI-68P CONNECTOR

AFI[5..0]

AFI[7,6]

Level Shifter

1.8/2.5/3.3V

Logic Level Selectable

Level Shifter

Level Shifter

DO DATA

I2C/SPI

AFI BUS

20K

FIFO

DO Buffer

AFI

Interface

Figure 3-1: PCIe-7360 Block Diagram

3.2 Programmable Logic Level

To interface different logic level applications, the PCIe-7360 supports three software selectable logic levels of 1.8 V, 2.5 V, or 3.3 V

(5 V compatible) for all digital I/O lines, sample clocks, I2C, SPI,

triggers, and events. All I/O lines conform to the selected logic

22 Operations

Page 33

PCIe-7360

level. When connecting PCIe-7360 to a device under test (DUT),

interface voltage levels must be compatible, as follows.

X V

: The digital input voltage at logic high; senses a binary

IH

one (1)

X V

: The digital input voltage at logic low; senses a binary

IL

zero (0)

X V

: The digital output voltage at logic high; generates a

OH

binary one (1)

X V

: The digital output voltage at logic low; generates a

OL

binary zero (0)

Logic Levels 1.8 V 2.5 V

Digital Input

Digital Output

Min. VIH 1.2 V 1.6 V 2 V

Max. VIL 0.63 V 0.7 V 0.8 V

Min. VOH 1.6 V 2.3 V 3.1 V

Max. VOL 0.2 V 0.2 V 0.2 V

Table 3-1: Logic Levels

3.3 V

(5 V compatible)

3.3 Digital I/O Configuration

32-channel high-speed digital I/O lines are bi-directional and

divided into four groups. Each group contains 8 channels and can

be configured as input port or output port individually. At power-up,

all I/O lines are preset to input ports. When configuring to digital

output mode, the initial status of digital outputs are in tri-state.

Possible configuration modes are as follows:

Port Channel Power-up status Direction

Port A D0 to D7 Input Input or output

Port B D8 to D15 Input Input or output

Port C D16 to D23 Input Input or output

Port D D24 to D31 Input Input or output

Operations 23

Page 34

DI Raw Data Mapping

For digital pattern acquisition, the data width can be configured to

8-bit, 16-bit, 24-bit, or 32-bit and the data transfer is based on

32-bit data width. Below is the mapping table for different DI port

combination.

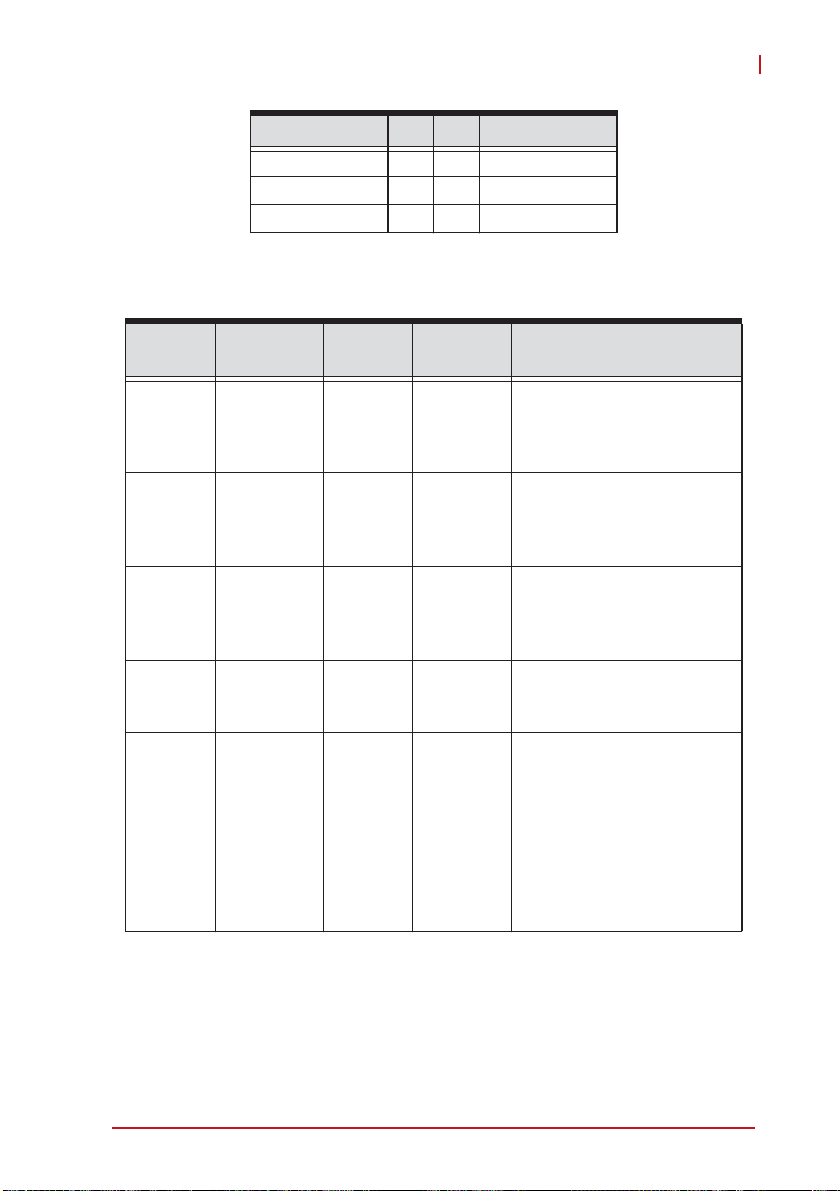

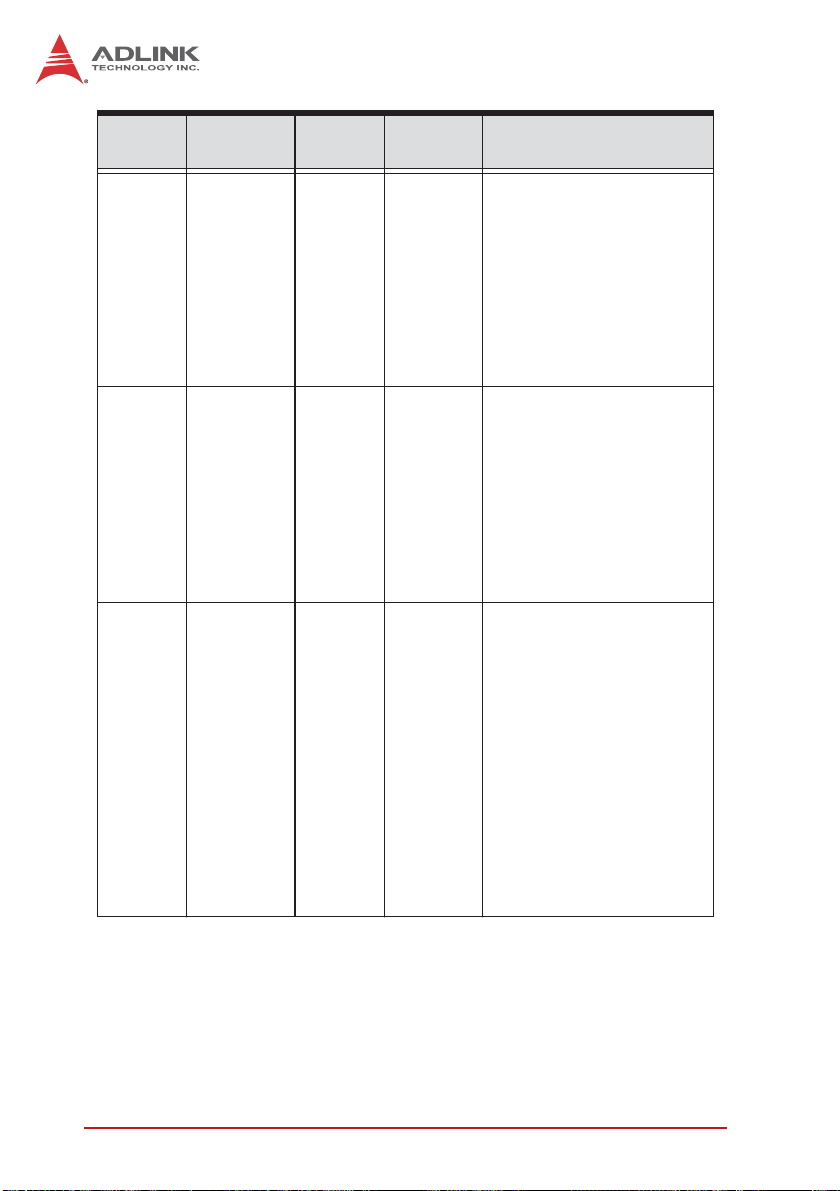

Data Width Input Ports raw data Mapping

D CBA

8 bits

16 bits

24 bits

32 bits DCBA See Figure 3-5

DCB A

D C BA

D CBA

DCBA

D C B A

D CBA

D CBA

D C B A

DCBA

D CBA

D C BA

DCB A

DCBA

See Figure 3-2

See Figure 3-3

See Figure 3-4

24 Operations

Page 35

PCIe-7360

Figure 3-2: DI Raw Data Mapping for 8-Bit Data Width

Operations 25

Page 36

Figure 3-3: DI raw data Mapping for 16-Bit Data Width

26 Operations

Page 37

PCIe-7360

Figure 3-4: DI raw data Mapping for 24-Bit Data Width

Figure 3-5: DI raw data Mapping for 32-Bit Data Width

3.4 Sample Clock Phase Shift

PCIe-7360 features phase shift of sample clock (on SMB connector or AFI6 & AFI7 of SCSI-VHDCI connector). The sample clock

can be from external DUT or can be the exporting clock generated

from internal time base. The resolution of phase shift is 80 step,

implemented by Phase-Locked Loop (PLL) function of FPGA. In

Operations 27

Page 38

other words, the phase shift of sample clock is 4.5° x N, where N is

any integer from 1 to 80. Furthermore, in phase shifting mode, the

supported clock frequency is from 20 to 100 MHz. This function

can optimize the timing of digital pattern acquisition or generation

to avoid sampling/exporting the data from/to DUT at transition

state. Therefore, for digital input, the data can be sampled in clean

and valid timing instead of transition timing. For digital output, it

can fine tune the exporting clock to avoid the sampling of DUT at

setup time or hold time instead of aligning the data.

PCIe-7360 Card

Generation of Digital Data

Exported

sampled clock

(to DUT)

DO Data

(to DUT)

External

sampled clock

(from DUT)

DI Data

(from DUT)

Transition area

D0 D1 D2 D3

Valid area

D0 D1 D2 D3

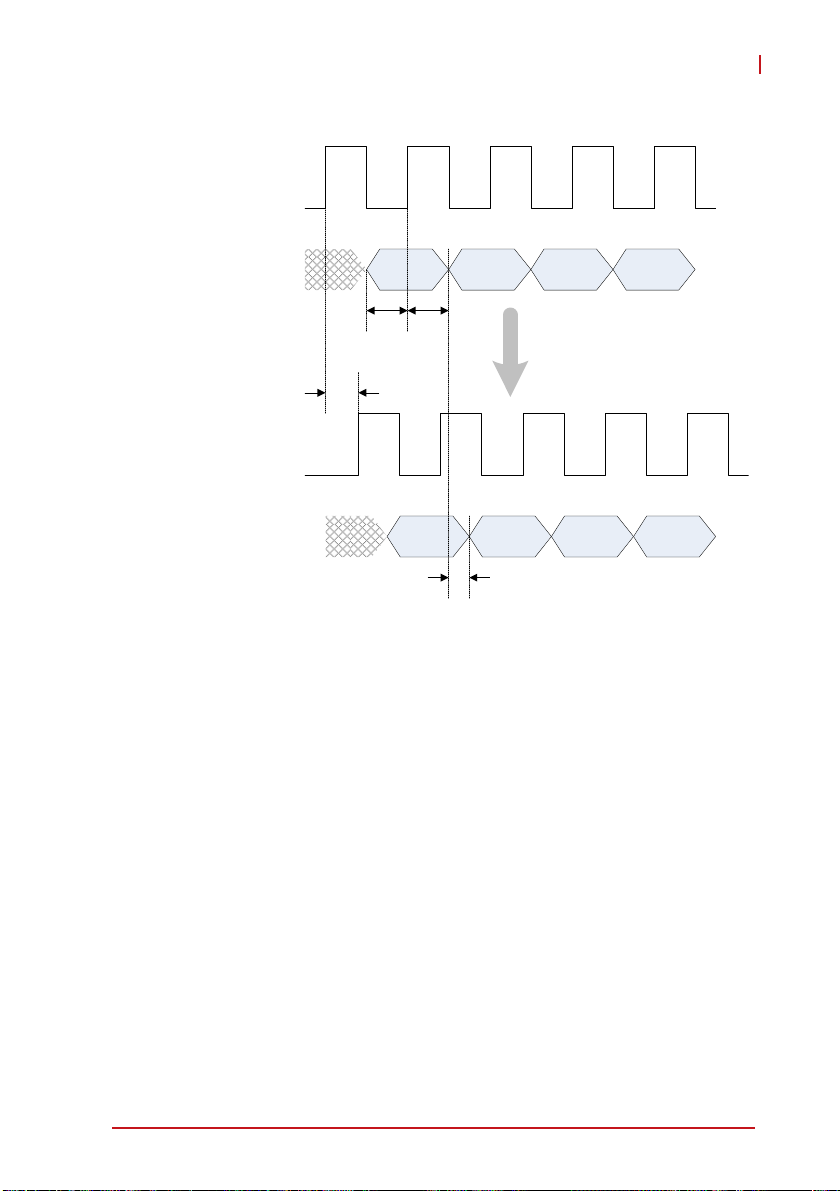

Figure 3-6: Phase Shift of Sample Clock

80-step phase shift

x

80-step phase shift

D0 D1 D2 D3

Transition area

Acquisition of Digital Data

D0 D1 D2 D3

Valid area

28 Operations

Page 39

PCIe-7360

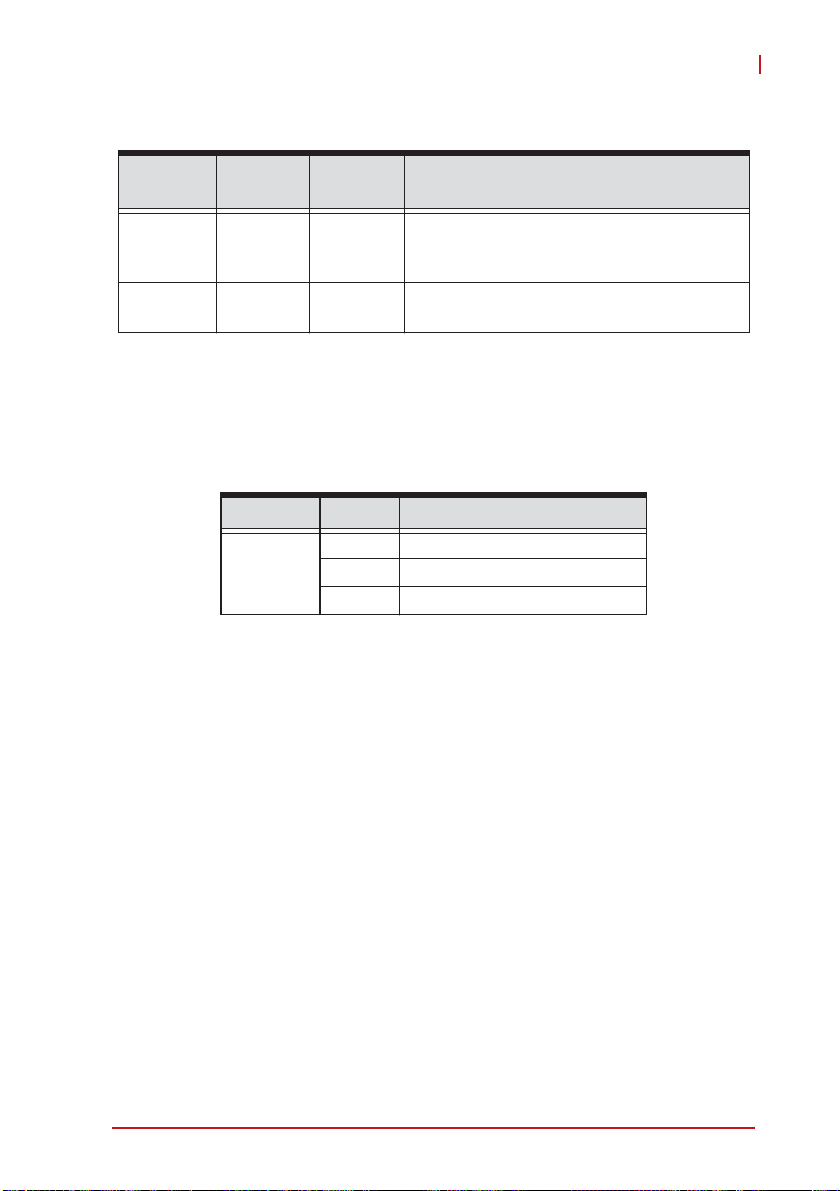

Value

Revolution 80 steps (1 step = 4.5°)

Supported

Frequency Range

20 MHz to 100MHz

User can shift the clock phase ofthe following clock:

External DI sample clock (from SMB CLK IN or AFI7)

Supported CLK

External DO sample clock (from SMB CLK IN or AFI6)

Exported DI sample clock (from SMB CLK IN or AFI7)

Exported DO sample clock (from SMB CLK IN or AFI6)

3.5 Bus-mastering DMA Data Transfer

Digital I/O data transfer between PCIe-7360 and PC’s system

memory is through bus mastering DMA, which is controlled by

PCIe IP Core.

System

Memory

PC Mainboard

NB

Chipset

500 MB/s

PCI-

Express

IP Core

500MB/s

FIFO

PCIe-7360

Figure 3-7: Maximum Data Throughput

The bus-mastering controller controls the PCI/PCIe bus when it

becomes the master of the bus. Bus mastering reduces the size of

the on-board memory and reduces the CPU loading because data

is directly transferred to the computer’s memory without host CPU

intervention.

Bus-mastering DMA provides the fastest data transfer rate on the

PCI/PCIe bus. Once the analog/digital input operation starts, control is returned to the program. The hardware temporarily stores

the acquired data in the onboard Data FIFO and then transfers the

data to a user-defined DMA buffer memory in the computer.

Please note that even when the acquired data length is less than

the Data FIFO, the data will not be kept in the Data FIFO but

directly transferred into host memory by the bus-mastering DMA.

DUT

Operations 29

Page 40

due to the complexity of programming DMA transfer mode, It is

recommended that a high-level program library provided by our

driver be used to configure this card, a number needs only to be

assigned to the sampling period and the number of conversion

into the specified counters. After the trigger condition is matched,

the data is transferred to the system memory by the bus-mastering

DMA.

The PCI/PCIe controller also supports scatter/gather bus mastering DMA, enabling transfer of large amounts of data by linking all

the memory blocks into a continuous linked list.

In a multi-user or multi-tasking OS, like Microsoft Windows, or

Linux, it is difficult to allocate a large continuous memory block to

DMA transfer. Therefore, the PCI/PCIe controller enables scatter-gather or chaining mode DMA to link the non-continuous memory blocks into a linked list avoiding fragments of small size

memory limiting transfer. Users can configure the linked list for the

input DMA channel or the output DMA channel.

As shown in a linked list constructed by three DMA descriptors,

each descriptor contains a PCI/PCIe address, PCI/PCIe dual

address, a transfer size, and the pointer to the next descriptor.

PCI/PCIe address and PCI/PCIe dual address support 64-bit

addresses which can be mapped into more than 4GB of the

address space. Many small size memory blocks can be allocated

and their associative DMA descriptors chained together by their

application programs. The software driver provides simple settings

of the scatter-gather function, and some sample programs are

also provided within the ADLINK all-in-one CD.

30 Operations

Page 41

PCIe-7360

First PCI Address

First Dual Address

Transfer Size

Next Descriptor

PCI Address

Dual Address

Transfer Size

Next Descriptor

PCI Bus

Local Memory

(FIFO)

PCI Address

Dual Address

Transfer Size

Next Descriptor

Figure 3-8: Scatter-Gather DMA for Data Transfer

Choose Finite or Continuous Operation

Data can be transferred continuously to or from computer memory

(continuous operation), or you can specify the number of samples

you want to transfer (one-shot operation). In either case, the

PCIe-7360 transfers the data using direct memory access (DMA)

without occupying CPU resources.

3.6 Sample Clock

The sample clock controls the data rate of digital pattern acquisition and generation. For PCIe-7360, the sample clock can be configured from internal timer pacer or external clock through the

SMB connectors or SCSI-VHDCI connector.

Digital Input (DI) Sample Clock

For the operation of digital pattern acquisition in continuous mode

or burst handshake mode, the PCIe-7360 card can acquire digital

data from external devices at a specific sampling rate (DI sample

Operations 31

Page 42

clock). DI sample clock can be selected as the following two clock

sources:

X Internal DI sample clock – the PCIe-7360 can internally

generate the sample clock signal for digital data acquisition.

With an internal base clock source of 100 MHz, the

PCIe-7360 can generate any clock frequency of 100 MHz/n,

where n is any integer from 1 to 65535.

X External DI sample clock – the PCIe-7360 can receive

external clock signal from AFI7 or SMB CLK as the DI sample clock for synchronization applications. The external DI

sample clock supports up to 100MHz @ 8/16/24/32-CH

(8/16/24/32-bit data width) or up to 200MHz @ 8/16-CH

(8/16-bit data width).

In addition, the PCIe-7360 can also export internal DI sample

clock to external devices through AFI7 pin or SMB CLK connector.

32 Operations

Page 43

PCIe-7360

Digital Output (DO) Sample Clock

For the operation of digital pattern generation in continuous mode

or burst handshake mode, PCIe-7360 card can generate digital

data to external devices at a specific update rate (DO sample

clock). DO sample clock can be selected as the following two

clock sources:

X Internal DO sample clock – the PCIe-7360 can internally

generate the sample clock signal for digital data generation.

With an internal clock source of 100MHz, the PCIe-7360

can generate any clock frequency of 100 MHz/n, where n is

any integer from 1 to 65535.

X External DO sample clock – the PCIe-7360 can receive an

external sample clock signal from AFI6 or SMB CLK connector as the DO sample clock for synchronization applications.

In addition, the PCIe-7360 can also export internal DO sample

clock to external devices through AFI6 pin or SMB CLK connector.

DI/DO sample clock architecture of PCIe-7360 is as follows.

Operations 33

Page 44

DO Sampled CLK

Generation

Engine

DO CLK

Mux

80-step

phase shift

Ext. DO sampled clk

Int. DO sampled clk

1/N

Ext. DO CLK

Mux

I

AFI6

DI Sampled CLK

Acquisition

Engine

100MHz

Mux

DI sampled clk

DO sampled clk

Int. Timebase

DI CLK

1/N

Int. DI sampled clk

Ext. DI sampled clk

80-step

phase shift

80-step

phase shift

80-step

phase shift

Ext. DI CLK

Mux

Mux

Export. DI CLK

Mux

Export. DI/DO CLK

Mux

Export. DO CLK

SMB CLK in

I

AFI7

O

AFI7

SMB CLK out

O

AFI6

Figure 3-9: DI/DO Sample Clock Architecture

34 Operations

Page 45

Internal

clock

External

clock

Sample

clock

exporting

DI Sample CLK DO Sample CLK

Source

Freq.

Source

Freq.

Freq.

(phase shift)

Destination

Freq. 0 – 100 MHz 0 – 100 MHz

Freq.

(phase shift)

Table 3-2: DI/DO Sample Clock Configuration

Onboard 100 MHz

oscillator

100 MHz/n

(n = 1 to 65535)

AFI7

SMB CLK in

0-100MHz @

8/16/24/32-CH

0-200MHz @

8/16-CH

20 to 100 MHz 20 to 100 MHz

AFI7

SMB CLK out

20 to 100 MHz 20 to 100 MHz

Onboard 100 MHz

oscillator

100 MHz/n

(n = 1 to 65535)

AFI6

SMB CLK in

0-100MHz @

8/16/24/32-CH

AFI6

SMB CLK out

PCIe-7360

3.7 Operating Modes

The PCIe-7360 supports four different modes for acquisition and

generation operation, including software polling, continuous,

handshake, and burst handshake mode..

Polling Mode (Single Read/Write)

The PCIe-7360 supports a software polling mode to read or write a

single chunk of data via a software command. That is, the 32-bit

high-speed I/O lines can be used as a static I/O. The data width

can be 8-bit, 16-bit, 24bit, or 32-bit.

DI DMA in Continuous Mode

For the DI pattern acquisition operation in continuous mode,

PCIe-7360 card can acquire input data from external devices at a

specific sampling clock rate (DI sampled clock). DI sample clock

Operations 35

Page 46

can be selected from internal or external clock source. The operation sequences are listed as follows:

Steps:

X Define DI port configuration (32/24/16/8-bits data width)

X Define DI logic level configuration (3.3/2.5/1.8 V)

X Define DI sample clock configuration (internal/external)

Z If choose internal sampled clock, you can define sam-

pling clock rate to be 100MHz/n (n = 1 to 65535)

Z If choose external sampled clock, the phase shift func-

tion is available when external clock is a free-running

clock (not a strobe signal) and external clock rate is from

20 to 100 MHz.

X Define DI starting mode configuration (NoWait or WaitTRIG)

Z If choose WaitTRIG, you can define start trigger source

to be software trigger or external trigger (DI-Start) from

AFI0 to AFI7.

X Define DI data count

X Execute DI DMA Read Command (continuous mode)

36 Operations

Page 47

PCIe-7360

Operating architecture of DI DMA in continuous mode is as

shown.

100MHz

Mux

DI CLK

1/N

Int. DI sampled clk

Ext. DI sampled clk

80-step

phase shift

Ext. DI CLK

Mux

AFI7

I

SMB CLK in

External clock in

DI sampled clk

clk

Bus Master DMA

8kS FIFO Flip Flop

enable

NoWait/

WaitTRIG

Software trigger DI-Start

Start Trigger

Mux

DI Data DI Data

Figure 3-10: DI Continuous Mode Architecture

Timing of DI DMA in continuous mode is as shown.

D[31:0]

AFI[7:0]

External trigger in

Software trigger out

Operations 37

Page 48

Figure 3-11: DI Timing Diagram

DO DMA in Continuous Mode

For the DO pattern generation operation in continuous mode,

PCIe-7360 card can generate digital data to external devices at a

specific update clock rate (DO sample clock). DO sample clock

can be selected from internal or external clock source. The operation sequences are listed as follows:

Steps:

X Define DO port configuration (32/24/16/8-bits data width)

X Define DO logic level configuration (3.3/2.5/1.8 V)

X Define DO sample clock configuration (internal/external)

Z If choose internal sample clock, you can define sampling

clock rate to be 100MHz/n (n = 1 to 65535)

Z If choose external sample clock, the phase shift function

is available when external clock rate is 20 to 100 MHz.

X Define DO exporting sample clock configuration (AFI6/SMB

CLK out)

38 Operations

Page 49

PCIe-7360

Z PCIe-7360 can also export DO sample clock to external

devices. The destination of DO sample clock exporting

can be AFI6 or SMB CLK out connector.

Z The phase shift function is available when exported

clock is a free-running clock and the clock rate is 20 to

100 MHz.

X Define DO starting mode configuration (NoWait or Wait-

TRIG)

Z If choose WaitTRIG, you can define start trigger source

to be software trigger or external trigger (DO-Start) from

AFI0 to AFI7.

X Define DO data count.

X Execute DO DMA Write Command (continuous mode)

Operational architecture of DO DMA in continuous mode is as

shown.

Operations 39

Page 50

Mux

DO CLK

100MHz

Int. DO sampled clk

Ext. DO sampled clk

1/N

Ext. DO CLK

Mux

AFI6

I

External clock in

Bus Master DMA

80-step

phase shift

SMB CLK in

AFI6

O

SMB CLK out

D[31:0]

AFI[7:0]

80-step

phase shift

DO sampled clk

clk

Export

clk gate

clk valid

20kS FIFO Flip Flop

enable

NoWait/

WaitTRIG

Software trigger DO-Start

Start Trigger

Mux

Mux

Export. DO CLK

DO Data DO Data

Figure 3-12: DO Continuous Mode Architecture

Exported sampled

clock out

External trigger in

Software trigger out

Timing of DO DMA in continuous mode is as shown.

40 Operations

Page 51

DO Sampled Clock

Start Trigger

(DO-Start)

Software Trigger out

(DO-SW)

PCIe-7360

t

ET2D

t

W

t

IT2D

Exported DO Sampled Clock

(falling edge)

DO Data

Wait for

start trigger

t

W

= Minimum detectable trigger width

t

ET2D

= Delay from external trigger to do data out (about 5 cycle)

t

IT2D

= Delay from software trigger out to do data out (about 4 cycle)

D0 D1 D2

Write data to

external device

D3 D4

Figure 3-13: DO Timing Diagram

DI DMA in Handshake Mode

For the DI pattern acquisition operation in handshake mode,

PCIe-7360 card can acquire input data from external devices by

handshake data transfer through DI-REQ input signal and DI-ACK

output signal of AFI interface. The operation sequences are listed

as follows:

Step1: Configuration

X Define DI port configuration (32/24/16/8-bits data width)

X Define DI logic level configuration (3.3/2.5/1.8V)

X Define DI-REQ and DI-ACK signal (AFI0 to AFI7)

Z For example: if configure AFI3 as DI-REQ and AFI4 as

DI-ACK, and then you must connect the handshake sig-

Operations 41

Page 52

nal (DI-REQ and DI-ACK) of external device to the AFI3

and AFI4.

X Define DI starting mode configuration (NoWait or WaitTRIG)

Z If choose WaitTRIG, you can define start trigger source

to be software trigger or external trigger (DI-Start or

DI-TRIG) from AFI0 to AFI7.

X Define DI data count

Step2: Execute DI DMA Read Command (handshake mode)

X After DI data is ready on device side, the peripheral device

strobe data into the PCIe-7360 by asserting a DI-REQ signal. (action_1)

X The DI-REQ signal caused the PCIe-7360 to latch DI data

and store it into DI FIFO. (action_2)

X The PCIe-7360 asserts a DI-ACK signal when it is ready for

another input. (action_3)

Z The action_1 to action_3 is repeated in handshake

mode.

X The DI data in the DI FIFO is transferred into system mem-

ory directly and automatically by bus mastering DMA.

The operating architecture of DI DMA in handshake mode is as

shown.

42 Operations

Page 53

AFI[7:0]

PCIe-7360

DI-ACK

DI-REQ

clk

ack

Bus Master DMA

8kS FIFO Flip Flop

enable

NoWait/

WaitTRIG

Software trigger

Start Trigger

Mux

DI Data DI Data

DI-Start or DI-TRIG

Figure 3-14: DI Handshake Mode Architecture

Timing of DI DMA in handshake mode is as shown.

DI-ACK

DI-REQ

D[31:0]

AFI[7:0]

External trigger in

Software trigger out

Operations 43

Page 54

Figure 3-15: DI Handshake Timing Diagram

DO DMA in Handshake Mode

For the DO pattern generation operation in handshake mode,

PCIe-7360 card can generate output data to external devices by

handshake data transfer through DO-REQ output signal and

DO-ACK input signal of AFI interface. The operation sequences

are listed as follows:

Step1: Configuration

X Define DO port configuration (32/24/16/8-bits data width)

X Define DO logic level configuration (3.3/2.5/1.8V)

X Define DO-REQ and DO-ACK signal (AFI0 to AFI7)

Z For example: if configure AFI3 as DO-REQ and AFI4 as

DO-ACK, and then you must connect the handshake sig-

44 Operations

Page 55

nal (DO-REQ and DO-ACK) of external device to the

AFI3 and AFI4.

X Define DO starting mode configuration (NoWait or Wait-

TRIG)

Z If choose WaitTRIG, you can define start trigger source

to be software trigger or external trigger (DO-Start or

DO-TRIG) from AFI0 to AFI7.

X Define DO write count

Step2: Execute DO DMA Write Command (handshake mode)

X The DO data saved in the system memory is transferred to

DO FIFO directly and automatically by bus mastering DMA.

X After DO data are ready, DO-REQ signal is generated and

DO data are sent to the external device. (action_1)

X After DO-ACK signal from external device is gotten

(action_2)

Z The action_1 to action_2 is repeated in handshake

mode.

PCIe-7360

Operations 45

Page 56

The operating architecture of DO DMA in handshake mode is as

shown.

AFI7

I

External clock in

Mux

DI CLK

Ext. DI sampled clk

80-step

phase shift

Ext. DI CLK

Mux

SMB CLK in

Bus Master DMA

DI sampled clk

clk

8kS FIFO Flip Flop

enable

NoWait/

WaitTRIG

Software trigger DI-Start or DI-TRIG

DI-REQ

DI-ACK

Start Trigger

Mux

DI-REQ

DI Data DI Data

DI-ACK

D[31:0]

AFI[7:0]

Figure 3-16: DO Handshake Mode Architecture

External trigger in

Software trigger out

DI-REQ

DI-ACK

46 Operations

Page 57

Timing of DO DMA in handshake mode is as shown.

t

t

2

DO -REQ

DO -ACK

3

PCIe-7360

DO Data

t

2

t

3

40 ns

50 ns

DO D1 D2

Write data to external device

Figure 3-17: DO Handshake Timing Diagram

DI DMA in Burst Handshake Mode

The burst handshake mode is a fast and reliable data transfer protocol. It has both advantage of handshake mode and continuous

mode.

In DI burst handshake mode, DI-REQ signal is active by external

device when it is ready to send DI data and sample clock. And

then DI-ACK signal is generated by PCIe-7360 when it is ready to

receive DI data from external device.

External device should start to send DI data after it detect DI-ACK

signal is active. DI data transfer between PCIe-7360 and external

device should be continued when both DI-REQ and DI-ACK are

active. When DI FIFO of PCIe-7360 becomes almost full, DI-ACK

signal is inactive. External device should stop to send DI data and

sample clock after it detects DI-ACK signal inactive. The operation

sequences are listed as follows:

Operations 47

Page 58

Step1: Configuration

X Define DI port configuration (32/24/16/8-bits data width)

X Define DI logic level configuration (3.3/2.5/1.8 V)

X Define DI sample clock configuration (only external)

Z The phase shift function is available when external clock

is a free-running clock (not a strobe signal) and external

clock rate is from 20 to 100 MHz.

X Define DI-REQ and DI-ACK signal (AFI0 to AFI7)

Z For example: if configure AFI3 as DI-REQ and AFI4 as

DI-ACK, and then you must connect the handshake signal (DI-REQ and DI-ACK) of external device to the AFI3

and AFI4.

X Define DI starting mode configuration (NoWait or WaitTRIG)

Z If choose WaitTRIG, you can define start trigger source

to be software trigger or external trigger (DI-Start or

DI-TRIG) from AFI0 to AFI7.

X Define DI data count

48 Operations

Page 59

PCIe-7360

Step2: Execute DI DMA Read Command (burst handshake mode)

X PCIe-7360 will generate DI-ACK signal when it is ready to

receive DI data after DI-REQ signal is active.

X External device starts to send DI data and DI sample clock

after DI-ACK signal is active.

X PCIe-7360 starts to receive DI data and DI sample clock

from external device when DI-REQ and DI-ACK are all

active.

X The DI data in the DI FIFO is transferred into system mem-

ory directly and automatically by bus mastering DMA.

The operating architecture of DI DMA in burst handshake mode is

as shown.

Figure 3-18: DI Burst Handshake Mode Architecture

Operations 49

Page 60

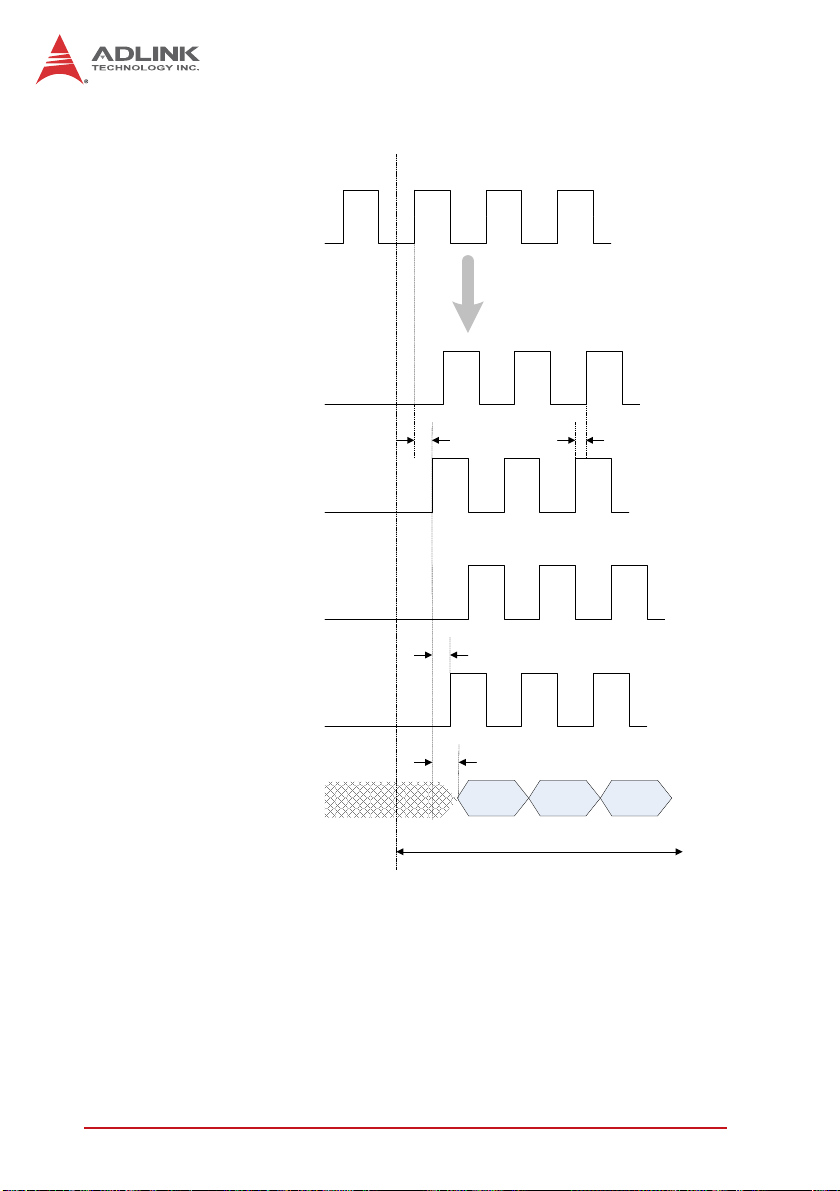

Timing of DI DMA in burst handshake mode is as shown.

DI Sampled Clock

(from external)

External Device is ready to send DI data

DI -REQ

(Active High)

DI -ACK

(Active High)

DI Data

Wait DI-REQ

asserted

Wait DI-ACK

asserted

PCIe-7360 is ready to

receive DI data

DO

D1 D2 D3 D9D7 D8

DI data transfer starts

(DI-REQ & DI-ACK

are all asserted)

PCIe-7360 is not ready

to receive DI data

(DI FIFO is full)

D5

DI data transfer stops

(DI-ACK is de-asserted)

DI data transfer re-start

(DI-REQ & DI-ACK

are all asserted)

Figure 3-19: DI Burst Handshake Timing Diagram

DO DMA in Burst Handshake Mode

In DO burst handshake mode, DO-REQ signal is active by

PCIe-7360 when it is ready to send out DO data. And then

DO-ACK signal should be generated by external device when it is

ready to receive DO data. Once DO-ACK is active, external device

has to keep DO-ACK active until its input buffer is almost full. The

operation sequences are listed as follows:

Step1: Configuration

X Define DO port configuration (32/24/16/8-bits data width)

X Define DO logic level configuration (3.3/2.5/1.8 V)

X Define DO sample clock configuration (internal/external)

Z If choose internal sampled clock, you can define sam-

pling clock rate to be 100 MHz/n (n = 1 to 65535)

Z If choose external sampled clock, the phase shift func-

tion is available when external clock rate is from 20 to

100 MHz.

X Define DO exporting sample clock configuration (AFI6/SMB

CLK out)

50 Operations

Page 61

PCIe-7360

Z The PCIe-7360 can also export DO sampled clock to

external devices. The destination of the exported DO

sampled clock can be AFI6 or SMB CLK out connector.

Z The phase shift function is available when exported

clock rate is from 20 to 100 MHz.

X Define DO-REQ and DO-ACK signal (AFI0 - AFI7)

Z For example: if configure AFI3 as DO-REQ and AFI4 as

DO-ACK, and then you must connect the handshake signal (DO-REQ and DO-ACK) of external device to the

AFI3 and AFI4.

X Define DO starting mode configuration (NoWait or Wait-

TRIG)

Z If choose WaitTRIG, you can define start trigger source

to be software trigger or external trigger (DO-Start or

DO-TRIG) from AFI0 - AFI7.

X Define DO data count

Step2: Execute DO DMA Write Command (burst handshake

mode)

X The DO data saved in the system memory is transferred to

DO FIFO directly and automatically by bus mastering DMA.

X After DO data are ready, DO-REQ signal is asserted.

X PCIe-7360 start to send DO data and DO sampled clock to

external device after DO-ACK signal is asserted.

X If input buffer of external device has no much space for new

DO data, DO-ACK signal is inactive and PCIe-7360 is only

allowed to send 4 more data to the receiver.

X If DO data are not ready (DO FIFO is empty), DO-REQ sig-

nal is inactive and PCIe-7360 stops to send DO data and

DO sample clock until DO data are ready again.

The operating architecture of DO DMA in burst handshake mode

is as shown.

Operations 51

Page 62

Mux

DO CLK

100MHz

Int. DO sampled clk

Ext. DO sampled clk

1/N

Ext. DO CLK

Mux

AFI6

I

External clock in

Bus Master DMA

Figure 3-20: DO Burst Handshake Mode Architecture

80-step

phase shift

80-step

phase shift

DO sampled clk

clk

Export

clk gate

clk valid

20kS FIFO Flip Flop

enable

NoWait/

WaitTRIG

Software trigger DO-Start or DO-TRIG

DO-REQ

DO-ACK

Start Trigger

Mux

SMB CLK in

AFI6

Exported sampled

Mux

Export. DO CLK

DO-REQ

DO Data DO Data

DO-ACK

O

SMB CLK out

D[31:0]

AFI[7:0]

External trigger in

Software trigger out

DO-REQ

DO-ACK

clock out

52 Operations

Page 63

PCIe-7360

Timing of DO DMA in burst handshake mode is as shown.

Figure 3-21: DO Burst Handshake Timing Diagram

DO DMA in Burst Handshake Mode 2

DO burst handshake mode 2 improves tolerance in burst handshaking applications with large wire delay. In this mode, the

PCIe-7360 confirms availability of the receiver indicated by the

DO-ACK signal before it starts to send data. Once the DO-ACK is

asserted, the external device (receiver) maintains assertion of the

DO-ACK signal before its input buffer becomes too small. When

the DO-ACK is de-asserted, indicating the receiver’s buffer is low

on space for new data, the PCIe-7360 is still allowed to send 4

data to the receiver, and the receiver has to receive the data. Timing of burst handshake mode 2 is as shown.

DO Sample Clock

DO -ACK

(Active High)

DO -REQ

(Active High)

Exported DO Sample Clock

DO Data

Wait DO-REQ

asserted

External device is ready to receive DO data

PCIe-7360 DO FIFO is empty or paused

PCIe-7360 is ready to

send DO data

DO

D1 D2 D3 D4 D5 D7

DO data transfer starts

(DI-REQ & DI-ACK are

all asserted)

DO data transfer stops

(DO-REQ is de-asserted)

DI data transfer

(DI-REQ & DI-ACK

are all asserted)

restart

D6 D8

Wire delay + DO

response time

DO stop

Figure 3-22: DO Burst Handshake 2 Timing Diagram

Operations 53

Page 64

3.8 Trigger Source and Trigger Mode

The PCIe-7360 supports 2 trigger sources, software command

trigger and external digital trigger, to start or pause the DI or DO

operation. In addition, the PCIe-7360 supports 3 trigger modes,

including post trigger, gated trigger, and post trigger with re-trigger. In post trigger mode and post trigger with re-trigger mode, the

polarity of digital trigger signal can be configured to rising edge or

falling edge. In gated trigger mode, the level of trigger signal will

start or pause the operation of digital pattern acquisition or generation. Below are the examples of these trigger conditions.

[Example 1] External digital trigger with post trigger mode

DI data Count: 8 samples

Trigger Event: DI-Start (rising edge)

Figure 3-23: DI Post Trigger

54 Operations

Page 65

PCIe-7360

[Example 2] External digital trigger with post trigger

DO data Count: 8 samples

Trigger Event: DO-Start (rising edge)

Re-Trigger Count: 3

Figure 3-24: DO Post Trigger

[Example 3] External digital trigger with post trigger and re-trigger

DI data Count: 4 samples per trigger

Trigger Event: DI-Start (rising edge)

Re-Trigger Count: 3

Figure 3-25: DI Post Trigger with Re-trigger

Operations 55

Page 66

[Example 4] External digital trigger with post trigger and re-trigger

DO data Count: 4 samples per trigger

Trigger Event: DO-Start (rising edge)

Re-Trigger Count: 3

Figure 3-26: DO Post Trigger with Re-Trigger

[Example 5] External digital trigger with gated trigger

DI data Count: 12 samples

Trigger Event: DI-Pause (logic high)

Figure 3-27: DI Gated Trigger

56 Operations

Page 67

PCIe-7360

[Example 6] External digital trigger with gated trigger

DO data Count: 12 samples

Trigger Event: DO-Pause (logic high)

Figure 3-28: DO Gated Trigger

3.9 Application Function I/O

The PCIe-7360 features eight AFI (Application Function I/O) lines.

These bi-directional digital I/O lines allow you to route I2C, SPI,

trigger, event, handshake, and clock signals to/from the

SCSI-VHDCI I/O connector. The following table lists the supporting functions of AFI lines and the corresponding pin out.

Function Signal I/O AFI0 AFI1 AFI2 AFI3 AFI4 AFI5 AFI6 AFI7

I2C Master

SPI Master

External

Trigger in

SCL O

SDA I/O

SCLK O

SDO O

SDI I

CS_0 O

DI-Start I

DO-Start I

DI-Pause I

DO-Pause I

Operations 57

Page 68

Function Signal I/O AFI0 AFI1 AFI2 AFI3 AFI4 AFI5 AFI6 AFI7

Trigger out

Event

Handshake

Clock

DI_SW O

DO_SW O

PM O

COS O

DI-REQ I

DI-ACK O

DI-TRIG I

DO-REQ O

DO-ACK I

DO-TRIG I

DO-SCLK I/O

DI-SCLK I/O

Function Signal I/O Description

2

I

C Clock– I2C clock signal to slave

device capable of clock rate up to

1953.125KHz.

2

I

C Serial Data– Data signal for I2C read/

write communication.

2

C Master

I

SCL O

SDA I/O

SPI Clock– SPI clock signal to slave

SCK O

device capable of clock rate up to

62.5MHz.

SDI I

SPI Master

SDO O

Master Input Slave Output– Data signal

for SPI read communication.

Master Output Slave Input– Data signal

for SPI write communication.

Chip Select of Slave Device 0– Output

CS_0 O

signal to select the desired SPI slave

device 0.

58 Operations

Page 69

Function Signal I/O Description

DI Start Trigger in– External digital trigger

signal to begin an acquisition operation.

DO Start Trigger in– External digital trigger signal to begin a generation operation.

DI Gate Trigger in– External digital signal

to start/pause an acquisition operation.

DO Gate Trigger in– External digital signal to start/pause a generation operation.

DI Trigger out– A pulse signal output generated by PCIe-7360 when receiving a

software start command of DI.

DO Trigger out– A pulse signal output

generated by PCIe-7360 when receiving a

software start command of DO.

Pattern Match Event– A pulse signal output to indicate the event of pattern match

of user-defined data lines.

Change Detection Event– A pulse signal

output to indicate the change detection of

any user-defined data lines.

External

Trigger in

Trigger out

Event

DI-Start I

DO-Start I

DI-Pause I

DO-Pause I

DI_SW O

DO_SW O

PM O

COS O

PCIe-7360

Operations 59

Page 70

Function Signal I/O Description

Digital Input Reques– In handshake

DI-REQ I

DI-ACK O

DI-TRIG I

Handshake

DO-REQ O

DO-ACK I

DO-TRIG I

mode for DI pattern acquisition, DI-REQ

carries handshake control information

from DUT to PCIe-7360.

Digital Input Acknowledge– In handshake mode for DI pattern acquisition,

DI-ACK carries handshake status information from PCIe-7360 to DUT.

Digital Input Trigger– In handshake

mode for DI pattern acquisition, DI-TRIG

can be used to start the operation.

Digital Output Request– In handshake

mode for DO pattern generation, DO-REQ

carries handshake control information

from PCIe-7360 to DUT.

Digital Output Acknowledge– In handshake mode for DO pattern generation,

DO-ACK carries handshake status information from DUT to PCIe-7360.

Digital Output Trigger– In handshake

mode for DO pattern generation, DO-TRIG

can be used to start the operation.

60 Operations

Page 71

Function Signal I/O Description

External DI Sampled Clock in– In

free-running mode or burst handshake

mode, PCIe-7360 can receive external

sampled clock from DUT for acquisition by

DI-SCLK I/O

Clock

DO-SCLK I/O

DI-SCLK.

Export DI Sampled Clock out– In

free-running mode or burst handshake

mode, PCIe-7360 can export sampled

clock of acquisition to DUT by DI-SCLK.

External DO Sample Clock in– In continuous mode or burst handshake mode,

PCIe-7360 can receive external sampled

clock from DUT for generation by

DO-SCLK.

Export DO Sample Clock out– In continuous mode or burst handshake mode,

PCIe-7360 can export sample clock of

generation to DUT by DO-SCLK.

PCIe-7360

Operations 61

Page 72

I2C Master

PCIe-7360’s application function I/O (AFI) can be configured as

I2C node for communicating with peripheral devices through

PCIe-7360’s built-in I2C master protocol and provided Windows

API directly. Along with I2C master of PCIe-7360, users can easily

communicate with ADC/ Microcontroller/ EEPROM/ image sensor

for initializing and programming.

Figure 3-29: I2C Master of PCIe-7360

The I2C master of the PCIe-7360 provides at most 8 bytes data

width -- 4 bytes address/ command and 4 bytes data. A basic I2C

command is consisted of at least two parts: slave address (with

Read/Write bit) and one or more types of data bytes (Command,

62 Operations

Page 73

PCIe-7360

Address or Data). Figure 3-29 shows the data transfer on the I2C

bus.

Figure 3-30: Data Transfer on the I2C Bus

I2C master of PCIe-7360 supports the clock range from 1.9 kHz to

244.14 kHz. After issuing command to I2C slave device, the clock

rate might be changed according the request from I2C slave. The

below formula is to calculate the I2C clock rate.

F

= 488.28 / (Clk Pre-scale + 1) (kHz),

scl

where Clk Pre-scale = 1 to 255

I2C Write Command: the content of Cmd/Addr and Data are

stored in registers I2C_A_CA and I2C_A_DAT and their byte

counts are indicated by I2C CmdAddr Byte Count and Access Byte

Count, respectively.

I2C Read Command: the format of Read command is similar with

a write command except that the data part is derived by slave

device.

Operations 63

Page 74

I2C Cmd/Addr Count is less than 4 byte:

I2C Data Count is less than 4 byte:

Figure 3-31: I2C Data Format

SPI Master

PCIe-7360’s application function I/O (AFI) can be configured as

SPI node for user to communicate with peripheral devices through

PCIe-7360’s built-in SPI master protocol and provided API

directly. Along with SPI master of PCIe-7360, user can easily communicate with ADC/ Microcontroller/ EEPROM/ image sensor for

initializing and programming.

64 Operations

Page 75

PCIe-7360 Card

SCK

SPI Master

SD0

SDI

CS#0 CS0

Figure 3-32: SPI Master of PCIe-7360

AFI0

AFI1

AFI2

AFI3

PCIe-7360

SCK

SI

Slave 0

S0

Operations 65

Page 76

SPI master of PCIe-7360 provide at most 64 bits -- 32 bits

address/ command and 32 bits data. SPI master of PCIe-7360

supports only one slave device. Figure 3-32 shows the data transfer on SPI bus.

CS#

SCK

SDO

SDI

Cmd/Addr

Cmd/Addr 0 ~ 32b

dummy dummy

dummy

Data

TD 0 ~ 32b

Data

RD 0 ~ 32b

Figure 3-33: Data Transfer on SPI Bus

SPI master of PCIe-7360 supports clock frequency range from

244.14 kHz to 62.5 MHz. After issuing command to SPI slave

device, the clock rate might be changed according the request

from SPI slave. The below formula is to calculate the SPI clock

rate.

Fscl = 62.5 / (Clk Pre-scale + 1) (MHz),

where Clk Pre-scale=0 to 255

SPI master of PCIe-7360 supports two different modes of SCK.

Clock modes 0 and 1 of SCK are as shown.

Figure 3-34: Clock Mode of SCK

66 Operations

Page 77

PCIe-7360

External Digital Trigger

PCIe-7360 supports external digital trigger mode to start or pause

an acquisition or generation operation. PCIe-7360 supports two

trigger sources, internal software trigger and external digital trigger. The digital pattern acquisition or generation will start upon a

software command or an external digital trigger signal to start or

pause the process. The PCIe-7360’s Application Function I/O

(AFI) can be configured as the external digital trigger source.

Figure 3-35: External Digital Trigger Input Configuration

Operations 67

Page 78

Trigger Out

PCIe-7360’s Application Function I/O (AFI) can be configured as

trigger output when receiving a software start command of digital

pattern acquisition or generation. The trigger out signal can synchronize the operation between PCIe-7360 and DUT.

The pulse width of trigger out signal can be configured from 16ns

to 524.288 s. (8 ns x (N+1), where N is from 1 to 65535 )

Figure 3-36: Configured AFI as Internal Software Trigger Output

68 Operations

Page 79

PCIe-7360

Event Out

PCIe-7360’s Application Function I/O (AFI) can be configured as

event output of pattern match or COS (Change of State).

Pattern Match event is a pulse signal generated while the

PCIe-7360’s digital data input lines matching the pre-defined pattern. COS (Change of State) event is a pulse signal generated

while the PCIe-7360 detects a change on the pre-defined data

input line. The pulse width of Event Out signal can be configured

from 16ns to 524.288 s. (8 ns x (N+1), where N is from 1 to

65535).

You can export this event out signal to trigger external devices for

synchronization or to inform external devices.

PCIe-7360 Card

AFI0

PM event

DI Pattern

Match Logic

DI Change

Detection Logic

PM

COS

PM event

Event out

Mux

COS event

AFI1

AFI2

AFI3

AFI4

AFI5

AFI6

COS event

DUT 0

Trigger in

DUT 1

Trigger in

AFI7

D0 ~ D31

DI PatternDI Pattern

Figure 3-37: Pattern Match and COS Event Configuration

Operations 69

Page 80

Handshake

PCIe-7360’s Application Function I/O (AFI) can be configured as

handshake mode (DI-REQ/DI-ACK/DI-TRIG/DO-REQ/DO-ACK/

DO-TRIG) to communicate with an external device using an

acknowledge signals to request and acknowledge each data

transfer. The handshake mode can ensure the data transfer without loss.

For the digital pattern acquisition using handshake, through