Page 1

Cost Effective

Network Processor

for TCP/IP

with ARM7TDMI

™

MLN7400

Evaluation Board Manual

Version 0.20

December 31, 2003

MCS Logic Inc.

Copyright © 2003 MCS LOGIC Limited. All rights reserved EVB7400

Page 2

EVB7400

Revision History

Version Date Revision Description

V 0.10 December 30, 2003 First Release

User’s Manual V.0.10 2/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 3

EVB7400

User’s Manual V.0.10 3/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 4

EVB7400

Table of Contents

CHAPTER 1 INTRODUCTION.................................................................................................................. 6

1.1 SYSTEM REQUIREMENTS............................................................................................................................................ 6

1.2 BOARD COMPONENTS ................................................................................................................................................ 8

CHAPTER 2 BOARD CONFIGURATION.............................................................................................. 11

2.1 ENDIAN SELECTION (SW1)...................................................................................................................................... 11

2.2 BOOT ROM AND ROM BANK0 LENGTH SELECTION (SW2).................................................................................... 11

2.3 NAND FLASH ....................................................................................................................................................... 11

2.4 GPIO SETTING......................................................................................................................................................... 12

CHAPTER 3 SETUP EVB7400 ENVIRONMENTS................................................................................ 13

3.1 ETHERNET 10/100 BASE-T CONNECTOR................................................................................................................ 13

3.2 CONNECTION METHOD FOR UTP CABLE ................................................................................................................. 13

CHAPTER 4 CONNECTION CONFIGURATIONS FOR DEBU G CO NSOLE..................................15

4.1 CONFIGURATION THE HYPER TERMINAL ................................................................................................................. 15

4.2 DOWNLOADING BINARY IMAGE AND FLASH WRITE ................................................................................................ 16

4.2.1 Downloading Binary Image............................................................................................................................ 16

4.2.2 Flash Write...................................................................................................................................................... 19

CHAPTER 5 OPENNICE32 INSTALLATION....................................................................................... 20

5.1 OPENICE32............................................................................................................................................................. 20

5.2 CONNECTING EVB7400 AND PC ............................................................................................................................. 20

5.3 POWERING UP THE BOARD AND OPENICE32 ........................................................................................................... 20

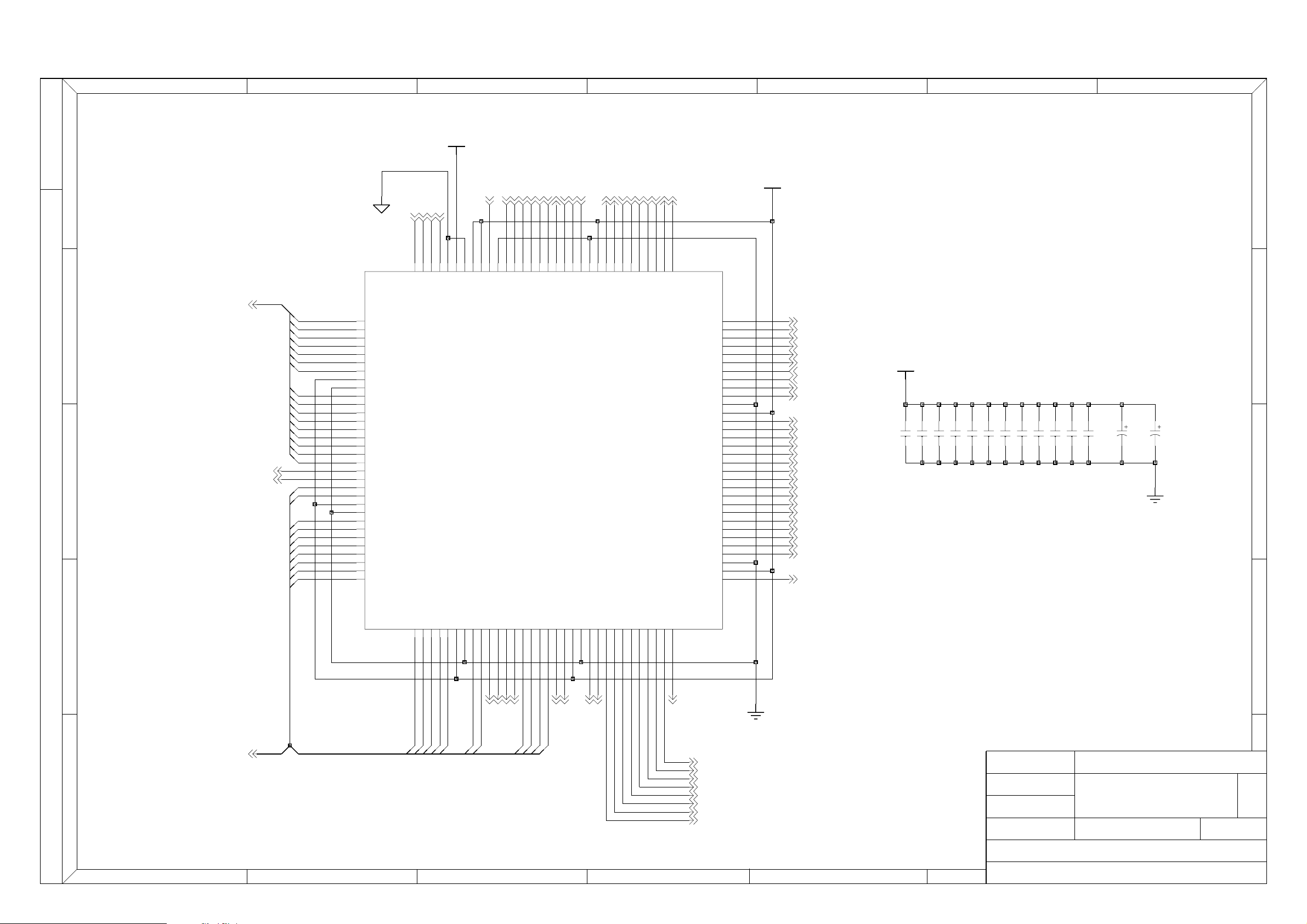

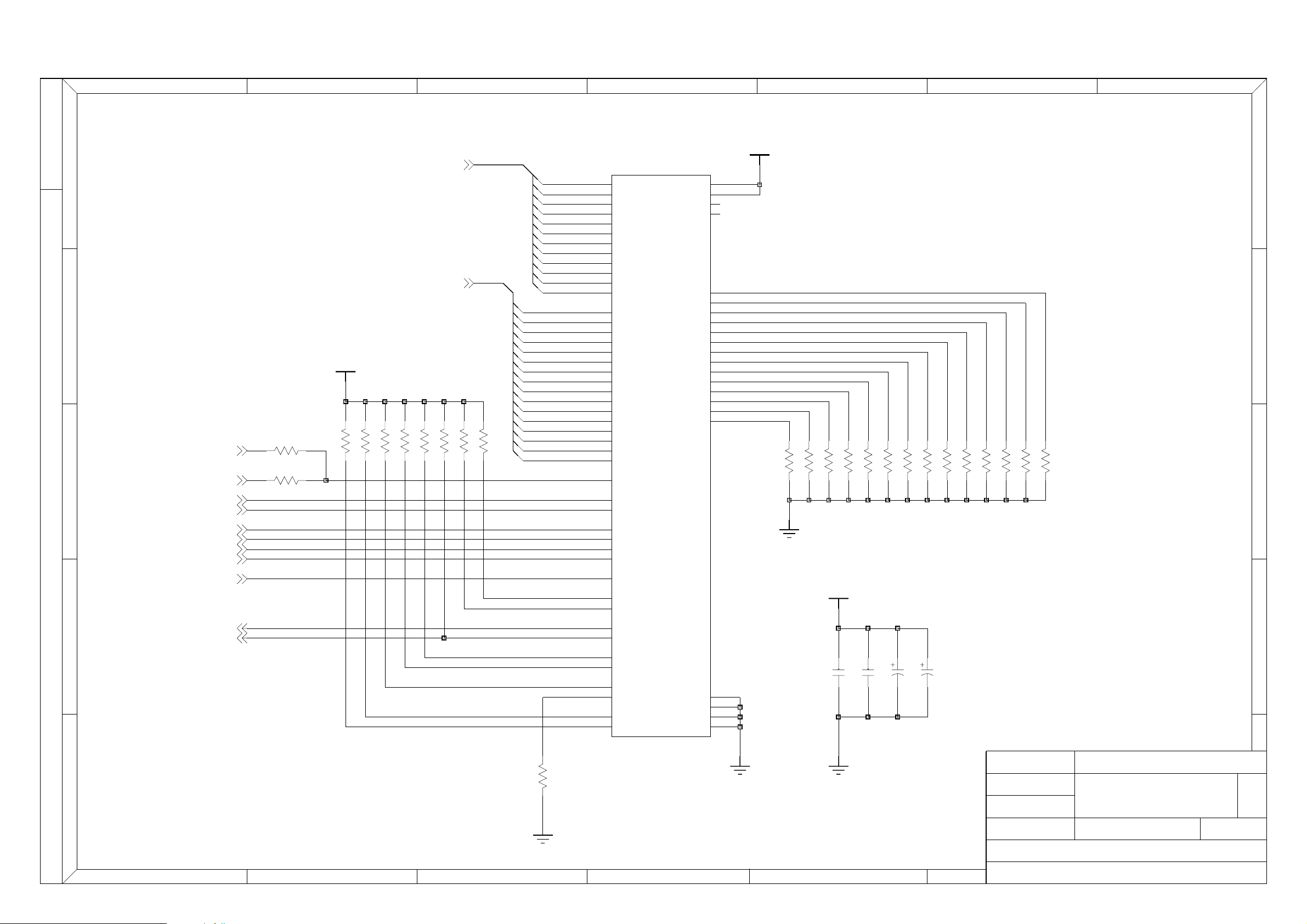

CHAPTER 6 EVB7400 1.0 SCHEMETIC AND BOM ............................................................................ 21

6.1 EVB7400 BOM....................................................................................................................................................... 21

6.2 EVB7400 SCHEMATIC............................................................................................................................................. 24

User’s Manual V.0.10 4/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 5

EVB7400

List of Figures

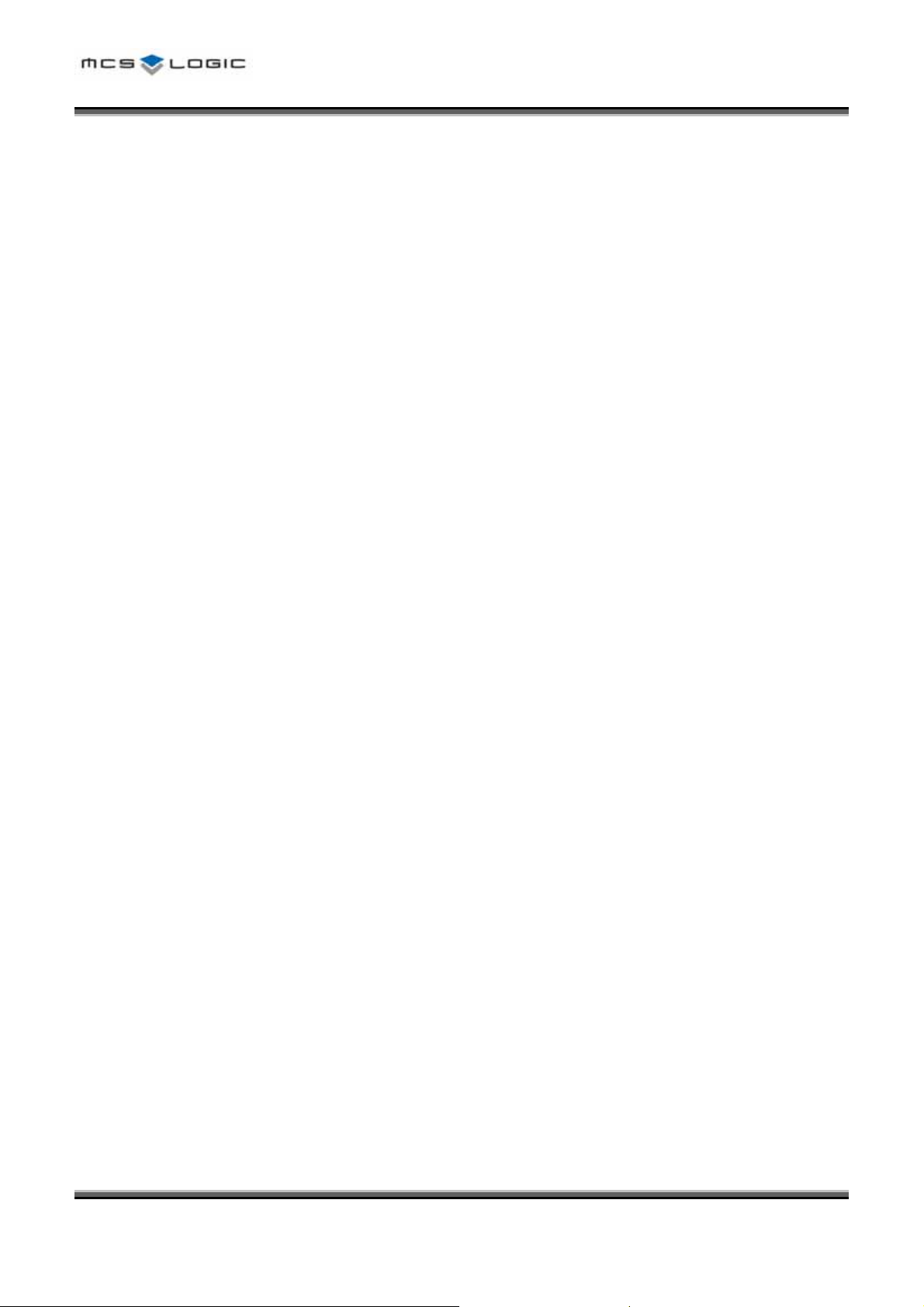

[FIGURE 1 ] EVB7400 BLOCK DIAGRAM....................................................................................................................... 6

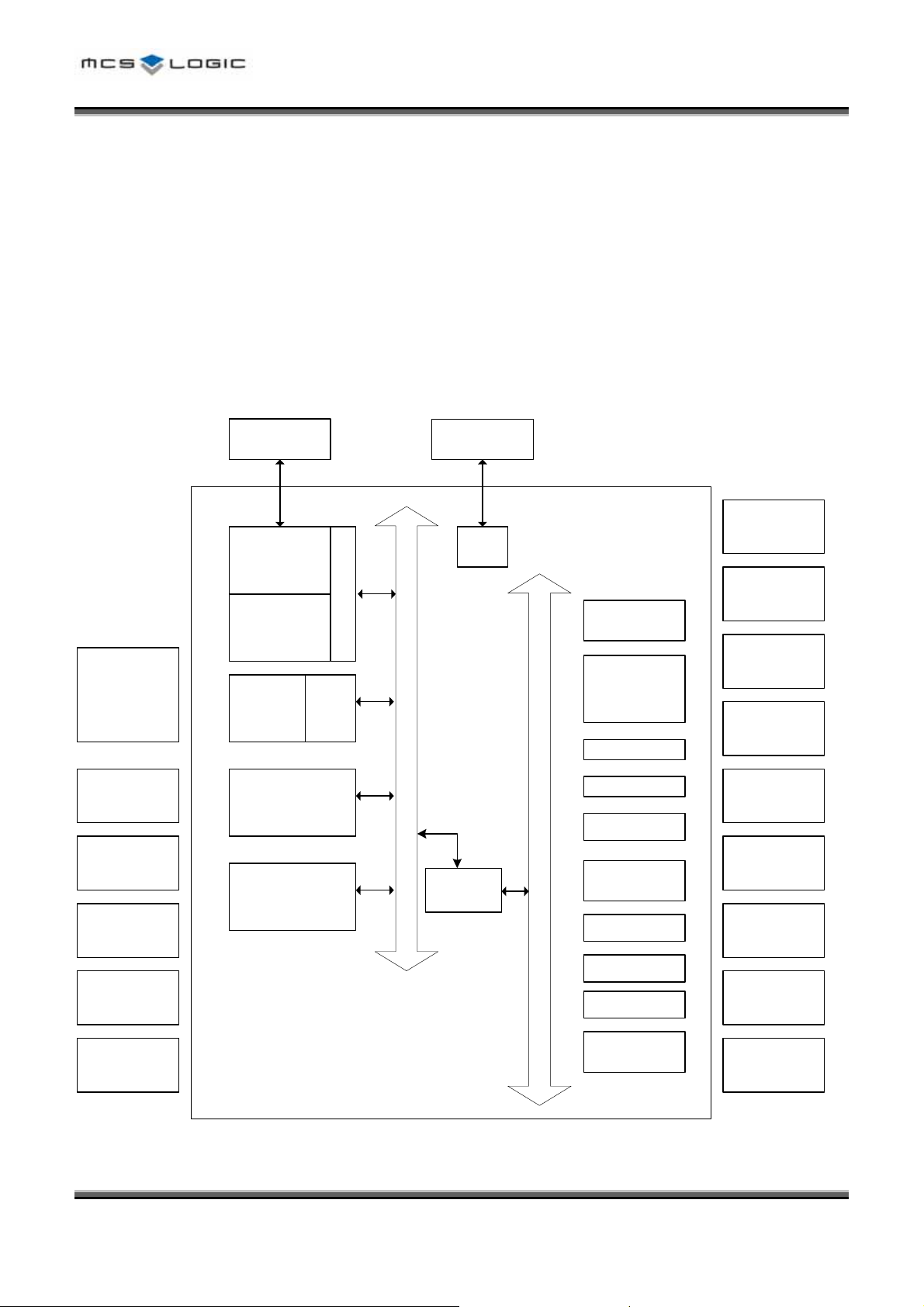

[FIGURE 2 ] MEMORY MAP.......................................................................................................................................... 7

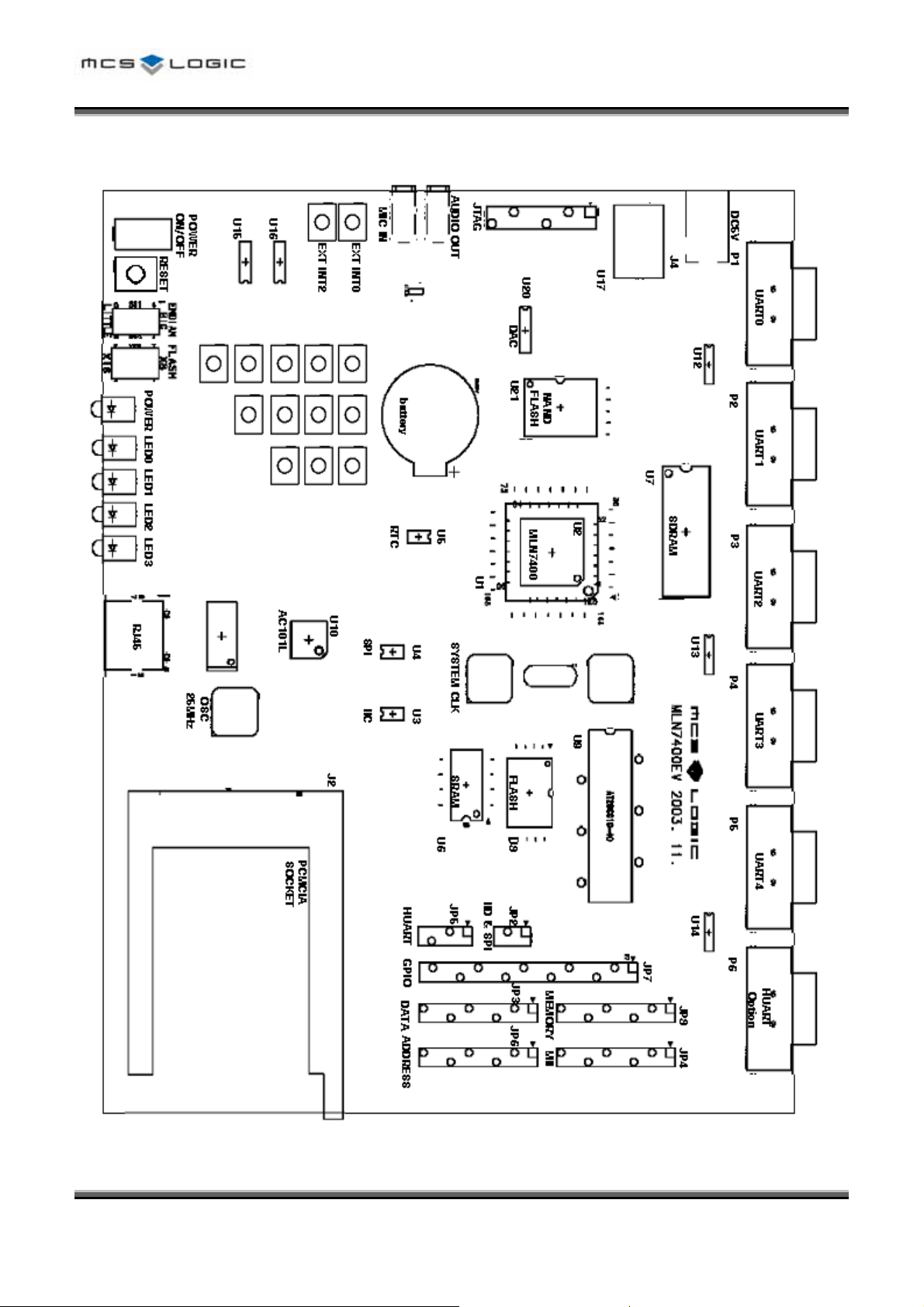

[FIGURE 3 ] BLOCK DIAGRAM (TOP VIEW).................................................................................................................. 8

[FIGURE 4 ] UTP CABLE CONNECTION...................................................................................................................... 14

[FIGURE 5 ] PROPERTIES SETTING PAGE................................................................................................................. 15

[FIGURE 6 ] CHOOSE SETTING PAGE........................................................................................................................ 16

[FIGURE 7 ] CONNECTING WITH OPENICE32............................................................................................................. 20

User’s Manual V.0.10 5/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 6

EVB7400

Chapter 1 Introduction

EVB7400 is a MLN7400 evaluation board and MCS-uClinux training kit that is suitable for code development and exploration of MN7400

with MCS-uClinux. It includes much of the hardware and software required completing your application development. It supports various

function related with network, communication such as IIC, SPI, UART, 10/100 Ethernet, multimedia module such as sound DAC, storage

media such as NAND FLASH memory module. Using the JTAG interface, you can debug the EVB7400 directly.

1.1 System Requirements

-. Host computer : IBM compatible PC

-. EVB7400 (Evaluation Board for MLN7400)

-. DC 5V Power

Ethernet

PHY

(AC101L)

Boot ROM

(ROM Bank0)

User Flash

(ROM Bank1)

SRAM

(ROM Bank2)

JTAG

ARM7TDMI

4KBytes

Cache

10/100

Ethernet

MAC

2ch GDMA

Memory

Contro ller

DMA

M_Bus I/F

M_Bus

Peripheral

Bridge

X-Tal/Osc

PLL

Peripheral Bus

4 Console

UARTs

1 high-

speed

UART

I2C

SPI

GPIOs

4 channel

ADC

4 Timers

UART0~4

IIC Serial

EEPROM

&RTC

SPI Serial

EEPROM

DAC(CS4340)

MIC IN

KEY

MATRIX

NAND Flash

PCMCIA

Socket

(ROM Bank3)

SDRAM

[Figure 1 ] EVB7400 B

LOCK DIAGRAM

WDT

DAC I/F

Interrupt

Controller

Status

LEDs

Eextenal

Interrupt Key

User’s Manual V.0.10 6/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 7

EVB7400

ADDRESS MLN7400 MAP EVB7400

0x000_0000 ~ 0x0FF_FFFF ROM/Flash bank 0 (16Mbytes) FLASH(512KB)

0x100_0000 ~ 0x1FF_FFFF ROM/Flash bank 1 (16Mbytes) SRAM(128KB)

0x200_0000 ~ 0x2FF_FFFF ROM/Flash bank 2 (16Mbytes) FLASH(2MB)

0x300_0000 ~ 0x3FF_FFFF ROM/Flash bank 3 (16Mbytes) PCMCIA Card

0x400_0000 ~ 0x5FF_FFFF Cacheable SDRAM area (32Mbytes) SDRAM 64Mbits(8Mbytes)

0x600_0000 ~ 0x600_5FFF

(Cacheable)

0x800_0000 ~ 0xEFF_FFFF

(Non-Cacheable)

0xF00_0000 ~ 0xFFF_FFFF SFR Registers

[Figure 2 ]

User’s Manual V.0.10 7/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

MEMORY MAP

Page 8

EVB7400

1.2 Board Components

The arrangement of major components on the board is shown in Figure 3. The major components include:

[Figure 3 ] B

User’s Manual V.0.10 8/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

LOCK DIAGRAM (TOP VIEW)

Page 9

EVB7400

A Flash ROM

There is a socket(U9) which accept 512Kbyte size of 8 bit Flash Memory(AT29C010 ~ 40). This is for diaganostic program(includes all

pheriperal device driver and TCP/IP protocol stack) and BIOS(MCS-uClinux Boot loader) program.

User Flash memory(Selectable Boot ROM)

A mounted 48 TSOP type flash(AM29LV160BB), U8, is mounted for saving MCS-uClinux image. It has 2Mbytes(1M x 16bits)size. If you

want to use this for boot ROM, SW2 should be set to to X16 and U9 should be removed. (The default setting is X8)

SDRAM

SDRAM size is 8Mbytes ( 4M x 16bits)

SRAM

There is a SRAM at ROM Bank1. SRAM SIZE is 64K x 16 bits.

NAND Flash

A mounted NAND Flash ROM is provided for saving user data.

To use NAND flash, you should install and uninstall some 0 ohm register at bottom of board. Please refer to chapter 2 and Schemetic.

EEPROM(AT24C256, AT25040)

There are two EEPROM(U3, U4). One is an IIC Serial EEPROM(U3) and the other is a SPI serial EEPROM(U4).

The size of EEPROM(U3) is 32Kbytes, and the size of EEPROM(U4) is 4Kbytes.

RTC & Thermometer

There is a DS1629(U5) for RTC and thermometer check. The RTC clock is supplied by the crystal(32.768KHz)

Serial Port

There are 5 9-pin female Serial ports for serial data communiation. One is for console between the host PC and EVB7400 and others for

converter(Serial to Ethernet, Serial to wireless and so on). And there is one 9-pin mail Serial ports for High Speed UART.

Ethernet Interface

There are RJ45 connector and Ethernet Phy for network.(AC101L, 10/100 BASE-T)

AUDIO IN/OUT

There is a stereo DAC(CS4340) for AUDIO out. And MIC and AMP is connected to ADIN3(ADC channel3) for AUDIO In.

Reset Button

There is a button for system reset.

Power On/Off Switch

There is a swithch for power on/off.

LED Indicatorst

Seven LEDs are supplied on the EVB7400. Each LED shows power status, user programmable status, ethernet link and activity.

PCMCIA Socket

There is a PCMCIA Socket(J2). To use it, you should set ROM BANK3 as PCMCIA mode.

JTAG Port

One 20-pin JTAG port(J3) is supplied to connect with JTAG based Emulator.

Expansion Connectors

Seven connectors(JP2~JP8) are supplied for system expansion. They contain board data bus, adddress bus, external memory bank

control, IIC, SPI, and MII signals.

Key Matrix

There are 12 key buttons. They can be used ADC application.

Five buttons(SW4, SW7, SW10, SW13, SW15) are connected to ADIN0(ADC channel 0).

User’s Manual V.0.10 9/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 10

EVB7400

Four buttons(SW5, SW8, SW11, SW14) are connected to ADIN1(ADC channel 1).

Three buttons(SW5, SW8, SW11, SW14) are connected to ADIN2(ADC channel 2).

External Interrrupt Key

There are two button to use external interrupts. Each button(S1,S2) is connected to External interrupt0 and 2.

External Timer0 Clock

Timer0 can be supplied by the external clock(ocsillator)

User’s Manual V.0.10 10/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 11

EVB7400

Chapter 2 Board Configuration

The EVB7400 is set with default configuration. You can use the board with the defualt settings direclty. However, you can also change

the settings according to your nedds.

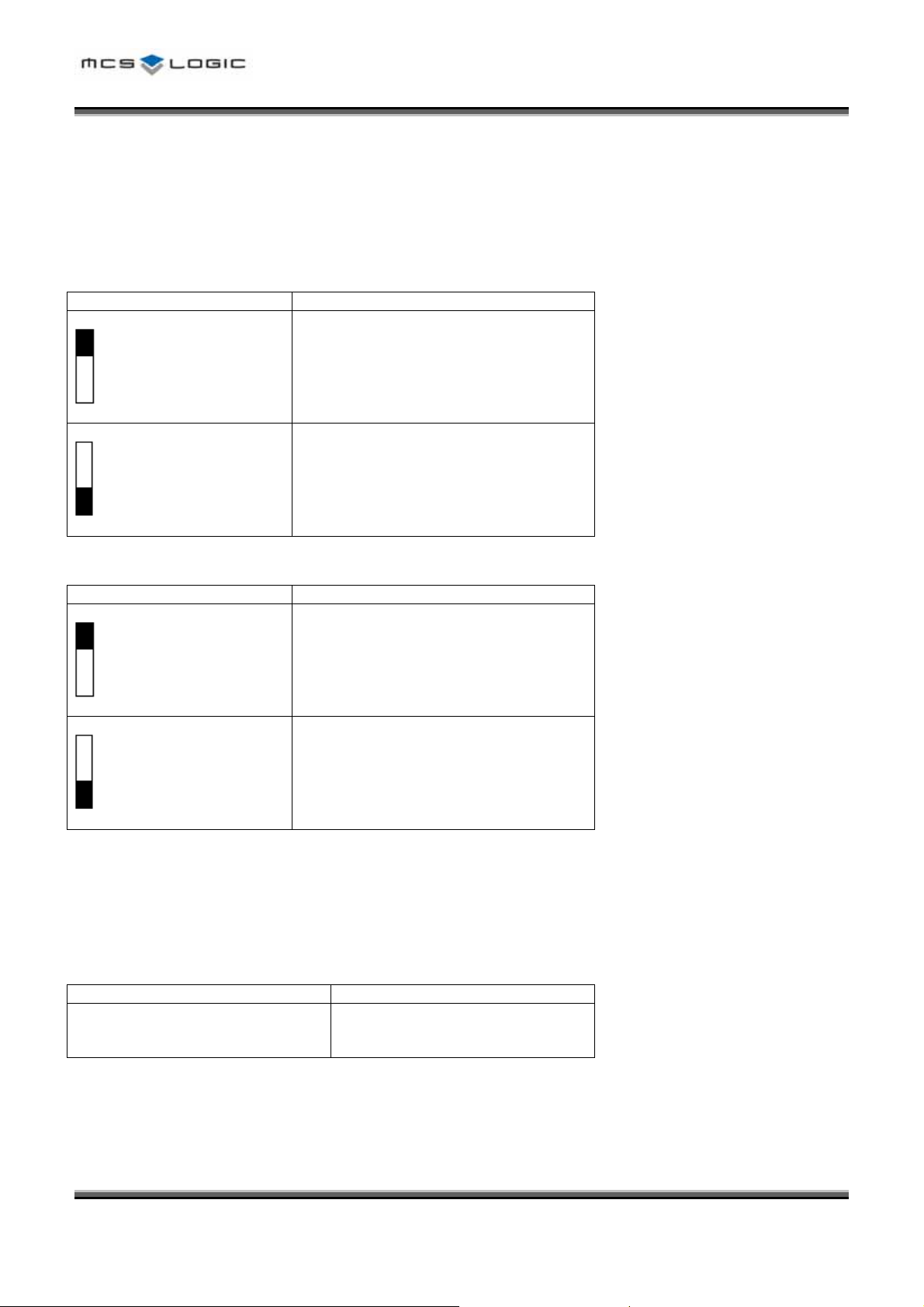

2.1 Endian Selection (SW1)

Status Description

BIG

LITTLE

BIG

LITTLE

BIG Endian

Little Endian

2.2 Boot ROM and ROM Bank0 length Selection (SW2)

Status Description

X8

X16

X8

X16

ROM BANK0 Size is 8 bits.

ROM BANK0 : AT29C040 512 X 8bits Flash

ROM BANK2 : AM29LV160BB 1M X 16bits Flash

ROM BANK 0 size is 16 bits.

ROM BANK0 : AM29LV160BB 1M X 16 bits Flash

*Note : AT29C040(U9) should be removed

2.3 NAND FLASH

You can use NAND Flash through GPIO of MLN7400. To use NAND Flash you shoud install 0 ohm registance.

Refer to schementic page4.

Install Register reference Unintall Register Reference

R12, R13, R14, R15, R16,

R17, R18, R19, R20, R21,

R22, R23, R24, R25, R26

*Note: To use NAND Flash, you can’t use SPI Interface, Console UART3 and High Speed UART(UART4)

R39, R40, R41,R42, R43,

R44, R54,R55,R56

User’s Manual V.0.10 11/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 12

EVB7400

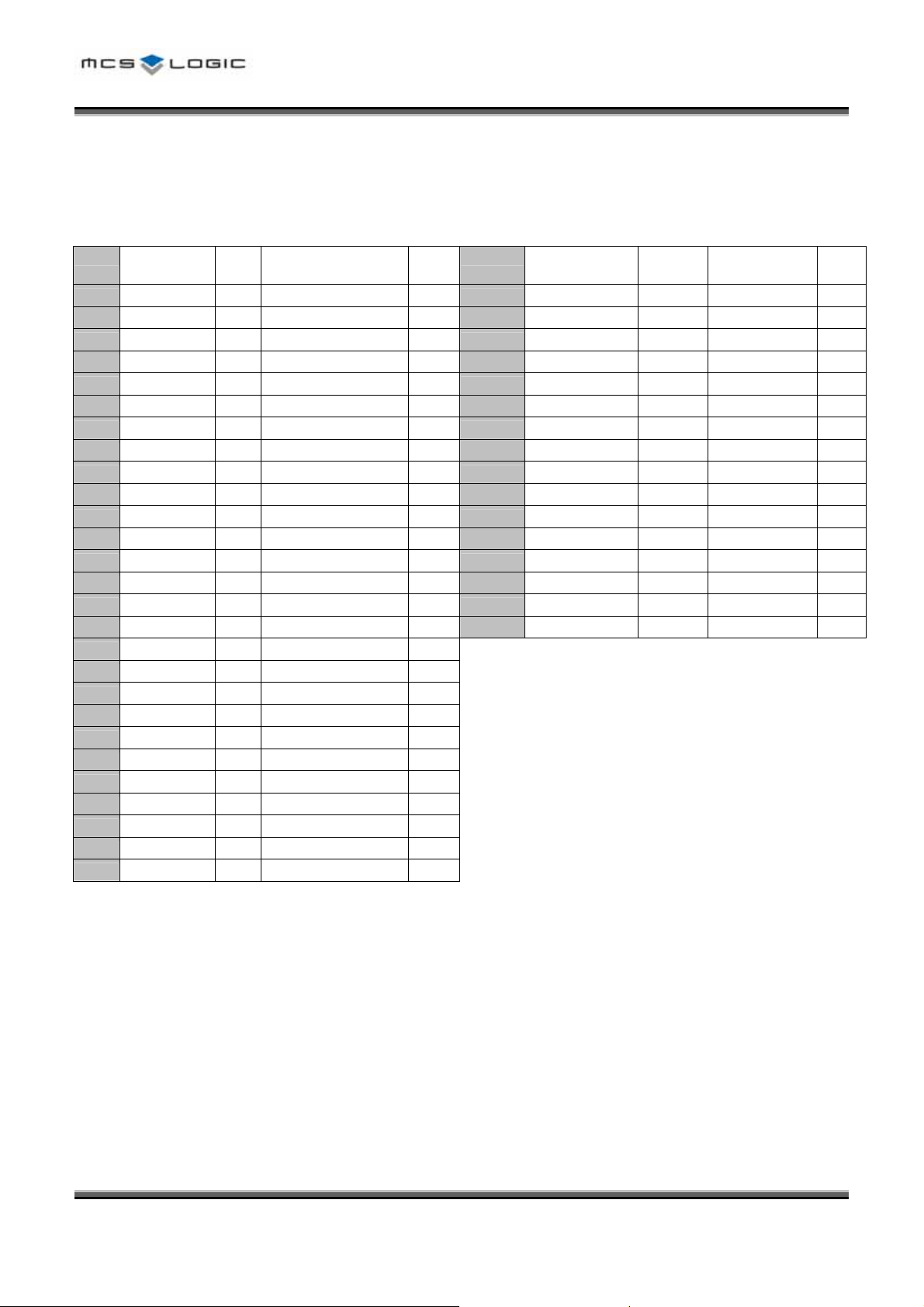

2.4 GPIO Setting

<128-TQFP/ 144 -LQFP Common I/O> <144 -LQFP Extended I/O>

Setting

PIN Shared Initial

GP00 CUTXD1 N,I UART1 S, O GP27 EXT_TCLK0 N,I Ext Timer0 Clk S, I

GP01 CURXD1 N,I UART1 S, O GP28 EXT_TCLK1 N,I LED 2 N, O

GP02 CUTXD2 N,I UART2 S, O GP29 EXT_TCLK2 N,I LED 3 N, O

GP03 CURXD2 N,I UART2 S, O GP30 HUARTnDCD4 N,I NFIO0 N, I

GP04 CUTXD3 N,I UART3/NFWEN S, O GP31 HUARTnCTS4 N,I NFIO1 N, I

GP05 CURXD3 N,I UART3/NFWRN S, O GP32(0) HUARTnRTS4 N,I NFIO2 N, I

GP06 CUTXD4 N,I UART4/NFALEN S, O GP33(1) HUARTnDSR4 N,I NFIO3 N, I

GP07 CURXD4 N,I UART4/NFCLEN S, O GP34(2) HUARTnDTR4 N,I NFIO4 N, I

GP08 nBE[0] N,I SRAM(nBE0) S, O GP35(3) EXINT2 N,I Ext Int2 Test S, I

GP09 nBE[1] N,I SRAM(nBE1) S, O GP36(4) EXINT3 N,I NFIO5 N, I

GP10 TOUT[0] N,I Timer0 TOUT0 S, O GP37(5) TOUT[2] N,I NFIO6 N, I

GP11 TOUT[1] N,I SPI SS# N, O GP38(6) TOUT[3] N,I NFIO7 N, I

GP12 TX_ERR S,0 LED 0 N, O GP39(7) DLRCK N,I DLRCK S, O

GP13 NTRST S,I JTAG(nTRST) S, I GP40(8) DBCK N,I DBCK S, O

GP14 ECSN2 S,O SRAM(ECSN2) S, O GP41(9) DMCK N,I DMCK S, O

GP15 ECSN3/CE1# S,O PCMCIA(CE1#) S, O GP42(10) DDATA N,I DDATA S, O

GP16 SPIMISO N,I SPI MISO/NFCEN S, I

GP17 SPIMOSI N,I SPI MOSI/NFRDN S, O

GP18 SPICLK N,I SPI Clock/NFRBN S, O S : Special

GP19 EXINT0 N,I Ext Int0 Test S, I N : Noraml

GP20 EXINT1 N,I PCMCIA IRQ S, I I : Input

GP21 EXT_UCLK N,I LED 1 N, O O : Output

GP22 REG#/DLRCK N,I PCMCIA REG#/DLRCK S, O

GP23 CE2#/DBCK S,O PCMCIA CE2#/DBCK S, O

GP24 IORD#/DMCK N,I PCMCIA IORD#DMCK S, O

GP25 IOWR#/DDATA N,I PCMCIA IOWR#/DDATA S, O

GP26 ENWAIT N,I PCMCIA ENWAIT S, O

Board Setting

Value PIN Shared Initial Board Setting

1) GP22 ~GP25 는 7400P 의 경우 PCMCIA 와 DAC 을

선택적으로 사용

Setting

Value

User’s Manual V.0.10 12/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 13

EVB7400

Chapter 3 Setup EVB7400 Environments

3.1 Ethernet 10/100 BASE-T Connector

Same connector and pin for both 10Base-T and 100 Base-Tx

< At the network interface card/hubs >

< At the cables >

RJ45 female connetor at the network interface cards and hubs

RJ45 male connector at the cable

Pin Name Descriptions

1 TX+ Tranmit Data+

2 TX- Tranmit Data3 RX+ Receive Data+

4 N/C Not Connected

5 N/C Not Connected

6 RX- Receive Data7 N/C Not Connected

8 N/C Not Connected

NOTE : TX & RX are swapped on hub

3.2 Connection Method for UTP Cable

RJ45 pins on EVB7400 is defined to Adapter side. So, you straight connect EVB7400 to hub through UTP cable. In this case, between

the EVB7400 and the Hub, the pin numbers correspond to each other.

Between the EVB7400 and the NIC which is on the Host PC, you have to connect each other through UTP cable which is crossover

patch cord.

User’s Manual V.0.10 13/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 14

EVB7400

[Figure 4 ]

UTP CABLE CONNECTION

User’s Manual V.0.10 14/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 15

EVB7400

Chapter 4 Connection Configurations for Debug Console

4.1 Configuration the Hyper Terminal

To configure the Hyper Terminal, which is a Windows utility program for serial communications, refer to following steps:

1. Run the Hyper Terminal program

-. Window 95/98/2000/XP start tool bar -> Program -> Accessories -> Hyper Terminal Group

-> Double click Hyperterm.exe -> Enter a connection name -> Select a icon -> Click OK.

2. Select COM Port to communicate with EVB7400 board.

-. Choose COM1 or COM2 as the serial communication port and click OK.

3. Set the serial port properties

-. Bits per second: 57600 bps

-. Data Bits : 8 bits

-. Stop Bits : 1

-. Flow control : None

4. Select the Properties from the File menu

[Figure 5 ] P

5. Choose Setting Page.

User’s Manual V.0.10 15/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

ROPERTIES SETTING PAGE

Page 16

EVB7400

[Figure 6 ] C

6. Re-connect Hyper Terminal to run at new properties

Disconnect : Call -> Disconnect

Connect: Call -> Call

7. Power-On Reset or push the reset button on EVB7400 board

Now, the diagnostic program menu is showed on the Hyper Terminal

HOOSE SETTING PAGE

4.2 Downloading Binary Image and Flash Write

4.2.1 Downloading Binary Image

You can download a binary image file through the serial cable to target without an emulator.

1. Type “ f ” to download user program to EVM7400 on Diagnostic program main menu.

User’s Manual V.0.10 16/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 17

EVB7400

2. Type “8” at Flash Program Menu and type address to download.

User’s Manual V.0.10 17/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 18

EVB7400

3. select the Send File from the Transfer menu

File Name : Select the file name, which you want too download.

Protocol : Select the Xmodem or 1K Xmodem.

4. Click Ok.

Then, the file that you selected will be downloaded.

User’s Manual V.0.10 18/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 19

EVB7400

4.2.2 Flash Write

You can write downloaded binary image at User flash memory(AM29LV160BB, U8).

Type “2” to write an executable binary file at User Flash memory.

Then, you can execute your image by changing Boot Rom selection switch(SW2) to X16(default is X8).

User’s Manual V.0.10 19/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 20

EVB7400

Chapter 5 Opennice32 Installation

5.1 OPENice32

The OPENice32 can also be connected with the EVB7400 as a debugging system for software applications development. OPENice32 is

a JTAG-based, nonintrusive, debugging system for ARM-based controllers or processors. JTAG provides the interface between a

debugger and the ARM-based controller development board.

To use the OPENice32, the following additional equipment are required:

- OPENice32

- 14-way ribbon cable

- 9-pin RS232 cable or parallel cable

- 5 V DC (Max. 3A) power supply

5.2 Connecting EVB7400 and PC

The OPENice32 should be connected to the EVB7400's JTAG Port (J3) via a 20-way cable, and to the host PC via a 9-pin RS232 serial

or parallel cable.

To power on the OPENice32, DC 5 V power supply is

required.

EVB7400

[Figure 7 ] C

ONNECTING WITH OPENICE32

5.3 Powering up the Board and OPENice32

We recommend that you power on the EVB7400 before the OPENice32 is powered on. In this way, the system initialization and memory

configuration for EVB7400 performed by the Boot Code can be completed first.

Otherwise, it may cause the failure of code download via JTAG.

User’s Manual V.0.10 20/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 21

EVB7400

Chapter 6 EVB7400 1.0 Schemetic and BOM

6.1 EVB7400 BOM

No. PART NO GEOMETRY COUNT DESCRIPTION REFERENCE Vendor

1 MLN7400 144LQFP 1 Microprocessor U1 MCS Logic

2 MLN7400P 128TQFP 1 Microprocessor U2 MCS Logic

3 AT24C256 8 SOIC 1 EEPROM(IIC) U3 Atmel

4 AT25040 8 SOIC 1 EEPROM(SPI) U4 Atmel

5 DS1629 8 SOIC 1 RTC U5 Dallas

6 K6R1016V1D 44TSOP 1 SRAM U6 Samsung

7 K4S641632 54TSOP 1 SDRAM U7 Samsung

8 AM29LV160BB 48TSOP 1 Flash U8 AMD

9 AT29C040A 32DIP 1 Flash U9 Atmel

10 AC101L 48 TQFP 1 PHY U10 Altima

11 H1102 1 Transformer U11 PULSE

12 MAX3232 16 SOIC 3 RS232 U12, U13, U14 MAXIM

13 74LVC14 1 U15

14 74LV08 1 U16

15 AMS1086 1 Regulator U17 semtech

16 MAX4468EKA 8pin SOT23 1 AMP U18 MAXIM

17 CS4340 16 SOIC 1 Stereo DAC U20 CRYSTAL

18 K9F2808-YCB0 48 TSOP 1 NAND Flash U21 Samsung

19 Xtal_osc 10MHz Half 1 Xtal-Oscillator

(System CLK)

20 Xtal_osc 25MHz Half 1 Xtal-Oscillator

(PHY CLK)

21 Crystal 32.768KHz DIP(cylinder

type)

22 Crystal 10MHz DIP(ATS Holder

type)

23 Xtal_oxc 1MHz Half 1 Test CLK X3

24 Battery CR2032 1 3V coin Battery BT1

25 Battery Connector 1

26 PushButton SW 15 Reset, ExtInt S1,S2,S3,SW4,SW5,

27 DPDT SW 3 SW1,SW2,SW16

28 Power Toggle SW 3pin DIP 1 A12AP SW3 NKK

29 1N4004 DIP 2 Diode D1,D2

30 1N4148 SMD 1 Diode D3

31 LED 5 D4,D5,D6,D7,D8

32 PCMCIA 68Pin Con 1 ICM-C68H-S112-

33 RJ-45 1 J1

34 HEADER 10X2 1 JTAG J3

35 POWER JACK 1 DC5V PWR J4

36 MIC IN JACK 1 J5

37 AUDIO OUT JACK 1 J6

1 Crystal(RTC) Y1

1 Crystal

(System CLK)

400N1

X2

Y2

X1

SW6,SW7,SW8,SW9,SW10,SW11,

SW12,SW13,SW14,

SW15

J2 JST

User’s Manual V.0.10 21/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 22

EVB7400

38 DB9 FEMAIL 5 UART0~4 P1,P2,P3,P4,P5

39 DB9 MAIL 1 HUART Option P6

40 HEADER 13X2 4 DATA, MII,

ADDRESS,

MEMORY

41 HEADER 24X2 1 GPIO heaser JP7

42 HEADER 4X2 1 IIC & SPI JP2

43 HEADER 6X2 1 HUART header JP5

44 HEADER 1 7 Test Pin JP1,TP1,TP2,TP3,TP4

45 Beads(100Mhz) 2012 1 L L1

46 0 0603(1608) 68 R R8,R9,R10,R11,R12,

47 0 1206(3216) 4 R R204,R205,R206,R207

48 33 0603(1608) 12 R R2,R3,R5,R65,R85

59 49.9 0603(1608) 4 R R89,R90,R91,R92

50 75 0603(1608) 5 R R84,R103,R104,R105,R106

51 100 0603(1608) 1 R R178

52 270 0603(1608) 3 R R155,R,156,R157

53 330 0603(1608) 5 R R144,145,R146,R147,R151

54 390 0603(1608) 3 R R158,R159,R160

55 500 0603(1608) 2 R R93 R94

56 560 0603(1608) 4 R R161,R162,R172,R174

57 820 0603(1608) 1 R R163

58 1K 0603(1608) 10 R R4,R7,R79,R82,R83

59 2K 0603(1608) 4 R R66,R67,R69,R70

60 3K 0603(1608) 1 R R179

61 2.2K 0603(1608) 1 R R167

62 4.7K 0603(1608) 50 R R6,R64,R68,R71,R75,

63 10K 0603(1608) 5 R R102,R148,R149,R173,R175

64 20K 0603(1608) 1 R R171

JP3,JP4,JP6,JP8

TP5, TP6

R13,R14,R15,R16,R17,

R18,R19,R20,R21,R22,

R23,R24,R25,R26,R27,

R28,R29,R30,R31,R32,

R33,R34,R35,R36,R37,

R38,R39,R40,R41,R42,

R43,R44,R45,R46,R47,

R48,R49,R50,R51,R52,

R53,R54,R55,R56,R57,

R58,R59,R60,R61,R62,

R63,R72,R73,R74,R77,

R80,R176,R177,R180,R181,

R200,R201,R202

R86,R87,R88,R95,R96

R97,R107

R152, R153,R154,R164,R168

R76,R78,R81,R98,R99,

R100,R101,R108,R109,R110,R111,

R112,R113,R114,R115,R116,R117,

R118,R119,R120,R121,R122,R123,

R124,R125,R126,R127,R128,R129,

R130,R131,R132,R133,R134,R135,

R136,R137,R138,R139,R140,R141,

R142,R143,R150,R166

User’s Manual V.0.10 22/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 23

EVB7400

65 100K 0603(1608) 3 R R165,R169,R170

66 1M 0603(1608) 1 R R1

67 0.01uF_2kV DIP 1 C56

68 0.01uF 0603(1608) 9 C C47,C57,C58,C59,C60,

C61,C62,C83,C87

69 0.1uF 0603(1608) 65 C C1,C2,C3,C4,C5,

C6,C7,C8,C9,C10,

C11,C12,C15,C17,C18,

C19,C20,C21,C22,C23,

C24,C25,C26,C27,C28,

C29,C32,C33,C34,C35,

C36,C37,C38,C39,C40,

C41,C42,C43,C44,C45,

C46,C48,C50,C52,C63,

C64,C65,C66,C79,C80,

C81,C82,C85,C89,C92,

C93,C94,C96,C97,C183,

C184,C185,C186C187,C188

70 1uF 0603(1608) 6 C C51,C53,C54,C55,C90,

C91

71 20pF 0603(1608) 2 C C13,C14

72 22pF 0603(1608) 2 C C30,C31

73 27pF 0603(1608) 1 C C49

74 47pF 0603(1608) 1 C C88

75 100pF 0603(1608) 1 C C95

76 330pF 0603(1608) 12 C C67,C68,C69,C70,C71,

C72,C73,C74,C75,C76,

C77,C78

77 820pF 0603(1608) 1 C C16

78 1uF SMD A(3216) 17 T/C TC11,TC12,TC13,TC14,TC15TC16,

TC17,TC18,TC19,TC20TC21,TC22,

TC37,TC38,TC39

TC41, TC42

79 2.2uF SMD A(3216) 2 T/C TC9,TC10

80 3.3uF SMD A(3216) 2 T/C TC35,TC36

81 10uF SMD B(3528) 8 T/C TC3,TC6,TC7,TC25,TC26,

TC28,TC29,TC34

82 22uF SMD B(3528) 1 T/C TC8

83 47uF SMD C(6032) 6 T/C TC1,TC2,TC4,TC5,TC23,

TC24

84 100uF SMD D(7343) 3 T/C TC27,TC31,TC33

User’s Manual V.0.10 23/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 24

EVB7400

6.2 EVB7400 Schematic

User’s Manual V.0.10 24/36

Copyright © 2004 MCS LOGIC Limited. All rights reserved

Page 25

1 34 567

2

A

B

A

B

MLN7400 Evaluation Board

C

C

D

DESIGN

CUSTOMER

D

E

MCS LOGIC

CHECK-1

E

CHECK-2

DATE

UPDATE SHEET

MLN7400EV

2003.11.18

REMARK

REV.

1 / 14

BLOCK DIAGRAM

12 3

45

6

Page 26

1

2

3

4

5

6

7

OPTIONAL

XI

A

B

VCC_33 VCC_33A

C

FILTER

D

R2 33

L1

BEADS_100MHz

C16

R1 1M

X1

12

10MHz

C13

20pF

C15

0.1uF

GROUND

ADDR(20:0)

820pF

GROUND

GROUNDGROUND

DATA(15:0)

TC310uF

21

SDCLK

SDCKE

C14

20pF

SYSTEM CLOCK

VCC_33

TDI

TCK

R3

33

XO

GROUND

VCC_33A

X2

1

NC

2

GND

VCC_33

10MHZ

VCC

OUT

4

3

ADIN0

ADIN1

ADIN2

ADIN3

C184

0.1uF

GROUND

SYSCLK

TMS

33R5

XI

NRESET

CUTXD0

CURXD0

GP41_DMCK

GP42_DDATA

FILTER

R4 1K

XO

GP40_DBCK

GROUND

GP39_DLRCK

TESTTDO

VCC_33

A

MDIO

MDC

MII_RXD3

MII_RXD2

MII_RXD1

MII_RXD0

MII_RXDV

MII_RXCLK

MII_RXERR

C1 C2

0.1uF

C3 C4

0.1uF

C5 C6

0.1uF

0.1uF0.1uF

0.1uF

TC1

21

47uF

GROUND

VCC_33

7

6

5

4

3

2

1

GP27_EXTTCLK0

GP28_EXTTCLK1

0

8

9

10

11

12

13

14

15

3

2

GP29_EXTTCLK2

GP30_HUARTNDCD4

1

0

4

5

6

7

8

9

AGND

U1

1

D07

2

D06

3

D05

4

D04

5

D03

6

D02

7

D01

8

VDD33_00

9

GND33_00

10

GP27_EXT_TCLK0

11

GP28_EXT_TCLK1

12

D00

13

D08

14

D09

15

D10

16

D11

17

D12

18

D13

19

D14

20

D15

21

SDCLK

22

CKE

23

AD03

24

AD02

25

VDD33_01

26

GND33_01

27

GP29_EXT_TCLK2

28

GP30_HUARTNDCD4

29

AD01

30

AD00

31

AD04

32

AD05

33

AD06

34

AD07

35

AD08

36

AD09

C8

122

136

141

142

143

144

140

ADIN1

ADIN2

ADIN3

ADIN0

AVSS33_00

135

138

139

137

FILTER

PLLVDD

PLLGND

AVREF33

AVDD33_00

AGND33_00

129

131

130

TMS

CUTXD0

RESETN

CURXD0

GP41_DMCK

GP42_DDATA

128

132

133

134

MLN7400_144LQFP

LDQM_AD15

VDD33_02

AD10

AD11

37

38

39

GND33_02

AD12

BA0_AD13

BA1_AD14

44

45

42

43

40

41

WEN

RASN

UDQM_AD16

SDCSN

GP31_HUARTNCTS4

GP32_HUARTNRTS4

EAD17

CASN

49

47

46

48

EAD18

50

51

52

53

54

123

120

118

119

117

127

126

TDI

TCK

EAD20_X8EN

EAD19_BIG

55

56

121

125

124

XI

XO

TDO

TEST

VDD33_03

EOEN

EWEN

GND33_03

58

60

57

59

MDIO

VDD33_06

GND33_06

GP40_DBCK

GP39_DLRCK

GP00_CUTXD1

GP33_HUARTNDSR4

GP34_HUARTNDTR4

ECSN0

ECSN1

64

65

61

63

62

112

113

114

115

111

116

MDC

RX_D2

RX_D3

GP01_CURXD1

GP02_CUTXD2

GP03_CURXD2

66

67

68

109

110

RX_D0

RX_D1

RX_DV

RX_CLK

RX_ERR

108

TX_CLK

107

TX_EN

106

TX_D0

105

TX_D1

104

TX_D2

103

TX_D3

RX_COL

RX_CRS

SDA

SCL

GND33_05

VDD33_05

GP23_CE2*

GND33_04

VDD33_04

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

GP38_TOUT3

GP37_TOUT2

GP36_EXINT3

GP35_EXINT2

SDA

SCL

GP26_ENWAIT

GP25_IOWR*

GP24_IORD*

GP23_CE2*

GP22_REG*

GP21_EXTUCLK

GP20_EXINT1

GP19_EXINT0

GP18_SPICLK

GP17_SPIMOSI

GP16_SPIMISO

GP15_ECSN3

GP14_ECSN2

GP13_NTRST

GP12_TXERR

GP11_TOUT1

GP10_TOUT0

GP09_NBE1

GP38_TOUT3

GP37_TOUT2

GP36_EXINT3

GP35_EXINT2

GP26_ENWAIT

GP25_IOWR*

GP24_IORD*

GP22_REG*

GP21_EXT_UCLK

GP20_EXINT1

GP19_EXINT0

GP18_SPICLK

GP17_SPIMOSI

GP16_SPIMISO

GP15_ECSN3

GP14_ECSN2

GP13_NTRST

GP12_TX_ERR

GP11_TOUT1

GP10_TOUT0

GP09_NBE1

GP04_CUTXD3

GP05_CURXD3

GP06_CUTXD4

GP07_CURXD4

GP08_NBE0

70

71

MLN7400_144LQFP

72

69

MII_TXCLK

MII_TXEN

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_COL

MII_CRS

C7

0.1uF

AGND

FGND

Endian Setting

ADDR(19)

0.1uF

R207 0_3216

R206

R205 0_3216

SW1

2

5

SW_DPDT

C9

0.1uF

1

3

4

6

0_3216R204

0_3216

R7 1K

C10

0.1uF

GROUND

GROUND

4.7KR6

C11

0.1uF

VCC_33

GROUND

C12

0.1uF

GROUND

H1

1

FHOLE3.5

FGND

BIG

LITTLE

TC2

21

47uF

B

C

D

GP08_NBE0

GP07_CURXD4

GROUND

NEOE

SDCSN

SDWEN

SDRASN

SDCASN

NEWE

NECS1

NECS0

E

GP31_HUARTNCTS4

GP32_HUARTNRTS4

15

14

10

12 13

11

16 17 18 19

20

GP34_HUARTNDTR4

GP33_HUARTNDSR4

GP06_CUTXD4

GP05_CURXD3

GP04_CUTXD3

GP03_CURXD2

GP02_CUTXD2

GP01_CURXD1

GP00_CUTXD1

DESIGN

CHECK-1

CHECK-2

DATE

2003.11.18

CUSTOMER

UPDATE

MCS LOGIC

MLN7400EV

SHEET

E

REV.

2/14

REMARK

Main CPU MLN7400

1

2

3

4

5

6

Page 27

1

23 567

4

VCC_33A

A

FILTER

CURXD0

CUTXD0

ADIN3

ADIN2

ADIN1

AGND

U2

DATA(15:0)

7

B

C

SDCLK

SDCKE

6

5

4

3

2

1

0

8

9

10

11

12

13

14

15

3

2

1

0

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

1

2

3

4

5

6

7

8

9

D07

D06

D05

D04

D03

D02

D01

VDD33_00

GND33_00

D00

D08

D09

D10

D11

D12

D13

D14

D15

SDCLK

CKE

AD03

AD02

VDD33_01

GND3_01

AD01

AD00

AD04

AD05

AD06

AD07

AD08

AD09

ADIN0

117

116

118

120

119

122

123

121

124

125

126

127

128

ADIN0

ADIN1

ADIN2

ADIN3

AVSS33_00

PLLVDD

AVREF33

AVDD33_00

AGND33_00

115

FILTER

CUTXD0

PLLGND

RESETN

CURXD0

MLN7400P_128TQFP

TDO

NRESET

TMS

TCK

TDI

TESTXOSYSCLK

113

112

111

110

114

XO

TDI

TCK

TDO

TMS

TEST

MDIO

MDC

MII_RXD3

MII_RXD2

106

108XI109

107

GND33_06

102

103

104

105

MDC

MDIO

RX_D2

RX_D3

VDD33_06

MII_RXCLK

MII_RXD1

101

RX_D1

MII_RXERR

MII_RXD0

MII_RXDV

99

97

100

98

RX_D0

RX_DV

RX_CLK

RX_ERR

96

TX_CLK

95

TX_EN

94

TX_D0

93

TX_D1

92

TX_D2

91

TX_D3

90

RX_COL

89

RX_CRS

88

SDA

87

SCL

86

GND33_05

85

VDD33_05

GND33_04

VDD33_04

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

GP26_ENWAIT

GP25_IOWR*

GP24_IORD*

GP23_CE2*

GP22_REG*

GP21_EXT_UCLK

GP20_EXIT1

GP19_EXIT_0

GP18_SPICLK

GP17_SPIMOSI

GP16_SPIMISO

GP15_ECSN3

GP14_ECSN2

GP13_NTRST

GP12_TX_ERR

GP11_TOUT(1)

GP10_TOUT(0)

GP09_NBE(1)

VCC_33

MII_TXCLK

MII_TXEN

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_COL

MII_CRS

SDA

SCL

GP26_ENWAIT

GP25_IOWR*

GP24_IORD*

GP23_CE2*

GP22_REG*

GP21_EXTUCLK

GP20_EXINT1

GP19_EXINT0

GP18_SPICLK

GP17_SPIMOSI

GP16_SPIMISO

GP15_ECSN3

GP14_ECSN2

GP13_NTRST

GP12_TXERR

GP11_TOUT1

GP10_TOUT0

GP09_NBE1

VCC_33

0.1uFC17

0.1uFC19

C18 0.1uF

0.1uFC21

C20 0.1uF

0.1uFC23

C22 0.1uF

0.1uFC25

C24 0.1uF

C26 0.1uF

0.1uF

0.1uFC27

C28

47uF

TC4

21

47uF

TC5

21

GROUND

A

B

C

GND33_22

UDQM_AD16

VDD33_02

BA0_AD13

AD10

AD11

AD12

36

33

34

D

35

10

13

11

12

LDQM_AD15

BA1_AD14

39

38

40

37

41

15

14

16

WEN

SDCSN

RASN

EAD17

EAD18

CASN

42

44

43

SDCSN

SDRASN

SDCASN

EAD19_BIG

45

46

47

48

SDWEN

18

19

17

ADDR(20:0)

E

VSS33_03

EWEN

GND33_03

GP00_CUTXD1

GP01_CURXD1

GP02_CUTXD2

EAD20_X8EN

50

49

NEWE

20

ECSN1

EOEN

52

51

55

54

53

NEOE

NECS1

GP03_CURXD2

ECSN0

56

57

58

59

NECS0

GP07_CURXD4

GP04_CUTXD3

60

GP08_NBE0

GP05_CURXD3

GP06_CUTXD4

62

63

64

61

MLN7400P_128TQFP

D

GROUND

GP08_NBE0

GP07_CURXD4

GP06_CUTXD4

GP05_CURXD3

GP04_CUTXD3

GP03_CURXD2

GP02_CUTXD2

GP01_CURXD1

GP00_CUTXD1

DESIGN

CHECK-1

CHECK-2

DATE

CUSTOMER

MCS LOGIC

MLN7400EV

UPDATE SHEET

2003.11.18

E

REV.

3/14

REMARK

Main CPU MLN7400P 128TQFP

12 3

45

6

Page 28

1

2

3

4

56

7

Do not install

Only use when CPU is

A

GP25_IOWR* DDATA

GP24_IORD* DMCK

GP23_CE2* DBCK

GP22_REG* DLRCK

GP42_DDATA DDATA

GP41_DMCK DMCK

GP40_DBCK DBCK

GP39_DLRCK DLRCK

B

GP26_ENWAIT PCMCIA_WAIT*

GP25_IOWR* PCMCIA_IOWR*

GP24_IORD* PCMCIA_IORD*

GP22_REG* PCMCIA_REG*

GP20_EXINT1 PCMCIA_IRQ*

GP23_CE2* PCMCIA_CE2*

GP15_ECSN3 PCMCIA_CE1*

GP37_TOUT2 PCMCIA_RESET_GP37

GP32_HUARTNRTS4 HUARTNRTS4

C

GP31_HUARTNCTS4 HUARTNCTS4

GP07_CURXD4 CURXD4

GP06_CUTXD4 CUTXD4

GP05_CURXD3 CURXD3

GP04_CUTXD3 CUTXD3

GP03_CURXD2 CURXD2

GP02_CUTXD2 CUTXD2

GP01_CURXD1 CURXD1

GP00_CUTXD1 CUTXD1

MLN7400P and need to use

DAC

R9 0

R11

R27

R29 0

R32 0

R34 0

R35 0

R37 0

R39 0

R41 0

R44 0

R46 0

R47 0

0R8

0R10

0

0

0R28

0R30

0R31

0R33

0R36

0R200

0R40

0R42

0R43

0R45

0R48

MLN7400P

DAC I/F

DAC I/F

PCMCIA

I/F

CUART

I/F

GP38_TOUT3 NFIO7

GP37_TOUT2 NFIO6

GP36_EXINT3 NFIO5

GP34_HUARTNDTR4 NFIO4

GP33_HUARTNDSR4 NFIO3

GP32_HUARTNRTS4 NFIO2

GP31_HUARTNCTS4 NFIO1

GP30_HUARTNDCD4 NFIO0

GP18_SPICLK NFRBN

GP17_SPIMOSI NFRDN

GP16_SPIMISO NFCEN

GP07_CURXD4 NFCLEN

GP06_CUTXD4 NFALEN

GP05_CURXD3 NFWRN

GP04_CUTXD3 NFWEN

GP10_TOUT0

OPTIONAL

Install to use

NAND Flash

R12 0

R14 0

R17 0

R19 0

R21 0

R23 0

R24 0

R26 0

R38 0

0R13

0R15

0R16

0R18

0R20

0R22

0R25

TOUT0_TEST

VCC_33

A

NAND

FLASH

I/F

B

JP1

1

JUMP

R644.7K

C

GP13_NTRST NTRST

GP12_TXERR LED0*

GP21_EXTUCLK LED1*

D

GP28_EXTTCLK1 LED2*

GP29_EXTTCLK2 LED3*

GP18_SPICLK SPI_CLK

GP17_SPIMOSI SPI_MOSI

GP16_SPIMISO SPI_MISO

GP11_TOUT1 SPI_SS*

R50 0

R53 0

R55 0

R56 0

0R51

0R52

0R54

0R57

LED

I/F

SPI

I/F

VCC_33

C185

0.1uF

GROUND

GROUND

X3

1

NC

2

GND

1MHZ

VCC

OUT

4

3

TIMER 0

EXTERNAL CLOCK

0R49

VCC_33

R65 33

EXT_TCLK0

R61 0

DESIGN

D

GP27_EXTTCLK0

E

CUSTOMER

MCS LOGIC

E

GP14_ECSN2 NECS2

GP09_NBE1 NBE1_UB

GP08_NBE0 NBE0_LB

R60 0

0R58

0R59

SRAM

I/F

GP35_EXINT2 EXTINT2

GP19_EXINT0 EXTINT0

R62 0

0R63

CHECK-1

CHECK-2

DATE

REMARK

2003.11.18

MLN7400EV

UPDATE SHEET

REV.

4/14

GPIO

12

3

4

5

6

Page 29

1

23

5

6

74

A

IIC EEPROM

SPI EEPROM

A

VCC_33

VCC_33

U3

1

A0

2

A1

3

A2

4

GND

B

S524A40X10

GROUND

VCC

WP

SCL

SDA

8

7

6

5

GROUND

R672K

VCC_33

2K R66

SCL

C186

0.1uF

SPI_SS*

SPI_MISO

SDA

GROUND

GROUND

U4

1

*CS

2

SO

3

*WP

4

GND

VCC

*HOLD

SCK

SI

AT25040

VCC_33

VCC_33

8

7

6

5

SPI_CLK

SPI_MOSI

C187

0.1uF

GROUND

B

External Interrupt Test

VCC_33

VCC_33

RTC

C

SDA

SCL

D

2K R69

R702K

GROUND

U5

18

SDA

SCL

3

ALRM

4

GND

DS1629

VDD

OSC

72

6

X1

5

X2

GROUND

12

3

C3022pF

Y1

XTAL_32_768KHZ_H49S

D1

1N4004

D2

1N4004

12

2

BT1A

22pF C31

BATTERY

1

VCC_33

12

R71 4.7K

C290.1uF

4.7KR68

S1

12

TACT_SW

TC41

1

EXTINT 0

2

1uF

GROUND

21

1uF

GROUND

S2

12

TACT_SW

TC42

EXTINT 2

GROUND

GROUND

EXTINT0

C

EXTINT2

D

GROUND GROUND

GROUND

GROUND

DESIGN

CUSTOMER

E

MCS LOGIC

CHECK-1

E

CHECK-2

DATE

UPDATE

MLN7400EV

SHEET

2003.11/18

REMARK

REV.

5/14

EEPROM & RTC

1

23

45

6

Page 30

12 3

45

VCC_33

67

A

1

14

27

3

9

43

49

ADDR(14:0)

SDCLK

SDCKE

SDCSN

SDRASN

SDCASN

SDWEN

0

1

2

3

4

5

6

7

8

9

10

11

12

14

0

R72

0

R73

0

R74

ADDR(15:0) DATA(15:0)

0

1

2

3

4

5

6

7

8

9

10

11 13

12

13

14

NECS1

NEWE

NEOE

NBE0_LB

NBE1_UB

15

B

U6

1

A0

2

A1

3

A2

4

A3

5

A4

18

A5

19

A6

20

A7

21

A8

24

A9

25

A10

26

A11

27

A12

42

A13

43

A14

44

A15

6

CS*

17

WE*

41

OE*

39

LB*

40

UB*

K6R1016V1D_SRAM

BANK2

I_O10

I_O11

I_O12

I_O13

I_O14

I_O15

I_O16

VCC1

VCC2

VSS1

VSS2

I_O1

I_O2

I_O3

I_O4

I_O5

I_O6

I_O7

I_O8

I_O9

NC1

NC2

NC3

VCC_33

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

VCC_33

0.1uFC32

0.1uFC36

0.1uFC34

C35 0.1uF

C33 0.1uF

0.1uFC38

C39 0.1uF

C37 0.1uF

GROUND

ADDR(15)

ADDR(16)

7

8

9

10

13

14

15

16

29

30

31

32

35

36

37

38

22

23

28

11

33

12

34

GROUND

VDD1

VDD2

VDD3

VDDQ1

VDDQ2

VDDQ3

VDDQ4

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

36

A12

20

A13

21

A14

38

CLK

37

CKE

19

CS*

18

RAS*

17

CAS*

16

WE*

15

DQML

39

DQMH

4MX16_SDRAM

VSS1

VSS2

28

41

U7

VSS3

VSSQ1

VSSQ2

6

54

12

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

42

DQ8

44

DQ9

45

DQ10

47

DQ11

48

DQ12

50

DQ13

51

DQ14

53

DQ15

40

NC

VSSQ3

VSSQ4

46

52

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

DATA(15:0)

VCC_33

C40 0.1uF

0.1uFC41

0.1uFC43

0.1uFC45

C42 0.1uF

C44 0.1uF

C46 0.1uF

TC6

21

10uF_16V

GROUND

A

B

SDRAM BANK

C

GROUND

VCC_33

GND

VCC_33

32

VDD

DATA(15:0)

13

DQ0

14

DQ1

15

DQ2

17

DQ3

18

DQ4

19

DQ5

20

DQ6

21

DQ7

16

0

1

2

3

4

5

6

7

GROUND

ADDR(20:0)

VCC_33

GROUND

NCS_AMD

NEOE

NEWE

NRESET

37

13

0

4.7K

0

25

24

23

22

21

20

19

18

8

7

6

5

4

3

2

1

48

17

16

9

10

15

47

14

26

28

11

12

U8

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

RY_BY#

BYTE_VCCQ

*WP

*CE

*OE

*WE

*RST

VPP

VCC

29

D0

31

D1

33

D2

35

D3

38

D4

40

D5

42

D6

44

D7

30

D8

32

D9

34

D10

36

D11

39

D12

41

D13

43

D14

45

D15

VSS1

VSS2

AM29LV160BB

46

27

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

R77

R78

R80

ADDR(18:0)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

NECS0

NEOE

NEWE

15

16

17

18

D

U9

12

A0

11

A1

10

A2

9

A3

8

A4

7

A5

6

A6

5

A7

27

A8

26

A9

23

A10

25

A11

4

A12

28

A13

29

A14

3

A15

2

A16

30

A17

1

A18

22

CE*

24

OE*

31

WE*

AT29C040A

BANK0

E

BANK1

GROUND

FLASH

AMD Flash

BANK

Selection

NCS_AMDDATA(15:0)

ADDR(20)

VCC_33

4.7K

R76

DESIGN

CHECK-1

CHECK-2

DATE

REMARK

SW2

1

2

3

4

5

6

SW_DPDT

2003.11.18

BOSIZE : 8 Bit

BOSIZE : 16Bit

X8

NECS2

NECS0

4.7K

1K

VCC_33

R75

R79

X16

GROUND

CUSTOMER

MCS LOGIC

MLN7400EN

UPDATE SHEET

MEMORY

C

D

E

REV.

6/14

12

3

45

6

Page 31

1

32 6

4

5

7

A

VCCPLL

VCC_25

VCC_33

GROUND

0.1uF C183

VCC_25

VCC_25

R9049.9

R9249.9

49.9 R91

49.9 R89

0.1uF C50

GROUND

C511uF_1608

VCC_25

U11

TCMT

RCMTRDC

H1102

21

16

TXP

15

14

TXN

13

NC3

12

NC4

11

RXP

10

9

RXN

R104 75

R106 75

C56

0.01uF_2KV

75R103

75R105

1

TXDP

2

TDC

3

TXDN

4

NC1

5

NC2

6

RDP

7

8

RDN

C541uF_1608

1uF_1608 C55

J1

1

2

3

4

5

6

7

8

RJ45

9

10

11

12

13

14

VCC_25

R94500

500 R93

LED_LNK

LED_SPD

FGND

VCC_25

21

GROUND

TC9

Place close to

C570.01uF

pin32 0f AC101L

2.2uF

GROUND

GROUND

FGND

37

GND8

ANEN_LED3

24

GROUND

GND7

VCC25OUT

VCCPLL

SD_FXEN

PDOWN*

VCC_33

75 R84

27pF C49

36

35

TXP

34

TXN

33

GND6

32

31

RBIAD

30

GND5

29

GND4

28

27

RXP

26

RXN

25

VCC4

PHYADCO4

PHYADCO3

PHYADCO2

PHYADCO1

PHYADCO0

4

3

GROUND

R109

R111 4.7K

R113 4.7K

NC_VDD

X2_OUT

XTAL_OSC_25MHZ

21

GROUND

4.7KR108

4.7K

4.7KR110

4.7KR112

4.7KR114

TC822uF

VCC_25

GROUND

Y2

NC_GND

VCC_25

C520.1uF

GROUND

1

X1_OE

2

C53

1uF_1608

4.7K R101

GROUNDGROUND

GROUND

R10210K

VCC_33

VCC_25

C480.1uF

U10

1

2

3

4

5

6

7

8

9

10

11

12

VCC_25

21

10uF TC7

48

PHYAD4_RXD0

VCC1

GND1

RXDV_CRSDV

RMII_MODEL_RXC

ISOLATE_RXER

GND2

VCC2

TXER

TXC

TXEN

TXD0

TXD1

TXD2

13

GROUND

R118 4.7K

R120 4.7K

0.01uF C47

GROUND

41

40

39

42

44

43

45

46

47

MDC

PHYAD1_RXD3

PHYAD2_RXD2

PHYAD3_RXD1

AC101L

REPEATER_CRS

TXD3

GND3

COL

18

16

14

17

15

4.7KR117

4.7KR119

38

XI

XO

RST*

MDIO

VCC33IN

VCC3

SPD100_LED1

BURNIN*_L_LED0

DUPLEX_LED2

PHYAD0_INTR

21

23

20

22

19

LED_SPD

LED_LNK

R814.7K

R831K

GROUND

NRESET

MDIO

B

MDC

MII_RXD3

MII_RXD2

MII_RXD1

MII_RXD0

R86 33

R88 33

1K R82

33R85

33R87

PHYADCO3

PHYADCO2

PHYADCO1

PHYADCO0

VCC_25

MII_RXDV

MII_RXCLK

MII_RXERR

R95 33

R97 33

33R96

R994.7K

C

4.7K R98

4.7K R100

GROUND

MII_TXCLK

MII_TXEN

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_COL

MII_CRS

D

33R107

R1154.7K

4.7K R116

GROUND

GROUND

A

B

C

D

E

DESIGN

CHECK-1

CHECK-2

21

TC10

2.2uF

C590.01uF

0.01uF C58

C610.01uF

0.01uF C60

0.01uF C62

C640.1uF

0.1uF C63

C660.1uF

0.1uF C65

E

CUSTOMER

MCS LOGIC

REV.

MLN7400EV

GROUND

Place close to

pins 0f AC101L

DATE

REMARK

2003.11.18

UPDATE

SHEET

7/14

AC101L ETHERNET PHY

1

23

4

5

6

Page 32

1

2

3

4

65

7

P1

1

6

VCC_33

U12

1

3

11 14

10 7

4

5

MAX3232

VCC

C1+

C1-

T1I

T1O

R1O

T2I

T2O

R2O

C2+

C2- GND

V+

R1I

R2I

V-

16

2

1312

89

6

15

TC11

21

1uF TC14

21

1uF

GROUND

C67330pF

C69330pF

330pF C68

330pF C70

CUTXD0

CURXD0

CUTXD1

CURXD1

1uF TC12

21

TC131uF

21

GROUND

B

GROUND

2

7

3

8

4

9

5

DB9_FEMALE

P2

1

6

2

7

3

8

4

9

5

DB9_FEMALE

UART0

AA

UART1

B

GROUND

P3

1

6

VCC_33

TC161uF

21

C

CUTXD2

CURXD2

CUTXD3

CURXD3

1uF TC17

21

U13

1

C1+

3

C1-

11

T1I T1O

12

10

T2I T2O

9

4

C2+

515

C2-

MAX3232

VCC

GND

16

2

14

13

7

8

6

TC15 1uF

21

21

GROUND

TC181uF

C72330pF

330pF C71

C74330pF

330pF C73

V+

R1IR1O

R2IR2O

V-

GROUND

GROUND

2

7

3

8

4

9

5

DB9_FEMALE

P4

1

6

2

7

3

8

4

9

5

DB9_FEMALE

UART2

C

UART3

GROUND

P5

1

GROUND

6

2

7

3

8

4

9

5

DB9_FEMALE

P6

1

6

2

7

3

8

4

9

5

DB9_MALE

D

VCC_33

1uF TC20

21

CUTXD4

CURXD4

HUARTNRTS4

HUARTNCTS4

TC211uF

21

E

U14

1

C1+

3

C1-

11 14

T1I

R1O

10 7

T2I

R2O

4

C2+

5

C2- GND

MAX3232

VCC

T1O

T2O

16

2

V+

1312

R1I

89

R2I

6

V-

15

1uFTC19

21

1uF TC22

21

C76

C75330pF

C77330pF

330pF

330pF C78

GROUND

GROUND

GROUND

1

2

3

45

UART4

HUART

OPTION

D

E

CUSTOMERDESIGN

MCS LOGIC

CHECK-1

CHECK-2

DATE

UPDATE

MLN7400EV

SHEET

2003.11.18

REMARK

6

RS232

REV.

8/14

Page 33

1

2

3

4

56

7

VCC_33

4.7K R124

ADDR(11:0)

DATA(15:0)

R1254.7K

4.7K R126

0

1

2

3

4

5

6

7

8

9

10

11

0

1

2

3

4

5

6

7

8

9

10

R1284.7K

11

12

13

14

15

4.7K R127

29

A0

28

A1

27

A2

26

A3

25

A4

24

A5

23

A6

22

A7

12

A8

11

A9

8

A10

10

A11 A12

30

D0

31

D1

32

D2

2

D3

3

D4

4

D5

5

D6

6

D7

64

D8

65

D9

66

D10

37

D11

38

D12

39

D13

40

D14

41

D15

58

RESET

7

CE1*

42

CE2*

9

OE*

15

WE*_PGM*

44

IORO*

45

IOWR*

61

REG*

67

CD2*

36

CD1*

59

WAIT*

16

RDY*_IREQ*

57

VS2*

43

VS1*

62

BVD2*_SPKR

63

BVD1*_STSCHG

60

INPACK*

33

WP*_IOIS16*

VCC0

VCC1

VPP2

VPP1

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

GND0

GND1

GND2

GND3

17

51

52

18

21

13

14

20

19

46

47

48

49

50

53

54

55

56

R1304.7K

4.7K R129

R1324.7K

4.7K R131

R1344.7K

R1354.7K

4.7K R133

4.7K R136

R1384.7K

4.7K R137

4.7K R139

R1414.7K

4.7K R140

4.7K R142

GROUND

VCC_33

TC23

47uF

21

TC24

21

47uF

C800.1uF

68

35

34

1

0.1uF C79

J2

A

B

VCC_33

R1234.7K

PCMCIA_RESET_GP37

R1214.7K

0R201

4.7K R122

C

PCMCIA_RESET

R202 0

PCMCIA_CE1*

PCMCIA_CE2*

NEOE

NEWE

PCMCIA_IORD*

PCMCIA_IOWR*

PCMCIA_REG*

PCMCIA_WAIT*

D

PCMCIA_IRQ*

PCMCIA_68PIN_CONN

DESIGN

CUSTOMER

A

B

C

D

E

MCS LOGIC

BANK3

E

4.7K R143

GROUND

GROUND

CHECK-1

CHECK-2

REV.

MLN7400EV

DATE

2003.11.18

GROUND

1

2

3

4

5

REMARK

PCMCIA INTERFACE

6

UPDATE SHEET

9/14

Page 34

1

2

3 5

4

6

7

RESET SYSTEM

3

VCC_33

GROUND

VCC_33

C820.1uF

0.1uF C81

GROUND

NTRST

A

VCC_33

RESET

R14810K

D3

VCC_33

1N4148

12

1

TC25

10uF

21

S3

12

B

SW_RESET

14 Pin : VCC_33

7 Pin : Ground

GROUND

U15

74LVC14

2

3

VCC_33

U15

74LVC14

4

10K R149

NRESET

VCC_33

U16

14

1

R1504.7K

2

7

74LV08

14 Pin : VCC_33

GROUND

7 Pin : Ground

GPIO LED

LED0*

LED1*

LED2*

LED3*

VCC_33

330 R144

D4 LED

VCC_33

R145330

LEDD5

VCC_33

330 R146

D6 LED

VCC_33

R147330

LEDD7

A

B

JTAG CONNECTOR

C

J3

2

10

20

HEADER2X10

D

GROUND

VCC_33

1

34

56

78

9

1112

1314

1516

1718

19

NTRST_JTAG

TDI

TMS

TCK

TDO

NRESET

VCC_5IN

SW3

J4

PWR_JACK

1

A1

B1

B2

2

A2

B3

3

A3

TC27

100uF_16V

21

1

2

3

SW_TOGGLE

E

21

GROUND

NRESET

21

TC26

10uF

TC33

100uF_16V

U15

VCC_5

1

2

74LVC14

6

TC28

10uF

3

U17

IN

PCMCIA_RESET

2

OUT

4

TAB

GND

1

AMS1086

TC29

10uF

VCC_33

21

C83

C85

0.1uF

0.01uF

21

TC31

100uF

DESIGN

CHECK-1

CHECK-2

5

POWER LED

C

VCC_33

330 R151

D

D8 LED

GROUND

E

CUSTOMER

MCS LOGIC

REV.

MLN7400EV

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

DATE UPDATE

2003.11.18

REMARK

SHEET

10/14

POWER&RESET

1

23

4

5

6

Page 35

1

32

54

6

7

DATA(15:0)

VCC_33

A

JP3

25 26

23 24

14

12

10

8

6

4

2

0

B

21 22

20

19

17 18

15 16

13 14

11 12

10

9

78

56

34

1

2

HEADER2X13

15

13

11

9

7

5

3

1

GROUNDGROUND

DATA

HEADER

ADDR(20:0)

20

18

16

14

12

C

10

8

6

4

2

0

JP6

25 26

23 24

21 22

19220

18

17

15 16

13 14

11 12

9

10

78

56

34

1

HEADER2X13

19

17

15

13

11

9

7

5

3

1

MII_TXCLK

MII_TXEN

MII_TXD3

MII_TXD2

MII_TXD1

MII_TXD0

SDA

SCL

MDC

MDIO

VCC_33

GROUND

VCC_33

VCC_33

JP2

12

34

56

78

HEADER2X4

IIC & SPI

HEADER

JP4

25 26

23 24

21 22

19220

17 18

15 16

13 14

11 12

9

10

78

56

4

3

1

HEADER2X13

MII I/F

HEADER

SPI_CLK

SPI_MOSI

SPI_MISO

SPI_SS*

VCC_33

JP5

1

2

GP06_CUTXD4 GP31_HUARTNCTS4

GP07_CURXD4

GP30_HUARTNDCD4

34

6

5

78

9

10

11 12

HEADER2X6

GP32_HUARTNRTS4

GP33_HUARTNDSR4

GP34_HUARTNDTR4

A

B

GROUND

GROUND

HIGH SPEED

TP2

TP_040

UART

HEADER

TP3 TP4

TP_040

TP_040

TP5

TP_040

VCC_33

TP6

TP_040

C

MII_CRS

MII_COL

MII_RXERR

MII_RXCLK

MII_RXDV

MII_RXD3

MII_RXD2

MII_RXD1

MII_RXD0

GROUNDGROUND

TP1

TP_040

GROUNDGROUND

ADDRESS

HEADER

GP42_DDATA

VCC_33

D

JP8

25 26

23 24

21 22

19220

SDCASN

SDRASN

SDWEN

SDCSN

SDCKE

SDCLK

E

17 18

15 16

13 14

11 12

9

10

78

56

34

1

HEADER2X13

GROUNDGROUND

GP15_ECSN3

GP14_ECSN2

GP09_NBE1

GP08_NBE0

NEOE

NEWE

NECS1

NECS0

GP40_DBCK

GP38_TOUT3

GP36_EXINT3

GP34_HUARTNDTR4

GP32_HUARTNRTS4

GP30_HUARTNDCD4

GP28_EXTTCLK1

GP26_ENWAIT

GP24_IORD*

GP22_REG*

GP20_EXINT1

GP18_SPICLK

GP16_SPIMISO

GP14_ECSN2

GP12_TXERR

GP10_TOUT0

GP08_NBE0

GP06_CUTXD4

GP04_CUTXD3

GP02_CUTXD2

GP00_CUTXD1

GP0~

EVEN

GPIO

GROUND GROUND

MEMORY

HEADER

JP7

47 48

45 46

43 44

41 42

39440

37 38

36

35

33 34

31 32

29330

27 28

25 26

23 24

21 22

20

19

17 18

15 16

13 14

11 12

10

9

78

5

6

1

2

HEADER24x2

GPIO

HEADER

GP41_DMCK

GP39_DLRCK

GP37_TOUT2

GP35_EXINT2

GP33_HUARTNDSR4

GP31_HUARTNCTS4

GP29_EXTTCLK2

GP27_EXTTCLK0

GP25_IOWR*

GP23_CE2*

GP21_EXTUCLK

GP19_EXINT0

GP17_SPIMOSI

GP15_ECSN3

GP13_NTRST

GP11_TOUT1

GP09_NBE1

GP07_CURXD4

GP05_CURXD3

GP03_CURXD2

GP01_CURXD1

GP1~

ODD

GPIO

GROUND

DESIGN

CHECK-1

CHECK-2

DATE

REMARK

2003.11.18

CUSTOMER

MCS LOGIC

MLN7400EV

D

E

REV.

SHEETUPDATE

11/14

Test Header Pin

21

3

54

6

Page 36

1 5

32

4

6

7

VCC_33A

VCC_33A

A

R152 1K

SW4

2

1

TACT_SW

PLAY

270R155

SW7

12

TACT_SW

STOP

B

SW10

12

TACT_SW

SKIP+

SW13

12

TACT_SW

SKIP-

R158 390560R162

1KR153

SW5

12

TACT_SW

PGM

SW8

2

1

TACT_SW

MENU

SW11

12

TACT_SW

ESP

SW14

12

TACT_SW

ENTER

R156 270

390R159

R161 560

C

AGND

SW15

12

TACT_SW

MODE

AGND

R163 820

J5

3

2

D

1

MICIN

MIC

VCC_33A

R167 2.2K

R154 1K

SW6

12

TACT_SW

EQ

SW9

12

TACT_SW

VOL_UP

SW12

12

TACT_SW

VOL_DN

AGND

R164 1K

21

270R157

R160 390

TC3410uF

AGND

A

ADIN2ADIN1ADIN0

B

VCC_33A

C188

0.1uF

8

7

6

VCC_33A

AGND

SHDN

ADIN3

SW16

2

5

SW_DPDT

1

3

4

6

R166 4.7K

100KR165

U18

1

GND

2

INP

3

INN

45

MBIAS

C87 0.01uF

R169 100K

AGND

OUT

VCC

SHDN

NC

MAX4468EKA_SOP8

VCC_33A

MUTE

Enable

1KR168

MUTE

Disable

AGND

C

MUTE

SW

100KR170

R171 20KC89 0.1uF

47pFC88

D

JACK

E

DESIGN

AGND

E

CHECK-1

CHECK-2

CUSTOMER

MCS LOGIC

REV.

MLN7400EV

DATE

REMARK

2003.11.18

UPDATE

SHEET

12/14

KEY MATRIX & MIC IN

1

2

3

4

5

6

Page 37

2

5

671 34

A

B

TC36

21

3.3uF

21

3.3uFTC35

R172 560

10KR173R175 10K

AGND

A

C901uF_1608

J6

B

560R174

AOUTR

AOUTL

3

2

VCC_33A

1

C

0R176

AOUTR_S

AOUTL_S

1uF_1608 C91

AGND

LINE_OUT_JACK

C

U20

NRESET

R177 0

DDATA

DBCK

DLRCK

DMCK

D

1

RST*

2

SDATA

3

SCLK

4

LRCK

5

MCLK

6

DIF1

7

DIF0

8

DEM0

MUTEC

AOUTL

AGND

AOUTR

REF_GND

VA

VQ

FILT+

16

15

14

13

12

11

10

9

CS4340

AGND

D

TC38

C920.1uF

C94

21

1uF TC39

21

0.1uF

1uF

0.1uF C93

R178 100

E

AGND

AGND

AGND

AGND

21

1uF TC37

AGND

DESIGN

CHECK-1

CHECK-2

DATE

REMARK

2003.11.18

CUSTOMER

UPDATE

MCS LOGIC

MLN7400EV

SHEET

E

REV.

13/14

DAC

1

2

3

4

5

6

Page 38

1

2

34

567

A

A

VCC_33

NAND_Flash

U21

IO7

IO6

IO5

IO4

IO3

IO2

IO1

IO0

48

47

46

45

44

43

42

41

40

39

38

37

35

34

33

32

31

30

29

28

27

26

25

NFIO7

NFIO6

NFIO5

NFIO4

NFPIN38

NFIO3

NFIO2

NFIO1

NFIO0

GROUND

B

VCC_33

C

C97 0.1uF

GROUND

D

1

NC1

2

3KR179

B

NFPIN6

NFRBN

VCC_33

NFRDN

NFCEN

C

C95 100pF

0.1uFC96

NFCLEN

GROUND

NFALEN

NFWRN

NFWEN

R180 0

NFPIN6

D

GROUND

GROUND

NC2

3

NC3

4

NC4

5

NC5

6

GND1

7

R_BN

8

REN

9

CEN

10

NC6

11

NC7

12

VCC1 VCC2

13 36

VSS1

14

NC8

15

NC9

16

CLE

17

ALE

18

WEN

19

WPN

20

NC10

21

NC11

22

NC12

23

NC13

24

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

VSS2

NC22

NC23

NC24

NC25

NC26

NC27

NC28

0R181

NFPIN38

GROUND

E

1

2

3

K9F2808_YCB0

4

E

DESIGN

CHECK-1

CHECK-2

DATE

2003.11.18

REMARK

5

6

CUSTOMER

MCS LOGIC

MLN7400

UPDATE SHEET

NAND FLASH

REV.

14/14

Loading...

Loading...