ACTEL 54SX User Manual

54SX Family FPGAs

v3.1

Leading Edge Performance

• 320 MHz Internal Performance

• 3.7 ns Clock-to-Out (Pin-to-Pin)

• 0.1 ns Input Set-Up

• 0.25 ns Clock Skew

Specifications

• 12,000 to 48,000 System Gates

• Up to 249 User-Programmable I/O Pins

• Up to 1080 Flip-Flops

• 0.35µ CMOS

Features

• 66 MHz PCI

• CPLD and FPGA Integration

• Single Chip Solution

• 100% Resource Utilization with 100% Pin Locking

• 3.3V Operation with 5.0V Input Tolerance

• Very Low Power Consumption

• Deterministic, User-Controllable Timing

• Unique In-System Diagnostic and Debug capability with

Silicon Explorer II

• Boundary Scan Testing in Compliance with IEEE Standard

1149.1 (JTAG)

• Secure Programming Technology Prevents Reverse

Engineering and Design Theft

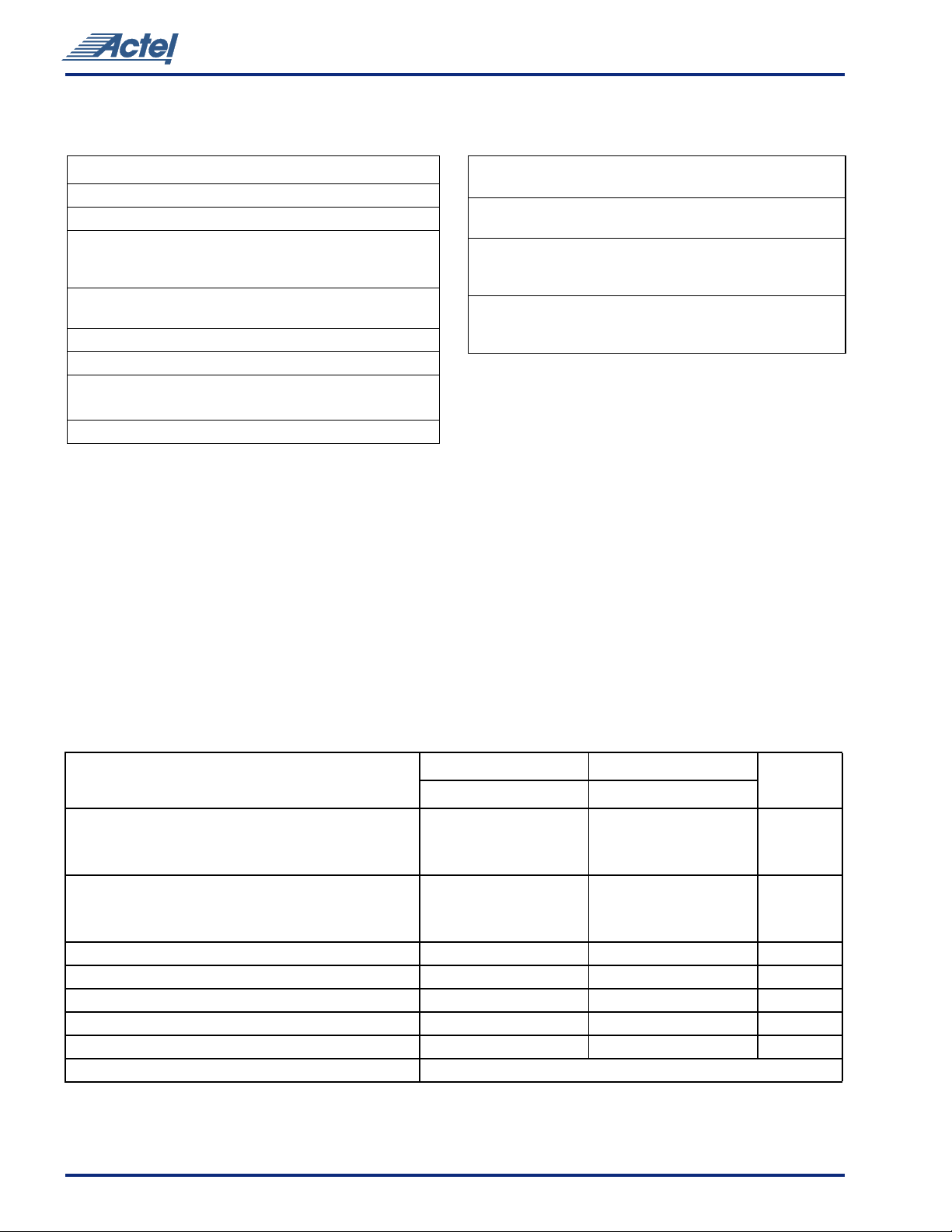

SX Product Profile

A54SX08 A54SX16 A54SX16P A54SX32

Capacity

Typical Gates

System Gates

Logic Modules

Combinatorial Cells

Register Cells (Dedicated Flip-Flops) 256 528 528 1,080

Maximum User I/Os 130 175 175 249

Clocks 3333

JTAG YesYesYesYes

PCI ——Yes—

Clock-to-Out 3.7 ns 3.9 ns 4.4 ns 4.6 ns

Input Set-Up (External) 0.8 ns 0.5 ns 0.5 ns 0.1 ns

Speed Grades Std, –1, –2, –3 Std, –1, –2, –3 Std, –1, –2, –3 Std, –1, –2, –3

Temperature Grades C, I, M C, I, M C, I, M C, I, M

Packages (by pin count)

PLCC

PQFP

VQFP

TQFP

PBGA

FBGA

8,000

12,000

768

512

84

208

100

144, 176

—

144

16,000

24,000

1,452

924

—

208

100

176

—

—

16,000

24,000

1,452

924

—

208

100

144, 176

—

—

32,000

48,000

2,880

1800

—

208

—

144, 176

313, 329

—

June 2003 1

© 2003 Actel Corporation

General Description

Actel’s SX family of FPGAs features a sea-of-modules

architecture that delivers device performance and

integration levels not currently achieved by any other FPGA

architecture. SX devices greatly simplify design time, enable

dramatic reductions in design costs and power

consumption, and further decrease time to market for

performance-intensive applications.

Actel’s SX architecture features two types of logic modules,

the combinatorial cell (C-cell) and the register cell (R-cell),

each optimized for fast and efficient mapping of synthesized

logic functions. The routing and interconnect resources are

in the metal layers above the logic modules, providing

optimal use of silicon. This enables the en tire floor of the

device to be spanned with an uninterrupted grid of

fine-grained, synthesis-friendly logic modules (or

“sea-of-modules”), which reduces the distance signals have

to travel between logic modules. To minimize signal

propagation delay, SX devices employ both local and general

routing resources. The high-speed local routing resources

(DirectConnect and FastConnect) enable very fast local

signal propagation that is optimal for fast counters, state

54SX Family FPGAs

machines, and datapath logic. The general system of

segmented routing tracks allows any logic module in the

array to be connected to any other logic or I/O module.

Within this system, propagation delay is minimized by

limiting the number of antifuse interconnect elements to

five (90 percent of connections typically use only three

antifuses). The unique local and general routing structure

featured in SX devices gives fast and predictable

performance, allows 100percent pin-locking with full logic

utilization, enables concurrent PCB development, reduces

design time, and allows designers to achieve performance

goals with minimum effort.

Further complementing SX’s flexible routing structure is a

hard-wired, constantly loaded clock network that has been

tuned to provide fast clock propagation with minimal clock

skew. Additionally, the high performance of the internal

logic has eliminated the need to embed latches or flip-flops

in the I/O cells to achieve fast clock-to-out or fast input

set-up times. SX devices have easy-to-use I/O cells that do

not require HDL instantiation, facilitating design re-use and

reducing design and verification time.

Ordering Information

A54SX16 – PQ 208

P

2

Application (Temperature Range)

Blank = Commercial (0 to +70°C)

I = Industrial (–40 to +85°C)

M = Military (–55 to +125°C)

PP = Pre-production

Package Lead Count

Package Type

BG = Ball Grid Array

PL = Plastic Leaded Chip Carrier

PQ = Plastic Quad Flat Pack

TQ = Thin (1.4 mm) Quad Flat Pack

VQ = Very Thin (1.0 mm) Quad Flat Pack

FG = Fine Pitch Ball Grid Array (1.0 mm)

Speed Grade

Blank = Standard Speed

–1 = App roximately 15% Faster than Standard

–2 = App roximately 25% Faster than Standard

–3 = Approximately 35% Faster than Standard

Blank = Not PCI Compliant

P = PCI Compliant

Part Number

A54SX08 = 12,000 System Gates

A54SX16 = 24,000 System Gates

A54SX16P = 24,000 System Gates

A54SX32 = 48,000 System Gates

2 v3.1

54SX Family FPGAs

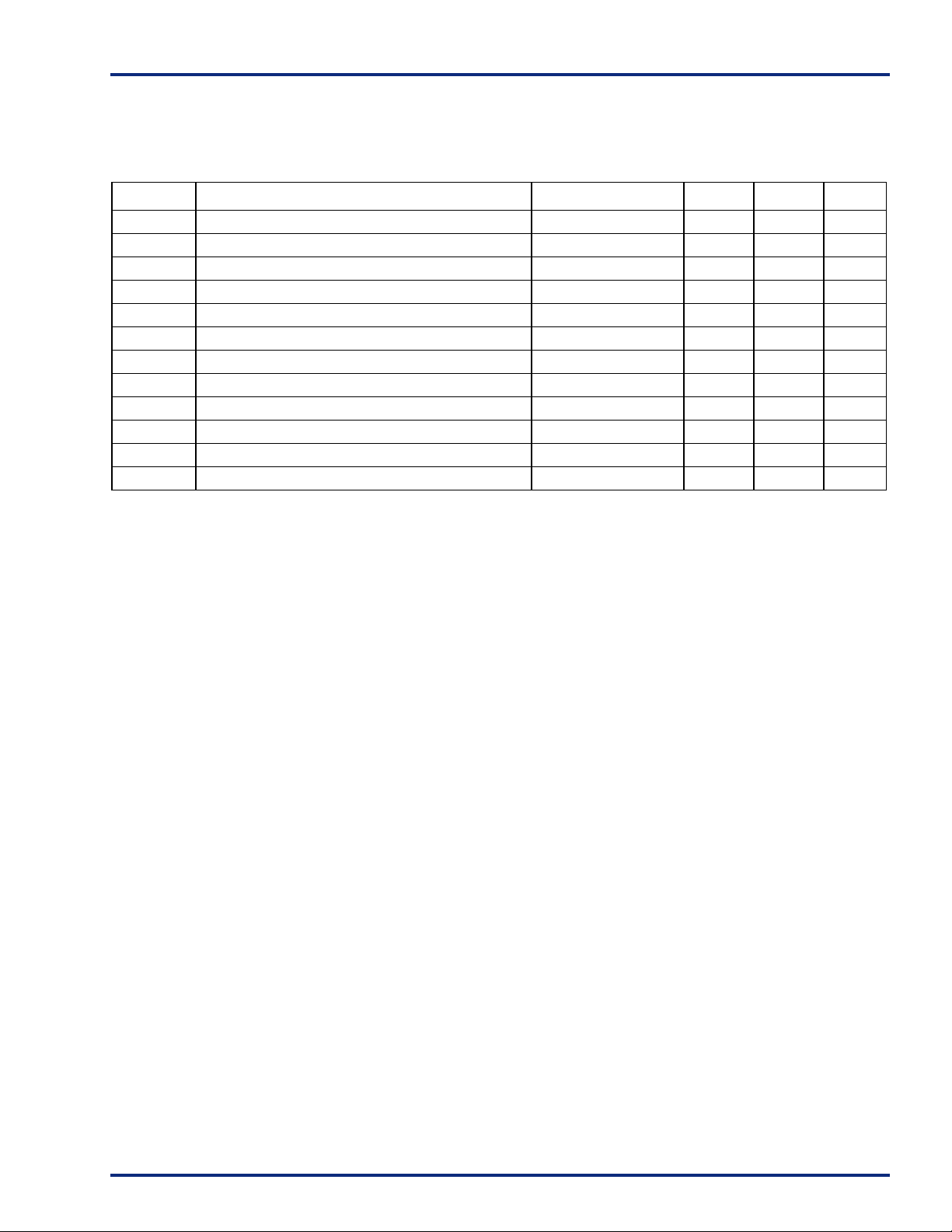

Product Plan

Speed Grade* Application

Std–1–2–3 C I†M

A54SX08 Device

84-Pin Plastic Leaded Chip Carrier (PLCC) ✔✔✔✔ ✔✔—

100-Pin Very Thin Plastic Quad Flat Pack (VQFP) ✔✔✔✔ ✔✔—

144-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔—

144-Pin Fine Pitch Ball Grid Array (FBGA) ✔✔✔✔ ✔✔—

176-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔—

208-Pin Plastic Quad Flat Pack (PQFP) ✔✔✔✔ ✔✔—

A54SX16 Device

100-Pin Very Thin Plastic Quad Flat Pack (VQFP) ✔✔✔✔ ✔✔P

176-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔P

208-Pin Plastic Quad Flat Pack (PQFP) ✔✔✔✔ ✔✔P

A54SX16P Device

100-Pin Very Thin Plastic Quad Flat Pack (VQFP) ✔✔✔✔ ✔✔—

144-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔—

176-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔—

208-Pin Plastic Quad Flat Pack (PQFP) ✔✔✔✔ ✔✔—

A54SX32 Device

144-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔P

176-Pin Thin Quad Flat Pack (TQFP) ✔✔✔✔ ✔✔P

208-Pin Plastic Quad Flat Pack (PQFP) ✔✔✔✔ ✔✔P

313-Pin Plastic Ball Grid Array (PBGA) ✔✔✔✔ ✔✔—

329-Pin Plastic Ball Grid Array (PBGA) ✔✔✔✔ ✔✔—

Contact your Actel sales representative for product availability.

Applications:C = CommercialAvailability:✔ = Available*Speed Grade:–1 = Approx. 15% faster than Standard

I = Industrial P = Planned –2 = Approx. 25% faster than Standard

M = Military — = Not Planned –3 = Approx. 35% faster than Standard

† Only Std, –1, –2 Speed Grade

Only Std, –1 Speed Grade

•

•

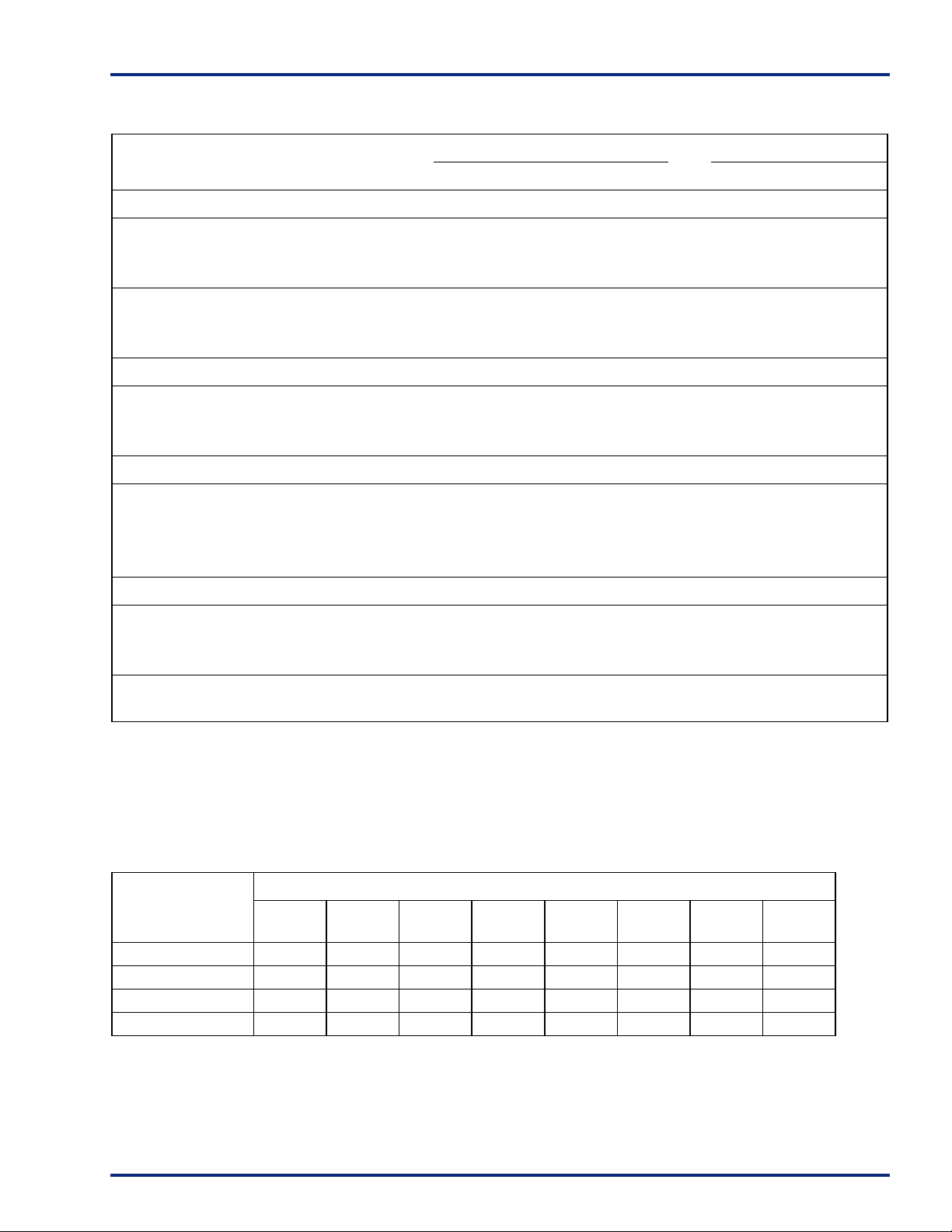

Plastic Device Resources

User I/Os (including clock buffers)

Device

84-Pin

A54SX08 69 81 130 113 128 — — 111

A54SX16 — 81 175 — 147 — — —

A54SX16P — 81 175 113 147 — — —

A54SX32 — — 174 113 147 249 249 —

Package Definitions (Consult your local Actel sales representative for product availability.)

PLCC = Plastic Leaded Chip Carrier, PQFP = Plastic Quad Flat Pack, TQFP = Thin Quad Flat Pack, VQFP = Very Thin Quad Flat Pack,

PBGA = Plastic Ball Grid Array, FBGA = Fine Pitch (1.0 mm) Ball Grid Array

PLCC

VQFP

100-Pin

PQFP

208-Pin

TQFP

144-Pin

v3.1 3

TQFP

176-Pin

PBGA

313-Pin

PBGA

329-Pin

FBGA

144-Pin

SX Family Architecture

The SX family architecture was designed to satisfy

next-generation performance and integration requirements

for production-volume designs in a broad range of

applications.

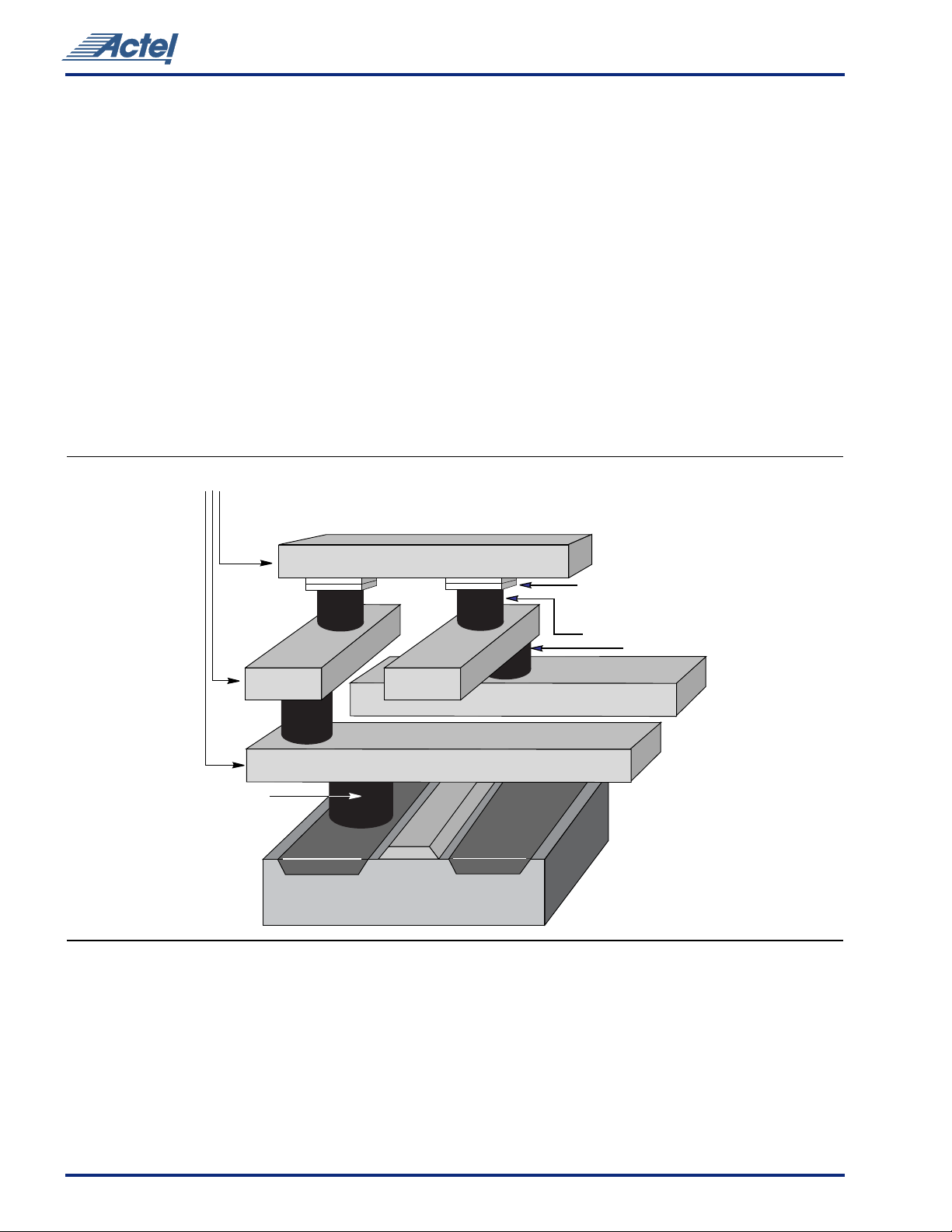

Programmable Interconnect Elemen t

The SX family provides efficient use of silicon by locating the

routing interconnect resources between the Metal 2 (M2)

and Metal 3 (M3) layers (Figure1). This completely

eliminates the channels of routing and interconnect

resources between logic modules (as implemented on SRAM

FPGAs and previous generations of antifuse FPGAs), and

enables the entire floor of the device to be spanned with an

uninterrupted grid of logic modules.

Interconnection between these logic modules is achieved

using Actel’s patented metal-to-metal programmable

Routing T rac ks

54SX Family FPGAs

antifuse interconnect elements, which are embedded

between the M2 and M3 layers. The antifuses are normally

open circuit and, when programmed, form a permanent

low-impedance connection.

The extremely small size of these interconnect elements

gives the SX famil y abundant routing resources and provides

excellent protection against design pirating. Reverse

engineering is virtually impossible because it is extremely

difficult to distinguish between programmed and

unprogrammed antifuses, and there is no configuration

bitstream to intercept.

Additionally, the interconnect (i.e., the antifuses and metal

tracks) have lower capacitance and lower resistance than

any other device of similar capacity, leading to the fastest

signal propagation in the industry.

Metal 3

Metal 2

Metal 1

Tungsten Plug

Contact

Silicon Substrate

Figure 1 • SX Family Interconnect Elements

Logic Module Design

The SX family architecture is described as a

“sea-of-modules” architecture because the entire floor of

the device is covered with a grid of logic modules with

virtually no chip area lost to interconnect elements or

routing. Actel’s SX family provides two types of logic

modules, the register cell (R-cell) and the combinatorial

cell (C-cell).

Amorphous Silicon/

Dielectric Antifuse

Tungsten Plug Via

Tungsten Plug Via

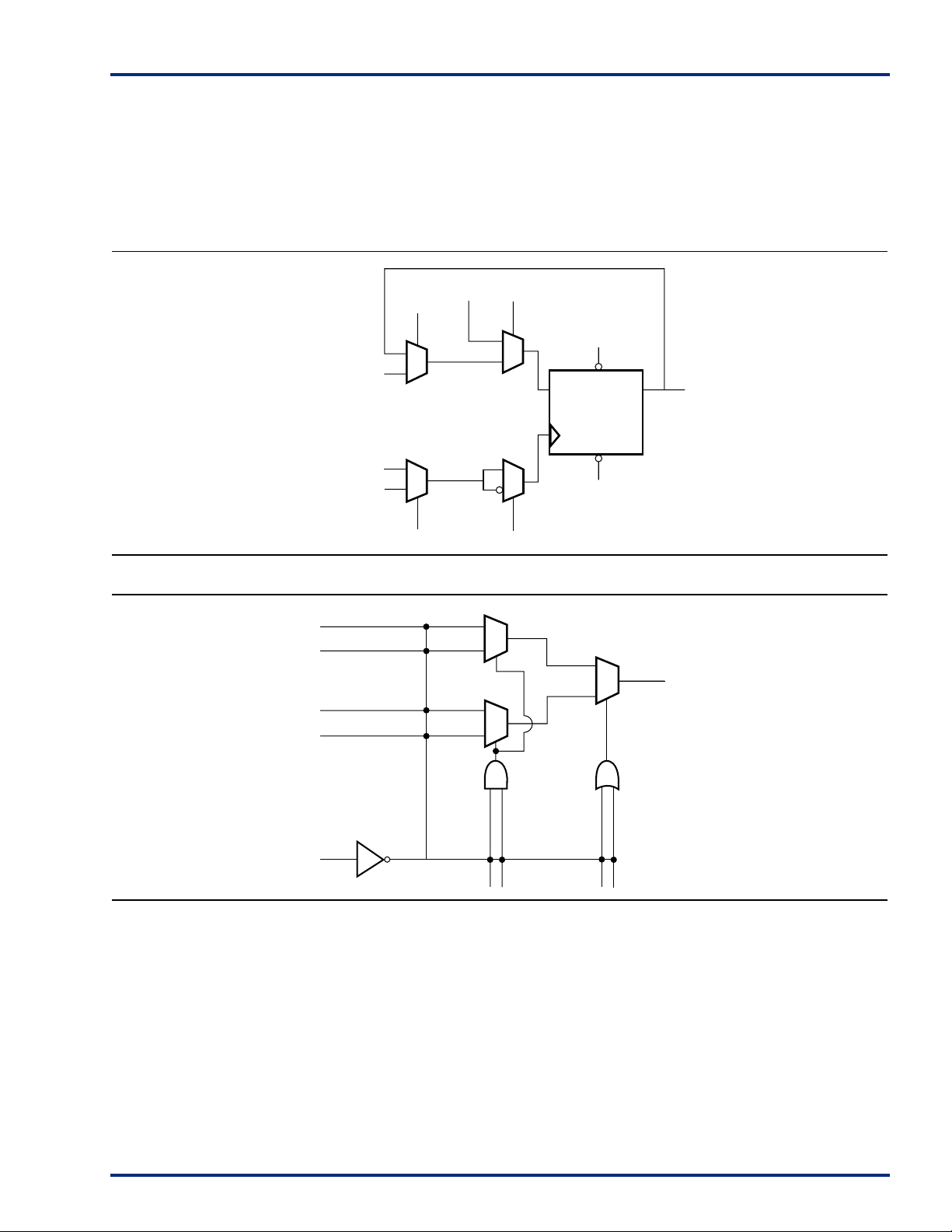

The R-cell contains a flip-flop featuring asynchronous clear,

asynchronous preset, and clock enable (using the S0 and S1

lines) control signals (Figure 2 on page5). The R-cell

registers feature programmable clock polarity selectable on

a register-by-register basis. This provides additional

flexibility while allowing mapping of synthesized functions

into the SX FPGA. The clock source for the R-cell can be

chosen from either the hard-wired clock or the routed clock.

4 v3.1

54SX Family FPGAs

The C-cell implements a range of combinatorial functions

up to 5-inputs (Figure 3). Inclusion of the DB input and its

associated inverter function dramatically increases the

number of combinatorial functions that can be

implemented in a single module from 800 options in

previous architectures to more than 4,000 in the SX

architecture. An example of the improved flexibility

Routed

Data Input

S0

Direct

Connect

Input

HCLK

CLKA,

CLKB,

Internal Logic

CKS CKP

enabled by the inversion capability is the ability to integrate

a 3-input exclusive-OR function into a single C-cell. This

facilitates construction of 9-bit parity-tree functions with 2

ns propagation delays. At the same time, the C-cell

structure is extremely synthesis friendly, simplifying the

overall design and reducing synthesis time.

S1

PSETB

YDQ

CLRB

Figure 2 • R-Cell

D0

D1

D2

D3

DB

A0 B0 A1 B1

Figure 3 • C-Cell

Chip Architecture

The SX family’s chip architecture provides a unique

approach to module organization and chip routing that

delivers the best register/logic mix for a wide variety of new

and emerging applications.

Module Organization

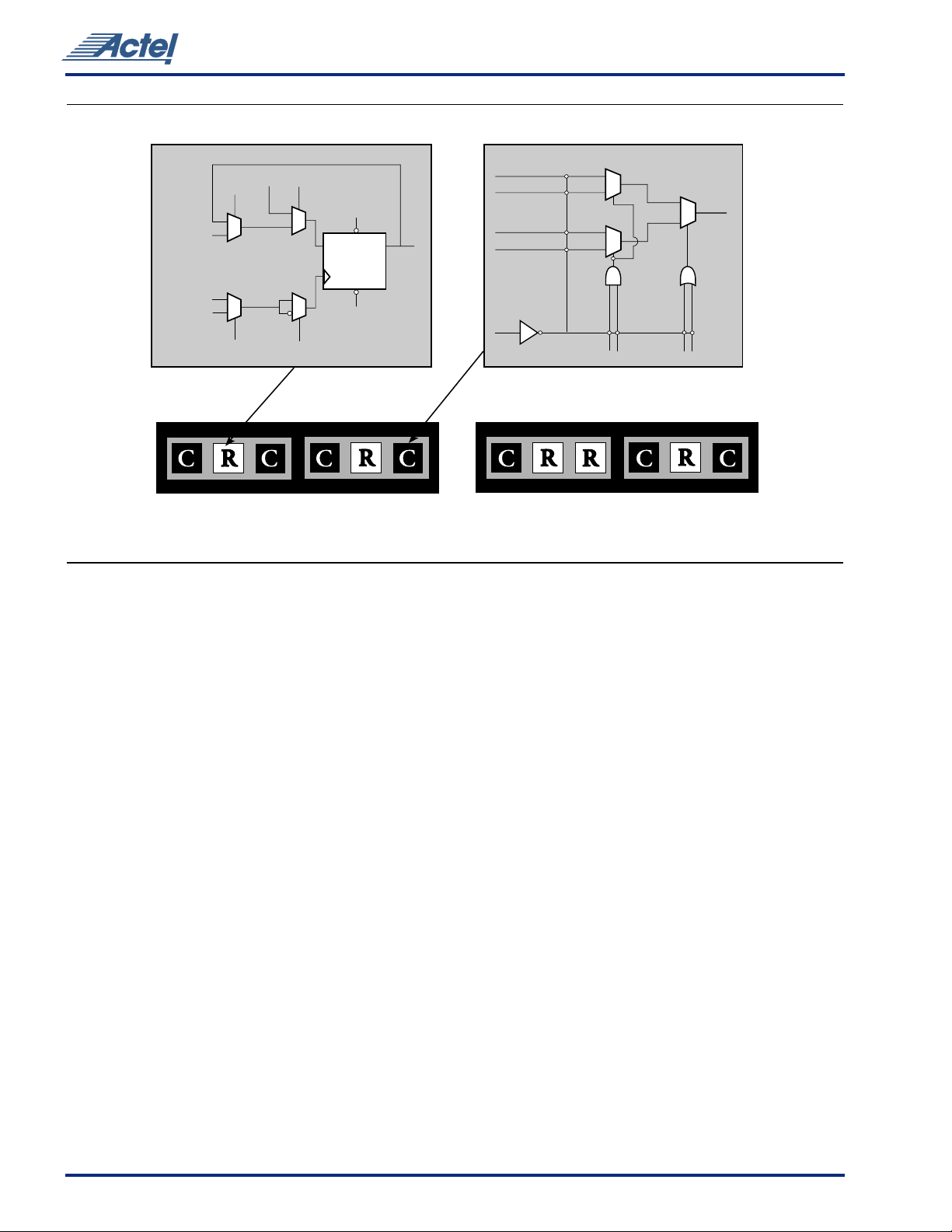

Actel has arranged all C-cell and R-cell logic modules into

horizontal banks called Clusters. There are two types of

Clusters: Type 1 contains two C-cells and one R-cell, while

Y

Sa Sb

Type 2 contains one C-cell and two R-cells.

To increase design efficiency and device performance, Actel

has further organized these modules into

SuperClusters

(Figure4 on page 6). SuperCluster 1 is a two-wide grouping

of Type 1 clusters. SuperCluster 2 is a two-wide group

containing one Type 1 cluster and one Type 2 cluster. SX

devices feature more SuperCluster 1 modules than

SuperCluster 2 modules because designers typically require

significantly more combinatorial logic than flip-flops.

v3.1 5

R-Cell C-Cell

54SX Family FPGAs

Routed

Data Input

S0

Direct

Connect

Input

HCLK

CLKA,

CLKB,

Internal Logic

CKS CKP

Cluster 1 Cluster 2 Cluster 2 Cluster 1

Type 1 SuperCluster Type 2 SuperCluster

Figure 4 • Cluster Organization

Routing Resources

S1

PSETB

YDQ

CLRB

D0

D1

Y

D2

D3

Sa Sb

DB

A0 B0 A1 B1

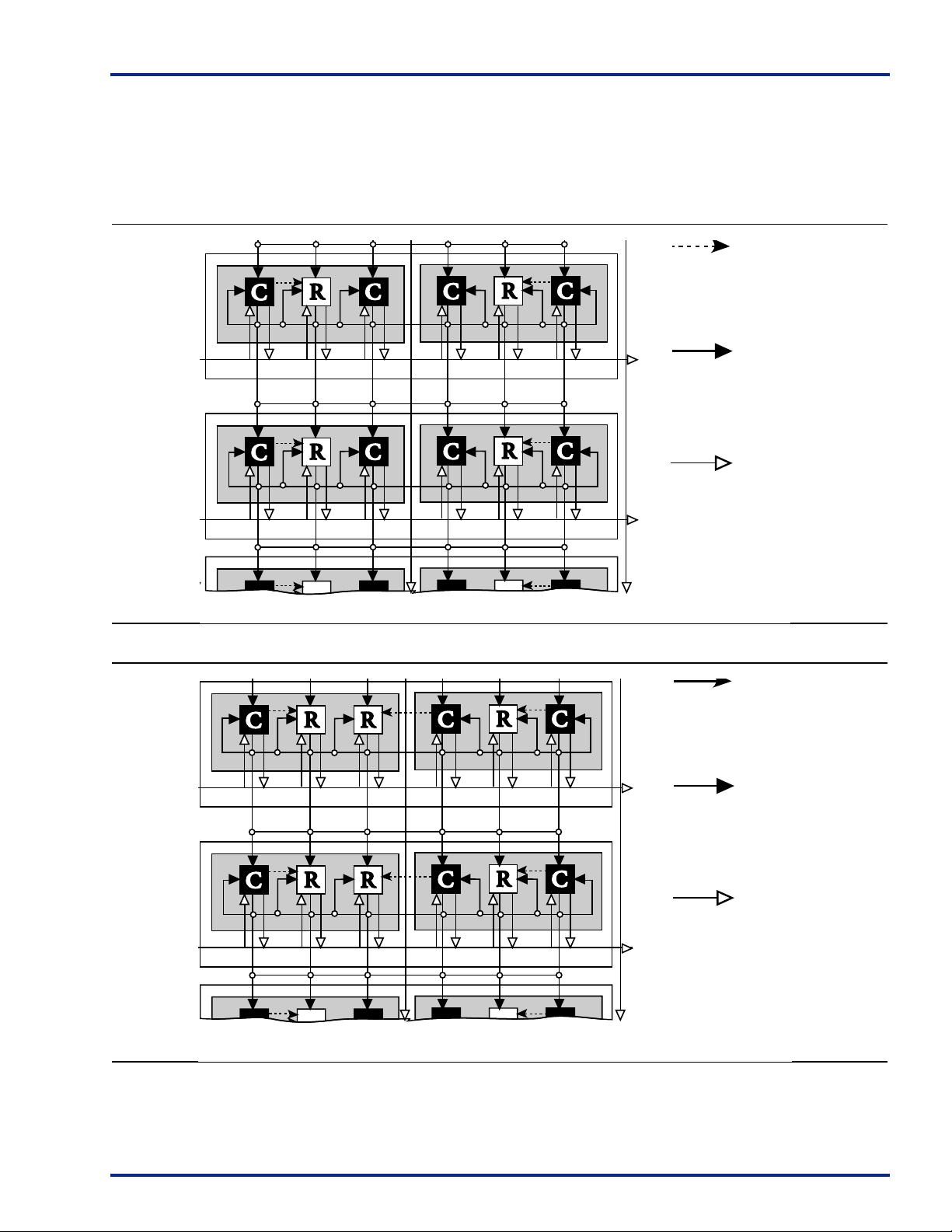

Clusters and SuperClusters can be connected through the

use of two innovative local routing resources called

FastConnect and DirectConnect, which enable extremely

fast and predictable interconnection of modules within

Clusters and SuperClusters (Figure 5 and Figure 6 on

page 7). This routing architectu re also dr amaticall y reduces

the number of antifuses required to complete a circuit,

ensuring the highest possible performance.

DirectConnect is a horizontal routing resource that provides

connections from a C-cell to its neighboring R-cell in a given

SuperCluster. DirectConnect uses a hard-wired signal path

requiring no programmable interconnection to achieve its

fast signal propagation time of less than 0.1 ns.

FastConnect enables horizontal routing between any two

logic modules within a given SuperCluster and vertical

routing with the SuperCluster immediately below it. Only

one programmable connection is used in a FastConnect

path, delivering maximum pin-to-pin propagation of 0.4 ns.

In addition to DirectConnect and FastConnect, the

architecture makes use of two globally oriented routing

resources known as segmented routing and high-drive

routing. Actel’s segmented routing structure provides a

variety of track lengths for extremely fast routing between

SuperClusters. The exact combination of track lengths and

antifuses within each path is chosen by the 100 percent

automatic place and route software to minimize signal

propagation delays.

Actel’s high-drive routing structure provides three clock

networks. The first clock, called HCLK, is hard wired from

the HCLK buffer to the clock select MUX in each R-cell. This

provides a fast propagation path for the clock signal,

enabling the 3.7 ns clock-to-out (pin-to-pin) performance of

the SX devices. The hard-wired clock is tuned to provide

clock skew as low as 0.25 ns. The remaining two clocks

(CLKA, CLKB) are global clocks that can be sourced from

external pins or from internal logic signals within the SX

device.

6 v3.1

54SX Family FPGAs

Other Architectural Features

Technology

Actel’s SX family is implemented on a high-voltage twin-well

CMOS process using 0.35µ design rules. The metal-to-metal

antifuse is made up of a combination of amorphous silicon

and dielectric material with barrier metals and has a

programmed (“on” state) resistance of 25Ω with

capacitance of 1.0 fF for low signal impedance.

Direct Connect

• No antifuses

• 0.1 ns routing delay

Fast Connect

• One antifuse

• 0.4 ns routing delay

Routing Segments

• Typically 2 antifuses

• Max. 5 antifuses

Figure 5 • DirectConnect and FastConnect for Type 1 SuperClusters

Figure 6 • DirectConnect and FastConnect for Type 2 SuperClusters

Direct Connect

• No antifuses

• 0.1 ns routing delay

Fast Connect

• One antifuse

• 0.4 ns routing delay

Routing Segments

• Typically 2 antifuses

• Max. 5 antifuses

v3.1 7

54SX Family FPGAs

Performance

The combination of architectural features described above

enables SX devices to operate with internal clock

frequencies exceeding 300 MHz, enabling very fast

execution of even complex logic functions. Thus, the SX

family is an optimal platform upon which to integrate the

functionality previously contained in multiple CPLDs. In

addition, designs that previously would have required a gate

array to meet performance goals can now be integrated into

an SX device with dramatic improvements in cost and time

to market. Using timing-driven place and route tools,

designers can achieve highly deterministic device

performance. With SX devices, designers do not need to use

complicated performance-enhancing design techniques

such as the use of redundant logic to reduce fanout on

critical nets or the instantiation of macros in HDL code to

achieve high performance.

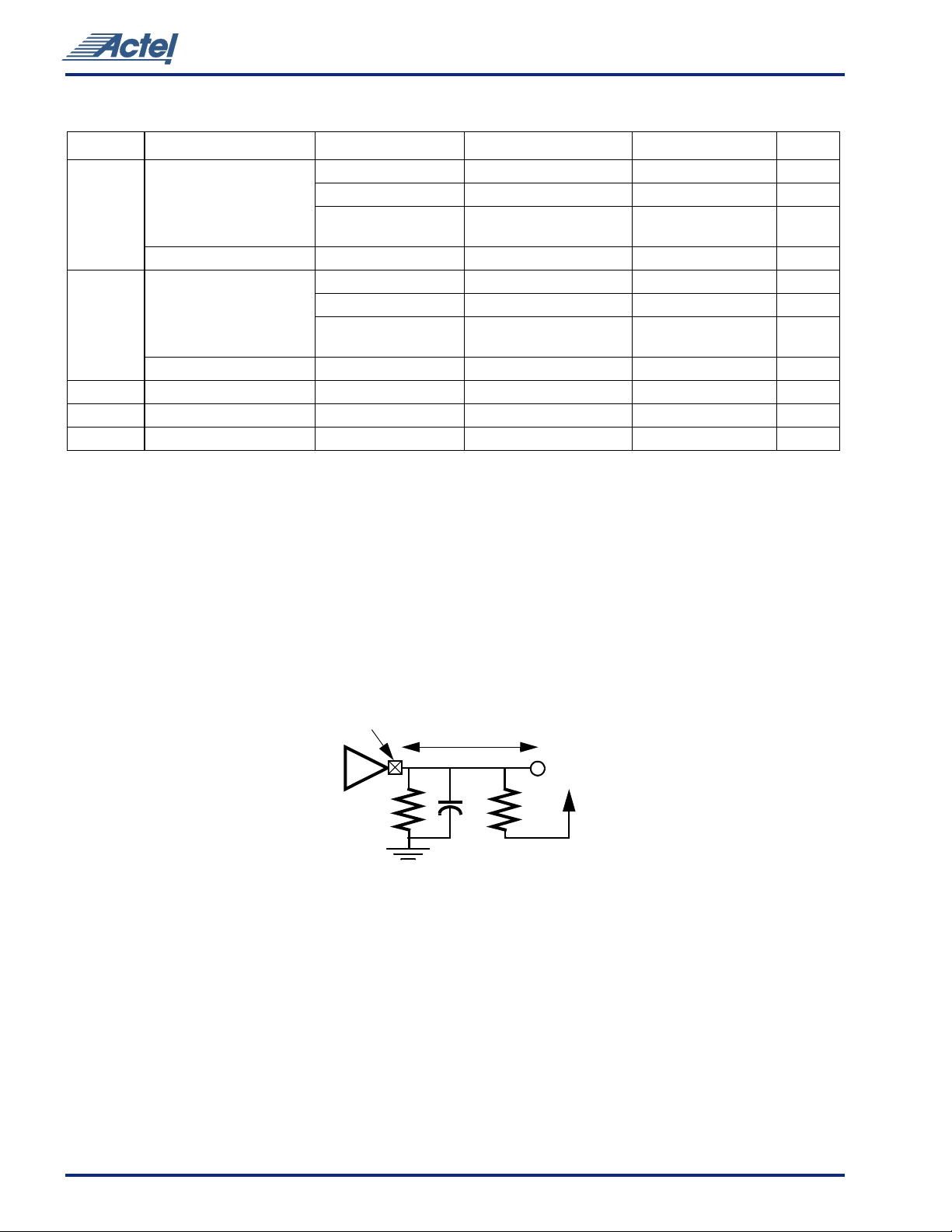

I/O Modules

Each I/O on an SX device can be configured as an input, an

output, a tristate output, or a bidirectional pin. Even without

the inclusion of dedicated I/O registers, these I/Os, in

combination with array registers, can achieve clock-to-out

(pad-to-pad) timing as fast as 3.7 ns. I/O cells that have

embedded latches and flip-flops require instantiation in

HDL code; this is a design complication not encountered in

SX FPGAs. Fast pin-to-pin timing ensures that the device

will have little trouble interfacing with any other device in

the system, which in turn enables parallel design of system

components and reduces overall design time.

Power Requirements

The SX family supports 3.3V operation and is designed to

tolerate 5.0V inputs. (Table 1). Power consumption is

extremely low due to the very short distances signals are

required to travel to complete a circuit. Power requirements

are further reduced because of the small number of

low-resistance antifuses in the path. The antifuse

architecture does not require active circuitry to hold a

charge (as do SRAM or EPROM), making it the lowest-power

architecture on the market.

Table 1 • Supply Voltages

Maximum

V

CCAVCCIVCCR

A54SX08

A54SX16

A54SX32

A54SX16-P

Note: A54SX16-P has three different entries because it is capable of

3.3V 3.3V 5.0V 5.0V 3.3V

3.3V

3.3V

3.3V

both a 3.3V and a 5V drive.

3.3V

3.3V

5.0V

3.3V

5.0V

5.0V

Input

Tolerance

3.3V

5.0V

5.0V

Maximum

Output

Drive

3.3V

3.3V

5.0V

Boundary Scan Testing (BST)

All SX devices are IEEE 1149.1 compliant. SX devices offer

superior diagnostic and testing capabilities by providing

Boundary Scan Testing (BST) and probing capabilities.

These functions are controlled through the special test pins

in conjunction with the program fuse. The functionality of

each pin is described in Table 2.In the dedicated test mode,

TCK, TDI and TDO are dedicated pins and cannot be used as

regular I/Os. In flexible mode, TMS should be set HIGH

through a pull-up resistor of 10kΩ. TMS can be pulled LOW

to initiate the test sequence.

The program fuse determines whether the device is in

dedicated or flexible mode. The default (fuse not blown) is

flexible mode. .

Table 2 • Boundary Scan Pin Functionality

Program Fuse Blown

(Dedicated Test Mode)

TCK, TDI, TDO are

dedicated BST pins

No need for pull-up resistor

for TMS

Development Tool Support

Program Fuse Not Blown

(Flexible Mode)

TCK, TDI, TDO are flexible

and may be used as I/Os

Use a pull-up resistor of 10k

Ω on TMS

The SX devices are fully supported by Actel’s line of FPGA

development tools, including the Actel DeskTOP series and

Designer Advantage tools. The Actel DeskTOP series is an

integrated design environment for PCs that includes design

entry, simulation, synthesis, and place and route tools.

Designer Advantage, Actel’s suite of FPGA development

point tools for PCs and Workstations, includes the ACTgen

Macro Builder, Designer with DirectTime timing driven

place and route and analysis tools, and device programming

software.

In addition, the SX devices contain ActionProbe circuitry

that provides built-in access to every node in a design,

enabling 100-percent real-time observation and analysis of a

device's internal logic nodes without design iteration. The

probe circuitry is accessed by Silicon Explorer II, an

easy-to-use integrated verification and logic analysis tool

that can sample data at 100 M Hz (asynchronous ) or 66 MHz

(synchronous). Silicon Explorer II attaches to a PC’s

standard COM port, turning the PC into a fully functional

18-channel logic analyzer. Silicon Explorer II allows

designers to complete the design verification process at

their desks and reduces verification time from several hours

per cycle to only a few seconds.

8 v3.1

54SX Family FPGAs

SX Probe Circuit Control Pins

The Silicon Explorer II tool uses the boundary scan ports

(TDI, TCK, TMS and TDO) to select the desired nets for

verification. The selected internal nets are assigned to the

PRA/PRB pins for observation. Figure 7 illustrates the

interconnection between Silicon Expl orer II and the FPGA

to perform in-circuit verification. The TRST pin is equipped

with a pull-up resistor. To remove the boundary scan state

machine from the reset state during probing, it is

16

Serial Connection

Silicon Explorer II

recommended that the TRST pin be left floating.

Design Considerations

The TDI, TCK, TDO, PRA, and PRB pins should not be used

as input or bidirectional ports. Because these pins are

active during probing, critical signals input through these

pins are not available while probing. In addition, the

Security Fuse should not be programmed because doing so

disables the Probe Circuitry.

Channel

TDI

TCK

TMS

TDO

PRA

PRB

SX FPGA

Figure 7 • Probe Setup

v3.1 9

3.3V/5V Operating Conditions Absolute Maximum Ratings

1

Recommended Operating Conditions

54SX Family FPGAs

Symbol Parameter Limits Units

V

V

V

CCR

CCA

CCI

2

DC Supply Voltage

2

DC Supply Voltage –0.3 to +4.0 V

DC Supply Voltage

2

(A54SX08, A54SX16,

3

–0.3 to +6.0 V

–0.3 to +4.0 V

A54SX32)

V

V

V

I

T

IO

CCI

I

O

STG

2

(A54SX16P)

Input Voltage –0.5 to +5.5 V

Output Voltage –0.5 to +3.6 V

I/O Source Sink

3

Current

Storage Temperature –65 to +150 °C

–0.3 to +6.0 V

–30 to +5.0 mA

DC Supply Voltage

Notes:

1. Stresses beyond those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device.

Exposure to absolute maximum rated conditions for extended

periods may affect device reliability. Device should not be

operated outside the Recommended Operating Conditions.

2. V

in the A54SX16P must be greater than or equal to V

CCR

during power-up and power-down sequences and during

CCI

normal operation.

3. Device inputs are normally high impedance and draw

extremely low current. However, when input voltage is greater

than V

+ 0.5V or less than GND – 0.5V, the internal protection

CC

diodes will forward-bias and can draw excessive current.

Parameter

Temperature

1

Range

cial Industrial Military Units

0 to+70 –40 to +85 –55 to +125 °C

3.3V Power

Commer

Supply

±10 ±10 ±10

Tolerance

5.0V Power

Supply

±5 ±10 ±10

Tolerance

Note:

1. Ambient temperature (T

industrial; case temperature (T

%V

%V

) is used for commercial and

A

) is used for military.

C

C

C

C

C

Electrical Specifications

Commercial Industrial

Symbol Parameter Min. Max. Min. Max. Units

(I

V

OH

V

OL

V

IL

V

IH

t

R

C

IO

I

CC

I

CC(D)

= -20uA) (CMOS)

OH

(I

= -8mA) (TTL)

OH

(I

= -6mA) (TTL)

OH

(IOL= 20uA) (CMOS)

(I

= 12mA) (TTL)

OL

(I

= 8mA) (TTL)

OL

, t

F

Input Transition Time tR, t

F

CIO I/O Capacitance 10 10 pF

Standby Current, ICC 4.0 4.0 mA

I

CC(D) IDynamic VCC

Supply Current See “Evaluating Power in 54SX Devices” on page 18

(V

CCI

– 0.1)

2.4

V

CCI

V

CCI

(V

CCI

– 0.1)

2.4

V

CCI

V

CCI

0.10

0.50

0.50

0.8 0.8 V

2.0 2.0 V

50 50 ns

V

V

10 v3.1

54SX Family FPGAs

PCI Compliance for the 54SX Family

The 54SX family supports 3.3V and 5V PCI and is compliant with the PCI Local Bus Specification Rev. 2.1.

A54SX16P DC Specifications (5.0V PCI Operation)

Symbol Parameter Condition Min. Max. Units

V

CCA

V

CCR

V

CCI

V

IH

V

IL

I

IH

I

IL

V

OH

V

OL

C

IN

C

CLK

C

IDSEL

Notes:

1. Input leakage currents include hi-Z output leakage for all bi-directional buffers with tri-state outputs.

2. Signals without pull-up resistors must have 3 mA low output current. Signals requiring pull up must have 6 mA; the latter include,

FRAME#, IRDY#, TRDY#, DEVSEL#, STOP#, SERR#, PERR#, LOCK#, and, when used AD[63::32], C/BE[7::4]#, PAR64, REQ64#, and ACK64#.

3. Absolute maximum pin capacitance for a PCI input is 10 pF (except for CLK).

4. Lower capacitance on this input-only pin allows for non-resistive coupling to AD[xx].

Supply Voltage for Array 3.0 3.6 V

Supply Voltage required for Internal Biasing 4.75 5.25 V

Supply Voltage for IOs 4.75 5.25 V

Input High Voltage

Input Low Voltage

1

1

2.0 VCC + 0.5 V

–0.5 0.8 V

Input High Leakage Current VIN = 2.7 70 µA

Input Low Leakage Current VIN = 0.5 –70 µA

Output High Voltage I

Output Low Voltage

Input Pin Capacitance

2

3

= –2 mA 2.4 V

OUT

I

= 3 mA, 6 mA 0.55 V

OUT

10 pF

CLK Pin Capacitance 5 12 pF

IDSEL Pin Capacitance

4

8pF

v3.1 11

54SX Family FPGAs

A54SX16P AC Specifications for (PCI Operation)

Symbol Parameter Condition Min. Max. Units

1

I

OH(AC)

I

OL(AC)

I

CL

slew

slew

≤ 1.4

OUT

OUT

OUT

= 3.1

≥ 2.2

OUT

OUT

= 0.71

< 2.4

< V

CC

3

1

> 0.55

> 0

3

1, 2

–44 + (V

1, 3

1

1, 3

Switching Current High

(Test Point) V

Switching Current High

(Test Point) V

0 < V

1.4 ≤ V

3.1 < V

OUT

V

OUT

2.2 > V

0.71 > V

OUT

Low Clamp Current –5 < VIN ≤ –1 –25 + (VIN + 1)/0.015 mA

R

F

Output Rise Slew Rate 0.4V to 2.4V load

Output Fall Slew Rate 2.4V to 0.4V load

4

4

–44 mA

– 1.4)/0.024 mA

OUT

Equation A: on

page 13

–142 mA

95 mA

V

/0.023

OUT

Equation B: on

page 13

mA

206 mA

15V/ns

15V/ns

Notes:

1. Refer to the V/I curves in Figure 8. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here;

i.e., half size output drivers may be used on these signals. This specification does not apply to CLK and RST# which are system outputs.

“Switching Current High” specification are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD# which are open drain outputs.

2. Note that this segment of the minimum current curve is drawn from the AC drive point directly to the DC drive point rather than toward

the voltage rail (as is done in the pull-down curve). This difference is intended to allow for an optional N-channel pull-up.

3. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (A and B)

are provided with the respective diagrams in Figure 8. The equation defined maxima should be met by design. In order to facilitate

component testing, a maximum current test point is defin ed for each side of the output driver.

4. This parameter is to be interpreted as the cumulative edge rate across the spe cified range, rather than the instantaneous rate at a ny poin t

within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an

unloaded output per revision 2.0 of the PCI Local Bus Specification. However, adherence to both maximum and minimum parameters is

now required (the maximum is no longer simply a guideline). Since adherence to the maximum slew rate was not required prior to

revision 2.1 of the specification, there may be components in the market for some time that have faster edge rates; therefore, motherboard

designers must bear in mind that rise and fall times faster than this specification could occur, and should ensure that signal integrity

modeling accounts for this. Rise slew rate does not apply to open drain outputs.

pin

1/2 in. max.

output

buffer

V

CC

10 pF

1kΩ

1kΩ

12 v3.1

54SX Family FPGAs

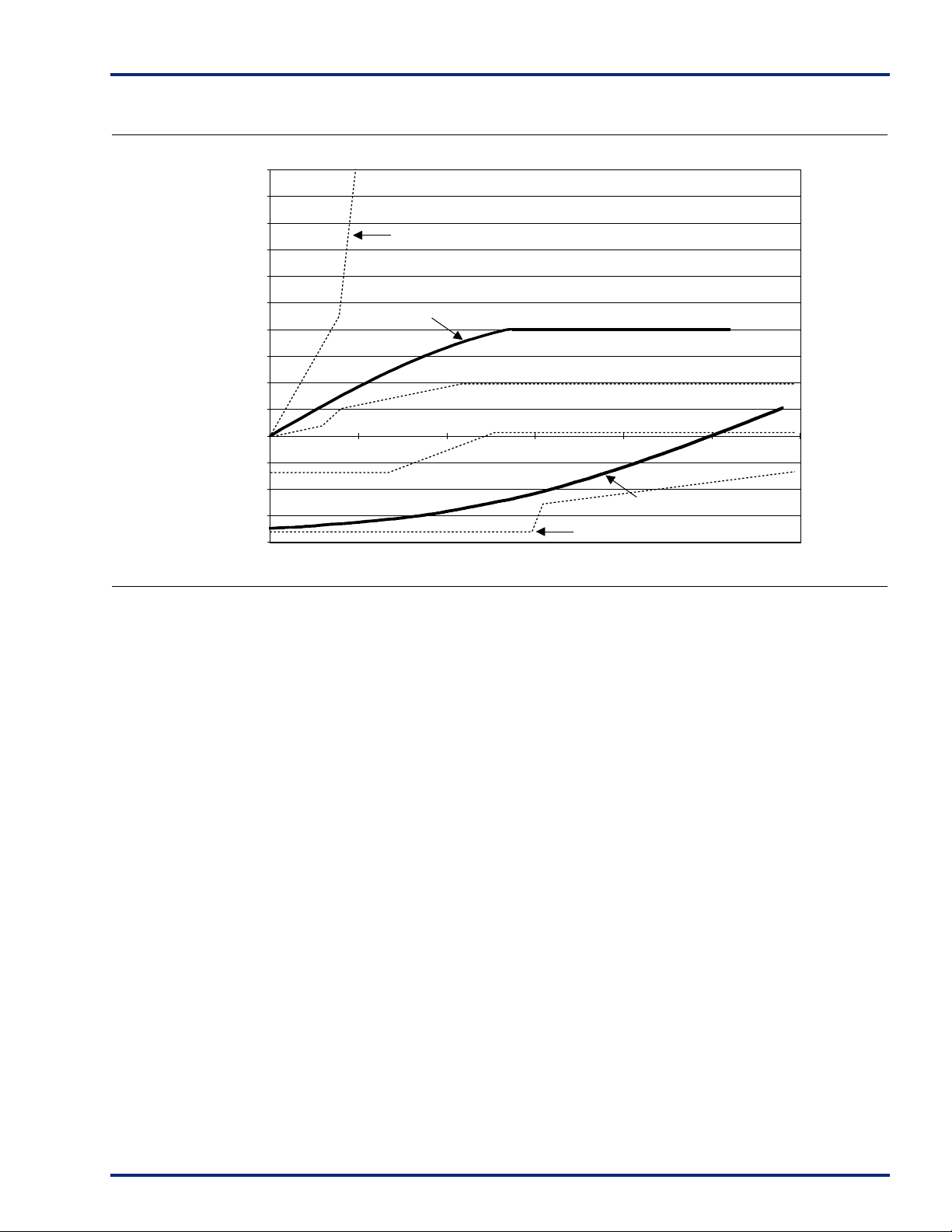

Figure 8 shows the 5.0V PCI V/I curve and the minimum and maximum PCI drive characteristics of the A54SX16P family.

0.50

0.45

0.40

0.35

0.30

0.25

0.20

0.15

Current (A)

0.10

0.05

0

–0.05

–0.10

–0.15

–0.20

PCI IOH Mininum

PCI IOL Maximum

SX PCI I

1

OL

Figure 8 • 5.0V PCI Curve for A54SX16P Family

Equation A:

I

= 11.9 * (V

OH

for VCC > V

– 5.25) * (V

OUT

OUT

> 3.1V

OUT

+ 2.45)

PCI IOL Mininum

23456

SX PCI I

PCI IOH Maximum

Voltage Out

OH

Equation B:

IOL = 78.5 * V

for 0V < V

OUT

OUT

* (4.4 – V

< 0.71V

OUT

)

v3.1 13

54SX Family FPGAs

A54SX16P DC Specifications (3 .3V PCI Operation)

Symbol Parameter Condition Min. Max. Units

V

CCA

V

CCR

V

CCI

V

IH

V

IL

I

IPU

I

IL

V

OH

V

OL

C

IN

C

CLK

C

IDSEL

Supply Voltage for Array 3.0 3.6 V

Supply Voltage required for Internal Biasing 3.0 3.6 V

Supply Voltage for IOs 3.0 3.6 V

Input High Voltage 0.5V

CCVCC

Input Low Voltage –0.5 0.3V

Input Pull-up Voltage

Input Leakage Current

Output High Voltage I

Output Low Voltage I

Input Pin Capacitance

1

2

3

0 < VIN < V

OUT

OUT

CC

= –500 µA 0.9V

= 1500 µA 0.1V

0.7V

CC

CC

+ 0.5 V

CC

V

V

±10 µA

V

CC

V

10 pF

CLK Pin Capacitance 5 12 pF

IDSEL Pin Capacitance

4

8pF

Notes:

1. This specification should be guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated

network. Applications sensitive to static power utilization should assure that the input buffer is conducting minimum current at this

input voltage.

2. Input leakage currents include hi-Z output leakage for all bi-directional buffers with tri-state outputs.

3. Absolute maximum pin capacitance for a PCI i nput is 10pF ( exc ept f or C LK).

4. Lower capacitance on this input-only pin allows for non-resistive coupling to AD[xx].

14 v3.1

54SX Family FPGAs

A 54SX16P AC Specifications (3.3V PCI Operation)

Symbol Parameter Condition Min. Max. Units

CC

< 0.9V

< V

2

CC

≥ 0.6V

> 0.1V

> 0

OUT

2

CC

1

mA

1

CC

1, 2

–17.1 + (VCC – V

CC

1

CC

1

CC

1, 2

–12V

CC

)

OUT

16V

CC

26.7V

OUT on page 16

– 1)/0.015 mA

OUT

Equation C: on

page 16

–32V

CC

38V

CC

mA

mA

mA

mA

mA

I

OH(AC)

I

OL(AC)

I

CL

I

CH

slew

slew

OUT

CC

OUT

≤ V

CC

= 0.7V

> V

> V

CC

≤ 0.3V

OUT

OUT

OUT

OUT

Switching Current High

(Test Point) V

Switching Current High

0 < V

0.3V

0.7VCC < V

V

0.6V

0.18VCC > V

(Test Point) V

OUT

= 0.18V

Low Clamp Current –3 < VIN ≤ –1 –25 + (VIN + 1)/0.015 mA

High Clamp Current –3 < VIN ≤ –1 25 + (VIN – V

Output Rise Slew Rate30.2VCC to 0.6VCC load 1 4 V/ns

R

Output Fall Slew Rate30.6VCC to 0.2VCC load 1 4 V/ns

F

Notes:

1. Refer to the V/I curves in Figure9. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here;

i.e., half size output drivers may be used on these signals. This specification does not apply to CLK and RST# which are system outputs.

“Switching Current High” specification are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD# which are open drain outputs.

2. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (C and D)

are provided with the respective diagrams in Figure 9. The equation defined maxima should be met by design. In order to facilit ate

component testing, a maximum current test point is defined for each side of t he output driver.

3. This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the instantaneous rate at any point

within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an

unloaded output per the latest revision of the PCI Local Bus Specification. However, adherence to both maximum and minimum

parameters is required (the maximum is no longer simply a guideline). Rise slew rate does not apply to open drain outputs.

pin

1/2 in. max.

output

buffer

V

CC

10 pF

1kΩ

1kΩ

v3.1 15

54SX Family FPGAs

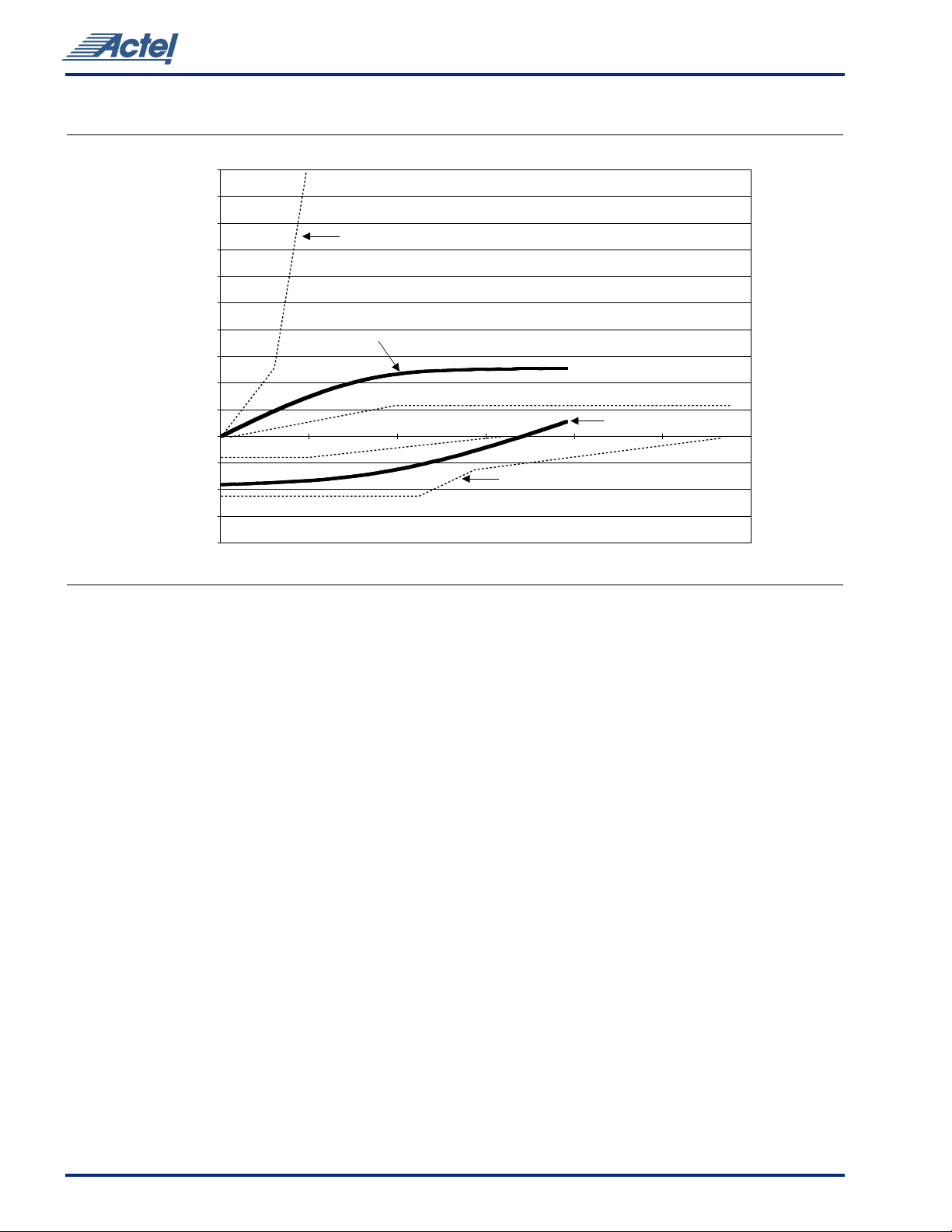

Figure 9 shows the 3.3V PCI V/I curve and the minimum and maximum PCI drive characteristics of the A54SX16P family.

0.50

0.45

0.40

0.35

0.30

0.25

0.20

0.15

Current (A)

0.10

0.05

0

–0.05

–0.10

–0.15

–0.20

PCI IOH Minimum

PCI IOL Maximum

SX PCI I

123456

OL

Figure 9 • 3.3V PCI Curve for A54SX16P Family

Equation C:

= (98.0/VCC) * (V

I

OH

for V

CC

> V

– VCC) * (V

OUT

OUT

> 0.7 V

OUT

CC

+ 0.4VCC)

PCI IOH Maximum

Voltage Out

Equation D:

PCI IOL Minimum

I

= (256/VCC) * V

OL

for 0V < V

SX PCI I

OUT

OH

* (VCC – V

OUT

< 0.18 V

CC

OUT

)

16 v3.1

54SX Family FPGAs

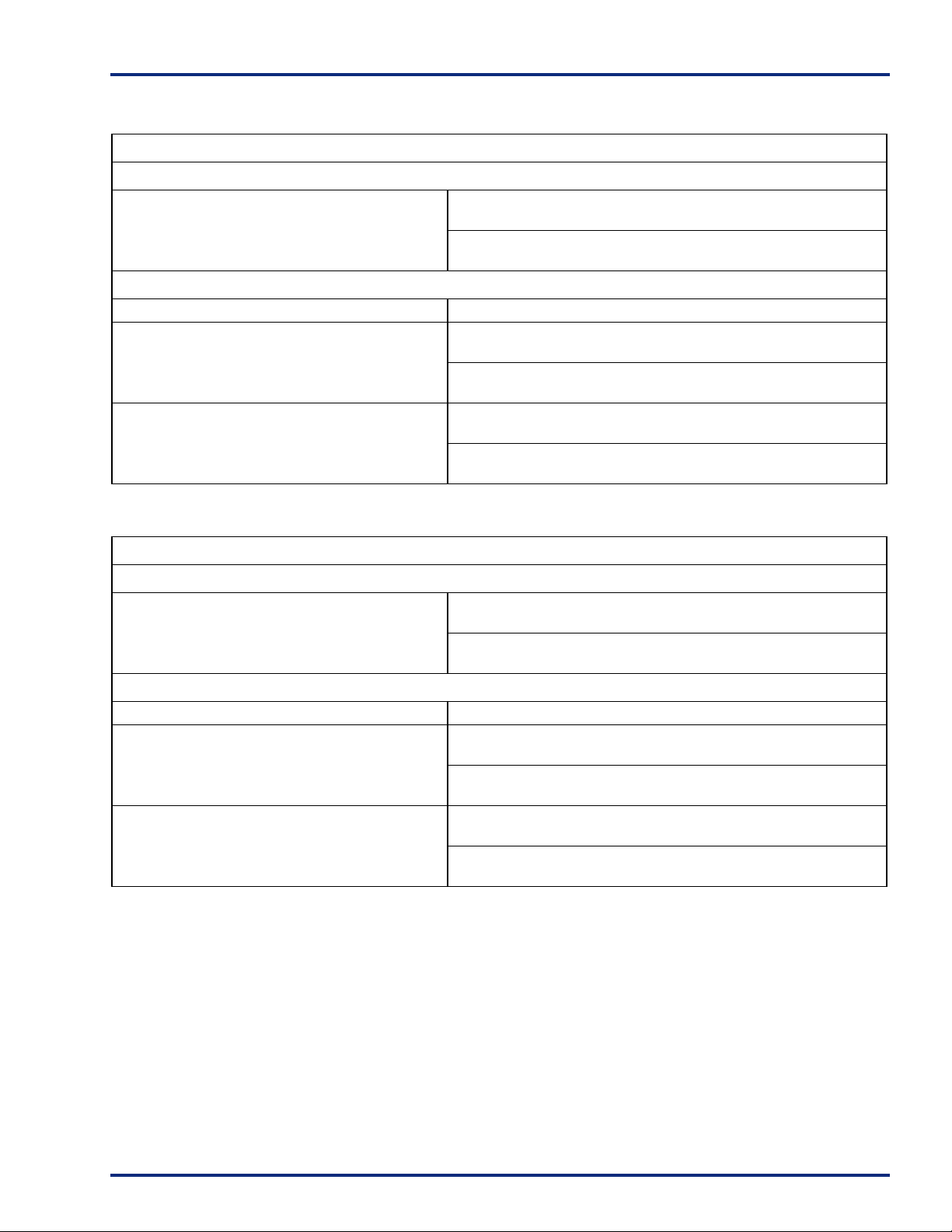

Power-Up Sequencing

V

CCA

V

CCR

V

CCI

Power-Up Sequence Comments

A54SX08, A54SX16, A54SX32

3.3V 5.0V 3.3V

5.0V First

3.3V Second

3.3V First

5.0V Second

No possible damage to device.

Possible damage to device.

A54SX16P

3.3V 3.3V 3.3V 3.3V Only No possible damage to device.

3.3V 5.0V 3.3V

3.3V 5.0V 5.0V

5.0V First

3.3V Second

3.3V First

5.0V Second

5.0V First

3.3V Second

3.3V First

5.0V Second

No possible damage to device.

Possible damage to device.

No possible damage to device.

No possible damage to device.

Power-Down Sequencing

V

CCA

V

CCR

V

CCI

Power-Down Sequence Comments

A54SX08, A54SX16, A54SX32

3.3V 5.0V 3.3V

5.0V First

3.3V Second

3.3V First

5.0V Second

No possible damage to device.

Possible damage to device.

A54SX16P

3.3V 3.3V 3.3V 3.3V Only No possible damage to device.

3.3V 5.0V 3.3V

3.3V 5.0V 5.0V

5.0V First

3.3V Second

3.3V First

5.0V Second

5.0V First

3.3V Second

3.3V First

5.0V Second

Possible damage to device.

No possible damage to device.

No possible damage to device.

No possible damage to device.

v3.1 17

54SX Family FPGAs

Evaluating Power in 54SX Devices

A critical element of system reliability is the ability of

electronic devices to safely dissipate the heat generated

during operation. The thermal characteristics of a circuit

depend on the device and package used, the operating

temperature, the operating current, and the system's ability

to dissipate heat.

You should complete a power evaluation early in the design

process to help identify potential heat-related problems in

the system and to prevent the system from exceeding the

device’s maximum allowed junction temperature.

The actual power dissipated by most applications is

significantly lower than the power the package can

dissipate. However, a thermal analysis should be performed

for all projects. To perform a power evaluation, follow these

steps:

• Estimate the power consumption of the application.

• Calculate the maximum power allowed for the device and

package.

• Compare the estimated power and maximum power

values.

Estimating Power Consumption

The total power dissipation for the 54SX family is the sum of

the DC power dissipation and the AC power dissipation. Use

Equation 1 to calculate the estimated power consumption of

your application.

= PDC + PAC (1)

P

Total

DC Power Dissipation

The power due to standby current is typically a small

component of the overall power. The Standby power is

shown below for commercial, worst case conditions (70°C).

Table 3 •

I

CC

4mA 3.6V 14.4mW

V

CC

Power

The DC power dissipation is defined in Equation 2 as

follows:

= (I

P

DC

(I

standby

AC Power Dissipation

)*V

standby

)*V

CCA

+ x*VOL*IOL + y*(V

CCI

+ (I

standby

)*V

CCI

+

CCR

– VOH)*V

OH

(2)

The power dissipation of the 54SX Family is usually

dominated by the dynamic power dissipation. Dynamic

power dissipation is a function of frequency, equivalent

capacitance and power supply voltage. The AC power

dissipation is defined as follows:

PAC = P

P

Output Buffer

= V

P

AC

(n * C

EQI

(0.5 * (q

(0.5 * (q

(0.5 * (s

Definition of Terms Used in Fo rmula

Module

2

CCA

* fn)

* C

1

* C

2

* C

1

+ P

RCLKA Net

+ P

Input Buffer

* [(m * C

Input Buffer

EQCR

EQCR

EQHV

EQM

* fq1) + (r1 * fq1))

* fq2)+ (r2 * fq2))

* fs1) + (C

+ P

RCLKB Net

+ P

HCLK Net

(3)

* fm)

+ (p * (C

EQHF

Module

EQO

RCLKB

* fs1))

+

+ CL) * fp)

+

RCLKA

+

](4)

HCLK

Output Buffer

m = Number of logic modules switching at f

n = Number of input buffers switching at f

p = Number of output buffers switching at f

q

1

= Number of clock loads on the first routed array

clock

q

2

= Number of clock loads on the second routed

array clock

x = Number of I/Os at logic low

y = Number of I/Os at logic high

r

1

= Fixed capacitance due to first routed array

clock

r

2

= Fixed capacitance due to second routed array

clock

s

1

= N umber of clock loads on the dedicated array

clock

C

C

C

C

EQM

EQI

EQO

EQCR

= Equivalent capacitance of logic modules in pF

= Equivalent capacitance of input buffers in pF

= Equivalent capacitance of output buffers in pF

= Equivalent capacitance of routed array clock in

pF

C

C

C

f

m

f

n

f

p

f

q1

f

q2

f

s1

EQHV

EQHF

L

= Variable capacitance of dedicated array clock

= Fixed capacitance of dedicated array clock

= Output lead capacitance in pF

= Average logic module switching rate in MHz

= Average input buffer switching rate in MHz

= Average output buffer switching rate in MHz

= Average first routed array clock rate in MHz

= Average second routed array clock rate in MHz

= Average dedicated array clock rate in MHz

A54SX08 A54SX16 A54SX16P A54SX32

(pF) 4.0 4.0 4.0 4.0

C

EQM

C

(pF) 3.4 3.4 3.4 3.4

EQI

(pF) 4.7 4.7 4.7 4.7

C

EQO

(pF) 1.6 1.6 1.6 1.6

C

EQCR

C

EQHV

C

EQHF

(pF) 87 138 138 171

r

1

(pF) 87 138 138 171

r

2

0.615 0.615 0.615 0.615

60 96 96 140

+

+

m

n

p

18 v3.1

Loading...

Loading...