ACT ACT-SF512K32N-39P1T, ACT-SF512K32N-39P1Q, ACT-SF512K32N-39P1M, ACT-SF512K32N-39P1I, ACT-SF512K32N-39P1C Datasheet

...

eroflex Circuit Technology - Advanced Multichip Modules © SCD3852 REV A 5/20/98

F

E

I

D

C

E

R

T

A

E

R

O

F

L

E

X

L

A

B

S

I

N

C

.

ACT-SF512K32 High Speed

512Kx32 SRAM / 512Kx32 Flash

Multichip Module

FEATURES

■

4 – 512K x 8 SRAMs & 4 – 512K x 8 Flash Die in

One MCM

■ Access Times of 25ns, 35ns (SRAM) and

60ns, 70ns, 90ns (Flash)

■ Organized as 512K x 32 of SRAM and 512K x 32

of Flash Memory with Common Data Bus

■ Low Power CMOS

■ Input and Output TTL Compatible Design

■ MIL-PRF-38534 Compliant MCMs Available

■ Decoupling Capacitors and Multiple Grounds for

Low Noise

■ Commercial, Industrial and Military Temperature

Ranges

■ Industry Standard Pinouts

■ TTL Compatible Inputs and Outputs

■ Packaging – Hermetic Ceramic

● 66–Lead, PGA-Type, 1.385"SQ x 0.245"max,

Aeroflex code# "P1,P5 with/without shoulders)"

● 68–Lead, Dual-Cavity CQFP(F2), 0.88"SQ x

.20"max (.18 max thickness available, contact

factory for details) (Drops into the 68 Lead

JEDEC .99"SQ CQFJ footprint)

CIRCUIT TECHNOLOGY

www.aeroflex.com

FLASH MEMORY FEATURES

■ Sector Architecture (Each Die)

● 8 Equal Sectors of 64K bytes each

● Any combination of sectors can be erased with one

ISO

900

1

I

command sequence

■ +5V Programing, +5V Supply

■ Embedded Erase and Program Algorithms

■ Hardware and Software Write Protection

■ Page Program Operation and Internal Program

Control Time.

■ 10,000 Erase/Program Cycles

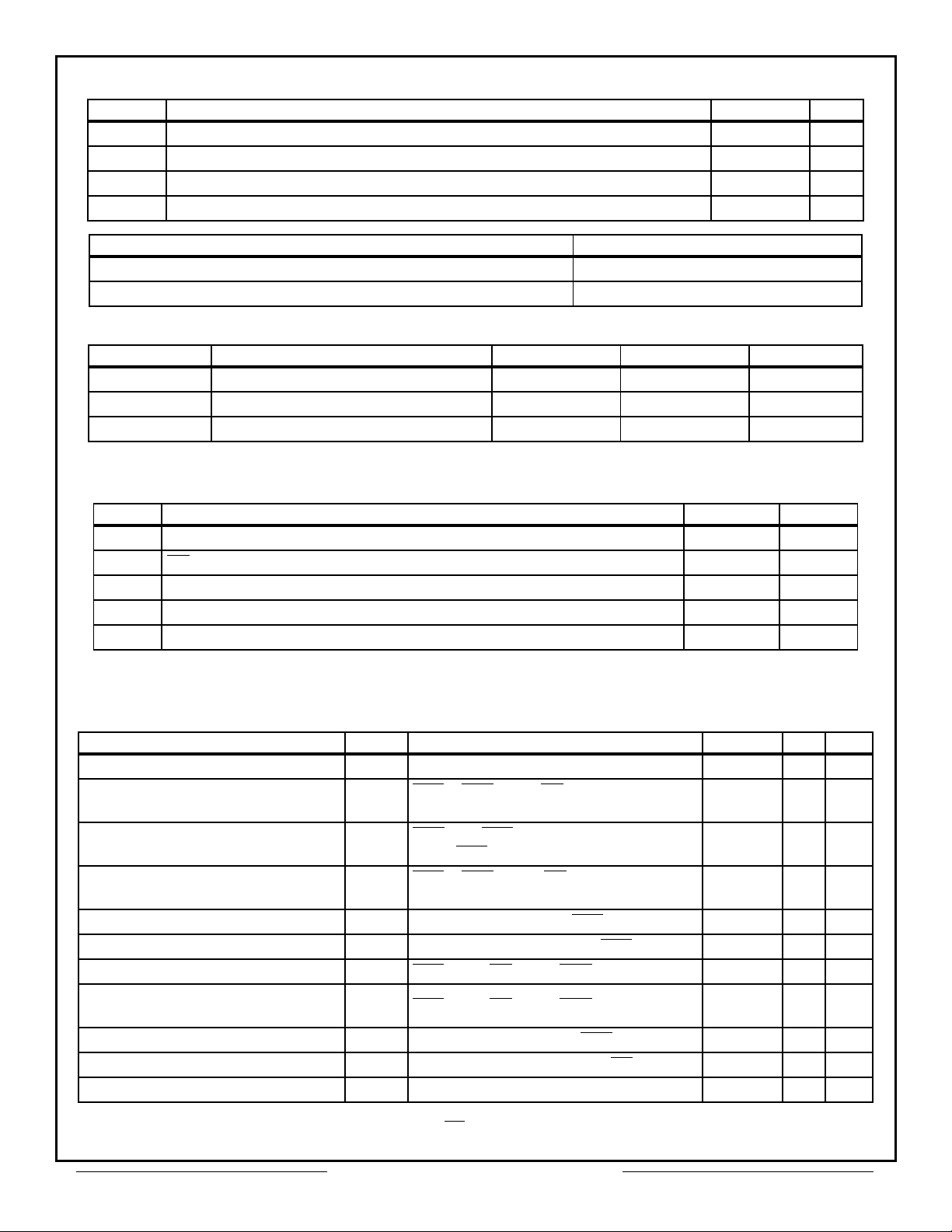

Block Diagram – PGA Type Package(P1 & P5) & CQFP(F2)

FWE4 SWE4 PIN DESCRIPTION

I/O

0-31 Data I/O

A

0–18 Address Inputs

FWE

1-4 Flash Write Enables

SWE

1-4 SRAM Write Enables

512K X 8 FLASH

512K X 8 SRAM

FCE

SCE

OE

NC Not Connected

V

CC Power Supply

GND Ground

Flash Chip Enable

SRAM Chip Enable

Output Enable

OE

A0–A18

SCE

FCS

FWE1

512K X 8 FLASH

512K X 8 SRAM

SWE1

FWE2 SWE2

512K X 8 FLASH

512K X 8 SRAM

I/O8-15 I/O16-23I/O0-7 I/O24-31

FWE3 SWE3

512K X 8 FLASH

512K X 8 SRAM

Absolute Maximum Ratings

Symbol Rating Range Units

-55 to +125 °C

-65 to +150 °C

-0.5 to +7 V

300 °C

T

T

STG

V

T

Operating Temperature

C

Storage Temperature

Maximum Signal Voltage to Ground

G

Maximum Lead Temperature (10 seconds)

L

Parameter

Flash Data Retention 10 Years

Flash Endurance (Write/Erase Cycles) 10,000

Normal Operating Conditions

Symbol Parameter Minimum Maximum Units

V

CC

V

IH

V

IL

Power Supply Voltage

Input High Voltage

Input Low Voltage

+4.5 +5.5 V

+2.2 V

+ 0.3 V

CC

-0.5 +0.8 V

Capacitance

(V

= 0V, f = 1MHz, TC = 25°C)

IN

Symbol Parameter Maximum Units

AD

C

C

C

WE1-4

C

C

A0 – A18 Capacitance

OE

OE Capacitance

F/S Write Enable Capacitance

CE

F/S Chip Enable Capacitance

I/O

I/O0 – I/O31 Capacitance

This parameter is guaranteed by design but not tested

80 pF

80 pF

30 pF

50 pF

30 pF

DC Characteristics

(VCC = 5.0V, VSS = 0V, TC = -55°C to +125°C)

Parameter Sym Conditions Min Max Units

I

Input Leakage Current

Output Leakage Current

SRAM Operating Supply Current x 32

Mode

I

CC

Standby Current

SRAM Output Low Voltage

SRAM Output High Voltage

Flash Vcc Active Current for Read (1)

Flash Vcc Active Current for Program

or Erase (2)

Flash Output Low Voltage

Flash Output High Voltage

Flash Low Vcc Lock Out Voltage

Notes: 1) The ICC current listed includes both the DC operating current and the frequency dependent component (at 5MHz). The

frequency component typically is less than 2mA/MHz, with OE

erase) is in progress 3) DC test conditions: V

V

V

I

I

V

V

V

IL = 0.3V, VIH = VCC - 0.3V

VCC = Max, VIN=0toV

LI

FCE = SCE = VIH, OE = V

I

LO

V

=0toV

OUT

SCE

x32

I

SB

OL

OH

CC1

CC2

OL

OH1

LKO

= VIL, OE = VIH, f = 5MHz, VCC =

Max, FCE

FCE = SCE = VIH, OE = VIH, f = 5MHz,

= Max

V

CC

IOL = 8 mA, VCC = Min, FCE = V

IOH = -4.0 mA, , VCC = Min, FCE = V

FCE = VIL, OE = VIH, SCE = V

FCE = VIL, OE = VIH, SCE = V

IOL = 12 mA, VCC = Min, SCE = V

IOH = -2.5 mA, , VCC = Min, SCE = V

CC

= V

IH

at VIH 2) ICC active while Embedded Algorithim (program or

CC

IH,

IH

IH

IH

IH

IH

IH

2.4 V

0.85 x VCC V

3.2 4.2 V

10 µA

10 µA

550 mA

80 mA

0.4 V

260 mA

300 mA

0.45 V

Aeroflex Circuit Technology SCD3852 REV A 5/20/98 Plainview NY (516) 694-6700

2

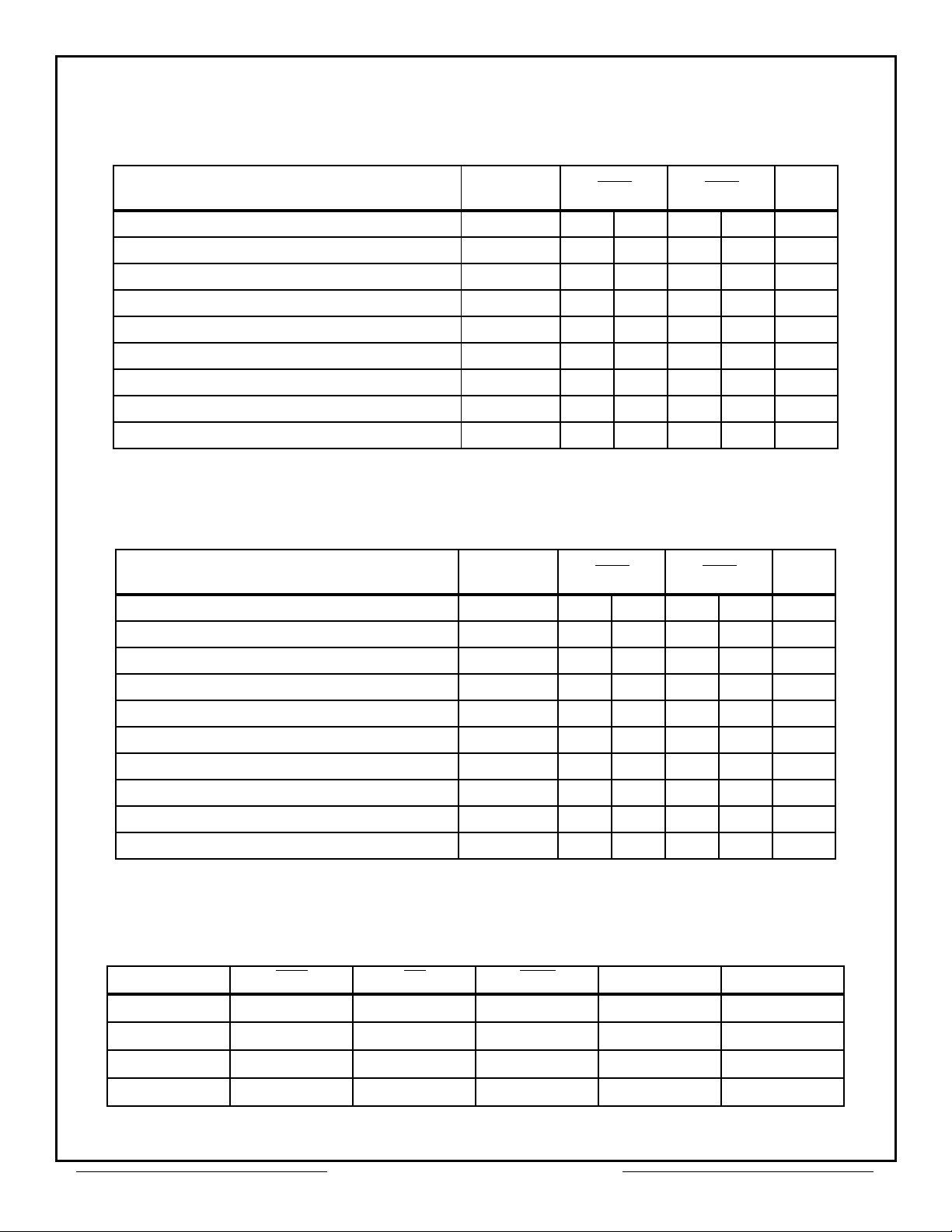

SRAM AC Characteristics

(VCC = 5.0V, VSS= 0V, Tc= -55°C to +125°C)

Read Cycle

Parameter Symbol

Read Cycle Time

Address Access Time

Chip Select Access Time

Output Hold from Address Change

Output Enable to Output Valid

Chip Select to Output in Low Z *

Output Enable to Output in Low Z *

Chip Deselect to Output in High Z *

Output Disable to Output in High Z *

* Parameters guaranteed by design but not tested

Write Cycle

Parameter Symbol

Write Cycle Time

Chip Select to End of Write

Address Valid to End of Write

Data Valid to End of Write

Write Pulse Width

Address Setup Time

Output Active from End of Write *

Write to Output in High Z *

Data Hold from Write Time

Address Hold Time

* Parameters guaranteed by design but not tested

t

t

t

ACE

t

t

t

CLZ

t

OLZ

t

CHZ

t

OHZ

t

WC

t

CW

t

AW

t

DW

t

WP

t

t

OW

t

WHZ

t

DH

t

RC

AA

OH

OE

AS

AH

–025

Min Max

–035

Min Max

Units

25 35 ns

25 35 ns

25 35 ns

0 0 ns

12 25 ns

2 4 ns

0 0 ns

12 15 ns

12 15 ns

–025

Min Max

–035

Min Max

Units

25 35 ns

17 25 ns

17 25 ns

13 20 ns

17 25 ns

2 2 ns

4 4 ns

13 15 ns

0 0 ns

0 0 ns

Truth Table

Mode SCE OE SWE Data I/O Power

Standby H X X High Z Standby

Read L L H Data Out Active

Output Disable L H H High Z Active

Write L X L Data In Active

Aeroflex Circuit Technology SCD3852 REV A 5/20/98 Plainview NY (516) 694-6700

3

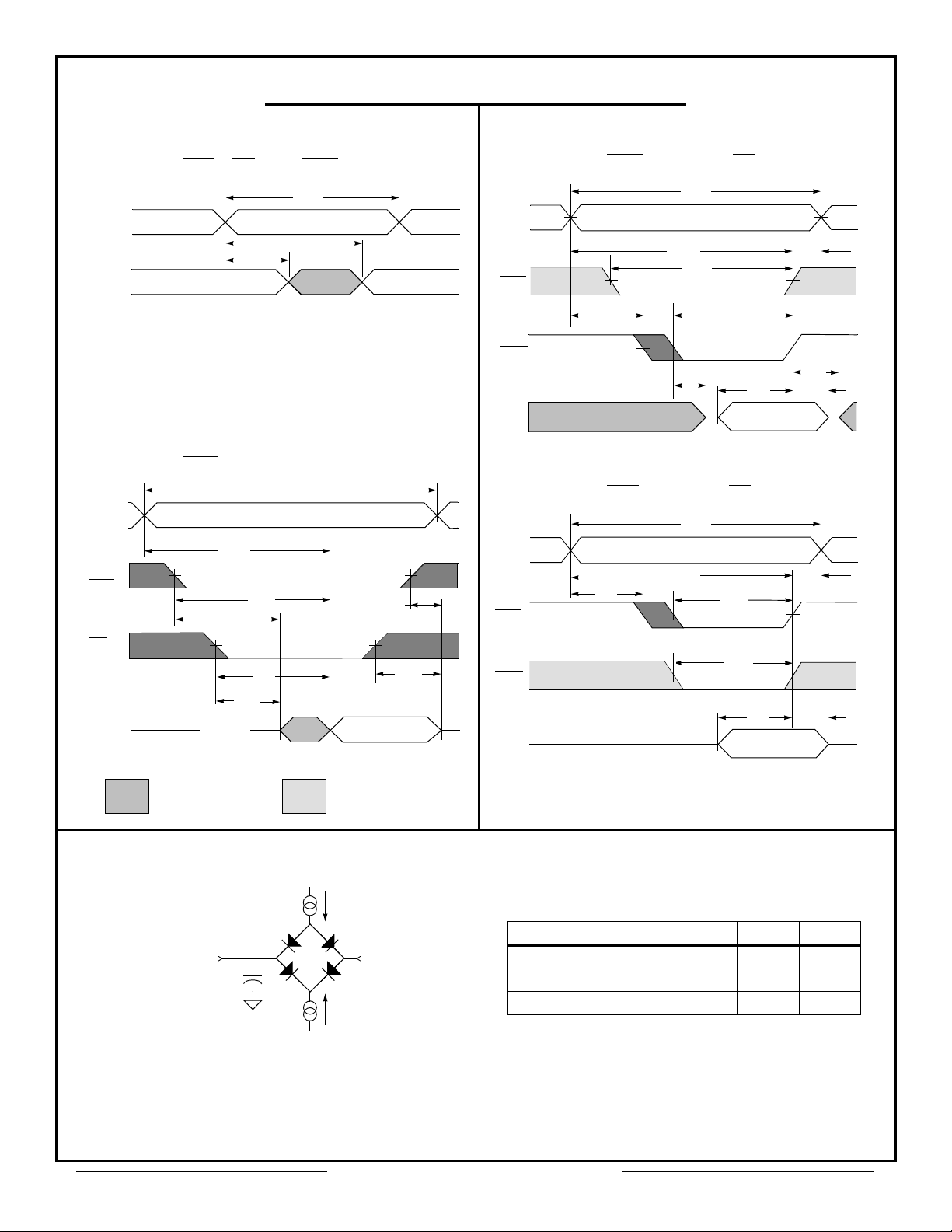

Timing Diagrams — SRAM

Read Cycle Timing Diagrams

Read Cycle 1 (SCE = OE = VIL, SWE = VIH)

tRC

A0-18

tAA

tOH

DI/O

Read Cycle 2 (SWE = VIH)

tRC

A0-18

tAA

SCE

OE

DI/O

tCLZ

SEE NOTE

tOLZ

SEE NOTE

High Z

tACE

OE

t

SEE NOTE

Data Valid

Data ValidPrevious Data Valid

tCHZ

t

OHZ

SEE NOTE

Write Cycle Timing Diagrams

Write Cycle (SWE Controlled, OE = VIH)

tWC

A0-18

tAW tAH

tWHZ

tCW

tDW

Data Valid

tWC

tAW

tCW

tWP

tDW

Data Valid

SCE

tAS tWP

SWE

DI/O

Write Cycle (SCE

A0-18

tAS

SCE

SWE

DI/O

SEE NOTE

Controlled, OE = VIH )

tOW

tDH

tAH

tDH

UNDEFINED

DON’T CARE

Note: Guaranteed by design, but not tested.

AC Test Circuit

Current Source

IOL

Z ~ 1.5 V (Bipolar Supply)

To Device Under Test

C

L = 50 pF

Current Source

V

OH

I

Input and Output Timing Reference Level 1.5 V

Notes:

1) V

Z is programmable from -2V to +7V. 2) IOL and IOH programmable from 0 to 16 mA. 3) Tester Impedance

Z

O =75Ω. 4) VZ is typically the midpoint of VOH and VOL. 5) IOL and IOH are adjusted to simulate a typical resistance

load circuit. 6) ATE Tester includes jig capacitance.

Aeroflex Circuit Technology SCD3852 REV A 5/20/98 Plainview NY (516) 694-6700

4

AC Test Conditions

Parameter Typical Units

Input Pulse Level 0 – 3.0 V

Input Rise and Fall 5 ns

Loading...

Loading...