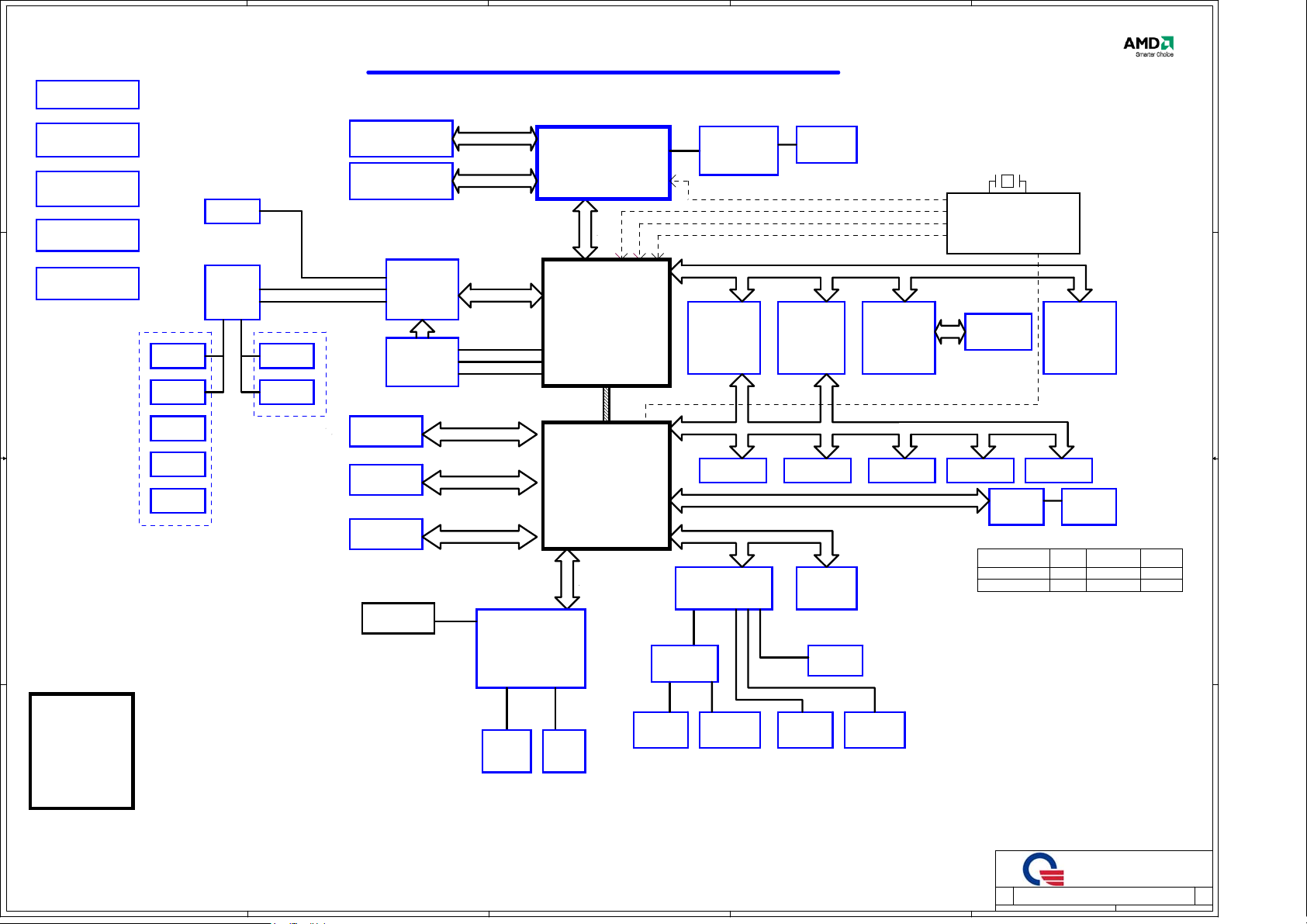

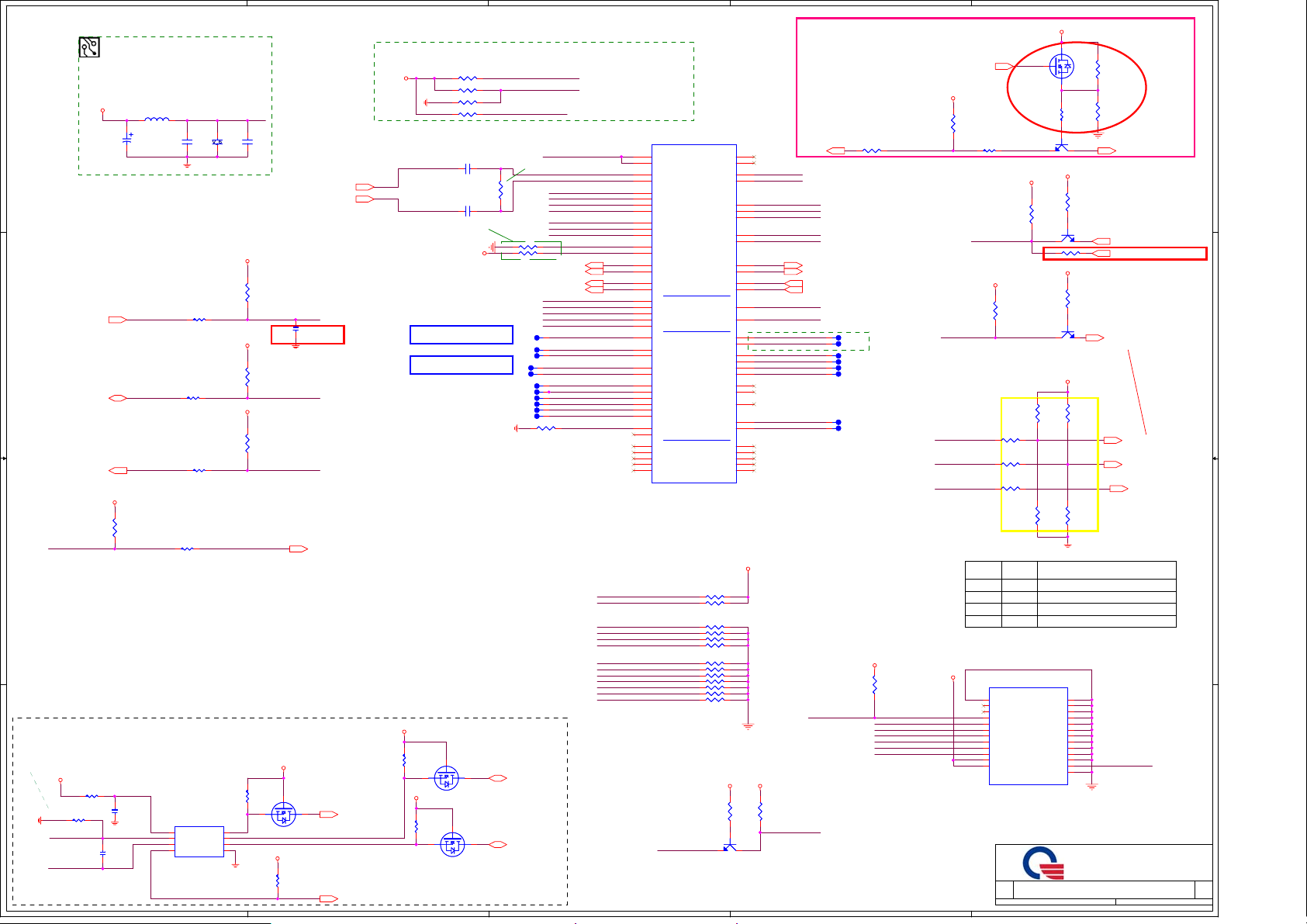

Acer TravelMate 7230, TravelMate 7530 Schematics

5

4

3

2

1

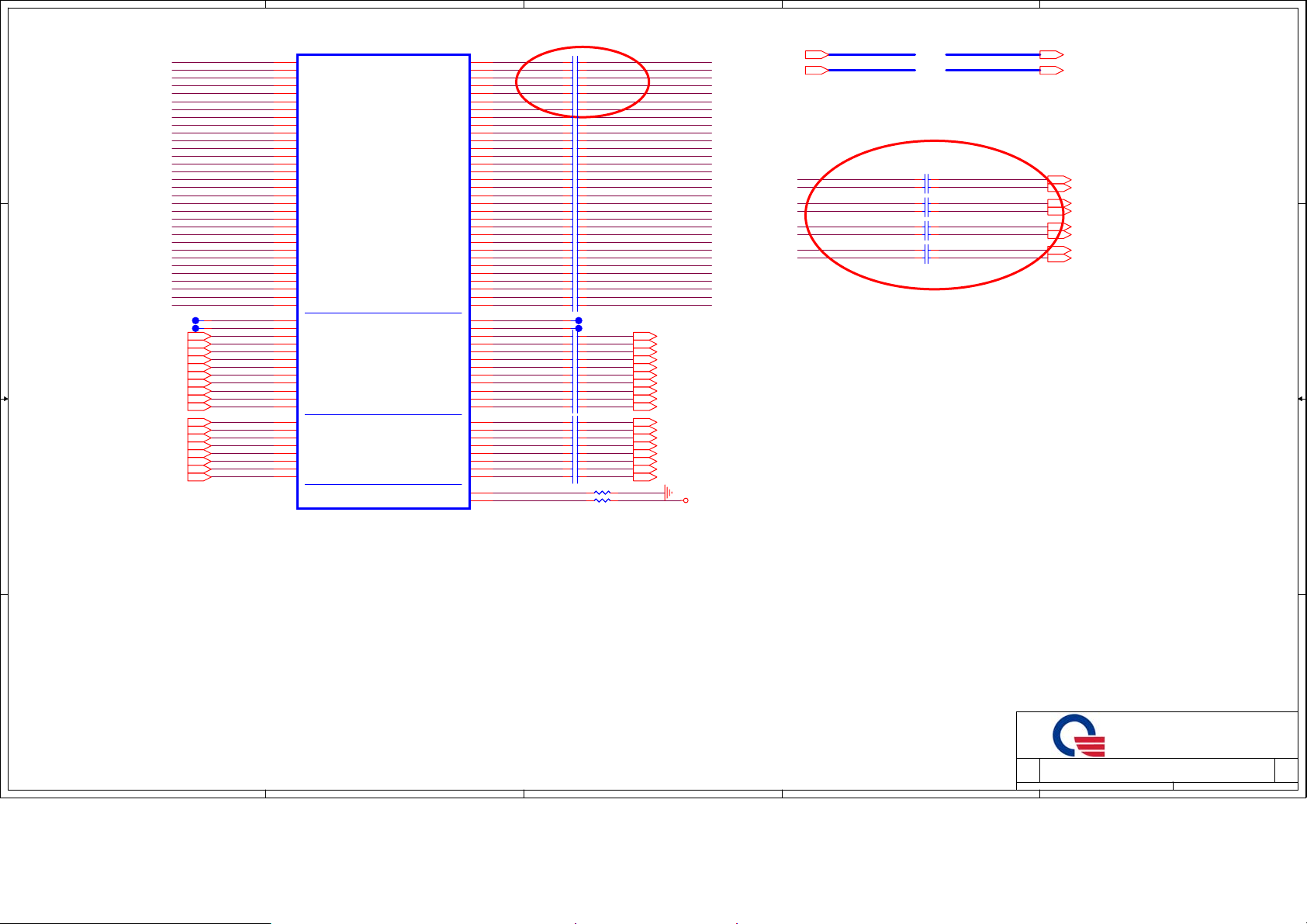

ZY7 SYSTEM BLOCK DIAGRAM

CPU CORE ISL6265A

PAGE 29

D D

NB CORE (RT8202)

PAGE XX

DDR II SMDDR_VTERM

1.8VSUS(TPS51116REGR)

SYSTEM POWER

ISL6237

SYSTEM CHARGER

(ISL6251A)

C C

PAGE 31

PAGE 28

PAGE 27

DVI-D

PAGE 26

CRT

PAGE 26

AUDIO

PAGE 26

LAN

PAGE 26

USB

PAGE 26

LVDS

PAGE 18

SWITCH

LVDS

CRT

HDMI

HDMI

PAGE 18

CRT

PAGE 18

M/B

DOCKING

B B

PCB STACK UP

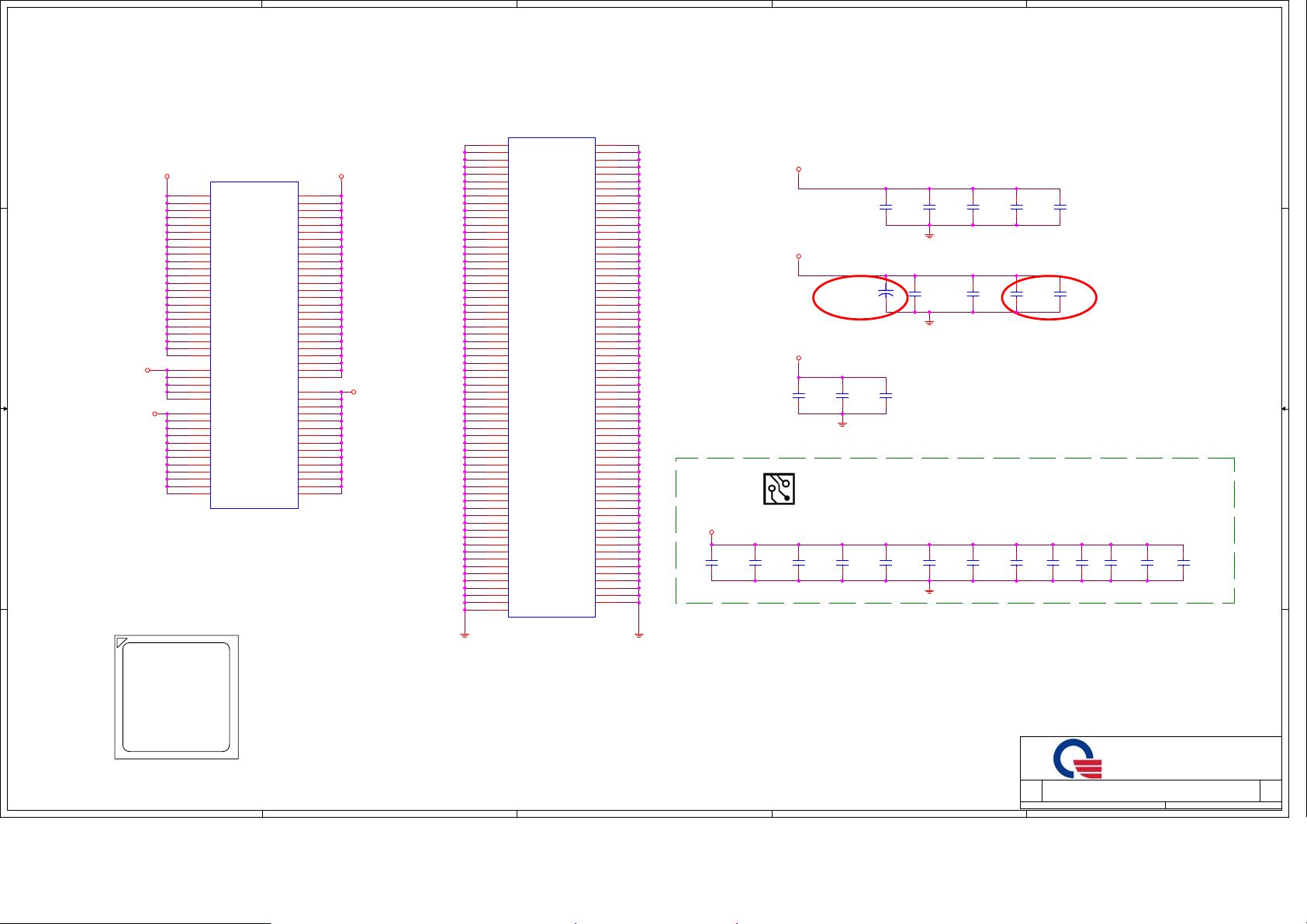

DDRII-SODIMM1

PAGE 7

DDRII-SODIMM2

PAGE 7

MXM

Connector

PAGE 17

Internal

selector

Resistor

PAGE 17

SATA - HDD

PAGE 20

SATA - HDD

PAGE 20

ODD(SATA)

PAGE 20

Keyboard

PAGE 25

DDRII 667/800 MHz

DDRII 667/800 MHz

PCI-Express 16X

LVDS

CRT

HDMI

SATA0

SATA1

SATA4

KBC

(WPCE775)

AMD Griffin

S1G2 Processor

638P (uPGA)/35W

PAGE 3,4,5,6

HT3

LINK

NORTH BRIDGE

/

21mm X 21mm, 528pin BGA

PAGE 8,9,10,11

PCIE X4

21mm X 21mm, 528pin BGA

PAGE 12,13,14,15,16

LPC

PAGE 25

RS780MRX780

SOUTH BRIDGE

SB700

4.5W(Ext)

4.3W(Int)

Lion

Sabie

CPU THERMAL

SENSOR

CPU Fan

PAGE 5

CPU_CLK

NBGFX_CLK

NBGPP_CLK

SBLINK_CLK

PCI-E

PCIE2 / 3 PCIE1 PCIE4

Mini PCI-E

Card

Wireless /TV

PAGE 19

1,11

USB2.0

3,4

8,0

USB2.0 Ports Bluetooth PC-cam

x4

X1 X1X2

Express

Card

(NEW CARD)

PAGE 19 PAGE 21

5

PCI BUS / 33MHz

Azalia

Azalia AudioController

RealTek ALC268

PAGE 22

MDC 1.5

PAGE 22

Audio

Amplifier

Int MIC

LAN

PCIE-LAN

BCM5764M

(10/100/GagaLAN)

PAGE 18PAGE 19PAGE 19

x1x1

14.318MHz

CLOCK GEN

ICS9LPRS476AKLFT-->HP

SLG8SP626VTR-->HP

RTM880N-795 -->HP

RJ45

PAGE 21

SBSRC_CLK

1026

Fingerprint

PAGE 19

x1

PCI ROUTING

TABLE

O2 OZ601

PAGE 23

USB Docking

x1

PAGE 2

PCIE5

X1

JMB385 4 IN 1

CARD READER

PAGE 24

7

PAGE 19

PCMCIA

CARD BUS

PAGE 23

IDSEL

AD20 OZ601REQ0# / GNT0#

INTERUPT DEVICE

INTF#

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1

LAYER 4 : IN2

Touch

Pad

PAGE 20 PAGE 25

SPI

ROM

Speaker

SPIDF/Phone

Jack

Line in

MIC Jack

LAYER 5 : SVCC

LAYER 6 : BOT

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZY7

ZY7

ZY7

135Thursday, June 26, 2008

135Thursday, June 26, 2008

1

135Thursday, June 26, 2008

1A

1A

1A

of

of

of

5

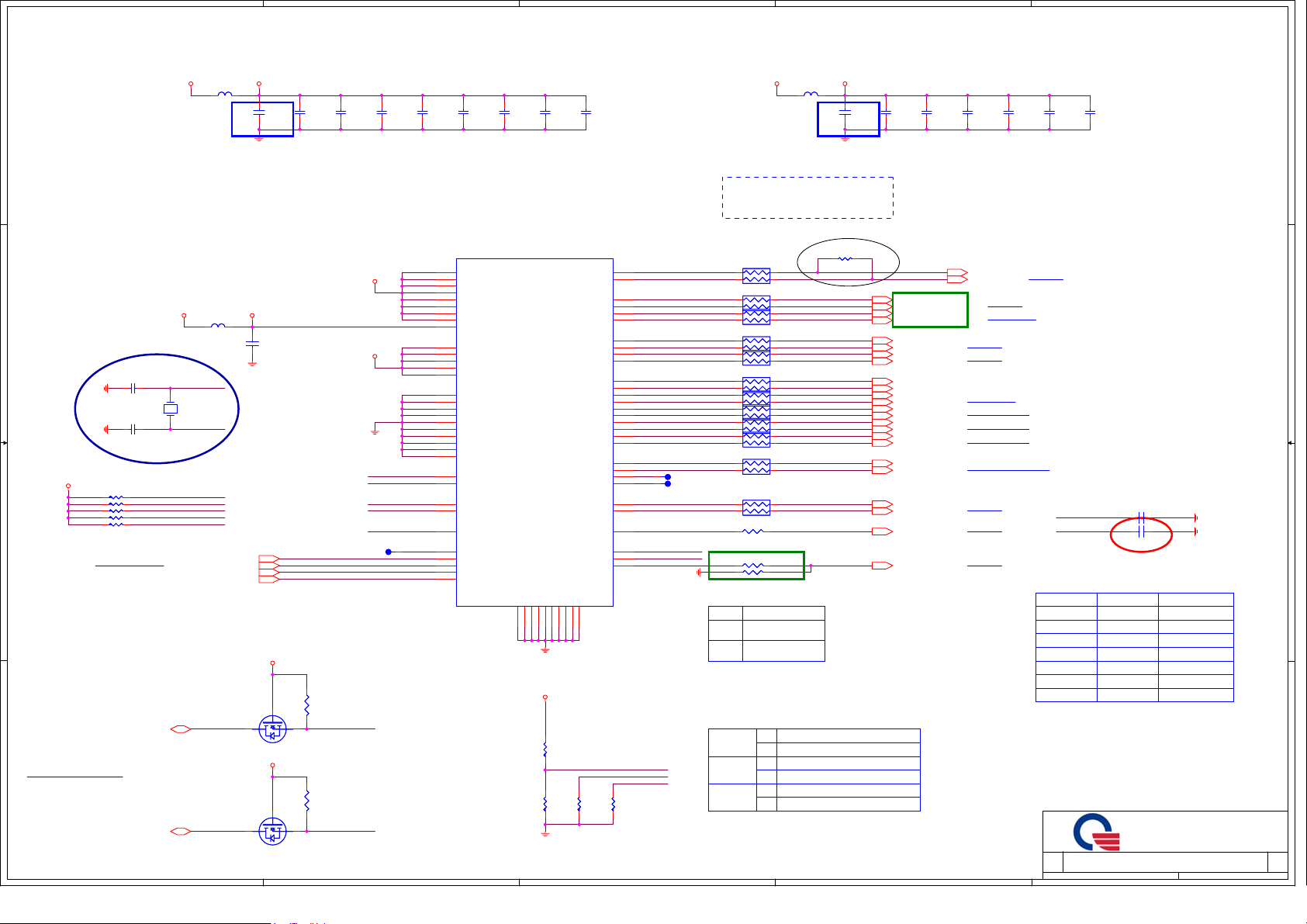

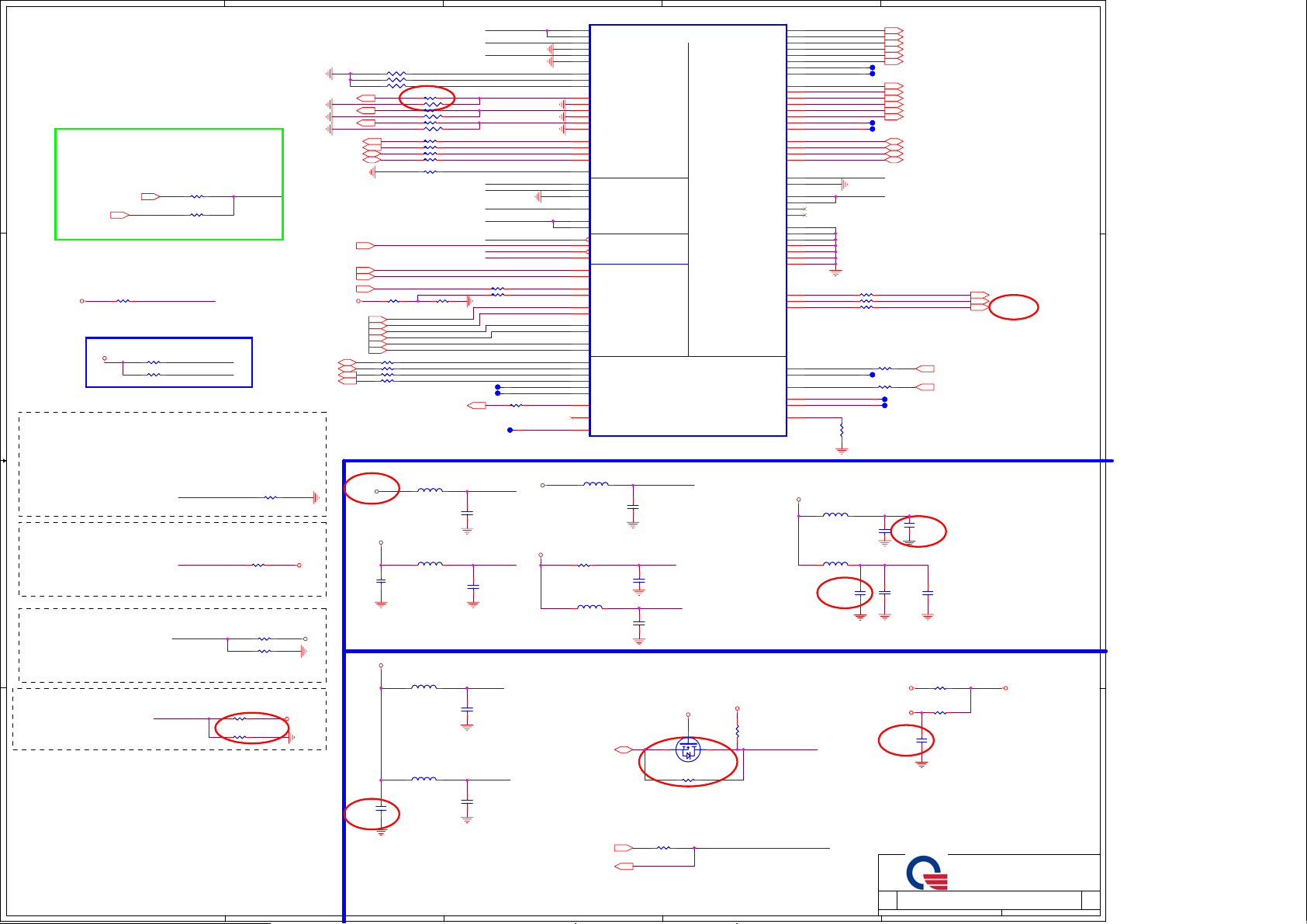

CLK_GEN_SLG8SP628

4

3

2

1

+3V +3V_CLK_VDD +1.2V +1.2V_CLK_VDDIO

L39

L39

BK1608HS600

BK1608HS600

D D

Change C1000/C1008 from 10u to 22u.-1001

+3V

L38

L38

BK1608HS600

21

CG_XIN

Y3

Y3

14.318MHZ

14.318MHZ

CG_XOUT

BK1608HS600

C C

C367

C367

20p/50V_4

20p/50V_4

C366

C366

20p/50V_4

20p/50V_4

+3V_CLK_48

12

C363

C363

2.2U/6.3V/06

2.2U/6.3V/06

C399

C399

22U-10V_8

22U-10V_8

Follow CLK 14.318 Check 20p 11/19

+3V_CLK_VDD

R272 8.2K_4R272 8.2K_4

R286 8.2K_4R286 8.2K_4

R264 8.2K_4R264 8.2K_4

R277 8.2K_4R277 8.2K_4

R283 8.2K_4R283 8.2K_4

B B

New Card CLKREQ#

NEW_CLKREQ#

LAN_CLKREQ#

CLK_PD#

MINI_CLKREQ#

TV_CLKREQ#

NEW_CLKREQ#13,19

MINI_CLKREQ#19

TV_CLKREQ#19

LAN_CLKREQ#21

C365

C365

.1u/10V_4

.1u/10V_4

C373

C373

.1u/10V_4

.1u/10V_4

+3V_CLK_VDD

+1.2V_CLK_VDDIO

CG_XIN

CG_XOUT

CGCLK_SMB

CGDAT_SMB

CLK_PD#

T87T87

C394

C394

C364

C364

.1u/10V_4

.1u/10V_4

.1u/10V_4

.1u/10V_4

ICS9LPRS480 P/N :

SLG8SP628

RTM880N-796

4

16

26

35

40

48

55

56

63

11

17

25

34

47

1

7

10

18

24

33

43

46

52

60

61

62

2

3

51

23

45

44

39

38

C409

C409

.1u/10V_4

.1u/10V_4

U14

U14

VDDDOT

VDDSRC

VDDATIG

VDDSB_SRC

VDDSATA

VDDCPU

VDDHTT

VDDREF

VDD48

VDDSRC_IO0

VDDSRC_IO1

VDDATIG_IO

VDDSB_SRC_IO

VDDCPU_IO

GND48

GNDDOT

GNDSRC0

GNDSRC1

GNDATIG

GNDSB_SRC

GNDSATA

GNDCPU

GNDHTT

GNDREF

X1

X2

SMBCLK

SMBDAT

PD#

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

SLG8SP628

SLG8SP628

C390

C390

C402

C402

.1u/10V_4

.1u/10V_4

.1u/10V_4

.1u/10V_4

P/N : AL8SP628000

P/N : AL000880000

CPUK8_0C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

QFN64

QFN64

SRC6T/SATAT

SRC6C/SATAC

SRC7T/27M_SS

SRC7C/27M_NS

HTT0T/66M

HTT0C/66M

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

TGND065TGND166TGND267TGND368TGND469TGND570TGND671TGND772TGND873TGND9

C381

C381

.1u/10V_4

.1u/10V_4

CPUK8_0T

ATIG0T

ATIG0C

ATIG1T

ATIG1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

SRC2C

SRC3T

SRC3C

SRC4T

SRC4C

48MHz_0

74

50

49

30

29

28

27

37

36

32

31

22

21

20

19

15

14

13

12

9

8

42

41

6

5

54

53

64

59

58

57

CPUCLKP_R

CPUCLKN_R

NBGFX_CLKP_R

NBGFX_CLKN_R

CLK_PCIE_MXM_R

CLK_PCIE_MXM#_R

SBLINK_CLKP_R

SBLINK_CLKN_R

SBSRC_CLKP_R

SBSRC_CLKN_R

NBGPP_CLKP_R

NBGPP_CLKN_R

CLK_PCIE_NEW_R

CLK_PCIE_NEW#_R

CLK_PCIE_MINI_R

CLK_PCIE_MINI#_R

CLK_PCIE_TV_R

CLK_PCIE_TV#_R

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

CLK_PCIE_CR_R

CLK_PCIE_CR#_R

T82T82

T81T81

NBHT_REFCLKP_R

NBHT_REFCLKN_R

CLK_48M_USB_R

SEL_HTT66

SEL_SATA

SEL_27

Clock chip has internal serial terminations

for differencial pairs, external resistors are

reserved for debug purpose.

Place within 0.5"

of CLKGEN

RP25 0X2RP25 0X2

1

3

RP35 0X2RP35 0X2

1

3

RP34 *EV^0X2RP34 *EV^0X2

1

3

RP30 0X2RP30 0X2

1

3

RP36 0X2RP36 0X2

1

3

RP33 *EV^0X2RP33 *EV^0X2

1

3

RP32 0X2RP32 0X2

1

3

RP31 0X2RP31 0X2

1

3

RP29 0X2RP29 0X2

1

3

RP27 0X2RP27 0X2

1

3

RP28 0X2RP28 0X2

1

3

RP26 0X2RP26 0X2

1

3

R268 33_4R268 33_4

R265 158/F_4R265 158/F_4

R250 90.9/F_4R250 90.9/F_4

R1004/R1005 (value may change)

1.8V 82.5R/130RRX780

+3V

RS780 1.1V 158R/90.9R

Clock Gen I2C

R275

Q26

Q26

RHU002N06

RHU002N06

PDAT_SMB7,13,18,19

A A

Check Chipset Power Domain

PCLK_SMB7,13,18,19

5

3

Q25

Q25

RHU002N06

RHU002N06

3

+3V

R275

2

10K_4

10K_4

CGDAT_SMBPDAT_SMB

1

R274

R274

10K_4

10K_4

2

CGCLK_SMBPCLK_SMB

1

4

+3V_CLK_VDD

R260

R260

*8.2K_4

*8.2K_4

R259

R259

8.2K_4

8.2K_4

R258

R258

8.2K_4

8.2K_4

SEL_SATA

SEL_HTT66

SEL_27

R249

R249

8.2K_4

8.2K_4

SEL_HTT66

SEL_SATA

SEL_27

* default

3

L42

L42

BK1608HS600

BK1608HS600

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

NB_OSC

66 MHz 3.3V single ended HTT clock

1

*0

100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

1*

0

100 MHz spreading differential SRC clock

27MHz and 27M SS outputs

1

0*

100 MHz SRC clock

C407

C407

22U-10V_8

22U-10V_8

R255

R255

*261/F_4

*261/F_4

RES CHIP 82.5 1/16W +-1%(0402) --> CS08252FB11

RES CHIP 130 1/16W +-1%(0402)L-F --> CS11302FB15

RES CHIP 158 1/16W +-1%(0402) --> CS11582FB00

RES CHIP 90.9 1/16W +-1%(0402) --> CS09092FB15

C405

C405

C378

C378

C406

.1u/10V_4

.1u/10V_4

C406

.1u/10V_4

.1u/10V_4

.1u/10V_4

.1u/10V_4

CHECK

CPU_CLKP

CPU_CLKN

NBGFX_CLKP 10

NBGFX_CLKN 10

CLK_PCIE_MXM 17

CLK_PCIE_MXM# 17

External VGA Card only

External VGA Card only

SBLINK_CLKP 10

SBLINK_CLKN 10

SBSRC_CLKP 12

SBSRC_CLKN 12

NBGPP_CLKP 10

NBGPP_CLKN 10

CLK_PCIE_NEW 19

CLK_PCIE_NEW# 19

CLK_PCIE_MINI 19

CLK_PCIE_MINI# 19

CLK_PCIE_TV 19

CLK_PCIE_TV# 19

CLK_PCIE_LAN 21

CLK_PCIE_LAN# 21

CLK_PCIE_CR 24

CLK_PCIE_CR# 24

NBHT_REFCLKP 10

NBHT_REFCLKN 10

CLK_48M_USB 13

EXT_NB_OSC 10

2

CPU_CLKP 5

CPU_CLKN 5

To NB

To MXM Card

To NB

To SB

To New Card

To Mini PCIE Slot

To TV PCIE Slot

To LAN Controller

To Card Reader Controller

To NB

To SB

To NB

C374

C374

C389

C408

C408

.1u/10V_4

.1u/10V_4

To CPU

REV B:Change to Stuff 22PF for

EMI request --0215

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

C389

.1u/10V_4

.1u/10V_4

.1u/10V_4

.1u/10V_4

CLK_48M_USB_R

SEL_27

CLOCK GENERATOR_SLG8SP628

CLOCK GENERATOR_SLG8SP628

CLOCK GENERATOR_SLG8SP628

C372 *10p_4C372 *10p_4

C350 22P/50V_4C350 22P/50V_4

RX780 RS780

100M DIFF

100M DIFF

14M SE (1.8V)

NC vref

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

14M SE (1.1V)

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

100M DIFF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZY7

ZY7

ZY7

1A

1A

1A

of

of

of

235Thursday, June 26, 2008

235Thursday, June 26, 2008

235Thursday, June 26, 2008

5

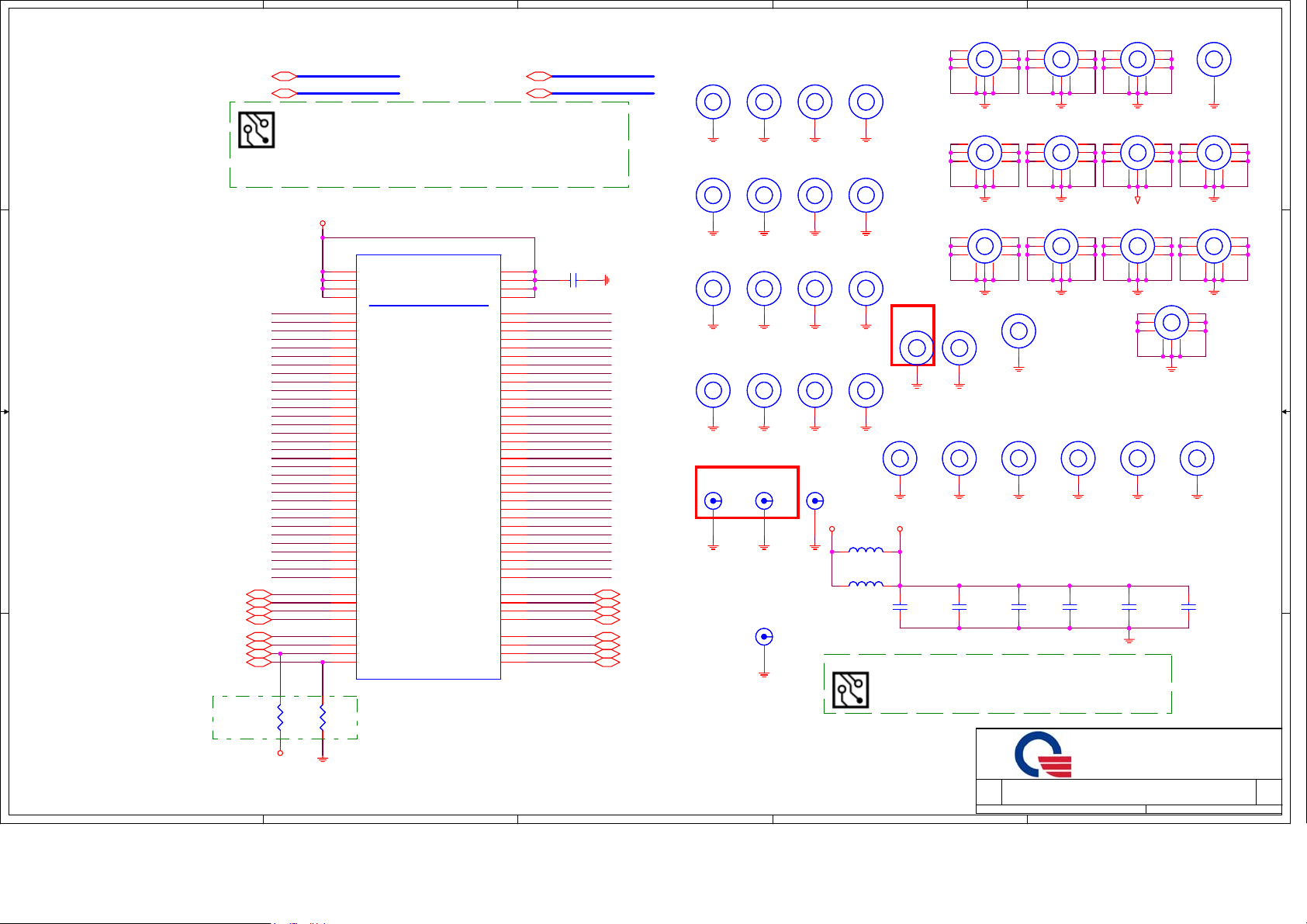

HT_RXD#[15..0]8 HT_TXD[15..0]8

HT_RXD[15..0]8

D D

HT_RXD#[15..0]

HT_RXD[15..0]

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

VLDT_RUN

D1

D2

D3

R133

R133

*51_4

*51_4

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

C C

B B

HT_CPU_UPCLK08

HT_CPU_UPCLK#08

HT_CPU_UPCLK18

HT_CPU_UPCLK#18

HT_CPU_UPCTL08

HT_CPU_UPCTL#08

HT_CPU_UPCTL18

HT_CPU_UPCTL#18

A A

5

NO STUB

for HT3

HT_RXD0

HT_RXD#0

HT_RXD1

HT_RXD#1

HT_RXD2

HT_RXD#2

HT_RXD3

HT_RXD#3

HT_RXD4

HT_RXD#4

HT_RXD5

HT_RXD#5

HT_RXD6

HT_RXD#6

HT_RXD7

HT_RXD#7

HT_RXD8

HT_RXD#8

HT_RXD9

HT_RXD#9

HT_RXD10

HT_RXD#10

HT_RXD11

HT_RXD#11

HT_RXD12

HT_RXD#12

HT_RXD13

HT_RXD#13

HT_RXD14

HT_RXD#14

HT_RXD15

HT_RXD#15

R135

R135

*51_4

*51_4

VLDT_RUN

4

U25A

U25A

HT LINK

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

HT LINK

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

Processor Socket

SOCKET_638_PIN

4

3

HOLE27

HT_TXD[15..0]

HT_TXD#[15..0]8

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

HT_TXD#[15..0]

C519

C519

4.7u/6.3V_6

4.7u/6.3V_6

HT_TXD0

HT_TXD#0

HT_TXD1

HT_TXD#1

HT_TXD2

HT_TXD#2

HT_TXD3

HT_TXD#3

HT_TXD4

HT_TXD#4

HT_TXD5

HT_TXD#5

HT_TXD6

HT_TXD#6

HT_TXD7

HT_TXD#7

HT_TXD8

HT_TXD#8

HT_TXD9

HT_TXD#9

HT_TXD10

HT_TXD#10

HT_TXD11

HT_TXD#11

HT_TXD12

HT_TXD#12

HT_TXD13

HT_TXD#13

HT_TXD14

HT_TXD#14

HT_TXD15

HT_TXD#15

HT_CPU_DWNCLK0 8

HT_CPU_DWNCLK#0 8

HT_CPU_DWNCLK1 8

HT_CPU_DWNCLK#1 8

HT_CPU_DWNCTL0 8

HT_CPU_DWNCTL#0 8

HT_CPU_DWNCTL1 8

HT_CPU_DWNCTL#1 8

3

HOLE27

*MINI_HOLE

*MINI_HOLE

HOLE9

HOLE9

CPU_HOLE

CPU_HOLE

HOLE8

HOLE8

MXM_HOLE

MXM_HOLE

HOLE6

HOLE6

*EV^MXM1_HOLE

*EV^MXM1_HOLE

1

1

1

1

PAD2

PAD2

EMIPAD

EMIPAD

1

HOLE28

HOLE28

MINI_HOLE

MINI_HOLE

1

HOLE10

HOLE10

CPU_HOLE

CPU_HOLE

1

HOLE17

HOLE17

MXM_HOLE

MXM_HOLE

1

HOLE21

HOLE21

*EV^MXM1_HOLE

*EV^MXM1_HOLE

1

PAD3

PAD3

EMIPAD

EMIPAD

1

SPAD1

SPAD1

*SPAD

*SPAD

1

HOLE36

HOLE36

MINI_HOLE

MINI_HOLE

HOLE19

HOLE19

CPU_HOLE

CPU_HOLE

HOLE16

HOLE16

MXM_HOLE

MXM_HOLE

HOLE11

HOLE11

1

1

1

MDC_HOLE

MDC_HOLE

1

PAD1

PAD1

*EMIPAD

*EMIPAD

1

+1.2V

HOLE37

HOLE37

MINI_HOLE

MINI_HOLE

HOLE20

HOLE20

CPU_HOLE

CPU_HOLE

HOLE7

HOLE7

MXM_HOLE

MXM_HOLE

HOLE13

HOLE13

MDC_HOLE

MDC_HOLE

L50

L50

FBJ3216HS800_1206

FBJ3216HS800_1206

L54

L54

FBJ3216HS800_1206

FBJ3216HS800_1206

80 ohm(4A)

LAYOUT: Place bypass cap on topside of board

2

HOLE2

5

6

7

5

6

7

5

6

7

HOLE2

*H-C295D118P2

*H-C295D118P2

2

3

4

HOLE25

HOLE25

*H-C295D118P2

*H-C295D118P2

2

3

4

HOLE33

HOLE33

*H-C295D118P2

*H-C295D118P2

2

3

4

HOLE14

HOLE14

*H-C295D118P2

*H-C295D118P2

2

3

4

1

8

9

HOLE4

1

1

HOLE39

HOLE39

1

*FAN_HOLE

*FAN_HOLE

1

HOLE4

*H-C295D118P2

*H-C295D118P2

2

3

4

HOLE32

HOLE32

*H-C295D118P2

*H-C295D118P2

2

3

4

HOLE38

HOLE38

FAN_HOLE

FAN_HOLE

1

1

8

9

1

8

9

5

2

6

3

7

4

5

2

6

3

7

4

5

2

6

3

7

4

HOLE15

HOLE15

*NONP_HOLE1

*NONP_HOLE1

1

HOLE5

HOLE5

*H-C295D118P2

*H-C295D118P2

1

8

9

HOLE35

HOLE35

*H-C295D118P2

*H-C295D118P2

1

8

9

HOLE34

HOLE34

*H-C295D118P2

*H-C295D118P2

1

8

9

REV B: Add Hole39 for ME request---0215

1

HOLE26

HOLE26

ODD1_HOLE

ODD1_HOLE

VLDT_RUN

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

1

C555

C555

4.7u/6.3V_6

4.7u/6.3V_6

2

HOLE30

HOLE30

ODD1_HOLE

ODD1_HOLE

HOLE31

HOLE31

HDD1_HOLE

HDD1_HOLE

1

Note:on MCP77,(HT=+1.1V) and CPU(HT=+1.2V)

and therefore cannot be connected to the

same HT power rail.

C560

C560

4.7u/6.3V_6

4.7u/6.3V_6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

HOLE29

HOLE29

HDD1_HOLE

HDD1_HOLE

1

C569

C569

.22U_4

.22U_4

AMD Griffin HT I/F

AMD Griffin HT I/F

AMD Griffin HT I/F

HOLE22

HOLE22

HDD2_HOLE

HDD2_HOLE

1

C527

C527

.22U_4

.22U_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

8

8

8

1

9

1

9

ADOGND

1

9

2

3

4

1

C522

C522

180P_4

180P_4

1

HOLE23

HOLE23

*H-C295D118P2

*H-C295D118P2

5

6

7

HOLE24

HOLE24

*H-C295D118P2

*H-C295D118P2

5

2

6

3

7

4

HOLE1

HOLE1

*H-C295D118P2

*H-C295D118P2

5

2

6

3

7

4

HOLE3

HOLE3

*H-C295D118P2

*H-C295D118P2

5

6

7

1

8

9

HOLE18

HOLE18

HDD2_HOLE

HDD2_HOLE

1

C565

C565

180P_4

180P_4

ZY7

ZY7

ZY7

335Thursday, June 26, 2008

335Thursday, June 26, 2008

335Thursday, June 26, 2008

1

1

5

6

7

1

8

9

5

6

7

1

8

9

1A

1A

1A

of

of

of

A

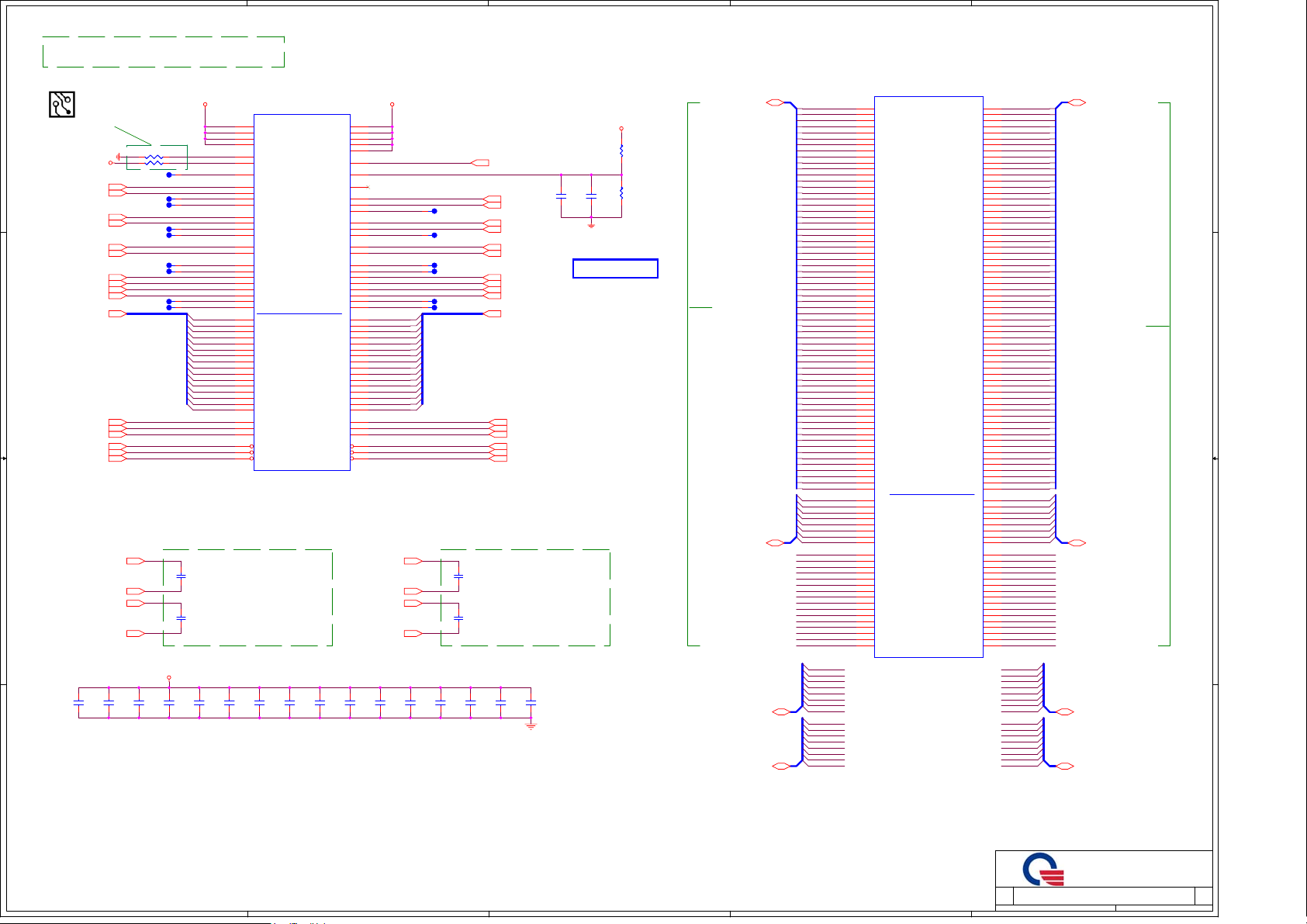

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

1 2

T27T27

T13T13

T10T10

T9T9

T11T11

T22T22

T20T20

T15T15

T16T16

+SMDDR_VTERM

C147

C147

4.7u/6.3V_6

4.7u/6.3V_6

+SMDDR_VTERM

12

C93

C93

4.7u/6.3V_6

4.7u/6.3V_6

M_ZP

M_ZN

MEM_MA_RESET#

M_A1_ODT0

M_A1_ODT1

M_A1_CS#0

M_A1_CS#1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

C264

C264

1.5pF_4

1.5pF_4

C90

C90

1.5pF_4

1.5pF_4

C255

C255

.22U_4

.22U_4

PLACE THEM CLOSE TO

M_A_CLKOUT17

M_A_CLKOUT1#7

M_A_CLKOUT77

M_A_CLKOUT7#7

M_A_A[0..15]7

CPU WITHIN 1"

+1.8VSUS

M_A_ODT07

M_A_ODT17

M_A_CS#07

M_A_CS#17

M_A_CKE07

M_A_CKE17

M_A_BS#07

M_A_BS#17

M_A_BS#27

M_A_RAS#7

M_A_CAS#7

M_A_WE#7

M_A_CLKOUT17

M_A_CLKOUT1#7

M_A_CLKOUT77

M_A_CLKOUT7#7

C92

C92

4.7u/6.3V_6

4.7u/6.3V_6

C259

C259

4.7u/6.3V_6

4.7u/6.3V_6

R367 39.2/F_4R367 39.2/F_4

R368 39.2/F_4R368 39.2/F_4

4 4

3 3

2 2

U25B

U25B

D10

VTT1

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

C10

VTT2

B10

VTT3

AD10

VTT4

AF10

MEMZP

AE10

MEMZN

H16

RSVD_M1

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U19

MA0_CS_L1

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

AA16

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2

Processor Socket

SOCKET_638_PIN

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C97

C95

C95

.22U_4

.22U_4

C97

.22U_4

.22U_4

C261

C261

.22U_4

.22U_4

VTT_SENSE

MEMVREF

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

VTT5

VTT6

VTT7

VTT8

VTT9

RSVD_M2

MB_CKE0

MB_CKE1

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

C94

C94

1000P_4

1000P_4

B

+SMDDR_VTERM

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

M_B_CLKOUT17

M_B_CLKOUT1#7

M_B_CLKOUT77

M_B_CLKOUT7#7

C96

C96

1000P_4

1000P_4

M_B1_ODT0

M_B1_CS#0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

C254

C254

1000P_4

1000P_4

CPU_VTT_SENSE

CPU_M_VREF

C260

C260

1000P_4

1000P_4

C

D

E

Processor DDR2 Memory Interface

U25C

U25C

MEM:DATA

M_B_DQ[0..63]7

+1.8VSUS

R100

R100

1K/F_4

C89

C89

1000p_4

1000p_4

1K/F_4

R101

R101

1K/F_4

1K/F_4

CPU_VTT_SENSE 31

C159

M_B_ODT0 7

T8T8

T12T12

T17T17

T18T18

T14T14

T19T19

M_B_ODT1 7

M_B_CS#0 7

M_B_CS#1 7

M_B_CKE0 7

M_B_CKE1 7

M_B_CLKOUT1 7

M_B_CLKOUT1# 7

M_B_CLKOUT7 7

M_B_CLKOUT7# 7

M_B_A[0..15] 7

C159

.1u/10V_4

.1u/10V_4

DEL T6,7,8,10.--0930

To reverse SODIMM socket

M_B_BS#0 7

M_B_BS#1 7

M_B_BS#2 7

M_B_RAS# 7

M_B_CAS# 7

M_B_WE# 7

M_B_DM[0..7]7

C252

C252

1.5pF_4

1.5pF_4

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C100

C100

1.5pF_4

1.5pF_4

C98

C98

C99

C257

C257

180P_4

180P_4

C256

C256

180P_4

180P_4

180P_4

180P_4

C99

180P_4

180P_4

M_B_DQS[0..7]7

M_B_DQS#[0..7]7

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS#0

M_B_DQS1

M_B_DQS#1

M_B_DQS2

M_B_DQS#2

M_B_DQS3

M_B_DQS#3

M_B_DQS4

M_B_DQS#4

M_B_DQS5

M_B_DQS#5

M_B_DQS6

M_B_DQS#6

M_B_DQS7

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

MEM:DATA

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2

Processor Socket

SOCKET_638_PIN

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS#0

M_A_DQS1

M_A_DQS#1

M_A_DQS2

M_A_DQS#2

M_A_DQS3

M_A_DQS#3

M_A_DQS4

M_A_DQS#4

M_A_DQS5

M_A_DQS#5

M_A_DQS6

M_A_DQS#6

M_A_DQS7

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQ[0..63] 7

To normal SODIMM socket

M_A_DM[0..7] 7

M_A_DQS[0..7] 7

M_A_DQS#[0..7] 7

1 1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

PROJECT :

AMD Griffin DDRII MEMORY I/F

AMD Griffin DDRII MEMORY I/F

AMD Griffin DDRII MEMORY I/F

ZY7

ZY7

ZY7

435Thursday, June 26, 2008

435Thursday, June 26, 2008

E

435Thursday, June 26, 2008

1A

1A

1A

of

of

of

5

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

CPU_VDDA_RUN

+2.5V

D D

CPU_PWRGD12

C C

CPU_LDT_STOP#10,12

CPU_LDT_RST#10,12

Add pull up

CPU_LDT_REQ#_CPU

B B

CPU H/W MONITOR

2/20/08' Reserve 0 ohm

for CPU thermal issue

on C-test

+3V

A A

R112 47/F_6R112 47/F_6

R615 *0_4R615 *0_4

CPU_THERMDA

10 mil trace /

10 mil space

+1.8VSUS

R448

R448

300_4

300_4

15 MIL

3V_THM

C105

C105

.1u/10V_4

.1u/10V_4

C102

C102

2200P_4

2200P_4

L57

L57

BLM18PG330SN1D_6

BLM18PG330SN1D_6

C602

C602

100U-6.3V_3528

100U-6.3V_3528

5

C593

C593

4.7u/6.3V_6

4.7u/6.3V_6

R439 0_4R439 0_4

R446 0_4R446 0_4

R437 0_4R437 0_4

R449 0_4R449 0_4

Address 98H

U6 G781U6 G781

1

VCC

3

DXN

2

DXP

-OVT4GND

CPU_VDDA_RUN

-ALT

SMDATA

SMCLK

C235

C235

.22U_4

.22U_4

6

7

8

5

C246

C246

3300p/50V_4

3300p/50V_4

+1.8VSUS

R435

R435

300_4

300_4

+1.8VSUS

R447

R447

300_4

300_4

LDT_STOP#

+1.8VSUS

R436

R436

300_4

300_4

LDT_RST#

CPU_LDT_REQ#

R105

R105

10K_4

10K_4

1

Q37 2N7002EQ37 2N7002E

KBSMDATCPU_THERMDC

KBSMCLK

PWRGD_C

+3V

2

+3V

R104

R104

10K_4

10K_4

C652

C652

.1u/10V_4

.1u/10V_4

CPU_LDT_REQ# 10

To SB GPIO

3

To FAN

4

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 390- ( 5%) pulldown to VSS.

+1.8VSUS

CPU_CLKP2

CPU_CLKN2

connect to CPU CORE power FB

+3V

THERM_ALERT# 13

CPUFAN#_ON 20

4

R363 390_4R363 390_4

R366 390_4R366 390_4

R374 *390_4R374 *390_4

R373 1K/F_4R373 1K/F_4

390 Ohm

CPU_CLKP

C262 3900P_4C262 3900P_4

CPU_CLKN

C263 3900P_4C263 3900P_4

place them to CPU within 1.5"

VLDT_RUN

Add PUll H/L RES.--0610

Add PUll H/L RES.--0610

R107

R107

4.7K_4

4.7K_4

+3V

1

R108

R108

4.7K_4

4.7K_4

Q41

Q41

2

2N7002E

2N7002E

3

Q40

Q40

2

2N7002E

2N7002E

1

3

ATHLON Control and Debug

∮

CPU_SID

CPU_SIC

CPU_ALERT

U25D

F10

AF4

AF5

AE6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

AB8

AF7

AE7

AE8

AC8

AF8

AA6

3

U25D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

LDTSTOP_L

C6

LDTREQ_L

SIC

SID

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

C2

TEST9

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2

Processor Socket

SOCKET_638_PIN

LDT_RST#

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2"

R175

R175

169/F_6

169/F_6

R132 44.2/F_4R132 44.2/F_4

R129 44.2/F_4R129 44.2/F_4

CPU_VDD0_FB_H29

CPU_VDD0_FB_L29

CPU_VDD1_FB_H29

CPU_VDD1_FB_L29

T91T91

T32T32

T29T29

T34T34

CPU_TEST25_L_BYPASSCLK_L

T31T31

T94T94

T90T90

T168T168

T93T93

T1T1

T92T92

R165 0_4R165 0_4

2ND_MBDATA 25

3

2ND_MBCLK 25

CPU_VDDA_RUN

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

LDT_RST#

PWRGD_C

LDT_STOP#

CPU_LDT_REQ#_CPU

CPU_SIC

CPU_SID

CPU_ALERT CPU_THERMDC

CPU_HTREF0

CPU_HTREF1

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST23_TSTUPD

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST27_SINGLECHAIN

CPU_TEST9_ANALOGIN

CPU_TEST27_SINGLECHAIN

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST23_TSTUPD

KEY1

KEY2

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

R369 300_4R369 300_4

R559 300_4R559 300_4

R141 300_4R141 300_4

R140 300_4R140 300_4

R450 300_4R450 300_4

R451 300_4R451 300_4

R383 300_4R383 300_4

R371 300_4R371 300_4

R372 300_4R372 300_4

R370 300_4R370 300_4

R379 300_4R379 300_4

R560 300_4R560 300_4

R561 300_4R561 300_4

+1.8VSUS +3V

1 3

Q51

Q51

MMBT3904

MMBT3904

M11

W18

CPU_SVC_R

A6

CPU_SVD_R

A4

CPU_THERMTRIP_L#

AF6

CPU_PROCHOT#

AC7

CPU_MEMHOT#

AA8

W7

CPU_THERMDA

W8

W9

Y9

H6

G6

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST28_H_PLLCHRZ_P

J7

CPU_TEST28_L_PLLCHRZ_N

H8

CPU_TEST17_BP3

D7

CPU_TEST16_BP2

E7

CPU_TEST15_BP1

F7

CPU_TEST14_BP0

C7

C3

K8

C4

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

H18

H19

AA7

D5

C5

+1.8VSUS

R462

R462

R456

R456

10K_4

10K_4

1K/F_4

1K/F_4

H_LDT_RST#

2

Need Check .-1001

CPU_THERMTRIP#13

CPU_VDDIO_FB_H 31

CPU_VDDIO_FB_L 31

VDD_NB_FB_H 29

VDD_NB_FB_L 29

T25T25

T26T26

T35T35

T33T33

T106T106

T105T105

T36T36

T104T104

CPU_DBREQ#

2

CPU_THERMTRIP_L#

R87 0_4R87 0_4

route as differential

as short as possible

testpoint under package

+1.8VSUS

R532

R532

300_4

300_4

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

2

CPU_COREPG16,29,32

+1.8VSUS

R92

R92

300_4

300_4

R91 33_4R91 33_4

CPU_PROCHOT#

+1.8VSUS

CPU_MEMHOT#

CPU_SVC_R

CPU_SVD_R

CPU_PWRGD

VFIX MODE

SVC SVD Voltage Output(CPU Power)

00

001

1

11

HDT CONNECTOR

+1.8VSUS

*ASP-68200-07-25P-LDV

*ASP-68200-07-25P-LDV

1

3

5

7

9

11

13

15

17

19

21

23

1

+1.8VSUS

3

Q15

Q15

R93

1

2

R97

R97

1K_4

1K_4

Q16

Q16

MMBT3904

MMBT3904

R90

R90

330_4

330_4

2

13

R99

R99

*330_4

*330_4

2

*MMBT3904

*MMBT3904

13

2N7002

2N7002

Q14

Q14

MMBT3904

MMBT3904

Q17

Q17

R93

*0_4

*0_4

R96

R96

100K_4

100K_4

SYS_SHDN# 28,32

EC_PROCHOT# 25

SB_PROCHOT# 12

CPUMEMHOT# 25

11/19

2

1 3

+1.8VSUS

+1.8VSUS

R89

R89

300_4

300_4

R88 *0_4R88 *0_4

+1.8VSUS

R122

R122

*300_4

*300_4

connect to CPU CORE power controlier

VID Override Circuit

+1.8VSUS

R433

R433

R434

R434

1K_4

1K_4

1K_4

1K_4

R432 0_4R432 0_4

R431 0_4R431 0_4

R438 0_4R438 0_4

R442

R442

*220_4

*220_4

1.4V

1.2V

1.0V

0.8V

CN22

CN22

GND1

RSVD1

RSVD0

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

TDO

VCC_PROC_IO_21

VCC_PROC_IO_23

KEY

KEY

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

GND2

GND4

GND6

GND8

GND10

GND12

GND14

GND16

GND18

GND20

GND22

RESET_L

GND26

AMD Griffin CTRL & DEBUG

AMD Griffin CTRL & DEBUG

AMD Griffin CTRL & DEBUG

Thursday, June 26, 2008

Thursday, June 26, 2008

Thursday, June 26, 2008

Serial VID Clock

SVC 29

Serial VID Data

SVD 29

PGD_IN 29

R441

R441

*220_4

*220_4

2

4

6

8

10

12

14

16

18

20

22

H_LDT_RST#

24

25

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZY7

ZY7

ZY7

5

5

5

of

of

1

of

1A

1A

1A

35

35

35

A

B

C

D

E

PROCESSOR POWER AND GROUND

4 4

U25F

U25F

AA4

VSS1

AA11

VSS2

AA13

CPU_CORE0 CPU_CORE1

3 3

CPU_VDDNB_CORE

+1.8VSUS

2 2

A1

U25E

U25E

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2

Processor Socket

SOCKET_638_PIN

A26

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

+1.8VSUS

AMD S1g2

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2 SOCKET_638_PIN

Athlon 64 S1g2

Processor Socket

SOCKET_638_PIN

Griffin

uPGA638

1 1

Top View

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+1.8VSUS

C127

C127

4.7u/6.3V_6

4.7u/6.3V_6

CPU_CORE0

CPU_CORE1

CPU_VDDNB_CORE

C214

C214

22U-10V_8

22U-10V_8

C234

C234

C128

C128

4.7u/6.3V_6

4.7u/6.3V_6

4.7u/6.3V_6

4.7u/6.3V_6

C207

C207

22U-10V_8

22U-10V_8

REV B:Del C193, C203, C178 and C184,C185

for ISL request --0226

12

C421

C421

+

+

C174

C174

22U-10V_8

C186

C186

22U-10V_8

22U-10V_8

22U-10V_8

330u_2V_7343

330u_2V_7343

C201

C201

22U-10V_8

22U-10V_8

C218

C218

22U-10V_8

22U-10V_8

C205

C205

.22U_4

.22U_4

C161

C161

.22U_4

.22U_4

C197

C197

.01u/25V_4

.01u/25V_4

C163

C163

.01u/25V_4

.01u/25V_4

C209

C209

180P_4

180P_4

C160

C160

180P_4

180P_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C232

C232

4.7u/6.3V_6

4.7u/6.3V_6

C129

C129

.22U_4

.22U_4

C239

C239

.22U_4

.22U_4

C126

C126

.22U_4

.22U_4

C236

C236

.22U_4

.22U_4

C237

C237

.22U_4

.22U_4

C118

C118

.22U_4

.22U_4

C117

C117

.01u/25V_4

.01u/25V_4

C238

C238

.01u/25V_4

.01u/25V_4

C131

C131

180P_4

180P_4

AF1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

PROJECT :

AMD Griffin PWR & GND

AMD Griffin PWR & GND

AMD Griffin PWR & GND

ZY7

ZY7

ZY7

1A

1A

1A

of

of

of

635Thursday, June 26, 2008

635Thursday, June 26, 2008

E

635Thursday, June 26, 2008

A

B

C

D

E

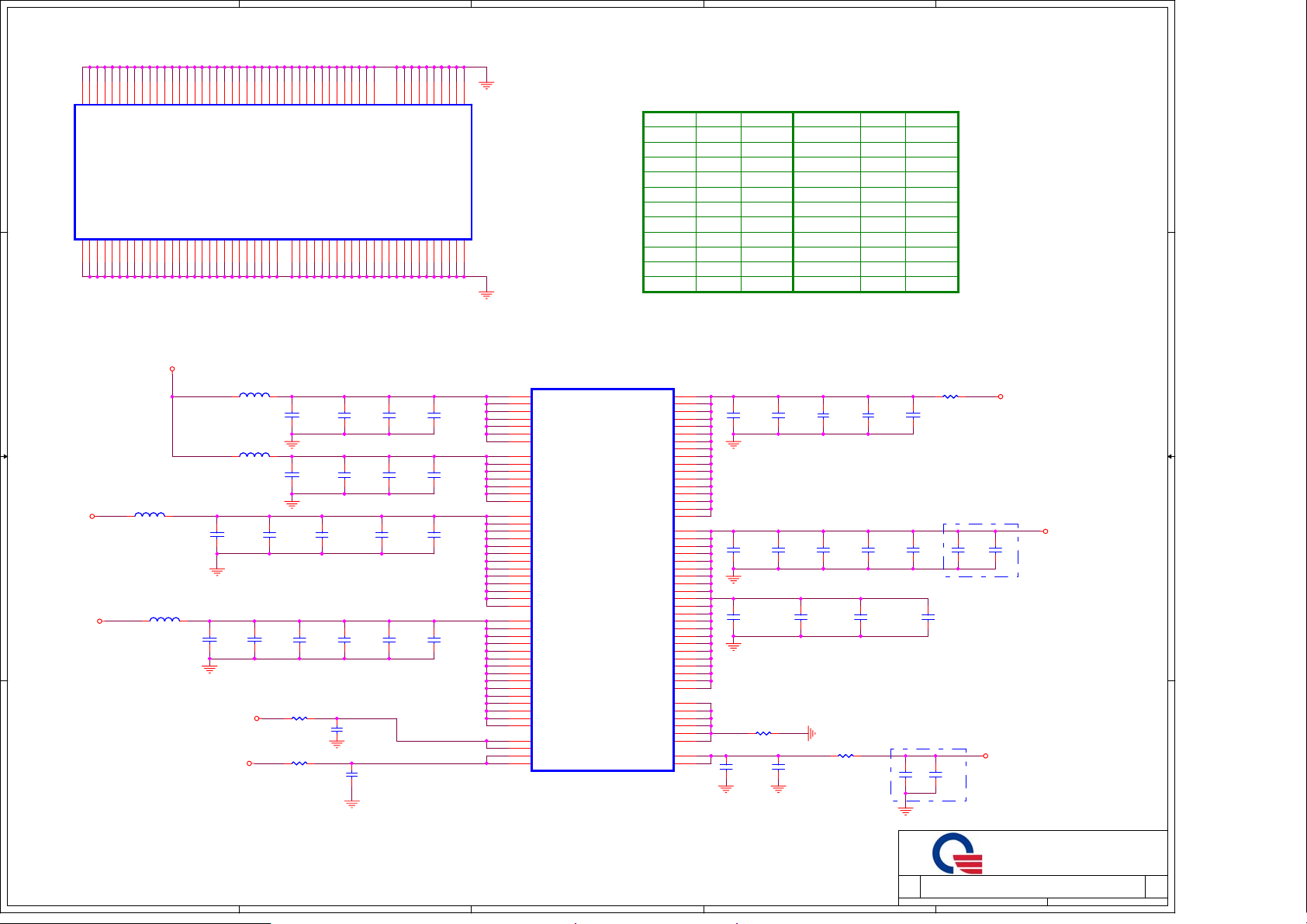

+1.8VSUS

103

111

104

112

117

M_A_A[0..15]4

4 4

M_A_BS#04

M_A_BS#14

M_A_BS#24

M_A_DM[0..7]4

M_A_DQS[0..7]4

3 3

M_A_DQS#[0..7]4

M_A_CLKOUT14

M_A_CLKOUT1#4

M_A_CLKOUT74

M_A_CLKOUT7#4

M_A_CKE04

M_A_CKE14

M_A_RAS#4

M_A_CAS#4

M_A_WE#4

M_A_CS#04

M_A_CS#14

M_A_ODT04

M_A_ODT14

+3V

MVREF_DIM

C273

C273

C271

C271

2.2U/6.3V_6

2.2U/6.3V_6

.1U/10V_4

.1U/10V_4

2 2

1 1

1 2

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

MEM_SMBDAT

MEM_SMBCLK

C86 .1U/10V_4C86 .1U/10V_4

C269

C269

1000P_4

1000P_4

A

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

A0

A1

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

(H=5.2)

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

59

J2

J2

REVERSE

118

5

DQ0

7

DQ1

VDD8

VDD7

VDD9

17

DQ2

VDD10

VDD11

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

NC/TEST

SO-DIMM

SO-DIMM

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

122

121

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

132

128

127

DDRII_SODIMM_R H5.2

DDRII_SODIMM_R H5.2

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

M_A_DQ1

M_A_DQ5

M_A_DQ2

M_A_DQ3

M_A_DQ0

M_A_DQ4

M_A_DQ7

M_A_DQ6

M_A_DQ12

M_A_DQ8

M_A_DQ10

M_A_DQ14

M_A_DQ13

M_A_DQ9

M_A_DQ15

M_A_DQ11

M_A_DQ21

M_A_DQ17

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ19

M_A_DQ22

M_A_DQ16

M_A_DQ29

M_A_DQ28

M_A_DQ31

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ27

M_A_DQ30

M_A_DQ38

M_A_DQ36

M_A_DQ35

M_A_DQ37

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ39

M_A_DQ45

M_A_DQ44

M_A_DQ42

M_A_DQ46

M_A_DQ41

M_A_DQ40

M_A_DQ43

M_A_DQ47

M_A_DQ55

M_A_DQ54

M_A_DQ50

M_A_DQ51

M_A_DQ53

M_A_DQ48

M_A_DQ49

M_A_DQ52

M_A_DQ56

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ61

M_A_DQ63

M_A_DQ62

M_A_DQ[0..63] 4

T37T37

T100T100

T95T95

NEED CUT

MVREF_DIMMVREF_DIM

B

R191

R191

*0_4

*0_4

MVREF_DIM

C274

C274

1U/10V/04

1U/10V/04

M_B_DM[0..7]4

M_B_DQS[0..7]4

M_B_DQS#[0..7]4

C272

C272

2.2U/6.3V_6

2.2U/6.3V_6

1 2

+1.8VSUS+SMDDR_VREF

M_B_A[0..15]4

M_B_BS#04

M_B_BS#14

M_B_BS#24

+3V

+3V

R193

R193

1K/F_4

1K/F_4

R192

R192

1K/F_4

1K/F_4

M_B_CLKOUT14

M_B_CLKOUT1#4

M_B_CLKOUT74

M_B_CLKOUT7#4

M_B_CKE04

M_B_CKE14

M_B_RAS#4

M_B_CAS#4

M_B_WE#4

M_B_CS#04

M_B_CS#14

M_B_ODT04

M_B_ODT14

MVREF_DIM

R360 10K_4R360 10K_4

R357 0_4R357 0_4

MEM_SMBDAT

MEM_SMBCLK

C87 .1U/10V_4C87 .1U/10V_4

C270

C270

C268

C268

.1U/10V_4

.1U/10V_4

1000P_4

1000P_4

MVREF_DIM

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

MEM_SMBDAT

MEM_SMBCLK

A0

A1

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

A2

A3

A4

A5

A6

A7

A8

A9

REVERSE

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

(H=9.2)

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

59

*DA204U

*DA204U

*DA204U

*DA204U

C

+1.8VSUS

103

111

104

112

VDD8

VDD7

J1

J1

SO-DIMM

SO-DIMM

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

122

121

D26

D26

1

3

2

D25

D25

1

3

2

117

118

VDD9

VDD10

VDD11

NC/TEST

VSS32

VSS31

VSS30

128

127

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

196

VSS56

193

VSS55

190

VSS54

187

VSS53

184

VSS52

183

VSS51

178

VSS50

177

VSS49

172

VSS48

171

VSS47

168

VSS46

165

VSS45

162

VSS44

161

VSS43

156

VSS42

155

VSS41

150

VSS40

149

VSS39

145

VSS38

144

VSS37

139

VSS36

138

VSS35

133

VSS34

VSS33

132

DDRII_SODIMM_R H9.2

DDRII_SODIMM_R H9.2

+3V

+3V

M_B_DQ4

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ5

M_B_DQ0

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ15

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ11

M_B_DQ16

M_B_DQ21

M_B_DQ19

M_B_DQ23

M_B_DQ20

M_B_DQ17

M_B_DQ18

M_B_DQ22

M_B_DQ29

M_B_DQ28

M_B_DQ26

M_B_DQ27

M_B_DQ24

M_B_DQ25

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ36

M_B_DQ39

M_B_DQ35

M_B_DQ33

M_B_DQ37

M_B_DQ34

M_B_DQ38

M_B_DQ40

M_B_DQ41

M_B_DQ46

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ47

M_B_DQ42

M_B_DQ53

M_B_DQ49

M_B_DQ55

M_B_DQ54

M_B_DQ48

M_B_DQ52

M_B_DQ50

M_B_DQ51

M_B_DQ60

M_B_DQ57

M_B_DQ62

M_B_DQ59

M_B_DQ61

M_B_DQ56

M_B_DQ63

M_B_DQ58

T103T103

T30T30

T3T3

NEED CUT

M_B_DQ[0..63] 4

PDAT_SMB2,13,18,19

PCLK_SMB2,13,18,19

M_A_CKE0

M_B_CKE0

M_A_ODT0

M_A_A10

M_B_CS#0

M_B_ODT0

M_A_BS#1

M_A_A0

M_A_BS#2

M_A_CAS#

M_A_ODT1

M_A_RAS#

M_A_CS#0

M_A_CS#1

M_A_A13

M_B_A2

M_B_BS#1

M_B_BS#2

M_B_WE#

M_B_CAS#

M_B_RAS#

M_B_CS#1

M_B_ODT1

M_B_A13

M_A_BS#0

M_A_WE#

M_A_A2

M_A_A4

M_A_A6

M_A_A7

M_A_A11

M_A_A14

M_A_A12

M_A_A9

M_A_A3

M_A_A1

M_A_A8

M_A_A5

M_A_A15

M_A_CKE1

M_B_A0

M_B_A6

M_B_A4

M_B_A7

M_B_A11

M_B_A14

M_B_A3

M_B_A1

M_B_A8

M_B_A5

M_B_A12

M_B_A9

M_B_A10

M_B_BS#0

M_B_A15

M_B_CKE1

11/19

D

+SMDDR_VTERM

R139 47_4R139 47_4

R142 47_4R142 47_4

RP5 47X2_4RP5 47X2_4

1 2

3 4

RP4 47X2_4RP4 47X2_4

1 2

3 4

RP9 47X2_4RP9 47X2_4

1 2

3 4

R137 47_4R137 47_4

RP2 47X2_4RP2 47X2_4

1 2

3 4

R128 47_4R128 47_4

R125 47_4R125 47_4

R126 47_4R126 47_4

R124 47_4R124 47_4

RP8 47X2_4RP8 47X2_4

1 2

3 4

R138 47_4R138 47_4

RP3 47X2_4RP3 47X2_4

3 4

1 2

R127 47_4R127 47_4

RP1 47X2_4RP1 47X2_4

3 4

1 2

R123 47_4R123 47_4

RP6 47X2_4RP6 47X2_4

1 2

3 4

RP11 47X2_4RP11 47X2_4

1 2

3 4

RP17 47X2_4RP17 47X2_4

1 2

3 4

RP21 47X2_4RP21 47X2_4

3 4

1 2

RP18 47X2_4RP18 47X2_4

1 2

3 4

RP10 47X2_4RP10 47X2_4

1 2

3 4

RP14 47X2_4RP14 47X2_4

1 2

3 4

RP22 47X2_4RP22 47X2_4

3 4

1 2

47X2_4

47X2_4

1 2

RP13

RP13

3 4

47X2_4

47X2_4

1 2

RP16

RP16

3 4

47X2_4

47X2_4

1 2

RP20

RP20

3 4

47X2_4

47X2_4

1 2

RP12

RP12

3 4

47X2_4

47X2_4

1 2

RP15

RP15

3 4

47X2_4

47X2_4

1 2

RP19

RP19

3 4

47X2_4

47X2_4

1 2

RP7

RP7

3 4

47X2_4

47X2_4

3 4

RP23

RP23

1 2

+3V

2

3

R355 0_4R355 0_4

+3V

2

3

R354 0_4R354 0_4

Q34

Q34

*2N7002E

*2N7002E

Q35

Q35

*2N7002E

*2N7002E

+SMDDR_VTERM

AMD suggestion : 0603 X7R

for each R-pack

2

4

RP37

RP37

*4.7KX2_4

*4.7KX2_4

1

3

MEM_SMBDAT

1

MEM_SMBCLK

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Change Vakue from 10u to 22u.-1001

*10U/6.3V_8C113 *10U/6.3V_8C113

*10U/6.3V_8C125 *10U/6.3V_8C125

.1U/10V_4C154 .1U/10V_4C154

.1U/10V_4C122 .1U/10V_4C122

.1U/10V_4C245 .1U/10V_4C245

.1U/10V_4C247 .1U/10V_4C247

.1U/10V_4C151 .1U/10V_4C151

.1U/10V_4C187 .1U/10V_4C187

.1U/10V_4C242 .1U/10V_4C242

.1U/10V_4C135 .1U/10V_4C135

.1U/10V_4C223 .1U/10V_4C223

.1U/10V_4C190 .1U/10V_4C190

.1U/10V_4C119 .1U/10V_4C119

.1U/10V_4C124 .1U/10V_4C124

.1U/10V_4C226 .1U/10V_4C226

.1U/10V_4C213 .1U/10V_4C213

.1U/10V_4C233 .1U/10V_4C233

.1U/10V_4C216 .1U/10V_4C216

.1U/10V_4C243 .1U/10V_4C243

.1U/10V_4C138 .1U/10V_4C138

.1U/10V_4C132 .1U/10V_4C132

.1U/10V_4C182 .1U/10V_4C182

.1U/10V_4C200 .1U/10V_4C200

*.1U/10V_4C240 *.1U/10V_4C240

*.1U/10V_4C224 *.1U/10V_4C224

*.1U/10V_4C139 *.1U/10V_4C139

*.1U/10V_4C170 *.1U/10V_4C170

*.1U/10V_4C164 *.1U/10V_4C164

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

DDR-II SODIMM*2

DDR-II SODIMM*2

DDR-II SODIMM*2

+1.8VSUS

AMD suggestion : 0603 X7R 0.1U each

R-Pack between +1.8VSUS and

+SMDDR_VTERM

+1.8VSUS

E

*10U/6.3V_8C165 *10U/6.3V_8C165

*10U/6.3V_8C110 *10U/6.3V_8C110

C228 22U-10V_8C228 22U-10V_8

C152 22U-10V_8C152 22U-10V_8

.1U/10V_4C149 .1U/10V_4C149

.1U/10V_4C144 .1U/10V_4C144

.1U/10V_4C211 .1U/10V_4C211

.1U/10V_4C196 .1U/10V_4C196

.1U/10V_4C123 .1U/10V_4C123

.1U/10V_4C210 .1U/10V_4C210

.1U/10V_4C191 .1U/10V_4C191

.1U/10V_4C137 .1U/10V_4C137

.1U/10V_4C220 .1U/10V_4C220

.1U/10V_4C192 .1U/10V_4C192

.1U/10V_4C183 .1U/10V_4C183

.1U/10V_4C194 .1U/10V_4C194

.1U/10V_4C225 .1U/10V_4C225

.1U/10V_4C208 .1U/10V_4C208

.1U/10V_4C231 .1U/10V_4C231

.1U/10V_4C171 .1U/10V_4C171

.1U/10V_4C153 .1U/10V_4C153

.1U/10V_4C219 .1U/10V_4C219

.1U/10V_4C198 .1U/10V_4C198

.1U/10V_4C176 .1U/10V_4C176

+SMDDR_VTERM

.1U/10V_4C195 .1U/10V_4C195

.1U/10V_4C177 .1U/10V_4C177

.1U/10V_4C121 .1U/10V_4C121

.1U/10V_4C148 .1U/10V_4C148

.1U/10V_4C244 .1U/10V_4C244

.1U/10V_4C142 .1U/10V_4C142

.1U/10V_4C227 .1U/10V_4C227

.1U/10V_4C229 .1U/10V_4C229

.1U/10V_4C180 .1U/10V_4C180

.1U/10V_4C204 .1U/10V_4C204

.1U/10V_4C172 .1U/10V_4C172

.1U/10V_4C206 .1U/10V_4C206

.1U/10V_4C136 .1U/10V_4C136

.1U/10V_4C166 .1U/10V_4C166

Add 2 Cap.-1001

ZY7

ZY7

ZY7

735Thursday, June 26, 2008

735Thursday, June 26, 2008

735Thursday, June 26, 2008

1A

1A

1A

of

of

of

5

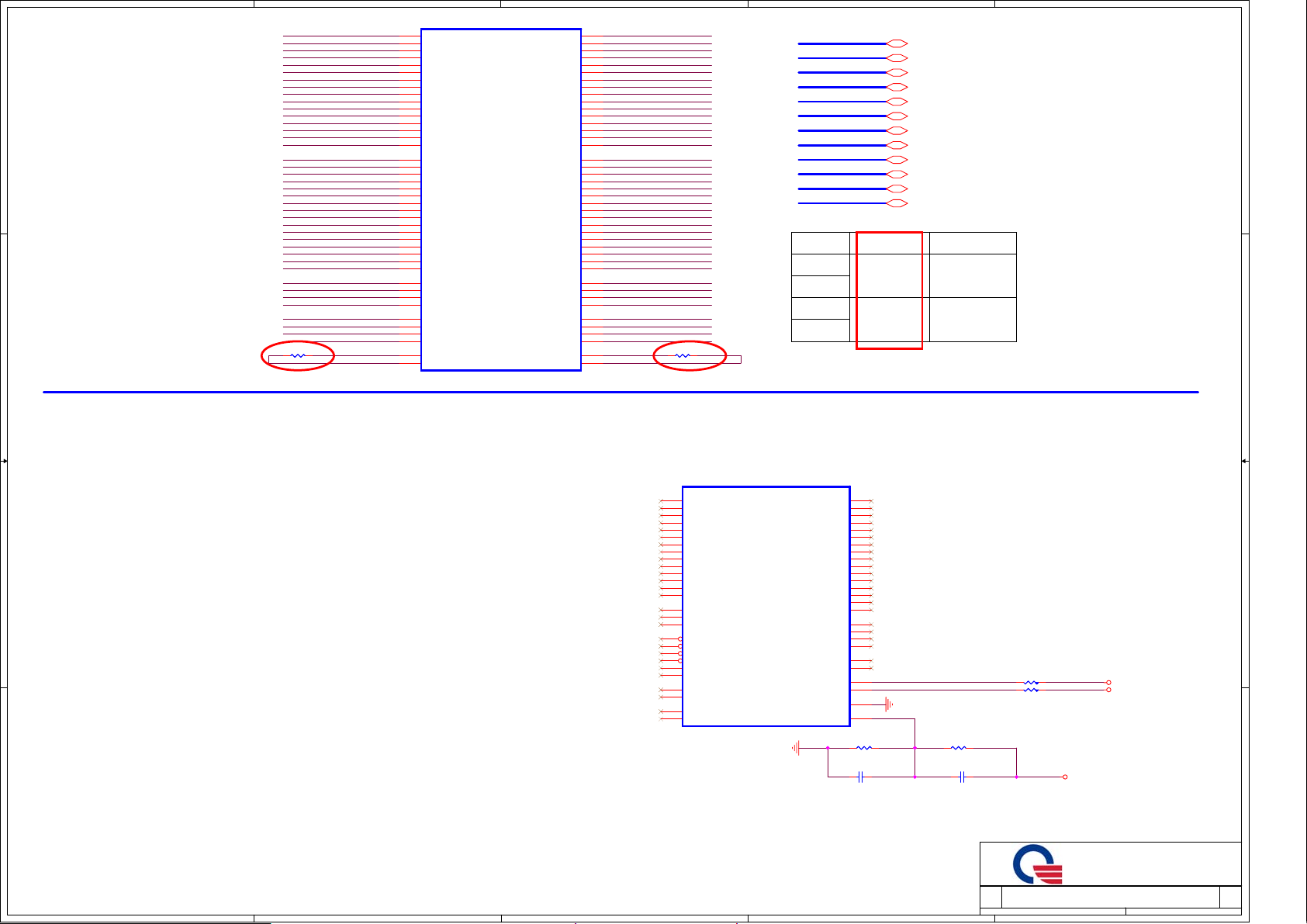

HT_TXD0

HT_TXD#0

HT_TXD1

HT_TXD#1

HT_TXD2

HT_TXD#2

HT_TXD3

HT_TXD#3

HT_TXD4

HT_TXD#4

HT_TXD5

HT_TXD#5

D D

C C

HT_TXD6

HT_TXD#6

HT_TXD7

HT_TXD#7

HT_TXD8

HT_TXD#8

HT_TXD9

HT_TXD#9

HT_TXD10

HT_TXD#10

HT_TXD11

HT_TXD#11

HT_TXD12

HT_TXD#12

HT_TXD13

HT_TXD#13

HT_TXD14

HT_TXD#14

HT_TXD15

HT_TXD#15

HT_CPU_DWNCLK0

HT_CPU_DWNCLK#0

HT_CPU_DWNCLK1

HT_CPU_DWNCLK#1

HT_CPU_DWNCTL0

HT_CPU_DWNCTL#0

HT_CPU_DWNCTL1

HT_CPU_DWNCTL#1

R406 301/04/FR406 301/04/F

HT_RXCALP

HT_RXCALN

4

U24A

U24A

Y25

AC24

AC25

AB25

AB24

AA24

AA25

W21

W20

AB23

AA22

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

Y22

Y23

V21

V20

U20

U21

U19

U18

T22

T23

M22

M23

R21

R20

C23

A24

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS780(RX780)

RS780(RX780)

PART 1 OF 6

PART 1 OF 6

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N