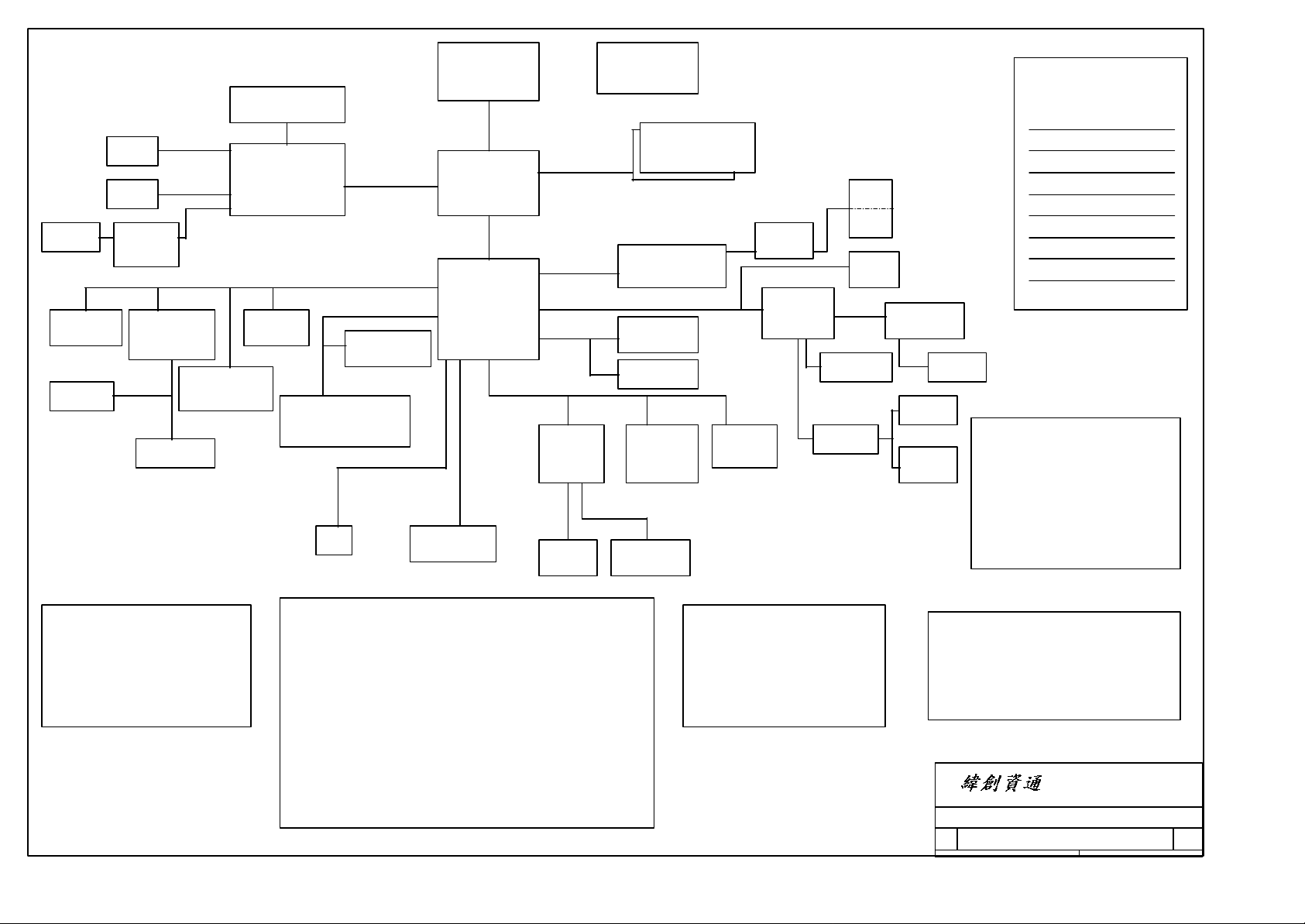

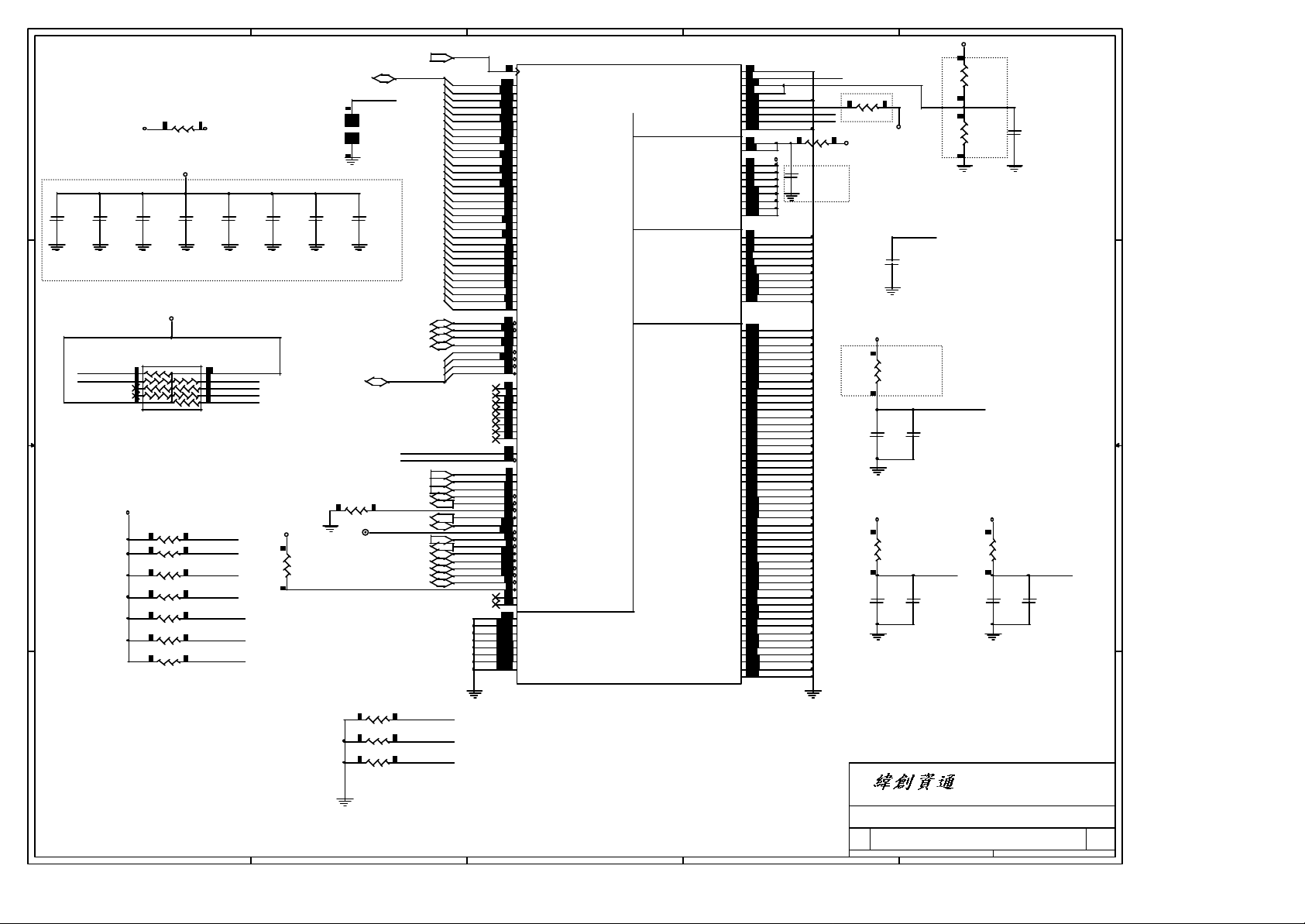

Acer TravelMate 630 Schematics

TV OUT

PG.17

1394

VT6306L

PG.28

SMART

CARD

CRT

PG.18

LCD

PG.18

TV ENCODER

CH7007

PG.17

CARDBUS

OZ6912/711E3

PG.25,26

CARDBUS

ONE SLOT

PG.27

DDR BUFFER

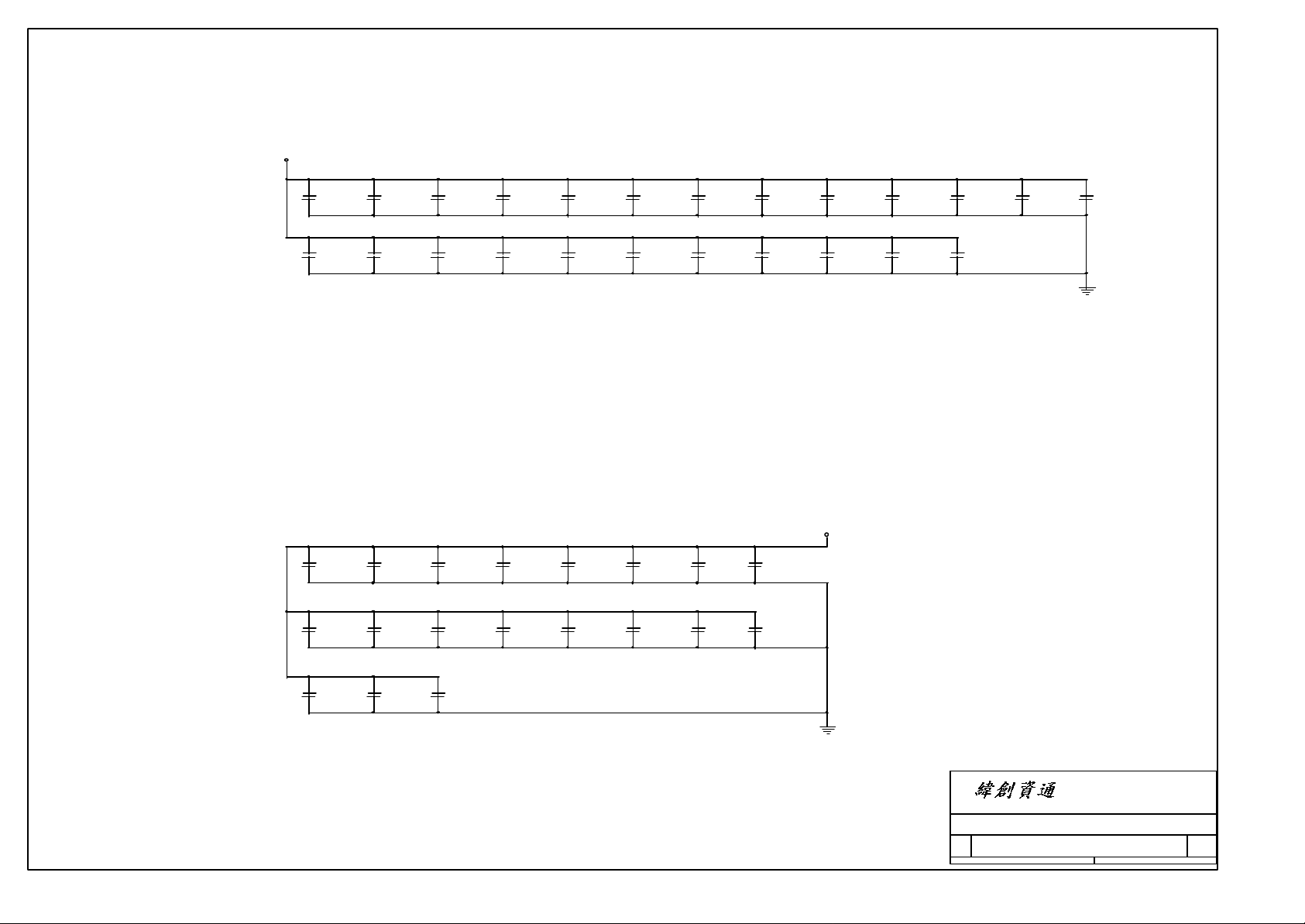

2M * 32bit*4Bank* 4

PG.15

LVDS

PG. 14,15,16

MiniPCI

PG.30

USB2.0

NEC uPD720100

PG.29

VGA

NVIDIA

GEFORCE2GO

100/200

802.11b

MODULAR BAY

CDROM (FDD)

PG.21

PG.23

PIDE HDD

PG.21

FIR

AGP 4x

1.5v

66MHz

PCI BUS

33MHz

ATA 66/100

PG.4,5

PG.6,7,8,9

PG.19,20,21

PRINTER

PG.35

CPU

Northwood-m

uFCPGA

AGTL+

100MHz

ALi

1671

PCI

Ali

1535+

DDR SDRAM

2.5v 266MHz

PCI BUS

33MHz

AC LINK

USB

ISA BUS

KBC

Mitsubishi

M38867

PG.33

KEY BD

CONN

CLK GEN

ICS 951104

PG.3

DDR*2

PG.11,12,13

LAN

RTL 8100BL

PG.24

Bluetooth

conn.

RF CONN

BIOS

MAX29F004TC

PG.34

TouchPad

CONN

PG.33PG.33

1GB MAX

PG.30

DEBUG

CONN

PG.34

Project code:

PCB P/N:01219

REVISION: -3

TXFM

PG.24

AC97

CODEC

CS4299

PG.31

PREAMP

PG.32

PG.32

RJ45

RJ11

PG.24

MDC

PG.27

A7

OP AMP

APA2020

PG.32

SPKR*2LINE-OUT

PG.32

INT MIC

PG.32

LINE-IN

/MIC

PG.32

BATTERY

CONN

PG.38,39

PCB STACKUP

LAYER 1 COMPONENT

LAYER 2 GND

LAYER 3 SIGNAL

LAYER 4 VCC

LAYER 5 SIGNAL

LAYER 6 GND

LAYER 7 SIGNAL

LAYER 8 COMPONENT

CHARGER

MAX1645

GND

BAT_IN#

SMBC_BT

SMBD_BT

BAT_TH

BAT+SENSE

BAT+

CPU DC/DC IMVP3

SEMTECH SC1474

INPUT

DCBATOUT

PG.33

OUTPUT

VCC_CORE

PM=1.3v, BM=1.3v

VCC_VID

1.2v, 300mA

SYSTEM DC/DC

MAX1632 / MAX1715 / G913C / MAX8863 / MAX1792 / SI3025

INPUT

DCBATOUT

5V_S5

DCBATOUT

3D3V_LAN_S5AC

3D3V_S0

3D3V_S0

DCBATOUT

PG.34,35,36

OUTPUT

3D3V_LAN_S5AC / 3D3V_S3 / 3D3V_S0

5V_S5 / 5V_S3 / 5V_S0

12V_S3

3D3V_S5

2D5V_S3

1D575V_S0

2D5V_LAN_S5AC

2D5V_S0

1D5V_S0

UP+5V

DDR DC/DC

MAX1715 / MAX4490

INPUT

DCBATOUT

2D5V_S3

PG.36

OUTPUT

DDR_VDD

= 2D5V_S3

DDR_VTT

= 1D25V_S3

PORT REPLICATOR

CRT PRINT PORT

TV SERIAL PORT

PS2 AUDIO JACK

PG.40

Title

Size Document Number Rev

A3

Date: Sheet of

A7

DC IN

LAN

MODEM

USB

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

BLOCK DIAGRAM

1 43Monday, June 03, 2002

-3

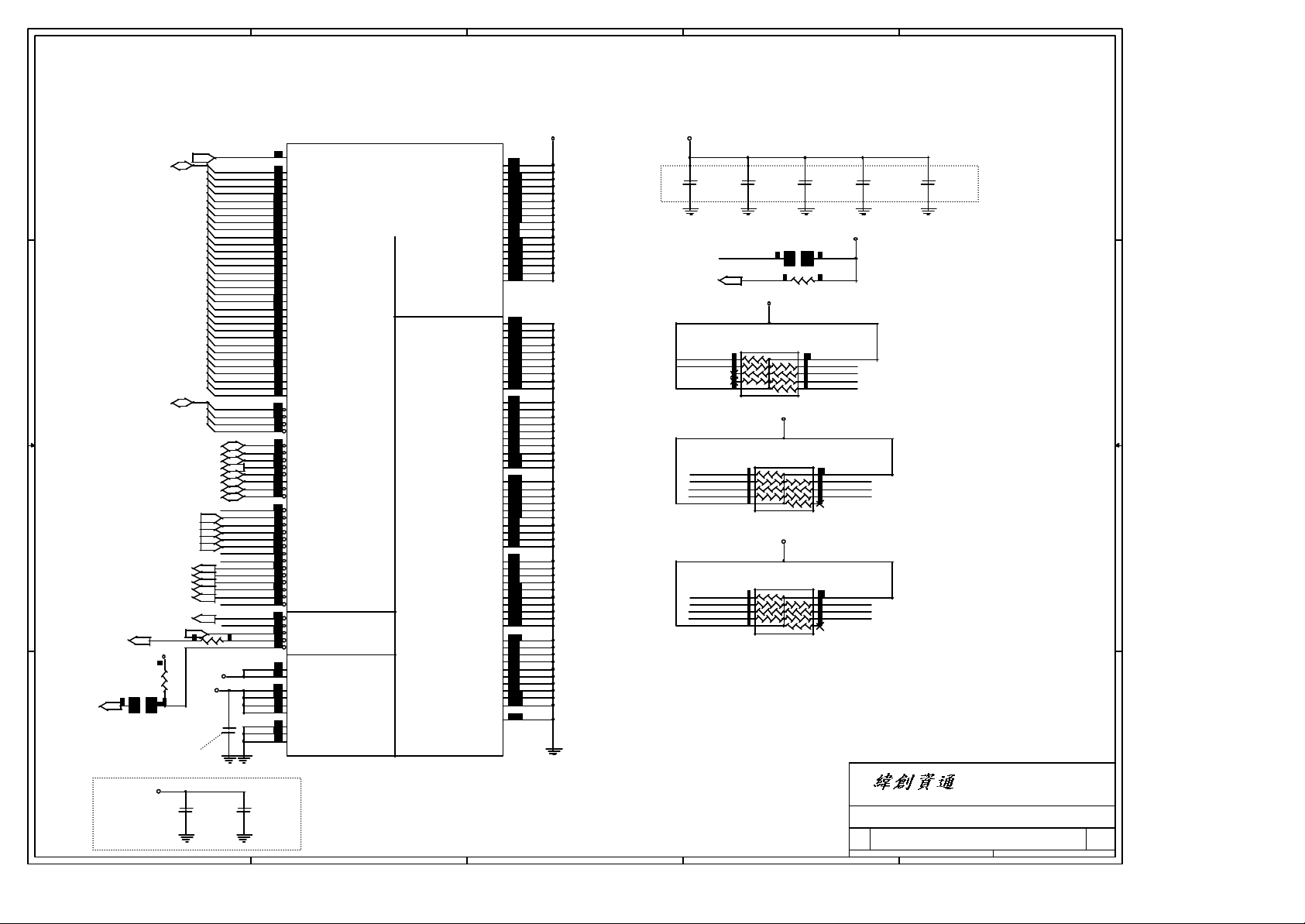

CONTENTS

01. BLOCK DIAGRAM

02. REVISION HISTORY

03. CLOCK GENERATOR -- ICS951104

04. CPU (1/2) --NORTHWOOD(1/2)

05. CPU (2/2) --NORTHWOOD(2/2)

06. N/B ALI 1671 (1/4)

07. N/B ALI 1671 (2/4)

08. N/B ALI 1671 (3/4))

09. N/B ALI 1671 (4/4)

10. N/B 1671 HARDWARE SETTING

11. DDR DAMPING & TERMINATION

12. DDR SO-DIMM SKT

13. DDR DECOUPLING

14. VGA_AGP/LVDS (1/4)

15. VGA_MEM/CRT/TV (2/4)

16. VGA_DDR (3/4)

17. TV_ENCODER (4/4)

18. LCD/CRT

19. M1535+ (1/2)

20. M1535+ (2/2)

21. HDD/SED. BAY CONN.

22. G768C

23. USB/DAUGHTER BD

24. LAN REALTEK 8100

25 .CARDBUS OZ711

26. CARDBUS OZ6912

27. CARDBUS CONN/POWER S/W

28. 1394_VT6306L_J

29. USB2.0

30.MINI PCI SOCKET - 802.11b/MDC

31. AUDIO(1/2)

32. AUDIO(2/2)

33. KBC_TOUCHPAD

34. RTC_FLASH

35. PRINTER PORT

36. PORT REPLICATOR

37. CPU_CORE -- IMVP3

38. DC/DC (1/3) 3/5V

39. DC/DC (2/3) 1.25/1.5/2.5V)

40. PWRCTL LOGIC

41. CHARGER (1/2

42. CHARGER (2/2)

43. JUMP SETTING & NO USE GATE

A7 REVISION HISTORY

Northwood SPEC summary Aug. 20

VERSION(SA)

Vcc=1.3V (Performace)

Northwood-m

478 pin

Northwood

(Desktop)

478 pin

Semtech SC1474 voltage setting

D4 D3 D2 D1 D0 Voltage(V)

0 0 0

0 0

0 0 0 0

0 0 0

0 0 0

0 0

0 0

=1.3V (Batt)

(40A)

VID=1.2V

(300mA)

1 1

1 1 1

1

1 1

1 1

1 1 1

1 1

0

1.45

1.40

1.35

1.30

1.25

1.20

1.15

CARDBUS

1394

LAN

USB2.0

MINIPCI

AGP

PCI RESOURCE TABLE

IDSEL

AD30

AD22

AD21

AD24

AD23

PCI IRQDEVICE REQ# / GNT#

P_IRQ2#/P_IRQ4#

P_IRQ3#

P_IRQ1#

P_IRQ5#

P_IRQ4#/P_IRQ6#

P_IRQ1#/

P_REQ2#/P_GNT2#

P_REQ3#/P_GNT3#

P_REQ1#/P_GNT1#

P_REQ5#/P_GNT5#

P_REQ4#/P_GNT4#

0

0 0

0

1 1 1

1 1 1

1 1 1 1

0

1.10

1.05

1.00

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Ta iwan, R.O.C.

REVISION HISTORY

A7

2 43Wednesday, May 2 9, 2002

-3

A

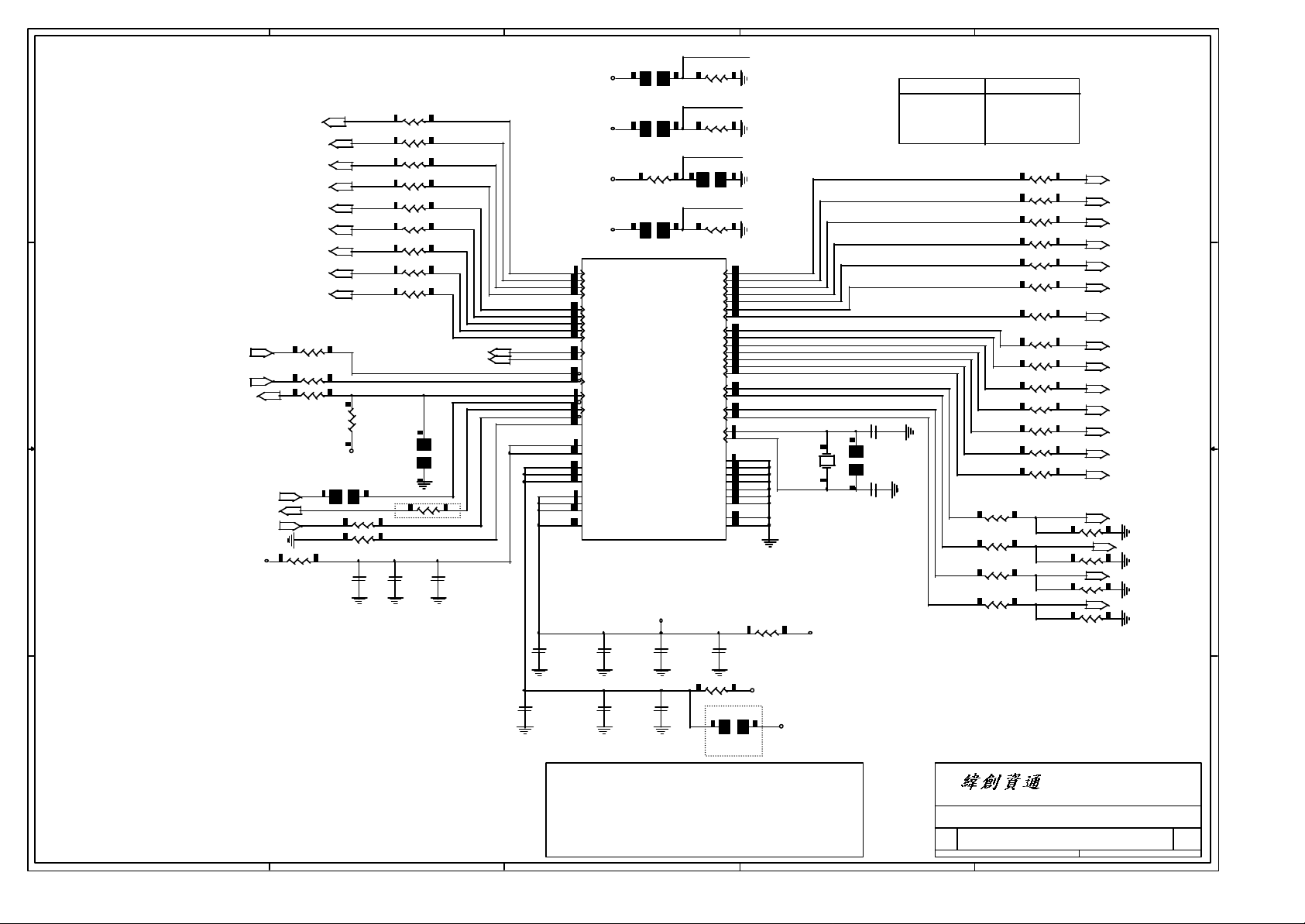

CLK66_16717

4 4

3 3

2 2

1 1

PM_PCI_STP#_319,20

PM_CPUSTP#4,19,37

CLK14_1535+17,19

RUNPWROK4,19,34,40,41

1474_PWROK37,40

3D3V_S0

A

CLK33_1535+19,26

CLK33_16718

CLK48_USB19,29,43

CLK33_USB29

CLK33_LAN24

CLK33_PCM25

CLK33_139428

CLK33_MINI30

R128 0R2-0

R163 0R2-0

R96 22R2

3D3V_CKG_S0

R97

CLK66_AGP14

R661 0R5

DUMMY-R2 R803 22R2

R617

10KR2

R161 0R2-0

R106 475R3F

3D3VA_CKG_SS

BC62

SCD1U16V

B

R98 22R2

R125 22R2

R126 22R2

R160 22R2

R124 22R2

R131 22R2

R130 22R2

R127 22R2

R129 22R2

ICS_PCISTP#

ICS_CLKSTP#

R616

DUMMY-R2

ICS_RESET#

VTTPWRGD

ICS_IREF

BC584

SCD1U16V

B

SMBC_1535+12,18,19,20,22

SMBD_1535+12,18,19,20,22

CKG_MULTSEL

SB

BC585

SC4D7U10V5ZY

C

CLK66_M_1671

3D3V_CKG_S0

3D3V_CKG_S0

3D3V_CKG_S0

3D3V_CKG_S0

CLK66_M_1671

CLK33_M_1535+

CLK33_M_1671

CLK48_M_USB

CLK33_M_USB

CLK33_M_LAN

CLK33_M_PCM

CLK33_M_1394

CLK33_M_MINI

BC95

SC4D7U10V5ZY

U7

FS0/AGP0

FS1/PCICLK_E

FS2/PCICLK0

FS3/48MHZ

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

SCLK

SDATA

PCI_STOP#

CLK_STOP#

MULTSEL/REF0

RESET#

AGP1

VTT_PWRGD/PD#

IREF

AVDD_CORE

AVDD48

VDDL

VDDL

VDDL

VDD

VDD

VDD

VDDCPU

ICS951104-1

BC70

SCD1U16V

FS3 FS2 FS1 FS0 CPU AGP DDR

0 0 0 0 66 66 66

0 0 0 1 66 66 100

0 0 1 0 100 66 66

0 0 1 1 100 66 100

0 1 0 0 100 66 133

0 1 0 1 133 66 66

R613

DUMMY-R2

R641

DUMMY-R2

R640

10KR2

R660

DUMMY-R2

3D3V_CKG_S0

BC65

SCD1U16V

VDDL

BC94

SC1000P50V3KX

C

R614

10KR2

CLK33_M_1535+

R615

10KR2

CLK33_M_1671

R639

DUMMY-R2

CLK48_M_USB

R659

10KR2

DDRC0

DDRC1

DDRC2

DDRC3

DDRC4

DDRC5

DDRC6

DDRT0

DDRT1

DDRT2

DDRT3

DDRT4

DDRT5

DDRT6

CPUCLKT0

CPUCLKT1

CPUCLKC0

CPUCLKC1

GNDCPU

GNDIREF

BC506

SCD1U16V

R172

0R2-0

BC71

SC1000P50V3KX

X1

X2

GND

GND

GND

GND

GND

GND

GND

DUMMY-R2

CLK_M_D1671#

CLK_M_DDR0#

CLK_M_DDR1#

CLK_M_DDR2#

CLK_M_DDR3#

CLK_M_DDR4#

CLK_M_DDR5#

CLK_M_D1671

CLK_M_DDR0

CLK_M_DDR1

CLK_M_DDR2

CLK_M_DDR3

CLK_M_DDR4

CLK_M_DDR5

CLK_M_CPU

CLKH_M_H1671

CLK_M_CPU#

CLKH_M_H1671#

R168 0R5

BC93

SC4D7U10V5ZY

2D5V_S0

R816

CLKGEN_X1

X-14.318MHZ-1

82.30005.031

CLKGEN_X2

2D5V_CKG_S0

SB

X1

3D3V_S0

D

BC63

SC33P

R80

DUMMY-R2

BC64

SC33P

D

E

INTERNAL PULL-UP 120K

MULT_SEL

FS1

FS2

PCI_STOP#

Vtt_PG

Title

Size Document Number Rev

A3

Date: Sheet of

INTERNAL PULL-DOWN 120K

FS0

FS3

R100

49D9R3F

R107

49D9R3F

R102

49D9R3F

R108

49D9R3F

CLKD_1671# 9

CLK_DDR0# 12

CLK_DDR1# 12

CLK_DDR2# 12

CLK_DDR3# 12

CLK_DDR4# 12

CLK_DDR5# 12

CLKD_1671 9

CLK_DDR0 12

CLK_DDR1 12

CLK_DDR2 12

CLK_DDR3 12

CLK_DDR4 12

CLK_DDR5 12

CLKH_CPU 4

CLKH_CPU# 4

CLKH_1671# 6

64.33R05.651

R99 33R3F

64.33R05.651

R104 33R3F

64.33R05.651

R101 33R3F

64.33R05.651

R105 33R3F

R139 22R2

R133 22R2

R136 22R2

R137 22R2

R171 22R2

R167 22R2

R170 22R2

R103 22R2

R138 22R2

R132 22R2

R135 22R2

R134 22R2

R166 22R2

R169 22R2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

CLOCK GENERATOR -- ICS951104

A7

3 43Monday, June 10, 2002

E

CLKH_1671 6

-3

3D3V_S0

R191

470R3

63.47134.151

CC_FERR#

CC_ FERR#_2

1D2V_VID_S0

R570

0R3-0-U

R571

0R3-0-U

L:RATED I = 60mA

C:ESR < 0.3 OHM, ESL < 5nH, +/- 20% TOLERANT

H_VID437

H_VID037

H_VID137

H_VID237

H_VID337

63.30134.151

Q16

UMX1N

84.UMX1N.01F

1D2V_HCA1_S0

1D2V_HCA2_S0

R143

10KR2

RN3

SRN10K

66.10336.080

R189

300R3

CC_FERR#_1

L26

IND-4D7UH

68.4R72B.1F1

L27

IND-4D7UH

68.4R72B.1F1

3D3V_S0

GTL_A#[16..3]6

GTL_ADSTB#06

GTL_REQ#[4..0]6

GTL_A#[31..17]6

GTL_ADSTB#16

VCC_CORE_S0

R190

56R3

63.56034.151

R192

470R3

63.47134.151

TC20

ST33U10VCM-U

77.23361.001

TC19

ST33U10VCM-U

77.23361.001

CC_STPCLK#19,43

CC_THRMTRIP_S#22

CLKH_CPU3

CLKH_CPU#3

CLKH_ITP5

CLKH_ITP#5

CC_A20M#19

CC_IGNNE#19

CC_INTR19

CC_NMI19

CC_SMI#19,43

TP48

TPAD30

TP45

TPAD30

1D2V_HCA3_S0

1D2V_HCA4_S0

H_VSSA

TP46

TPAD30

1D2V_VID_S0

THERMDP122

THERMDN22

GTL_A#16

GTL_A#15

GTL_A#14

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

GTL_REQ#4

GTL_REQ#3

GTL_REQ#2

GTL_REQ#1

GTL_REQ#0

GTL_A#31

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

U8C

CC_FERR_S#

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

H_VCCS

H_VSSS

U8D

A#16

A#15

A#14

A#13

A#12

A#11

A#10

A#9

A#8

A#7

A#6

A#5

A#4

A#3

ADSTB#0

REQ#4

REQ#3

REQ#2

REQ#1

REQ#0

A#35

A#34

A#33

A#32

A#31

A#30

A#29

A#28

A#27

A#26

A#25

A#24

A#23

A#22

A#21

A#20

A#19

A#18

A#17

ADSTB#1

RSVD3

NORTHWOOD-1D5-U1

BCLK0

BCLK1

ITP_CLK0

ITP_CLK1

A20M#

FERR#

IGNNE#

LINT0

LINT1

SMI#

STPCLK#

VID4

VID3

VID2

VID1

VID0

RSVD3

VCCVID

VCCA

VCCSENSE

VCCIOFLL

VSSA

VSSSENSE

VCCVID

NC

NC

THERMDA

THERMDC

THERMTRIP#

NC

NC

NC

NC

NC

NORTHWOOD-1D5-U1

ADS#

AP#0

AP#1

BINIT#

BNR#

BPRI#

DP#3

DP#2

DP#1

DP#0

DEFER#

DRDY#

DBSY#

TESTHI10

TESTHI9

TESTHI8

BR#0

IERR#

INIT#

LOCK#

MCERR#

RESET#

RS#2

RS#1

RS#0

RSP#

TRDY#

HIT#

HITM#

R142

DUMMY-R3

H_BSEL0

BSEL0

H_BSEL1

BSEL1

TESTHI11

PROCHOT#

PWRGOOD

H_TESTHI11

H_COMP0

COMP1

H_COMP1

COMP0

CC_DPSLP#

CC_PROCHOT_S# 22

CC_CPUSLP# 19

H_TCK 5

H_TDI 5

H_TDO 5

H_TMS 5

H_TRST# 5

GTL_ADS# 6,43

GTL_BNR# 6

GTL_BPRI# 6

GTL_DEFER# 6

GTL_DRDY# 6

GTL_DBSY# 6

RN76

SRN10K

66.10336.080

TP67

TPAD30

TP43

TPAD30

TP53

TPAD30

H_BPM5_PREQ# 5

H_BPM4_PRDY# 5

H_BPM1_ITP# 5

H_BPM0_ITP# 5

R82

0R3-0-U

RN1 SRN10K

RN2 SRN10K

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

H_BYPASSEN#

TESTHI0

DPSLP#

GTLREF

GTLREF

GTLREF

GTLREF

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

DBRST#

DBR#

H_ODT

H_MCLK0

H_MCLK1

H_MCLK2

H_MCLK3

H_MCLKIO0

H_MCLKIO1

H_BYPASSEN#

SLP#

TCK

TDI

TDO

TMS

TRST#

CPU MUST BE CHANGED TO CPU SOCKET

62.10053.061(AMP), OR 62.10055.011(FOXCONN)

FOR BOM

H_AP#0

H_AP#1

H_BINIT#

H_DP#3

H_DP#2

H_DP#1

H_DP#0

H_BR3#

H_BR2#

H_BR1#

H_IERR_PU#

CC_INIT# 19

GTL_LOCK# 6

H_MCERR#

H_RSP#

R663 51D1R3F

R567 51D1R3F

64.51R15.651

H_GTLREF_3

H_GTLREF_1

VCC_CORE_S0

TP54 TPAD30

TP42 TPAD30

TP47 TPAD30

TP41 TPAD30

TP40 TPAD30

TP39 TPAD30

TP38 TPAD30

R643

51R3

63.51034.151

R569

DUMMY-R3

VCC_CORE_S0

R141

0R3-0-U

ITP_RST# 5

R622

300R3

63.30134.151

VCC_CORE_S0

PM_CPUPERF#_1

GTL_BR0# 6

GTL_CPURST# 5,6

GTL_RS#2 6

GTL_RS#1 6

GTL_RS#0 6

GTL_TRDY# 6

GTL_HIT# 6

GTL_HITM# 6

RESET#(AB25) : change 51ohm to dummy (from EV BD)

PM_CPUPERF#_1

VCC_CORE_S0

R620

49D9R3F

64.49R95.651

R618

100R2

R621

100R2

R683

DUMMY-R2

SB

CC_DPSLP#

CC_PWG

VCC_CORE_S0

VCC_CORE_S0

SB

R619

49D9R3F

64.49R95.651

BC512

SC220P25V3JN

BC516

SC220P25V3JN

D25

RB731U

BC510

SC220P25V3JN

BC514

SC220P25V3JN

R817

0R3-0-U

PM_CPUPERF#

CC_A20M#

CC_IGNNE#

CC_INTR

CC_NMI

CC_SMI#

CC_STPCLK#

CC_DPSLP#

CC_CPUSLP#

CC_INIT#

CC_PROCHOT_S#

GTL_D#[15..0]6

GTL_DINV#06

GTL_DSTBN#06

GTL_DSTBP#06

BC549

SC1U10V3ZY

BC559

SC1U10V3ZY

GTL_D#[31..16]6

GTL_DSTBN#16

GTL_DSTBP#16

PM_CPUSTP# 3,19,37

RUNPWROK 3,19,34,40,41

PM_CPUPERF# 19,20

PM_GMUXSEL 37

SB

VCC_CORE_S0

R679

R684

56R3

200R3

63.56034.151

63.20134.151

GTL_D#15

GTL_D#14

GTL_D#13

GTL_D#12

GTL_D#11

GTL_D#10

GTL_D#9

GTL_D#8

GTL_D#7

GTL_D#6

GTL_D#5

GTL_D#4

GTL_D#3

GTL_D#2

GTL_D#1

GTL_D#0

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#28

GTL_D#27

GTL_D#26

GTL_D#25

GTL_D#24

GTL_D#23

GTL_D#22

GTL_D#21

GTL_D#20

GTL_D#19

GTL_D#18

GTL_D#17

GTL_D#16

R81

200R3

63.20134.151

U8B

D#15

D#14

D#13

D#12

D#11

D#10

D#9

D#8

D#7

D#6

D#5

D#4

D#3

D#2

D#1

D#0

DINV#0

STBN#0

STBP#0

D#31

D#30

D#29

D#28

D#27

D#26

D#25

D#24

D#23

D#22

D#21

D#20

D#19

D#18

D#17

D#16

DINV#1

STBN#1

STBP#1

D#47

D#46

D#45

D#44

D#43

D#42

D#41

D#40

D#39

D#38

D#37

D#36

D#35

D#34

D#33

D#32

DINV#2

STBN#2

STBP#2

D#63

D#62

D#61

D#60

D#59

D#58

D#57

D#56

D#55

D#54

D#53

D#52

D#51

D#50

D#49

D#48

DINV#3

STBN#3

STBP#3

GTL_D#47

GTL_D#46

GTL_D#45

GTL_D#44

GTL_D#43

GTL_D#42

GTL_D#41

GTL_D#40

GTL_D#39

GTL_D#38

GTL_D#37

GTL_D#36

GTL_D#35

GTL_D#34

GTL_D#33

GTL_D#32

GTL_D#63

GTL_D#62

GTL_D#61

GTL_D#60

GTL_D#59

GTL_D#58

GTL_D#57

GTL_D#56

GTL_D#55

GTL_D#54

GTL_D#53

GTL_D#52

GTL_D#51

GTL_D#50

GTL_D#49

GTL_D#48

GTL_DINV#2 6

GTL_DSTBN#2 6

GTL_DSTBP#2 6

GTL_DINV#3 6GTL_DINV#16

GTL_DSTBN#3 6

GTL_DSTBP#3 6

w22,23 swap

NORTHWOOD-1D5-U1

R646

DUMMY-R3

H_BSEL1

H_BSEL0

R664

1KR3

63.10234.151

ZZ.DUMMY.XR3

R645

DUMMY-R3

R644

ZZ.DUMMY.XR3

1KR3

63.10234.151

PULL TO 3.3V OR VCC_CORE??

Northwood EMTS rev0.5 P52

3D3V_S0

< 3" from CPU

R83

R685

R662

R682

R681

R677

200R3

200R3

200R3

200R3

63.20134.151

63.20134.151

63.20134.151

Title

Size Document Number Rev

A3

Date: Sheet of

200R3

63.20134.151

63.20134.151

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

NORTHWOOD(1/2)

A7

200R3

63.20134.151

4 43Monday, June 10, 2002

R642

200R3

63.20134.151

GTL_D#[47..32] 6

GTL_D#[63..48] 6

R140

10KR3

63.10334.151

SB

-3

10U/X7R 1206 DECOUPLING CAPS

8X IN SOCKET CAVITY

10X IN CRB

*AF2 :

VCCFUSEPRG

10U/X7R 1206 DECOUPLING CAPS

10X AROUND SOCKET

28X IN CRB

CLOSE TO CPU CLOSE TO ITP

In-Target Probe

CLOSE TO ITP

0.1U/X5R 0603 DECOUPLING CAPS

20X AROUND SOCKET

0.47U/X5R 0603 10X IN CRB

ITP Connector Placement

Pin2

GND

ITP11 ITP8 ITP9 ITP12

GND GND

ITP4 ITP3

ITP2 ITP1 ITP10ITP7 ITP13

Pin1

GNDGND

Pin24

ITP6 ITP5

ITP14

Pin23

NORTHWOOD(2/2)

A7

Pin25

Wistron Corporation

-3

BC53

SCD33U16V

BC56

SCD33U16V

BC472

SCD33U16V

BC467

SCD33U16V

BC466

SCD1U16V

5

R42

DUMMY-R2

[1.25V]

R564

DUMMY-R2

BC501

SCD1U16V

5

[1V]

HSCRHDP

BC54

SCD047U25V3KX

HSCRHDPHSCRHDN

HSCRHDN

BC55

SCD047U25V3KX

[1V]

HSCRSBP

BC470

SCD047U25V3KX

HSCRSBPHSCRSBN

[1.25V]

HSCRSBN

BC469

SCD047U25V3KX

Placed as closee to

ADDR/M1671 package as

possible

BC426

SCD1U16V

VCC_CORE_S0

R519

4D7R3

VCC_HIPOW1_S0

BC428

SC1000P50V3KX

2D5V_S3

BC427

SC1000P50V3KX

BC473

SCD1U16V

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

R518

4D7R3

2D5V_HIPOW2_S3

BC471

SCD1U16V

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

2D5V_S3

-1

L43

4D7R5

63.4R733.161

BC90

SC1000P50V3KX

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

G23

GAP-CLOSE

ZZ.CON2C.XXX

VCC_CORE_S0

BC503

BC504

BC465

SCD1U16V

SCD1U16V

SCD1U16V

-1

2D5V_S0

R40

121R3F

D D

R41

80D6R3F

Use 10 mils trace, isolate with 7 mils

-1

space, place caps near to NB pins

2D5V_S0

R44

121R3F

R43

121R3F

C C

B B

A A

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

-1

2D5V_S0

R566

121R3F

R565

80D6R3F

Use 10 mils trace, isolate with 7 mils

-1

space, place caps near to NB pins

2D5V_S0

R562

121R3F

R563

121R3F

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

Placed as closee to DATA/M1671

package as possible

BC468

SCD1U16V

2D5V_S3

2D5V_HVDDA_S3

BC425

SC10U10V-U

4

R158

DUMMY-R2

BC91

SCD1U16V

4

GTL_A#[31:3]4

CLKH_1671

CLKH_1671#

Placed near to M1671

pin, for debugging

GTL_REQ#[4:0]4

M1671

0.1uF 0603

BC424

SC10U10V-U

3

U6B

CLKH_16713

CLKH_1671#3

C35

DUMMY-C3

C34

DUMMY-C3

GTL_ADSTB#04

GTL_ADSTB#14

GTL_RS#[2..0]4

GTL_HIT#4

GTL_HITM#4

GTL_BR0#4

GTL_BPRI#4

GTL_BNR#4

GTL_DEFER#4

GTL_DBSY#4

GTL_DRDY#4

GTL_ADS#4,43

GTL_LOCK#4

GTL_TRDY#4

GTL_CPURST#4,5

HDVREF

HACVREF

DATA

ADDR

VCC_CORE_S0

GTL_A#3

GTL_A#4

GTL_A#5

GTL_A#6

GTL_A#7

GTL_A#8

GTL_A#9

GTL_A#10

GTL_A#11

GTL_A#12

GTL_A#13

GTL_A#14

GTL_A#15

GTL_A#16

GTL_A#17

GTL_A#18

GTL_A#19

GTL_A#20

GTL_A#21

GTL_A#22

GTL_A#23

GTL_A#24

GTL_A#25

GTL_A#26

GTL_A#27

GTL_A#28

GTL_A#29

GTL_A#30

GTL_A#31

GTL_REQ#0

GTL_REQ#1

GTL_REQ#2

GTL_REQ#3

GTL_REQ#4

GTL_RS#0

GTL_RS#1

GTL_RS#2

2D5V_HVDDA_S3

HOSTSENSENP

HOSTSENSEN

VCC_HIPOW1_S0

2D5V_HIPOW2_S3

HSCRHDP

HSCRHDN

HSCRSBP

HSCRSBN

VCORE 1.1V~1.85V/60A

HCLK

HCLK#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADSTB0#

HADSTB1#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HIT#

HITM#

BREQ0#

BPRI#

BNR#

DEFER#

DBSY#

DRDY#

ADS#

LOCK#

CPUTRDY#

CPURST#

HAG

HVDDA

HOST_SENSE_P

HOST_SENSE_N

HI_POW1

HI_POW2

HI_GND

HOST_SCRHDP

HOST_SCRHDN

HOST_SCRSHIELD

HOST_SCRSBP

HOST_SCRSBN

HOST_DVREF

HOST_DVREF

HOST_VSHIELD

HOST_VSHIELD

HOST_CVREF

HOST_AVREF

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

VTT

VTT

VTT

VTT

VTT

M1671-U1

71.M1671.00U

3

ALi M1671

( 1 of 4 )

CPU P4

Address

Bus

PLL

CPU GND

(15Balls)

Data

Bus

CPU

POWER

(25Ball)

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

2

2

GTL_D#0

GTL_D#1

GTL_D#2

GTL_D#3

GTL_D#4

GTL_D#5

GTL_D#6

GTL_D#7

GTL_D#8

GTL_D#9

GTL_D#10

GTL_D#11

GTL_D#12

GTL_D#13

GTL_D#14

GTL_D#15

GTL_D#16

GTL_D#17

GTL_D#18

GTL_D#19

GTL_D#20

GTL_D#21

GTL_D#22

GTL_D#23

GTL_D#24

GTL_D#25

GTL_D#26

GTL_D#27

GTL_D#28

GTL_D#29

GTL_D#30

GTL_D#31

GTL_D#32

GTL_D#33

GTL_D#34

GTL_D#35

GTL_D#36

GTL_D#37

GTL_D#38

GTL_D#39

GTL_D#40

GTL_D#41

GTL_D#42

GTL_D#43

GTL_D#44

GTL_D#45

GTL_D#46

GTL_D#47

GTL_D#48

GTL_D#49

GTL_D#50

GTL_D#51

GTL_D#52

GTL_D#53

GTL_D#54

GTL_D#55

GTL_D#56

GTL_D#57

GTL_D#58

GTL_D#59

GTL_D#60

GTL_D#61

GTL_D#62

GTL_D#63

GTL_DSTBN#0

GTL_DSTBN#1

GTL_DSTBN#2

GTL_DSTBN#3

GTL_DSTBP#0

GTL_DSTBP#1

GTL_DSTBP#2

GTL_DSTBP#3

GTL_DINV#0

GTL_DINV#1

GTL_DINV#2

GTL_DINV#3

1

HDVREF

BC477

SCD047U25V3KX

HACVREF

BC476

SCD047U25V3KX

R521

HOSTSENSENP

51R3F

The resistors should be placed near

to NB

R520

41D2R3F

64.41R25.651

SB

VCC_CORE_S0

VCC_CORE_S0

R611

80D6R3F

R612

121R3F

VCC_CORE_S0

R609

80D6R3F

R610

121R3F

GTL_DSTBN#0 4

GTL_DSTBN#1 4

GTL_DSTBN#2 4

GTL_DSTBN#3 4

GTL_DSTBP#0 4

GTL_DSTBP#1 4

GTL_DSTBP#2 4

GTL_DSTBP#3 4

GTL_DINV#0 4

GTL_DINV#1 4

GTL_DINV#2 4

GTL_DINV#3 4

GTL_D#[63..0] 4

BC475

SCD1U16V

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

BC474

SCD1U16V

Use 10 mils trace, isolate with 7 mils

space, place caps near to NB pins

HOSTSENSEN

VCORE 1.1V~1.85V/60A

VCC_CORE_S0

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Ta iwan, R.O.C.

N/B ALI 1671 (1/4)

A7

1

6 43Monday, June 10, 2002

-3

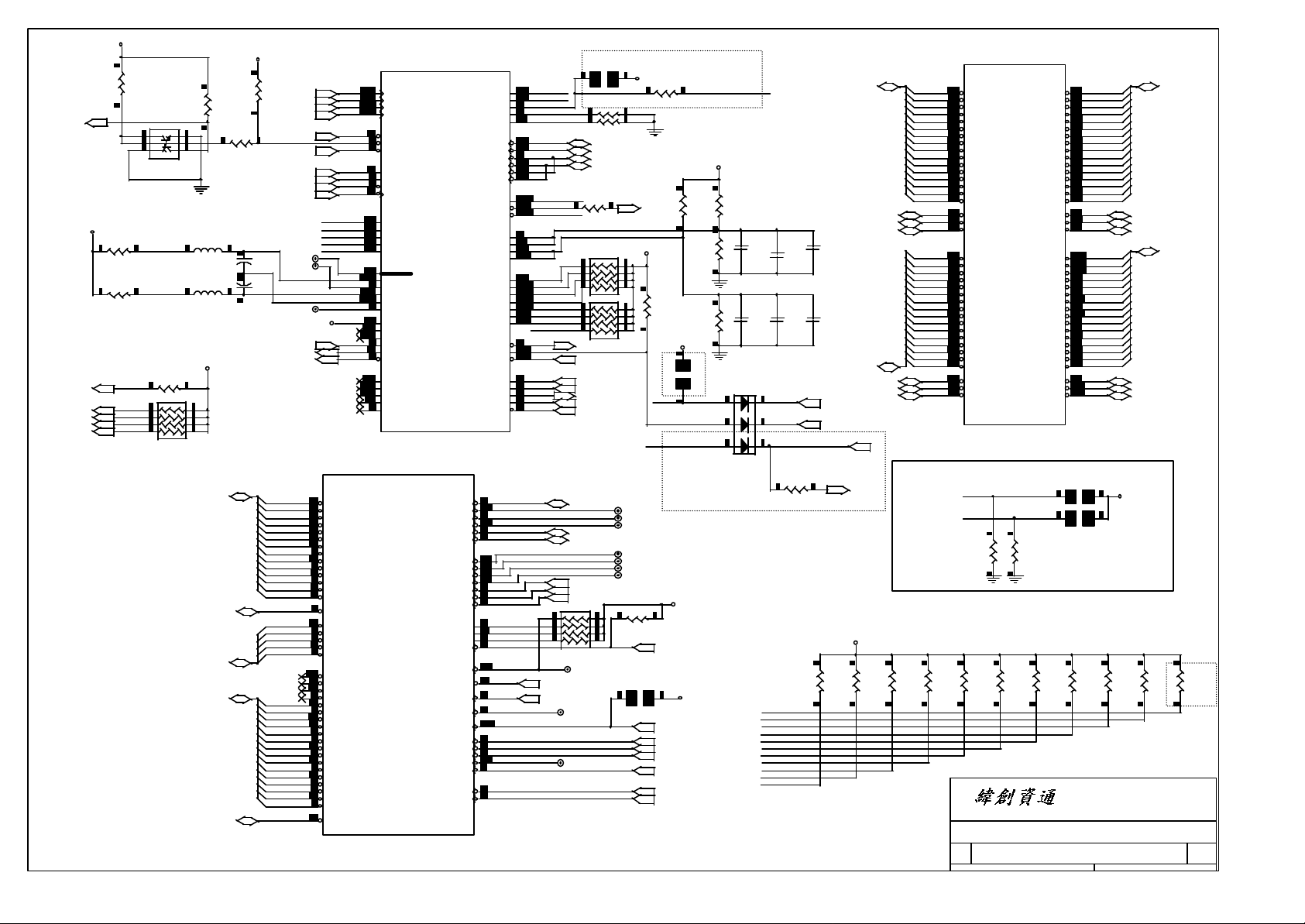

5

R600

D D

1D5V_S0 1D5V_AGP_S0

0R5

1D5V_AGP_S0

BC464

BC581

SCD1U16V

BC537

SCD1U16V

SCD1U16V

BC538

SCD1U16V

BC535

SCD1U16V

BC497

SCD1U16V

Near M1671

1D5V_S0

C C

1D5V_S0

RP12

SRP8K2-1

R76 8K2R2

R72 8K2R2

R633 8K2R2

R151 8K2R2

R95 8K2R2

R558 8K2R2

R559 8K2R2

5

AGP_FRAME#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_WBF#

AGP_RBF#

AGP_ADSTB1

AGP_ADSTB0

AGP_SB_STB

AGP_REQ#

AGP_PIPE#

3D3V_S0

R606

8K2R3

AGP_C/BE#[3..0]14

AGP_DEVSEL#

AGP_SERR#

B B

A A

AGP_AD[31..0]14

BC496

SCD1U16V

4

CLK66_1671

C31

DUMMY-C3

R560

0R2-0

TP44

TPAD30

R603 8K2R2

R152 8K2R2

R94 8K2R2

4

CLK66_16713

AGP_AD[31..0]

BC494

SC10U10V6ZY-U

AGP_ADSTB1#14

AGP_ADSTB0#14

AGP_ADSTB114

AGP_ADSTB014

AGP_ST010,14

AGP_ST110,14

AGP_ST210,14

AGP_RBF#14

AGP_WBF#14

AGP_PIPE#14

AGP_PAR14

AGP_GNT#10,14

AGP_REQ#14

AGP_STOP#14

AGP_DEVSEL#14

AGP_TRDY#14

AGP_IRDY#14

AGP_FRAME#14

AGP_ADSTB1#

AGP_ADSTB0#

AGP_SB_STB#

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_SB_STB

AGP_SB_STB#

TYPEDETJ

AGP_SERR#

AGP8X_DET#

U6C

GCLK

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

AD_STB1#

AD_STB0#

AD_STB1

AD_STB0

GCBE0#

GCBE1#

GCBE2#

GCBE3#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STB

SB_STB#

ST0

ST1

ST2

RBF#

WBF#

TYPEDET#

PIPE#

GPAR

GSERR#

GGNT#

GREQ#

GSTOP#

GDEVSEL#

GTRDY#

GIRDY#

GFRAME#

AGP8X_DET#

DBI_L0

DBI_H1

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

M1671-U1

71.M1671.00U

3

ALi M1671

( 3 of 4 )

AGP

CPU GND

(57Balls)

3

PLL

AGP

POWER

(10Ball)

AGP

GND

(10Ball)

AAG_AGP

AVDDA_AGP

VREF_AGP

VREF1_AGP

SHIELD_AGP

SENSE_AGP

AIPOW1

AIPOW2

AIGND

P3G

P3G

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

AGPGND

AGPGND

AGPGND

AGPGND

AGPGND

AGPGND

AGPGND

AGPGND

AGPGND

AGPGND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

HOST_GND

2

2D5V_AVDDA_S3

SENSE_AGP

1D5V_AIPOW1_S3

2D5V_A2POW2_S3

R634

3D3V_AGP_S3

0R3-0-U

1D5V_AGP_S0

BC711

SCD1U16V

2

NB_GREF

R635

1D5V_S0

R586

1KR3

63.10234.151

1

SC

120R3-1

3D3V_S3

1D5V_S0

SB

R584

1KR3

63.10234.151

BC536

SCD1U16V

-2

PLACE ON M1647 SOLDER SIDE

1D5V_AGP_S0

Title

Size Document Number Rev

Custom

Date: Sheet of

NB_GREF

BC495

SCD1U16V

2D5V_S3

SC1 000P50V3KX

SC1 000P50V3KX

-1

L44

4D7R5

63.4R733.161

2D5V_AVDDA_S3

BC499

BC498

SCD1U16V

2D5V_S3

R636

4D7R3

1D5V_AIPOW1_S3 2D5V_A2POW2_S3

BC540

BC539

SCD1U16V

R637

4D7R3

BC543

SC1 000P50V3KX

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

N/B ALI 1671 (2/4)

A7

1

7 43Monday, June 10, 2002

BC542

SCD1U16V

-3

5

4

3

2

1

2D5V_S3

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

P2A

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

G/T

BC709

SCD1U16V

U6D

PCICLK

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0#

CBE1#

CBE2#

CBE3#

PTRDY#

PIRDY#

PSTOP#

PLOCK#

PDEVSEL#

PAR_PCI

PFRAME#

SERR#/CLKRUN#

PREQ0#

PREQ1#

PREQ2#

PREQ3#

PREQ4#

PREQ5#

PREQ6#

PGNT0#

PGNT1#

PGNT2#

PGNT3#

PGNT4#

PGNT5#

PGNT6#

PHLD#

PHLDA#

PCIRST#

AREQ#

RATIO#

PCI_5V

PCI_5V

P3A

P3A

PCI

P3A

P3A

POWER

PCI_GND

PCI_GND

PCI_GND

M1671-U1

71.M1671.00U

ALi M1671

( 4 of 4 )

Core

POWER

(17Ball)

PCI

Thermal

GND

(51Ball)

SB

Signal

D D

CLK33_16713

P_AD[31..0]10,19,24,25,26,28,29,30

C C

P_C/BE#[3..0]10,19,24,25,26,28,29,30

P_REQ#124

P_REQ#225,26

P_REQ#328

P_REQ#430

B B

PCIREQ#_310,20

PM_DPRSLPVR

A A

P_REQ#529

P_GNT#124

P_GNT#225,26

P_GNT#328

P_GNT#430

P_GNT#529

PHOLD#19,20

3D3V_S0

R210

DUMMY-R2

3D3V_S3

PCIRST#14,17,19,24,25,26,27,28,29,30,33

R605

10KR2

BC707

SC10U10V-U

P_TRDY#19,24,25,26,28,29,30

P_IRDY#19,24,25,26,28,29,30

P_STOP#19,24,25,26,28,29,30

P_PLOCK#25

P_DEVSEL#19,24,25,26,28,29,30

P_PAR19,24,25,26,28,29,30

P_FRAME#19,24,25,26,28,29,30

P_SERR#10,19,24,25,26,29,30

5V_S3

3D3V_S3

-2

BC708

SCD1U16V

R561

0R2-0

P_AD0

P_AD1

P_AD2

P_AD3

P_AD4

P_AD5

P_AD6

P_AD7

P_AD8

P_AD9

P_AD10

P_AD11

P_AD12

P_AD13

P_AD14

P_AD15

P_AD16

P_AD17

P_AD18

P_AD19

P_AD20

P_AD21

P_AD22

P_AD23

P_AD24

P_AD25

P_AD26

P_AD27

P_AD28

P_AD29

P_AD30

P_AD31

P_C/BE#0

P_C/BE#1

P_C/BE#2

P_C/BE#3

P_REQ#0

P_REQ#6

P_GNT#0

P_GNT#6

AREQ#

RATIOJ_NB

PHLDA#

-2

5

4

3

2D5V_S3

BC544

SCD1U16V

PCIREQ#_3

PHLDA#19

P_STOP#

P_PLOCK#

P_GNT#0

P_GNT#1

P_GNT#2

P_GNT#3 P_GNT#6

P_REQ#0

P_REQ#1

P_REQ#2

P_REQ#3

RP10

SRP8K2-1

RP9

SRP8K2-1

RP11

SRP8K2-1

BC541

SCD1U16V

R702

DUMMY-R3

R604 10KR2

3D3V_S0

3D3V_S0

3D3V_S0

2

BC502

SCD1U16V

BC500

SCD1U16V

BC505

SC10U10V6ZY-U

Near M1671

3D3V_S0

P_FRAME#

P_DEVSEL#

P_IRDY#

P_TRDY#

P_GNT#4

P_GNT#5

P_REQ#4

P_REQ#5

P_REQ#6

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Title

Size Document Number Rev

Custom

Date: Sheet of

Taipei Hsien 221, Ta iwan, R.O.C.

N/B ALI 1671 (3/4)

A7

1

8 43Monday, June 10, 2002

-3

5

CLKD_1671 CLKD_1671#

C32

DUMMY-C3

D D

2D5V_S3

BC85

BC86

BC84

SCD1U16V

SCD1U16V

SCD1U16V

BC87

SC10U10V-U

C33

DUMMY-C3

BC96

SC10U10V-U

BC665

SCD1U16V

Near M1671

SB

C C

SB_SUS#_314,19

B B

2D5V_S3

PLACE NEAR M1671 SOLDER SIDE

-1

L45

4D7R5

63.4R733.161

2D5V_MVDDA_S3

BC88

A A

BC89

SC1 000P50V5KX

SC D1U16V3KX

5

2D5V_S3

BC582

SCD1U16V3KX

78.10421.2B1

DDR_VREF_1

BC583

SCD1U16V3KX

78.10421.2B1

-1

R657

470R3F

R658

470R3F

-1

CLKD_16713

CLKD_1671#3

BC666

SCD1U16V

3D3V_S3

4

R155

10KR2

4

BC667

SCD1U16V

M_A[12..0]11

R154

10KR2

5V_S3

U95A

+

LMV822MM

74.00822.019

R863 DUMMY-R3

CLK32KO_5RSM19,20

R638

121R5F

64.12105.561

M_A[12..0]

M_BS0_R#11

M_BS1_R#11

M_CKE0_R#11

M_CKE1_R#11

M_CKE2_R#11

M_CKE3_R#11

M_CS0_R#11

M_CS1_R#11

M_CS2_R#11

M_CS3_R#11

R153

10KR2

M_WE#11

M_CAS#11

M_RAS#11

TESTMODE

TESTEN1

DDR_VREF

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

2D5V_MVDDA_S3

2D5V_S3

BC670

SCD1U16V

3

U6A

DCLK

DCLK#

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

BA0

BA1

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

WE#

SCAS#

SRAS#

CLK32KI

SUSPEND#

TESTMODE

TESTEN1

MVDDA

MAG

D_VREF1

D_VREF2

D_VREF3

D_VSHIELD1

D_VSHIELD2

P1B

P1B

P1B

P1B

P1B

P1B

P1B

P1B

P1B

P1B

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

M1671-U1

71.M1671.00U

BC671

SCD1U16V

3

ALi M1671

(2 of 4)

DRAM DDR

Address

Bus

MISC

PLL

DRAM

POWER

DRAM

GND

BC672

SCD1U16V

Data

Bus

VREFOUT = 1.25V

BC706

SCD47U10V3ZY

-1

DDR_VREF 12

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

2

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_DQS0

M_DQS1

M_DQS2

M_DQS3

M_DQS4

M_DQS5

M_DQS6

M_DQS7

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

2

M_DATA[63..0]

M_DQS[7..0]

M_DM[7..0]

Title

Size Document Number Rev

Custom

Date: Sheet of

M_DATA[63..0] 11

M_DQS[7..0] 11

M_DM[7..0] 11

N/B ALI 1671 (4/4)

A7

1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

9 43Monday, June 10, 2002

1

-3

5

1D5V_AGP_S0 3D3V_S0

1D5V_AGP_S0

D D

1D5V_AGP_S0

1D5V_AGP_S0

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0

C C

R602 10KR2 R557 10KR2

R73 DUMMY-R2

R75 DUMMY-R2

R78 10KR2

R592 DUMMY-R2

-2

R554 DUMMY-R2

R601

DUMMY-R2

R79 2K2R2

R77 2K2R2

R74

DUMMY-R2

R591 2K2R2

R84 10KR2R86 DUMMY-R2

R109 DUMMY-R2R110 2K2R2

R555 2K2R2

AGP_ST2 7,14

AGP_ST1 7,14

AGP_ST0 7,14

AGP_GNT# 7,14

P_C/BE#3 8,19,24,25,26,28,29,30

P_C/BE#2 8,19,24,25,26,28,29,30

P_C/BE#1 8,19,24,25,26,28,29,30

P_C/BE#0 8,19,24,25,26,28,29,30

4

R556 DUMMY-R2

3D3V_S0

R113 DUMMY-R2

3D3V_S0

R122 DUMMY-R2

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0 3D3V_S0

R112 10KR2

R121 DUMMY-R2

R599 DUMMY-R2

R593 10KR2

R111 2K2R2

R123 2K2R2

R115 DUMMY-R2

R120 2K2R2

R596 2K2R2

R594 DUMMY-R2

R117 DUMMY-R2R118 10KR2

3

P_AD11 8,19,24,25,26,28,29,30

3D3V_S0

P_AD12 8,19,24,25,26,28,29,30

3D3V_S0

P_AD13 8,19,24,25,26,28,29,30

3D3V_S0

P_AD14 8,19,24,25,26,28,29,30

3D3V_S0

P_AD15 8,19,24,25,26,28,29,30

3D3V_S0

P_AD16 8,19,24,25,26,28,29,30

3D3V_S0

P_AD17 8,19,24,25,26,28,29,30

3D3V_S0

P_AD18 8,19,24,25,26,28,29,30

R68 DUMMY-R2

R59 10KR2

R67 10KR2

R62 DUMMY-R2

R598 DUMMY-R2

R57 10KR2

R70 10KR2

R553 DUMMY-R2

R66 2K2R2

R60 DUMMY-R2

R69 DUMMY-R2

R61 2K2R2

R595 2K2R2

R58 DUMMY-R2

R71 DUMMY-R2

R552 2K2R2

2

P_AD24 8,19,24,25,26,28,29,30

P_AD25 8,19,24,25,26,28,29,30

P_AD26 8,19,24,25,26,28,29,30

P_AD27 8,19,24,25,26,28,29,30

P_AD28 8,19,24,25,26,28,29,30

P_AD29 8,19,24,25,26,28,29,30

P_AD30 8,19,24,25,26,28,29,30

P_AD31 8,19,24,25,26,28,29,30

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0

3D3V_S0

R607 10KR2

R89 10KR2

R91 10KR2

R116 DUMMY-R2

R87 DUMMY-R2

R93 DUMMY-R2

R64 10KR2

1

P_SERR# 8,19,24,25,26,29,30

R114

DUMMY-R2

P_AD19 8,19,24,25,26,28,29,30

R90 DUMMY-R2

P_AD20 8,19,24,25,26,28,29,30

R119 2K2R2

P_AD21 8,19,24,25,26,28,29,30

R88 2K2R2

P_AD22 8,19,24,25,26,28,29,30

R92 2K2R2

P_AD23 8,19,24,25,26,28,29,30

R85 DUMMY-R2

PCIREQ#_3 8,20

AD BUS

AD11

AD[14:12]

Ctrl target

CPU Bus Drivint Ctrl mode.

CPU Bus Drving Low Strength

Ctrl. (when AD[11] pull low)

Definition

1: tracking circuit; 0: by AD[17:12]

000: Default Driving

001: Default + 1X Driving

:

111: Default + 7X Driving

AD[17:15]

B B

AD BUS

GGNT

CBE3 IntPLLSel(3) , Select number

A A

CBE2

CBE1

CBE0

CPU Bus Termination Strength

Ctrl (when AD[11] pull low)

DRAM type selection

ST2

ST1

ST0

PLL_EN , Internal PLL

enable/disable

IntPLLSel(5) , Select number

of PLL stage compensation

IntPLLSel(4) , Select number

of PLL stage compensation

Reserved for interal PLL

test mode

of PLL stage compensation

IntPLLSel(2) , Select number

of PLL stage compensation

IntPLLSel(1) , Select number

of PLL stage compensation

IntPLLSel(0) , Select number

of PLL stage compensation

Ctrl target

5

000: Default Driving

001: Default + 1X Driving

:

111: Default + 7X Driving

1: DDR; 0 : SDRAD18

Definition

Pull high for normal

fucntion

Ref. Config Register

Ref. Config Register

1: Disable PLL test mode

0: Enable PLL test mode

Ref. Config Register

Ref. Config Register

Ref. Config Register

Ref. Config Register

AD[27:24]

CPU Data Bus Strobe (N)

Timing Ctrl Offset mode.

AD[31:28]:CPU Data Bus Strobe (P)

Timing Ctrl Offset mode.

OFFset mode:

0000 : 1 stage delay (~150ps)

0001 : 2 stage delay

:

1111 : 16 stage delay

Multiply mode

0000 : 1/64 front-side bus cycle time

0001 : 2/64 front-side bus cycle time

:

1111 : 16/64 front-side bus cycle time

OFFset mode:

0000 : 1 stage delay (~150ps)

0001 : 2 stage delay

:

PCIREQ#

SERRJ

AD19

AD[23:20]

Reserved

Reserved for Normal

and Test Mode

CPU Bus Strobe Timing Ctrl

CPU Address/Command

Bus Strobe Timing

Control Offset mode.

Must pull high

1: Enable Normal mode

0: Enable Test mode

1: Multiply mode; 0 : Offset mode

OFFset mode:

0000 : 1 stage delay (~150ps)

0001 : 2 stage delay

:

1111 : 16 stage delay

Multiply mode

0000 : 1/32 front-side bus cycle time

0001 : 2/32 front-side bus cycle time

:

1111 : 16/32 front-side bus cycle time

1111 : 16 stage delay

Multiply mode

0000 : 1/64 front-side bus cycle time

0001 : 2/64 front-side bus cycle time

1111 : 16/64 front-side bus cycle time

4

3

2

Title

N/B 1671 HARDWARE SETTING

Size Document Number Rev

Custom

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

A7

10 43Monday, June 10, 2002

1

-3

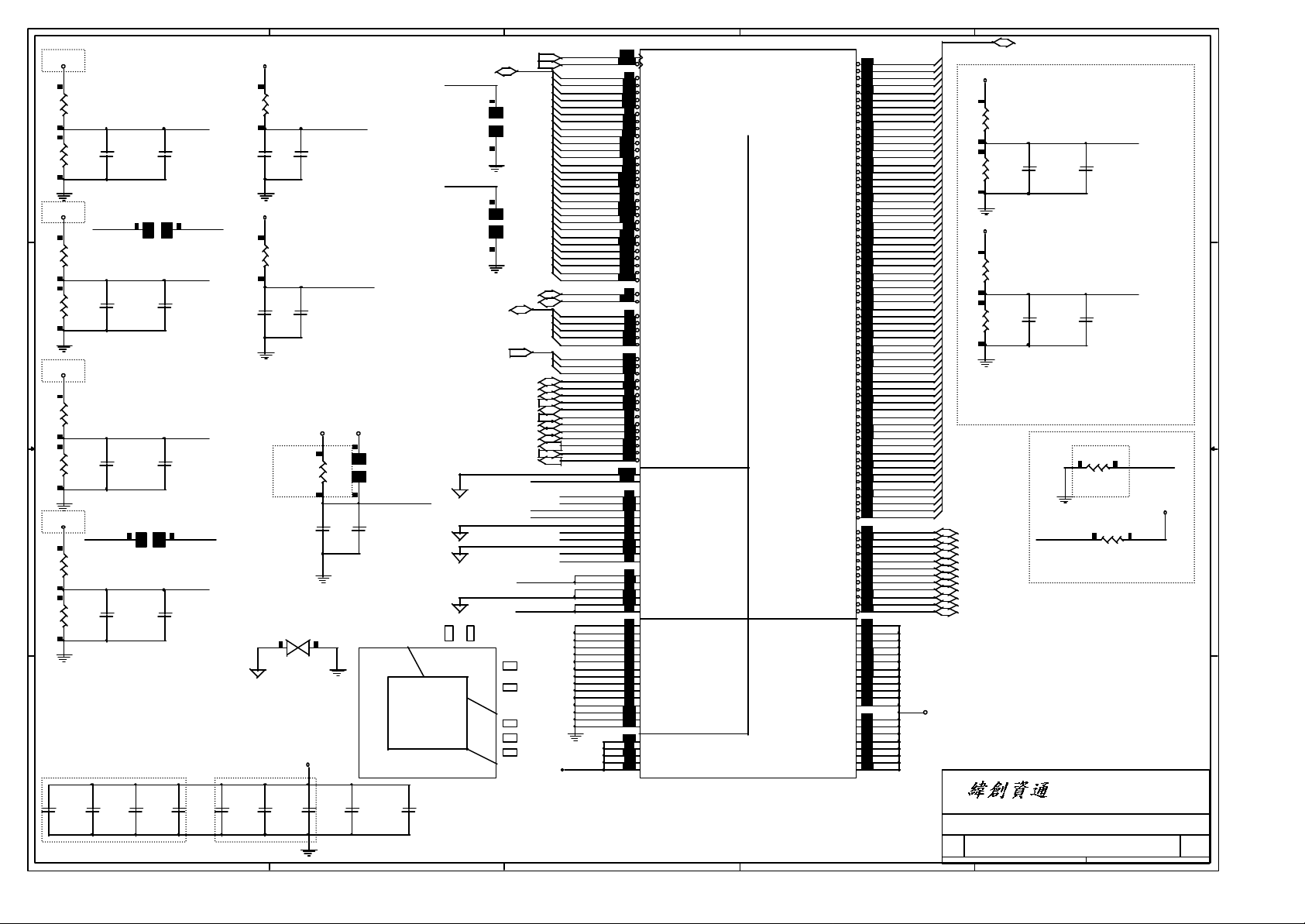

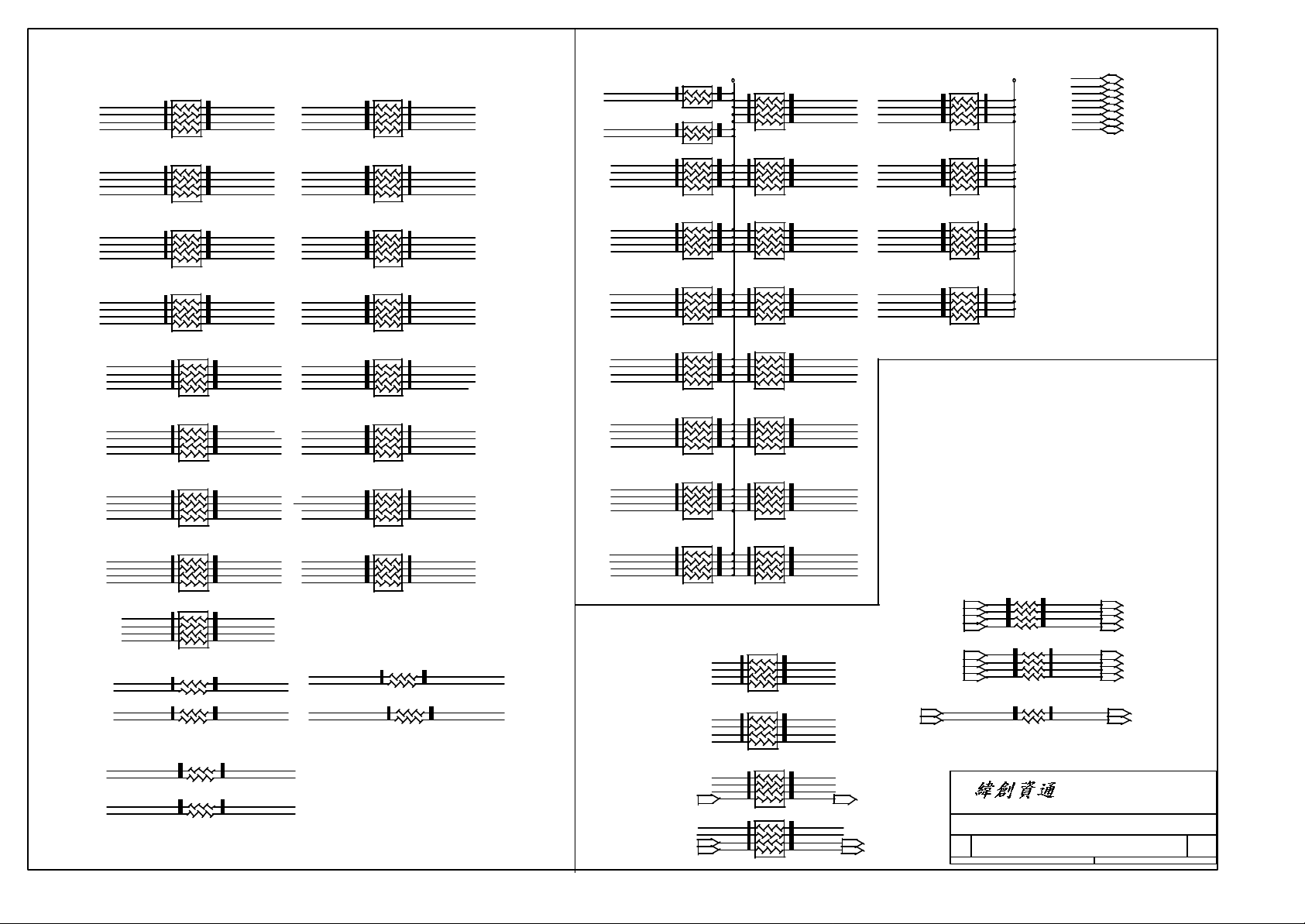

SERIES DAMPING PARALLEL TERMINATION

PLACE RNs CLOSE TO DM1, < 0.75"

STRICT EQUAL LENGTH LIMITATION WITH DQS, CB PINS

M_DATA0

M_DATA1

M_DQS0

M_DATA2

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA3

M_DATA8

M_DATA9

M_DQS1

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA25

M_DQS3

M_DATA26

M_DATA27

M_DATA29

M_DM3

M_DATA30

M_DATA31

M_DQS2

M_DATA18

M_DATA19

M_DATA24

M_DATA42

M_DATA43

M_DATA48

M_DATA49

M_DM5

M_DM4

M_DM7

M_DM6

M_DM1

M_DM0

M_DATA28

M_DM2 M_DM_R2

RN48

M_DATA_R_0

M_DATA_R_1

M_DQS_R0

M_DATA_R_2

SRN22-1

RN27

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

SRN22-1

RN47

M_DATA_R_3

M_DATA_R_8

M_DATA_R_9

M_DQS_R1

SRN22-1

RN25

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

SRN22-1

RN24

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

SRN22-1

RN40

M_DATA_R_25

M_DQS_R3

M_DATA_R_26

M_DATA_R_27

SRN22-1

RN22

M_DATA_R_29

M_DM_R3

M_DATA_R_30

M_DATA_R_31

SRN22-1

RN42

SRN22-1

RN32

M_DATA_R_42

M_DATA_R_43

M_DATA_R_48

M_DATA_R_49

SRN22-1 RN20

RN17

SRN22J

RN14

SRN22J

RN26

SRN22J

RN23

SRN22J

M_DQS_R2

M_DATA_R_18

M_DATA_R_19

M_DATA_R_24

M_DM_R5

M_DM_R4

M_DM_R7

M_DM_R6

M_DM_R1

M_DM_R0

M_DATA_R_28

M_DATA32

M_DATA33

M_DQS4

M_DATA34

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA35

M_DATA40

M_DATA41

M_DQS5

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DQS6

M_DATA50

M_DATA51

M_DATA56

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA57

M_DQS7

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_DATA17

M_DATA16

M_DATA11

M_DATA10

1D25V_S3 MUST KEEP A 15~20 MILS AWAY FROM OTHER SIGNALS

M_DATA_R_1

RN36

SRN22-1

RN18

SRN22-1

RN34

SRN22-1

RN16

SRN22-1

RN30

SRN22-1

RN15

SRN22-1

RN28

SRN22-1

RN13

SRN22-1

RN44

SRN22J

RN45

SRN22J

M_DATA_R_32

M_DATA_R_33

M_DQS_R4

M_DATA_R_34

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_35

M_DATA_R_40

M_DATA_R_41

M_DQS_R5

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DQS_R6

M_DATA_R_50

M_DATA_R_51

M_DATA_R_56

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_57

M_DQS_R7

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_DATA_R_17

M_DATA_R_16

M_DATA_R_11

M_DATA_R_10

M_DATA_R_0

M_DATA_R_4

M_DATA_R_5

M_DQS_R0

M_DM_R0

M_DATA_R_6

M_DATA_R_2

M_DATA_R_3

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DM_R2

M_DATA_R_19

M_DATA_R_24

M_DATA_R_25

M_DATA_R_13

M_DM_R1

M_DATA_R_14

M_DATA_R_15

M_DQS_R3

M_DM_R3

M_DATA_R_26

M_DATA_R_27

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_16

M_DATA_R_17

M_DQS_R2

M_DATA_R_18

1D25V_S3 1D25V_S3

RN50

SRN33-2-U1

RN49

SRN33-2-U1

RN62

SRN33-1

RN61

SRN33-1

RN58

SRN33-1

RN46

SRN33-1

RN57

SRN33-1

RN43

SRN33-1

RN59

SRN33-1

PLACE BETWEEN DM1, DM2

CLOSE TO DM2 < 0.2", TO DM1 < 1.1"

EQUAL LENGTH LIMITATION WITH

SCK/SCK#

M_WE#9

M_CAS#9

M_RAS#9

M_A11

M_A8

M_A6

M_A4

M_A12

M_A9

M_A7

M_A5

M_A3

M_A1

M_A10

M_A2

M_A0

RN56

SRN33-1

RN35

SRN33-1

RN53

SRN33-1

RN33

SRN33-1

RN52

SRN33-1

RN31

SRN33-1

RN51

SRN33-1

RN29

SRN33-1

SRN10-1

SRN10-1

RN37

SRN10-1

RN19

SRN10-1

PULL HIGH STUBS < 0.8", PLACE RPs CLOSE TO DM2

NO EQUAL LENGTH LIMITATION

M_DATA_R_34

M_DQS_R4

M_DATA_R_33

M_DATA_R_32

M_DATA_R_39

M_DATA_R_38

M_DATA_R_37

M_DATA_R_36

M_DATA_R_49

M_DATA_R_48

M_DQS_R6

M_DM_R6

M_DATA_R_47

M_DATA_R_46

M_DATA_R_45

M_DATA_R_44

M_DATA_R_50

M_DATA_R_51

M_DATA_R_56

M_DATA_R_57

M_DATA_R_55

M_DATA_R_54

M_DATA_R_53

M_DATA_R_52

M_DATA_R_59

M_DATA_R_58

M_DQS_R7

M_DM_R7

M_DATA_R_63

M_DATA_R_62

M_DATA_R_61

M_DATA_R_60

M_A_R_11

M_A_R_8

M_A_R_6

M_A_R_4

M_A_R_12

M_A_R_9

M_A_R_7

M_A_R_5

M_A_R_3

M_A_R_1

M_A_R_10

M_A_R_2

M_A_R_0

M_DATA_R_12

M_DQS_R1

M_DATA_R_10

M_DATA_R_11

M_DQS_R5

M_DM_R5

M_DATA_R_42

M_DATA_R_43

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DM_R4

M_DATA_R_35

M_DATA_R_40

M_DATA_R_41

M_BS0_R#9

M_BS1_R#9

M_WE_R# 12

M_CAS_R# 12

M_RAS_R# 12

RN60

SRN33-1

RN54

SRN33-1

RN41

SRN33-1

RN55

SRN33-1

M_CKE0_R#9

M_CKE1_R#9

M_CKE2_R#9

M_CKE3_R#9

M_CS0_R#9

M_CS1_R#9

M_CS2_R#9

M_CS3_R#9

Title

Size Document Number Rev

A3

Date: Sheet of

M_DATA[63..0] 9

M_DATA_R_[63..0] 12

M_DQS[7..0] 9

M_DQS_R[7..0] 12

M_DM[7..0] 9

M_DM_R[7..0] 12

M_A[12..0] 9

M_A_R_[12..0] 12

R213 10R2

R253 10R2

R252 10R2

R277 10R2

R250 10R2

R212 10R2

R275 10R2

R249 10R2

R276

R251RN38

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Taipei Hsien 221, Ta iwan, R.O.C.

MCKE0_R# 12

MCKE1_R# 12

MCKE2_R# 12

MCKE3_R# 12

MCS0_R# 12

MCS1_R# 12

MCS2_R# 12

MCS3_R# 12

MBS0_R# 12

MBS1_R# 12

DDR DAMPING & TERMINATION

A7

11 43Monday, June 10, 2002

-3

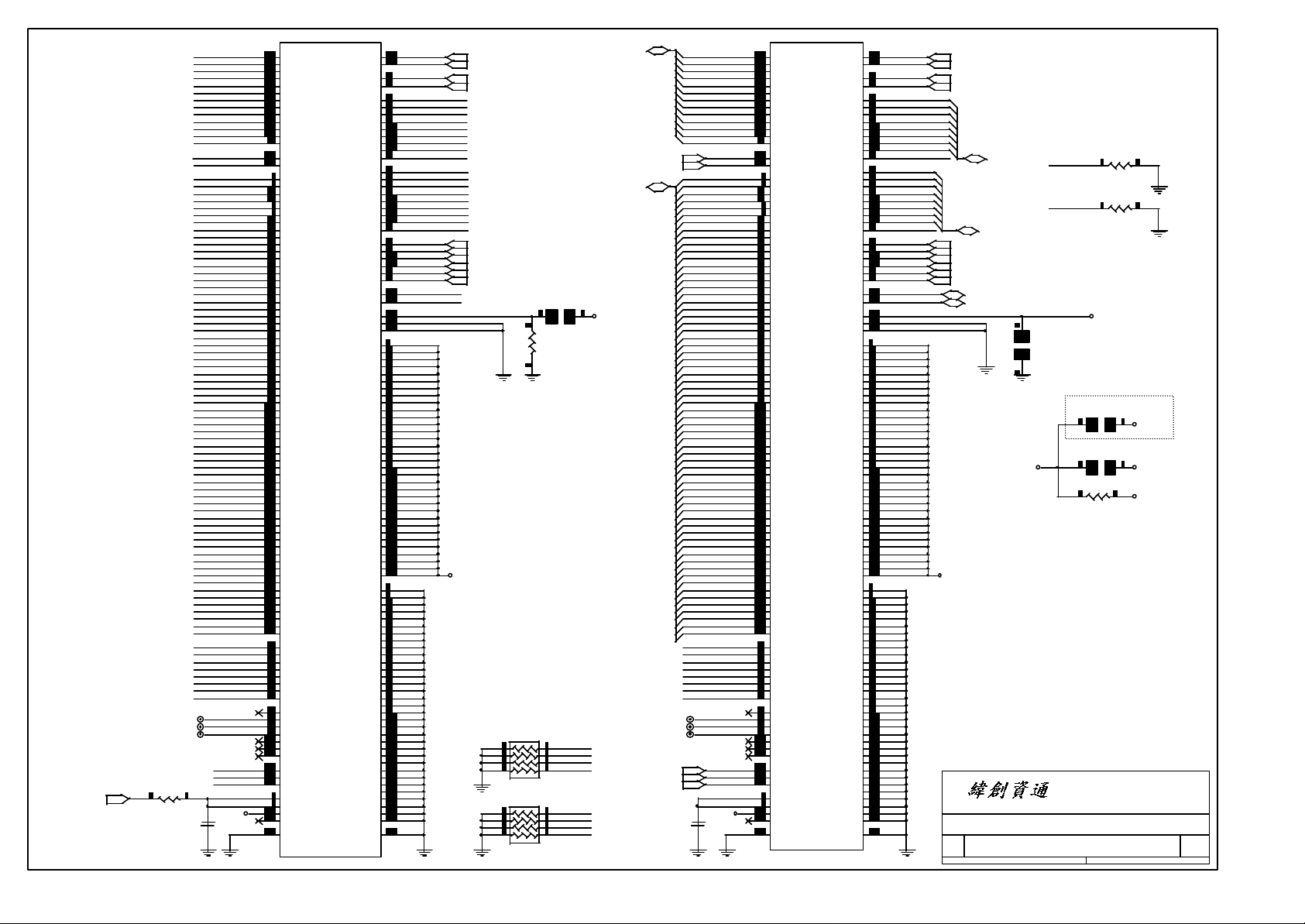

M_A_R_0

M_A_R_1

M_A_R_2

M_A_R_3

M_A_R_4

M_A_R_5

M_A_R_6

M_A_R_7

M_A_R_8

M_A_R_9

M_A_R_10

M_A_R_11

M_A_R_12

MBS0_R#

MBS1_R#

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_CB_R0

M_CB_R1

M_CB_R2

M_CB_R3

M_CB_R4

M_CB_R5

M_CB_R6

M_CB_R7

DM1_RESET#

TP52TPAD30

DM1_A13

TP12TPAD30

DM1_BA2

TP51TPAD30

M_RAS_R#

M_CAS_R#

BC113

SCD1U16V

M_WE_R#

DDR_VREF_SKT

VDD_SPD_S0

DDR_VREF9

R215

0R3-0-U

DM1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 / AP

A11

A12

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32 VDD

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC/(RESET#)

NC/A13

NC/BA2

NC

NC

NC

/RAS

/CAS

/WE

VREF

VREF

VDDSPD

VDDID

DDR-SODIMM-N

62.10017.191

NORMAL TYPE

/CS0

/CS1

CKE0

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GNDGND

SMBC_1535+

SMBD_1535+

DM1_SA0

DM1_SA1

DM1_SA2

MCS0_R# 11

MCS1_R# 11

MCKE0_R# 11

MCKE1_R# 11

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_DQS_R8

M_DM_R0

M_DM_R1

M_DM_R2

M_DM_R3

M_DM_R4

M_DM_R5

M_DM_R6

M_DM_R7

M_DM_R8

CLK_DDR1 3

CLK_DDR1# 3

CLK_DDR2 3

CLK_DDR2# 3

CLK_DDR0 3

CLK_DDR0# 3

R246

DUMMY-R2

R248

0R2-0

2D5V_S3 2D5V_S3

RN39

SRN10K-3

RN21

SRN10K-3

M_CB_R0

M_CB_R1

M_CB_R2

M_CB_R3

M_CB_R4

M_CB_R5

M_CB_R6

M_CB_R7

M_A_R_[12..0]11

MBS0_R#11

MBS1_R#11

M_DATA_R_[63..0]11

M_RAS_R#11

M_CAS_R#11

M_WE_R#11

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_CB_R0

M_CB_R1

M_CB_R2

M_CB_R3

M_CB_R4

M_CB_R5

M_CB_R6

M_CB_R7

TP20TPAD30

TP62TPAD30

TP19TPAD30

BC139

SCD1U16V

M_A_R_0

M_A_R_1

M_A_R_2

M_A_R_3

M_A_R_4

M_A_R_5

M_A_R_6

M_A_R_7

M_A_R_8

M_A_R_9

M_A_R_10

M_A_R_11

M_A_R_12

DM2_RESET#

DM2_A13

DM2_BA2

DDR_VREF_SKT

VDD_SPD_S0

DM2

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 / AP

A11

A12

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32 VDD

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC/(RESET#)

NC/A13

NC/BA2

NC

NC

NC

/RAS

/CAS

/WE

VREF

VREF

VDDSPD

VDDID

GND GND

DDR-SODIMM-R

62.10017.201

REVERSE

CKE0

CKE1

/CS0

/CS1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_DQS_R8

M_DM_R0

M_DM_R1

M_DM_R2

M_DM_R3

M_DM_R4

M_DM_R5

M_DM_R6

M_DM_R7

M_DM_R8

DM2_SA1

DM2_SA2

TYPE

MCS2_R# 11

MCS3_R# 11

MCKE2_R# 11

MCKE3_R# 11

M_DQS_R[7..0] 11

M_DM_R[7..0] 11

CLK_DDR4 3

CLK_DDR4# 3

CLK_DDR5 3

CLK_DDR5# 3

CLK_DDR3 3

CLK_DDR3# 3

SMBC_1535+ 3,18,19,20,22

SMBD_1535+ 3,18,19,20,22

M_DM_R8

R247

DUMMY-R2

M_DQS_R8

R214

10KR2

R673

10KR2

VDD_SPD_S0VDD_SPD_S0

Should be 0 ohmShould be 0 ohm

-2

R884

DUMMY-R2

2D5V_S0

R245

DUMMY-R2

VDD_SPD_S0

R244

0R2-0

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Ta iwan, R.O.C.

DDR SO-DIMM SKT

A7

3D3V_S3

3D3V_S0

12 43Monday, June 10, 2002

-3

1D25V_S3

PLACE ONE CAP CLOSE TO EVERY 2 PULL-UP TERMINATION RESISTORS, CRB-P13

DATA(64)+ADD(13)+DQS(9)+CB(8)+CMD(13)=107

0.1UF 0603 Y5V 27X

BC161

SCD1U16V

BC126

SCD1U16V

BC110

SCD1U16V

BC112

SCD1U16V

BC164

SCD1U16V

BC130

SCD1U16V

BC132

SCD1U16V

BC134

SCD1U16V

BC165

SCD1U16V

BC135

SCD1U16V

PLACE CAPS BETWEEN AND NEAR DDR SKTS

PLACE EACH 0.1UF CAP CLOSE TO POWER

PIN

BC128

SCD1U16V

BC108

SCD1U16V

BC163

SCD1U16V

BC138

SCD1U16V

BC156

SCD1U16V

BC127

SCD1U16V

BC167

SCD1U16V

BC152

SCD1U16V

BC136

SCD1U16V

BC160

SCD1U16V

BC170

SCD1U16V

BC162

SCD1U16V

BC168

SCD1U16V

BC131

SCD1U16V

BC169

SCD1U16V

BC157

SCD1U16V

BC111

SCD1U16V

BC109

SCD1U16V

BC166

SCD1U16V

BC153

SCD1U16V

BC137

SCD1U16V

BC124

SCD1U16V

2D5V_S3

BC125

SCD1U16V

BC154

SCD1U16V

BC140

SCD1U16V

BC155

SCD1U16V

BC133

SCD1U16V

BC159

SCD1U16V

BC158

SCD1U16V

BC129

SCD1U16V

BC107

SCD1U16V

BC115

SC4D7U10V-U

BC114

SC4D7U10V-U

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Ta iwan, R.O.C.

DDR DECOUPLING

A7

13 43Monday, June 10, 2002

-3

Loading...

Loading...