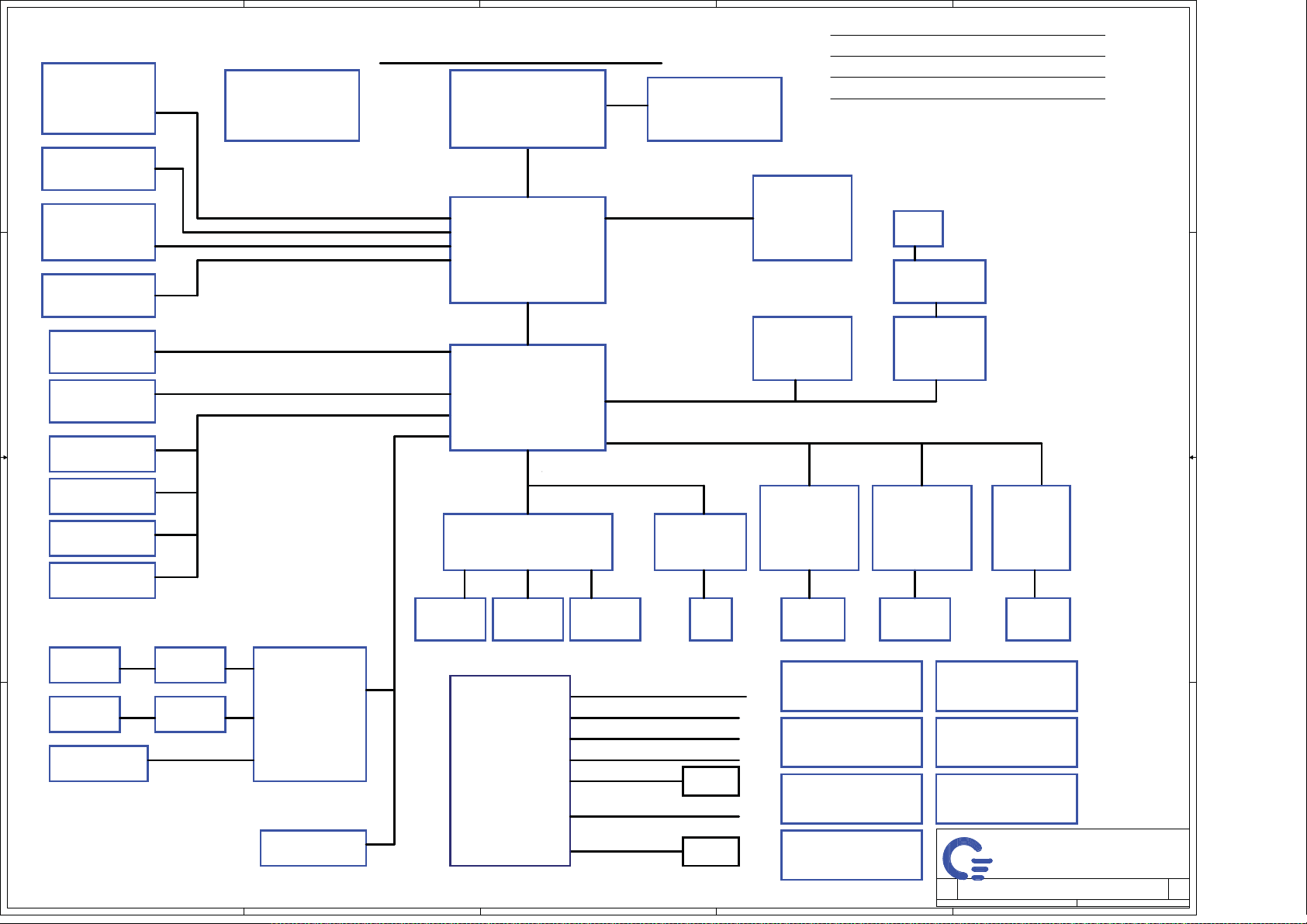

Acer TravelMate 6230, TravelMate 6231, TravelMate 6290, TravelMate 6291, TravelMate 6292 Schematics Rev1D

5

DVI / 7307

Chrontel

D D

(only for ezDock)

Page 17

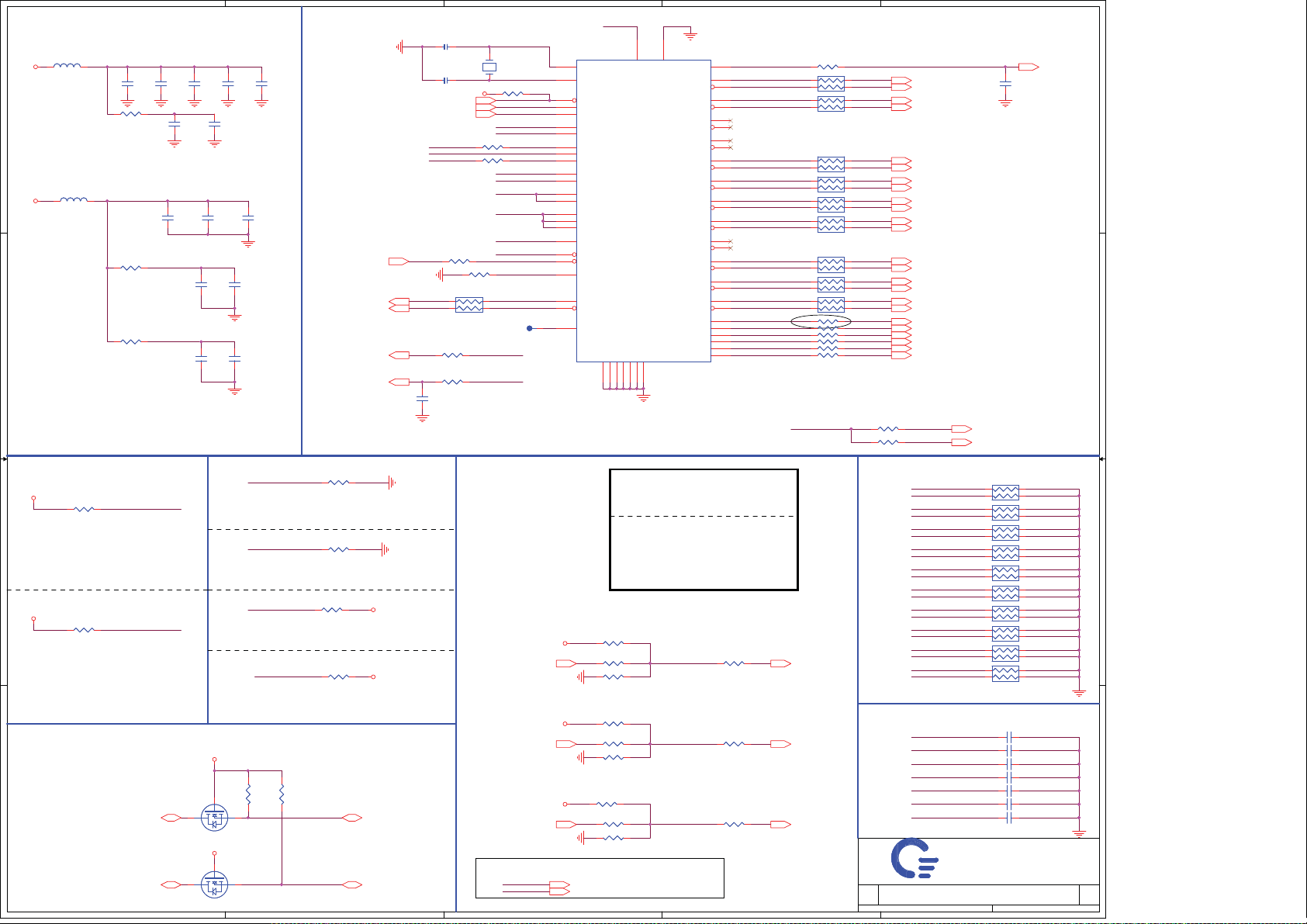

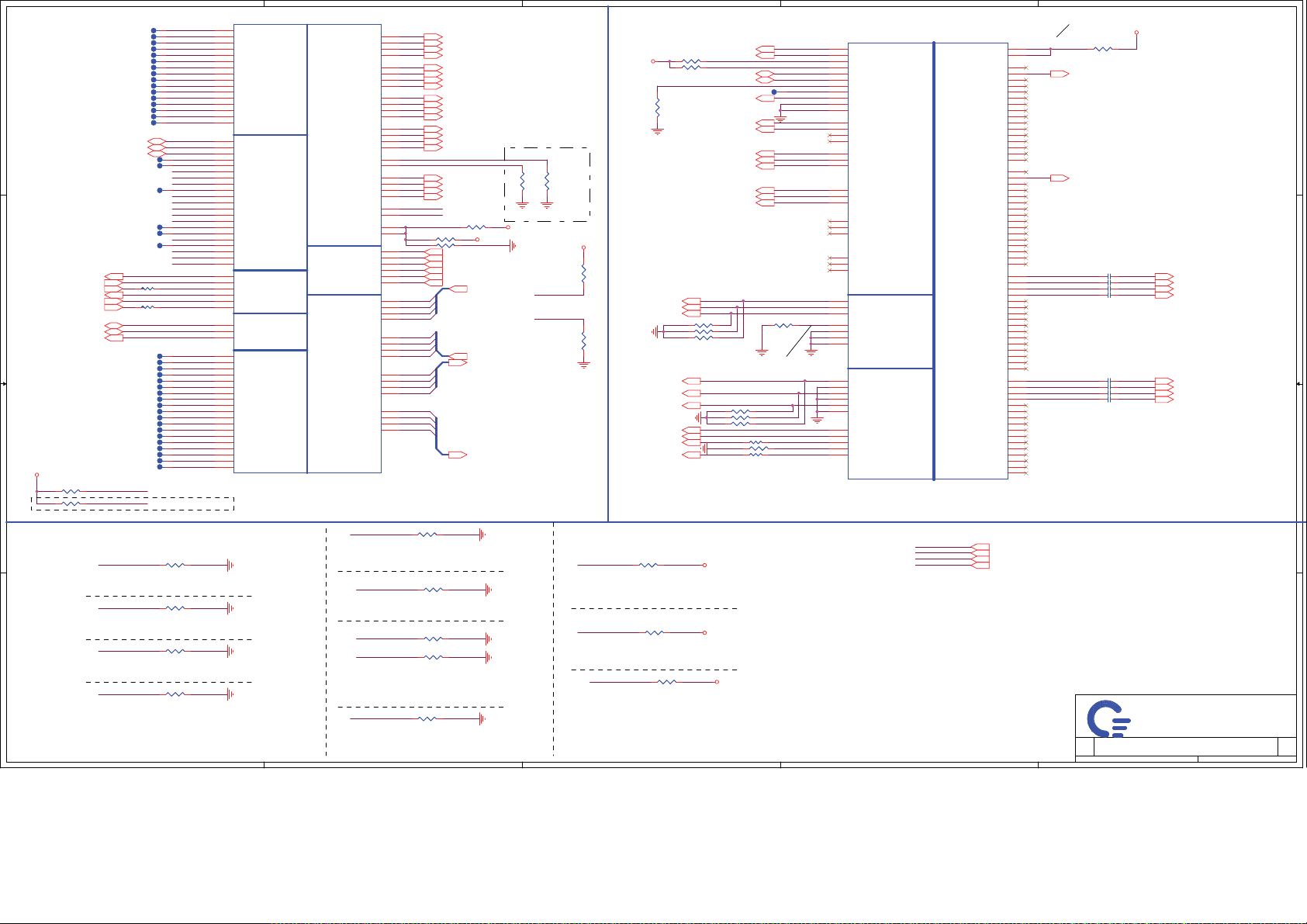

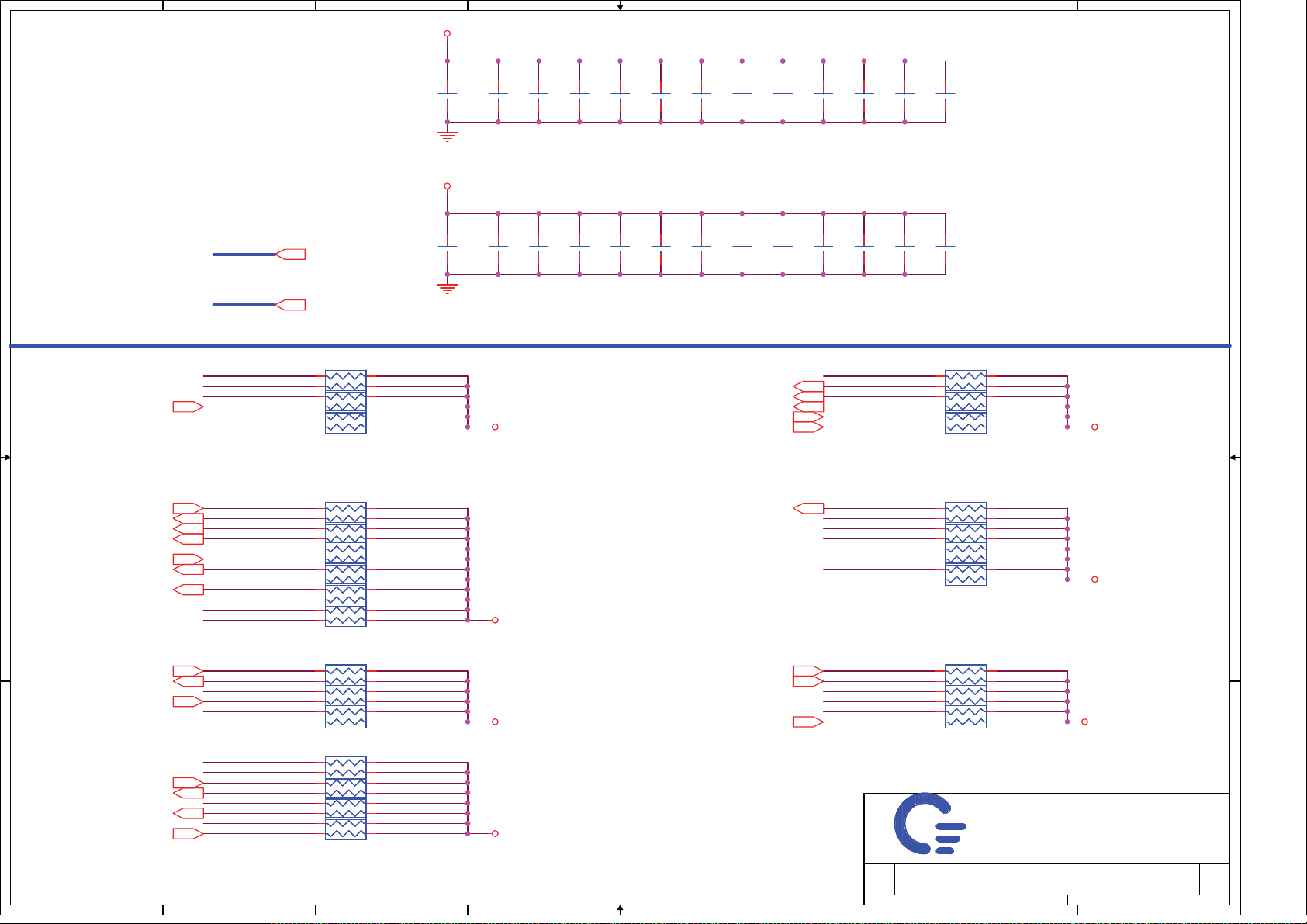

CLOCK GENERATOR

CK410-M

S-VIDEO CONN

Page 16

LCD CONN

(12.1"WXGA)

Page 16

CRT Port

Page 15

C C

HDD (SATA)

Page 22

ODD (PATA)

Page 22

USB Port x 3

USB1,4,5

Page 23

Page 2

SDVO

TV

LVDS

VGA

4

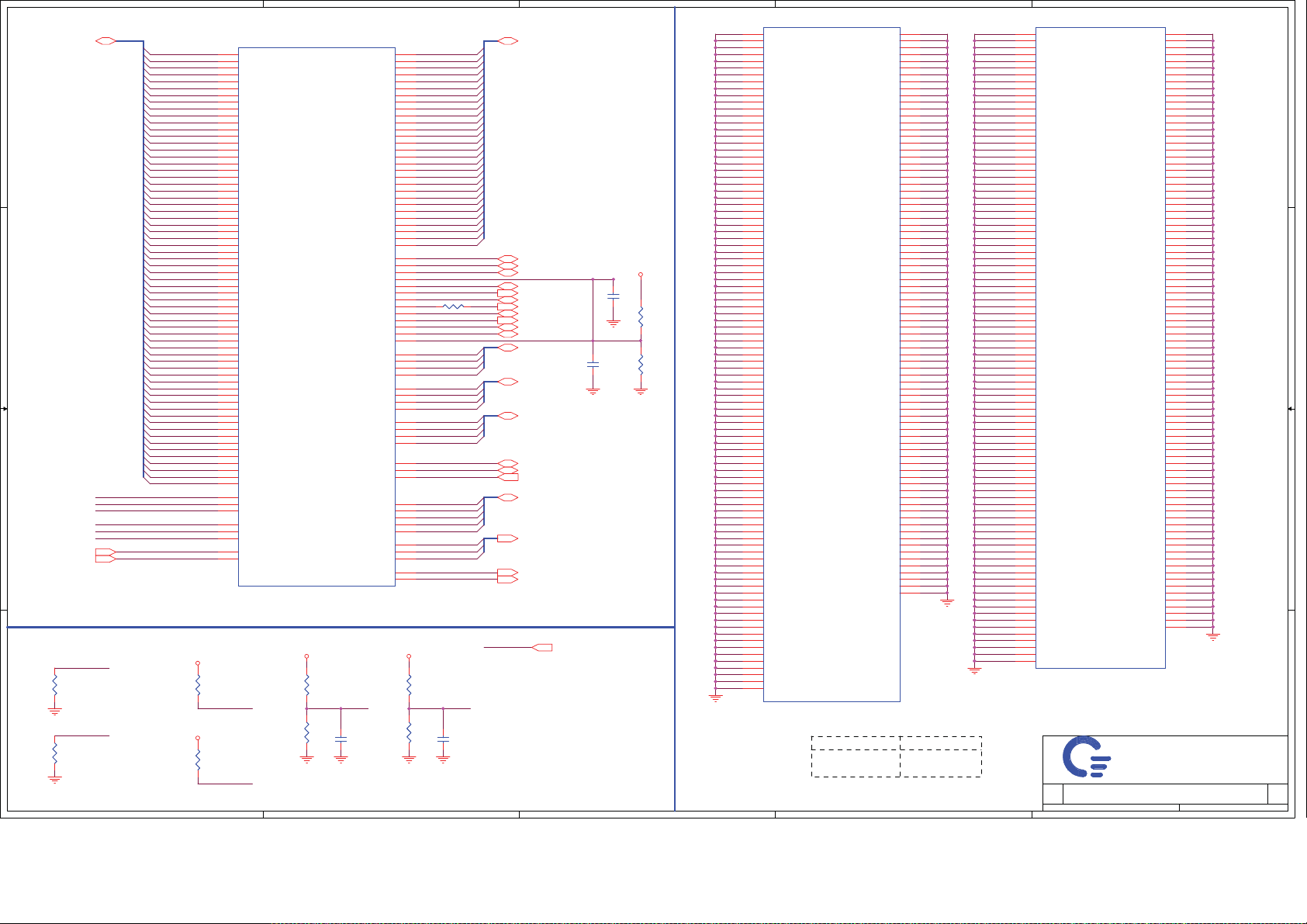

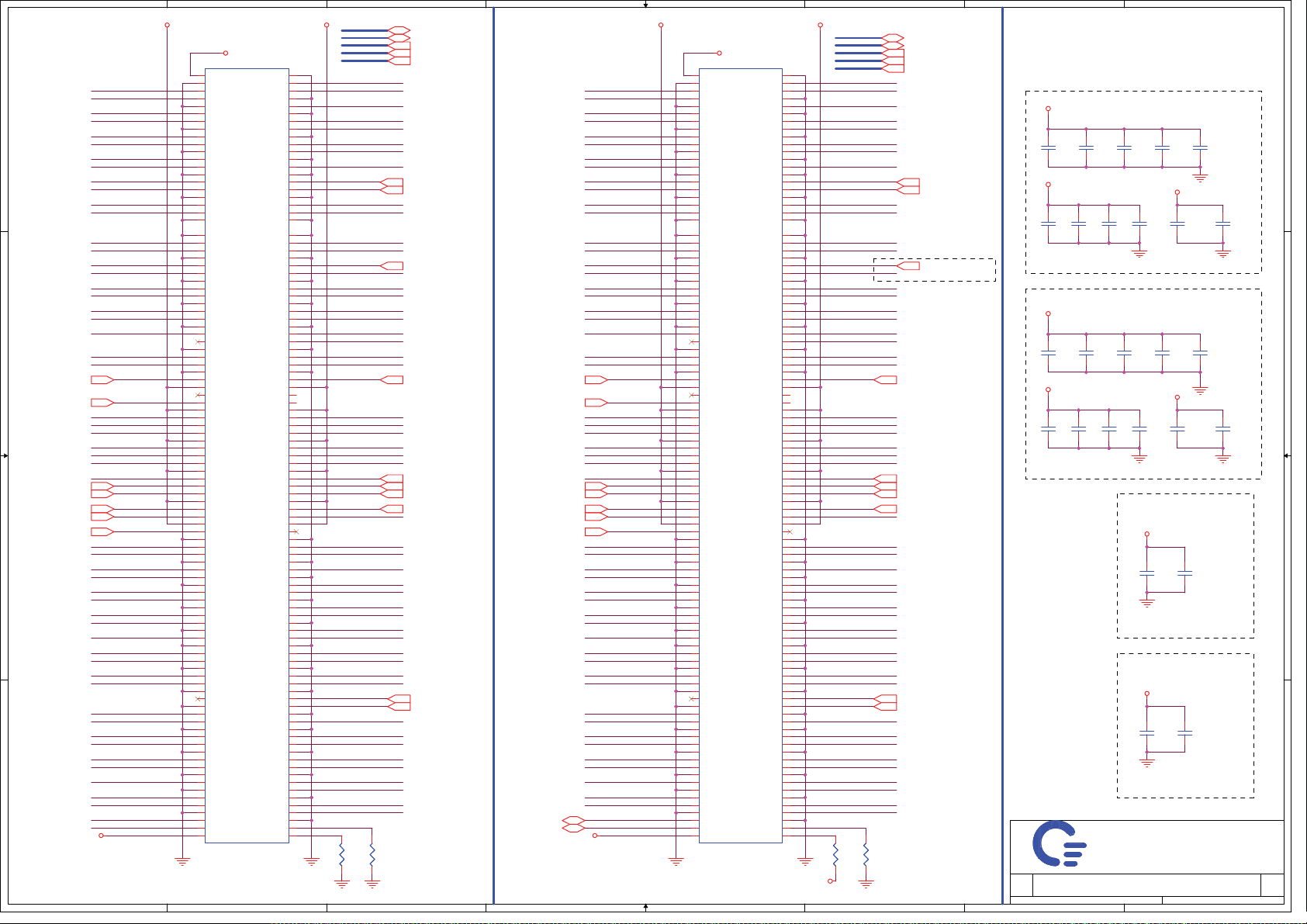

ZU2 SYSTEM BLOCK DIAGRAM

Yonah/Celeron-M

(479 FCPGA)

Page 3,4

HOST BUS

533/667MHz

+1.05V

+2.5V+1.5V

NB

1466FCBGA

Page 5~8

DMI interface

SB

ICH7-M

652BGA

Page 11~13

SATA

PATA

USB 2.0

Azalia

+1.8VSUS

CALISTOGA-GM/PM

+1.5V

+2.5V

+3V

+3VSUS

+1.5VSUS

+1.05V

3

CPU

Thermal Sensor

Dual Channel DDR2

533/667 MHz

PCI-Express

PCI Bus

Page 3

DDRII

SO-DIMM 0

SO-DIMM 1

Mini Card /

WLAN

Page 9,10

Page 23

PCIE-1

2

REQ# / GNT#PCI DEVICE InterruptsIDSEL#

REQ0# / GNT0# INTE#CB1410

AD17

AD25

REQ2# / GNT2# INTF#TIAB23

AD18

REQ1# / GNT1# INTG#MR510

RJ45

Page 14

1

CLOCK

CK410/PCI3

CK410/PCI8

CK410/PCI4

Transformer

Page 14

Giga Lan

(BCM 5787)

Page 14

PCIE-2

LPC

Bluetooth

USB2

Finger Printer

USB7

B B

CCD

USB3

Page 23

Page 29

Page 16

uR PC8763L

Page 24

SPI ROM

Page 24 Page 25 Page 25

Touch Pad

K/B CONN

Super I/O

NS PC87383

Page 26

FIR

Page 26

PCMCIA

Controller

(CB 1410)

Page 18

PCMCIA

Page 20

Card Reader

Controller

(MR510)

Page 19

Card Reader

Page 20

1394

Controller

(TI 43AB23)

Page 21

1394 CONN

Page 25

5

HP AMPHP

Page 27

SPK AMP

Page 28

Audio Codec

(ALC268)

Page 27

MDC 1.5

Page 27 Page 29

PCI-Express

ezDockII/II+

Connector

PCIE , Lan ,1394

Ser & Par Port

PS2 , VGA, DVI

SPDIF,SM BUS

MediaBay

Express Card

DVI

USB

1394*2

TV out / CRT

Audio

10/100/1G

4

3

PCIE-3

USB0

Switch

Page 15

Switch

Page 14

5V/3V (ISL6236)

Page 30

VCORE(ISL6262A)

Page 31

VTT 1.05V (SC411)

Page 32

1.8V (TPS51116)

Page 33

2

Page 28

INT SPK

Page 28

Line in & MIC

A A

Page 28

1.25V 1.5V 2.5V

Page 34

Discharge

Page 34

Charger (ISL6251)

Page 35

PROJECT : ZU2

PROJECT : ZU2

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Quanta Computer Inc.

Block Diagram

Block Diagram

Block Diagram

of

of

of

139Wednesday, March 21, 2007

139Wednesday, March 21, 2007

139Wednesday, March 21, 2007

1

1A

1A

1A

A

L54

L54

BK2125HS121-T_8

BK2125HS121-T_8

+3V

120 ohms@100Mhz

L:300mA

4 4

L55

L55

+3V

BK2125HS121-T_8

BK2125HS121-T_8

L:300mA

3 3

PCIE CLK e nable/disa ble contro l

+3V

R159 *10K_4R159 *10K_4

REQ3 Latched Select

"0" : CLK Enable

"1" : CLK Disable Control : PCIE 2,4

2 2

+3V

R155 10K_4R155 10K_4

REQ2 Latched Select

"0" : CLK Enable

"1" : CLK Disable Control : PCIE 3,5,7

25 mils

R374 2.2/F_6R374 2.2/F_6

25 mils

R162 2.2/F_6R162 2.2/F_6

R149 1_6R149 1_6

CLKGN_REQ3_PCIE

CLKGN_REQ4_PCIE

VDD_SRC_CPUVDD_SRC_CPU

C275

C275

.1U_4

.1U_4

VDD_PCI

C256

C256

.1U_4

.1U_4

VDD_A

.1U_4

.1U_4

C277

C277

.1U_4

.1U_4

VDD_48

VDD_REF

C259

C259

.1U_4

.1U_4

C279

C279

C278

C278

.1U_4

.1U_4

C255

C255

.1U_4

.1U_4

C519

C519

10U_8

10U_8

C276

C276

.1U_4

.1U_4

Starpping

C520

C520

C260

C260

10U_8

10U_8

.1U_4

.1U_4

C283

C283

10U_8

10U_8

C530

C530

10U_8

10U_8

C248

C248

10U_8

10U_8

R_PCLK_SIO

Latched Select. (Pin 17,18)

"0" : LCD CLK

"1" : PCIEX CLK

R_PCLK_591

ITP/SRC8 SELECT

0: SRC8

1: ITP

R_PCLK_ICH

SELLCD_27# Select. (Pin 17,18)

"0" : 27MHzSS/27MHzSS# pair

"1" : LCD CLK pair

R_PCLK_1394

PCIE CLK/REQ select

"0" : PCIE CLK

"1" : REQ pin

SM BUS level shift

+3V

R376

R376

R375

Q29

1 1

PDAT_SMB(13,29)

PCLK_SMB(13,29)

A

Q29

RHU002N06

RHU002N06

3

Q30

Q30

RHU002N06

RHU002N06

3

R375

2

+3V

2

10K_4

10K_4

10K_4

10K_4 R372 *1K_4R372 *1K_4

1

1

CGCLK_SMB/CGDAT_SMB(CLK GEN&DDR,+3V)PCLK_SMB/PDAT_SMB(SB&LAN&MINI CARD&EZ,+3V_S5)

R161 10K_4R161 10K_4

CGDAT_SMB

CGCLK_SMB

B

PCIE_CLKREQ#(29)

CLKUSB_48(13)

R380 10K_4R380 10K_4

R382 10K_4R382 10K_4

R154 *10K_4R154 *10K_4

B

DREFCLK(6)

DREFCLK#(6)

SIO_14M(26)

+3V

+3V

CGDAT_SMB (9,23)

CGCLK_SMB (9,23)

C262 27P/50V_4C262 27P/50V_4

C274 27P/50V_4C274 27P/50V_4

VR_PWRGD_CK410#(13,31)

PM_STPCPU#(13)

PM_STPPCI#(13)

CLK_BSEL0

CLK_BSEL1

R156 475_4R156 475_4

R150 475/F_6R150 475/F_6

RP35 33_4P2RRP35 33_4P2R

1

3

R165 33_4R165 33_4

R153 33_4R153 33_4

C251

C251

*10P_4

*10P_4

C

U15

U15

58

X1

57

X2

10

Vtt_PwrGd#/PD

62

CPU_STOP#

63

PCI/PCIE_STOP#

54

SCLK

55

SDATA

12

FSA/USB_48MHz

16

FSB/TEST_MODE

61

REF1/FSLC/TEST_SEL

56

VDD_REF

50

VDDCPU

1

VDD_PCI_1

7

VDD_PCI_2

21

VDD_PCIE

28

VDDPCIE

42

VDD_PCIE

11

VDD_48

32

REQ3(PCIE)

33

REQ4(PCIE)

47

IREF

14

DOT96MHz

15

DOT96MHz#

34

PWRSAVE#

VDD_A

45

VDDA

CK-410M

CK-410M

27Mfix/LCD_SSCGT/PCIE0T

27SS/LCD_SSCGC/PCIE0C

GND

GND_PCI_26GND_SRC

GND_PCI_1

GND_48

GND

2

59

29

13

53

46

GNDA

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2/PCIET8

CPUCLKC2/PCIEC8

REQ1#/PCIET7

REQ2#/PCIEC7

SATA_CKT

SATA_CKC

selPCIEX0_LCD#/PCI5

PCICLK2/REQ_SEL

PCIF1/selLCD_27#

PCIF0/ITP_EN

GND

ICS954310BGLF

ICS954310BGLF

37

pin5,pin9,pin32,pin33,pin34 internal PU

pin64 internal PD

Place these termination to close CK410M.

14M_REF

60

REF0

52

R_HCLK_CPU#

51

R_HCLK_MCH

49

R_HCLK_MCH#

48

44

43

41

40

R_CLK_PCIE_3GPLL

39

PCIET6

R_CLK_PCIE_3GPLL#

38

PCIEC6

R_CLK_PCIE_DOCK

36

PCIET5

R_CLK_PCIE_DOCK#

35

PCIEC5

R_CLK_PCIE_ICH

30

PCIET4

R_CLK_PCIE_ICH#

31

PCIEC4

R_CLK_PCIE_SATA

26

R_CLK_PCIE_SATA#

27

24

PCIET3

25

PCIEC3

R_CLK_PCIE_MINI1

22

PCIET2

R_CLK_PCIE_MINI1#

23

PCIEC2

R_CLK_PCIE_LAN

19

PCIET1

R_CLK_PCIE_LAN#

20

PCIEC1

R_DREFSSCLK

17

R_DREFSSCLK#

18

R_PCLK_SIO

5

R_PCI_CLK_510

4

PCI4

R_PCLK_PCM

3

PCI3

R_PCLK_1394

64

R_PCLK_ICH

9

R_PCLK_591

8

Close to IC <500mils

+3V

R164 4.7K_4R164 4.7K_4

CG_XIN

21

Y2

Y2

14.318MHZ

14.318MHZ

CG_XOUT R_HCLK_CPU

R381 *10K_4R381 *10K_4

CGCLK_SMB

CGDAT_SMB

R_48M

R_14M_SIOCLK_BSEL2

VDD_REF

VDD_SRC_CPU

VDD_PCI

VDD_SRC_CPU

VDD_48

CLKGN_REQ3_PCIE

CLKGN_REQ4_PCIE

IREF

Iref=5mA, Ioh=4*Iref

R_DOT96

2

R_DOT96#

4

T58T58

INTERNAL PULL HIGH

R_48M

R_14M_SIO

SEL0SEL1SEL2

Frequence select

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

0 1 1 166 100 33

0 1 0 200 100 33

0 0 0 266 100 33

1 0 0 333 100 33

1 1 0 400 100 33

1 1 1 200 100 33

BSEL strappings need to be set for 533MHz Moby Dick

(Intel?915GM - Calistoga Interposer)

(if Calistoga is designed for 667MHz board).

R390 *1K_4R390 *1K_4

+1.05V

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

R396 1K_4R396 1K_4

R392 1K_4R392 1K_4

R370 1K_4R370 1K_4

+1.05V

+1.05V

R389 0_4R389 0_4

R391 *1K_4R391 *1K_4

R394 *1K_4R394 *1K_4

R393 0_4R393 0_4

R395 *0_4R395 *0_4

R369 0_4R369 0_4

R371 *0_4R371 *0_4

CPU_BSEL0(3)

CPU_BSEL1(3)

CPU_BSEL2(3) MCH_BSEL2 (6)

Power check

+3V (3,6,8,9,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,29,30,31,32,34)

+1.05V (3,4,5,8,11,13,31,32,34)

C

D

R373 33_4R373 33_4

RP31 33_4P2RRP31 33_4P2R

RP32 33_4P2RRP32 33_4P2R

RP33 33_4P2RRP33 33_4P2RR152 4.7K_4R152 4.7K_4

RP34 33_4P2RRP34 33_4P2R

RP40 33_4P2RRP40 33_4P2R

RP39 33_4P2RRP39 33_4P2R

RP38 33_4P2RRP38 33_4P2R

RP37 33_4P2RRP37 33_4P2R

RP36 33_4P2RRP36 33_4P2R

R_PCLK_SIO

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

R385 33_4R385 33_4

R160 33_4R160 33_4

R379 33_4R379 33_4

R151 33_4R151 33_4

R163 33_4R163 33_4

R386 33_4R386 33_4

"EA report, fail in PCI_CLK_SIO. It is too fast.

BOM change. R385 change to 33 ohm and unstuff R384."

R384 *10_4R384 *10_4

R383 10_4R383 10_4

CLK_CPU_BCLK (3)

CLK_CPU_BCLK# (3)

CLK_MCH_BCLK (5)

CLK_MCH_BCLK# (5)

CLK_PCIE_3GPLL (6)

CLK_PCIE_3GPLL# (6)

CLK_PCIE_DOCK (29)

CLK_PCIE_DOCK# (29)

CLK_PCIE_ICH (12)

CLK_PCIE_ICH# (12)

CLK_PCIE_SATA (11)

CLK_PCIE_SATA# ( 11)

CLK_PCIE_MINI1 (23)

CLK_PCIE_MINI1# (23)

CLK_PCIE_LAN (14)

CLK_PCIE_LAN# (14)

DREFSSCLK (6)

DREFSSCLK# (6)

PCI_CLK_SIO (26)

PCI_CLK_510 (19)

PCI_CLK_CB714 (18)

PCLK_1394 (21)

PCLK_ICH (12)

PCLK_591 (24)

Terminal Re sistor

CLK_CPU_BCLK#

CLK_CPU_BCLK

CLK_MCH_BCLK#

Default

MCH_BSEL0 (6)

CLK_MCH_BCLK

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_LAN

CLK_PCIE_LAN#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

CLK_PCIE_ICH

CLK_PCIE_ICH#

DREFSSCLK#

DREFSSCLK

DREFCLK#

DREFCLK

CLK_PCIE_DOCK

CLK_PCIE_DOCK#

Reserve for EMI

PCI_CLK_SIO

PCI_CLK_510

PCI_CLK_CB714

PCLK_DEBUG_SW

PCLK_ICH

PCLK_591

PCLK_1394

D

MCH_BSEL1 (6)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Gen.

Clock Gen.

Clock Gen.

Date: Sheet

Date: Sheet

Date: Sheet of

E

14M_ICH (13)

C518

C518

*10P_4

*10P_4

PCLK_DEBUG_SW (24)

PCLK_DEBUG_HW (23)

RP29 49.9_4P2RRP29 49.9_4P2R

RP30 49.9_4P2RRP30 49.9_4P2R

RP41 49.9_4P2RRP41 49.9_4P2R

RP49 49.9_4P2RRP49 49.9_4P2R

RP47 49.9_4P2RRP47 49.9_4P2R

RP50 49.9_4P2RRP50 49.9_4P2R

RP42 49.9_4P2RRP42 49.9_4P2R

RP51 49.9_4P2RRP51 49.9_4P2R

RP52 49.9_4P2RRP52 49.9_4P2R

RP48 49.9_4P2RRP48 49.9_4P2R

PROJECT : ZU2

PROJECT : ZU2

Quanta Computer Inc.

Quanta Computer Inc.

3

1

3

1

3

1

3

1

1

3

3

1

3

1

3

1

3

1

1

3

C533 *10P_4C533 *10P_4

C284 *10P_4C284 *10P_4

C526 *10P_4C526 *10P_4

C534 *10P_4C534 *10P_4

C285 *10P_4C285 *10P_4

C286 *10P_4C286 *10P_4

C250 *10P_4C250 *10P_4

E

4

2

4

2

4

2

4

2

2

4

4

2

4

2

4

2

4

2

2

4

239Thursday, March 22, 2007

239Thursday, March 22, 2007

239Thursday, March 22, 2007

of

of

1B

1B

1B

5

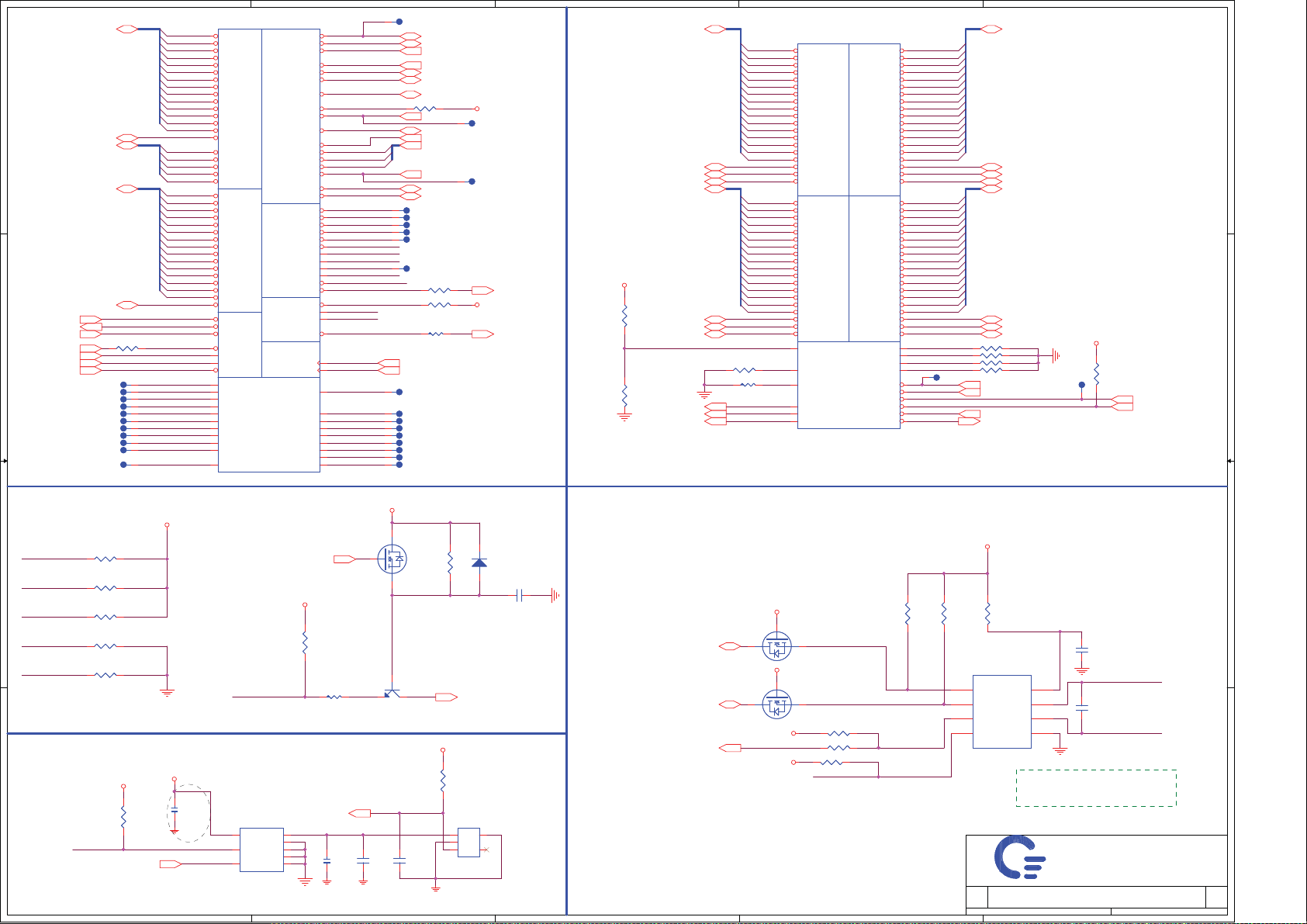

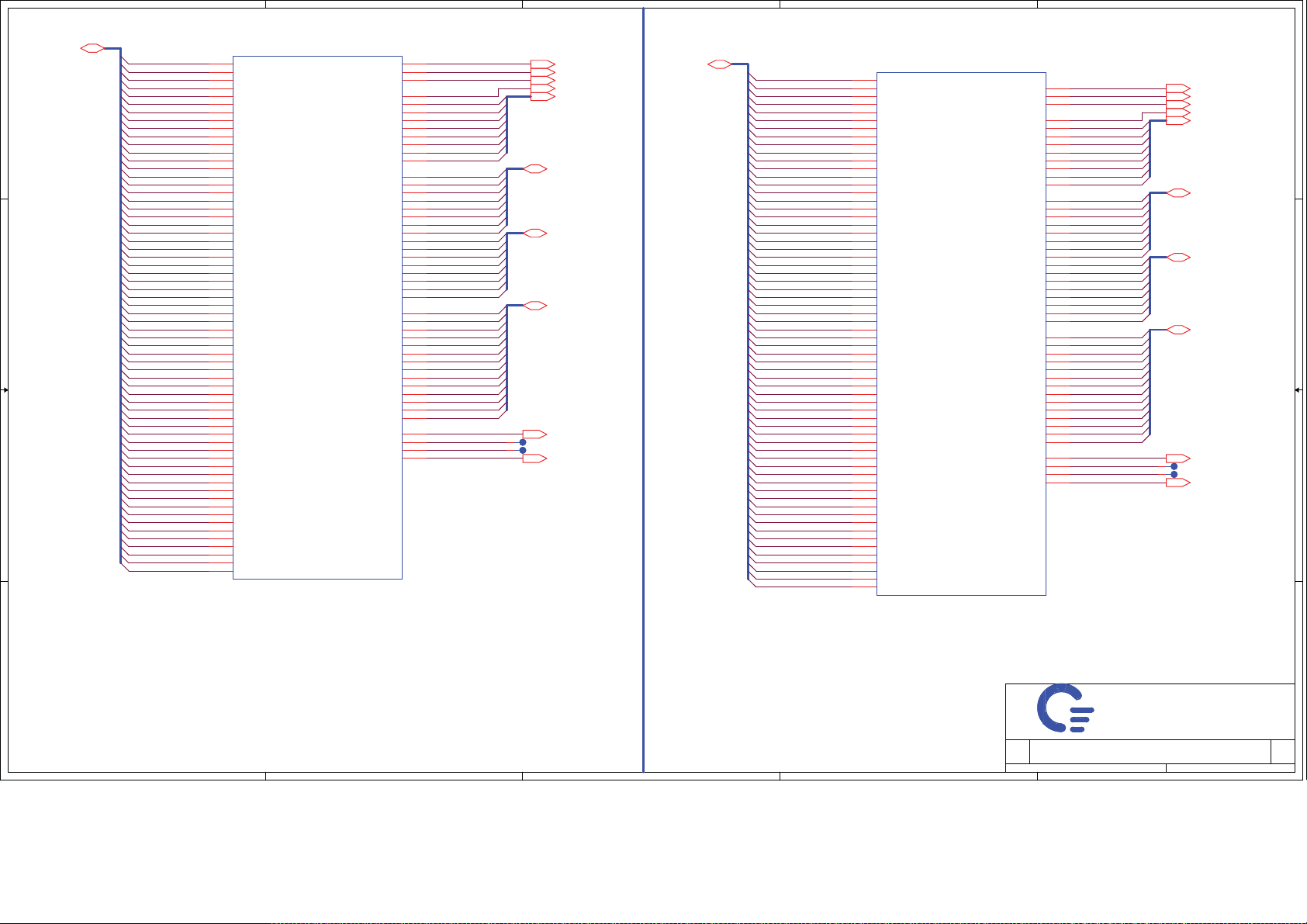

U28A

H_A#[31:3](5)

D D

C C

H_ADSTB0#(5)

H_REQ#[4:0](5)

H_A#[31:3](5)

H_ADSTB1#(5)

H_A20M#(11)

H_FERR#(11)

H_IGNNE#(11)

H_STPCLK#(11)

H_INTR(11)

H_SMI#(11)

R143 0_4R143 0_4

H_NMI(11)

T35T35

T44T44

T40T40

T42T42

T30T30

T29T29

T41T41

T34T34

T32T32

T85T85

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_STPCLK_R#

TP_A32#

TP_A33#

TP_A34#

TP_A35#

TP_A36#

TP_A37#

TP_A38#

TP_A39#

TP_APM0#

TP_APM1#

TP_HFPLL

U28A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L1

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

L2

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L5

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U2

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W3

A[27]#

W5

A[28]#

Y4

A[29]#

W2

A[30]#

Y1

A[31]#

V4

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

AA1

RSVD[01]#

AA4

RSVD[02]#

AB2

RSVD[03]#

AA3

RSVD[04]#

M4

RSVD[05]#

N5

RSVD[06]#

T2

RSVD[07]#

V3

RSVD[08]#

B2

RSVD[09]#

C3

RSVD[10]#

B25

RSVD[11]#

PZ47903-2741-01

PZ47903-2741-01

ADDR GROUP 0

ADDR GROUP 0

DEFER#

DRDY#

DBSY#

CONTROL

CONTROL

LOCK#

RESET#

TRDY#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT

THERMDA

THERMDC

THERMTRIP#

THERMH CLK

THERMH CLK

BCLK[0]

BCLK[1]

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RESERVED

RESERVED

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

ADS#

BNR#

BPRI#

BR0#

IERR#

INIT#

RS[0]#

RS[1]#

RS[2]#

HIT#

HITM#

TCK

TDO

TMS

DBR#

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

TDI

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

4

H_IERR#

H_RS#0

H_RS#1

H_RS#2

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT_R#

THERMDA

THERMDC

THERMTRIP#_PWR

TP_EXTBREF

TP_SPARE0

TP_SPARE1

TP_SPARE2

TP_SPARE3

TP_SPARE4

TP_SPARE5

TP_SPARE6

TP_SPARE7

T36T36

H_ADS# (5)

H_BNR# (5)

H_BPRI# (5)

H_DEFER# (5)

H_DRDY# (5)

H_DBSY# ( 5)

H_BREQ#0 (5)

R347 56.2/F_4R347 56.2/F_4

H_INIT# (11)

H_LOCK# (5)

H_CPURST# (5)

H_RS#[2:0] ( 5)

H_TRDY# (5)

H_HIT# (5)

H_HITM# ( 5)

T50T50

T54T54

T51T51

T48T48

T46T46

T43T43

R349 0_4R349 0_4

R345 68_4R345 68_4

R126 *0_4R126 *0_4

CLK_CPU_BCLK (2)

CLK_CPU_BCLK# (2)

T10T10

T38T38

T31T31

T47T47T39T39

T45T45

T53T53

T3T3

T88T88

T84T84

+1.05V

T55T55

T37T37

SYS_RST# (13)

+1.05V

PM_THRMTRIP# (6,11)

R330

R330

1K/F_4

1K/F_4

R326

R326

2K/F_6

2K/F_6

3

+1.05V

H_D#[63:0](5)

H_DSTBN#0(5)

H_DSTBP#0(5)

H_DINV#0(5)

H_D#[63:0](5)

H_DSTBN#1(5)

H_DSTBP#1(5)

H_DINV#1(5)

H_GTLREF

CPU_BSEL0(2)

CPU_BSEL1(2)

CPU_BSEL2(2)

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

*1K/F_4

*1K/F_4

R328

R328

R329 51_4R329 51_4

H22

G25

G24

H26

H25

H23

G22

N22

R23

M23

R24

N24

M24

N25

M26

AD26

C26

D25

C21

E22

F24

E26

F23

E25

E23

K24

J24

J23

F26

K22

J26

K25

P26

L25

L22

L23

P25

P22

P23

T24

L26

T25

B22

B23

U28B

U28B

D[0]#

D[1]#

D[2]#

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

MISC

MISC

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

PZ47903-2741-01

PZ47903-2741-01

2

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

DATA GRP 3

DATA GRP 3

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

T49T49

27.4/F_6

27.4/F_6

H_D#[63:0] (5)

H_DSTBN#2 (5)

H_DSTBP#2 (5)

H_DINV#2 (5)

H_D#[63:0] (5)

H_DSTBN#3 (5)

H_DSTBP#3 (5)

H_DINV#3 (5)

R327

R327

COMP[0,2]=18mils

R33154.9/F_4 R33154.9/F_4

R14227.4/F_6 R14227.4/F_6

R13654.9/F_4 R13654.9/F_4

ICH_DPRSTP# (11,31)

H_DPSLP# (11)

H_CPUSLP# (5,11)

PSI# (31)

1

+1.05V

R144

R144

*200/F_6

*200/F_6

T4T4

H_DPWR# (5)

H_PWRGD is CMOS driving by ICH

H_PWRGD (11)

C444

C444

2.2U_8

2.2U_8

+1.05V

3

2

1

2

1 3

Q17 MMBT3904Q17 MMBT3904

C440

C440

C445

C445

.01U_4

.01U_4

*.01U_4

*.01U_4

4

Q16

Q16

FDV301N

FDV301N

R357

R357

*10K_4

*10K_4

+3V

R324

R324

10K_4

10K_4

CN26

CN26

1

2

345

PTI_CWY030-B0G 1Z

PTI_CWY030-B0G 1Z

D35

D35

*BAS316

*BAS316

C175 *1U_6C175 *1U_6

SYS_SHDN# (30)

&387KHUPDOPRQLWRU

2ND_MBCLK(24)

2ND_MBDATA(24)

THERM_ALERT#(13)

3

+3V

+3V

Q28

Q28

2

RHU002N06

RHU002N06

3

3

+3V

Q27

Q27

2

RHU002N06

RHU002N06

+3V

+5V

R321 10K_4R321 10K_4

1

1

R322 *10K_4R322 *10K_4

R323 *0_4R323 *0_4

CPUFAN#_ON

2

R333

R333

10K_4

10K_4

THERM_ALERT#_R

THERM_ALERT#_R

R325

R325

R332

R332

200_6

200_6

10K_4

10K_4

U26

U26

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

MAX6657

MAX6657

$''5(66+

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

LM86VCC

1

VCC

2

DXP

3

DXN

5

GND

<check list>

Layout Note:Routing 10:10 m ils and away

from noise source with ground gard

YOHNA (HOST)

YOHNA (HOST)

YOHNA (HOST)

C451

C451

.1U_4

.1U_4

C448

C448

2200P_4

2200P_4

PROJECT : ZU2

PROJECT : ZU2

Quanta Computer Inc.

Quanta Computer Inc.

1

THERMDA

THERMDC

339Thursday, March 22, 2007

339Thursday, March 22, 2007

339Thursday, March 22, 2007

of

of

of

1A

1A

1A

XDP/ITP Thermal protect

XDP_TMS

B B

XDP_TDI

XDP_BPM#5

XDP_TCK

XDP_TRST#

&38)$1

A A

FANPWR = 1.6*VSET

G995/Pin1- intern al pull high (+5V)

R139 54.9/F_4R139 54.9/F_4

R141 54.9/F_4R141 54.9/F_4

R140 54.9/F_4R140 54.9/F_4

R368 54.9/F_4R368 54.9/F_4

R367 54.9/F_4R367 54.9/F_4

ZU2 change C437 from 10U_8 to 2.2U_6(1/26)

Add one 2.2uF in U46 G955's VIN.GMT request to add it.

CPUFAN#_ON

+1.05V

DELAY_VR_PWRGOOD(6,13,31)

+1.05V

R129

R129

56_4

56_4

R127

3

5

6

7

8

R127

330_4

330_4

FANSIG(24)

TH_FAN_POWER

TH_FAN_POWER

THERMTRIP#_PWR

CPUFAN#(24)

5

R317

R317

*10K_4

*10K_4

+5V

C437

C437

2.2U_8

2.2U_8

U25

U25

1

4

G995

G995

VIN2VO

GND

/FON

GND

GND

VSET

GND

+5V

5

U28D

U28D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

D D

C C

B B

A A

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

P3

VSS[081]

PZ47903-2741-01

PZ47903-2741-01

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

5

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

A7

A9

B7

B9

C9

D9

E7

E9

F7

F9

U28C

U28C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[100]

VCC[034]

VCC[035]

VCCP[01]

VCC[036]

VCCP[02]

VCC[037]

VCCP[03]

VCC[038]

VCCP[04]

VCC[039]

VCCP[05]

VCC[040]

VCCP[06]

VCC[041]

VCCP[07]

VCC[042]

VCCP[08]

VCC[043]

VCCP[09]

VCC[044]

VCCP[10]

VCC[045]

VCCP[11]

VCC[046]

VCCP[12]

VCC[047]

VCCP[13]

VCC[048]

VCCP[14]

VCC[049]

VCCP[15]

VCC[050]

VCCP[16]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCCSENSE

VCC[066]

VCC[067]

VSSSENSE

PZ47903-2741-01

PZ47903-2741-01

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

4

VCC_COREVCC_CORE

36A (T2700)

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

VCCA

AD6

VID[0]

AF5

VID[1]

AE5

VID[2]

AF4

VID[3]

AE3

VID[4]

AF2

VID[5]

AE2

VID[6]

AF7

AE7

Add 100_F PU on VCCSENSE.

Add 100_F PD on VSSSENSE.

Check intel circuit by Alan(1/26)

+1.05V

3A

+

+

C452

C452

330U_7343

330U_7343

+1.5V

4

120mA

H_VID0 (31)

H_VID1 (31)

H_VID2 (31)

H_VID3 (31)

H_VID4 (31)

H_VID5 (31)

H_VID6 (31)

+1.05V

VCC_CORE

+1.5V

VCC_CORE

12

C173

C173

+

+

*330u_2V_7343

*330u_2V_7343

+1.05V

C460

C460

.1U_4

.1U_4

+1.5V

C455

C455

.01U_4

.01U_4

3

12

C174

C174

+

+

330U_7343

330U_7343

C219

C219

.1U_4

.1U_4

C453

C453

10U/X5R_8

10U/X5R_8

VCC_CORE

+1.05V (2,3,5,8,11,13,31,32,34)

VCC_CORE (31)

+1.5V (8,12,13,23,27,34)

C218

C218

.1U_4

.1U_4

R365

R365

100/F_4

100/F_4

R366

R366

100/F_4

100/F_4

C503

C503

.1U_4

.1U_4

3

C461

C461

.1U_4

.1U_4

VCCSENSE (31)

VSSSENSE (31 )

C459

C459

.1U_4

.1U_4

2

VCC_CORE CAP.

VCC_CORE

C188

C188

*10U_8

*10U_8

VCC_CORE

2

1

C471

C471

*10U_8

*10U_8

C210

C210

*10U_8

*10U_8

C499

C499

*10U_8

*10U_8

reserve cap

C487

C487

C485

C485

10U_8

10U_8

10U_8

10U_8

C209

C209

C207

C207

10U_8

10U_8

10U_8

10U_8

C484

C484

C486

C486

10U_8

10U_8

10U_8

10U_8

C159

C159

C158

C158

10U_8

10U_8

10U_8

10U_8

C199

C199

C201

C201

10U_8

10U_8

10U_8

10U_8

C474

C474

C473

C473

10U_8

10U_8

10U_8

10U_8

C492

C492

C481

C481

10U_8

10U_8

10U_8

10U_8

C493

C493

C482

C482

10U_8

10U_8

10U_8

10U_8

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Yonah/Merom CPU(POWER/GND)-2

Yonah/Merom CPU(POWER/GND)-2

Yonah/Merom CPU(POWER/GND)-2

Date: Sheet

Date: Sheet

Date: Sheet

C160

C160

C472

C472

10U_8

10U_8

10U_8

10U_8

C498

C498

C497

C497

10U_8

10U_8

10U_8

10U_8

C208

C208

C206

C206

10U_8

10U_8

10U_8

10U_8

C200

C200

C500

C500

10U_8

10U_8

10U_8

10U_8

C187

C187

C189

C189

10U_8

10U_8

10U_8

10U_8

C494

C494

C186

C186

10U_8

10U_8

10U_8

10U_8

C467

C467

C465

C465

10U_8

10U_8

10U_8

10U_8

C466

C466

C480

C480

10U_8

10U_8

10U_8

10U_8

PROJECT : ZU2

PROJECT : ZU2

Quanta Computer Inc.

Quanta Computer Inc.

1

of

of

of

439Thursday, March 22, 2007

439Thursday, March 22, 2007

439Thursday, March 22, 2007

1A

1A

1A

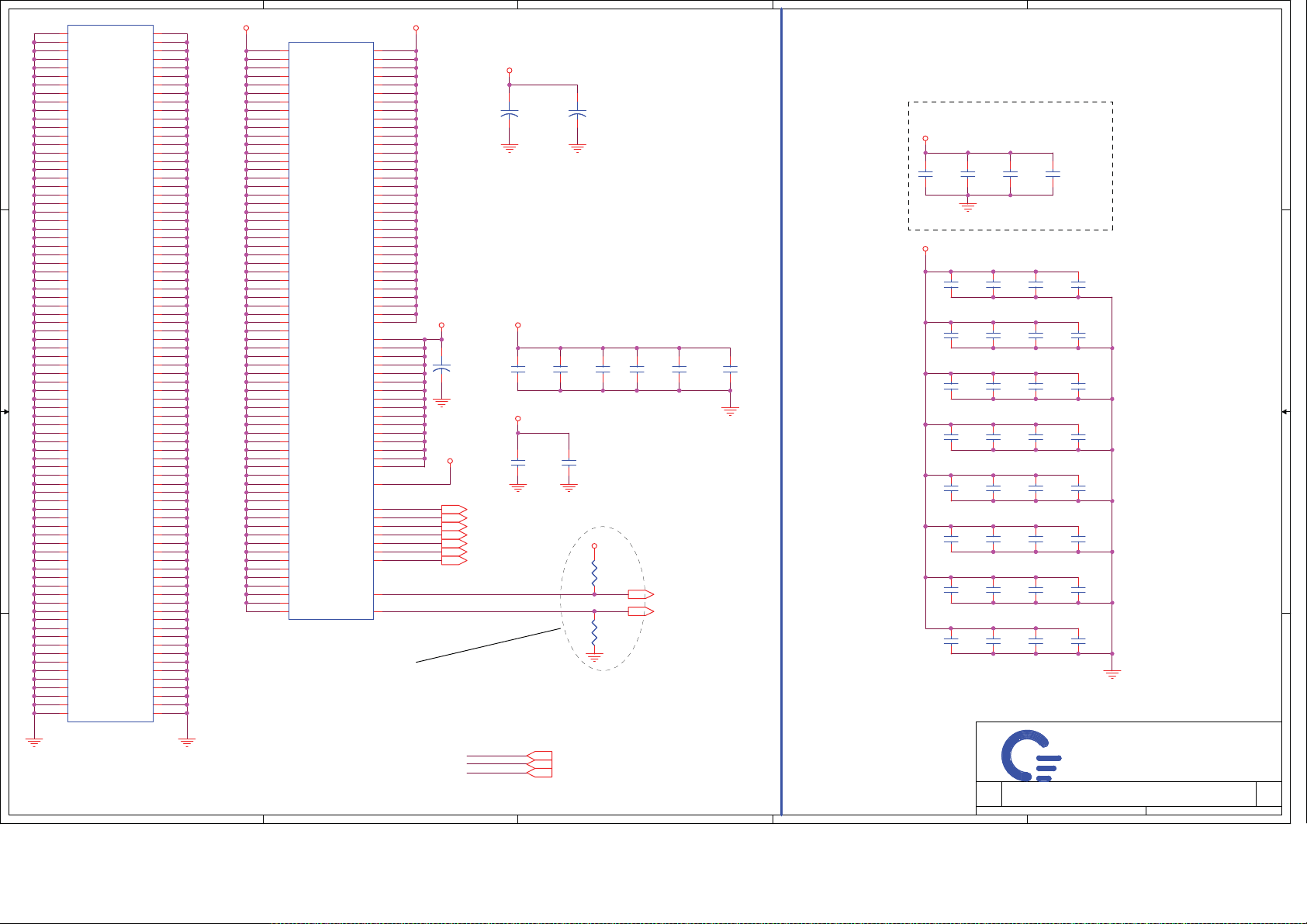

5

H_D#[63:0](3)

D D

C C

H_XRCOMP

H_XSCOMP

B B

CLK_MCH_BCLK(2)

CLK_MCH_BCLK#(2)

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

Short Stub < 100mils

extract from same point

Slew/IO Buffer COMP.

H_XRCOMP

15 mils/10mils

R91

R91

24.9/F_4

24.9/F_4

A A

H_YRCOMP

15 mils/10mils

R88

R88

24.9/F_4

24.9/F_4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

+1.05V

+1.05V

5

U27A

U27A

F1

H_D#_0

J1

H_D#_1

H1

H_D#_2

J6

H_D#_3

H3

H_D#_4

K2

H_D#_5

G1

H_D#_6

G2

H_D#_7

K9

H_D#_8

K1

H_D#_9

K7

H_D#_10

J8

H_D#_11

H4

H_D#_12

J3

H_D#_13

K11

H_D#_14

G4

H_D#_15

T10

H_D#_16

W11

H_D#_17

T3

H_D#_18

U7

H_D#_19

U9

H_D#_20

U11

H_D#_21

T11

H_D#_22

W9

H_D#_23

T1

H_D#_24

T8

H_D#_25

T4

H_D#_26

W7

H_D#_27

U5

H_D#_28

T9

H_D#_29

W6

H_D#_30

T5

H_D#_31

AB7

H_D#_32

AA9

H_D#_33

W4

H_D#_34

W3

H_D#_35

Y3

H_D#_36

Y7

H_D#_37

W5

H_D#_38

Y10

H_D#_39

AB8

H_D#_40

W2

H_D#_41

AA4

H_D#_42

AA7

H_D#_43

AA2

H_D#_44

AA6

H_D#_45

AA10

H_D#_46

Y8

H_D#_47

AA1

H_D#_48

AB4

H_D#_49

AC9

H_D#_50

AB11

H_D#_51

AC11

H_D#_52

AB3

H_D#_53

AC2

H_D#_54

AD1

H_D#_55

AD9

H_D#_56

AC1

H_D#_57

AD7

H_D#_58

AC6

H_D#_59

AB5

H_D#_60

AD10

H_D#_61

AD4

H_D#_62

AC8

H_D#_63

E1

H_XRCOMP

E2

H_XSCOMP

E4

H_XSWING

Y1

H_YRCOMP

U1

H_YSCOMP

W1

H_YSWING

AG2

H_CLKIN

AG1

H_CLKIN#

Calistoga

Calistoga

R92

R92

54.9/F_4

54.9/F_4

H_XSCOMP H_YSWING

R89

R89

54.9/F_4

54.9/F_4

H_YSCOMP

HOST

HOST

R87

R87

221/F_4

221/F_4

H_XSWING

R86

R86

100/F_4

100/F_4

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

C130

C130

.1U_4

.1U_4

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_HIT#

4

4

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

+1.05V+1.05V

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

R334 0_4R334 0_4

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

R84

R84

221/F_4

221/F_4

R80

R80

100/F_4

100/F_4

C121

C121

.1U_4

.1U_4

+1.05V

H_A#[31:3] (3)

H_VREF :10 mils/20 mils space

H_ADS# (3)

H_ADSTB0# (3)

H_ADSTB1# (3)

H_BNR# (3)

H_BPRI# (3)

H_BREQ#0 (3 )

H_CPURST# (3)

H_DBSY# (3)

H_DEFER# (3)

H_DPWR# (3)

H_DRDY# (3)

H_DINV#[3:0] (3)

H_DSTBN#[3:0] (3)

H_DSTBP#[3:0] (3)

H_HIT# (3)

H_HITM# (3)

H_LOCK# (3)

H_REQ#[4:0] (3)

H_RS#[2:0] (3)

H_CPUSLP# (3,11)

H_TRDY# (3)

+1.05V (2,3,4,8,11,13,31,32,34)

C143

C143

.1U_4

.1U_4

H_VREF

C140

C140

.1U_4

.1U_4

+1.05V

3

R106

R106

100/F_4

100/F_4

R107

R107

200/F_4

200/F_4

3

AC41

AA41

AV40

AP40

AN40

AK40

AJ40

AH40

AG40

AF40

AE40

AY39

AW39

AV39

AR39

AN39

AJ39

AC39

AB39

AA39

W39

AT38

AM38

AH38

AG38

AF38

AE38

AK37

AH37

AB37

AA37

W37

AY36

AW36

AN36

AH36

AG36

AF36

AE36

AC36

BA35

AV35

AR35

AH35

AB35

AA35

W35

AN34

W41

M41

R39

N39

M39

H39

G39

D39

C38

R37

N37

M37

H37

G37

D37

C36

R35

N35

M35

H35

G35

D35

2

U27J

U27I

U27I

VSS_0

VSS_1

VSS_2

T41

VSS_3

P41

VSS_4

VSS_5

J41

VSS_6

F41

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

B40

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

Y39

VSS_27

VSS_28

V39

VSS_29

T39

VSS_30

VSS_31

P39

VSS_32

VSS_33

VSS

VSS

VSS_34

L39

VSS_35

J39

VSS_36

VSS_37

VSS_38

F39

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

Y37

VSS_52

VSS_53

V37

VSS_54

T37

VSS_55

VSS_56

P37

VSS_57

VSS_58

VSS_59

L37

VSS_60

J37

VSS_61

VSS_62

VSS_63

F37

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

B36

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

Y35

VSS_82

VSS_83

V35

VSS_84

T35

VSS_85

VSS_86

P35

VSS_87

VSS_88

VSS_89

L35

VSS_90

J35

VSS_91

VSS_92

VSS_93

F35

VSS_94

VSS_95

VSS_96

Calistoga

Calistoga

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

AK34

AG34

AF34

AE34

AC34

C34

AW33

AV33

AR33

AE33

AB33

Y33

V33

T33

R33

M33

H33

G33

F33

D33

B33

AH32

AG32

AF32

AE32

AC32

AB32

G32

B32

AY31

AV31

AN31

AJ31

AG31

AB31

Y31

AB30

E30

AT29

AN29

AB29

T29

N29

K29

G29

E29

C29

B29

A29

BA28

AW28

AU28

AP28

AM28

AD28

AC28

W28

J28

E28

AP27

AM27

AK27

J27

G27

F27

C27

B27

AN26

M26

K26

F26

D26

AK25

P25

K25

H25

E25

D25

A25

BA24

AU24

AL24

AW23

COMPONENTS P/N

945GM AJSL8Z20T25

ICH7-M AJSL8YB0T21

2

U27J

AT23

VSS_180

AN23

VSS_181

AM23

VSS_182

AH23

VSS_183

AC23

VSS_184

W23

VSS_185

K23

VSS_186

J23

VSS_187

F23

VSS_188

C23

VSS_189

AA22

VSS_190

K22

VSS_191

G22

VSS_192

F22

VSS_193

E22

VSS_194

D22

VSS_195

A22

VSS_196

BA21

VSS_197

AV21

VSS_198

AR21

VSS_199

AN21

VSS_200

AL21

VSS_201

AB21

VSS_202

Y21

VSS_203

P21

VSS_204

K21

VSS_205

J21

VSS_206

H21

VSS_207

C21

VSS_208

AW20

VSS_209

AR20

VSS_210

AM20

AA20

AN19

AC19

AH18

AY17

AR17

AP17

AM17

AK17

AV16

AN16

AL16

AN15

AM15

AK15

BA14

AT14

AK14

AD14

AA14

AV13

AR13

AN13

AM13

AL13

AG13

AY12

AC12

AD11

AA11

W19

G19

M15

K20

B20

A20

K19

C19

P18

H18

D18

A18

J16

F16

C16

N15

L15

B15

A15

U14

K14

H14

E14

P13

F13

D13

B13

K12

H12

E12

Y11

VSS

VSS

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

Calistoga

Calistoga

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH (HOST/GND)

GMCH (HOST/GND)

GMCH (HOST/GND)

Date: Sheet

Date: Sheet

Date: Sheet

1

J11

VSS_273

D11

VSS_274

B11

VSS_275

AV10

VSS_276

AP10

VSS_277

AL10

VSS_278

AJ10

VSS_279

AG10

VSS_280

AC10

VSS_281

W10

VSS_282

U10

VSS_283

BA9

VSS_284

AW9

VSS_285

AR9

VSS_286

AH9

VSS_287

AB9

VSS_288

Y9

VSS_289

R9

VSS_290

G9

VSS_291

E9

VSS_292

A9

VSS_293

AG8

VSS_294

AD8

VSS_295

AA8

VSS_296

U8

VSS_297

K8

VSS_298

C8

VSS_299

BA7

VSS_300

AV7

VSS_301

AP7

VSS_302

AL7

VSS_303

AJ7

VSS_304

AH7

VSS_305

AF7

VSS_306

AC7

VSS_307

R7

VSS_308

G7

VSS_309

D7

VSS_310

AG6

VSS_311

AD6

VSS_312

AB6

VSS_313

Y6

VSS_314

U6

VSS_315

N6

VSS_316

K6

VSS_317

H6

VSS_318

B6

VSS_319

AV5

VSS_320

AF5

VSS_321

AD5

VSS_322

AY4

VSS_323

AR4

VSS_324

AP4

VSS_325

AL4

VSS_326

AJ4

VSS_327

Y4

VSS_328

U4

VSS_329

R4

VSS_330

J4

VSS_331

F4

VSS_332

C4

VSS_333

AY3

VSS_334

AW3

VSS_335

AV3

VSS_336

AL3

VSS_337

AH3

VSS_338

AG3

VSS_339

AF3

VSS_340

AD3

VSS_341

AC3

VSS_342

AA3

VSS_343

G3

VSS_344

AT2

VSS_345

AR2

VSS_346

AP2

VSS_347

AK2

VSS_348

AJ2

VSS_349

AD2

VSS_350

AB2

VSS_351

Y2

VSS_352

U2

VSS_353

T2

VSS_354

N2

VSS_355

J2

VSS_356

H2

VSS_357

F2

VSS_358

C2

VSS_359

AL1

VSS_360

PROJECT : ZU2

PROJECT : ZU2

Quanta Computer Inc.

Quanta Computer Inc.

of

of

of

539Thursday, March 22, 2007

539Thursday, March 22, 2007

1

539Thursday, March 22, 2007

1A

1A

1A

5

U27B

CLK_MCH_OE#

T28T28

MCH_RSVD_1

T27T27

MCH_RSVD_2

T26T26

MCH_RSVD_3

T5T5

MCH_RSVD_4

T6T6

MCH_RSVD_5

T9T9

MCH_RSVD_6

T8T8

MCH_RSVD_7

T7T7

MCH_RSVD_8

T19T19

TV_DCONSEL0

T25T25

TV_DCONSEL1

T24T24

MCH_RSVD_11

T101T101

MCH_RSVD_12

D D

PM_BMBUSY#(13)

PM_EXTTS#0(9)

C C

B B

PM_DPRSLPVR(13,31)

PM_THRMTRIP#(3,11)

DELAY_VR_PWRGOOD(3,13,31)

PLT_RST-R#(12)

SDVO_CTRLCLK(17)

SDVO_CTRLDAT A(17)

MCH_ICH_SYNC(12)

+3V

R356 10K/F_4R356 10K/F_4

R359 *10K/F_4R359 *10K/F_4

GMCH Strap pin

A A

T95T95

MCH_RSVD_13

T94T94

MCH_RSVD_14

T23T23

MCH_RSVD_15

T92T92

MCH_BSEL0(2)

MCH_BSEL1(2)

MCH_BSEL2(2)

PM_EXTTS#0

PM_EXTTS#1

T13T13

T12T12

T11T11

T90T90

T17T17

T14T14

R358 0_4R358 0_4

R128 100/F_4R128 100/F_4

T81T81

T103T103

T80T80

T97T97

T96T96

T93T93

T91T91

T89T89

T87T87

T98T98

T79T79

T102T102

T82T82

T99T99

T83T83

T104T104

T86T86

T100T100

T78T78

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

PM_EXTTS#0

PM_EXTTS#1

RST IN# MCH

TP_MCH_NC0

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

TP_MCH_NC17

TP_MCH_NC18

CFG[3..17] has internal PU CFG[18..20] has internal PD

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

R341 *2.2K_4R341 *2.2K_4

MCH_CFG_5 DMI speed mode

Low = DMI X2

High=DMIX4

R348 *2.2K_4R348 *2.2K_4

MCH_CFG_6 DDR

Low =Moby Dick

High= Calistoga (Default)

R112 *2.2K_4R112 *2.2K_4

MCH_CFG_7 CPU Strap

Low=RSVD

High=Mobile CPU

R111 *2.2K_4R111 *2.2K_4

MCH_CFG_9 PCI Exp Graphics Lane

Low =Reserved

High=Normal

5

U27B

H32

RSVD_0

T32

RSVD_1

R32

RSVD_2

F3

RSVD_3

F7

RSVD_4

AG11

RSVD_5

AF11

RSVD_6

H7

RSVD_7

J19

RSVD_8

K30

RSVD_9

J29

RSVD_10

A41

RSVD_11

A35

RSVD_12

A34

RSVD_13

D28

RSVD_14

D27

RSVD_15

K16

CFG_0

K18

CFG_1

J18

CFG_2

F18

CFG_3

E15

CFG_4

F15

CFG_5

E18

CFG_6

D19

CFG_7

D16

CFG_8

G16

CFG_9

E16

CFG_10

D15

CFG_11

G15

CFG_12

K15

CFG_13

C15

CFG_14

H16

CFG_15

G18

CFG_16

H15

CFG_17

J25

CFG_18

K27

CFG_19

J26

CFG_20

G28

PM_BMBUSY#

F25

PM_EXTTS#_0

H26

PM_EXTTS#_1

G6

PM_THRMTRIP#

AH33

PWROK

AH34

RSTIN#

H28

SDVO_CTRLCLK

H27

SDVO_CTRLDATA

K28

LT_RESET#

D1

NC0

C41

NC1

C1

NC2

BA41

NC3

BA40

NC4

BA39

NC5

BA3

NC6

BA2

NC7

BA1

NC8

B41

NC9

B2

NC10

AY41

NC11

AY1

NC12

AW41

NC13

AW1

NC14

A40

NC15

A4

NC16

A39

NC17

A3

NC18

< 0.1" . 15mils/15mils space

use 1% R

PM

PM

MISC

MISC

NC

NC

Calistoga

Calistoga

CFGRSVD

CFGRSVD

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_RCOMP#

SM_RCOMP

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

SM_VREF_0

SM_VREF_1

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

4

AY35

SM_CK_0

AR1

SM_CK_1

AW7

SM_CK_2

AW40

SM_CK_3

AW35

SM_CK#_0

AT1

SM_CK#_1

AY7

SM_CK#_2

AY40

SM_CK#_3

AU20

SM_CKE_0

AT20

SM_CKE_1

BA29

SM_CKE_2

AY29

SM_CKE_3

AW13

SM_CS#_0

AW12

SM_CS#_1

AY21

SM_CS#_2

AW21

SM_CS#_3

AL20

AF10

BA13

SM_ODT_0

BA12

SM_ODT_1

AY20

SM_ODT_2

AU21

SM_ODT_3

AV9

AT9

SMDDR_VREF_MCH

AK1

AK41

AF33

G_CLKIN#

AG33

G_CLKIN

A27

A26

C40

D41

DMI_TXN0

AE35

DMI_TXN1

AF39

AG35

DMI_TXN3

AH39

DMI_TXP0

AC35

DMI_TXP1

AE39

DMI_TXP2

AF35

DMI_TXP3

AG39

DMI_RXN0

AE37

DMI_RXN1

AF41

DMI_RXN2

AG37

DMI_RXN3

AH41

DMI_RXP0

AC37

DMI_RXP1

AE41

DMI_RXP2

AF37

DMI_RXP3

AG41

MCH_CFG_10

MCH_CFG_16

R346 *2.2K_4R346 *2.2K_4

MCH_CFG_10 Host PLL VCC Select

Low=Reserved

High=Mobility

MCH_CFG_11

MCH_CFG_11 PSB 4x CLK ENABLE

Low=Reserved

High=Calistoga

MCH_CFG_12

MCH_CFG_13

MCH_CFG_12,13 XOR/ALLZ

0,0=Partial clock gating disable

0,1=All-Z mode enable

1,0=XOR mode enable

1,1=Normal

R344 *2.2K_4R344 *2.2K_4

MCH_CFG_16 FSB Dynmic ODT

Low=Dynamic ODT Disabled

High=Dynamic ODT Enabled.

4

CLK_SDRAM0 (9)

CLK_SDRAM1 (9)

CLK_SDRAM3 (9)

CLK_SDRAM4 (9)

CLK_SDRAM0# (9)

CLK_SDRAM1# (9)

CLK_SDRAM3# (9)

CLK_SDRAM4# (9)

CKE0 (9,10)

CKE1 (9,10)

CKE2 (9,10)

CKE3 (9,10)

SM_CS0# (9,10)

SM_CS1# (9,10)

SM_CS2# (9,10)

SM_CS3# (9,10)

M_OCDCOMP_0

M_OCDCOMP_1

M_ODT0 (9,10)

M_ODT1 (9,10)

M_ODT2 (9,10)

M_ODT3 (9,10)

M_RCOMP #

M_RCOMP

R83 0_6R83 0_6

R85 *10K_6R85 *10K_6

R82 *10K_6R82 *10K_6

CLK_PCIE_3GPLL# (2)

CLK_PCIE_3GPLL (2)

DREFCLK# (2)

DREFCLK (2)

DREFSSCLK# (2)

DREFSSCLK (2)

R343 *2.2K_4R343 *2.2K_4

R336 *2.2K_4R336 *2.2K_4

R109 *2.2K_4R109 *2.2K_4

15mils/15mils

*40.2/F_4

*40.2/F_4

Layout as short as passable

NC from WW45

SMDDR_VREF

+1.8VSUS

DMI_TXN[3:0] (12)

DMI_TXP[3:0] ( 12)

DMI_RXN[3:0] (12)

DMI_RXP[3:0] (12)

3

+3V

R104

R104

R115

R115

*40.2/F_4

*40.2/F_4

20 mil

+1.8VSUS

R102

R102

80.6/F_4

80.6/F_4

M_RCOMP #

15mils/10mils

M_RCOMP

R101

R101

80.6/F_4

80.6/F_4

MCH_CFG_18

MCH_CFG_18 VCC Select

LOW=1.05V

High=1.5V

MCH_CFG_19

MCH_CFG_19 DMI LANE Reversal

Low=Normal

High=LANES Reversed

MCH_CFG_20

MCH_CFG_20 PCIE Backward interpoerability mode

Low= only SDVO or PCIE x1 is

operational (defaults)

High=SDVO and PCIE x1 are operation

simultaneously via the PEG port

TV_COMP(16)

TV_Y/G(16)

TV_C/R(16)

CRT_BLU(15)

CRT_GRN(15)

CRT_RED(15)

CRT_DDCCLK(15)

CRT_DDCDAT(15)

HSYNC(15)

VSYNC(15)

R360 *1K/F_4R360 *1K/F_4

R361 *1K/F_4R361 *1K/F_4

R364 *1K/F_4R364 *1K/F_4

3

R363 10K/F_4R363 10K/F_4

R362 10K/F_4R362 10K/F_4

R131

R131

1.5K/F_4

1.5K/F_4

R113 150/F_4R113 150/F_4

R114 150/F_4R114 150/F_4

R108 150/F_4R108 150/F_4

LVDS_PWM(16)

LVDS_BLON( 16)

I_EDIDCLK(16)

I_EDIDDAT A(16)

LCD_PWRON( 16)

TXLCLKOUT-(16)

TXLCLKOUT+(16)

TXLOUT0-(16)

TXLOUT1-(16)

TXLOUT2-(16)

TXLOUT0+(16)

TXLOUT1+(16)

TXLOUT2+(16)

< 0.1" . 15mils/15mils space

R119 150/F_4R119 150/F_4

R117 150/F_4R117 150/F_4

R118 150/F_4R118 150/F_4

R354 39_4R354 39_4

R120 255/F_6R120 255/F_6

R355 39_4R355 39_4

+3V

+3V

+3V

T33T33

TV_COMP

TV_Y/G

TV_C/RDMI_TXN2

R116

R116

CRT_BLU

CRT_GRN

CRT_RED

4.99K/F_6

4.99K/F_6

L_CLKCTLA

L_CLKCTLB

L_IBG

L_VBG

L_VREFH

L_VREFL

HSYNC_R

CRTIREF

VSYNC_R

TVIREF

U27C

U27C

D32

J30

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

J20

B16

B18

B19

E23

D23

C22

B22

A21

B21

C26

C25

G23

J22

H23

Calistoga

Calistoga

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DAC A_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

2

LVDS

LVDS

TV

TV

VGA

VGA

+V1.5_PCIE

+3V

SMDDR_VREF

+1.8VSUS

2

20mils/20mils space

EXP_A_COMPX

D40

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

D38

F34

EXP_A_RXN_0

G38

EXP_A_RXN_1

H34

EXP_A_RXN_2

J38

EXP_A_RXN_3

L34

EXP_A_RXN_4

M38

EXP_A_RXN_5

N34

EXP_A_RXN_6

P38

EXP_A_RXN_7

R34

EXP_A_RXN_8

T38

EXP_A_RXN_9

V34

W38

Y34

AA38

AB34

AC38

D34

EXP_A_RXP_0

F38

EXP_A_RXP_1

G34

EXP_A_RXP_2

H38

EXP_A_RXP_3

J34

EXP_A_RXP_4

L38

EXP_A_RXP_5

M34

EXP_A_RXP_6

N38

EXP_A_RXP_7

P34

EXP_A_RXP_8

R38

EXP_A_RXP_9

T34

V38

W34

Y38

AA34

AB38

F36

EXP_A_TXN_0

G40

EXP_A_TXN_1

H36

EXP_A_TXN_2

J40

EXP_A_TXN_3

L36

EXP_A_TXN_4

M40

EXP_A_TXN_5

N36

EXP_A_TXN_6

P40

EXP_A_TXN_7

R36

EXP_A_TXN_8

T40

EXP_A_TXN_9

V36

W40

Y36

AA40

AB36

AC40

D36

EXP_A_TXP_0

F40

EXP_A_TXP_1

G36

EXP_A_TXP_2

H40

EXP_A_TXP_3

J36

EXP_A_TXP_4

L40

EXP_A_TXP_5

M36

EXP_A_TXP_6

N40

EXP_A_TXP_7

P36

EXP_A_TXP_8

R40

EXP_A_TXP_9

T36

V40

W36

Y40

AA36

AB40

+V1.5_PCIE (8)

+3V (2,3,8,9,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,29,30,31,32,34)

SMDDR_VREF (9,33,34)

+1.8VSUS (8,9,33, 34)

GMCHEXP_RXN1 (17)

GMCHEXP_RXP1 (17 )

CGMCHEXP_TXN0

CGMCHEXP_TXN1

CGMCHEXP_TXN2

CGMCHEXP_TXN3

CGMCHEXP_TXP0

CGMCHEXP_TXP1

CGMCHEXP_TXP2

CGMCHEXP_TXP3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

+V1.5_PCIE

R132 24.9/F_4R132 24.9/F_4

C245 0.1U_4C245 0.1U_4

C510 0.1U_4C510 0.1U_4

C247 0.1U_4C247 0.1U_4

C512 0.1U_4C512 0.1U_4

C244 0.1U_4C244 0.1U_4

C509 0.1U_4C509 0.1U_4

C246 0.1U_4C246 0.1U_4

C511 0.1U_4C511 0.1U_4

GMCH (DMI&PCIE&VGA )

GMCH (DMI&PCIE&VGA )

GMCH (DMI&PCIE&VGA )

1

SDVOB_R- (17)

SDVOB_G- (17)

SDVOB_B- (17)

SDVOB_CLK- (17)

SDVOB_R+ (17)

SDVOB_G+ ( 17)

SDVOB_B+ ( 17)

SDVOB_CLK+ (17)

PROJECT : ZU2

PROJECT : ZU2

Quanta Computer Inc.

Quanta Computer Inc.

639Thursday, March 22, 2007

639Thursday, March 22, 2007

639Thursday, March 22, 2007

of

of

1

of

1A

1A

1A

5

4

3

2

1

R_A_MD[63:0](9)

D D

C C

B B

R_A_MD0

R_A_MD1

R_A_MD2

R_A_MD3

R_A_MD4

R_A_MD5

R_A_MD6

R_A_MD7

R_A_MD8

R_A_MD9

R_A_MD10

R_A_MD11

R_A_MD12

R_A_MD13

R_A_MD14

R_A_MD15

R_A_MD16

R_A_MD17

R_A_MD18

R_A_MD19

R_A_MD20

R_A_MD21

R_A_MD22

R_A_MD23

R_A_MD24

R_A_MD25

R_A_MD26

R_A_MD27

R_A_MD28

R_A_MD29

R_A_MD30

R_A_MD31

R_A_MD32

R_A_MD33

R_A_MD34

R_A_MD35

R_A_MD36

R_A_MD37

R_A_MD38

R_A_MD39

R_A_MD40

R_A_MD41

R_A_MD42

R_A_MD43

R_A_MD44

R_A_MD45

R_A_MD46

R_A_MD47

R_A_MD48

R_A_MD49

R_A_MD50

R_A_MD51

R_A_MD52

R_A_MD53

R_A_MD54

R_A_MD55

R_A_MD56

R_A_MD57

R_A_MD58

R_A_MD59

R_A_MD60

R_A_MD61

R_A_MD62

R_A_MD63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U27D

U27D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Calistoga

Calistoga

AU12

SA_BS_0

AV14

SA_BS_1

BA20

SA_BS_2

AY13

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

R_A_DM0

R_A_DM1

R_A_DM2

R_A_DM3

R_A_DM4

R_A_DM5

R_A_DM6

R_A_DM7

R_A_DQS0

R_A_DQS1

R_A_DQS2

R_A_DQS3

R_A_DQS4

R_A_DQS5

R_A_DQS6

R_A_DQS7

R_A_DQS#0

R_A_DQS#1

R_A_DQS#2

R_A_DQS#3

R_A_DQS#4

R_A_DQS#5

R_A_DQS#6

R_A_DQS#7

R_A_MA0

R_A_MA1

R_A_MA2

R_A_MA3

R_A_MA4

R_A_MA5

R_A_MA6

R_A_MA7

R_A_MA8

R_A_MA9

R_A_MA10

R_A_MA11

R_A_MA12

R_A_MA13

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

R_A_BS1# (9,10)

R_A_BS2# (9,10)

R_A_SCASA# (9, 10)

R_A_DM[7:0] (9)

R_A_DQS[7:0] (9)

R_A_DQS#[7:0] (9)

R_A_MA[13:0] (9,10)

R_A_SRASA# (9, 10)

T20T20

T21T21

R_A_BMWEA# (9,10)

R_B_MD[63:0](9)R_A_BS0# (9, 10)

R_B_MD0

R_B_MD1

R_B_MD2

R_B_MD3

R_B_MD4

R_B_MD5

R_B_MD6

R_B_MD7

R_B_MD8

R_B_MD9

R_B_MD10

R_B_MD11

R_B_MD12

R_B_MD13

R_B_MD14

R_B_MD15

R_B_MD16

R_B_MD17

R_B_MD18

R_B_MD19

R_B_MD20

R_B_MD21

R_B_MD22

R_B_MD23

R_B_MD24

R_B_MD25

R_B_MD26

R_B_MD27

R_B_MD28

R_B_MD29

R_B_MD30

R_B_MD31

R_B_MD32

R_B_MD33

R_B_MD34

R_B_MD35

R_B_MD36

R_B_MD37

R_B_MD38

R_B_MD39

R_B_MD40

R_B_MD41

R_B_MD42

R_B_MD43

R_B_MD44

R_B_MD45

R_B_MD46

R_B_MD47

R_B_MD48

R_B_MD49

R_B_MD50

R_B_MD51

R_B_MD52

R_B_MD53

R_B_MD54

R_B_MD55

R_B_MD56

R_B_MD57

R_B_MD58

R_B_MD59

R_B_MD60

R_B_MD61

R_B_MD62

R_B_MD63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

U27E

U27E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

Calistoga

Calistoga

AT24

SB_BS_0

AV23

SB_BS_1

AY28

SB_BS_2

AR24

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_WE#

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

R_B_DM0

R_B_DM1

R_B_DM2

R_B_DM3

R_B_DM4

R_B_DM5

R_B_DM6

R_B_DM7

R_B_DQS0

R_B_DQS1

R_B_DQS2

R_B_DQS3

R_B_DQS4

R_B_DQS5

R_B_DQS6

R_B_DQS7

R_B_DQS#0

R_B_DQS#1

R_B_DQS#2

R_B_DQS#3

R_B_DQS#4

R_B_DQS#5

R_B_DQS#6

R_B_DQS#7

R_B_MA0

R_B_MA1

R_B_MA2

R_B_MA3

R_B_MA4

R_B_MA5

R_B_MA6

R_B_MA7

R_B_MA8

R_B_MA9

R_B_MA10

R_B_MA11

R_B_MA12