Acer TravelMate 6252, TravelMate 6292 Schematics

5

4

3

2

1

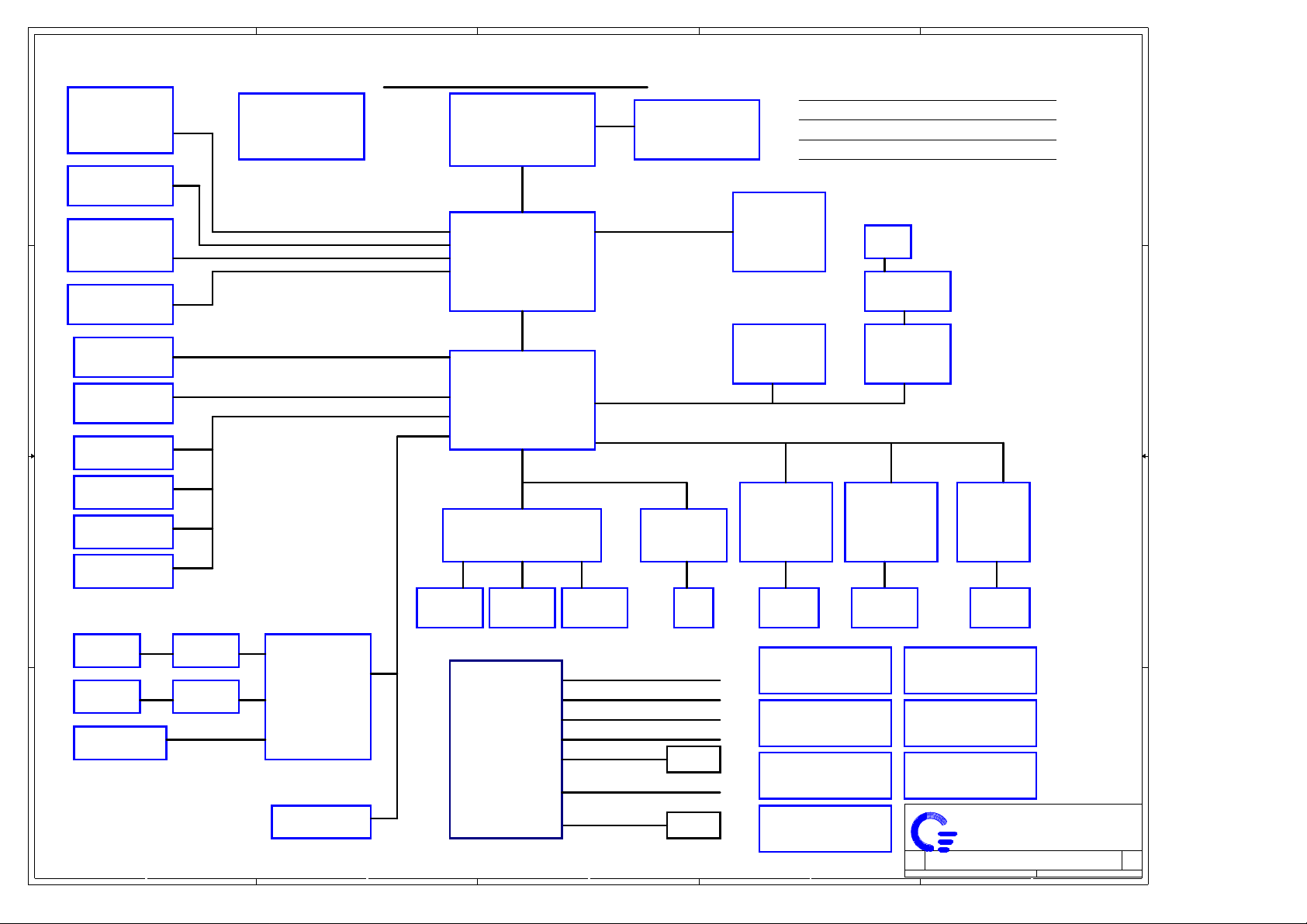

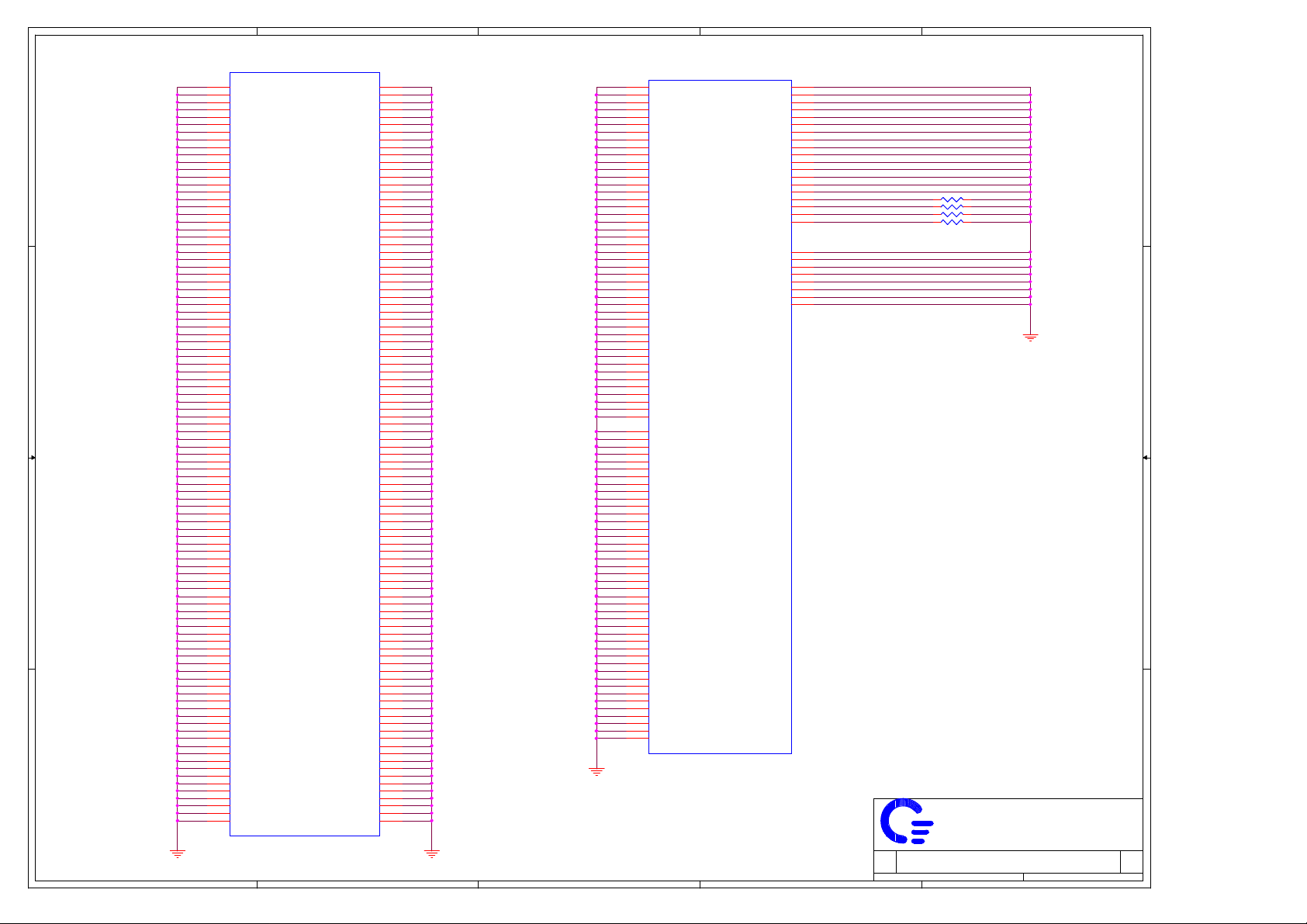

ZU1 SYSTEM BLOCK DIAGRAM

DVI / 7307

Chrontel

(only for ezDock)

D D

Page 21

S-VIDEO CONN

Page 20

LCD CONN

(12.1"WXGA)

Page 20

CRT Port

Page 19

C C

HDD (SATA)

Page 26

ODD (PATA)

Page 26

USB Port x 3

USB0~2

Page 27

CLOCK GENERATOR

CK505

Page 2

SDVO

TV

LVDS

VGA

SATA

PATA

USB 2.0

Azalia

Merom 479

uFCPGA

Page 3,4

FSB

667/800 Mhz

NB

Crestline

(GM965)

Page 5~11

X4 DMI interface

SB

ICH8M

Page 14~17

CPU

Thermal Sensor

Dual Channel DDR2

533/667 MHz

PCI-Express

PCI Bus

Page 3

DDRII

SO-DIMM 0

SO-DIMM 1

Page 12,13

Mini Card /

WLAN

Page 27

PCIE-0

REQ# / GNT#PCI DEVICE InterruptsIDSEL#

AD17 REQ0# / GNT0# INTA#CB1410

AD18 REQ1# / GNT1# INTB#MR510

RJ45

Page 18

Transformer

Giga Lan

(BCM 5787)

Page 18

Page 18

PCIE-1

CLOCK

CK505/PCI1

CK505/PCI0

CK505/PCI2AD25 REQ2# / GNT2# INTE#TIAB23

LPC

Bluetooth

USB4

Finger Printer

USB6

B B

CCD

USB8

Page 27

Page 29

Page 20

uR PC8763L

Page 28

SPI ROM

Page 28 Page 29 Page 29

Touch Pad

K/B CONN

Super I/O

NS PC87383

Page 30

FIR

Page 30

PCMCIA

Controller

(CB 1410)

Page 22

PCMCIA

Page 24

Card Reader

Controller

(MR510)

Page 23

Card Reader

Page 24

1394

Controller

(TI 43AB23)

Page 25

1394 CONN

Page 25

5

HP AMPHP

Page 31

SPK AMP

Page 32

Audio Codec

(ALC268)

Page 31

MDC 1.5

Page 31 Page 33

ezDockII/II+

Connector

PCIE , Lan ,1394

Ser & Par Port

PS2 , VGA, DVI

SPDIF,SM BUS

MediaBay

Express Card

DVI

USB

1394*2

TV out / CRT

Audio

10/100/1G

PCI-Express

4

3

PCIE-2

USB3

Switch

Page 20

Switch

Page 18

5V/3V (ISL6236)

Page 34

VCORE(ISL6262A)

Page 35

VTT 1.05V (SC411)

Page 36

1.8V (TPS51116)

Page 37

2

1.25V 1.5V 1.25V

Page 38

Discharge

Page 38

Page 39

A1A

(11/2):(1) Re-name.

(2) Gerber out

1 39Thursday, November 02, 2006

1

Charger (ISL6251)

PROJECT : ZU1

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

Block Diagram

1A

Page 32

INT SPK

Page 32

Line in & MIC

Page 32

A A

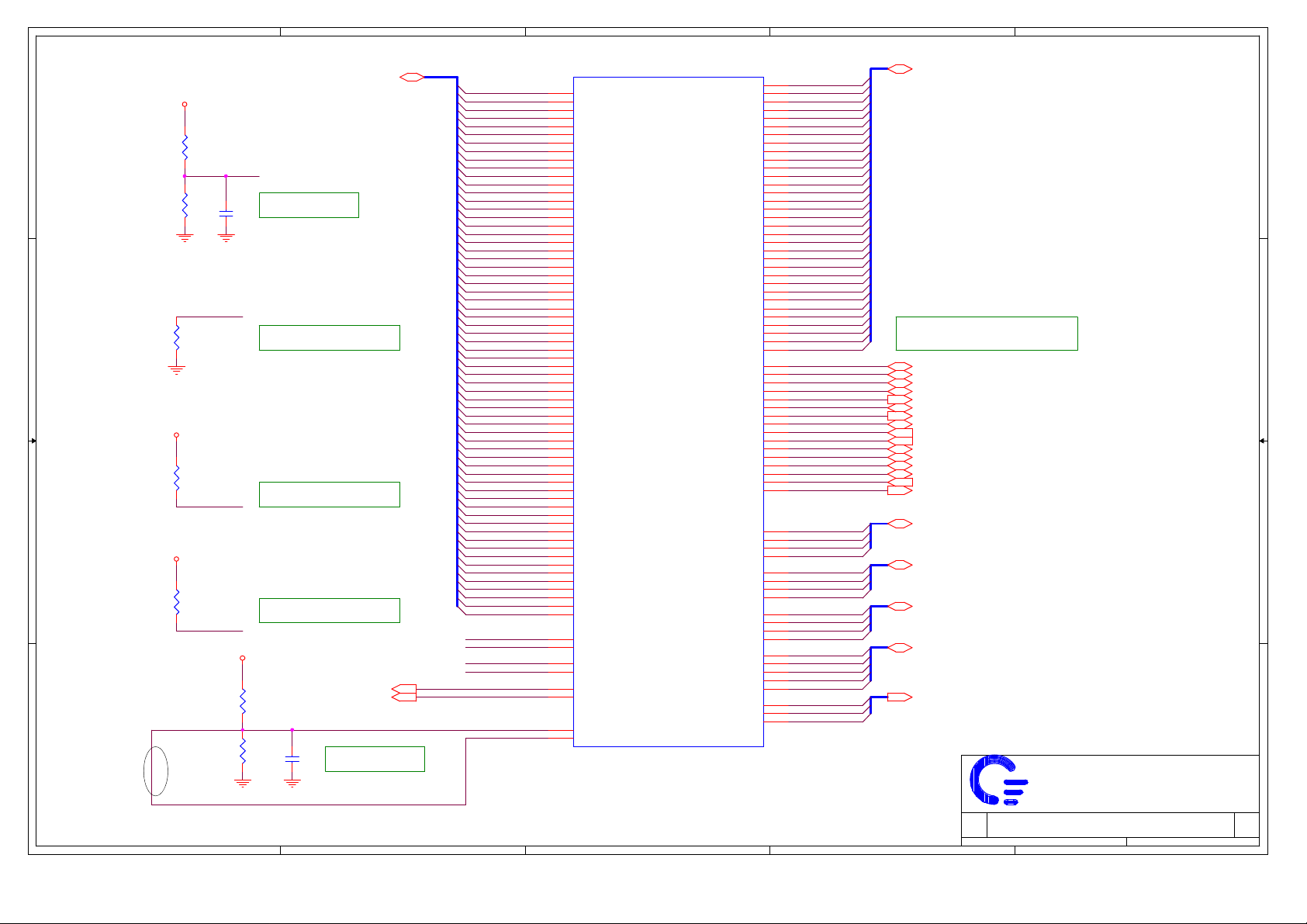

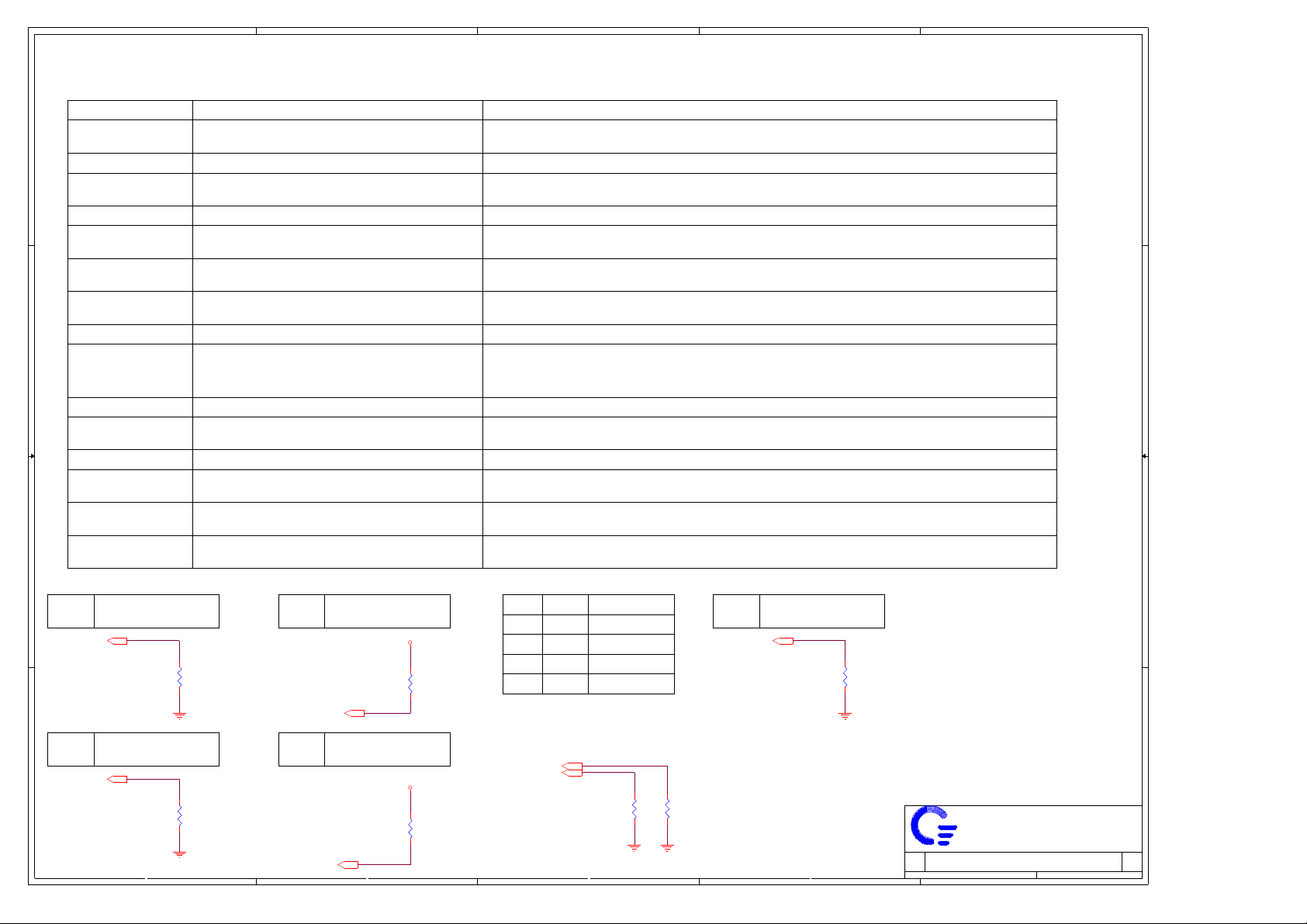

Clock Generator

L55

+3V

BKP1608HS181-T_6

A1A:(9/24)

ICS FAE suggest to change

C2,C4 from 4.7uF to 10uF

A1A:(9/28)

D D

Reverse RC0603 footprint for EMI

PCI_CLK_51023

PCI_CLK_CB71422

PCLK_139425

PCLK_59128

PCI_CLK_SIO27,30

PCLK_ICH15

C C

CLKUSB_4816

14M_ICH16

A1A:(9/24) FAE : (14M_ICH and SIO_14M) signals trace should be equal length

SIO_14M30

A1A:(9/20) change R value from 33ohm to 22 ohm(Intel check list 1.301)

5

C288 .1U_4

0_6

R436

0_6

R199

0_6

R444

R429 10K_4

R428 *10K_4

R427 10K_4

R181 *10K_4

R182 10K_4

R426 2.2K_4

R441 10K_4

R442 22_4

R443 22_4

C294 .1U_4

C287 10U_8

C540 .1U_4

C292 .1U_4

C319 .1U_4

C318 .1U_4

+1.05V_VDD

R188 22_4 RP34 0X2

R434 33_4

R433 33_4

R187 33_4

R431 22_4

R186 22_4

R430 33_4

C542

10U_8

A1A:(9/20) remove SATACLKREQ function, change R value from 475ohm to 22 ohm

+3V

+3V

+3V

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2 FSC

A1A:(9/24) ICS FAE suggest R change from 22 to 33 ohm

4

VDD_CK_VDD_PCI

VDD_CK_VDD_48

VDD_CK_VDD_SRC

VDD_CK_VDD_REF

VDD_CK_VDD_SRC

VDD_CK_VDD_CPU

PCI_CLK_510_R

PCI_CLK_CB714_R

PCLK_1394_R

PCLK_591_R

PCI_CLK_SIO_R

PCLK_ICH_R

CG_XIN

CG_XOUT

FSA

U19

IC(64P)SLG8SP512TTR(TSSOP)

2

VDD_PCI

9

VDD_48

16

VDD_PLL3

61

VDD_REF

39

VDD_SRC

55

VDD_CPU

12

VDD_96_IO

20

VDD_PLL3_IO

26

VDD_SRC_IO_1

45

VDD_SRC_IO_3

36

VDD_SRC_IO_2

49

VDD_CPU_IO

1

PCI0/CR#_A

3

PCI1/CR#_B

4

PCI2/TME

5

PCI3

6

PCI4/SRC5_EN

7

PCIF5/ITP_EN

60

XTAL_IN

59

XTAL_OUT

10

USB_48/FSA

57

FSB/TEST/MODE

62

REF0/FSC/TESTSEL

8

VSS_PCI

11

VSS_48

15

VSS_IO

19

VSS_PLL3

52

VSS_CPU

23

VSS_SRC1

29

VSS_SRC2

42

VSS_SRC3

58

VSS_REF

CK505

SRC5/PCI_STOP#

SRC5#/CPU_STOP#

SRC11/CR#_H

SRC11#/CR#_G

SRC7/CR#_F

SRC7#/CR#_E

SRC3/CR#_C

SRC3#/CR#_D

SRC2#/SATA#

SRC0/DOT96

SRC0#/DOT96#

CKPWRGD/PWRDWN#

ICS9LPRS365AGLFT/ SLG8SP512T

ICS9LPRS365BGLFT

SLG8SP512T: AL8SP512K05

48

IO_VOUT

SRC8/ITP

SRC8#/ITP#

SRC10#

SRC2/SATA

SRC1/SE1

SRC1#/SE2

CGCLK_SMB

64

SCLK

CGDAT_SMB

63

SDA

38

37

CLK_CPU_BCLK_R

54

CPU0

CLK_CPU_BCLK#_R

53

CPU0#

CLK_MCH_BCLK_R

51

CPU1

CLK_MCH_BCLK#_R

50

CPU1#

47

46

CLK_PCIE_3GPLL#_R

35

CLK_PCIE_3GPLL_R

34

SRC10

PCIE_CLK_RBS_R

33

PCIE_CLK_RBS#_R

32

CLK_PCIE_EZ1_R

30

SRC9

CLK_PCIE_EZ1#_R

31

SRC9#

44

43

CLK_PCIE_ICH_R

41

SRC6

CLK_PCIE_ICH#_R

40

SRC6#

CLK_PCIE_MINI1_R

27

SRC4

CLK_PCIE_MINI1#_R

28

SRC4#

CLK_PCIE_LAN_R

24

CLK_PCIE_LAN#_R PCIE_CLKREQ#

25

CLK_PCIE_SATA_R

21

CLK_PCIE_SATA#_R

22

DREFSSCLK_R

17

DREFSSCLK#_R

18

DREFCLK_R

13

DREFCLK#_R

14

56

3

A1A:(9/20) remove IO_VOUT

RP36 0X2

RP35 0X2

RP29 0X2

RP37 0X2

RP30 0X2

RP31 0X2

RP32 0X2

RP41 0X2

RP33 0X2

2

1

4

3

2

1

4

3

4

3

2

1

R194 475_4

R185 475_4

4

3

2

1

2

1

4

3

4

3

2

1

4

3

2

1

4

3

2

1

2

1

4

3

4

3

2

1

During initial power-up be used to

sample FSB speed with FSA/B/C

2

PM_STPPCI#16

PM_STPCPU#16

CLK_CPU_BCLK3

CLK_CPU_BCLK#3

CLK_MCH_BCLK5

CLK_MCH_BCLK#5

CLK_PCIE_3GPLL#6

CLK_PCIE_3GPLL6

CLK_MCH_OE#6

PCIE_CLKREQ#33

PCIE_CLK1+33

PCIE_CLK1-33

CLK_PCIE_ICH15

CLK_PCIE_ICH#15

CLK_PCIE_MINI127

CLK_PCIE_MINI1#27

CLK_PCIE_LAN18

CLK_PCIE_LAN#18

CLK_PCIE_SATA14

CLK_PCIE_SATA#14

DREFSSCLK6

DREFSSCLK#6

DREFCLK6

DREFCLK#6

CK_PWRGD16

1

Clock Gen I2C

+3V

Q21

RHU002N06

PDAT_SMB13,16,18,27,33

PCLK_SMB13,16,18,27,33

Pin

3

+3V

Q20

RHU002N06

3

Active

32

33

Control signal

Low

Low

A1A:(9/24) Base on above table, SWAP SRC3 and SRC9

+3V

R184 10K_4

A1A:(9/24) Add PCIE_CLKREQ# PU to +3V

2

2

SRC9/9#

SRC10/10#

R197

10K_4

CGDAT_SMB

1

R195

10K_4

CGCLK_SMB

1

C310 33P_4

C299 33P_4

<check list>

B B

PCLK_DEBUG28

XTAL length < 500mils

BIOS/ ERIC

IF M/B NEED LPC DEBUG PORT, \THEN STUFF THIS RESITER.

R432 *33_4

21

CG_XIN

Y2

14.318MHZ

CG_XOUT

PCLK_1394_R

CPU Clock select

CPU_BSEL03

+1.05V_CPU

CPU_BSEL13

A A

+1.05V_CPU

CPU_BSEL23

+1.05V_CPU

R180 0_4

R425 *56_4

R179 1K_4

A1A: (10/23) stuff

R440 0_4

R439 *0_4

R198 1K_4

A1A: (10/23) stuff

R448 0_4

R449 *0_4

R447 1K_4

A1A: (10/23) stuff

5

CLK_BSEL0

CLK_BSEL1

A1A: (9/20) Remove 0ohm

CLK_BSEL2

MCH_BSEL06

MCH_BSEL16

MCH_BSEL26

<check list>

(1)PCI2/TME: PU be used, the CK505 cannot over clock any of the clock for Trust Mode security purposes.

(2)PCI4/SRC5_EN: PU be used, the CK505 will be configured to use Pin37/38 to SRC5 clock.

If PD be detect at powe-on,the CK505 will setting Pin 37/38 to PCI_STOP/CUP_SOTP

(Default is setting to PCI_STOP/CUP_SOTP)

(3)PCIF5/ITP_EN: PU be used, the CK505 will be configured to use Pin46/47 to CPU ITP clock.

If PD be detect at powe-on,the CK505 will setting Pin 46/47 to SRC8

(Default is setting to SRC8)

(4)SLG8SP512 Pin 6 select Pin 17, 18 output is LCDCLK or 27 M, PD is LCDCLK, PU is 27 M ,

Pin 37, 38 will fixed be use CPU_Stop and PCI_Stop.

(5)SLG505YC64 CK505 Standar parts follow standar setting

BSEL Frequency Select Table

FSC FSB FSA Frequency

0

0

0

0

1

0

1

1

1

1

0

1

0

1

4

266Mhz0

0

1

133Mhz

1

166Mhz

0

200Mhz

01

400Mhz

1

Reserved

1

100Mhz

0

333Mhz

3

Clock Gen Differential IO power

C320

*10U_8

2

C309

*10U_8

C300

*10U_8

C314

C301

10U_8

C317

C316

.1U_4

0.1U close to each VDD_IO Power pin

.1U_4

.1U_4

C290

.1U_4

PROJECT : ZU1

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

CLK. GEN./ CK505

C315

.1U_4

+1.05V_VDD

L26

BKP1608HS181-T_6

EMI FILTER BKP1608HS181-T(180,1.5A)

C293

C291

.1U_4

.1U_4

1

+1.05V

2 39Thursday, November 02, 2006

1A

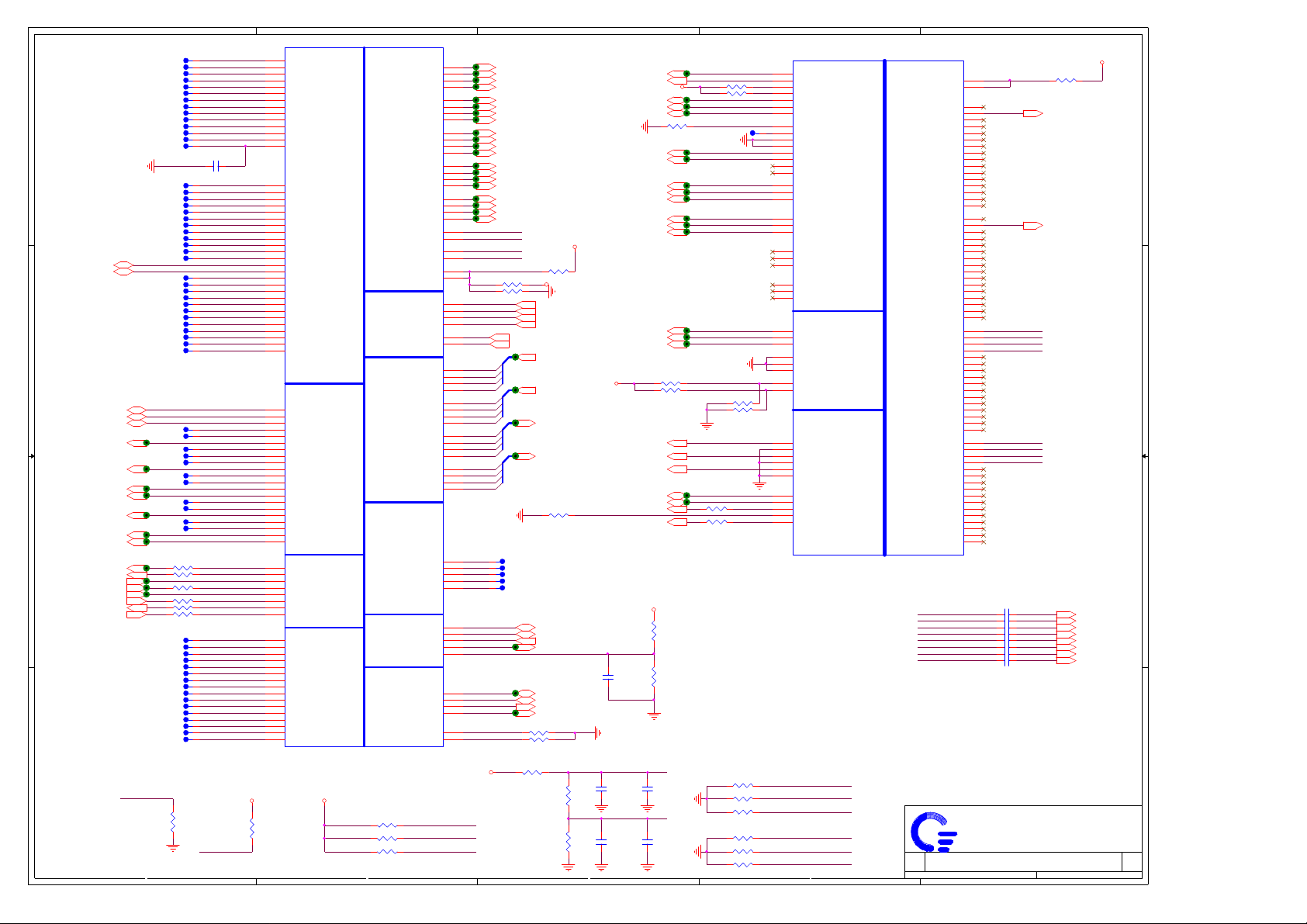

5

H_A#[16:3]5

CPU(HOST)

D D

C C

H_STPCLK#14

B B

+1.05V_CPU

A A

H_ADSTB0#5

H_REQ#[4:0]5

H_A#[35:17]5

R173 0_4

H_D#[15:0]5

H_DSTBN#05

H_DSTBP#05

H_DINV#05

H_D#[31:16]5

<Check list & CRB>

Layout note: Z=55 ohm

H_GTLREF<0.5"

R92

H_DSTBN#15

1K_4

H_DSTBP#15

H_DINV#15

T4

T57

T6

R90

2K_6

H_ADSTB1#5

H_A20M#14

H_FERR#14

H_IGNNE#14

H_INTR14

H_NMI14

H_SMI#14

T55

T50

T56

T53

T108

T48

T52

T5

T54

T49

R94 *1K_4

R93 *1K_4

C132 *.1U_4

CPU_BSEL02

CPU_BSEL12

CPU_BSEL22

5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_STPCLK_R#

TP_CPU_RSVD01

TP_CPU_RSVD02

TP_CPU_RSVD03

TP_CPU_RSVD04

TP_CPU_RSVD05

TP_CPU_RSVD06

TP_CPU_RSVD07

TP_CPU_RSVD08

TP_CPU_RSVD09

TP_CPU_RSVD10

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_GTLREF

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

U30A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

U30B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Merom Ball-out Rev 1a

ADDR GROUP 0 ADDR GROUP 1

XDP/ITP SIGNALS

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

THERMTRIP#

H CLK

RESERVED

DATA GRP 0

DATA GRP 1

MISC

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

BCLK[0]

BCLK[1]

DATA GRP 2DATA GRP 3

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

SLP#

PSI#

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

4

H_IERR#

XDP_TCK

XDP_TDI

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT_R#

H_THERMDA

H_THERMDC

THERMTRIP#_PWR

H_D#32

Y22

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

Y26

AA26

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

AE25

AF24

AC20

COMP0

R26

COMP1

U26

COMP2

AA1

COMP3

Y1

E5

B5

D24

D6

D7

AE6

4

H_ADS# 5

H_BNR# 5

H_BPRI# 5

H_DEFER#5

H_DRDY#5

H_DBSY#5

R109 56.2_4

A1A: (9/4)

Remove XDP/ITP signals

R112 0_4

R107 56.2_4

R111 *2.2K_4

<check list>

Default PU 56ohm if no use.

Serial R NC, If connect to power side PU 68ohm. Serial R 2.2K

CLK_CPU_BCLK2

CLK_CPU_BCLK#2

H_D#[47:32]5

H_DSTBN#25

H_DSTBP#25

H_DINV#25

H_D#[63:48]5

H_DSTBN#35

H_DSTBP#35

R89 27.4_6

R91 54.9_4

R172 27.4_6

R169 54.9_4

H_DINV#35

H_DPSLP#14

H_DPWR#5

H_CPUSLP#5

PSI# 35

H_BREQ#05

+1.05V_CPU

H_INIT# 14

H_LOCK#5

H_CPURST#5

H_RS#0 5

H_RS#1 5

H_RS#2 5

H_TRDY#5

H_HIT# 5

H_HITM# 5

SYS_RST#16

+1.05V_CPU

H_PROCHOT#35

<Check list & CRB>

Layout note: L<0.5"

COMP0/2 Z=27.4ohm

COMP1/3 Z=54.9

<CRB & Design guide>

Layout Note:Connect from

SB and daisy chain to CPU

CORE VR.Not use T

connect.(SB/VR/CPU/NB)

ICH_DPRSTP#6,14,35

A1A: (9/22) Remove H_PWRGD_XDP

3

3

H_PWRGD14

2

CPU Thermal monitor

A1A:(9/29) change from MBCLK/MNDATA to 2ND_MBCLK/2ND_MBDATA

2ND_MBCLK28

2ND_MBDATA28

THERM_ALERT#16

+3V

Q31

2

+3V

2

+3V

RHU002N06

1

Q30

RHU002N06

1

R390 *0_4

R381 10K_4

3

3

A1A: (9/26) Add (U3/Pin6) PU to 3V

A1A: (10/30) remove, already PU in ICH8

CPU FAN

A1A: (9/26) Add CPUFAN#_ON to (U4/PIN1)

A1A: (10/23) Add Diode D36 and PU +5V for (U4/Pin1)

+5V

R383

10K_4

CPUFAN#_ON CPUFAN#_ON_R

D39

CPUFAN#28

PU/PD (ITP700)

XDP_TMS

R157 39_4

XDP_TDI

R150 150_4

XDP_TCK

R152 27_4

XDP_TRST#

R151 680_4

A1A: (9/4) <checklist>

Retain the termination resistors

on these signals even when ITP700Flex

is not implemented.

+5V

BAS316

FANPWR = 1.6*VSET

Thermal Trip

+1.05V_CPU

THERMTRIP#_PWR

2

1

+3V

R387

10K_4

U27

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

MAX6657

ADDRESS: 98H

FANSIG28

TH_FAN_POWER

TH_FAN_POWER

C99

10U_8

R385

200_6

LM86VCC

1

VCC

2

DXP

3

DXN

5

GND

<check list>

Layout Note:Routing 10:10 mils and away

from noise source with ground gard

+3V

C106

C96

*.01U_4

.01U_4

+3V

U28

1

4

G995

VIN2VO

/FON

VSET

R388

10K_4

R389

*10K_4

THERM_ALERT#_R

CPUFAN#_ON

3

5

GND

6

GND

7

GND

8

GND

A1A: (9/24) change FAN CONN (follow ZC3)

+1.05V_CPU

3

R183

Q18

R174

56.2_4

2

FDV301N

*10K_4

1

A1A: (9/26)

change name from THERM_SYS_PWR to SYS_SHDN#

Q19

2

MMBT3904

DELAY_VR_PWRGOOD6,16,35

+1.05V_CPU

1 3

R175 *0_4

<CRB & Design guide>

Layout Note: Thermal trip should connect to ICH8 & GMCH without T-ing

(ZS1 default NC)

PROJECT : ZU1

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

CPU(1 of 2)/FAN/Thermal

1

C466

.1U_4

H_THERMDA

C461

2200P_4

H_THERMDC

R70

10K_4

CN23

1

2

345

PTI_CWY030-B0G1Z

D19

*BAS316

C271 *1U_6

SYS_SHDN#34

PM_THRMTRIP#6,14

3 39Thursday, November 02, 2006

1A

5 4 3 2

CPU(Power)

VCC_CORE

U30C

A7

C499

C222

C517

D D

10U_8

C478

10U_8

C230

10U_8

C C

C516

10U_8

+

C198

330U_7343

A1A:(10/13) stuff C69, unstuff C68

(base on layout location)

<Check list>

Option1:330U*6(ESR=1.5m ohm aggregate , ESL=0.8nH/6) and 22U*20(ESR=3mohm typ/20 , ESL=0.6nH/20)

Option2:330U*6(ESR=1.5m ohm aggregate , ESL=1.8nH/6) and 22U*32(ESR=3mohm typ/32 , ESL=0.6nH/32)

B B

10U_8

C480

10U_8

C223

10U_8

C193

10U_8

C481

10U_8

C482

10U_8

C500

10U_8

C504

10U_8

C483

10U_8

C514

10U_8

C503

10U_8

C192

10U_8

C479

10U_8

10U_8

C502

C171

10U_8

10U_8

C501

C231

10U_8

10U_8

C173

C484

10U_8

10U_8

CH61001ME96

CAP CHIP 10UF 6.3V(+-20%,X5R,0805)

+

+

C217

C197

*330U_7343

330U_7343

C515

C513

10U_8

C191

10U_8

DESIGN GUIDE

CHANGE FROM 22UF *20 TO 10UF *32

10U_8

C172

10U_8

C221

10U_8

C512

10U_8

C498

10U_8

C521

10U_8

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

.

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

CPU_G21

CPU_V6

+VCCA_PROC

<CRB>

R for test only

R108 0_4

R159 0_4

H_VID0 35

H_VID1 35

H_VID2 35

H_VID3 35

H_VID4 35

H_VID5 35

H_VID6 35

<REV.NO. 0.5/REF.NO.19343>

Ivcc Max 52A

Ivccp Max 6A(VCCP supply before Vcc stable)

Max 2A(VCCP supply after Vcc stable)

Ivcca Max 130mA

+1.05V_CPU

C250

.1U_6

+

VCC_CORE

R156

100_6

R160

100_6

C154

C153

.1U_6

.1U_6

R176 0_1210

C280

<Check list>

330U_7343

ESR=12m ohm

<CRB>

.01U near to B26 ball

R386 0_6

C471

C472

10U_8

.01U_4

<Demo board>

Routing 27.4ohm with 50mils spacing

PU/PD near to CPU 1"

C251

.1U_6

+1.05V+1.05V_CPU

+1.5V

VCCSENSE35

VSSSENSE35

C249

.1U_6

C152

.1U_6

1

U30D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Merom Ball-out Rev 1a

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

A A

PROJECT : ZU1

Size Document Number Rev

2

Date: Sheet of

Quanta Computer Inc.

CPU(2 of 2)

4 39Thursday, November 02, 2006

1

1A

5

4

3

2

1

NB(HOST)

M10

N12

P13

W10

AD12

AE3

AD9

AC9

AC7

AC14

AD11

AC11

AB2

AD7

AB1

AC6

AE2

AC5

AG3

AJ9

AH8

AJ14

AE9

AE11

AH12

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

AH13

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

N9

H5

K9

M2

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

Y3

B3

C2

W1

W2

B6

E5

B9

A9

U29A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

HOST

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_D#[63:0]3

+1.05V_GMCH

D D

C C

B B

A A

R86

221_4

R85

100_4

R95

24.9_4

+1.05V_GMCH

R87

54.9_4

+1.05V_GMCH

R88

54.9_4

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

C137

<check list>

0.1U close to B3

.1U_4

<check list>

10:20 mils(Width:Spacing)

<check list>

Impedance 55ohm

<check list>

Impedance 55ohm

+1.05V_GMCH

R392

1K_4

R391

2K_4

C473

.1U_4

H_CPURST#3

<check list>

0.1U close to B9

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_AVREF

H_DVREF

H_A#[35:3]3

H_A#[35:32] are not supported in

Calero Interposer

Crestline support 36 bit address

H_ADS# 3

H_ADSTB0#3

H_ADSTB1#3

H_BNR# 3

H_BPRI# 3

H_BREQ#03

H_DEFER#3

H_DBSY#3

CLK_MCH_BCLK2

CLK_MCH_BCLK#2

H_DPWR#3

H_DRDY#3

H_HIT# 3

H_HITM# 3

H_LOCK#3

H_TRDY#3

H_DINV#[3:0]3

H_DSTBN#[3:0]3

H_DSTBP#[3:0]3

H_REQ#[4:0]3

H_RS#[2:0]3H_CPUSLP#3

PROJECT : ZU1

Quanta Computer Inc.

A1A:(9/20) remove R74 (0 ohm)

5

4

3

2

Size Document Number Rev

GMCH HOST(1 of 7)

Date: Sheet of

5 39Thursday, November 02, 2006

1

1A

5

MCH_RSVD1

T39

MCH_RSVD2

T46

MCH_RSVD3

T36

MCH_RSVD4

T43

MCH_RSVD5

T9

MCH_RSVD6

T12

MCH_RSVD7

T8

MCH_RSVD8

T11

MCH_RSVD9

T10

MCH_RSVD10

T45

MCH_RSVD11

T42

MCH_RSVD12

T38

MCH_RSVD13

M_RCOMP#

5

T40

T21

C157 .1U_4

T7

T103

T84

T86

T13

T25

T83

T82

T30

T15

T33

T17

T44

T18

T85

T98

T51

T95

T96

T90

T91

T89

T88

T87

T24

T26

T19

T27

T22

T32

T23

T20

T28

T29

T34

R158 0_4

R424 0_4

R147 0_4

R115 100_4

R116 *0_4

R149 0_4

T105

T106

T107

T102

T99

T80

T78

T76

T75

T77

T81

T104

T100

T101

T97

T79

R105

20_4

MCH_RSVD14

MCH_RSVD20

MCH_RSVD21

MCH_RSVD22

MCH_RSVD23

MCH_RSVD24

MCH_RSVD25

MCH_RSVD26

MCH_RSVD27

MCH_RSVD28

MCH_RSVD29

MCH_RSVD30

MCH_RSVD31

MCH_RSVD34

MCH_RSVD35

MCH_RSVD36

MCH_RSVD37

MCH_RSVD38

MCH_RSVD39

MCH_RSVD40

MCH_RSVD41

MCH_RSVD42

MCH_RSVD43

MCH_RSVD44

MCH_RSVD45

MCH_CFG_3

MCH_CFG_4

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_10

MCH_CFG_11

MCH_CFG_14

MCH_CFG_15

MCH_CFG_17

MCH_CFG_18

PM_BMBUSY#_R

ICH_DPRSTP#_R

PM_EXTTS#1_R

RST_IN#_MCH

PM_THRMTRIP#_GMCH

PM_DPRSLPVR_GMCH

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

+1.8VSUS_GMCH

M_RCOMP

D D

M_A_A1412,13

M_B_A1412,13

C C

MCH_BSEL02

MCH_BSEL12

MCH_BSEL22

MCH_CFG_511

MCH_CFG_911

MCH_CFG_1211

MCH_CFG_1311

MCH_CFG_1611

MCH_CFG_1911

MCH_CFG_2011

B B

A A

PM_BMBUSY#16

ICH_DPRSTP#3,14,35

PM_EXTTS#013

PM_EXTTS#113

DELAY_VR_PWRGOOD3,16,35

PLTRST#_NB15

PM_THRMTRIP#3,14

PM_DPRSLPVR16,35

R106

20_4

AR12

AR13

AM12

AN13

AR37

AM36

AL36

AM37

BJ20

BK22

BF19

BH20

BK18

BJ18

BF23

BG23

BC23

BD24

BJ29

BE24

BH39

AW20

BK20

AW49

AV20

BJ51

BK51

BK50

BL50

BL49

P36

P37

R35

N35

J12

D20

H10

B51

C48

D47

B44

C44

A35

B37

B36

B34

C34

P27

N27

N24

C21

C23

F23

N23

G23

J20

C20

R24

L23

J23

E23

E20

K23

M20

M24

L32

N33

L35

G41

L39

L36

J36

N20

G36

BL3

BL2

BK1

BJ1

E1

A5

C51

B50

A50

A49

BK2

U29B

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BM_BUSY#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

CRESTLINE_1p0

+3V

4

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

DDR MUXINGCLK

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

CFGRSVD

PM

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

GRAPHICS VID

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

ME

NC

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

MISC

TEST_1

TEST_2

R423 10K_4

R421 10K_4

R419 10K_4

4

AV29

BB23

BA25

AV23

AW30

BA23

AW25

AW23

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

BL15

BK14

BK31

BL31

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

R32

+1.8VSUS_GMCH

CLK_MCH_OE#

PM_EXTTS#0

PM_EXTTS#1

M_CLK_DDR013

M_CLK_DDR113

M_CLK_DDR313

M_CLK_DDR413

M_CLK_DDR#013

M_CLK_DDR#113

M_CLK_DDR#313

M_CLK_DDR#413

M_CKE012,13

M_CKE112,13

M_CKE312,13

M_CKE412,13

M_CS#012,13

M_CS#112,13

M_CS#212,13

M_CS#312,13

M_ODT012,13

M_ODT112,13

M_ODT212,13

M_ODT312,13

M_RCOMP

M_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SMDDR_VREF_MCH

R84 *10K_6

R82 *10K_6

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

T37

T93

T92

T94

T41

+1.25V_CL_VREF

CLK_MCH_OE#

GMCH_TEST1

GMCH_TEST2

R133 1K_4

SMDDR_VREF

R83 0_6

+1.8VSUS_GMCH

DREFCLK2

DREFCLK#2

DREFSSCLK2

DREFSSCLK#2

CLK_PCIE_3GPLL2

CLK_PCIE_3GPLL#2

DMI_TXN[3:0]15

DMI_TXP[3:0]15

DMI_RXN[3:0]15

DMI_RXP[3:0]15

R411 1.3K_6

CL_CLK016

CL_DATA016

MPWROK16

CL_RST#016

SDVO_CTRLCLK21

SDVO_CTRLDATA21

CLK_MCH_OE#2

MCH_ICH_SYNC#16

R143 0_4

R129 20K_4

R114

3.01K_4

R123

1K_4

3

INT_LVDS_EDIDCLK20

INT_LVDS_EDIDDATA20

INT_LVDS_DIGON20

+3V

INT_CRT_DDCCLK19

INT_CRT_DDCDAT19

SM_RCOMP_VOH

C207

.01U_4

SM_RCOMP_VOL

C194

.01U_4

3

INT_LVDS_PWM20

INT_LVDS_BLON20

INT_TXLCLKOUT-20

INT_TXLCLKOUT+20

C246

.1U_4

INT_TXLOUT0-20

INT_TXLOUT1-20

INT_TXLOUT2-20

INT_TXLOUT0+20

INT_TXLOUT1+20

INT_TXLOUT2+20

INT_TV_COMP20

INT_TV_Y/G20

INT_TV_C/R20

INT_CRT_BLU19

INT_CRT_GRN19

INT_CRT_RED19

INT_HSYNC19

INT_VSYNC19

+3V

R148 2.4K_4

R417 2.2K_4

R415 2.2K_4

+1.25V_AXD

R155

1K_4

R161

392_6

C177

2.2U_6

C180

2.2U_6

R146 10K_4

R154 10K_4

TV_DCONSEL_0

TV_DCONSEL_1

R153 *0_4

R145 *0_4

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

R416 30_4

R418 30_4

R117 150_4

R118 150_4

R113 150_4

R119 150_4

R122 150_4

R126 150_4

LVDS_IBG

T47

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

HSYNC1

CRTIREF

VSYNC1

U29C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

CRESTLINE_1p0

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

2

N43

PEG_COMPI

M43

PEG_COMPO

J51

PEG_RX#_0

L51

PEG_RX#_1

N47

PEG_RX#_2

T45

PEG_RX#_3

T50

PEG_RX#_4

U40

PEG_RX#_5

Y44

PEG_RX#_6

Y40

PEG_RX#_7

AB51

PEG_RX#_8

W49

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

C_PEG_TXP0

C_PEG_TXN0

C_PEG_TXP1

C_PEG_TXN1

C_PEG_TXP2

C_PEG_TXN2

C_PEG_TXP3

C_PEG_TXN3

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

C270 .1U_4

C272 .1U_4

C278 .1U_4

C277 .1U_4

C276 .1U_4

C275 .1U_4

C273 .1U_4

C274 .1U_4

LVDS

TV VGA

PCI-EXPRESS GRAPHICS

EXP_A_COMPX

PEG_RXN1

PEG_RXP1

C_PEG_TXN0

C_PEG_TXN1

C_PEG_TXN2

C_PEG_TXN3

C_PEG_TXP0

C_PEG_TXP1

C_PEG_TXP2

C_PEG_TXP3

1

R164 24.9_4

PEG_RXN121

PEG_RXP121

+VCC_PEG

SDVOB_R+21

SDVOB_R-21

SDVOB_G+21

SDVOB_G-21

SDVOB_B+21

SDVOB_B-21

SDVOB_CLK+21

SDVOB_CLK-21

PROJECT : ZU1

Size Document Number Rev

2

Date: Sheet of

Quanta Computer Inc.

GMCH DMI/VIDEO(2 of 7)

6 39Thursday, November 02, 2006

1

1A

5

NB(Memory controller)

4

3

2

1

M_A_DQ[63:0]13

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BD8

AY9

BG10

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT9

AN9

AM9

AN11

U29D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRESTLINE_1p0

BB19

SA_BS_0

BK19

SA_BS_1

BF29

SA_BS_2

BL17

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

DDR SYSTEM MEMORY A

SA_WE#

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

TP_SA_RCVEN#

M_A_BS#012,13

M_A_BS#112,13

M_A_BS#212,13

M_A_CAS#12,13

M_A_DM[7:0]13

M_A_DQS[7:0]13

M_A_DQS#[7:0]13

M_A_A[13:0]12,13

M_A_RAS#12,13

T31

M_A_WE#12,13

M_B_DQ[63:0]13

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BL9

BK5

BL5

BK9

BK10

BJ8

BJ6

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

U29E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRESTLINE_1p0

AY17

SB_BS_0

BG18

SB_BS_1

BG36

SB_BS_2

BE17

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

TP_SB_RCVEN#

M_B_BS#012,13

M_B_BS#112,13

M_B_BS#212,13

M_B_CAS#12,13

M_B_DM[7:0]13

M_B_DQS[7:0]13

M_B_DQS#[7:0]13

M_B_A[13:0]12,13

M_B_RAS#12,13

T14

M_B_WE#12,13

A A

PROJECT : ZU1

Quanta Computer Inc.

Size Document Number Rev

MCH DDR(3 of 7)

5

4

3

2

Date: Sheet of

7 39Thursday, November 02, 2006

1

1A

5 4 3

NB(Power-1)

+1.05V_VCC_GMCH

U29G

AT35

VCC_1

AT34

VCC_2

AH28

VCC_3

AC32

VCC_5

D D

R127 0_4

+1.8VSUS

C210

330U_7343

C C

B B

A A

.1U_4

+1.05V_VCC_GMCH_VCC13

C215

+

C144

22U_8

C232

22U_8

AC31

AK32

AJ31

AJ28

AH32

AH31

AH29

AF32

R30

+1.8VSUS_GMCH

AU32

AU33

AU35

AV33

AW33

AW35

AY35

BA32

BA33

BA35

BB33

BC32

BC33

BC35

BD32

BD35

BE32

BE33

BE35

BF33

BF34

BG32

BG33

BG35

BH32

BH34

BH35

BJ32

BJ33

BJ34

BK32

BK33

BK34

BK35

BL33

AU30

+VGFX_CORE_INT

R20

T14

W13

W14

Y12

AA20

AA23

AA26

AA28

AB21

AB24

AB29

AC20

AC21

AC23

AC24

AC26

AC28

AC29

AD20

AD23

AD24

AD28

AF21

AF26

AA31

AH20

AH21

AH23

AH24

AH26

AD31

AJ20

AN14

VCC_4

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_AXG_1

VCC_AXG_2

VCC_AXG_3

VCC_AXG_4

VCC_AXG_5

VCC_AXG_6

VCC_AXG_7

VCC_AXG_8

VCC_AXG_9

VCC_AXG_10

VCC_AXG_11

VCC_AXG_12

VCC_AXG_13

VCC_AXG_14

VCC_AXG_15

VCC_AXG_16

VCC_AXG_17

VCC_AXG_18

VCC_AXG_19

VCC_AXG_20

VCC_AXG_21

VCC_AXG_22

VCC_AXG_23

VCC_AXG_24

VCC_AXG_25

VCC_AXG_26

VCC_AXG_27

VCC_AXG_28

VCC_AXG_29

VCC_AXG_30

VCC_AXG_31

VCC_AXG_32

VCC_AXG_33

VCC_AXG_34

VCC CORE

POWER

VCC SMVCC GFX

VCC_AXG_NCTF_1

VCC_AXG_NCTF_2

VCC_AXG_NCTF_3

VCC_AXG_NCTF_4

VCC_AXG_NCTF_5

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_29

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

VCC GFX NCTF

VCC_AXG_NCTF_55

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57

VCC_AXG_NCTF_58

VCC_AXG_NCTF_59

VCC_AXG_NCTF_60

VCC_AXG_NCTF_61

VCC_AXG_NCTF_62

VCC_AXG_NCTF_63

VCC_AXG_NCTF_64

VCC_AXG_NCTF_65

VCC_AXG_NCTF_66

VCC_AXG_NCTF_67

VCC_AXG_NCTF_68

VCC_AXG_NCTF_69

VCC_AXG_NCTF_70

VCC_AXG_NCTF_71

VCC_AXG_NCTF_72

VCC_AXG_NCTF_73

VCC_AXG_NCTF_74

VCC_AXG_NCTF_75

VCC_AXG_NCTF_76

VCC_AXG_NCTF_77

VCC_AXG_NCTF_78

VCC_AXG_NCTF_79

VCC_AXG_NCTF_80

VCC_AXG_NCTF_81

VCC_AXG_NCTF_82

VCC_AXG_NCTF_83

VCC_SM_LF1

VCC_SM_LF2

VCC_SM_LF3

VCC_SM_LF4

VCC_SM_LF5

VCC_SM_LF6

VCC_SM_LF7

VCC SM LF

T17

T18

T19

T21

T22

T23

T25

U15

U16

U17

U19

U20

U21

U23

U26

V16

V17

V19

V20

V21

V23

V24

Y15

Y16

Y17

Y19

Y20

Y21

Y23

Y24

Y26

Y28

Y29

AA16

AA17

AB16

AB19

AC16

AC17

AC19

AD15

AD16

AD17

AF16

AF19

AH15

AH16

AH17

AH19

AJ16

AJ17

AJ19

AK16

AK19

AL16

AL17

AL19

AL20

AL21

AL23

AM15

AM16

AM19

AM20

AM21

AM23

AP15

AP16

AP17

AP19

AP20

AP21

AP23

AP24

AR20

AR21

AR23

AR24

AR26

V26

V28

V29

Y31

AW45

BC39

BE39

BD17

BD4

AW8

AT6

+VGFX_CORE_INT

VCCSM_LF1

VCCSM_LF2

VCCSM_LF3

VCCSM_LF4

VCCSM_LF5

VCCSM_LF6

VCCSM_LF7

R136 10_4

+1.05V

A1A(10/23): Short R116

+1.05V

C145

.1U_4

VCCGFPLLOW

ADD 10ohm

THEY ONLY USE IN UMA (GM OR GML)

A1A:(9/26) Change +VCC_CFXCORE_INT to +1.05V

A1A(10/23): Short R115,R117

+

C464

330U_7343

C147

.1U_4

D13 PDZ5.6B

+

C95

C225

330U_7343

22U_8

C156

+

C463

.47U_6

330U_7343

+1.05V

C188

22U_8

C158

C136

.22U_4

.22U_4

21

C199

.22U_4

+VGFX_CORE_INT

C150

1U_6

C179

.22U_4

C238

.47U_6

+1.05V_VCC_GMCH

C208

C216

.1U_4

.22U_4

C182

C164

22U_8

10U_8

C206

.22U_4

C224

C252

1U_6

1U_6

2

C186

.1U_4

+1.05V_VCC_GMCH+3V_VCCSYNC

C151

.1U_4

C178

.1U_4

C155

.1U_4

C189

.1U_4

U29F

AB33

AB36

AB37

AC33

AC35

AC36

AD35

AD36

AF33

AF36

AH33

AH35

AH36

AH37

AJ33

AJ35

AK33

AK35

AK36

AK37

AD33

AJ36

AM35

AL33

AL35

AA33

AA35

AA36

AP35

AP36

AR35

AR36

Y32

Y33

Y35

Y36

Y37

T30

T34

T35

U29

U31

U32

U33

U35

U36

V32

V33

V36

V37

AL24

AL26

AL28

AM26

AM28

AM29

AM31

AM32

AM33

AP29

AP31

AP32

AP33

AL29

AL31

AL32

AR31

AR32

AR33

CRESTLINE_1p0

VCC_NCTF_1

VCC_NCTF_2

VCC_NCTF_3

VCC_NCTF_4

VCC_NCTF_5

VCC_NCTF_6

VCC_NCTF_7

VCC_NCTF_8

VCC_NCTF_9

VCC_NCTF_10

VCC_NCTF_11

VCC_NCTF_12

VCC_NCTF_13

VCC_NCTF_14

VCC_NCTF_15

VCC_NCTF_16

VCC_NCTF_17

VCC_NCTF_18

VCC_NCTF_19

VCC_NCTF_20

VCC_NCTF_21

VCC_NCTF_22

VCC_NCTF_23

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

VCC_NCTF_27

VCC_NCTF_28

VCC_NCTF_29

VCC_NCTF_30

VCC_NCTF_31

VCC_NCTF_32

VCC_NCTF_33

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

VCC_NCTF_37

VCC_NCTF_38

VCC_NCTF_39

VCC_NCTF_40

VCC_NCTF_41

VCC_NCTF_42

VCC_NCTF_43

VCC_NCTF_44

VCC_NCTF_45

VCC_NCTF_46

VCC_NCTF_47

VCC_NCTF_48

VCC_NCTF_49

VCC_NCTF_50

VCC_AXM_NCTF_1

VCC_AXM_NCTF_2

VCC_AXM_NCTF_3

VCC_AXM_NCTF_4

VCC_AXM_NCTF_5

VCC_AXM_NCTF_6

VCC_AXM_NCTF_7

VCC_AXM_NCTF_8

VCC_AXM_NCTF_9

VCC_AXM_NCTF_10

VCC_AXM_NCTF_11

VCC_AXM_NCTF_12

VCC_AXM_NCTF_13

VCC_AXM_NCTF_14

VCC_AXM_NCTF_15

VCC_AXM_NCTF_16

VCC_AXM_NCTF_17

VCC_AXM_NCTF_18

VCC_AXM_NCTF_19

PROJECT : ZU1

VSS NCTF

VCC NCTF

POWER

VCC AXM NCTF

1

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS_NCTF_15

VSS_NCTF_16

VSS_NCTF_17

VSS_NCTF_18

VSS_NCTF_19

VSS_NCTF_20

VSS_NCTF_21

VSS_SCB1

VSS_SCB2

VSS_SCB3

VSS_SCB4

VSS_SCB5

VSS_SCB6

VSS SCBVCC AXM

VCC_AXM_1

VCC_AXM_2

VCC_AXM_3

VCC_AXM_4

VCC_AXM_5

VCC_AXM_6

VCC_AXM_7

T27

T37

U24

U28

V31

V35

AA19

AB17

AB35

AD19

AD37

AF17

AF35

AK17

AM17

AM24

AP26

AP28

AR15

AR19

AR28

A3

B2

C1

BL1

BL51

A51

AT33

AT31

AK29

AK24

AK23

AJ26

AJ23

+1.05V

Quanta Computer Inc.

CRESTLINE_1p0

Size Document Number Rev

GMCH Power-1(4 of 7)

3

2

Date: Sheet of

8 39Thursday, November 02, 2006

1

1A

5

NB(Power-2)

IND CHIP 10UH(20%,100MA,LB2012T100MR)

L53 10UH_8

+1.25V

+

C527

C262

470U_7343

D D

L25 10UH_8

+1.25V

EMI FILTER BKP1608HS181-T(180,1.5A)

+1.25V

C C

C465 22U_8

L51

BKP1608HS181-T_6

+3V

B B

C485

22U_8

C492

10U_8

R137 0_6

+1.5V

A A

A1A:(10/18)

INTEL CRB VCCD_QDAC Filter Modification:

change L13 to R258(100ohm),

change R145(*0 ohm) to C247(1uF)

5

.1U_4

+

C528

C264

470U_7343

.1U_4

L49 BKP1608HS181-T_6

L50 BKP1608HS181-T_6

V1.25M_MPLL_RC

+1.25V

R125 100_6

+3V_TV_DAC

C489

.1U_4

C488

.1U_4

C494

.1U_4

C196

.1U_4

C143

+

100U_7343

C487

22N_4

C493

22N_4

C495

22N_4

C214

22N_4

C519

.1U_4

R130 0_6

+3V

<FAE>

INT VGA disable

VCCSYNC connect to GND

L18 BKP1608HS181-T_6

+3V

C469

22U_8

R384

0.5_6

R404

*0_4

R402

*0_4

R401

*0_4

C511

22N_4

R128 0_6

C138

.1U_4

C133

.1U_4

R124 0_6

C507

1U_6

+3V_TV_DAC

R120 0_6

+1.25V

C165

*22U_8

4

+3V_VCCSYNC

C205

.1U_4

C226

*22U_8

R166 0_8

+3V

C159

4.7U_6

C200

C203

*1U_6

*1U_6

R131 *0_4

R138 0_6

+1.25V

L24 BKP1608HS181-T_6

+1.25V

+V1.25S_PEGPLL_FB

C263

10U_8

R163 0_6

+1.8VSUS

4

C522

C220

.1U_4

22N_4

C505

C508

.1U_4

22N_4

C176

22U_8

C213

22U_8

R81 0_6

R412

*0_4

R132

*0_4

C244

1000P_4

C266

.1U_4

C168

1U_6

C201

.1U_4

C128

.1U_4

R168

1_8

C257

1U_6

3

CRT/TV Disable/Enable guideline

EnableBall EnableDisable DisableBall

VCCA_CRT

3.3V GND

1.5V

3.3V

3.3V

AW18

AV19

AU19

AU18

AU17

AT22

AT21

AT19

AT18

AT17

AR17

AR16

BC29

BB29

GND

GND

GND

GND

J32

A33

B33

A30

B32

B49

H49

AL2

AM2

A41

B41

K50

K49

U51

C25

B25

C27

B27

B28

A28

M32

L29

N28

AN2

U48

J41

H42

U29H

VCCSYNC

VCCA_CRT_DAC_1

VCCA_CRT_DAC_2

VCCA_DAC_BG

VSSA_DAC_BG

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

VCCA_LVDS

VSSA_LVDS

VCCA_PEG_BG

VSSA_PEG_BG

VCCA_PEG_PLL

VCCA_SM_1

VCCA_SM_2

VCCA_SM_3

VCCA_SM_4

VCCA_SM_5

VCCA_SM_7

VCCA_SM_8

VCCA_SM_9

VCCA_SM_10

VCCA_SM_11

VCCA_SM_NCTF_1

VCCA_SM_NCTF_2

VCCA_SM_CK_1

VCCA_SM_CK_2

VCCA_TVA_DAC_1

VCCA_TVA_DAC_2

VCCA_TVB_DAC_1

VCCA_TVB_DAC_2

VCCA_TVC_DAC_1

VCCA_TVC_DAC_2

VCCD_CRT

VCCD_TVDAC

VCCD_QDAC

VCCD_HPLL

VCCD_PEG_PLL

VCCD_LVDS_1

VCCD_LVDS_2

CRESTLINE_1p0

3

VCCD_CRT

VCCDQ_CRT

VCCA_A_TVO

VCCA_B_TVO VCC_SYNC

+3V_VCCA_CRT_DAC

+3V_VCCA_DAC_BG

+1.25V_VCCA_DPLLA

+1.25V_VCCA_DPLLB

+1.25VM_VCCA_HPLL

+1.25VM_VCCA_MPLL

+1.8VSUS_VCC_TX_LVDS

+3V_VCCA_PEG_BG

+1.25V_VCCD_PEG_PLL

+1.25VM_VCCA_SM

+1.25VM_VCCA_SM_CK

+1.5V_VCCD_CRT

+1.5V_VCCD_TVDAC

+1.5V_VCCD_QDAC

+1.25VM_MCH_VCCD_HPLL

+1.25V_VCCD_PEG_PLL

C259

.1U_4

C268

.1U_4

+1.8V_VCCD_LVDS

C243

*10U_8

VCCA_C_TVO

VCCD_TVO

VCCABG_DAC

VSSABG_DAC

+1.05V

+3V

GND

3.3V

1.5V1.5V

1.5V

GND

3.3V

GND

GND

GND

3.3V

CRTPLLA PEGA SMTV

VTT

VCC_AXD_1

VCC_AXD_2

VCC_AXD_3

VCC_AXD_4

VCC_AXD_5

AXD

VCC_AXD_6

VCC_AXD_NCTF

VCC_AXF_1

POWER

VCC_AXF_2

VCC_AXF_3

AXF

VCC_DMI

VCC_SM_CK_1

VCC_SM_CK_2

VCC_SM_CK_3

VCC_SM_CK_4

SM CK

VCC_TX_LVDS

A CK A LVDS

VCC_HV_1

VCC_HV_2

HV

VCC_PEG_1

VCC_PEG_2

VCC_PEG_3

VCC_PEG_4

PEG

VCC_PEG_5

VCC_RXR_DMI_1

VCC_RXR_DMI_2

DMI

D TV/CRTLVDS

VTTLF

D8 PDZ5.6B

2 1

<CRB>

+1.25V AND +1.25M shall be

+1.5V for Calero Interposer