A

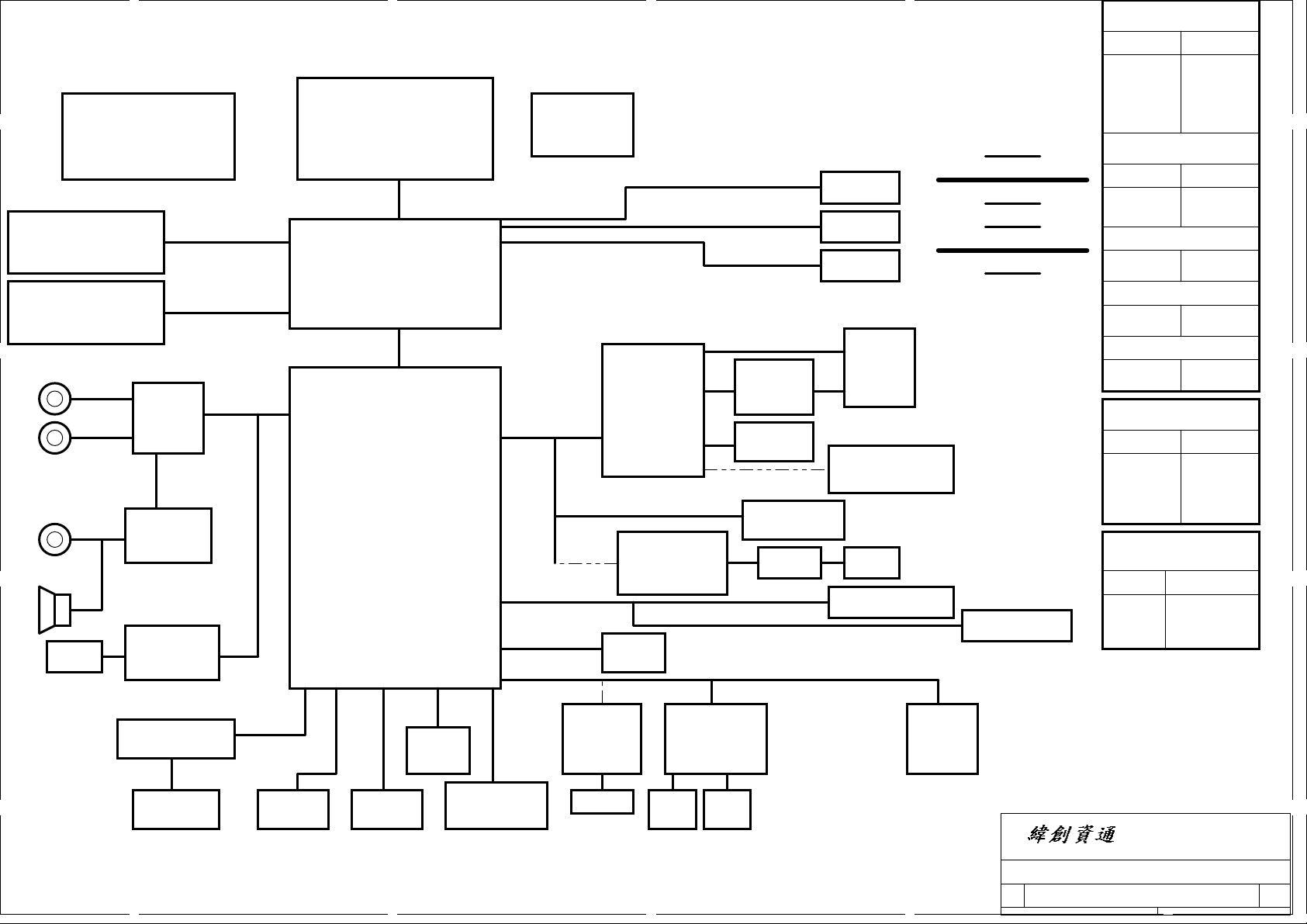

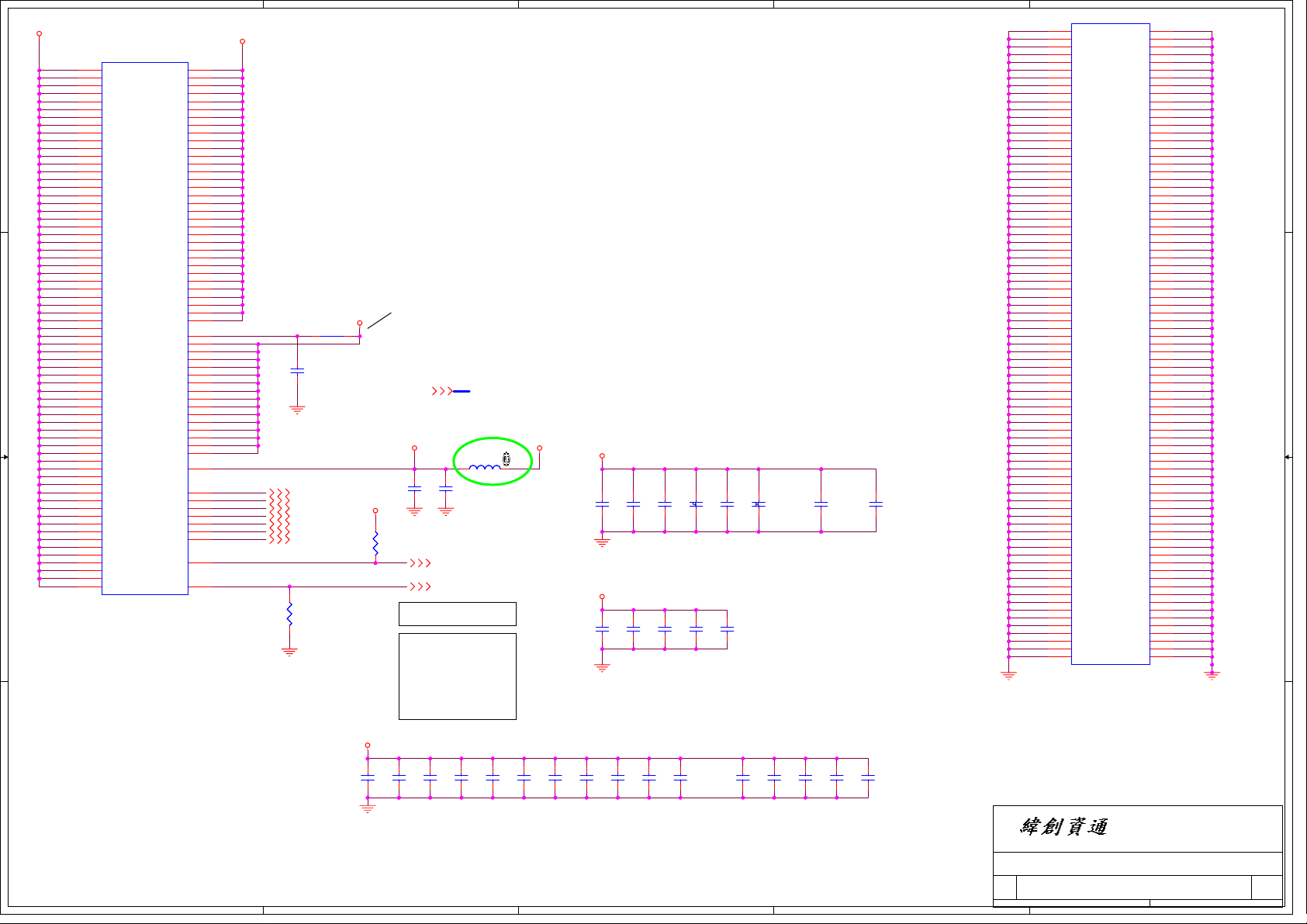

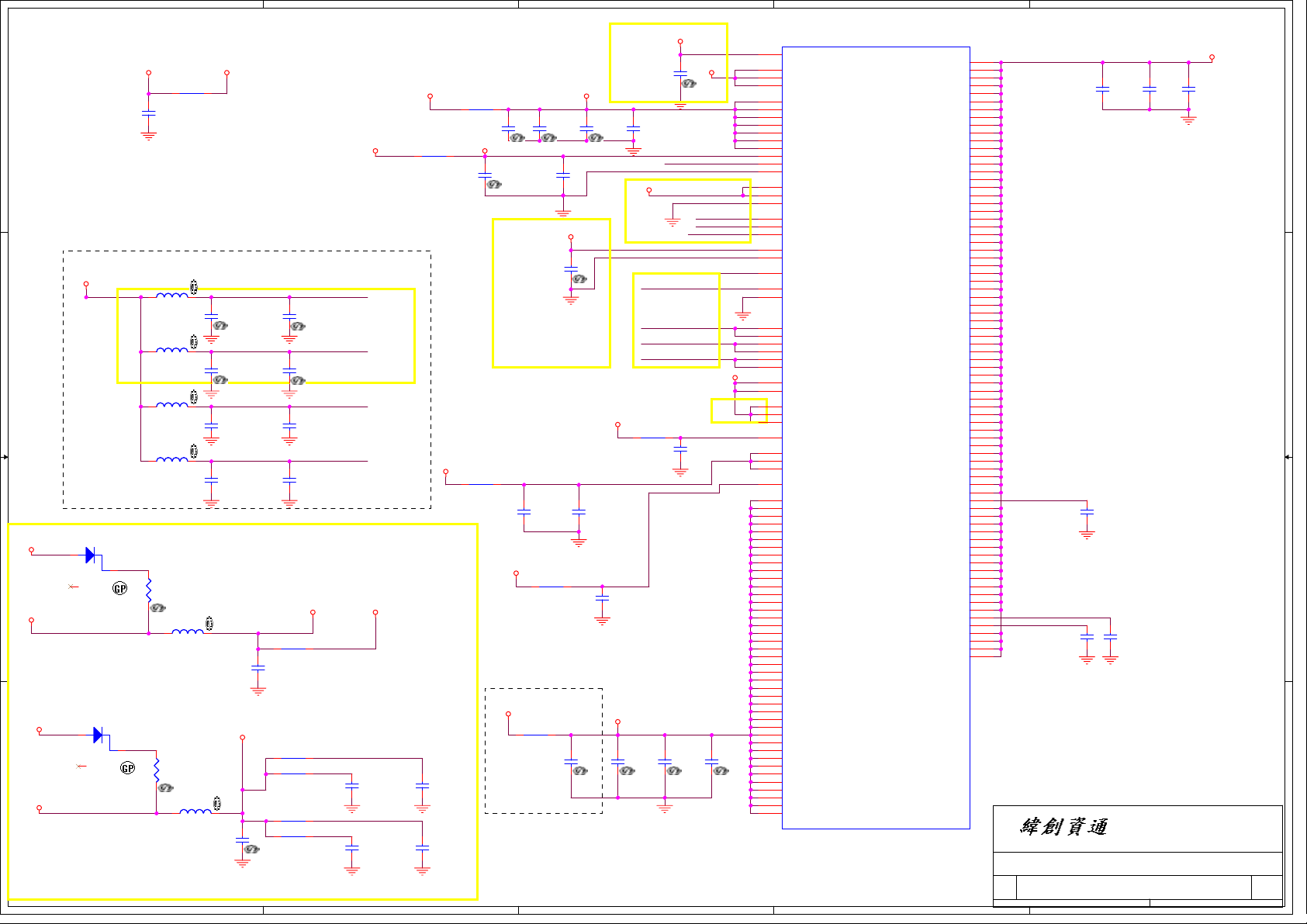

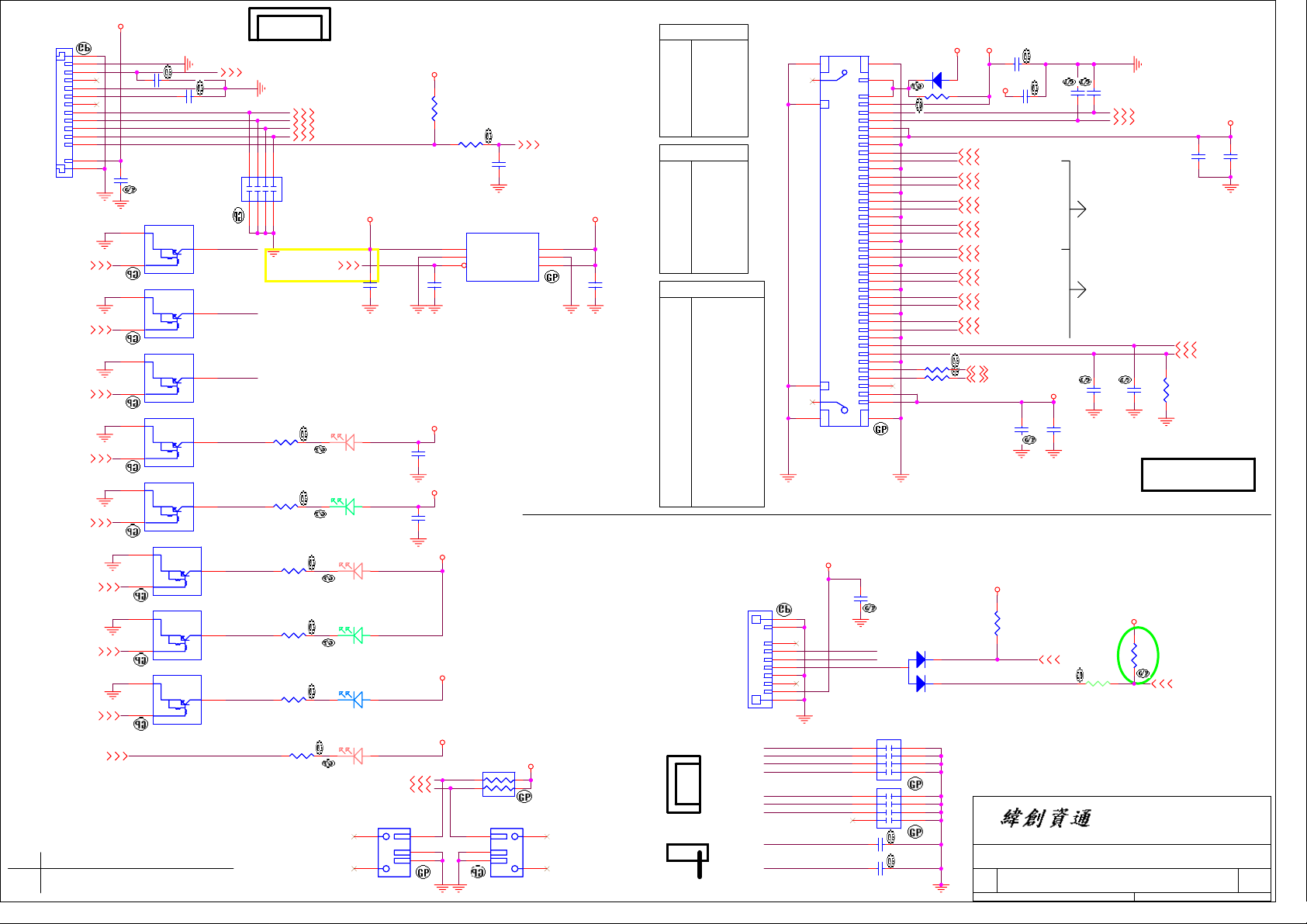

AG1 Block Diagram

4 4

DDR2

CLK GEN.

ICS954305D

(IDT CV155)

3 4, 5

533/667MHz

533/667 MHz

11,12

DDR2

533/667MHz

533/667 MHz

3 3

Line In

29

29

MIC In

Line Out

(SPDIF)

29

INT.SPKR

2 2

29

RJ11

11,12

Codec

ALC883

28

OP AMP

G1421B

29

MODEM

MDC Card

AZALIA

21

Mobile CPU

Yonah 478

Celeron M

HOST BUS

Calistoga

DMI I/F

ICH7-M

B

400/533/667MHz

6,7,8,9,10

100MHz

15,16,17,18

G792

PCI BUS

PCIEx1

SPI I/F

LPC BUS

C

19

TI

PCI 7412

CARDBUS

1394

CardReader

24,25

LAN

10/100

BCM4401-E

SPI

Flash

D

Project code: 91.4A901.001

PCB P/N : 55.4A903.XXX

REVISION : 05225-1

(Hannstar, GCE)

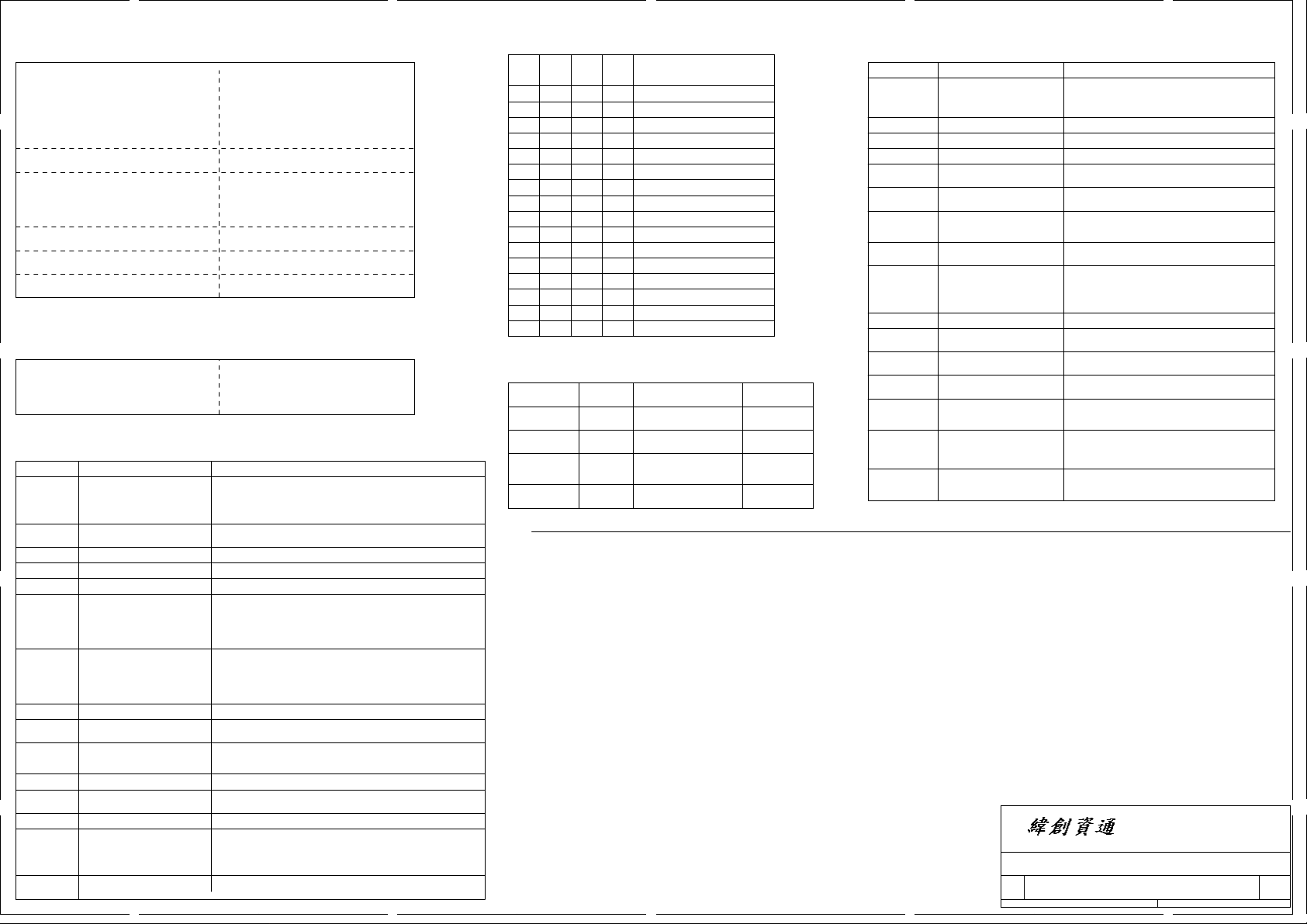

PCB STACKUP

TOP

14

13

14

23

27

VCC

S

S

GND

BUTTOM

26

26

Giga LAN

BCM5798

PCMCIA I/F

PWR SW

TSP2220A

22

LVDS

RGB CRT

27

1394

CONN

26

Mini-PCI

TV Tuner

TXFM

23

TVO

14"WSXGA+

LCD

CRT

PCMCIA

SLOT

Support

TypeII

MS/MS Pro/xD/

MMC/SD/SDIO

6 in 1

30

RJ45

Mini Card*2

802.11A/B/G

22

E

SYSTEM DC/DC

TPS51120

INPUTS

DCBATOUT

SYSTEM DC/DC

INPUTS OUTPUTS

DCBATOUT

TPS51100

APL5332KAC

3D3V_S5 2D5V_S0

APL5912-U

3D3V_S5 1D5V_S0

MAXIM CHARGER

MAX8725+Max1773

DCBATOUT

CPU DC/DC

ISL6262

INPUTS

DCBATOUT

OUTPUTS

5V_S5

3V_S5

MAX8743EE

1D05V_S0

1D8V_S3

DDR_VREF1D8V_S3

OUTPUTSINPUTS

BT+

18V 4.0A

UP+5V

5V 100mA

OUTPUTS

VCC_CORE

0~1.3V

48A

41

42

44

44

44

43

39,40

PCI Express

New card

1 1

PWR SW

TPS2231

30

30

HDD

SATA

20

PATA

CDROM

USB

3 PORT

MINI USB

Blue-tooth

18

21

21

NS

87392

FIR

32

32

Touch

Pad

SIO

KBC

HD64F2111BVC

INT.

KB

33 33

LPC

DEBUG

CONN.

3431

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

AG1 -1

AG1 -1

AG1 -1

of

of

of

145Monday, January 09, 2006

145Monday, January 09, 2006

145Monday, January 09, 2006

A

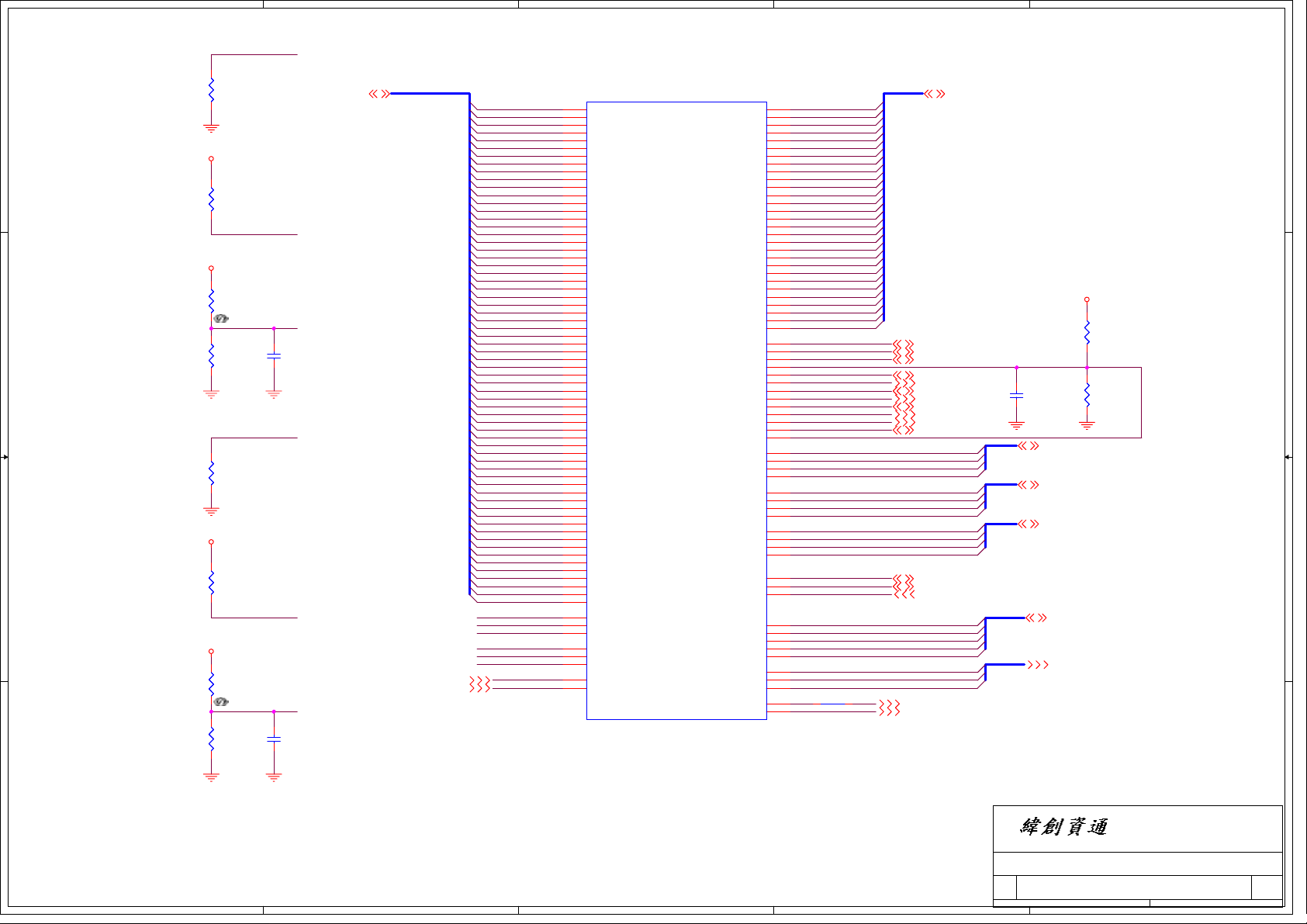

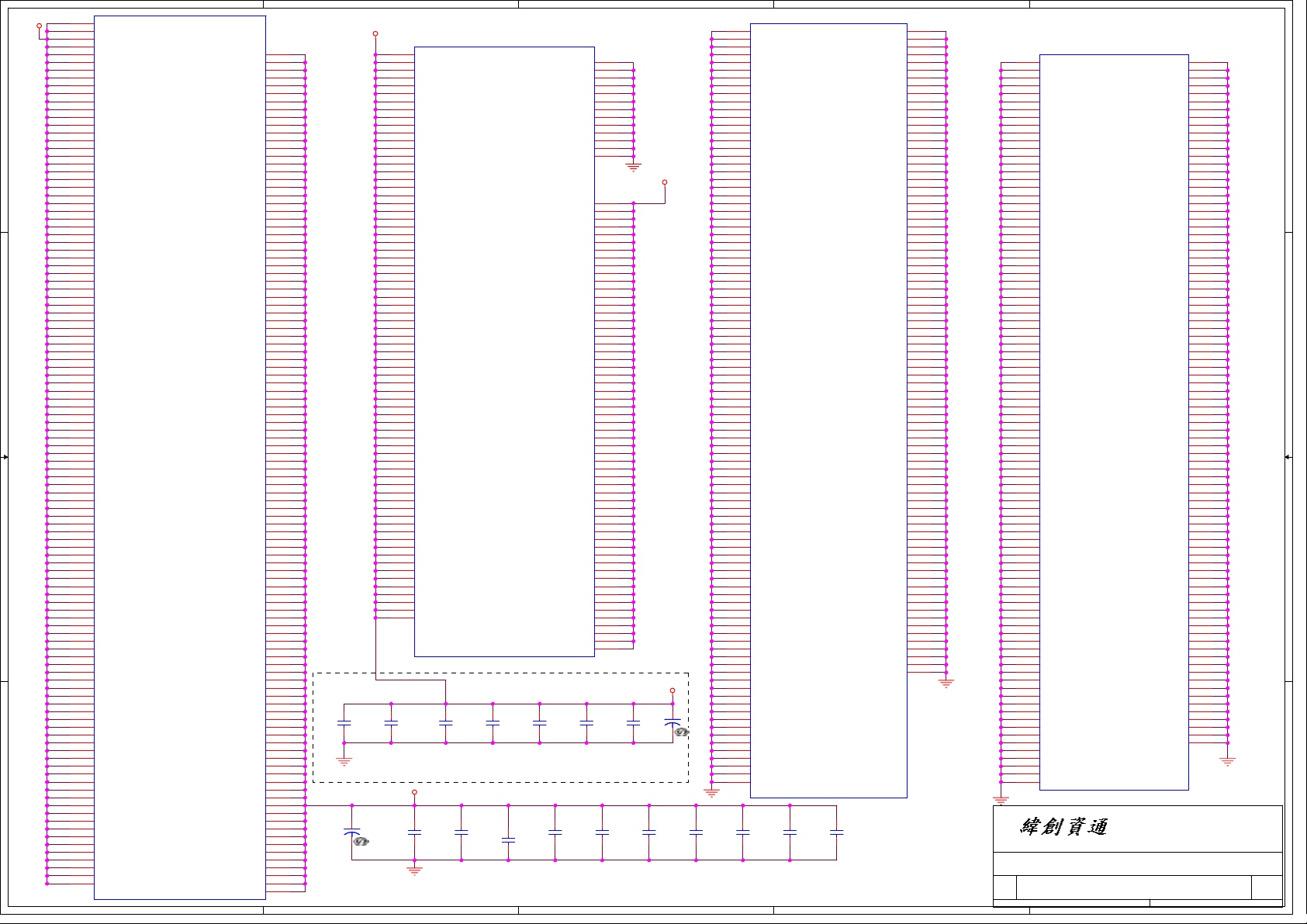

ICH7M Integrated Pull-up

and Pull-down Resistors

EE_DIN,EE_DOUT,

GNT[4]#/GPIO48,

LAD[3:0]#/FHW[3:0]#,

LDRQ[0], LDRQ[1]/GPIO[41],

4 4

PWRBTN#,

DDREQ

DD[7],

ACZ_BIT_CLK, ACZ_RST#, ACZ_SDIN[2:0],

EE_CS,

SPI_ARB, SPI_CLK,

USB[7:0][P,N]

LAN_CLK

GNT[3:0],

GNT[5]#/GPO17,

TP[3]

ACZ_SYNC,ACZ_SDOUT,

GPIO[25],

PME#,

LAN_RXD[2:0]

DPRSLPVR/GPIO16,

SPKR,

ICH7 internal 20K pull-ups

ICH7 internal 11.5K pull-downs

ICH7 internal 20K pull-downs

ICH7 internal 15K pull-downs

ICH7 internal 15K pull-upSATALED#

ICH7 internal 100K pull-down

ICH7-M EDS 17837 1.5V1

ICH7M IDE Integrated Series

Termination Resistors

3 3

DD[15:0],

DDACK#,

DCS3#,

IORDY,

IDEIRQ

DIOR#, DREQ,DIOW#,

DA[2:0],

DCS1#,

approximately 33 ohm

ICH7M Functional Strap Definitions

Signal

ACZ_SDOUT

ACZ_SYNC

EE_CS

EE_DOUT

2 2

GNT2#

GNT3#

GNT5#/

GPIO17#,

GNT4#/

GPIO48

DPRSLPVR Reserved

GPIO25

INTVRMEN

LINKALERT#

REQ[4:1]#

1 1

SATALED#

SPKR

TP3

Usage/When Sampled

XOR Chain Entrance/

PCIE Port Config bit1,

Rising Edge of PWROK

PCIE bit0,

Rising Edge of PWROK.

Reserved

Reserved

Reserved

Top-Block

Swap Override.

Rising Edge of PWROK.

Boot BIOS Destination

Selection.

Rising Edge of PWROK.

Reserved.

Rising Edge of RSMRST#.

Integrated VccSus1_05

VRM Enable/Disable.

Always sampled.

Reserved

XOR Chain Selection.

Rising Edge of PWROK.

Reserved This signal should not be pull low.

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

Allows entrance to XOR Chain testing when TP3

pulled low.When TP3 not pulled low at rising edge

of PWROK,sets bit1 of RPC.PC(Config Registers:

offset 224h)

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

This signal should not be pull high.

This signal should not be pull low.

This signal should not be pull low.

Sampled low:Top-Block Swap mode(inverts A16 for

all cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT5# is MSB, 01-SPI, 10-PCI, 11-LPC.

This signal should not be pull high.

This signal should not be pull low.

Enables integrated VccSus1_05 VRM when

sampled high

Requires an external pull-up resistor.

TBD, Chapter 8.

If sampled high, the system is strapped to the

"No Reboot" mode(ICH7 will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.

This signal should not be pull low unless using

XOR Chain testing.

Comment

B

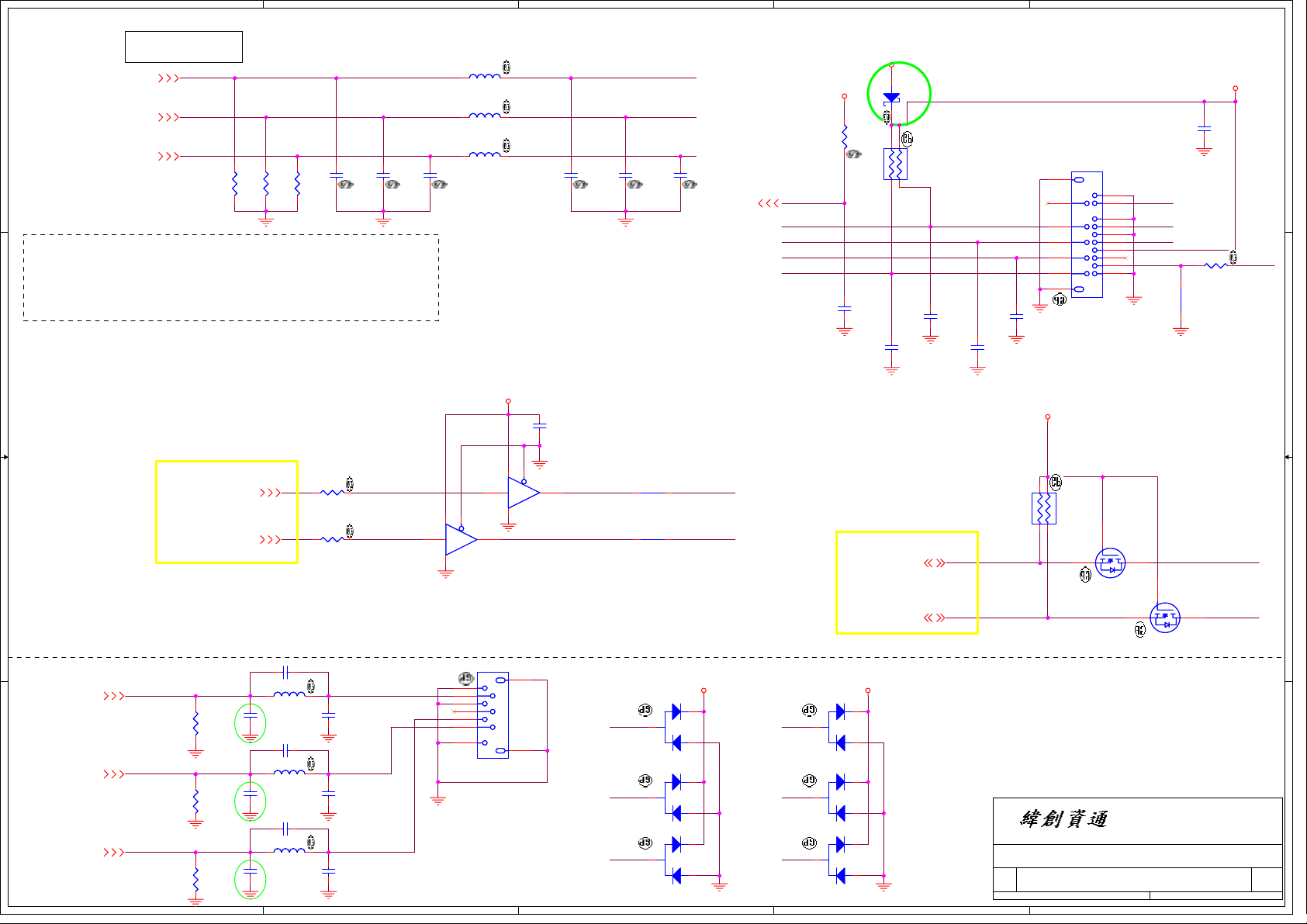

954305D 27Mhz/LCDCLK Spread

and Frequency Selection Table

SS3

SS2

Byte9

bit 7

000

0000

0

0

0

0

0

1 +-0.25 Center

1

1

1

1

1

11

11

SS1

bit6

bit5

1

0

1

0

0

1

0

1

1

1

11

0

0

00

001

1

0

1

0

1

1

1

PCI Routing

7412

page 16

MiniPCI

LAN

21

23

SS0

bit4

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

22

C

Spread Amount%

-0.50 Down

-1.00 Down

-1.50 Down

-2.00 Down

-0.75 Down

-1.25 Down

-1.75 Down

-2.25 Down

+-0.5 Center

+-0.75 Center

+-1.0 Center

+-0.25 Center

+-0.5 Center

+-0.75 Center

+-1.0 Center

page 16

INT -> PIRQ

A->G, B->B,

C->F, D->G

A/C -> E

B/D -> E

A -> H

A->G, B->B,251410 0

REQ/GNTIDSEL

page 3

0

1

2

D

E

Calistoga Strapping Signals and

Configuration

Pin Name

CFG[2:0]

CFG[4:3]

CFG5

CFG7

CFG8

CFG9

CFG[11:10] Reserved

CFG[13:12]

CFG[15:14]

CFG16

CFG17

CFG18

CFG19

CFG20

SDVOCRTL

_DATA

All strap signals are sampled with respect to the leading

NOTE:

edge of the Calistoga GMCH PWORK in signal.

Strap Description

FSB Frequency Select

Reserved

DMI x2 Select

ReservedCFG6

CPU Strap

Reserved

PCI Express Graphics

Lane Reversal

XOR/ALL Z test

straps

Reserved

FSB Dynamic ODT

Global R-comp Disable

(All R-comps)

VCC Select

DMI Lane Reversal

SDVO/PCIE

Concurrent

SDVO Present

EDS 17050 0.71

Configuration

001 = FSB533

011 = FSB667

others = Reserved

0 = DMI x2

1 = DMI x4

0 = Reserved

1 =Mobile CPU(Default)

0 = Reverse Lanes,15->0,14->1 ect..

1= Normal operation(Default):Lane

Numbered in order

00 = Reserved

01 = XOR mode enabled

10 = All Z mode enabled

11 = Normal Operation

(Default)

Reserved

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

0 = All R-comp Disable

1 = Normal Operation (Default)

0 = 1.05V

1 = 1.5V

0 = Normal operation (Default):lane

Numbered in order

1 =Reverse Lane,4->0,3->1 ect...

0 = Only SDVO or PCIE x1 is

operational (Default)

1 =SDVO and PCIE x1 are operating

simultaneously via the PEG port

0 = No SDVO Card present

1= SDVO Card present

(Default)

(Default)

(Default)

page 7

(Default)

History

6/6 drawing SA

7/11 Rename for placement

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet

Reference

Reference

Reference

AG1 -1

AG1 -1

AG1 -1

of

245Monday, January 09, 2006

245Monday, January 09, 2006

245Monday, January 09, 2006

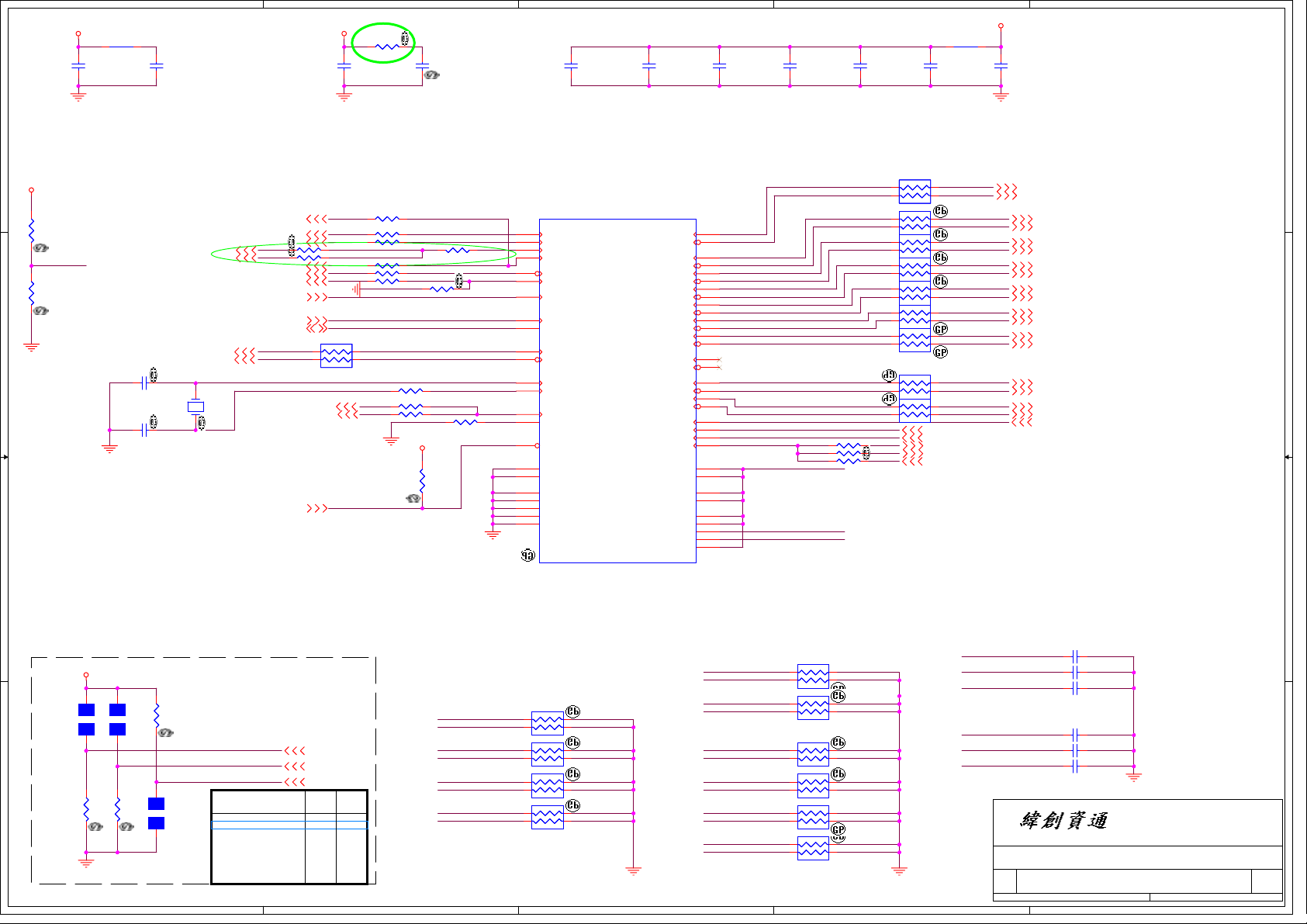

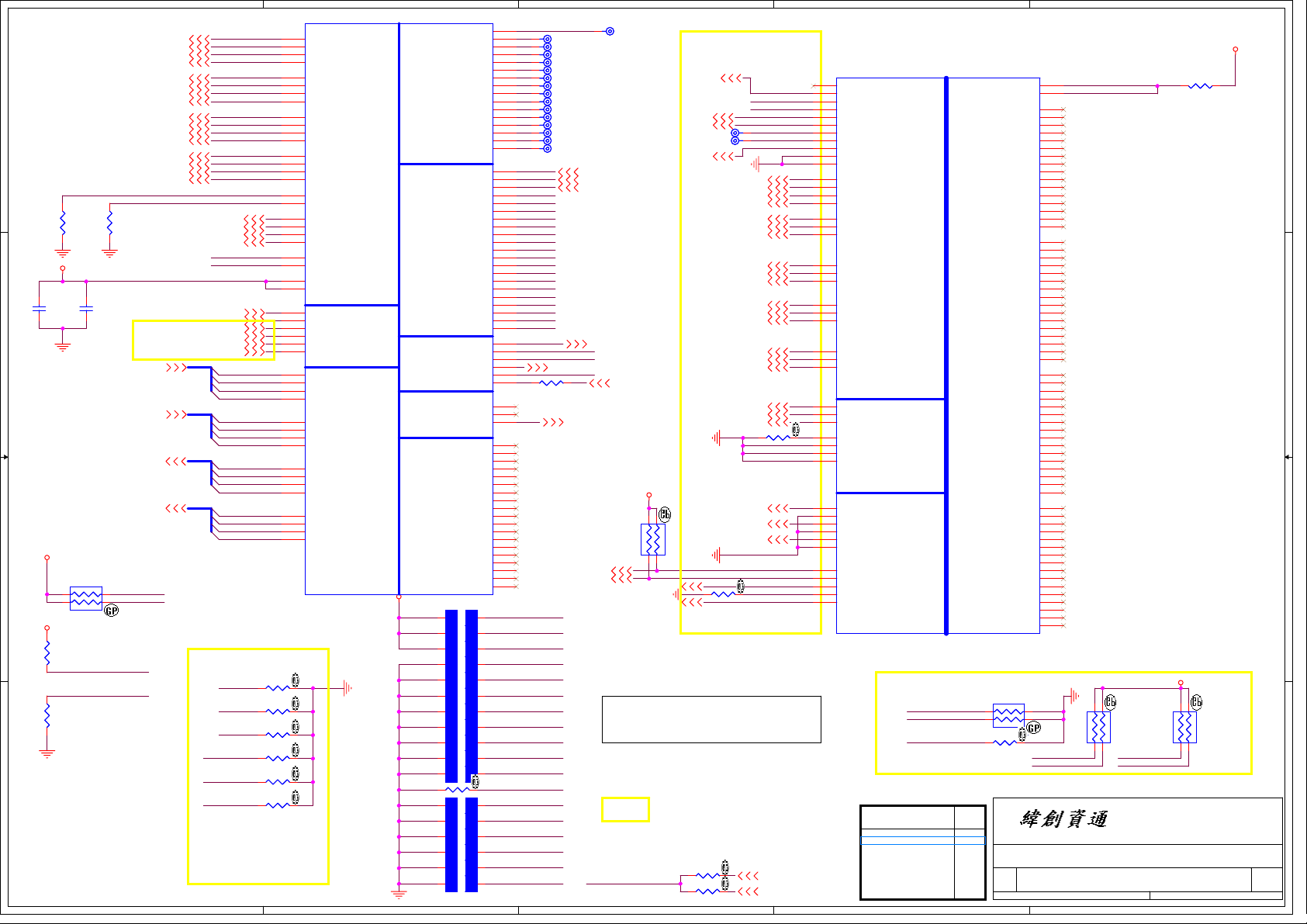

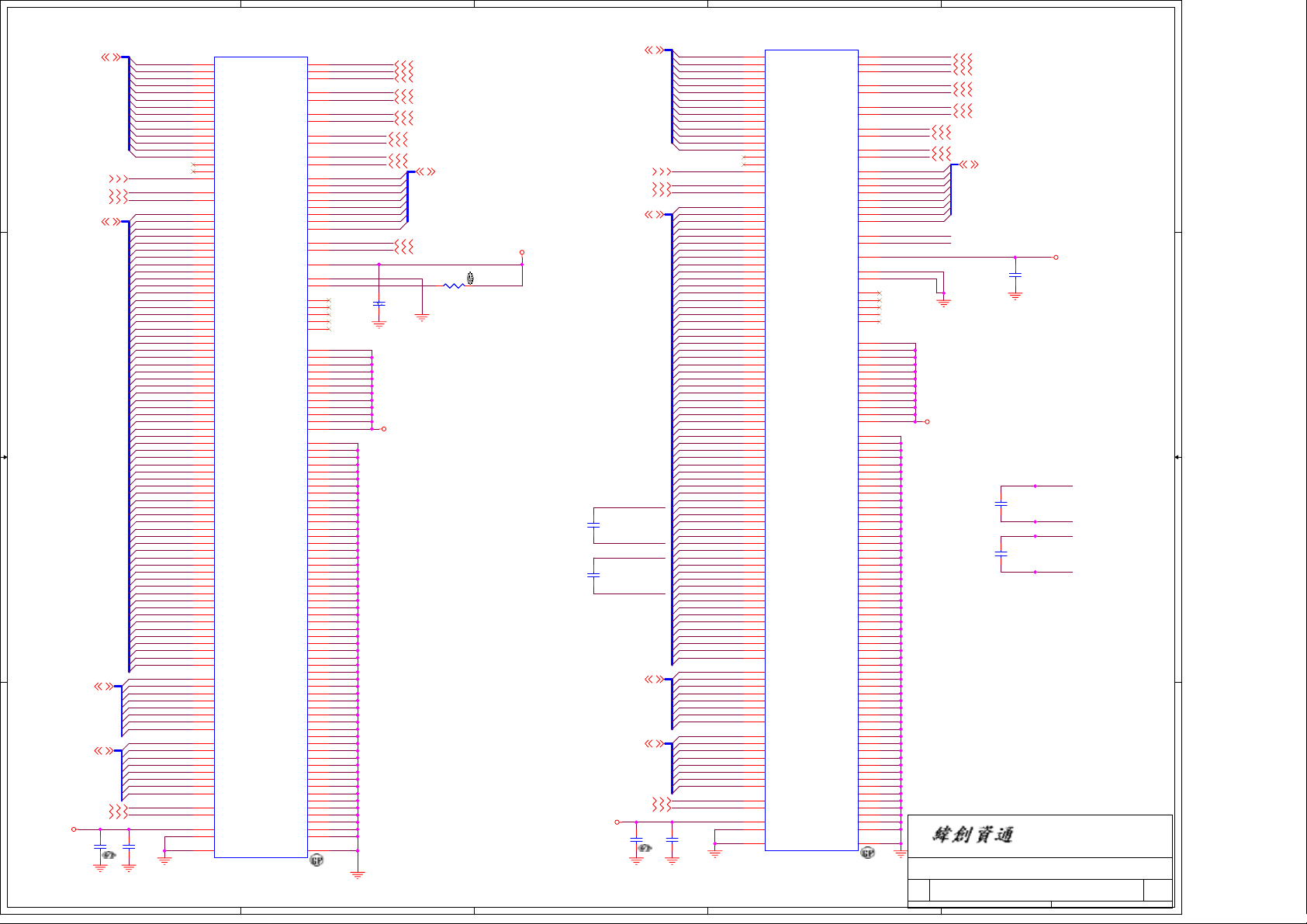

A

3D3V_S0 3D3V_S0

3D3V_CLKPLL_S0

R74

R74

1 2

0R0603-PAD

0R0603-PAD

12

C147

C147

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C96

C96

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

12

B

-1

R123

R123

1 2

5D1R3F-GP

5D1R3F-GP

C139

C139

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_48MPWR_S0

12

C137

C137

C136

C136

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

C

12

C114

C114

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_CLKGEN_S0

12

C131

C131

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C115

C115

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C130

C130

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

D

R122

R122

1 2

0R0603-PAD

0R0603-PAD

12

C88

C88

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_S0

12

C91

C91

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

E

4 4

3D3V_S0

12

R457

R457

10KR2J-3-GP

10KR2J-3-GP

TIPCI

TIPCI

No TIPCI

SS_SEL

H/L: 100/96MHz

12

R455

R455

10KR2J-3-GP

10KR2J-3-GP

DY

DY

3 3

2 2

No TIPCI

C283

C283

1 2

SC20P50V2JN-1GP

SC20P50V2JN-1GP

C278

C278

1 2

SC20P50V2JN-1GP

SC20P50V2JN-1GP

PCLK_PCM_TI25

PCLK_PCM_ENE35

D_REFCLK7

D_REFCLK#7

12

PCLK_FWH34

PCLK_KBC31

-1

PCLK_LAN22

FIR

FIR

PCLK_SIO32

PCLK_MINI30

CLK_ICHPCI16

PM_STPPCI#16

SMBC_ICH11,18

SMBD_ICH11,18

GEN_XTAL_OUT_R

X3

X3

X-14D31818M-31GP

X-14D31818M-31GP

82.30005.831

82.30005.831

R456 0R2J-2-GP

R456 0R2J-2-GP

R454 0R2J-2-GP

R454 0R2J-2-GP

CLK14_SIO32

CLK_ICH1416

CLK_EN#38

R661 22R2J-2-GPR661 22R2J-2-GP

R449 33R2J-2-GPR449 33R2J-2-GP

1 2

R448 33R2J-2-GPR448 33R2J-2-GP

1 2

12

12

R453 22R2J-2-GP

R453 22R2J-2-GP

R452 33R2J-2-GP

R452 33R2J-2-GP

1 2

MINI

MINI

R459 33R2J-2-GPR459 33R2J-2-GP

1 2

1

4

2 3

GEN_XTAL_IN

RN34SRN33J-5-GP-U RN34SRN33J-5-GP-U

R116 470R2J-2-GPR116 470R2J-2-GP

R439 22R2J-2-GPR439 22R2J-2-GP

R445 22R2J-2-GPR445 22R2J-2-GP

12

12

H/L : CPU_ITP/SRC7

1 2

1 2

1 2

R101

R101

10KR2J-3-GP

10KR2J-3-GP

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

PCLKCLK0

PCLKCLK1

R699

R699

1 2

33R2J-2-GP

33R2J-2-GP

PCLKCLK3

1 2

R460 10KR2J-3-GPR460 10KR2J-3-GP

D_REFCLK_1

D_REFCLK#_1

GEN_XTAL_OUT

R86475R2F-L1-GP R86475R2F-L1-GP

3D3V_S0

12

DY

DY

PCLKCLK2

SS_SEL

ITP_EN

GEN_REF

GEN_REF

12

GEN_IREF

56

PCI0

3

PCI1

4

PCI2

5

PCI3

9

PCIF1/SEL100/96#

8

PCIF0/ITP_EN

55

PCI_STOP#

46

SCL

47

SDA

14

DOT96

15

DOT96#

50

XTAL_IN

49

XTAL_OUT

52

REF

39

IREF

10

VTT_PWRGD#/PD

2

VSS_PCI

6

VSS_PCI

51

VSS_REF

45

VSS_CPU

38

VSSA

13

VSS48

29

VSS_SRC

IDTCV125PAG-GP 71.00125.A0W

IDTCV125PAG-GP 71.00125.A0W

CPU2_ITP/SRC7

CPU2_ITP#/SRC7#

CPU_STOP#

FSC/TEST_SEL

FSB/TEST_MODE

USB48/FSA

LVDS

LVDS#

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC4

SRC4#

SRC5

SRC5#

SRC6

SRC6#

CPU0

CPU0#

CPU1

CPU1#

VDD_SRC

VDD_SRC

VDD_PCI

VDD_PCI

VDD_REF

VDD_CPU

VDDA

VDD48

VDD_SRC

U15

U15

17

18

CLK_MCH_3GPLL_1

19

CLK_MCH_3GPLL_1#

20

CLK_PCIE_ICH_1

22

CLK_PCIE_ICH_1#

23

CLK_PCIE_LAN_1

24

CLK_PCIE_LAN_1#

25

CLK_PCIE_SATA_1

26

CLK_PCIE_SATA_1#

27

CLK_PCIE_NEW_1

31

CLK_PCIE_NEW_1#

30

CLK_PCIE_MINI1_1

33

CLK_PCIE_MINI1_1#

32

36

35

CLK_CPU_BCLK_1

44

CLK_CPU_BCLK_1#

43

41

40

54

53

16

12

34

21

7

1

48

42

37

11

28

D_REFSSCLK_1

D_REFSSCLK#_1

CLK_MCH_BCLK_1

CLK_MCH_BCLK_1#

CPU_SEL2

CPU_SEL1

CPU_SEL0_1

3D3V_CLKGEN_S0

3D3V_CLKPLL_S0

3D3V_48MPWR_S0

1 2

1 2

R662

R662

1 2

SRN33J-5-GP-U

RN30

RN30

RN22 SRN33J-5-GP-URN22 SRN33J-5-GP-U

RN27 SRN33J-5-GP-URN27 SRN33J-5-GP-U

RN24 SRN33J-5-GP-U

RN24 SRN33J-5-GP-U

RN20 SRN33J-5-GP-U

RN20 SRN33J-5-GP-U

RN21 SRN33J-5-GP-U

RN21 SRN33J-5-GP-U

RN23 SRN33J-5-GP-U

RN23 SRN33J-5-GP-U

RN33 SRN33J-5-GP-URN33 SRN33J-5-GP-U

RN37 SRN33J-5-GP-URN37 SRN33J-5-GP-U

R43522R2J-2-GP R43522R2J-2-GP

R43722R2J-2-GP R43722R2J-2-GP

2K2R2J-2-GP

2K2R2J-2-GP

SRN33J-5-GP-U

4

2 3

1

2 3

1

2 3

GIGA

GIGA

1

2 3

1

SATA

SATA

1

2 3

NEW

NEW

1

2 3

MINIC

MINIC

4

4

CPU_SEL2 4,7

CPU_SEL1 4,7

CLK48_ICH 16

CLK48_CARDBUS 25

CPU_SEL0 4,7

1

23

4

4

4

4

4

4

23

1

23

1

D_REFSSCLK 7

D_REFSSCLK# 7

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_PCIE_ICH 16

CLK_PCIE_ICH# 16

CLK_PCIE_LAN 22

CLK_PCIE_LAN# 22

CLK_PCIE_SATA 15

CLK_PCIE_SATA# 15

CLK_PCIE_NEW 30

CLK_PCIE_NEW# 30

CLK_PCIE_MINI1 26

CLK_PCIE_MINI1# 26

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

PM_STPCPU# 16

RN31

1D05V_S0

12

12

12

R433

R433

R92

R92

DY

DY

A

DUMMY-R2

DUMMY-R2

12

R438

R438

470R2J-2-GP

470R2J-2-GP

DY

DY

12

R441

R441

DUMMY-R2

DUMMY-R2

SEL1

SEL2

0

0

0

1

1 100M

1

1

SEL0

0

0

0

01200M

1

1

1

00333M

0

1

0

1

0

1

1

CPU_SEL2 4,7

CPU_SEL1 4,7

CPU_SEL0 4,7

CPU

266M

133M

166M

400M

Reserved

FSB

X

533M

X

667M

X

X

X

X

RN83

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

SRN49D9F-GP

SRN49D9F-GP

CLK_PCIE_LAN

CLK_PCIE_LAN#

SRN49D9F-GP

SRN49D9F-GP

CLK_PCIE_SATA

CLK_PCIE_SATA#

SRN49D9F-GP

SRN49D9F-GP

CLK_PCIE_ICH

CLK_PCIE_ICH#

B

RN83

2 3

MINIC

MINIC

1

RN84

RN84

2 3

GIGA

GIGA

1

RN80

RN80

2 3

SATA

SATA

1

2 3

1

RN86SRN49D9F-GP RN86SRN49D9F-GP

4

4

4

4

C

R447

R447

DUMMY-R2

DUMMY-R2

1 1

470R2J-2-GP

470R2J-2-GP

R440

R440

DY

DY

12

470R2J-2-GP

470R2J-2-GP

D_REFSSCLK#

D_REFSSCLK

SRN49D9F-GP

SRN49D9F-GP

CLK_PCIE_NEW

CLK_PCIE_NEW#

SRN49D9F-GP

SRN49D9F-GP

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

D_REFCLK#

D_REFCLK

SRN49D9F-GP

SRN49D9F-GP

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

SRN49D9F-GP

SRN49D9F-GP

RN31

1

2 3

2 3

NEW

NEW

1

RN81

RN81

RN32SRN49D9F-GP RN32SRN49D9F-GP

2 3

1

RN36SRN49D9F-GP RN36SRN49D9F-GP

2 3

1

RN35

RN35

1

2 3

2 3

1

RN82

RN82

4

4

4

4

4

4

D

PCLK_SIO

CLK_ICH14

PCLK_MINI

PCLK_KBC

CLK_ICHPCI

CLK48_ICH

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Clock Generator ICS954305D

Clock Generator ICS954305D

Clock Generator ICS954305D

EC29

EC29

1 2

1 2

1 2

1 2

1 2

1 2

DY

DY

SC10P50V3JN-GP

SC10P50V3JN-GP

EC26

EC26

DY

DY

SC10P50V3JN-GP

SC10P50V3JN-GP

EC28

EC28

DY

DY

SC10P50V3JN-GP

SC10P50V3JN-GP

EC27

EC27

DY

DY

SC10P50V3JN-GP

SC10P50V3JN-GP

EC32

EC32

DY

DY

SC10P50V3JN-GP

SC10P50V3JN-GP

EC15

EC15

DY

DY

SC10P50V3JN-GP

SC10P50V3JN-GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

AG1 -1

AG1 -1

AG1 -1

345Wednesday, January 18, 2006

345Wednesday, January 18, 2006

345Wednesday, January 18, 2006

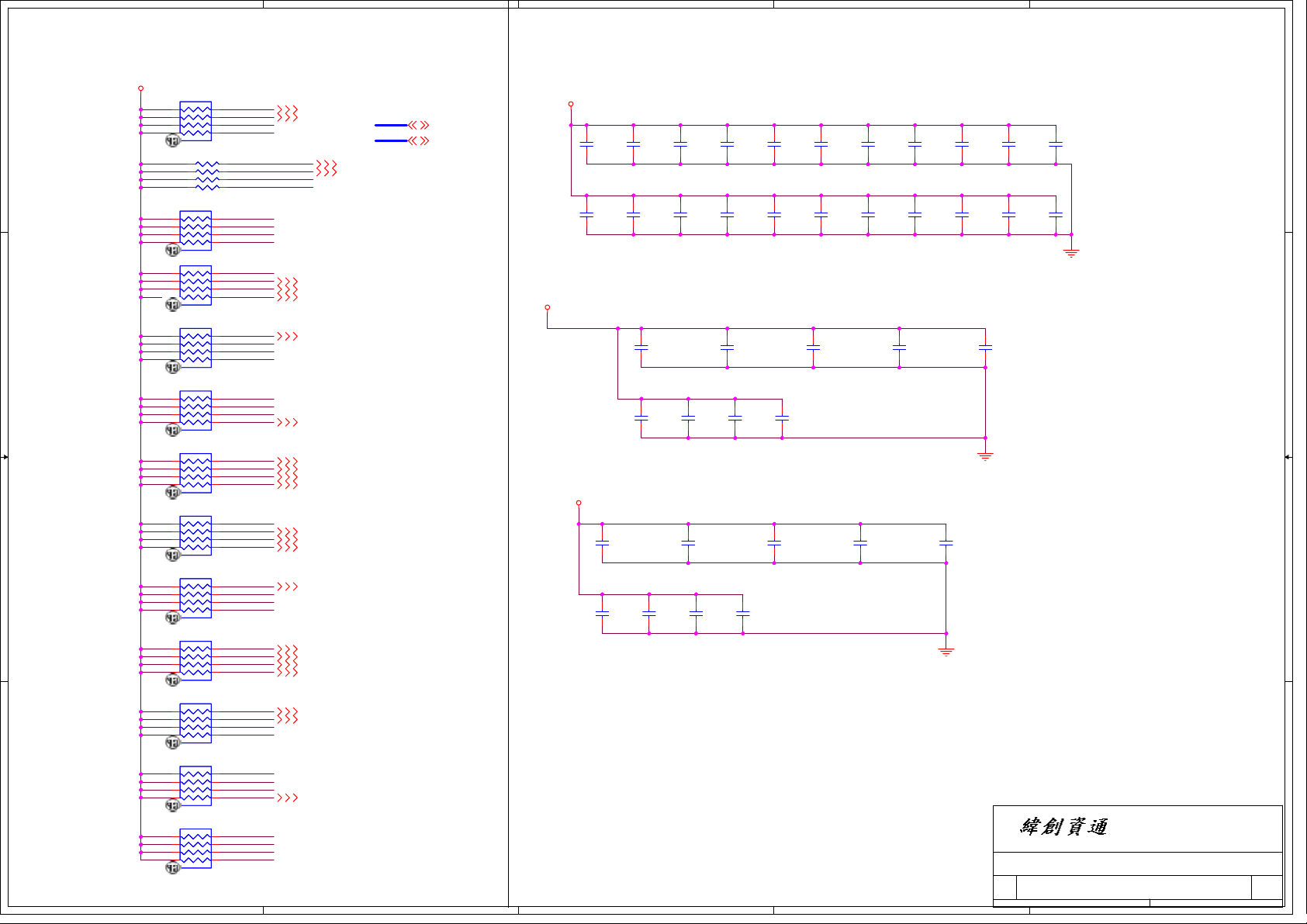

E

EMI capacitor

A

B

C

D

E

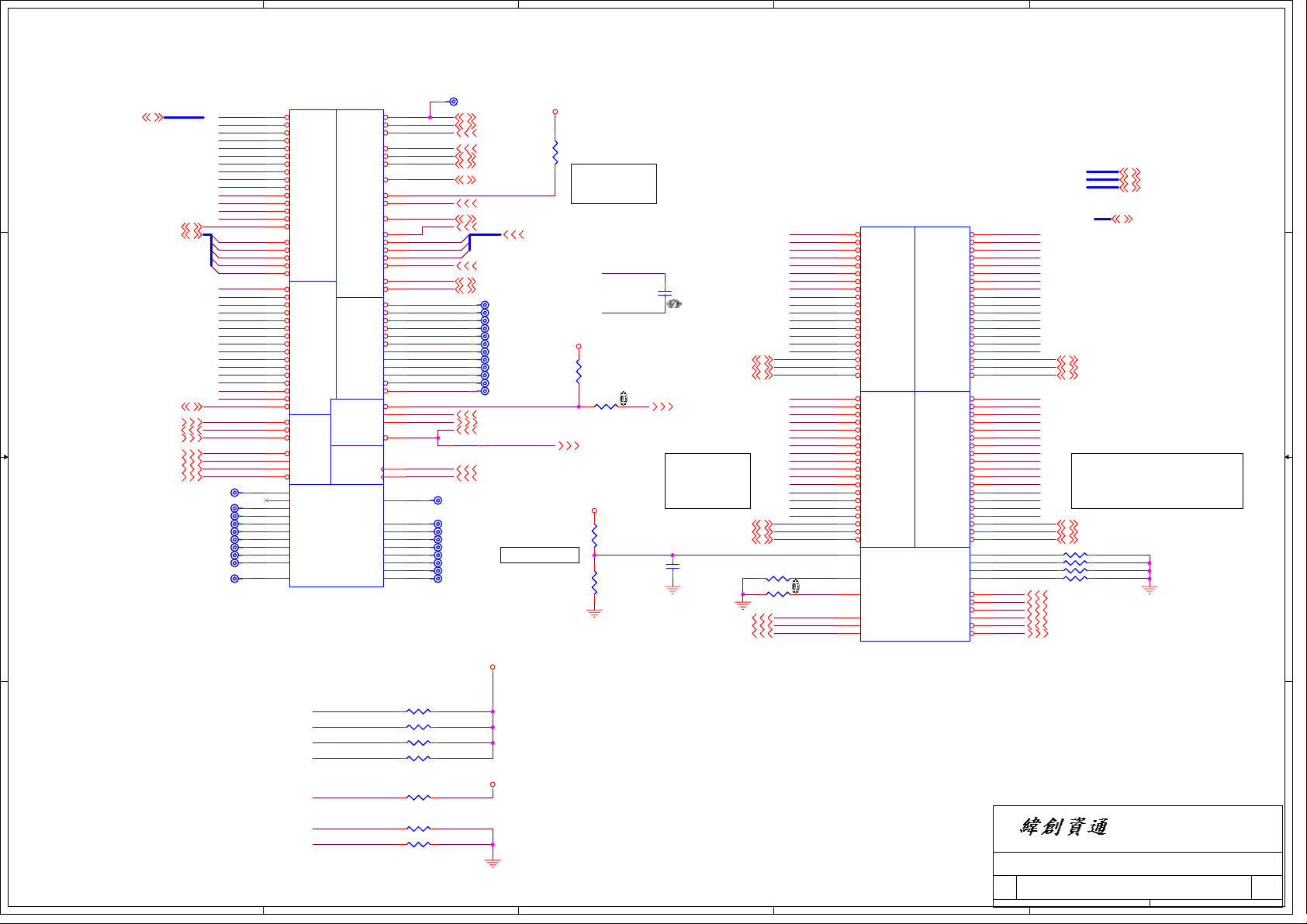

H_RS#0

H_RS#1

H_RS#2

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

R138

R138

1 2

0R0402-PAD

0R0402-PAD

TP38 TPAD30TP38 TPAD30

TP24 TPAD30TP24 TPAD30

TP27 TPAD30TP27 TPAD30

TP20 TPAD30TP20 TPAD30

TP22 TPAD30TP22 TPAD30

TP53 TPAD30TP53 TPAD30

TP19 TPAD30TP19 TPAD30

TP18 TPAD30TP18 TPAD30

TP17 TPAD30TP17 TPAD30

TP30 TPAD30TP30 TPAD30

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_INIT# 15

H_LOCK# 6

H_CPURST# 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

TP50 TPAD30TP50 TPAD30

TP51 TPAD30TP51 TPAD30

TP91 TPAD30TP91 TPAD30

TP47 TPAD30TP47 TPAD30

TP90 TPAD30TP90 TPAD30

TP89 TPAD30TP89 TPAD30

TP52 TPAD30TP52 TPAD30

TP43 TPAD30TP43 TPAD30

TP48 TPAD30TP48 TPAD30

TP46 TPAD30TP46 TPAD30

TP44 TPAD30TP44 TPAD30

TP14 TPAD30TP14 TPAD30

H_THERMDA 19

H_THERMDC 19

PM_THRMTRIP-A# 7

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

U59A

4 4

3 3

2 2

H_A#[31..3]6

H_ADSTB#06

H_REQ#[4..0]6

H_ADSTB#16

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

H_NMI15

H_SMI#15

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP87TPAD30 TP87TPAD30

TP88TPAD30 TP88TPAD30

TP45TPAD30 TP45TPAD30

TP33TPAD30 TP33TPAD30

TP35TPAD30 TP35TPAD30

TP39TPAD30 TP39TPAD30

TP40TPAD30 TP40TPAD30

TP15TPAD30 TP15TPAD30

TP21TPAD30 TP21TPAD30

TP84TPAD30 TP84TPAD30

U59A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L1

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

L2

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L5

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U2

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W3

A[27]#

W5

A[28]#

Y4

A[29]#

W2

A[30]#

Y1

A[31]#

V4

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

AA1

RSVD[01]

AA4

RSVD[02]

AB2

RSVD[03]

AA3

RSVD[04]

M4

RSVD[05]

N5

RSVD[06]

T2

RSVD[07]

V3

RSVD[08]

B2

RSVD[09]

C3

RSVD[10]

B25

RSVD[11]

BGA479-SKT6-GPU1

BGA479-SKT6-GPU1

62.10079.001

62.10079.001

ADS#

BNR#

BPRI#

ADDR GROUP 0

ADDR GROUP 0

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

ADDR GROUP 1

ADDR GROUP 1

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALSH CLK

XDP/ITP SIGNALSH CLK

PROCHOT#

THERMDA

THERMDC

THERM

THERM

THERMTRIP#

BCLK[0]

BCLK[1]

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RESERVED

RESERVED

RSVD[18]

RSVD[19]

RSVD[20]

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

2nd source: 62.10053.401

1D05V_S0

1D05V_S0

12

H_IERR#

H_RS#[2..0] 6

1D05V_S0

Layout Note:

0.5" max length.

R144

R144

56R2J-4-GP

56R2J-4-GP

Place testpoint on

H_IERR# with a GND

0.1" away

H_THERMDA

H_THERMDC

R145

R145

56R2J-4-GP

56R2J-4-GP

1 2

R143

R143

1 2

0R2J-2-GP

0R2J-2-GP

DY

DY

PM_THRMTRIP-I# 36

1D05V_S0

12

R498

R498

1KR2F-3-GP

1KR2F-3-GP

12

R500

R500

2KR2F-3-GP

2KR2F-3-GP

12

C511

C511

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

H_DSTBN#06

H_DSTBP#06

H_DINV#06

CPU_PROCHOT# 38

PM_THRMTRIP#

should connect to

ICH7 and Calistoga

without T-ing

( No stub)

H_DSTBN#16

H_DSTBP#16

H_DINV#16

12

C678

C678

CPU_SEL03,7

SC1KP16V2KX-GP

SC1KP16V2KX-GP

CPU_SEL13,7

CPU_SEL23,7

CPU_GTLREF0

R477 1KR2J-1-GP

R477 1KR2J-1-GP

DY

DY

1 2

R478 51R2F-2-GPR478 51R2F-2-GP

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST1

12

TEST2

U59B

U59B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H26

D[12]#

F26

D[13]#

K22

D[14]#

H25

D[15]#

H23

DSTBN[0]#

G22

DSTBP[0]#

J26

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L25

D[20]#

L22

D[21]#

L23

D[22]#

M23

D[23]#

P25

D[24]#

P22

D[25]#

P23

D[26]#

T24

D[27]#

R24

D[28]#

L26

D[29]#

T25

D[30]#

N24

D[31]#

M24

DSTBN[1]#

N25

DSTBP[1]#

M26

DINV[1]#

AD26

GTLREF

C26

TEST1

D25

TEST2

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

BGA479-SKT6-GPU1

BGA479-SKT6-GPU1

MISC

MISC

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

DATA GRP 3

DATA GRP 3

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

H_DINV#[3..0] 6

H_DSTBN#[3..0] 6

H_DSTBP#[3..0] 6

H_D#32

AA23

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

W25

H_D#37

U23

H_D#38

U25

H_D#39

U22

H_D#40

AB25

H_D#41

W22

H_D#42

Y23

H_D#43

AA26

H_D#44

Y26

H_D#45

Y22

H_D#46

AC26

H_D#47

AA24

W24

Y25

V23

H_D#48

AC22

H_D#49

AC23

H_D#50

AB22

H_D#51

AA21

H_D#52

AB21

H_D#53

AC25

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AD24

H_D#58

AE21

H_D#59

AD21

H_D#60

AE25

H_D#61

AF25

H_D#62

AF22

H_D#63

AF26

AD23

AE24

AC20

COMP0

R26

COMP1

U26

COMP2

U1

COMP3

V1

E5

B5

D24

D6

D7

AE6

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

R492 27D4R2F-L1-GPR492 27D4R2F-L1-GP

1 2

R496 54D9R2F-L1-GPR496 54D9R2F-L1-GP

1 2

R165 27D4R2F-L1-GPR165 27D4R2F-L1-GP

1 2

R168 54D9R2F-L1-GPR168 54D9R2F-L1-GP

1 2

H_DPRSLP# 15,38

H_DPSLP# 15

H_DPWR# 6

H_PWRGD 15,36

H_CPUSLP# 6,15

PSI# 38

H_D#[63..0] 6

XDP_TDI

XDP_TMS

XDP_TDO

H_CPURST#

1 1

A

XDP_DBRESET#

XDP_TCK

XDP_TRST#

R174 150R2F-1-GPR174 150R2F-1-GP

1 2

R172 39D2R3F-2-GPR172 39D2R3F-2-GP

1 2

DY

DY

R175 54D9R2F-L1-GP

R175 54D9R2F-L1-GP

1 2

DY

DY

R139 54D9R2F-L1-GP

R139 54D9R2F-L1-GP

1 2

DY

DY

R470 150R2F-1-GP

R470 150R2F-1-GP

1 2

R180 27D4R2F-L1-GPR180 27D4R2F-L1-GP

1 2

R176 680R3F-GPR176 680R3F-GP

1 2

All place within 2" to CPU

B

3D3V_S0

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

C

D

Date: Sheet

CPU (1 of 2)

CPU (1 of 2)

CPU (1 of 2)

AG1 -1

AG1 -1

AG1 -1

E

of

445Wednesday, January 18, 2006

of

445Wednesday, January 18, 2006

of

445Wednesday, January 18, 2006

A

VCC_CORE_S0

U59C

U59C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

4 4

3 3

2 2

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

BGA479-SKT6-GPU1

BGA479-SKT6-GPU1

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

VCC_CORE_S0

CPU_V6

1 2

0R0402-PAD

0R0402-PAD

12

C194

C194

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

H_VID0 38

H_VID1 38

H_VID2 38

H_VID3 38

H_VID4 38

H_VID5 38

H_VID6 38

12

R179

R179

100R2F-L1-GP-U

100R2F-L1-GP-U

R164

R164

1D05V_S0

B

Layout Note

H_VID[0..6]38

1D5V_VCCA_S0

C158

C158

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

VCC_CORE_S0

12

R178

R178

100R2F-L1-GP-U

100R2F-L1-GP-U

Layout Note:

-1

L14

L14

1 2

HCB1608KF121T30-GP

HCB1608KF121T30-GP

12

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

68.00230.041

68.00230.041

C153

C153

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

VCC_SENSE 38

VSS_SENSE 38

1D5V_S0

1D05V_S0

12

C191

C191

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

VCC_CORE_S0

12

C211

C211

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C

12

12

C198

C198

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C210

C210

C215

C215

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C189

C189

C172

C172

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C209

C209

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C178

C178

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C507

C507

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C183

C183

D

U59D

U59D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

12

C542

C542

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C186

C186

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

BGA479-SKT6-GPU1

BGA479-SKT6-GPU1

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

E

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VCC_CORE_S0

12

12

12

12

C171

C539

C539

DY

1 1

DY

A

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

B

C171

C208

C208

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C170

C170

C169

C169

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

12

C192

C192

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C528

C528

C536

C536

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C534

C534

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

12

12

C537

C537

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C

C529

C529

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C533

C533

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

12

12

C222

C222

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C221

C221

C538

C538

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

12

C220

C220

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

D

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU (2 of 2)

CPU (2 of 2)

CPU (2 of 2)

AG1 -1

AG1 -1

AG1 -1

E

of

545Wednesday, January 18, 2006

of

545Wednesday, January 18, 2006

of

545Wednesday, January 18, 2006

A

H_XRCOMP

12

R511

R511

24D9R2F-L-GP

24D9R2F-L-GP

4 4

1D05V_S0

R510

R510

54D9R2F-L1-GP

54D9R2F-L1-GP

1 2

H_XSCOMP

1D05V_S0

12

R515

R515

221R2F-2-GP

221R2F-2-GP

H_XSWING

3 3

2 2

12

12

1D05V_S0

1 2

1D05V_S0

12

12

R513

R513

100R2F-L1-GP-U

100R2F-L1-GP-U

H_YRCOMP

R507

R507

24D9R2F-L-GP

24D9R2F-L-GP

R509

R509

54D9R2F-L1-GP

54D9R2F-L1-GP

H_YSCOMP

R514

R514

221R2F-2-GP

221R2F-2-GP

H_YSWING

R508

R508

100R2F-L1-GP-U

100R2F-L1-GP-U

H_D#[63..0]4

C552

C552

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1 2

C551

C551

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1 2

B

U58A

W11

AB7

AA9

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

K11

T10

U11

T11

Y10

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

G4

T3

U7

U9

W9

T1

T8

T4

W7

U5

T9

W6

T5

W4

W3

Y3

Y7

W5

W2

Y8

E1

E2

E4

Y1

U1

W1

U58A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

CALISTOGA

CALISTOGA

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

CLK_MCH_BCLK3

CLK_MCH_BCLK#3

C

H_ADSTB#_0

H_ADSTB#_1

HOST

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_VREF

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

R512

R512

1 2

0R0402-PAD

0R0402-PAD

D

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_CPURST# 4

H_DBSY# 4

H_DEFER# 4

H_DPWR# 4

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_CPUSLP# 4,15

H_TRDY# 4

H_A#[31..3] 4

C187

C187

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1 2

H_DINV#[3..0] 4

H_DSTBN#[3..0] 4

H_DSTBP#[3..0] 4

H_REQ#[4..0] 4

1D05V_S0

12

12

H_RS#[2..0] 4

R161

R161

100R2F-L1-GP-U

100R2F-L1-GP-U

R157

R157

200R2F-L-GP

200R2F-L-GP

E

1 1

Place them near to the chip ( < 0.5")

A

B

C

D

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

GMCH (1 of 5)

GMCH (1 of 5)

GMCH (1 of 5)

AG1 -1

AG1 -1

AG1 -1

E

of

645Wednesday, January 18, 2006

of

645Wednesday, January 18, 2006

of

645Wednesday, January 18, 2006

A

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

1 2

1 2

1 2

1 2

1 2

1 2

R488

R488

R485

R485

R483

R483

R148

R148

R146

R146

R481

R481

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

150R2F-1-GP

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

G_CLKIN

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

CALISTOGA

CALISTOGA

M_CLK_DDR011

M_CLK_DDR111

M_CLK_DDR211

M_CLK_DDR311

M_CLK_DDR#011

M_CLK_DDR#111

M_CLK_DDR#211

M_CLK_DDR#311

12

DMI_TXN[3..0]16

DMI_TXP[3..0]16

DMI_RXN[3..0]16

DMI_RXP[3..0]16

4

M_RCOMPN

M_RCOMPP

M_CKE011,12

M_CKE111,12

M_CKE211,12

M_CKE311,12

M_CS0#11,12

M_CS1#11,12

M_CS2#11,12

M_CS3#11,12

M_OCDCOMP0

M_OCDCOMP1

R163

R163

40D2R2F-GP

40D2R2F-GP

DY

DY

PM_EXTTS#0

PM_EXTTS#1

A

M_ODT011,12

M_ODT111,12

M_ODT211,12

M_ODT311,12

CLK_MCH_3GPLL#3

CLK_MCH_3GPLL3

D_REFSSCLK#3

D_REFSSCLK3

D_REFCLK#3

D_REFCLK3

TV_DACA

TV_DACB

TV_DACC

GMCH_BLUE

GMCH_GREEN

GMCH_RED

M_RCOMPN

M_RCOMPP

DMI_TXP3

4 4

12

R152

R152

40D2R2F-GP

40D2R2F-GP

DY

DY

DDR_VREF_S3

12

C548

C548

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3 3

3D3V_S0

2 2

1D8V_S3

1 1

C501

C501

1

2 3

12

R170

R170

80D6R2F-L-GP

80D6R2F-L-GP

12

R171

R171

80D6R2F-L-GP

80D6R2F-L-GP

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

RN41

RN41

SRN10KJ-5-GP

SRN10KJ-5-GP

B

CFGRSVD

CFGRSVD

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

B

PM

PM

PM_THRMTRIP#

MISC

MISC

SDVO_CTRLCLK

SDVO_CTRLDATA

NC

NC

3D3V_S0

RSVD_0

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PWROK

RSTIN#

LT_RESET#

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

R142

R142

1 2

DUMMY-R2

DUMMY-R2

R140

R140

1 2

DUMMY-R2

DUMMY-R2

R141

R141

1 2

DUMMY-R2

DUMMY-R2

R153

R153

1 2

DUMMY-R2

DUMMY-R2

R158

R158

1 2

DUMMY-R2

DUMMY-R2

R491

R491

1 2

DUMMY-R2

DUMMY-R2

R486

R486

1 2

DUMMY-R2

DUMMY-R2

R150

R150

1 2

DUMMY-R2

DUMMY-R2

R154

R154

1 2

DUMMY-R2

DUMMY-R2

R489

R489

1 2

DUMMY-R2

DUMMY-R2

R156

R156

1 2

DUMMY-R2

DUMMY-R2

R160

R160

1 2

2K2R2J-2-GP

2K2R2J-2-GP

R162

R162

1 2

DUMMY-R2

DUMMY-R2

R495

R495

1 2

DUMMY-R2

DUMMY-R2

R159

R159

1 2

DUMMY-R2

DUMMY-R2

R490

R490

1 2

DUMMY-R2

DUMMY-R2

R484

R484

1 2

DUMMY-R2

DUMMY-R2

R493

R493

1 2

DUMMY-R2

DUMMY-R2

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

U58B

U58B

H32

T32

R32

F3

F7

AG11

AF11

H7

J19

K30

J29

A41

A35

A34

D28

D27

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

G28

PM_EXTTS#0

F25

PM_EXTTS#1

H26

G6

GMCH_PWROK

AH33

AH34

H28

H27

K28

D1

C41

C1

BA41

BA40

BA39

BA3

BA2

BA1

B41

B2

AY41

AY1

AW41

AW1

A40

A4

A39

A3

DY

DY

CLKREQ_MCH

TP11 TPAD30TP11 TPAD30

TP12 TPAD30TP12 TPAD30

TP49 TPAD30TP49 TPAD30

TP42 TPAD30TP42 TPAD30

TP36 TPAD30TP36 TPAD30

TP37 TPAD30TP37 TPAD30

TP41 TPAD30TP41 TPAD30

TP31 TPAD30TP31 TPAD30

TP16 TPAD30TP16 TPAD30

TP23 TPAD30TP23 TPAD30

TP83 TPAD30TP83 TPAD30

TP10 TPAD30TP10 TPAD30

TP86 TPAD30TP86 TPAD30

TP25 TPAD30TP25 TPAD30

TP26 TPAD30TP26 TPAD30

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

1 2

GMCH_DDCCLK14

GMCH_DDCDATA14

CFG18

CFG19

CFG20

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CPU_SEL0 3,4

CPU_SEL1 3,4

CPU_SEL2 3,4

PM_BMBUSY# 16

PM_THRMTRIP-A# 4

R118

R118

100R2J-2-GP

100R2J-2-GP

MCH_ICH_SYNC# 16

SRN10KJ-5-GP

SRN10KJ-5-GP

When High 1K Ohm

CFG6:

0=Moby Dick ,1=Calistoga (default)

When Low choice

lower than 3.5K

Ohm

GMCH_PWROK

C

TP13 TPAD30TP13 TPAD30

for calistoga configuration

L_BKLTEN31

LDDC_CLK13

LDDC_DATA13

GMCH_LCDVDD_ON13

PLT_RST1# 16,20,22,26,30,31,32,34

3D3V_S0

4

RN87

RN87

1

2 3

GMCH_HSY14

GMCH_VSY14

TP85TPAD30 TP85TPAD30

TP9TPAD30 TP9TPAD30

LA_CLK#13

LA_CLK13

LB_CLK#13

LB_CLK13

LA_DATA#_013

LA_DATA#_113

LA_DATA#_213

LA_DATA_013

LA_DATA_113

LA_DATA_213

LB_DATA#_013

LB_DATA#_113

LB_DATA#_213

LB_DATA_013

LB_DATA_113

LB_DATA_213

TV_DACA14

TV_DACB14

TV_DACC14

GMCH_BLUE14

GMCH_GREEN14

GMCH_RED14

R147

R147

1 2

255R2F-L-GP

255R2F-L-GP

When PM replace to GM

DY

DY

R120

R120

1 2

0R2J-2-GP

0R2J-2-GP

R119

R119

1 2

0R2J-2-GP

C

0R2J-2-GP

L_BKLTEN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LIBG

L_LVBG

GMCH_LCDVDD_ON

R151

R151

1 2

4K99R2F-L-GP

4K99R2F-L-GP

GMCH_DDCCLK

GMCH_DDCDATAGMCH_DDCDATA

VGATE_PWRGD 16,38

PWROK 16,19

D32

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

B16

B18

B19

E23

D23

C22

B22

A21

B21

C26

C25

G23

H23

J30

J20

J22

U58C

U58C

CALISTOGA

CALISTOGA

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

SEL2

0

0

0

1

1 100M

1

1

D

LVDS

LVDS

TV

TV

VGA

VGA

L_BKLTEN

GMCH_LCDVDD_ON

LIBG

SEL1

SEL0

0

0

0

01200M

1

1

1

0

00333M

1

0

0

1

1

1

D

E

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

RN108

RN108

1

2 3

SRN100KJ-6-GP

SRN100KJ-6-GP

R466

R466

1 2

1K5R2F-2-GP

1K5R2F-2-GP

<Variant Name>

<Variant Name>

<Variant Name>

CPU

266M

133M

Title

Title

Title

166M

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

400M

A3

A3

A3

Reserved

Date: Sheet of

Date: Sheet of

Date: Sheet of

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

4

LCTLA_CLK

LCTLB_DATA

3D3V_S0

4

RN39

RN39

SRN10KJ-5-GP

SRN10KJ-5-GP

1

2 3

LDDC_CLK

LDDC_DATA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

GMCH (2 of 5)

GMCH (2 of 5)

GMCH (2 of 5)

AG1 -1

AG1 -1

AG1 -1

E

4

1

2 3

745Wednesday, January 18, 2006

745Wednesday, January 18, 2006

745Wednesday, January 18, 2006

1D5V_PCIE_S0

R127

R127

12

24D9R2F-L-GP

24D9R2F-L-GP

RN40

RN40

SRN10KJ-5-GP

SRN10KJ-5-GP

A

4 4

U58D

M_A_DQ[63..0]11

3 3

2 2

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U58D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

CALISTOGA

CALISTOGA

B

M_B_DQ[63..0]11

AU12

SA_BS_0

AV14

SA_BS_1

BA20

SA_BS_2

AY13

SA_CAS#

AJ33

SA_DM_0

AM35

SA_DM_1

AL26

SA_DM_2

AN22

SA_DM_3

AM14

SA_DM_4

AL9

SA_DM_5

AR3

SA_DM_6

AH4

SA_DM_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_RAS#

SA_WE#

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

SA_RCVENIN#

SA_RCVENOUT#

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

M_A_CAS# 11,12

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

Place Test PAD Near to Chip

as could as possible

M_A_BS#0 11,12

M_A_BS#1 11,12

M_A_BS#2 11,12

M_A_DM[7..0] 11

M_A_DQS[7..0] 11

M_A_DQS#[7..0] 11

M_A_A[13..0] 11,12

M_A_RAS# 11,12

TP29 TPAD30TP29 TPAD30

TP28 TPAD30TP28 TPAD30

M_A_WE# 11,12

C

U58E

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ9

AJ8

AJ5

AJ3

U58E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

CALISTOGA

CALISTOGA

D

AT24

SB_BS_0

AV23

SB_BS_1

AY28

SB_BS_2

AR24

SB_CAS#

AK36

SB_DM_0

AR38

SB_DM_1

AT36

SB_DM_2

BA31

SB_DM_3

AL17

SB_DM_4

AH8

SB_DM_5

BA5

SB_DM_6

AN4

SB_DM_7

AM39

SB_DQS_0

AT39

SB_DQS_1

AU35

SB_DQS_2

AR29

SB_DQS_3

AR16

SB_DQS_4

AR10

SB_DQS_5

AR7

SB_DQS_6

AN5

SB_DQS_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_WE#

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

M_B_CAS# 11,12

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7M_A_DQS5

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

SB_RCVENIN#

SB_RCVENOUT#

Place Test PAD Near to Chip

ascould as possible

E

M_B_BS#0 11,12

M_B_BS#1 11,12

M_B_BS#2 11,12

M_B_DM[7..0] 11

M_B_DQS[7..0] 11

M_B_DQS#[7..0] 11

M_B_A[13..0] 11,12

M_B_RAS# 11,12

M_B_WE# 11,12

TP34 TPAD30TP34 TPAD30

TP32 TPAD30TP32 TPAD30

1 1

A

B

C

D

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

GMCH (3 of 5)

GMCH (3 of 5)

GMCH (3 of 5)

AG1 -1

AG1 -1

AG1 -1

845Wednesday, January 18, 2006

845Wednesday, January 18, 2006

845Wednesday, January 18, 2006

E

of

A

B

C

D

E

2D5V_S0

C500

C500

2D5V_3GBG_S0

V_TVBG

V_DACA

V_DACB

V_DACC

1D5V_TVDAC_S0

R149

R149

C166

C166

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C184

C184

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C

12