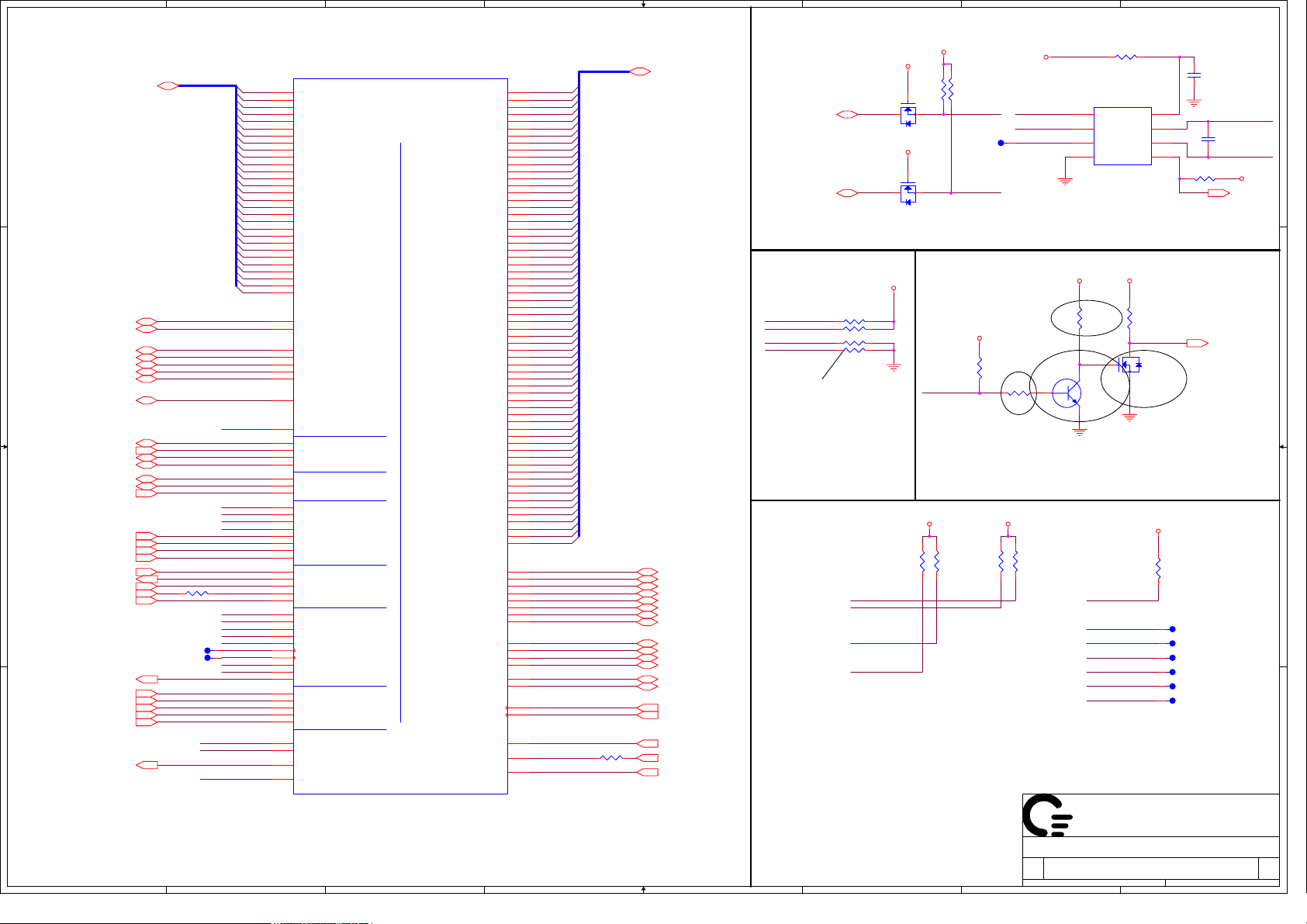

Acer TM800x Schematics

1

DC/DC

BATT SELECTOR

1.25VDDR

2.5VDDR

A A

PG 31

1.5V/1.8V

PG 32

BATT CHARGER

AC/BATT

CONNECTOR

CPU CORE

System Power

MAX1632

PG 34

DDR-SODIMM1

PG 10

DDR-SODIMM2

B B

PG 10

DDR-Termiation

PG 11

2

PG 37

PG 36

PG 33

266/200 MHZ DDR

3

4

ZI6 BLOCK DIAGRAM

CENTRINO

Banias/Dothan

(Micro-FCPGA)

PG 3,4

Montara-GM+

732 Micro-FCBGA

PG 5,6,7

66(266)MHZ, 1.8V

HUB I/F

4X100MHZ

AGP 1.5V, 66MHz

LVDS

TV out

DVOB

+2.5V

Video

Controller

+1.5V

ATI M11CSP64

VGA_CORE(+1.2V)

+1.8V

Chrontel 7009

TV EN-CONDE

5

CLOCKS

PG 12

DVI

R

LVDS

6

@:ZI66 Internal Gra.

#:ZI68 External Gra.

R

R

TV out

R

R.G,B

7

VGA

CARDBUS

IEEE 1394

MINI-PCI

LAN

USB 2.0

Panel Connector

DVI

CRT port

R

PIRQ#

X

C, (B)

B

E, F

D

X

REQ#/GNT#

X

3

2

1

0

X

Port Replicator

PS2 X2

1S1P

LINE-IN

LINE-OUT

MICROPHONE-IN

USB 1.1 X2

CRT

S-VIDEO

LAN

8

IDSEL

X

22

23

20

18

X

PG 30

Primary IDE

HDD

PG 17

ATA 66/100

Secondary IDE - Swap Bay

(Optical Drive, 2ND HDD)

C C

PG 17

USB 2.0

ICH4-M

421 BGA

PG 8,9

R.G,B

4-IN-1 SLOT

PG 19

USB connec*4

LED/B

Connector

PG 28

PG 19

SIO PC87391

3.3V LPC, 33MHz

PC87591

AC LINK

USB 1.1

AC LINK

MDC

CONNECTOR

PG 21

RJ11

100 Pins TQFP 176 Pins LQFP

D D

PG 26

2

Touchpad

PG 29

FAN 1,2

3

PG 26 PG 19

1

PG 26 PG 27 PG 29

ParallelFIR Keyboard FLASH

AUDIO

CODEC

4

PG 24

AUDIO

AMP

TPA0312

PG 25

5

33MHZ, 3.3V PCI

LAN

BCM5705M

PG 22

RJ45

PG 16

HEAD PHONE

LINE IN

EXT. /INT.

MIC

PG 24, 25

6

MINI-PCI

SOCKET

PG 21

CALEXICO

PG 21

CARDBUS

OZ711EC1

PG 18

CARDBUS SLOT

SCR SLOT

PG 18

IEEE-1394

TSB43AB21

PG 20

1394 CONN.

PG 20

QUANTA

Title

Size Document Number Re v

Date: Sheet

COMPUTER

Schematic Block Diagram1

ZI6

7

C

of

143Monday, January 12, 2004

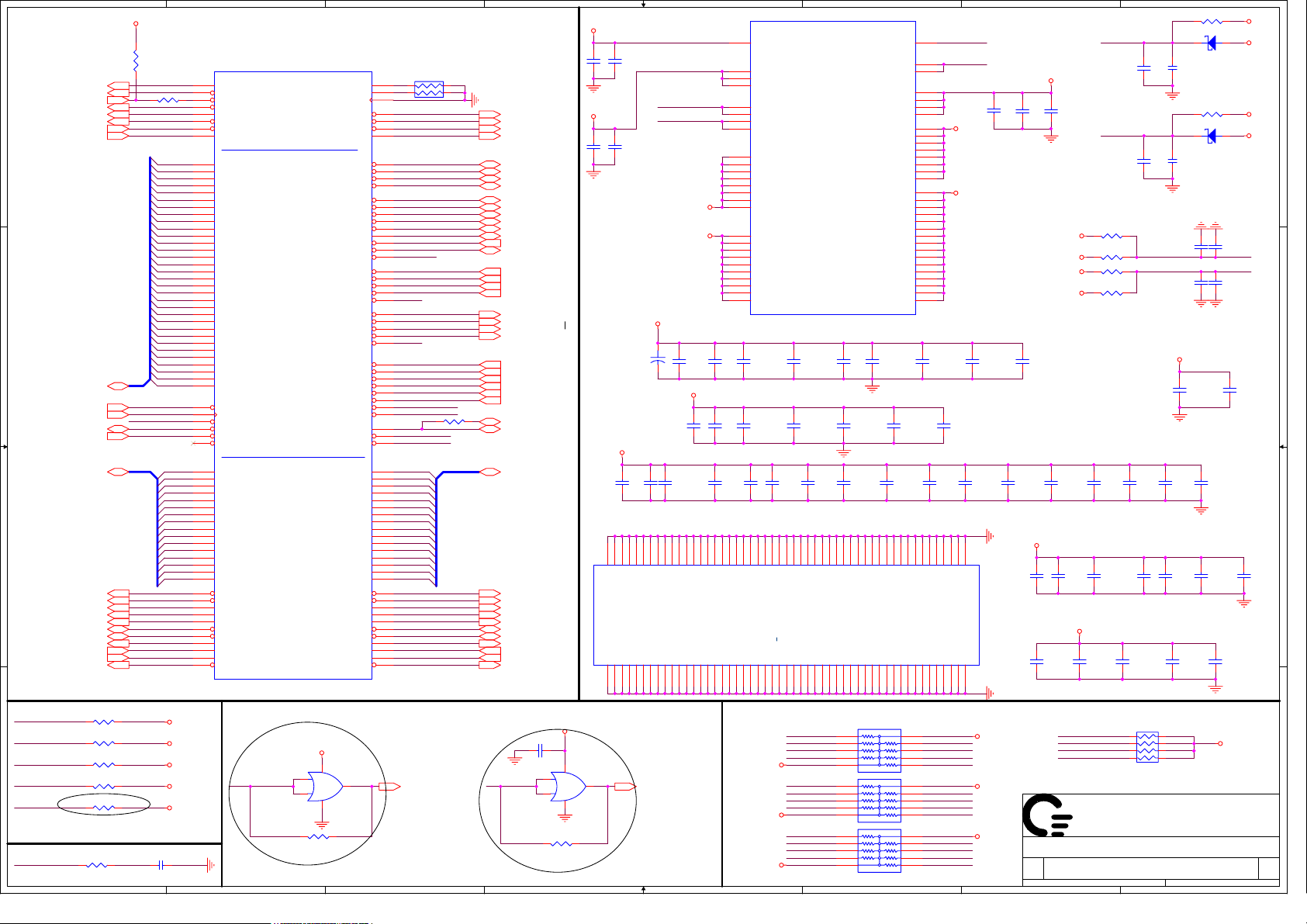

8

3

PU8

MAX1632

ALWAYS ON VOLTAGE

ENVL 3V_591

2

2.5VSUS

PU1

SC1565

VIN +1.8V

VOUT

1

5VPCU

C C

12VOUT

MAINON

CTRL

PQ10 NPN + PQ9 PMOS

PU4

SC1486

EN

2.5VSUS5VSUS

7.5A

VIN

CTRL

+12VVOUT12VOUT

MAINON

PQ5 SI5402

SMDDR_VTERM

NMOS

3A

VIN

+1.5VVOUT1.5V_S5

PU3

MAX1844

S5_ON

B B

EN

1.5V_S5

MAIND

PQ40 SI9936

PQ39 NPN

ES5_ON

2-NMOS

G3V_S5

G

S

S

5V_S5

DD

S5_LAN

S3_MODEM

PQ11 NPN

E

E

PQ12 NPN

3V_591 5VPCU

CTRL

PQ4 SI9936

2-NMOS

G

G

3V_591

D

S

S

D

3V_591

LANVCC

3V_MODEM

PU6

MAX1907

MAIND S

VRON

EN

VCC_CORE

25A

A A

PU2

SC338

VIN

DRV15VSUS

PQ1 SI9936

2-NMOS

G

S

VTT

PQ3 SI9936

2-NMOS

G

G

DD

3V_591

2.5VSUS

PQ38 SI9936

2-NMOS

+3V

+2.5VS

V TRANS CIRCUITSUSON SUSD

V TRANS CIRCUIT MAINDMAINON

(1.05V)

VRON

CTRL

DRV2

1.5V_S5

3

G 1.2VCCT

S

D

MAIND S

SUSD

G

G

DD

5VPCU 5VPCU

2

+5V

5VSUSS

QUANTA

Title

Size Document Number Re v

Date: Sheet

COMPUTER

POWER BLOCK DIAGRAM

ZI6

1

of

243Monday, January 12, 2004

C

1

2

3

4

5

6

7

8

+3V

MBDATA

MBCLK

TDI

TMS

TDO

CPURST#

+5V

2

3 1

Q37

RHU002N06

+5V

2

3 1

Q35

RHU002N06

VTT

VTT VTT

R440

54.9/F

R330

R328

10K

10K

THDAT_SMB

THCLK_SMB

R333

56/F

CPU_PROCHOT#

R435

*54.9/F

VTT

HA#[3..31]<5>

A A

HADSTB0#<5>

B B

C C

D D

HADSTB1#<5>

HREQ#0<5>

HREQ#1<5>

HREQ#2<5>

HREQ#3<5>

HREQ#4<5>

ADS#<5>

HBREQ0#<5>

BPRI#<5>

BNR#<5>

HLOCK#<5>

HIT#<5>

HITM#<5>

DEFER#<5>

HTRDY#<5>

RS#0<5>

RS#1<5>

RS#2<5>

A20M#<8>

FERR#<8>

IGNNE#<8>

CPUPWRGD<9>

SMI#<8>

DBR#<9>

INTR<8>

NMI<8>

STPCLK#<8>

CPUSLP#<8>

DPSLP#<6,8>

THERMTRIP#<9>

HA#[3..31]

R513 0

T29 * PAD

T28 * PAD

IERR#

BPM0#

BPM1#

BPM2#

BPM3#

A20M#

FERR#

IGNNE#

R_CPUPWRGD

SMI#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

DBR#

STPCLK#

CPUSLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

CPU_PROCHOT#

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A13

A12

C12

C11

B13

A16

A15

B10

A10

B18

A18

C17

B17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

N2

A4

N4

J3

L1

J2

K3

K4

L4

C8

B8

A9

C9

M3

H1

K1

L2

C2

D3

A3

E4

B4

A7

D1

D4

C6

A6

B7

U21A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BPM0#

BPM1#

BPM2#

BPM3#

TRDY#

RS0#

RS1#

RS2#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

ITP_CLK0

ITP_CLK1

PREQ#

PRDY#

DBR#

LINT0

LINT1

STPCLK#

SLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

Banias_Processor

Banias

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

1 OF 3

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DBI0#

DBI1#

DBI2#

DBI3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

A19

D0#

A25

D1#

A22

D2#

B21

D3#

A24

D4#

B26

D5#

A21

D6#

B20

D7#

C20

D8#

B24

D9#

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

CPUINIT#

B5

R_CPURST#

B11

C19

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

R515 0

HD#[0..63] <5>

HDSTBN0# <5>

HDSTBP0# <5>

HDSTBN1# <5>

HDSTBP1# <5>

HDSTBN2# <5>

HDSTBP2# <5>

HDSTBN3# <5>

HDSTBP3# <5>

HDBI0# <5>

HDBI1# <5>

HDBI2# <5>

HDBI3# <5>

DBSY# <5>

DRDY# <5>

HCLK_CPU# <12>

HCL K_CPU <12>

CPUINIT# <8>

CPURST# <5>

DPW R# <6>

MBDATA<23,31>

MBCLK<31,42> 6648_OVT# <33>

IERR#

CPUPWRGD

TCK

TRST#

R520 56

R519 330

R322 27.4/F

R516 680

R516 should

be place

within 2" of

the processor ;

others place

near ITP

Del ITP700

Del R434,R439,C542,R442

T117

*PAD

For ATE

R431

39.2/F

R332

*330

+3V

THCLK_SMB

THDAT_SMB

12

2

R428

150

+3V

8

7

6

5

MAX6648

R336

*2K/F

Q40

*MMBT3904

1 3

SMCLK

SMDATA

-ALT

GND

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

R325 150/F

U26

VCC

DXP

DXN

-OVT

+3V

R337

330

1 2

31

2

*RHU002N06

DBR#

1

2

3

4

ICH_THRM#

Q44

+3V

R443

150

T120 *PA D

T121 *PA D

T122 *PA D

T124 *PA D

T125 *PA D

T126 *PA D

C415

0.1U/50V

1 2

R324 1K

ICH_T HRM# <9,33>

C407

2200P

12

THERMDA

THERMDC

+3V

QUANTA

Title

Size Document Number Re v

1

2

3

4

5

6

Date: Sheet

COMPUTER

Banias Processor (HOST)

ZI6

7

C

of

343Monday, January 12, 2004

8

1

These 4 Resistors need to place with 0.5'' of CPU.

Comp0,2 trace need to be zo=27.4 ohm,

comp1,3 traces need to be zo=55 ohm.

A A

CPU_VCCA

B B

C C

VTT

D D

VTT

C730

+

150U/6.3V

SPC

CC7343

C664

10U/6.3V

X5R

C583

10U/6.3V

X5R

C650

10U/6.3V

X5R

C375

10U/6.3V

X5R

C665

10U/6.3V

X5R

C572

10U/6.3V

X5R

C651

10U/6.3V

X5R

C383

10U/6.3V

X5R

VCC_CORE

C698

1000P/50V

C770

+

*150U/6.3V

SPC

CC7343

R308

27.4/F

C396

C399

0.01U/50V

0.01U/50V

VCC_CORE

C603

10U/6.3V

X5R

VCC_CORE VCC_CORE

C608

10U/6.3V

X5R

VCC_CORE

C640

10U/6.3V

X5R

VCC_CORE

C358

10U/6.3V

X5R

C700

C610

1000P/50V

1000P/50V

C387

.01U/25V_0402

1

R307

54.9/F

C311

*10U/6.3V

X5R

C577

*10U/6.3V

X5R

C619

10U/6.3V

X5R

C351

10U/6.3V

X5R

C699

1000P/50V

C366

.01U/25V_0402

R291

27.4/F

C337

0.01U/50V

C590

10U/6.3V

X5R

C578

*10U/6.3V

X5R

C679

10U/6.3V

X5R

C782

10U/6.3V

X5R

C611

1000P/50V

2

COMP0

COMP1

COMP2

COMP3

R290

54.9/F

C335

C338

10U/6.3V

0.01U/50V

X5R

C594

10U/6.3V

X5R

C629

10U/6.3V

X5R

C380

10U/6.3V

X5R

10U/6.3V Total

caps (X5R)

33PCS=330U

VTT

C392

0.1U/50V

C364

C359

0.01U/50V

.01U/25V_0402

2

C582

10U/6.3V

X5R

C628

10U/6.3V

X5R

C783

10U/6.3V

X5R

C701

C356

0.1U/50V

C350

.01U/25V_0402

C393

10U/6.3V

X5R

VCC_CORE

C581

10U/6.3V

X5R

C639

10U/6.3V

X5R

VCC_CORE

C781

10U/6.3V

X5R

C379

0.1U/50V

C662

10U/6.3V

X5R

10U/6.3V

X5R

C697

0.1U/50V

VTT

C580

C355

10U/6.3V

X5R

0.1U/50V

C391

0.1U/50V

3

C648

10U/6.3V

X5R

C310

*10U/6.3V

X5R

C365

10U/6.3V

X5R

C378

.01U/25V_0402

C348

C370

0.1U/50V

0.1U/50V

3

C680

10U/6.3V

X5R

C386

0.1U/50V

A0 CPU install R514 R502

A1 CPU not install R514 R502

C390

0.1U/50V

4

GTLREF: 2/3 VCCP+-2%

T<0.5" 25 mils space

VTT

R299

1K/F

R296

2K/F

R514

*1K

+1.8V

+1.5V

1.5V option is not used.

It is ok to leave in there.

4

R319

R300

TEST1

TEST2

R502

*1K

CPU_VCCA

0_0805

*0_0805

COMP0

COMP1

COMP2

COMP3

GTLREF0

VCC_CORE

5

25 MILS (>50 MILS PREFFERD) SPACE

T < 0.5"

U21B

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TEST1

TEST2

VCCA3

VCCA2

VCCA1

VCCA0

VCC00

VCC01

VCC02

VCC03

VCC04

VCC05

VCC06

VCC07

VCC08

VCC09

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Banias_Processor

Banias

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

AD26

AC26

AA11

AA13

AA15

AA17

AA19

AA21

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC11

AC13

AC15

AC17

AC19

AD10

AD12

AD14

AD16

AD18

AE11

AE13

AE15

AE17

AE19

AF10

AF12

AF14

AF16

AF18

5

E26

AC1

D18

D20

D22

E17

E19

E21

G21

H22

K22

V22

W21

Y22

AA5

AA7

AA9

AB6

AB8

AC9

AD8

AE9

AF8

G1

C5

F23

N1

B1

F26

D6

D8

E5

E7

E9

F6

F8

F18

F20

F22

G5

H6

J5

J21

U5

V6

W5

Y6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

6

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

CPU_VID0<38>

CPU_VID1<38>

CPU_VID2<38>

CPU_VID3<38>

CPU_VID4<38>

CPU_VID5<38>

R474 *54.9/F

R481 *54.9/F

T91 *P AD

T41 *P AD

T30 *P AD

T90 *P AD

T89 *P AD

R326

*1K

7

VTT

U21C

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

L5

L21

M6

M22

N5

N21

P6

P22

R5

R21

T6

T22

U21

P23

W4

E2

F2

F3

G3

G4

H4

AE7

AF6

B2

AF7

C14

C3

C16

E1

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

*

POWER, GR OUND AND NC

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VID0

VID1

VID2

VID3

VID4

VID5

VCCSENSE

VSSSENSE

NC0

NC1

NC2

NC3

TEST3

PSI

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC,BOOT 1.2V

VCC_CORE 1.468V

(DEEPER SLEEP) 0.956V

VTT 1.05V

VCCA 1.8V

Banias

3 OF 3

VID

Banias_Processor

8

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

QUANTA

Title

Size Document Number Re v

6

Date: Sheet

COMPUTER

Banias Processor (POWER)

ZI6

7

C

of

443Monday, January 12, 2004

8

1

HA#[3..31]<3> HD#[0..63] <3>

A A

B B

C C

HUBSWING_MCH

1.2VCCT

HUBVREF_GMCH

HA#[3..31]

ADS#<3>

HADSTB0#<3>

HADSTB1#<3>

HREQ#0<3>

HREQ#1<3>

HREQ#2<3>

HREQ#3<3>

HREQ#4<3>

RS#0<3>

RS#1<3>

RS#2<3>

DBSY#<3>

BPRI#<3>

BNR#<3>

HBREQ0#<3>

HLOCK#<3>

HIT#<3>

HITM#<3>

DRDY#<3>

HTRDY#<3>

DEFER#<3 >

CPURST#<3>

HCLK_MCH<12>

HCLK_MCH#<12>

R501 27.4/F

R528 27.4/F

HL[0..10]<9>

HLSTB<9>

HLSTB#<9>

R476 37.4/F

C326

0.01U/50V

HL[0..10]

HXSWING

HYSWING

HXRCOMP

HYRCOMP

12

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HLRCOMP

12

2

P23

T25

T28

R27

U23

U24

R24

U28

V28

U27

T27

V27

U25

V26

Y24

V25

V23

W25

Y25

AA27

W24

W23

W27

Y27

AA28

W28

AB27

Y26

AB28

L28

T26

AA26

R28

P25

R23

R25

T23

N23

P26

M27

M26

P28

N25

M23

P27

N27

N28

N24

M25

M28

F15

AE29

AD29

B18

K28

B20

H28

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

C312

0.01U/50V

U22A

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

ADS#

HADSTB#0

HADSTB#1

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

RS#0

RS#1

RS#2

DBSY#

BPRI#

BNR#

BREQ0#

HLOCK#

HIT#

HITM#

DRDY#

HTRDY#

DEFER#

CPURST#

BCLK

BCLK#

HXSWING

HYSWING

HXRCOMP

HYRCOMP

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

HLSTB

HLSTB#

HLRCOMP

PSWING

HLVREF

HOST

HUB I/F

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

DINV#0

DINV#1

DINV#2

DINV#3

HDSTBN#0

HDSTBP#0

HDSTBN#1

HDSTBP#1

HDSTBN#2

HDSTBP#2

HDSTBN#3

HDSTBP#3

HAVREF

HCCVREF

HDVREF0

HDVREF1

HDVREF2

Montara-GM+

3

HD#[0..63]

HD#0

K22

HD#1

H27

HD#2

K25

HD#3

L24

HD#4

J27

HD#5

G28

HD#6

L27

HD#7

L23

HD#8

L25

HD#9

J24

HD#10

H25

HD#11

K23

HD#12

G27

HD#13

K26

HD#14

J23

HD#15

H26

HD#16

F25

HD#17

F26

HD#18

B27

HD#19

H23

HD#20

E27

HD#21

G25

HD#22

F28

HD#23

D27

HD#24

G24

HD#25

C28

HD#26

B26

HD#27

G22

HD#28

C26

HD#29

E26

HD#30

G23

HD#31

B28

HD#32

B21

HD#33

G21

HD#34

C24

HD#35

C23

HD#36

D22

HD#37

C25

HD#38

E24

HD#39

D24

HD#40

G20

HD#41

E23

HD#42

B22

HD#43

B23

HD#44

F23

HD#45

F21

HD#46

C20

HD#47

C21

HD#48

G18

HD#49

E19

HD#50

E20

HD#51

G17

HD#52

D20

HD#53

F19

HD#54

C19

HD#55

C17

HD#56

F17

HD#57

B19

HD#58

G16

HD#59

E16

HD#60

C16

HD#61

E17

HD#62

D16

HD#63

C18

J25

E25

B25

G19

J28

K27

C27

D26

E22

E21

D18

E18

HAVREF

Y22

HCCVREF

Y28

K21

J21

J17

HDBI0# <3>

HDBI1# <3>

HDBI2# <3>

HDBI3# <3>

HDSTBN0# <3>

HDSTBP0# <3>

HDSTBN1# <3>

HDSTBP1# <3>

HDSTBN2# <3>

HDSTBP2# <3>

HDSTBN3# <3>

HDSTBP3# <3>

HDVREF

C685

1U/10V_0805

12

C710

0.1U/50V

C707

0.1U/50V

C693

0.1U/50V

4

VTT

R_MA[0..12]

R503

49.9/F

R500

100/F

R_SM_DQS[0..7]

R_SDM[0..7]

5

R_MA1<10 ,11>

R_MA2<10 ,11>

R_MA4<10 ,11>

R_MA5<10 ,11>

T80 *P AD

SMA_B1<10,11>

SMA_B2<10,11>

SMA_B4<10,11>

SMA_B5<10,11>

-SM_CS0<10,11>

-SM_CS1<10,11>

-SM_CS2<10,11>

-SM_CS3<10,11>

T27 *P AD

R_BA0< 10,11>

R_BA1< 10,11>

R_SRASA#<10,11>

R_SCASA#<10,11>

R_BMWEA#<10,11>

CKE0<10,11>

CKE1<10,11>

CKE2<10,11>

CKE3<10,11>

CLK_SDRAM0<10>

CLK_SDRAM0#<10>

CLK_SDRAM1<10>

CLK_SDRAM1#<10>

CLK_SDRAM2<10>

CLK_SDRAM2#<10>

CLK_SDRAM3<10>

CLK_SDRAM3#<10>

CLK_SDRAM4<10>

CLK_SDRAM4#<10>

CLK_SDRAM5<10>

CLK_SDRAM5#<10>

SMDDR_VREF

R_MA[ 0..12] <10,11>

R_SM_ DQS[0..7] <11>

R_SDM[0..7] <11>

+2.5V +2.5V

C406

0.1U/50V

6

R_MA0

R_MA1

R_MA2

R_MA3

R_MA4

R_MA5

R_MA6

R_MA7

R_MA8

R_MA9

R_MA10

R_MA11

R_MA12

R_SM_DQS0

R_SM_DQS1

R_SM_DQS2

R_SM_DQS3

R_SM_DQS4

R_SM_DQS5

R_SM_DQS6

R_SM_DQS7

R_SM_DQS8

SMA_B1

SMA_B2

SMA_B4

SMA_B5

-SM_CS1

-SM_CS2

-SM_CS3

R_SDM0

R_SDM1

R_SDM2

R_SDM3

R_SDM4

R_SDM5

R_SDM6

R_SDM7

R_SDM8

R_BA0

R_BA1

R_SRASA#

R_SCASA#

R_BMWEA#

CKE0

CKE1

CKE2

CKE3

SMRCOMP

SMVSWINGH

SMVSWINGL

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

AD16

AC12

AF11

AD10

AD23

AD26

AC22

AC25

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

AD22

AD20

AC21

AC24

AD25

AC7

AB7

AC9

AC10

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AJ24

AB1

AJ19

AJ22

U22C

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SMA_B1

SMA_B2

SMA_B4

SMA_B5

SCS#0

SCS#1

SCS#2

SCS#3

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SDM8

SBA0

SBA1

SRAS#

SCAS#

SWE#

SCKE0

SCKE1

SCKE2

SCKE3

SCMDCLK0

SCMDCLK#0

SCMDCLK1

SCMDCLK#1

SCMDCLK2

SCMDCLK#2

SCMDCLK3

SCMDCLK#3

SCMDCLK4

SCMDCLK#4

SCMDCLK5

SCMDCLK#5

SMVREF

SMRCOMP

SMVSWINGH

SMVSWINGL

7

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

DDR 200/266 MHz

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

SRCVENIN#

SRCVENOUT#

Montara-GM+

R_MD0

AF2

R_MD1

AE3

R_MD2

AF4

R_MD3

AH2

R_MD4

AD3

R_MD5

AE2

R_MD6

AG4

R_MD7

AH3

R_MD8

AD6

R_MD9

AG5

R_MD10

AG7

R_MD11

AE8

R_MD12

AF5

R_MD13

AH4

R_MD14

AF7

R_MD15

AH6

R_MD16

AF8

R_MD17

AG8

R_MD18

AH9

R_MD19

AG10

R_MD20

AH7

R_MD21

AD9

R_MD22

AF10

R_MD23

AE11

R_MD24

AH10

R_MD25

AH11

R_MD26

AG13

R_MD27

AF14

R_MD28

AG11

R_MD29-SM_CS0

AD12

R_MD30

AF13

R_MD31

AH13

R_MD32

AH16

R_MD33

AG17

R_MD34

AF19

R_MD35

AE20

R_MD36

AD18

R_MD37

AE18

R_MD38

AH18

R_MD39

AG19

R_MD40

AH20

R_MD41

AG20

R_MD42

AF22

R_MD43

AH22

R_MD44

AF20

R_MD45

AH19

R_MD46

AH21

R_MD47

AG22

R_MD48

AE23

R_MD49

AH23

R_MD50

AE24

R_MD51

AH25

R_MD52

AG23

R_MD53

AF23

R_MD54

AF25

R_MD55

AG25

R_MD56

AH26

R_MD57

AE26

R_MD58

AG28

R_MD59

AF28

R_MD60

AG26

R_MD61

AF26

R_MD62

AE27

R_MD63

AD27

AG14

T81 *PAD

AE14

T78 *PAD

AE17

T85 *PAD

AG16

T86 *PAD

AH14

T79 *PAD

AE15

T82 *PAD

AF16

T83 *PAD

AF17

T88 *PAD

AC16

T87 *PAD

AC15

T84 *PAD

remove RCVENIN#

and RCVENOUT#

R_MD[0..63]

+2.5V

8

R_MD [0..63] <11>

C561

0.1U/50V

5

R472

60.4/F

SMRCOMP SMVSWINGH SMVSWINGL

R471

60.4/F

6

+1.5V

C787

0.1U/50V

VTT

R526

49.9/F

R525

C784

100/F

1U/10V_0805

R294

C586

0.1U/50V

2

255/F

HUBSWING_MCH

R297

162/F

HUBVREF_GMCH

12

R293

C313

127/F

0.1U/50V

12

C325

0.1U/50V

HAVREF

C777

1U/6.3V

3

VTT VTT

R313

D D

301/F

R316

150/F

HXSWING

C400

0.01U/50V

R524

301/F

HYSWING

R522

C795

150/F

0.01U/50V

1

HCCVREF

12

C785

0.1U/50V

4

VTT

R521

49.9/F

R523

100/F

C394

0.1U/50V

R312

150/F

R309

604/F

R315

604/F

C398

0.1U/50V

C384

0.1U/50V

R317

150/F

QUANTA

Title

Size Document Number Re v

Date: Sheet

COMPUTER

Montara - GM+ ( HOST & DDR )

ZI6

7

543Monday, January 12, 2004

8

C402

0.1U/50V

C

of

1

2

3

4

5

6

7

+3V

8

R857 @2.2K_0402

R858 @2.2K_0402

R292 *4.7K

R491 *4.7K

+3V

R487 @10K

R484 10K

+1.5V

R486 @2.2K

R479 @2.2K

R482 @100K

R865 #1K_0402

R811 @1K_0402

+1.5V

If no DVO port, Pull down (RDDP, p207)

R854 *100K

R289 *100K

R288 @100K

R480 @100K

R287 @1K

+1.5V

R493

@10K

DPMSCLK

@RHU002N06

Q75

DREFCLK48

CLK66_MCH

31

2

R496

1 2

22

R492

22

AA29

W29

U29

N29

G29

E29

C29

AE28

AC28

E28

D28

AJ27

AG27

AC27

F27

A27

AJ26

AB26

W26

U26

R26

N26

G26

AE25

AA25

D25

A25

AG24

AA24

V24

T24

P24

M24

K24

H24

F24

B24

AJ23

AC23

AA23

D23

A23

AE22

W22

U22

R22

N22

F22

C22

AG21

AB21

AA21

Y21

V21

T21

P21

M21

H21

D21

A21

AJ20

AC20

AA20

AE19

AB19

H19

D19

A19

AJ18

AG18

AA18

F18

AC17

AB17

U17

R17

N17

H17

D17

A17

AE16

AA16

T16

U22E

DVOBD0

DVOBCLK

DVOBCLK#

GAD0

DVOBHSYNC

GAD1

DVOBVSYNC

DVOBLANK#

GAD14

DVOBFLDSTL

GAD30

DVOBINTRB#

GAD13

DVOBCLKINT

GTRDY#/DVICLK

GFRAME#/DVIDATA

GPAR

GAD3

DVOBD1

GAD2

DVOBD2

GAD5

DVOBD3

GAD4

DVOBD4

GAD7

DVOBD5

GAD6

DVOBD6

GAD8

GCBE0#

GAD10

GAD9

GAD12

GAD11

GAD19

GAD20

GAD21

GAD22

GAD23

GCBE3#

GAD25

GAD24

GAD27

GAD26

GAD29

GAD28

GAD17

GAD16

GAD18

GAD31

GAD15

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

DPMSCLK

AGP_BUSY#

CLK66_MCH

DVORCOMP

VREF

C329

0.1U/50V

VSS0

VSS1

VSS2

VSS3

L29

VSS4

J29

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

L26

VSS24

J26

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

L22

VSS51

J22

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

J20

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

J18

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

Montara-GM+

P16

J16

F16

AG15

AB15

U15

R15

N15

H15

D15

AC14

AA14

T14

P14

J14

AE13

AB13

U13

R13

N13

H13

F13

D13

A13

AJ12

AG12

AA12

J12

AJ11

AC11

AB11

H11

F11

D11

AJ10

AE10

AA10

J10

C10

AG9

AB9

W9

U9

T9

R9

N9

L9

E9

AC8

Y8

V8

T8

P8

K8

H8

AJ7

AE7

AA7

R7

M7

J7

G7

E7

C7

AG6

Y6

L6

Y5

U5

B5

AE4

AC4

AA4

W4

T4

N4

K4

G4

D4

AJ3

AG3

R2

AJ1

AE1

AA1

U1

L1

G1

C1

F20

GTRDY#/DVICLK<13>

GFRAME#/DVIDATA<13>

AGP_BUSY#<9,13>

CLK66_MCH<12>

VREF<13,17>

Check AGP_BUSY# on ext VGA

GTRDY#/DVICLK

GFRAME#/DVIDATA

AD_STB0<13,17>

AD_STB0#<13,17>

GAD0<13,17>

GAD1<13,17>

GCBE1#<13,17>

GAD14<13,17>

GAD30<13,17>

GAD13<13,17>

SBA[0..7]<13>

GPAR<13>

AD_STB1#<13>

GIRDY#<13,17>

GDEVSEL#<13,17>

R295 40.2/F

GAD3<13,17>

GAD2<13,17>

GAD5<13,17>

GAD4<13,17>

GAD7<13,17>

GAD6<13,17>

GAD8<13,17>

GCBE0#<13,17>

GAD10<13,17>

GAD9<13,17>

GAD12<13,17>

GAD11<13,17>

GAD19<13>

GAD20<13>

GAD21<13>

GAD22<13>

GAD23<13>

GCBE3#<13>

GAD25<13>

GAD24<13>

GAD27<13>

GAD26<13>

GAD29<13>

GAD28<13>

AD_STB1<13>

GAD17<13>

GAD16<13>

GCBE2#<13>

GAD18<13>

GAD31<13>

GSTOP#<13>

GAD15<13>

R775 @0_0402

R776 @0_0402

A A

B B

C C

D D

DVOBD7

DVOBD8

DVOBD9

DVOBD10

DVOBD11

U22B

R3

DVOBD0/GAD3

R5

DVOBD1/GAD2

R6

DVOBD2/GAD5

R4

DVOBD3/GAD4

P6

DVOBD4/GAD7

P5

DVOBD5/GAD6

N5

DVOBD6/GAD8

P2

DVOBD7/GCBE#0

N2

DVOBD8/GAD10

N3

DVOBD9/GAD9

M1

DVOBD10/GAD12

M5

DVOBD11/GAD11

P3

DVOBCLK/GADSTB0

P4

DVOBCLK#/GADSTB0#

T6

DVOBHSYNC/GAD0

T5

DVOBVSYNC/GAD1

L2

DVOBLANK#/GCBE#1

M2

DVOBFLDSTL/GAD14

G2

DVOBINTRB#/GAD30

M3

DVOBCLKINT/GAD13

K5

DVOCD0/GAD19

K1

DVOCD1/GAD20

K3

DVOCD2/GAD21

K2

DVOCD3/GAD22

J6

DVOCD4/GAD23

J5

DVOCD5/GCBE#3

H2

DVOCD6/GAD25

H1

DVOCD7/GAD24

H3

DVOCD8/GAD27

H4

DVOCD9/GAD26

H6

DVOCD10/GAD29

G3

DVOCD11/GAD28

J3

DVOCCLK/GADSTB1

J2

DVOCCLK#/GADSTB1#

K6

DVOCHSYNC/GAD17

L5

DVOCVSYNC/GAD16

L4

RVSD4/GCBE#2

L3

DVOCBLANK#/GAD18

H5

DVOCFLDSTL/GAD31

K7

I2CCLK/GIRDY#

N6

I2CDATA/GDEVSEL#

N7

DVICLK/GTRDY#

M6

DVIDATA/GFRAME#

P7

DVI2CLK/GSTOP#

T7

DVI2DATA/GAD15

E5

ADDID0/GSBA0

F5

ADDID1/GSBA1

E3

ADDID2/GSBA2

E2

ADDID3/GSBA3

G5

ADDID4/GSBA4

F4

ADDID5/GSBA5

G6

ADDID6/GSBA6

F6

ADDID7/GSBA7

L7

ADDETECT/GPAR

D5

DPMS/GPIPE#

F7

AGPBUSY#

Y3

CLK66IN

D1

DVORCOMP

F1

GVREF

A2

NC11

B1

NC10

AH1

NC9

AJ2

NC8

AJ4

NC7

AA9

NC6

A28

NC5

AJ28

NC4

A29

NC3

B29

NC2

AH29

NC1

AJ29

NC0

DVO

MISC

RVSD10/GSBSTB

RVSD6/GSBSTB#

RVSD13/GGNT#

RVSD11/GWBF#

DVIC LK <18>

DVIDAT A <18>

IYAM0

IYAP0

IYAM1

IYAP1

IYAM2

IYAP2

IYAM3

IYAP3

ICLKAM

ICLKAP

IYBM0

IYBP0

IYBM1

IYBP1

IYBM2

IYBP2

LVDSDAC

IYBM3

IYBP3

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

LCDVCCEN

BLKCTL

BLKEN

LIBG

RED

GRN

RED#

GRN#

BLU#

HSYNC

VSYNC

DDCACLK

DDCADATA

REFSET

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

DPWR#

DPSLP#

RSTIN#

PWROK

EXTTS0

RVSD14

RVSD3

RVSD2

RVSD1

RVSD0

GST0

GST1

GST2

RVSD9/GREQ#

RVSD7/GRBF#

Montara-GM+

BLU

LVDS_NB_L0-

G14

LVDS_NB_L0+

F14

LVDS_NB_L1-

E15

LVDS_NB_L1+

E14

LVDS_NB_L2-

C15

LVDS_NB_L2+

C14

C13

B13

LVDS_NB_LC-

D14

LVDS_NB_LC+

E13

LVDS_NB_U0-

H12

LVDS_NB_U0+

G12

LVDS_NB_U1-

E12

LVDS_NB_U1+

E11

LVDS_NB_U2-

C12

LVDS_NB_U2+

C11

G11

G10

LVDS_NB_UC-

E10

LVDS_NB_UC+

F10

PNL_CLK_NB

B4

PNL_DATA_NB

C5

A5

G8

F8

R497 1.5K/F

A10

A7

C8

C9

A8

D8

D9

R477 @39

H10

R475 @39

J9

B6

G9

E8

B7

B17

H9

C6

AA22

Y23

AD28

J11

D6

D7

AA5

B12

D12

F12

C4

C3

C2

F2

F3

B3

B2

D3

D2

DISP_ON_NB

T69 *PAD

IREF

DREFCLK48

SSCLK66

LCLKCTLA

LCLKCTLB

EXTTS0

T77 *PAD

T73 *PAD

T72 *PAD

T71 *PAD

R845 @0_0402

R846 @0_0402

BLON_NB

NBHSYNC

NBVSYNC

NB_DDCCLK

NB_DDCDAT

R495 127/F

R847 @0_0402

R848 @0_0402

NB_RED

NB_GRN

NB_BLU

R483 0

R478 *0

R490 *0

ST0 <13>

ST1 <13>

ST2 <13>

SB_STB <13>

SB_STB# <13>

GREQ# <13>

GGNT# <13>

GRB F# <13>

GWBF # <13>

LVDS_NB_L0- <18>

LVDS_NB_L0+ <18>

LVDS_NB_L1- <18>

LVDS_NB_L1+ <18>

LVDS_NB_L2- <18>

LVDS_NB_L2+ <18>

LVDS_NB_LC- <18>

LVDS_N B_LC+ <18>

LVDS _NB_U0- <18>

LVDS_N B_U0+ <18>

LVDS _NB_U1- <18>

LVDS_N B_U1+ <18>

LVDS _NB_U2- <18>

LVDS_N B_U2+ <18>

LVDS_ NB_UC- <18>

LVDS_ NB_UC+ <18>

NB_R ED <16>

NB_G RN <16>

NB_BL U <16>

NBHSYNC <16>

NB VSYN C <16>

NB_DDCCLK <16>

NB_DDCDAT <16>

DREF CLK48 <12>

SSCLK66 <12>

LCLKCTLA <12,17>

LCLKCTLB <12,17>

DPWR# <3>

DPSLP# <3,8>

PCIRST1# <8,17,20,21,24>

PNL_CL K <13,18>

PNL_DATA <13,18>

PWRO K <9,31>

PWROK_DELAY <9>

HWPG_POWE R-G <9,12,27,31>

DISP_ ON <13,18>

BLON < 13,18>

PNL_CLK_NB

PNL_DATA_NB

LCLKCTLA

LCLKCTLB

AGP_BUSY#

EXTTS0

GIRDY#

GDEVSEL#

GAD30

DVOBINTRB#

GAD13

GAD31

DVOCFLDSTL

GAD14

DVOBFLDSTL

SBA7

ADDID7

SUSCL K <9,21>

C614

*12P

C593

5P

GPAR

DVOBCCLKINT

QUANTA

Title

Size Document Number Re v

1

2

3

4

5

6

Date: Sheet

COMPUTER

Montara - GM+ ( DDR & DVO )

ZI6

7

C

of

643Monday, January 12, 2004

8

1

2

3

4

5

6

7

8

C658

0.1U/50V

C362

0.1U/50V

C423

0.1U/50V

VCCAHPLL

C422

0.1U/50V

VCCAGPLL

C333

0.1U/50V

C647

VCCTXLVDS

C630

C763

1000P/50V

C425

0.1U/50V

VCCDLVDS

0.1U/50V

0.1U/50V

C373

0.1U/50V

C634

0.1U/50V

C748

1000P/50V

C421

0.1U/50V

C381

0.1U/50V

C631

0.1U/50V

C776

1000P/50V

U22D

0.1U/50V

C681

C667

C323

0.1U/50V

+3V

0.1U/50V

C653

0.1U/50V

0.1U/50V

C714

0.1U/50V

0.1U/50V

C330

0.1U/50V

C624

0.1U/50V

C308

10U/6.3V

+1.5V

C652

0.1U/50V

C676

C609

0.1U/50V

C636

0.1U/50V

C668

0.1U/50V

C691

0.1U/50V

C599

0.1U/50V

0.1U/50V

C675

0.1U/50V

C587

0.1U/50V

C670

0.1U/50V

C315

0.1U/50V

C623

VCCDA

VSSDA

1.2VCCT VTT

1.2VCCT

1.2VCCT

+1.5V

+1.5V

C559

+

150U/6.3V

SPC

CC7343

C669

C563

10U/6.3V

C296

+

150U/6.3V

SPC

CC7343

C318

10U/6.3V

0.1U/50V

C612

C560

10U/6.3V

C660

0.1U/50V

C708

0.1U/50V

C622

0.1U/50V

0.1U/50V

C566

0.1U/50V

C635

0.1U/50V

+1.5V

C682

0.1U/50V

C657

0.1U/50V

C621

0.1U/50V

C637

C601

0.1U/50V

C605

0.1U/50V

C625

0.1U/50V

C598

0.1U/50V

0.1U/50V

R604 0

R605 0

C659

C677

0.1U/50V

C686

0.1U/50V

C607

0.1U/50V

C600

C615

C585

0.1U/50V

C626

0.1U/50V

VCCAHPLL

VCCAGPLL

VCCADPLLA

VCCADPLLB

C620

0.1U/50V

0.01U/50V

VCCDLVDS

VCCTXLVDS

C327

0.1U/50V

C328

0.1U/50V

0.1U/50V

C573

C574

0.1U/50V

0.1U/50V

C319

0.01U/50V

W21

AA19

AA17

AA15

T17

P17

U16

R16

N16

T15

P15

U14

R14

N14

H14

T13

P13

D29

B16

B15

B14

G13

A12

D10

B10

A11

B11

J15

V9

W8

U8

V7

U6

W5

Y1

V1

Y2

A6

P9

M9

K9

R8

N8

M8

L8

J8

H7

E6

M4

J4

E4

N1

J1

E1

B9

A9

B8

J13

F9

A4

A3

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCCHL0

VCCHL1

VCCHL2

VCCHL3

VCCHL4

VCCHL5

VCCHL6

VCCHL7

VCCAHPLL

VCCAGPLL

VCCADPLLA

VCCADPLLB

VCCDVO0

VCCDVO1

VCCDVO2

VCCDVO3

VCCDVO4

VCCDVO5

VCCDVO6

VCCDVO7

VCCDVO8

VCCDVO9

VCCDVO10

VCCDVO11

VCCDVO12

VCCDVO13

VCCDVO14

VCCDVO15

VCCADAC0

VCCADAC1

VSSADAC

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCDLVDS3

VCCTXLVDS0

VCCTXLVDS1

VCCTXLVDS2

VCCTXLVDS3

VCCGPIO0

VCCGPIO1

VCCALVDS

VSSALVDS

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

POWER

VTTLF20

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCASM1

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

Montara-GM+

AB29

Y29

K29

F29

A26

V22

T22

P22

M22

H22

U21

R21

N21

L21

H20

A20

J19

H18

A18

H16

G15

AG29

AF29

AC29

AF27

AJ25

AF24

AB22

AJ21

AF21

AB20

AF18

AB18

AJ17

AB16

AF15

AB14

AJ13

AA13

AF12

AB12

AA11

AB10

AJ9

AF9

Y9

AB8

AA8

AC1

Y7

AF6

AB6

AA6

AJ5

Y4

AF3

AB3

AG1

AJ8

AJ6

AF1

AD1

V29

M29

H29

A24

A22

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

C401

0.1U/50V

C724

0.1U/50V

C695

0.1U/50V

0.1U/50V

C322

0.1U/50V

C565

0.1U/50V

C644

0.1U/50V

C403

C409

0.1U/50V

C417

VCCQSM

C408

0.1U/50V

0.1U/50V

C696

0.1U/50V

C411

0.1U/50V

C324

C649

0.1U/50V

C349

C775

0.1U/50V

C715

0.1U/50V

C705

0.1U/50V

C798

0.1U/50V

0.1U/50V

C346

0.1U/50V

0.1U/50V

0.1U/50V

C419

0.1U/50V

C786

0.1U/50V

C692

C803

0.1U/50V

0.1U/50V

C332

VCCASM

0.1U/50V

C709

0.1U/50V

0.1U/50V

C661

C343

C360

0.1U/50V

C414

0.1U/50V

C418

0.1U/50V

L20 0.22 UH

C320

4.7U/16V

R278 1/F

C321

0.1U/50V

C780

0.1U/50V

C722

0.1U/50V

C713

C416

0.1U/50V

C564

0.1U/50V

C368

0.1U/50V

C372

0.1U/50V

0.1U/50V

C674

0.1U/50V

C721

0.1U/50V

C431

+

150U/6.3V

SPC

CC7343

C354

C568

0.1U/50V

C300

+

100U/2V-7343

SPC

CC7343

C723

0.1U/50V

C666

C800

0.1U/50V

0.1U/50V

2.5VSUS

L17 1.8 UH

25mA

0.1U/50V

C301

+

150U/6.3V

SPC

CC7343

C633

0.1U/50V

C627

0.1U/50V

C569

0.1U/50V

C729

+

150U/6.3V

SPC

CC7343

2.5VSUS

VTT

C790

10U/6.3V

2.5VSUS

2.5VSUS

2.5VSUS

1.2VCCT

1.2VCCT

A A

B B

C C

1.2VCCT

+1.5V

+2.5V

VTT

VCC_CORE

R329 0

R298 0

R498 0_0805

C367

C295

22U/10V

47U/6.3V

R302 0_0805

C357

C347

22U/10V

47U/6.3V

VCC_CORE

C706

1000P/50V

C420

C424

0.1U/50V

0.1U/50V

C694

1000P/50V

1.2VCCT

1.2VCCT

D D

R301 1/F

R310 1/F

1

L18 0.18 UH

L23 0.18 UH

+

+

2

C604

220U/2.5V

SPC

CC7343

C654

220U/2.5V

SPC

CC7343

C345

0.1U/50V

C389

0.1U/50V

VCCADPLLA

VCCADPLLB

QUANTA

Title

Size Document Number Re v

3

4

5

6

Date: Sheet

COMPUTER

Montara - GM+ ( POWER )

ZI6

7

C

of

743Monday, January 12, 2004

8

1

VTT

R266

56/F

1 2

R265 56/F

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

V21

AB23

AA21

12

W21

AB22

V22

U22

Y22

AC2

AB11

AC11

Y10

AA10

AA7

AB8

AA8

AB9

AC9

AB10

W10

W11

Y11

Y13

AB14

AA13

AB13

W13

AC12

W12

AB12

AC13

AA11

Y12

NMI<3>

A20M#<3>

FERR#<3>

IGNNE#<3>

A A

B B

C C

INTR<3>

CPUINIT#<3>

RCIN#<31>

GATEA20<31>

AD[0..31]<21,24,25,26>

ICH_PME#<21,24,25,26>

PCLK_ICH<12>

CLKRUN#<21,24,25,26,30,31>

FPBACK#<18>

PDD[0..15]<20>

PDCS1#<20>

PDCS3#<20>

PDA0<20>

PDA1<20>

PDA2<20>

PDIOR#<20>

PDIOW#<20>

PIORDY<20>

IRQ14<20>

PDDREQ<20>

PDDACK#<20>

ICH_PME#

PCLK_ICH ICH_GPIO2

SYSRST#

CLKRUN#

FPBACK#

PDD[0..15]

PDCS1#

PDCS3#

PDA0

PDA1

PDA2

PDIOR#

PDIOW#

PIORDY

IRQ14

PDDREQ

PDDACK#

U40A

NMI

A20M#

FERR#

IGNNE#

INTR

INIT#

RCIN#

A20GATE

H5

AD0

J3

AD1

H3

AD2

K1

AD3

G5

AD4

J4

AD5

H4

AD6

J5

AD7

K2

AD8

G2

AD9

L1

AD10

G4

AD11

L2

AD12

H2

AD13

L3

AD14

F5

AD15

F4

AD16

N1

AD17

E5

AD18

N2

AD19

E3

AD20

N3

AD21

E4

AD22

M5

AD23

E2

AD24

P1

AD25

E1

AD26

P2

AD27

D3

AD28

R1

AD29

D2

AD30

P4

AD31

W2

PME#

P5

PCICLK

U5

PCIRST#

CLKRUN#/GPIO24

E8

GNTA#/GPIO16

C5

GNTB#/GNT5#/GPIO17

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

Y8

PDD6

PDD7

PDD8

Y9

PDD9

PDD10

W9

PDD11

PDD12

PDD13

PDD14

PDD15

PDCS1#

PDCS3#

PDA0

PDA1

PDA2

PDIOR#

PDIOW#

PIORDY

IRQ14

PDDREQ

PDDACK#

ICH4

2

APICD0

APICD1

CPU

PCI

IDE

APICCLK

SMI#

STPCLK#

CPUSLP#

DPSLP#

C/BE0#

C/BE1#

C/BE2#

C/BE3#

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

SERR#

PERR#

PLOCK#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PIRQE#/GPIO2

PIRQF#/GPIO3

PIRQG#/GPIO4

PIRQH#/GPIO5

SERIRQ

REQA#/GPIO0

REQB#/REQ5#/GPIO1

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

SDIOR#

SDIOW#

SIORDY

IRQ15

SDDREQ

SDDACK#

PAR

H19

K20

J19

W23

V23

U21

U23

J2

K4

M4

N4

F1

L5

F2

M3

F3

G1

K5

L4

M2

B1

A2

B3

C7

B6

C1

E6

A7

B7

D6

D5

C2

B4

A3

C8

D7

C3

C4

J22

B5

A6

W17

AB17

W16

AC16

W15

AB15

W14

AA14

Y14

AC15

AA15

Y15

AB16

Y16

AA17

Y17

AB21

AC22

AA20

AC20

AC21

Y18

AA18

AC19

AA19

AB18

AB19

PLOCK#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

ICH_GPIO4

3

RP7 4P2 R_S_10K

4

3

2

1

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PIRQE#

PIRQF#

R518

1 2

0

REQA#

REQB#

SDD[0..15]

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

SDIOR#

SDIOW#

SIORDY

IRQ15

SDDREQ

SDDACK#

4

SMI# <3>

STPCLK# <3>

CPUSLP# <3>

DPSLP# <3,6>

C/BE0# <21,24,25,26>

C/BE1# <21,24,25,26>

C/BE2# <21,24,25,26>

C/BE3# <21,24,25,26>

FRAME# <21,24,25,26>

IRDY# <21,24,25,2 6>

TRDY# <21,24,25,26>

DEVSEL# <21,24,25,26>

STOP# <21,24,25,26>

PAR <21,24,25,26>

SERR# <21,24,25,26>

PERR# <21,24,25,26>

REQ0# <26>

REQ1# <25>

REQ2# <24>

REQ3# <21>

GNT0# <26>

GNT1# <25>

GNT2# <24>

GNT3# <21>

PIRQ A# <13>

PIRQB # <21,24>

PIRQ C# <21>

PIRQ D# <26>

PIRQ E# <25>

PIR QF# <25>

SERIR Q_SIO <30>

SERI RQ <21,31>

SDD[0..15] <20>

SDCS1 # <20>

SDCS3 # <20>

SDA0 <20>

SDA1 <20>

SDA2 <20>

SDIO R# <20>

SDIO W# <20>

SIORDY <20>

IRQ15 <20>

SDDREQ <20>

SDDACK# <20>

+1.5V

C254

.1U/10V_0402

VTT

C225

0.1U/50V

C527

22U/10V

C215

0.01U/50V

C548

0.01U/50V

C543

100U/2V-7343

CC7343

+3V

C532

22U/10V

C21

C23

D12

VSS051

VSS052

VSS053C6VSS054D1VSS055

VSS000

VSS001

VSS002N5VSS003

P11

P13

N21

N23

+1.5V

D15

D17

VSS056

VSS004

VSS005

P20

P22

+

C194

.1U/10V_0402

D19

D21

VSS057

VSS058

VSS059

VSS006

VSS007P3VSS008

R18

VCCLAN3_3

VCCLAN1_5

+1.5V

3V_S5

C547

22U/10V

3V_S5

C550

22U/10V

D23

D22

VSS060

VSS061D4VSS062D8VSS063

VSS009

VSS010R5VSS011T1VSS012

T19

R21

C251

0.1U/50V

C534

4.7U/10V_0805

C530

0.1U/50V

E10

E14

E16

VSS064

VSS065

VSS066

VSS013

VSS014

VSS015

T23

V15

U20

5

C22

AA23

P14

U18

K10

K12

K18

K22

P10

T18

U19

V14

E11

F10

F15

F16

F17

F18

K14

.1U/10V_0402

E17

E18

E19

VSS067

VSS068

VSS016

VSS017

V3

V17

W22

U40C

VCCPLL

V_CPU_IO_0

V_CPU_IO_1

V_CPU_IO_2

E9

VCCLAN3_3_1

F9

VCCLAN3_3_0

F6

VCCLAN1_5_0

F7

VCCLAN1_5_1

VCC1_5_0

VCC1_5_1

VCC1_5_2

VCC1_5_3

VCC1_5_4

VCC1_5_5

VCC1_5_6

VCC1_5_7

VCCSUS3_3_0

VCCSUS3_3_1

VCCSUS3_3_2

VCCSUS3_3_3

VCCSUS3_3_4

VCCSUS3_3_5

VCCSUS3_3_6

V7

VCCSUS3_3_7

V8

VCCSUS3_3_8

V9

VCCSUS3_3_9

ICH4

C250

.1U/10V_0402

C236

.1U/10V_0402

C233

E22

E21

VSS069

VSS070

VSS018

VSS019W5VSS020W8VSS021

Y19

C184

0.1U/50V

G21

G19

VSS073

VSS072F8VSS071

GND

VSS022Y7VSS023A1VSS024

A16

VSS025

A18

C270

.1U/10V_0402

C246

.1U/10V_0402

C531

0.1U/50V

K13

K11

VSS080

VSS079

VSS078J6VSS077H1VSS076G6VSS075G3VSS074

VSS026

VSS027

VSS028A4VSS029

A20

A22

AA12

VCC

K23

K19

VSS081

VSS030

VSS031

AA3

AA16

AA22

C549

0.1U/50V

C185

.1U/10V_0402

C256

.1U/10V_0402

L11

L12

L10

VSS085

VSS086

VSS084

VSS083K3VSS082

VSS032

VSS033

VSS034

VSS035

AA9

AB7

AB20

6

V5REF_SUS

V5REF1

V5REF2

VCCHI_0

VCCHI_1

VCCHI_2

VCCHI_3

VCCSUS1_5_0

VCCSUS1_5_1

VCCSUS1_5_2

VCCSUS1_5_3

VCCSUS1_5_4

VCCSUS1_5_5

VCCSUS1_5_6

VCCSUS1_5_7

VCC3_3_0

VCC3_3_1

VCC3_3_2

VCC3_3_3

VCC3_3_4

VCC3_3_5

VCC3_3_6

VCC3_3_7

VCC3_3_8

VCC3_3_9

VCC3_3_10

VCC3_3_11

VCC3_3_12

VCC3_3_13

VCC3_3_14

VCC3_3_15

C199

.1U/10V_0402

C222

.1U/10V_0402

C255

.1U/10V_0402

M11

M1

L21

L14

L13

VSS091

VSS090

VSS089

VSS088

VSS087

VSS036

VSS037

VSS038

VSS039

VSS040

AC1

AC10

AC14

AC18

AC23

M13

M12

VSS092

VSS041

B12

AC5

E15

E7

V6

L23

M14

P18

T22

E12

E13

E20

F14

G18

R6

T6

U6

A5

AC17

AC8

B2

H18

H6

J1

J18

K6

M10

P12

P6

U1

V10

V16

V18

C218

.1U/10V_0402

M22

M20

VSS095

VSS094

VSS093

VSS042

VSS043

VSS044

B16

B18

C538

0.1U/50V

N11

N10

VSS097

VSS096

VSS045

VSS046

B20

B22

V5REF_SUS

VCC5REF

1.5V_S5

+3V

C179

.1U/10V_0402

C198

.1U/10V_0402

N19

N14

N13

N12

VSS101

VSS100

VSS099

VSS098

VSS047B9VSS048

VSS049

VSS050

C15

C17

C19

C555

22U/10V

C207

.1U/10V_0402

U40D

ICH4

10U/6.3V

7

C266

.1U/10V_0402

C197

.1U/10V_0402

C211

.1U/10V_0402

1.5V_S5

C206

C243

10U/16V

+1.5V

C271

.1U/10V_0402

3V_S5

1.5V_S5

+1.5V

C248

.1U/10V_0402

+3V

C219

0.1U/50V

1.5V_S5

R159 *0_0805

R166 0_0805

R180 0_0805

R158 *0_0805

C529

0.1U/50V

C213

.1U/10V_0402

C186

0.1U/50V

V5REF_SUS

VCC5REF

12

12

12

12

C263

.1U/10V_0402

C546

0.1U/50V

C528

0.1U/50V

VCCLAN3_3

VCCLAN1_5

C203

0.1U/50V

C223

.1U/10V_0402

8

R462 1K

D29

C554

1U/16V_0805

CC0805

R419 1K

D28

C533

1U/16V_0805

CC0805

C196

1U/6.3V

C175

1U/6.3V

3V_S5

C230

.1U/10V_0402

C541

C183

0.1U/50V

0.1U/50V

C180

C170

0.1U/50V

.1U/10V_0402

C241

0.1U/50V

12

21

RB751V

12

21

RB751V

C190

1U/6.3V

C181

1U/6.3V

C200

.1U/10V_0402

C240

0.1U/50V

5V_S5

3V_S5

+5V

+3V

C212

0.1U/50V

GNT4#

R147 *10K

1 2

REQB#

R139 10K

1 2

ICH_GPIO2

R132 10K

1 2

D D

CLKRUN#

R433 10K

1 2

ICH_PME#

R107 4.7K

1 2

Had inernal pull up

PCLK_ICH

R146 33/F

12

1

C174

+3V

+3V

+3V

3V_S5

18P/50V_0402

2

3V_S5

84

U39B

5

6

NC7WZ32

R607 *0

12

3V_S5

C537

0.1U/50V

U39A

84

1

3

3

SYSRST#SYSRST#

2

R606 *0

NC7WZ32

4

7

12

PCIRST# <13, 16,22,25,26,30,31>PCIRST1# <6,17,20,21,24>

5

+3V

+3V

+3V

PCI Pullups

IRQ14

SERIRQ

REQ3#

IRQ15

TRDY#

STOP#

FRAME#

PIRQB#

PIRQA#

PIRQC#

PIRQD#

REQ2#

RP2 10P8R_8.2K

6

7

8

9

10

RP3 10P8R_8.2K

6

7

8

9

10

RP5 10P8R_8.2K

6

7

8

9

10

5

4

3

2

1

5

4

3

2

1

5

4

3

2

1

6

IRDY#

PERR#

DEVSEL#

PLOCK#

PIRQE#

PIRQF#

SERR#

ICH_GPIO4

REQA#

REQ1#

REQ4#

REQ0#

+3V

+3V

GNT0#

GNT2#

GNT3#

GNT1#

RP4

7 8

5 6

3 4

1 2

*8P4R_10K

QUANTA

+3V

Title

Size Document Number Re v

Date: Sheet

COMPUTER

ICH4-M (CPU,P CI,IDE)

ZI6

7

+3V+3V

C

of

843Tuesday, January 13, 2004

8

1

RBAYID0<20>

RBAYID1<20>

BT_DETACH<25>

RBAYON#<20>

SYSUSBP0+<32>

SYSUSBP0-<32>

USBOC0#<32>

S5_ON

PWROK_DELAY<6>

3V_S5

SYSUSBP2+<32>

SYSUSBP2-<32>

USBOC2#<32>

CLK48_USB<12>

CLK66_ICH<12>

HLSTB<5>

HLSTB#<5>

LAD0/FWH0<30,31>

LAD1/FWH1<30,31>

LAD2/FWH2<30,31>

LAD3/FWH3<30,31>

AC_RESET#<25,28>

AC_SYNC<25,28>

AC_SDIN0<28>

AC_SDIN1<25>

AC_BITCLK<25,28>

PCLK_SMB<12>

PDAT_SMB<12>

RI#<27>

ICH_THRM#<3,33>

DNBSWON#<31>

THERMTRIP#<3>

DPRSLPVR<38>

STP_AGP#<13>

AGP_BUSY#<6,13>

14M_ICH<12>

CLK_SMB<12>

DAT_SMB<12>

PCSPK<27>

CRT_SENSE#<16,34>

KBSMI#<30,31>

CPUPWRGD<3>

IMVP_OK<27,38>

PWROK<6,31>

1

A A

B B

Change signal

C C

31,36,40>

D D

RBAYID0

RBAYID1

BT_DETACH

RBAYON#

USBOC0#

USBOC2#

SYSUSBP4+

SYSUSBP4USBOC4#

CLK48_USB

HL0

HL0<5>

HL1

HL1<5>

HL2

HL2<5>

HL3

HL3<5>

HL4

HL4<5>

HL5

HL5<5>

CLK66_ICH

AC_RESET#

R424 33/F

AC_SDIN0

AC_SDIN1

*PAD

T13

AC_BITCLK

R430 22

PCLK_SMB

PDAT_SMB

RI#

ICH_THRM#

PWROK_DELAY

R864

DNBSWON#

RSMRST#

THERMTRIP#

DPRSLPVR

14M_ICH

PCSPK

CRT_SENSE#

KBSMI#

CPUPWRGD

T14*PAD

T16*PAD

1 2

R264 0

1 2

R263 *0

3V_S5

3V_S5

R274

100K

D13

-RSMRSTS5_ON

21

1SS355

-RSMRST

C292

0.1U/50V

U18

1

1A

2

3Y

3

2A

GND42Y

2

RTCRST# delay 18-25ms

AC_SYNC_1

AC_BITCLK_1

BATLOW#_SB

12

10K_0402

CPUPERF#

R_VR_PWRGOOD

T12 *PAD

T35 *PAD

T9 *PAD

T6 *PAD

5

VCC

3

B

6

GND

2

8

VCC

7

1Y

6

3A

5

TC7W14FU

R275 *0

2

ORGND

1

C294

*0.1U

J20

G22

F20

G20

F21

H20

C20

D20

B15

C18

D18

A15

C16

D16

A14

F19

L19

L20

M19

M21

P19

R19

T21

P21

N20

R4

U2

C13

C9

D13

A13

B13

AC4

AB4

AB6

AB2

AA1

AA6

W20

V20

R2

J23

AC3

AB1

H23

R3

Y23

Y20

J21

V19

C12

D11

D10

YA

U20

*NC7SZ58

3V_S5

T2

T4

B8

Y1

V1

T3

V4

A8

U40B

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

USBP0P

USBP0N

OC0#

USBP2P

USBP2N

OC2#

USBP4P

USBP4N

OC4#

CLK48

HI0

HI1

HI2

HI3

HI4

HI5

HI_CLK

HL_STB/HL_STBS

HL_STB#/HLSTBF

LAD0/FWH0

LAD1/FWH1

LAD2/FWH2

LAD3/FWH3

AC_RST#

AC_SYNC

AC_SDIN0

AC_SDIN1

AC_SDIN2

AC_BITCLK

SMBCLK

SMBDATA

RI#

THRM#

PWROK

BATLOW#

PWRBTN#

RSMRST#

THRMTRIP#

DPRSLPVR

C3_STAT#/GPIO21

AGPBUSY#/GPIO6

CLK14

SMLINK0

SMLINK1

SPKR

GPIO7

GPIO8

CPUPWRGD

CPUPERF#/GPIO22

SSMUXSEL/GPIO23

VGATE/VRMPWRGD

EE_SHCLK

EE_DOUT

EE_DIN

EE_CS

ICH4

RSMRST#

4

R277

22K

*0.1U

C293

RSMRST#

3

USB

HUB LINK

LPC&FWH

LFRAME#/FWH4

AC97&RTC

SMBALERT#/GPIO11

SM

PM

SLP_S1#/GPIO19

STP_PCI#/GPIO18

STP_CPU#/GPIO20

SUS_STAT#/LPCPD#

MISC&GPIO

SpeedStep

LAN

LAN_RSTSYNC

3

GPIO38

GPIO39

GPIO40

GPIO41

GPIO42