Page 1

TI Extensa 61X Series

(AcerNote 370P) Notebook

Service Guide

PART NO.: 2238309-0809

DOC. NO.: PRINTED IN USA

Page 2

Copyright

Copyright © 1997 by Acer Incorporated. All rights reserved. No part of this publication may be

reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or

computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical,

manual or otherwise, without the prior written permission of Acer Incorporated.

Disclaimer

Acer Incorporated makes no representations or warranties, either expressed or implied, with respect to the

contents hereof and specifically disclaims any warranties of merchantability or fitness for any particular

purpose. Any Acer Incorporated software described in this manual is sold or licensed "as is". Should the

programs prove defective following their purchase, the buyer (and not Acer Incorporated, its distributor, or

its dealer) assumes the entire cost of all necessary servicing, repair, and any incidental or consequential

damages resulting from any defect in the software. Further, Acer Incorporated reserves the right to revise

this publication and make changes from time to time in the contents hereof without obligation of Acer

Incorporated to notify any person of such revision or changes.

Acer is a registered trademark of Acer Incorporated.

IBM, PS/2 and OS/2 are registered trademarks of International Business Machines Corporation.

Intel and Pentium are registered trademarks of Intel Corporation.

MS-DOS, Windows and Windows 95 are registered trademarks of Microsoft Corporation.

Other brands and product names are trademarks and/or registered trademarks of their respective holders.

ii

Page 3

About this Manual

Purpose

This service guide contains reference information for the Extensa 610 notebook computer. It gives the

system and peripheral specifications, shows how to identify and solve system problems and explains the

procedure for removing and replacing system components. It also gives information for ordering spare

parts.

Manual Structure

This service guide consists of four chapters and seven appendices as follows:

Chapter 1 System Introduction

This chapter gives the technical specifications for the notebook and its peripherals.

Chapter 2 Major Chip Descriptions

This chapter lists the major chips used in the notebook and includes pin descriptions and related

diagrams of these chips.

Chapter 3 BIOS Setup Information

This chapter includes the system BIOS information, focusing on the BIOS setup utility.

Chapter 4 Disassembly and Unit Replacement

This chapter tells how to disassemble the notebook and replace components.

Appendix A Model Number Definition

This appendix lists the model number definition of this notebook model series.

Appendix B Exploded View Diagram

This appendix shows the exploded view diagram of the notebook.

Appendix C Spare Parts List

This appendix contains spare parts information.

Appendix D Schematics

This appendix contains the schematic diagrams of the notebook.

iii

Page 4

Appendix E BIOS POST Checkpoints

This appendix lists all the BIOS POST checkpoints.

Appendix F Technical Bulletins and Updates

This appendix reserves a space for technical bulletins and future updates.

Appendix G Forms

This appendix contains standard forms that can help improve customer service.

Related product information

AcerNote 370P User's Manual contains system description and general operating instructions.

M1521, M1523 and M7101 Data Sheets contain information on the Acer chips.

C&T 65550 Data Sheet contains detailed information on the Chips & Tech. VGA controller.

TI PCI1131 Data Sheet contains detailed information on the Texas Instrument PCMCIA controller.

NS87336VJG Data Sheet contains detailed information on the NS super I/O controller.

YMF715 Data Sheet contains detailed information on the Yamaha YMF715 audio controller.

T62.062.C, T62.061.C, T62.064.C, and T62.066.C Data Sheets contain detailed information on the Ambit

components.

iv

Page 5

Conventions

The following are the conventions used in this manual:

Text entered by user

Screen messages

Represents text input by the user.

Denotes actual messages that appear onscreen.

NOTE

Gives bits and pieces of additional information related to the

current topic.

WARNING

Alerts you to any damage that might result from doing or not

doing specific actions.

CAUTION

Gives precautionary measures to avoid possible hardware or

software problems.

IMPORTANT

Reminds you to do specific actions relevant to the accomplishment

of procedures.

TIP

Tells how to accomplish a procedure with minimum steps through

little shortcuts.

v

Page 6

vi

Page 7

Table of Contents

Chapter 1 System Introduction

1.1 Overview..........................................................................................................................1-1

1.1.1 Features ...........................................................................................................1-2

1.1.2 Rear Ports ........................................................................................................ 1-3

1.1.3 Indicator Light.................................................................................................1-4

1.1.4 System Specifications Overview.......................................................................1-5

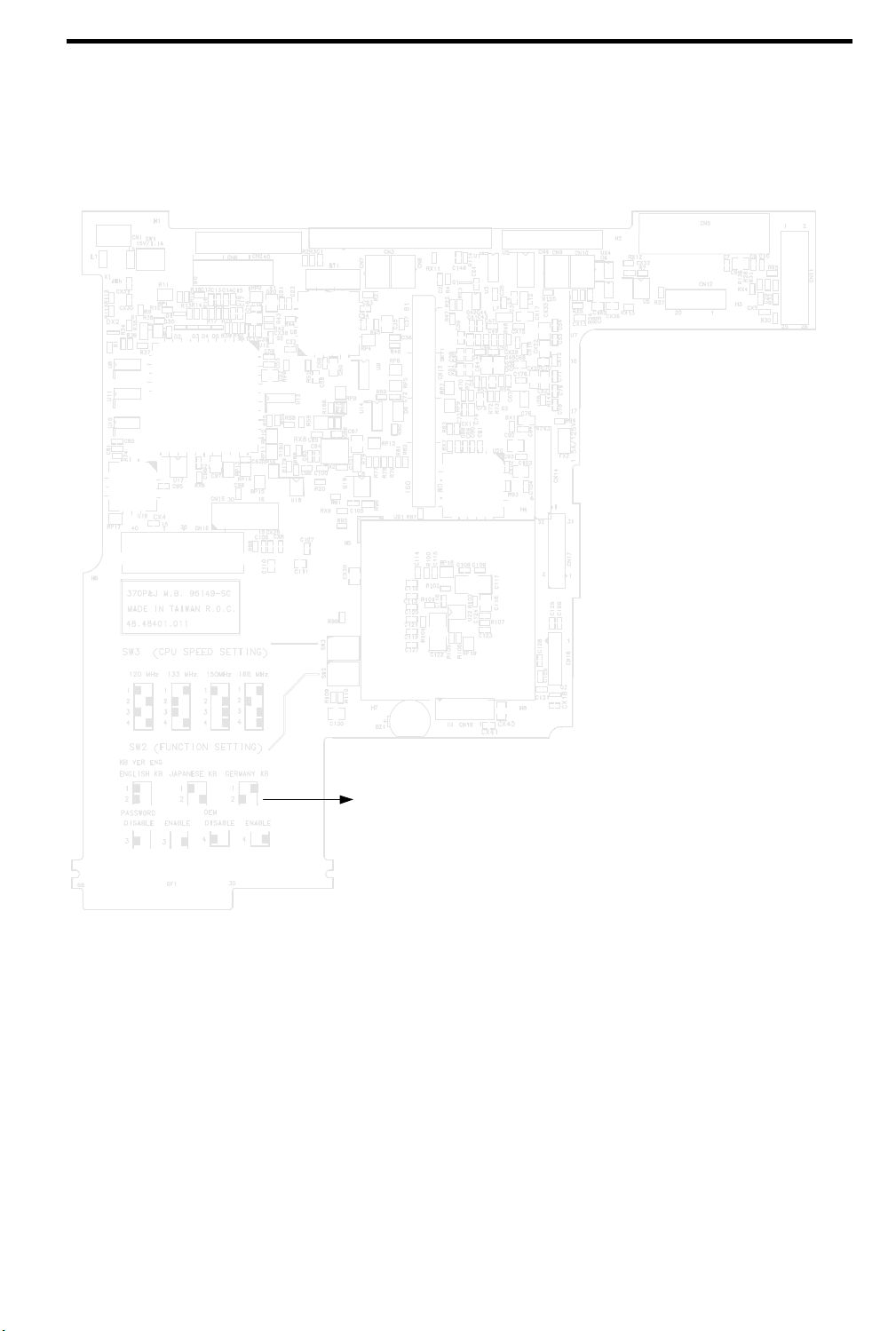

1.2 System Board Layout........................................................................................................1-7

1.2.1 Main Board (PCB No: 96149-SC)....................................................................1-7

1.2.2 Audio Connection Board (PCB No:96467-1).................................................... 1-9

1.2.3 Battery Connection Board (PCB No:95498-1) .................................................. 1-9

1.2.4 HDD Connection Board (PCB No:96463-1) ...................................................1-10

1.2.5 Keyboard Connection Board (PCB No: 96465-1)............................................1-11

1.3 Jumpers and Connectors.................................................................................................1-12

1.4 Hardware Configuration and Specification.....................................................................1-14

1.4.1 Memory Address Map....................................................................................1-14

1.4.2 Interrupt Channel Map...................................................................................1-14

1.4.3 DMA Channel Map .......................................................................................1-15

1.4.4 I/O Address Map............................................................................................1-15

1.4.5 M7101 GPIO (General Purpose I/O) Port Definition ......................................1-16

1.4.6 Processor........................................................................................................1-16

1.4.7 BIOS..............................................................................................................1-17

1.4.8 System Memory .............................................................................................1-17

1.4.9 Second-Level Cache.......................................................................................1-18

1.4.10 Video Memory...............................................................................................1-19

1.4.11 Video.............................................................................................................1-19

1.4.11.1 External CRT Resolution Support ...............................................1-19

1.4.11.2 LCD Resolution Support .............................................................1-20

1.4.12 Parallel Port...................................................................................................1-21

1.4.13 Serial Port......................................................................................................1-21

1.4.14 Audio............................................................................................................. 1-22

1.4.15 PCMCIA........................................................................................................1-22

1.4.16 Touchpad.......................................................................................................1-23

vii

Page 8

1.4.17 Keyboard........................................................................................................1-23

1.4.17.1 Windows 95 Keys ........................................................................1-23

1.4.18 FDD...............................................................................................................1-24

1.4.19 HDD...............................................................................................................1-24

1.4.20 CD-ROM........................................................................................................1-25

1.4.21 Battery............................................................................................................1-25

1.4.22 Charger..........................................................................................................1-26

1.4.23 DC-DC Converter...........................................................................................1-27

1.4.24 DC-AC Inverter..............................................................................................1-27

1.4.25 LCD...............................................................................................................1-28

1.4.26 AC Adapter....................................................................................................1-29

1.5 Software Configuration and Specification.......................................................................1-30

1.5.1 BIOS..............................................................................................................1-30

1.5.1.1 Keyboard Hotkey Definition.........................................................1-30

1.5.1.2 MultiBoot....................................................................................1-31

1.5.1.3 Power Management.....................................................................1-31

1.5.2 Drivers, Applications and Utilities.................................................................. 1-36

1.6 System Block Diagram ...................................................................................................1-38

1.7 Environmental Requirements..........................................................................................1-39

1.8 Mechanical Specifications ..............................................................................................1-40

Chapter 2 Major Chips Description

2.1 Major Component List......................................................................................................2-1

2.2 ALI M1521 ......................................................................................................................2-2

2.2.1 Features............................................................................................................2-2

2.2.2 Block Diagram.................................................................................................2-4

2.2.3 System Architecture .........................................................................................2-5

2.2.4 Data Path .........................................................................................................2-6

2.2.5 Pin Diagram.....................................................................................................2-7

2.2.6 Signal Descriptions ..........................................................................................2-8

2.3 ALI M1523 ....................................................................................................................2-14

2.3.1 Features.......................................................................................................... 2-14

viii

2.3.2 Block Diagram............................................................................................... 2-16

2.3.3 Pin Diagram...................................................................................................2-17

2.3.4 Signal Descriptions ........................................................................................2-18

Page 9

2.4 ALI M7101 (Power Management Unit)..........................................................................2-24

2.4.1 Features .........................................................................................................2-24

2.4.2 Pin Diagram...................................................................................................2-25

2.4.3 Pin Description ..............................................................................................2-26

2.4.4 Different Pin definition setting.......................................................................2-34

2.4.5 Numerical Pin List.........................................................................................2-36

2.4.6 Alphabetical Pin List......................................................................................2-37

2.4.7 Function Description...................................................................................... 2-38

2.5 C&T 65550 High Performance Flat Panel/CRT VGA Controller....................................2-40

2.5.1 Features .........................................................................................................2-40

2.5.2 Block Diagram ...............................................................................................2-41

2.5.3 Pin Diagram...................................................................................................2-42

2.5.4 Pin Descriptions .............................................................................................2-43

2.6 TI PCI1131 CardBus Controller.....................................................................................2-56

2.6.1 Overview........................................................................................................2-56

2.6.2 Architecture...................................................................................................2-57

2.6.3 Features .........................................................................................................2-57

2.6.4 Block Diagram ...............................................................................................2-59

2.6.5 Pin Diagram...................................................................................................2-61

2.6.6 Terminal Functions........................................................................................2-63

2.7 NS87336VJG Super I/O Controller ................................................................................2-75

2.7.1 Features .........................................................................................................2-75

2.7.2 Block Diagram ...............................................................................................2-77

2.7.3 Pin Diagram...................................................................................................2-78

2.7.4 Pin Description ..............................................................................................2-79

2.8 Yamaha YMF715 Audio Chip........................................................................................2-87

2.8.1 Features .........................................................................................................2-87

2.8.2 Pin Diagram...................................................................................................2-88

2.8.3 Pin Descriptions .............................................................................................2-89

2.9 T62.062.C Battery Charger ............................................................................................2-91

2.9.1 Overview........................................................................................................2-91

2.9.2 Features .........................................................................................................2-91

2.9.3 Absolute Maximum Ratings...........................................................................2-92

2.9.4 Electrical Characteristics................................................................................2-92

ix

Page 10

2.9.5 Pin Diagram...................................................................................................2-94

2.9.6 Pin Description...............................................................................................2-95

2.9.7 Functions Description..................................................................................... 2-96

2.9.7.1 Charge Function ..........................................................................2-96

2.9.7.2 Discharge Function......................................................................2-96

2.9.7.3 Safety Concerns........................................................................... 2-97

2.10 T62.061.C DC-DC Converter......................................................................................... 2-98

2.10.1 Pin Diagram...................................................................................................2-98

2.10.2 Pin Assignment..............................................................................................2-98

2.10.3 Specifications................................................................................................. 2-99

2.10.4 Control.........................................................................................................2-100

2.10.5 Application: ................................................................................................. 2-100

2.11 T62.064.C DC-AC Inverter (11.3”) ..............................................................................2-102

2.11.1 Electrical Specifications ............................................................................... 2-102

2.11.2 Pin & Connector Assignment .......................................................................2-103

2.11.3 Top Overlay ................................................................................................. 2-104

2.11.4 Bottom Overlay ............................................................................................2-104

2.12 T62.066.C DC-AC Inverter (12.1”) ..............................................................................2-105

2.12.1 Electrical Specifications ............................................................................... 2-105

2.12.2 Pin & Connector Assignment .......................................................................2-106

2.12.3 Top Overlay ................................................................................................. 2-107

2.12.4 Bottom Overlay ............................................................................................2-107

Chapter 3 BIOS Setup Information

3.1 When to Use Setup ...........................................................................................................3-1

3.2 Entering Setup..................................................................................................................3-2

3.3 Basic System Configuration ..............................................................................................3-4

3.3.1 Date and Time..................................................................................................3-4

3.3.2 Floppy Disk Drives ...........................................................................................3-4

3.3.3 Hard Disk Drive...............................................................................................3-4

3.3.4 Large Hard Disk Capacity ................................................................................3-4

3.3.5 Memory Test....................................................................................................3-5

3.3.6 Boot Display.....................................................................................................3-5

3.3.7 Quiet Boot........................................................................................................3-5

x

Page 11

3.4 System Security ................................................................................................................3-6

3.4.1 Floppy Disk Drive Control...............................................................................3-6

3.4.2 Hard Disk Drive Control..................................................................................3-6

3.4.3 System Boot Drive Control...............................................................................3-7

3.4.4 CD-ROM Bootable...........................................................................................3-7

3.4.5 Serial Port 1 Base Address ............................................................................... 3-8

3.4.6 Parallel Port Base Address ...............................................................................3-8

3.4.7 Parallel Port Operation Mode...........................................................................3-8

3.4.8 Passwords ........................................................................................................3-9

3.4.9 CardBus Support ............................................................................................3-10

3.5 Power Management Settings ..........................................................................................3-11

3.5.1 Power Management Mode..............................................................................3-11

3.5.2 Display Standby Timer...................................................................................3-11

3.5.3 Hard Disk Standby Timer...............................................................................3-11

3.5.4 System Sleep Timer .......................................................................................3-12

3.5.5 System Sleep Mode........................................................................................3-12

3.5.6 System Resume Timer Mode..........................................................................3-12

3.5.7 System Resume Date and Time ......................................................................3-12

3.5.8 Modem Ring Resume On Indicator ................................................................3-12

3.5.9 Battery-low Warning Beep.............................................................................3-13

3.5.10 Sleep Upon Battery-low..................................................................................3-13

3.6 System Information Reference ........................................................................................3-14

3.7 Load Setup Default Settings ...........................................................................................3-16

Chapter 4 Disassembly and Unit Replacement

4.1 General Information .........................................................................................................4-2

4.1.1 Before You Begin.............................................................................................4-2

4.1.2 Connector Types .............................................................................................. 4-3

4.1.3 Disassembly Sequence......................................................................................4-4

4.2 Replacing Memory...........................................................................................................4-6

4.3 Removing the Hard Disk Drive ........................................................................................4-7

4.4 Removing the Keyboard...................................................................................................4-9

xi

Page 12

4.5 Disassembling the Inside Frame Assembly .....................................................................4-10

4.5.1 Removing the Heat Sink Assembly.................................................................4-10

4.5.2 Removing the Internal Drive ..........................................................................4-11

4.5.3 Replacing the CPU......................................................................................... 4-12

4.5.4 Removing the Display ....................................................................................4-13

4.5.5 Detaching the Top Cover ................................................................................4-14

4.5.6 Removing the Base Assembly.........................................................................4-16

4.5.7 Removing the Motherboard ............................................................................4-17

4.5.8 Disassembling the Motherboard......................................................................4-20

4.5.9 Removing the Touchpad.................................................................................4-21

4.6 Disassembling the Display ..............................................................................................4-22

Appendix A Model Number Definition

Appendix B Exploded View Diagram

Appendix C Spare Parts List

Appendix D Schematics

Appendix E BIOS POST Checkpoints

Appendix F Technical Bulletins and Updates

Appendix G Forms

xii

Page 13

List of Figures

1-1 Notebook..........................................................................................................................1-1

1-2 Rear Ports ........................................................................................................................1-3

1-3 Indicator Light.................................................................................................................1-4

1-4 Main Board Layout (Top Side).........................................................................................1-7

1-5 Main Board Layout (Bottom Side) ....................................................................................1-8

1-6 Audio Connection Board Layout (Top Side).....................................................................1-9

1-7 Battery Connection Board Layout (Top Side) ...................................................................1-9

1-8 Battery Connection Board Layout (Bottom Side) .............................................................. 1-9

1-9 HDD Connection Board Layout (Top Side) ....................................................................1-10

1-10 HDD Connection Board Layout (Bottom Side) ...............................................................1-10

1-11 Keyboard Connection Board Layout (Top Side) ..............................................................1-11

1-12 Keyboard Connection Board Layout (Bottom Side).........................................................1-11

1-13 Jumpers and Connectors (Top View)..............................................................................1-12

1-14 Power Management Block Diagram ...............................................................................1-31

1-15 System Block Diagram...................................................................................................1-38

2-1 Alladin III Block Diagram ...............................................................................................2-4

2-2 Alladin III System Architecture........................................................................................2-5

2-3 M1521 Data Path.............................................................................................................2-6

2-4 M1521 Pin Diagram.........................................................................................................2-7

2-5 M1523 Block Diagram...................................................................................................2-16

2-6 M1523 Pin Diagram.......................................................................................................2-17

2-7 M7101 Pin Diagram......................................................................................................2-25

2-8 State Machine for PCI Interface .....................................................................................2-39

2-9 C&T 65550 Block Diagram............................................................................................2-41

2-10 C&T 65550 Pin Diagram ...............................................................................................2-42

2-11 Functional Block Diagram - 16-bit PC Card Interface ....................................................2-59

2-12 Functional block diagram - CardBus Card Interface.......................................................2-60

2-13 PCI-to-PC Card (16-bit) terminal assignments ...............................................................2-61

xiii

Page 14

2-14 PCI-to-CardBus terminal assignments............................................................................ 2-62

2-15 NS87336VJG Block Diagram.........................................................................................2-77

2-16 NS87336VJG Pin Diagram............................................................................................. 2-78

2-17 YMF715 Block Diagram ................................................................................................2-88

2-18 T62.062.C Pin Diagram..................................................................................................2-94

2-19 T62.061.C Pin Diagram..................................................................................................2-98

2-20 T62.064.C DC-AC Inverter Top Overlay diagram ........................................................2-104

2-21 T62.064.C DC-AC Inverter Bottom Overlay diagram...................................................2-104

2-22 T62.066.C DC-AC Inverter Top Overlay diagram ........................................................2-107

2-23 T62.066.C DC-AC Inverter Bottom Overlay diagram...................................................2-107

4-1 Removing the Battery Pack ...............................................................................................4-2

4-2 Using Connectors With Locks ..........................................................................................4-3

4-3 Disassembly Sequence Flowchart......................................................................................4-5

4-4 Removing the Memory Door.............................................................................................4-6

4-5 Installing and Removing Memory.....................................................................................4-6

4-6 Removing the Hard Disk Drive Bay Cover........................................................................4-7

4-7 Removing the Hard Disk Drive .........................................................................................4-8

4-8 Removing the Display Hinge Covers.................................................................................4-9

4-9 Unplugging the Keyboard Connectors...............................................................................4-9

4-10 Removing the Heat Sink Assembly Screws .....................................................................4-10

4-11 Removing the Internal Drive ..........................................................................................4-11

4-12 Replacing the CPU .........................................................................................................4-12

4-13 Unplugging the Display Cable........................................................................................4-13

4-14 Removing the Display Hinge Screws ..............................................................................4-13

4-15 Removing the Bottom Screws......................................................................................... 4-14

4-16 Detaching the Top Cover from the Base Assembly..........................................................4-15

4-17 Detaching the Base Assembly.........................................................................................4-16

4-18 Removing the Fan ..........................................................................................................4-17

4-19 Removing the Audio Board.............................................................................................4-17

xiv

Page 15

4-20 Removing the Battery Connector Board..........................................................................4-18

4-21 Unplugging the LCD Cover Switch and Speaker Cables .................................................4-18

4-22 Removing the Charger Board.........................................................................................4-19

4-23 Detaching the Motherboard from the Inside Assembly Frame.........................................4-19

4-24 Removing the PC Card Slot Unit ....................................................................................4-20

4-25 Removing the Keyboard Connection Board ....................................................................4-20

4-26 Removing the Touchpad.................................................................................................4-21

4-27 Removing the LCD Bumpers..........................................................................................4-22

4-28 Removing the Display Bezel Screws ...............................................................................4-22

4-29 Removing the Display Bezel...........................................................................................4-23

4-30 Removing the Hinge Cable Cover...................................................................................4-23

4-31 Removing the LCD Panel ...............................................................................................4-24

4-32 Removing the LCD ........................................................................................................4-24

4-33 Removing the DC-AC Inverter and LCD ID Inverter Boards ..........................................4-25

4-34 Removing the Display Cable Assembly ..........................................................................4-25

xv

Page 16

List of Tables

1-1 Port Descriptions.............................................................................................................1-3

1-2 Indicator Status Descriptions............................................................................................1-4

1-3 System Specifications .......................................................................................................1-5

1-3 System Specifications (continued).....................................................................................1-6

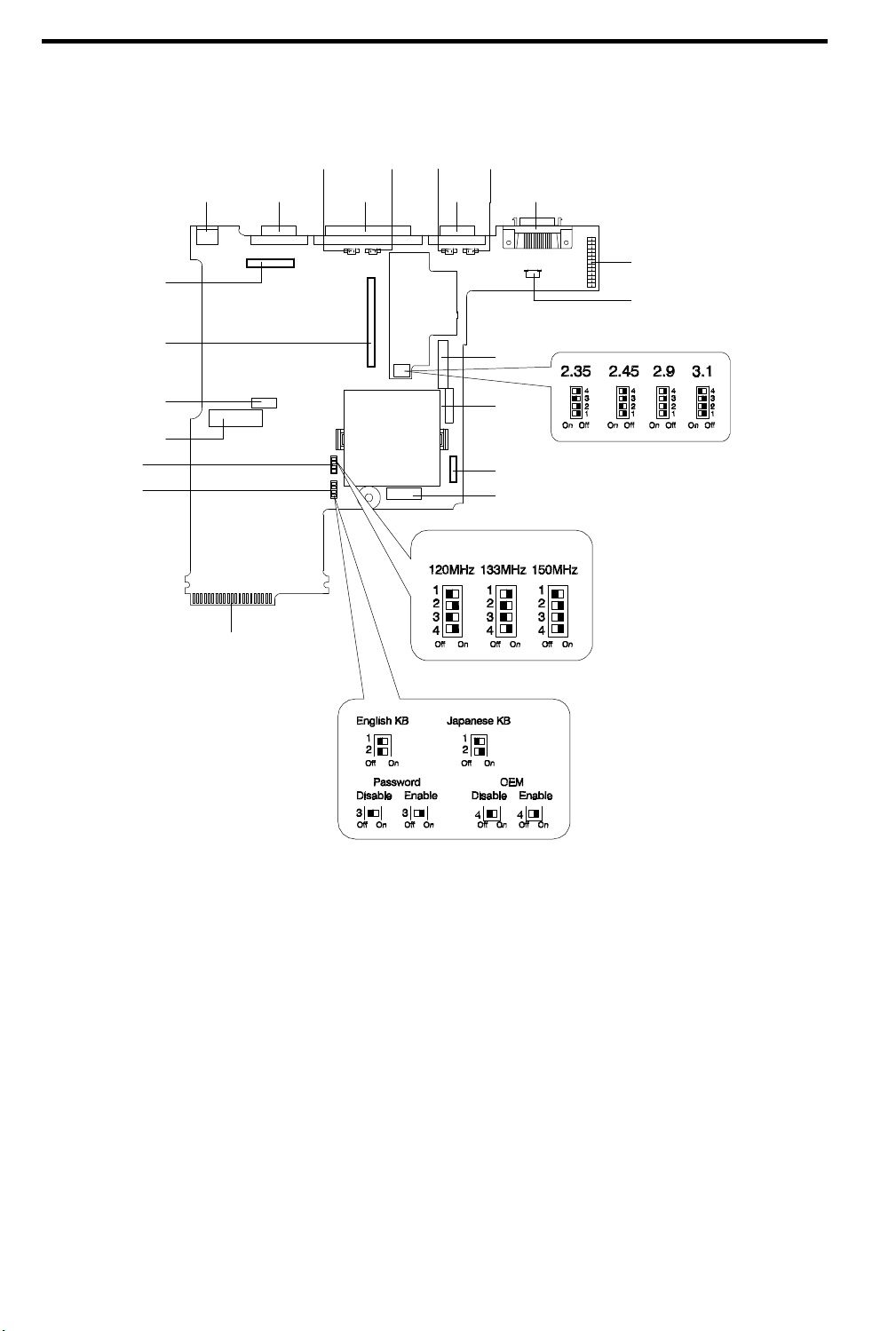

1-4 CPU Voltage (S1) Settings..............................................................................................1-13

1-5 CPU Speed (SW3) Settings .............................................................................................1-13

1-6 Multi-Function Switch (SW2) Settings ...........................................................................1-13

1-7 Memory Address Map ....................................................................................................1-14

1-8 Interrupt Channel Map...................................................................................................1-14

1-9 DMA Channel Map........................................................................................................1-15

1-10 I/O Address Map............................................................................................................ 1-15

1-11 M7101 GPIO Port Definition ..........................................................................................1-16

1-12 Processor Specifications..................................................................................................1-16

1-13 BIOS Specifications........................................................................................................ 1-17

1-14 Memory Configurations ..................................................................................................1-18

1-15 Video RAM Configuration .............................................................................................1-19

1-16 Video Hardware Specification.........................................................................................1-19

1-17 Supported External CRT Resolutions.............................................................................. 1-19

1-18 Supported LCD Resolutions............................................................................................ 1-20

1-19 Parallel Port Configurations............................................................................................1-21

1-20 Serial Port Configurations ..............................................................................................1-21

1-21 Audio Specifications .......................................................................................................1-22

1-22 PCMCIA Specifications.................................................................................................. 1-22

1-23 Touchpad Specifications.................................................................................................1-23

1-24 Keyboard Specifications..................................................................................................1-23

1-25 Windows 95 Key Descriptions........................................................................................1-23

1-26 FDD Specifications......................................................................................................... 1-24

1-27 HDD Specifications........................................................................................................ 1-24

xvi

Page 17

1-28 CD-ROM Specifications................................................................................................. 1-25

1-29 Battery Specifications .....................................................................................................1-25

1-30 Charger Specifications ...................................................................................................1-26

1-31 DC-DC Converter Specifications ....................................................................................1-27

1-32 DC-AC Inverter Specifications.......................................................................................1-27

1-33 LCD Specifications ........................................................................................................1-28

1-34 AC Adapter Specifications .............................................................................................1-29

1-35 Hotkey Descriptions .......................................................................................................1-30

1-36 Standby Mode Conditions and Descriptions....................................................................1-32

1-37 Suspend Mode Conditions and Descriptions...................................................................1-34

1-38 Display Standby Mode Conditions and Descriptions .......................................................1-34

1-39 Hard Disk Standby Mode Conditions and Descriptions...................................................1-35

1-40 Location of Drivers in the System Utility CD..................................................................1-36

1-41 Location of Applications in the System Utility CD .........................................................1-36

1-42 Environmental Requirements.........................................................................................1-38

1-43 Mechanical Specifications..............................................................................................1-39

2-1 Major Chips List..............................................................................................................2-1

2-2 M1521 Signal Descriptions..............................................................................................2-8

2-3 M1523 Signal Descriptions............................................................................................2-18

2-4 M7101 Pin Descriptions.................................................................................................2-26

2-5 M7101 Different Pin Definition Setting..........................................................................2-34

2-6 M7101 Original Pin Definition Setting...........................................................................2-35

2-7 M7101 Numerical Pin List.............................................................................................2-36

2-8 M7101 Alphabetical Pin List..........................................................................................2-37

2-9 M7101 PCI Interface Lock Register................................................................................2-39

2-10 C&T 65550 Pin Descriptions..........................................................................................2-43

2-11 Flat Panel Display Interface Configurations....................................................................2-54

2-12 Bus Output Signal Status During Standby Mode.............................................................2-55

2-13 PCI1131 Pin Descriptions ..............................................................................................2-63

xvii

Page 18

2-14 NS87336VJG Pin Descriptions.......................................................................................2-79

2-15 YMF715 Descriptions.....................................................................................................2-89

2-16 T62.062.C Absolute Maximum Ratings Table ................................................................2-92

2-17 T62.062.C Electrical Characteristics Table.....................................................................2-92

2-18 T62.062.C Pin Description table.....................................................................................2-95

2-19 T62.061.C Pin Descriptions ............................................................................................2-98

2-20 MAXIMUM RATINGS................................................................................................2-102

2-21 Electrical Characteristics.............................................................................................. 2-102

2-22 Pin Description.............................................................................................................2-103

2-23 Pin Description.............................................................................................................2-103

2-24 MAXIMUM RATINGS................................................................................................2-105

2-25 Electrical Characteristics.............................................................................................. 2-105

2-26 J1: 52103-1217 (MOLEX) Pin Description ..................................................................2-106

2-27 J2:SM02(8.0)B-BHS-1-TB2P (JST) Pin Description.....................................................2-106

3-1 Display Device Settings....................................................................................................3-5

3-2 Floppy Disk Drive Control Settings ..................................................................................3-6

3-3 Hard Disk Drive Control Settings.....................................................................................3-6

3-4 System Boot Drive Control Settings ..................................................................................3-7

3-5 CD-ROM Image Descriptions ...........................................................................................3-7

3-6 System Status Descriptions.............................................................................................3-15

4-1 Guide to Disassembly Sequence........................................................................................4-4

C-1 Spare Parts List ...............................................................................................................C-1

E-1 POST Checkpoint List.....................................................................................................E-1

xviii

Page 19

C h a p t e r 1C h a p t e r 1

System Introduction

This chapter introduces the notebook, its features, components and specifications.

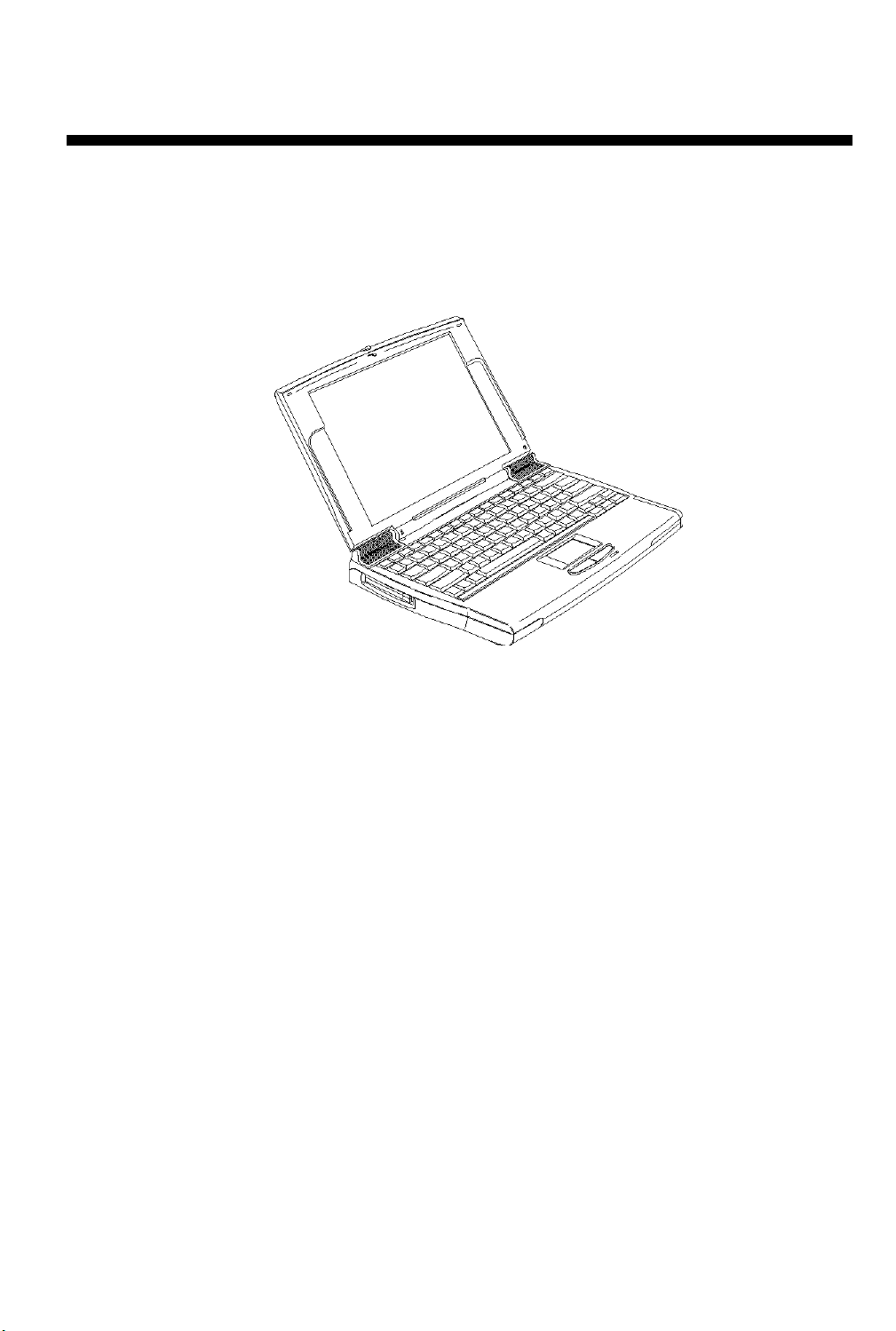

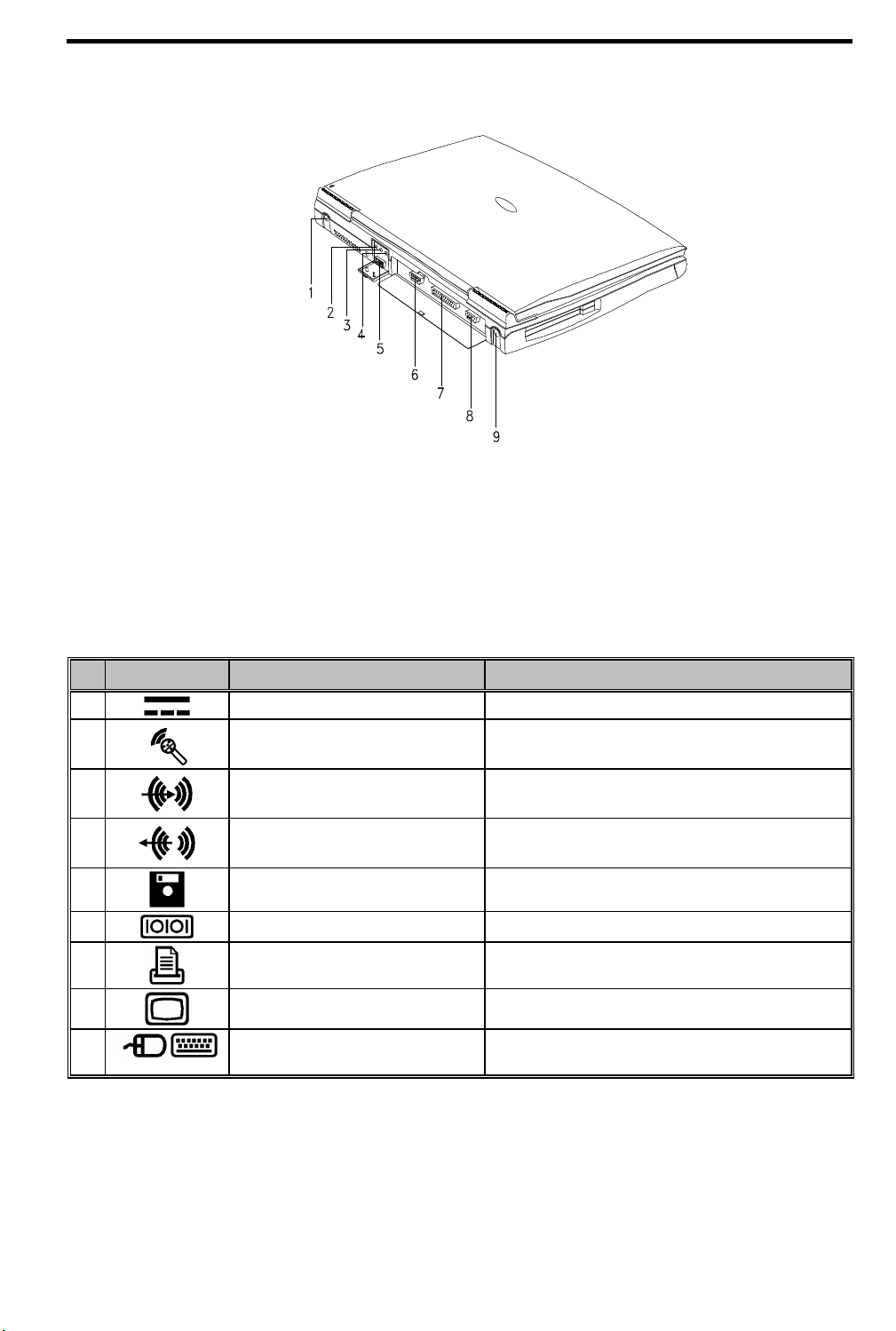

1.1 Overview

The notebook was designed with the user in mind. The figure below shows the notebook with the display

open.

Figure 1-1 Notebook

System Introduction 1-1

Page 20

1.1.1 Features

Here are just a few of the notebook’s many features:

Performance

• High-end Pentium microprocessor

• Support 64-bit main memory and external (L2) cache memory

• Large LCD display (DualScan STN and TFT active matrix.)

• PCI local bus video with graphics acceleration and 1MB video RAM boost video performance

• Internal 3.5-inch floppy drive or CD-ROM drive

• High-capacity, Enhanced-IDE hard disk

• Lithium-Ion or Nickel Metal-Hydride battery pack

• Power management system with standby and hibernation power saving modes

Multimedia

• 16-bit stereo audio with software wavetable

• Built-in dual speakers

• Ultra-slim, high-speed CD-ROM drive

Human-centric Design and Ergonomics

1

• Lightweight and slim

• Sleek, smooth and stylish design

• Full-sized keyboard

• Wide and curved palm rest

• Centrally-located touchpad pointing device

Expansion

• PC card (formerly PCMCIA) slots (two type II/I or one type III) with ZV (Zoomed Video) port support

• Upgradeable memory, hard disk, CPU

1

Some areas or regions may not offer models with a built-in CD-ROM drive.

1-2 Service Guide

Page 21

1.1.2 Rear Ports

1 DC-in Port 6 Serial Port

2 Microphone-in Port 7 Parallel Port

3 Line-in Port 8 External CRT Port

4 Line-out Port 9 PS/2 Port

5 External Floppy Drive Connector

Figure 1-2 Rear Ports

The following table describes these ports.

Table 1-1 Port Descriptions

# Icon Port Connects to...

1 DC-in Port AC adapter and power outlet

2 Microphone-in Port External 3.5mm minijack condenser microphone

3 Line-in Port Line-in device (e.g., CD player, stereo walkman)

4 Line-out Port Line-out device (e.g., speakers, headphones)

5 External Floppy Drive Connector External floppy drive

6 Serial Port Serial device (e.g., serial mouse)

7 Parallel Port Parallel device (e.g., parallel printer)

8 External CRT port Monitor (up to 1024x768, 256-colors )

9

PS/2 Port PS/2-compatible device

(e.g., PS/2 keyboard, keypad, mouse)

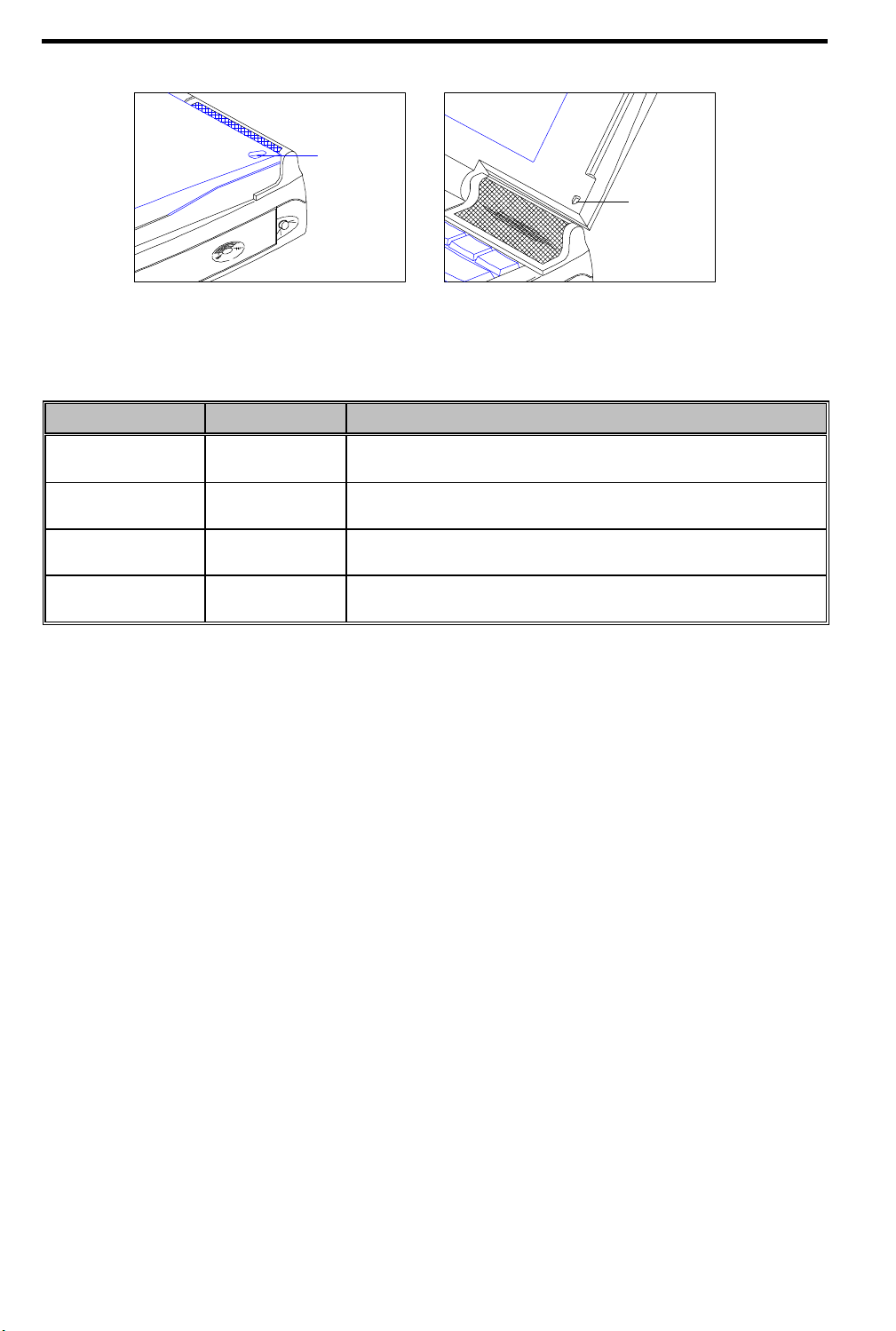

1.1.3 Indicator Light

A two-way indicator light is found on the inside and outside of the display. See figure below.

System Introduction 1-3

Page 22

Indicator

Light

Indicator

Light

Figure 1-3 Indicator Light

This two-way indicator light allows you to see the notebook status when the display is open or closed. The

indicator serves both as a power and battery-charging indicator. See Table 1-2.

Table 1-2 Indicator Status Descriptions

Indicator Status Power Switch Condition

Green On

Red Off Battery is installed and a powered AC adapter is connected to the

Orange On Battery is installed and a powered AC adapter is connected to the

Flashing On Battery is running low on power and no AC adapter is connected to the

Charged battery is installed or a power AC adapter is connected to the

notebook.

notebook and charging the battery (rapid charge mode).

notebook and charging the battery (charge-in-use mode).

notebook.

1-4 Service Guide

Page 23

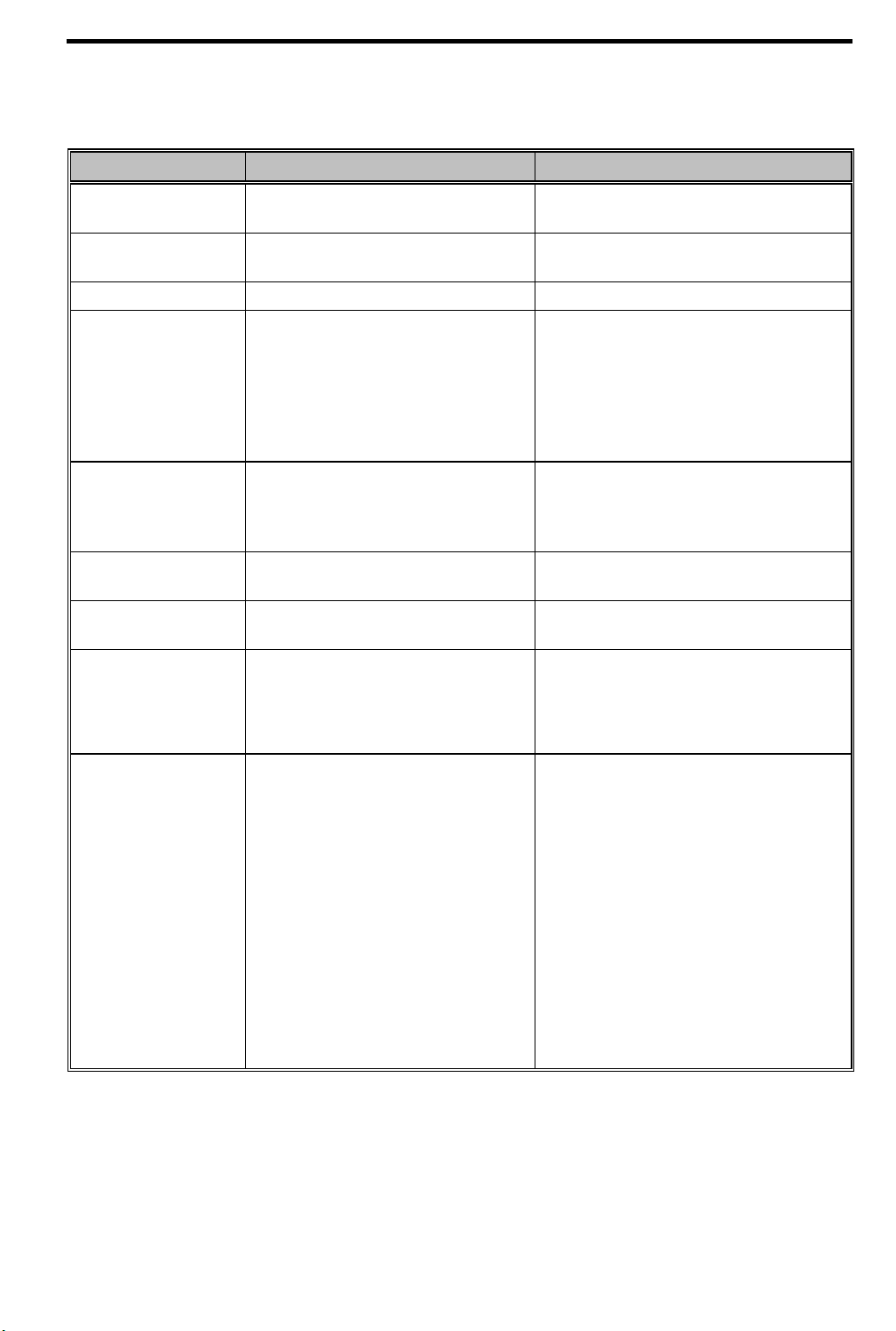

1.1.4 System Specifications Overview

Table 1-3 System Specifications

Item Standard Optional

Microprocessor Intel Pentium™ processor

(Intel P54CSLM 120/133/150 MHz)

System memory 8MB / 16MB

Dual 64-bit memory banks

Flash ROM BIOS 256KB

Data storage devices

CD-ROM model

FDD model

Display DualScan STN or TFT active matrix,

Video PCI local bus video with graphics

Audio 16-bit stereo audio; built-in dual

Keyboard and pointing

device

Removable 12.5mm, 2.5-inch, 1.0GB

Enhanced-IDE hard disk

Internal 15mm, 5.25-inch high-speed

CD-ROM drive

Internal 3.5-inch, 1.44MB floppy drive

800x600, 256 colors (SVGA)

accelerator and 1MB video RAM

speakers; separate audio ports

84-/85-/88-key with Windows 95 keys

Intel P55CLM - 133/150 with MMX

Expandable to 64MB using 8, 16 and 32MB

soDIMMs

1+GB Enhanced-IDE hard disk drive

External 3.5-inch, 1.44MB diskette drive

Up to 1024x768, 256-color ultra-VGA

monitor

LCD projection panel

101-/102-key, PS/2-compatible keyboard or

17-key numeric keypad

Touchpad (centrally-located on palmrest)

I/O ports One 9-pin RS-232 serial port

(UART16550-compatible)

One 25-pin parallel port

(EPP/ECP-compliant)

One 15-pin CRT port

One 6-pin PS/2 keypad/ keyboard/mouse

connector

One type III or two type II PC Card

slot(s) with ZV port support

One external FDD port

External serial or PS/2 mouse or similar

pointing device

Serial mouse, printer or other serial devices

Parallel printer or other parallel devices

Up to a 1024x768, 256-color

ultra-VGA monitor

17-key numeric keypad, PS/2 keyboard or

mouse

LAN card or other PC cards

External diskette drive

System Introduction 1-5

Page 24

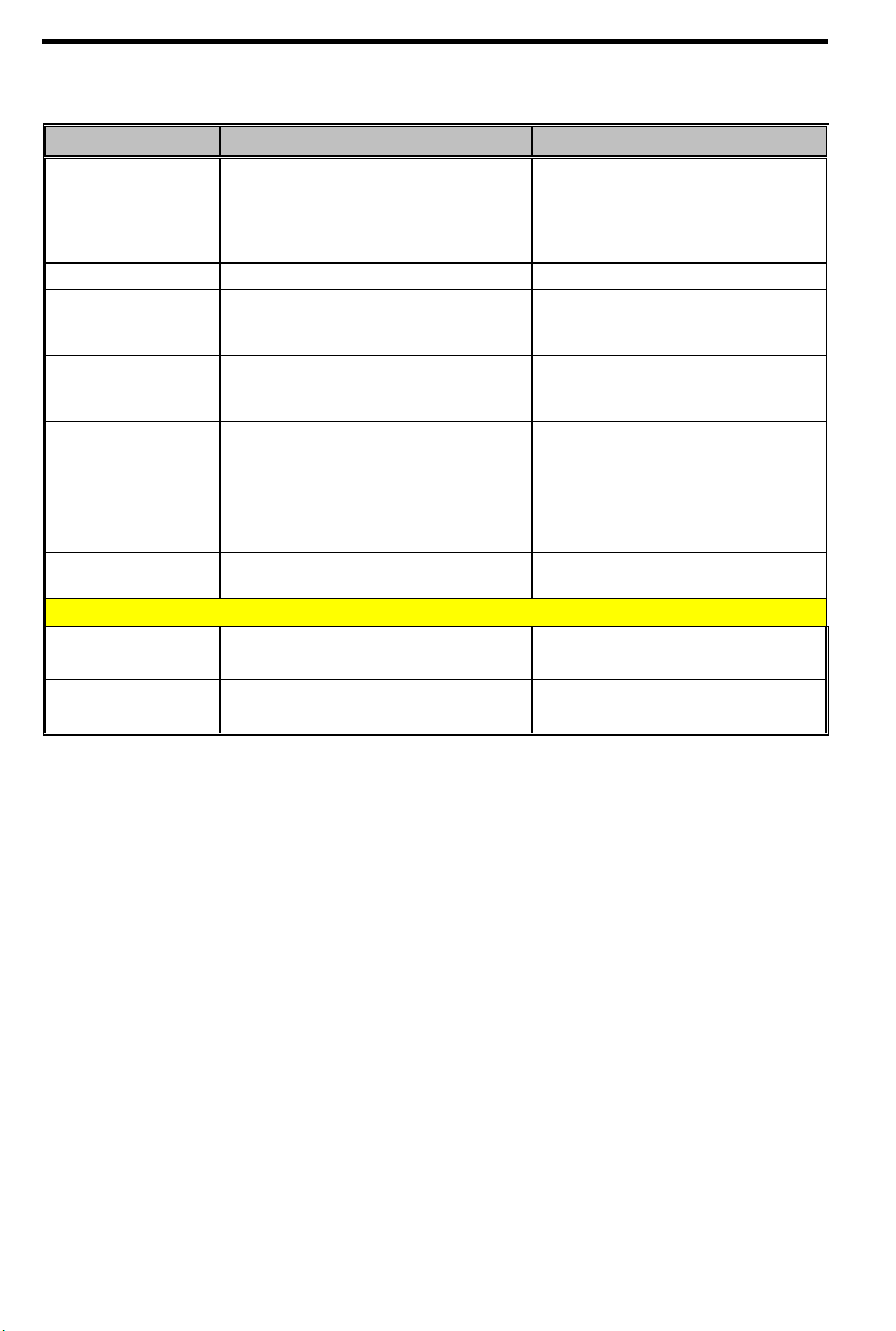

Table 1-3 System Specifications (continued)

Item Standard Optional

I/O ports (continued) One 3.5mm minijack mic-in port

Microphone

One 3.5mm minijack line-in port

One 3.5mm minijack line-out port

Operating system Windows 95 Windows 3.1

Weight

FDD model

CD-ROM model

Dimensions

(main footprint)

Temperature

Operating

Non-operating

Humidity

Operating

Non-operating

AC adapter 100~240 Vac, 50~60 Hz, 45W autosensing

Battery pack

Lithium-Ion 4-5 hr. (rapid-charge)

Nickel Metal-Hydride

battery

(includes battery)

2.6 kg. (5.7 lbs.)

2.8 kg. (6.2 lbs.)

W x D x H

306mm x 228mm x 46mm

(12.05” x 8.98” x 1.81”)

10ºC ~ 35ºC

-20ºC ~ 60ºC

(non-condensing)

20% ~ 80%

20% ~ 80%

AC adapter

6-8 hr. (charge-in-use)

2-2.5 hr. (rapid-charge)

5.5-6.5 hr. (charge-in-use)

Audio CD player or other line-in devices

Speakers or headphones

Extra AC adapter

Extra battery pack

External battery charger/discharger

Extra battery pack

External battery charger/discharger

1-6 Service Guide

Page 25

1.2 System Board Layout

1.2.1 Main Board (PCB No: 96149-SC)

Note: This switch setting is not for Extensa 610 use.

Figure 1-4 Main Board Layout (Top Side)

System Introduction 1-7

Page 26

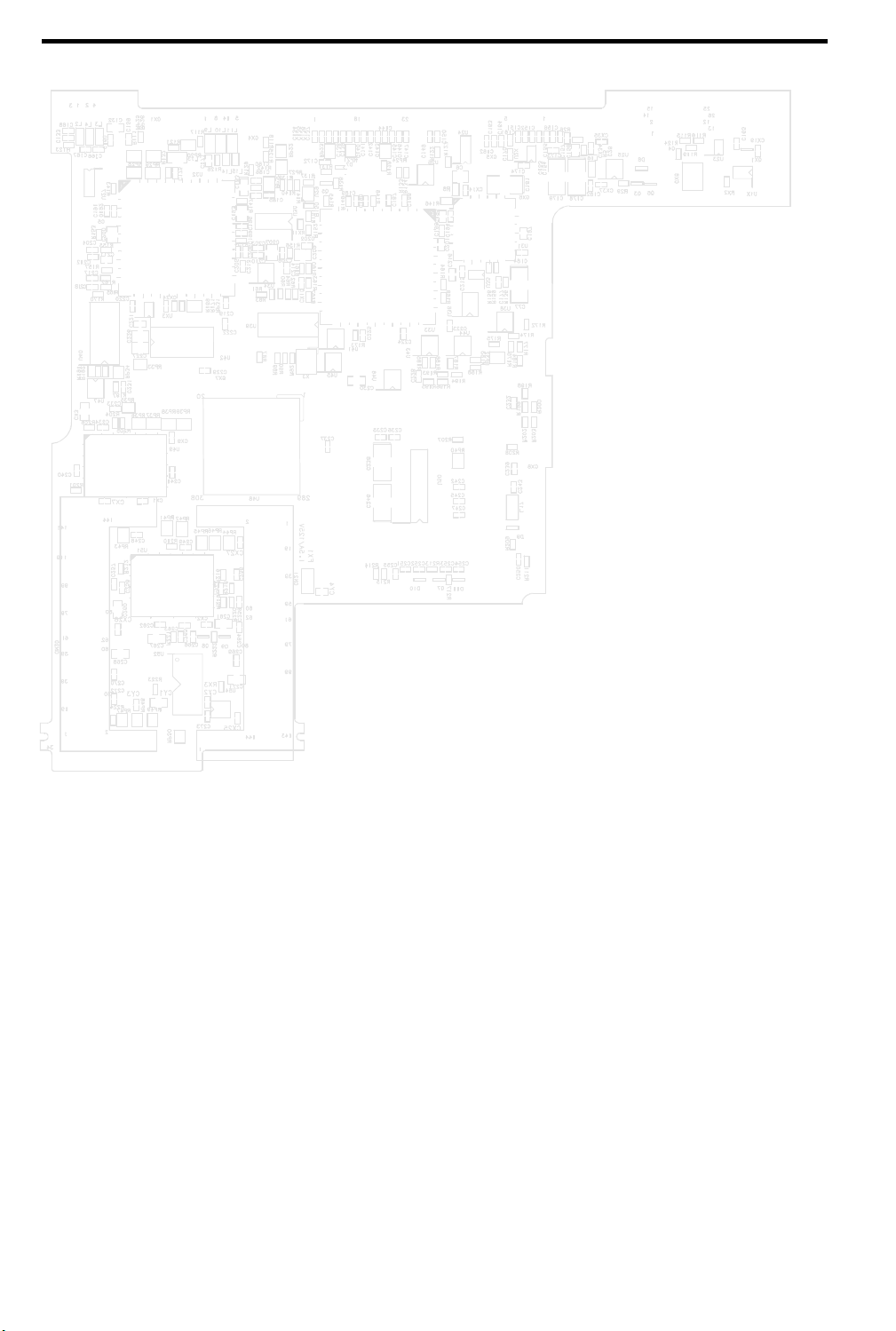

Figure 1-5 Main Board Layout (Bottom Side)

1-8 Service Guide

Page 27

1.2.2 Audio Connection Board (PCB No:96467-1)

Figure 1-6 Audio Connection Board Layout (Top Side)

1.2.3 Battery Connection Board (PCB No:95498-1)

Figure 1-7 Battery Connection Board Layout (Top Side)

Figure 1-8 Battery Connection Board Layout (Bottom Side)

System Introduction 1-9

Page 28

1.2.4 HDD Connection Board (PCB No:96463-1)

Figure 1-9 HDD Connection Board Layout (Top Side)

Figure 1-10 HDD Connection Board Layout (Bottom Side)

1-10 Service Guide

Page 29

1.2.5 Keyboard Connection Board (PCB No: 96465-1)

Figure 1-11 Keyboard Connection Board Layout (Top Side)

Figure 1-12 Keyboard Connection Board Layout (Bottom Side)

System Introduction 1-11

Page 30

1.3 Jumpers and Connectors

Debug Card

CN13

CN15

CN16

SW3

SW2

CN1

CN6

Golden Finger for

CN2

CN7

CN3

CN8

CN9

CN4

CN10

CN14

CN17

CN18

CN19

CN5

CN11

CN12

S1

NOTE: The shaded area

(Black) indicates the position

of the switch.

CN1 External PS/2 keyboard/mouse port CN12 Audio Board Connector

CN2 VGA port CN13 PCMCIA socket connector

CN3 Parallel port CN14 Diskette Drive connector

CN4 Serial port CN15 HDD Connector

CN5 External floppy drive port CN16 Keyboard connector

CN6 LCD Connector CN17 CD-ROM connector

CN7 Audio speaker connector (left) CN18 Battery pack connector

CN8 LCD cover switch connector CN19 Track Point Board Connector

CN9 Fan connector S1 CPU Voltage Setting

CN10 Audio speaker connector (right) SW2 Function Setting

CN11 Charger Connector SW3 CPU Speed Setting

Figure 1-13 Jumpers and Connectors (Top View)

1-12 Service Guide

Page 31

Table 1-4 CPU Voltage (S1) Settings

CPU Voltage 2.35V 2.45V 2.9V 3.1V

Switch 1

Switch 2

Switch 3

Switch 4

Off Off Off Off

Off On Off Off

On Off Off Off

Off Off Off On

Table 1-5 CPU Speed (SW3) Settings

CPU Speed 120MHz 133MHz 150MHz

Switch 1

Switch 2

Switch 3

Switch 4

Off On Off

On Off On

Off Off On

On On On

Table 1-6 Multi-Function Switch (SW2) Settings

Switch ON OFF

1 Keyboard Type (Default OFF)

2 Keyboard Type

3 Password

4 Generic boot-up screen show on screen in

88-key (Japan keyboard) 84/85-key (U.S. keyboard)

- -

Bypass Check

No Yes

POST

System Introduction 1-13

Page 32

1.4 Hardware Configuration and Specification

1.4.1 Memory Address Map

Table 1-7 Memory Address Map

Address Range Definition Function

000000 - 09FFFF 640 KB memory Base memory

0A0000 - 0BFFFF 128 KB video RAM Reserved for graphics display buffer

0C0000 - 0CBFFF Video BIOS Video BIOS

0E0000 - 0EFFFF

128 KB system BIOS System BIOS

0F0000 - 0FFFFF

10000 - 7FFFF

80000 - 27FFF

FE0000 - FFFFFF 256 KB system ROM Duplicate of code assignment at 0E0000-0FFFFF

Extended memory Onboard Memory

System BIOS

SIMM memory

1.4.2 Interrupt Channel Map

Table 1-8 Interrupt Channel Map

Priority Interrupt Number Interrupt Source

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

SMI

NMI

IRQ 0

IRQ 1

IRQ 2

IRQ 8

IRQ 9

IRQ 10

IRQ 11

IRQ 12

IRQ 13

IRQ 14

IRQ 15

IRQ 3

IRQ 4

IRQ 5

IRQ 6

IRQ 7

Power management unit

Parity error detected, I/O channel error

Interval timer, counter 0 output

Keyboard

Interrupt from controller 2 (cascade)

Real-time clock

Cascaded to INT 0AH (IRQ 2)

Audio (option) / PCMCIA

Audio (option) / PCMCIA

PS/2 mouse

INT from coprocessor

Hard disk controller

CD-ROM controller

Serial communication port 2

Serial communication port 1

Parallel port (option) / Audio

Diskette controller

Parallel port (option)

A PCMCIA card can use IRQ 3, 4, 5, 7, 9 and 11 as long as it does not conflict with the

interrupt address of any other device.

1.4.3 DMA Channel Map

Table 1-9 DMA Channel Map

Controller Channel Address Function

1 0 0087 Audio (option)/ECP(option)

1-14 Service Guide

Page 33

1

1

1

2

2

2

2

1

2

3

4

5

6

7

1.4.4 I/O Address Map

Table 1-10 I/O Address Map

Address Range Device

000 - 00F

020 - 021

040 - 043

048 - 04B

060 - 064

070 - 071

080 - 08F

0A0 - 0A1

0C0 - 0DF

170 - 177

178, 17A

1F0 - 1F7

3F6, 3F7

220 - 22F, 240 - 24F

300 - 301, 330 - 331

370 - 371, 388 - 38F

530 - 537, E80 - E89

278 - 27F

2E8 - 2EF

2F8 - 2FF

378, 37A

3BC - 3BE

3B4, 3B5, 3BA

3C0 - 3C5

3C6 - 3C9

3C0 - 3CF

3D0 - 3DF

3E0 - 3E1

3E8 - 3EF

3F0 - 3F7

3F8 - 3FF

CF8 - CFF

DMA controller-1

Interrupt controller-1

Timer 1

Timer 2

Keyboard controller 38802 chip select

Real-time clock and NMI mask

DMA page register

Interrupt controller-2

DMA controller-2

CD-ROM

M7101 registers

Hard disk select

Audio (option) - default

Audio (option)

Audio (option)

Audio (option)

Parallel port 3

COM 4

COM 2

Parallel port 2

Parallel port 1

Video subsystem

Video DAC

Enhanced graphics display

Color graphics adapter

PCMCIA controller

COM3

Floppy disk controller

COM 1

PCI configuration register

0083

0081

0082

Cascade

008B

0089

008A

Audio

Diskette

Audio (option)/ECP(option)

Cascade

-

Spare

-

System Introduction 1-15

Page 34

1.4.5 M7101 GPIO (General Purpose I/O) Port Definition

Table 1-11 M7101 GPIO Port Definition

Item Description

GPIOA2 Smart inverter contrast counter control

GPIOA3 0: Normal operation of system

1: Shutdown system

GPIOA4 Serial data on X24C02

GPIOA5 Battery gauge communication control

GPIOA6 Battery data line

GPIOA7 Thermal sensor data line

GPIOC6 VGA thermal sensor data line

GPIOC7 0: VGA chip standby mode

1: Normal operation

Register E0h bit 8 Serial clock on X24C02

Register E0h bit 9 0: Disable 12V for flash ROM

1: Enable 12V for flash ROM

Register E0h bit 10 0: 3 mode FDD

1: Normal

Register E0h bit 11 Thermal sensor clock line

Register E0h bit 12 Thermal sensor reset

Register E0h bit 13 0: Enable battery LED

1: Disable battery LED

Register E0h bit 14 0: Disable audio amplifier

1: Enable audio amplifier

Register E1h bit 0 0: NiMH battery

1: Li-ion battery

Register E1h bit 1 CPU thermal high

1.4.6 Processor

Table 1-12 Processor Specifications

Item Specification

CPU type P54CSLM-120,P54CSLM-133, P54CSLM-150, P55CLM-133,

P55CLM - 150

CPU package SPGA

Switchable processor speed (Y/N) Yes

Minimum working speed 0MHz while hibernation mode

CPU voltage 3.1V/2.9V/2.45V

1.4.7 BIOS

Table 1-13 BIOS Specifications

1-16 Service Guide

Page 35

Item Specification

BIOS vendor Acer

BIOS version v2.1

BIOS in flash EPROM (Y/N) Yes

BIOS ROM size 256KB

BIOS package type 32-pin TSOP

Same BIOS for STN color/TFT color (Y/N) Yes

The BIOS can be overwritten/upgradeable using the “AFLASH” utility (AFLASH.EXE).

Please refer to software specification section for details.

1.4.8 System Memory

Memory is upgradeable from 8 to 64 MB, employing 8-/16-/32-MB 64-bit soDIMMs (Small Outline Dual

Inline Memory Modules). After installing the memory modules, the system automatically detects and

reconfigures the total memory size during the POST routines. The following lists important memory

specifications.

• Memory bus width: 64-bit

• Expansion RAM module type:144-pin, 64-bit, small outline Dual Inline Memory Module (soDIMM)

• Expansion RAM module size/configuration:

• 8MB (1M*16 x4)

• 16MB (2M*8 x8)

• 32MB (4M*16 x4)

• Expansion RAM module speed/voltage/package: 60ns/3.3v/TSOP EDO

• EDO and fast-page mode DIMMs may be used together in a memory configuration.

System Introduction 1-17

Page 36

The following table lists all possible memory configurations.

Table 1-14 Memory Configurations

Slot 1 Slot 2 Total Memory

8 MB 0 MB 8 MB

0 MB 8 MB 8 MB

8 MB 8 MB 16 MB

16 MB 0 MB 16 MB

0 MB 16 MB 16 MB

16 MB 8 MB 24 MB

8 MB 16 MB 24 MB

16 MB 16 MB 32 MB

32 MB 0 MB 32 MB

0 MB 32 MB 32 MB

32 MB 8 MB 40 MB

8 MB 32 MB 40 MB

32 MB 16 MB 48 MB

16 MB 32 MB 48 MB

32 MB 32 MB 64 MB

1.4.9 Second-Level Cache

This notebook supports 256KB pipeline burst second-level (L2) cache.

1-18 Service Guide

Page 37

1.4.10 Video Memory

Table 1-15 Video RAM Configuration

Item Specification

DRAM or VRAM DRAM(EDO type)

Fixed or upgradeable Fixed

Memory size/configuration 1MB (256K x 16 x 2pcs)

Memory speed 60ns

Memory voltage 3.3V

Memory package TSOP

1.4.11 Video

Table 1-16 Video Hardware Specification

Item Specification

Video chip C&T65550B

Working voltage C&T65550B: 3.3V

C&T65550XX: 3.3V/5V (“XX” represents codes other than “A” (i.e. “B1”))

Video Chip substitutability Yes

During power-on, system supplies 5V to video chip and read its register to determine

whether the video chip is 5V or 3.3V/5V type. If 5V video chip is detected, system

maintains video voltage at 5V; if 3.3V/5V video chip is detected, system switches

video voltage to 3.3V.

1.4.11.1 External CRT Resolution Support

Table 1-17 Supported External CRT Resolutions

Resolution x Color on

External CRT

640x480x16 60,75,85 60 Y Y

640x480x256 60,75,85 60 Y Y

640x480x65,536 60,75,85 60 Y Y

640x480x16,777,216 60,75,85 60 Y N

800x600x16 56,60,75 60 Y Y

800x600x256 56,60,75 60 Y Y

800x600x65,536 56,60 60 Y N

1024x768x16 60,75,86I 60 Y Y

CRT Refresh Rate Simultaneous on

TFT LCD

CRT only Simultaneous SVGA SVGA

Simultaneous on

STN LCD

Table 1-17 Supported External CRT Resolutions (Continued)

Resolution x Color on

External CRT

1024x768x256 60,75,86I 60 Y Y

CRT Refresh Rate Simultaneous on

TFT LCD

Simultaneous on

STN LCD

System Introduction 1-19

Page 38

1280x1024x16 86I 60 Y Y

1.4.11.2 LCD Resolution Support

Table 1-18 Supported LCD Resolutions

Resolution x Color on LCD Only TFT LCD (SVGA) STN LCD (SVGA)

640x480x16 Y Y

640x480x256 Y Y

640x480x65,536 Y Y

640x480x16,777,216 Y 800x600x16 Y Y

800x600x256 Y Y

800x600x65,536 Y 1024x768x16 Y Y

1024x768x256 Y Y

• DSTN color number: 256 colors

• TFT color number: 65536 colors

• Maximum resolution (LCD Panel): 800x600

• Maximum resolution (External CRT): 1280x1024

Using software, you can set the LCD to a higher resolution than its physical resolution, but

the image shown on the LCD will pan.

1-20 Service Guide

Page 39

1.4.12 Parallel Port

Table 1-19 Parallel Port Configurations

Item Specification

Number of parallel ports 1

ECP/EPP support Yes (set by BIOS setup)

Connector type 25-pin D-type

Location Rear side

Selectable parallel port (by BIOS Setup)

• Parallel 1 (3BCh, IRQ7)

• Parallel 2 (378h, IRQ7)

• Parallel 3 (278h, IRQ5)

• Disable

1.4.13 Serial Port

Table 1-20 Serial Port Configurations

Item Specification

Number of serial ports 1

16550 UART support Yes

Connector type 9-pin D-type

Location Rear side

Selectable serial port (by BIOS Setup)

• Serial 1 (3F8h, IRQ4)

• Serial 2 (2F8h, IRQ3)

• Disable

System Introduction 1-21

Page 40

1.4.14 Audio

Table 1-21 Audio Specifications

Item Specification

Chipset YMF715

Audio onboard or optional Built-in

Mono or stereo Stereo

Resolution 16-bit

Compatibility SB-16 , Windows Sound System

Mixed sound sources Voice, Synthesizer, Line-in, Microphone, CD

Voice channel 8-/16-bit, mono/stereo

Sampling rate 44.1 kHz

Internal microphone No

Internal speaker / quantity Yes / 2 pcs.

Microphone jack Yes

Headphone jack Yes

1.4.15 PCMCIA

PCMCIA is an acronym for Personal Computer Memory Card International Association. The PCMCIA

committee set out to standardize a way to add credit-card size peripheral devices to a wide range of personal

computers with as little effort as possible.

There are two type II/I or one type III PC Card slots found on the left panel of the notebook. These slots

accept credit-card-sized cards that enhances the usability and expandability of the notebook.

ZV (Zoomed Video) port support allows your system to support hardware MPEG in the form of a ZV PC

card.

Table 1-22 PCMCIA Specifications

Item Specification

Chipset TI 1131

Supported card type Type-II / Type-III

Number of slots Two Type-II or one Type-III

Access location Left side

ZV (Zoomed Video) port support Yes (only in lower slot)

1-22 Service Guide

Page 41

1.4.16 Touchpad

Table 1-23 Touchpad Specifications

Item Specification

Vendor & model name

Power supply voltage (V) 5 ± 10%

Location Palm-rest center

Internal & external pointing device work simultaneously Yes

Support external pointing device hot plug Yes

X/Y position resolution (points/mm) 20

Interface PS/2 (compatible with Microsoft mouse driver)

Synaptics TM1002MPU

1.4.17 Keyboard

Table 1-24 Keyboard Specifications

Item Specification

Vendor & model name SMK KAS1901-0161R (English)

Total number of keypads 84/85 keys

Windows 95 keys Yes, (Logo key / Application key):

Internal & external keyboard work simultaneously Yes

1.4.17.1 Windows 95 Keys

The keyboard has two keys that perform Windows 95-specific functions. See Table 1-26.

Table 1-25 Windows 95 Key Descriptions

Key Description

Windows logo key Start button. Combinations with this key performs special functions. Below are a few

examples:

• Windows + Tab Activate next Taskbar button

• Windows + E Explore My Computer

• Windows + F Find Document

• Windows + M Minimize All

• Shift + Windows + M Undo Minimize All

• Windows + R Display Run dialog box

Application key Opens the application’s context menu (same as right-click).

System Introduction 1-23

Page 42

1.4.18 FDD

Table 1-26 FDD Specifications

Item Specification

Vendor & model name Mitsumi D353F2

Floppy Disk Specifications

Media recognition 2DD (720K) 2HD (1.2M, 3-mode) 2HD (1.44M)

Sectors / track 9 15 18

Tracks 80 80 80

Data transfer rate (Kbits/s) 250 300 500 500

Rotational speed (RPM) 300 360 360 300

Read/write heads 2

Encoding method MFM

Power Requirement

Input Voltage (V) +5 ± 10%

1.4.19 HDD

Table 1-27 HDD Specifications

Item Specification

Vendor & Model Name IBM DMCA21080 IBM DMCA21440 IBM DTNA22160 Toshiba

MK1002MAV

Drive Format

Capacity (MB) 1080 1440 2160 1085

Bytes per sector

Logical heads

Logical sectors

Logical cylinders 2100 2800 4200 2100

Physical read/write heads 3

Disks

Spindle speed (RPM) 4009 4009 4000 4635

Performance Specifications

Buffer size (KB) 128 96 96 128

Interface ATA-3 ATA-3 ATA-3 ATA-3

Data transfer rate

(disk-buffer, Mbytes/s)

512 512

16 16

63 63

4

2 2

39.5 ~ 61.8 39.5 ~ 61.8 39.1~ 61.6 29.3 ~ 55.5

512 512

16 16

63 63

6 6

3 3

1-24 Service Guide

Page 43

Item Specification

Performance Specifications

Data transfer rate

(host-buffer, Mbytes/s)

DC Power Requirements

Voltage tolerance (V)

16.6 (max., PIO

mode 4)

5 ± 5%

16.6 (max., PIO

mode 4)

5 + 5%, -10%

16.6 (max., PIO

mode 4)

5 ± 5% 5 ± 5%

1.4.20 CD-ROM

Table 1-28 CD-ROM Specifications

Item Specification

Vendor & Model Name

Performance Specification

Speed (KB/sec) 150 (normal speed)

Access time (ms) 170 (Typ.)

Buffer memory (KB) 128

Interface Enhanced IDE (ATAPI) compatible

Applicable disc format CD-DA, CD-ROM, CD-ROM XA (except ADPCM), CD-I,

Loading mechanism Drawer type, manual load/release

Power Requirement

Input Voltage (V) 5

Panasonic UJDCD8730

1500 (10X speed)

Photo CD (Multisession), Video CD, CD+

16.6 (max., PIO

mode 4)

1.4.21 Battery

Table 1-29 Battery Specifications

Item Specification

Battery gauge on screen Yes, by hotkey Yes, by hotkey Yes, by hotkey

Vendor & model name Sanyo BTP-W31 Sony BTP-T31 Toshiba BTP-X31

Battery type NiMH Li-Ion NiMH

Cell capacity (mAH) 3500 4050 3500

Cell voltage (V) 1.2 3.6 1.2

Number of battery cell 9-cell 9-Cell 9-Cell

Package configuration 9 serial 3 serial, 3 parallel 9 serial

Package voltage (V) 10.8 10.8 10.8

Package capacity (WAH) 37.8 40.5 37.8

System Introduction 1-25

Page 44

1.4.22 Charger

To charge the battery, place the battery pack inside the battery compartment and plug the AC adapter into

the notebook and an electrical outlet. The adapter has three charging modes:

• Rapid mode

The notebook uses rapid charging when power is turned off and a powered AC adapter is connected to

it. In rapid mode, a fully depleted battery gets fully charged in approximately two hours.

• Charge-in-use mode

When the notebook is in use with the AC adapter plugged in, the notebook also charges the battery

pack if installed. This mode will take longer to fully charge a battery than rapid mode. In charge-inuse mode, a fully depleted battery gets fully charged in approximately six to eight hours.

• Trickle mode

When the battery is fully charged, the adapter changes to trickle mode to maintain the battery charge

level. This prevents the battery from draining while the notebook is in use.

Table 1-30 Charger Specifications

Item Specification

Vendor & model name Ambit T62.062.C.00

Input voltage (from adapter, V) 19 (min.)

20 (typ.),

20.5 (max.)

Battery Low Voltage

Battery Low 1 level (V) 10.7 (typ., for NiMH)

8.65 (typ., for LIB)

Battery Low 2 level (V) 10.35 (typ., for NiMH)

8.23 (typ., for LIB)

Battery Low 3 level (V) 9.22 (typ., for NiMH)

7.73 (typ., for LIB)

Charge Current

Fast charge (charge when system is still operative, A) 0.65 (typ.)

Quick charge (charge while system is not operative, A) 1.9 (typ.)

Charging Protection

Safety timer for Fast Charge mode while notebook is operating (minute) 576 (NiMH)

Safety timer for Quick Charge mode while notebook is not operating (minute) 192 (NiMH)

Maximum temperature protection (ºC) 60

Maximum voltage protection (V) 16.2V for NiMH

Over voltage protection 13V for Li-ion

1.4.23 DC-DC Converter

DC-DC converter generates multiple DC voltage level for whole system unit use.

Table 1-31 DC-DC Converter Specifications

1-26 Service Guide

Page 45

Item Specification

Vendor & model name Ambit T62.061.C.00

Input voltage (Vdc) 8~21

Output Rating 5V 3.3V 2.9V

(2.35/2.45/2.9/3.1V)

Current (w/ load, A) 0~3.2 0~3.3 0~3.0 0~0.15 0~0.1 0.005

Voltage ripple (max., mV) 75 75 50 100 300 75

Voltage noise (max., mV) 100 100 100 200 500 100

OVP (Over Voltage Protection, V) 6.5~8.2 4.5~6.2 3.3~5.0 for

2.9/3.1/2.35V/2.45V

+12V +6V 5VSB

14~20 7~9 -

1.4.24 DC-AC Inverter

DC-AC inverter is used to generate very high AC voltage, then supply to LCD CCFT backlight use, and is

also responsible for the control of LCD brightness. Avoid touching the DC-AC inverter area while the

system unit is turned on.

Table 1-32 DC-AC Inverter Specifications

Item Specification

Vendor & model name Ambit T62.066.C.00 / Ambit T62.064.C.00

Input voltage (V) 7.3 (min.) - 20 (max.)

Input current (mA) - 420 (typ.) 550 (max.)

Output voltage (Vrms, no load) 1000 (min.) - 1500 (max.)

Output voltage frequency (kHz) 25 (min.) 42 (typ.) 60 (max.)

Output current (mArms) 1.5~5.5 (min.) 2.0~6.0 (typ.) 2.5~6.5 (max.)

System Introduction 1-27

Page 46

1.4.25 LCD

Table 1-33 LCD Specifications

Item Specification

Vendor & model name HITACHI

LMG9900ZWCC

Mechanical Specifications

LCD display area

(diagonal, inch)

Display technology STN STN TFT TFT

Resolution SVGA (800x600) VGA (800x600) SVGA (800x600) SVGA (800x600)

Supported colors -- -- 262,144 colors 262,144 colors

Optical Specification

Contrast ratio 30 (typ.) 30 (typ.) 100 (typ.) 100 (typ.)

Brightness (cd/m2)

Brightness control keyboard hotkey keyboard hotkey keyboard hotkey keyboard hotkey

Contrast control using keyboard

Electrical Specification

Supply voltage for LCD

display

Supply voltage for LCD

backlight (Vrms)

11.3 11.3 11.3 12.1

70 (typ.) 70 (typ.) 70 (typ.) 70 (typ.)

hotkey

3.3 or 5 (typ.) 3.3 (typ.) 3.3 3.3 (typ.), 3.63

590 (typ.) 590 (typ.) 590 480

TORiSAN

LM-FH53-22NAW

using keyboard

hotkey

IBM

ITSV45E

none none

GOLDSTAR

LP121S1-J

(max.)

The LCD ID code can be set by using the LCD ID utilization utility

(370pw.exe/370pr.exe). Please refer to the software specification section for details.

1-28 Service Guide

Page 47

1.4.26 AC Adapter

Table 1-34 AC Adapter Specifications

Item Specification

Vendor & model name Delta ADP-45GB REV.E2

Input Requirements

Nominal voltages (Vrms) 90 - 264

Frequency variation range (Hz) 47 - 63

Maximum input current (A, @90Vac, full load) 1.5 A

Inrush current The maximum inrush current will be less than 50A and 100A

when the adapter is connected to 115Vac(60Hz) and

230Vac(50Hz) respectively.

Efficiency It should provide an efficiency of 83% minimum, when

measured at maximum load under 115V(60Hz)

Output Ratings (CV mode)

DC output voltage (V) +19

Noise + Ripple (mV) 300

Load (A) 0 (min.) 2.4 (max.)

Dynamic Output Characteristics

Turn-on delay time (s, @115Vac) 2

Hold up time (ms; @115 Vac input, full load) 5 (min.)

Over Voltage Protection (OVP, V) 26

Short circuit protection Output can be shorted without damage

Electrostatic discharge (ESD, kV) ±15 (at air discharge)

Dielectric Withstand Voltage

Primary to secondary 3000 Vac (or 4242 Vdc), 10 mA for 1 second

Leakage current 0.25 mA maximum @ 254 Vac, 60Hz.

Regulatory Requirements

Internal filter meets:

1. FCC class B requirements.

2. CISPR 22 Class B requirements.

System Introduction 1-29

Page 48

1.5 Software Configuration and Specification

1.5.1 BIOS

The BIOS is compliant to PCI v2.1, APM v1.2, E-IDE and PnP specification. It also defines the hotkey

functions and controls the system power-saving flow.

1.5.1.1 Keyboard Hotkey Definition

The notebook supports the following hotkeys.

Table 1-35 Hotkey Descriptions

Hotkey

Fn-Esc Hotkey Escape Exits the hotkey control.

Fn-F1

Fn-F2 Brightness Control

Fn-F3 Display Toggle Switches display from LCD to CRT to both LCD and CRT.

Fn-F4 Battery Gauge Displays the battery gauge.

Fn-F5 Volume Control

Fn-F6 Setup Gains access to BIOS Setup’s Advanced System Configuration