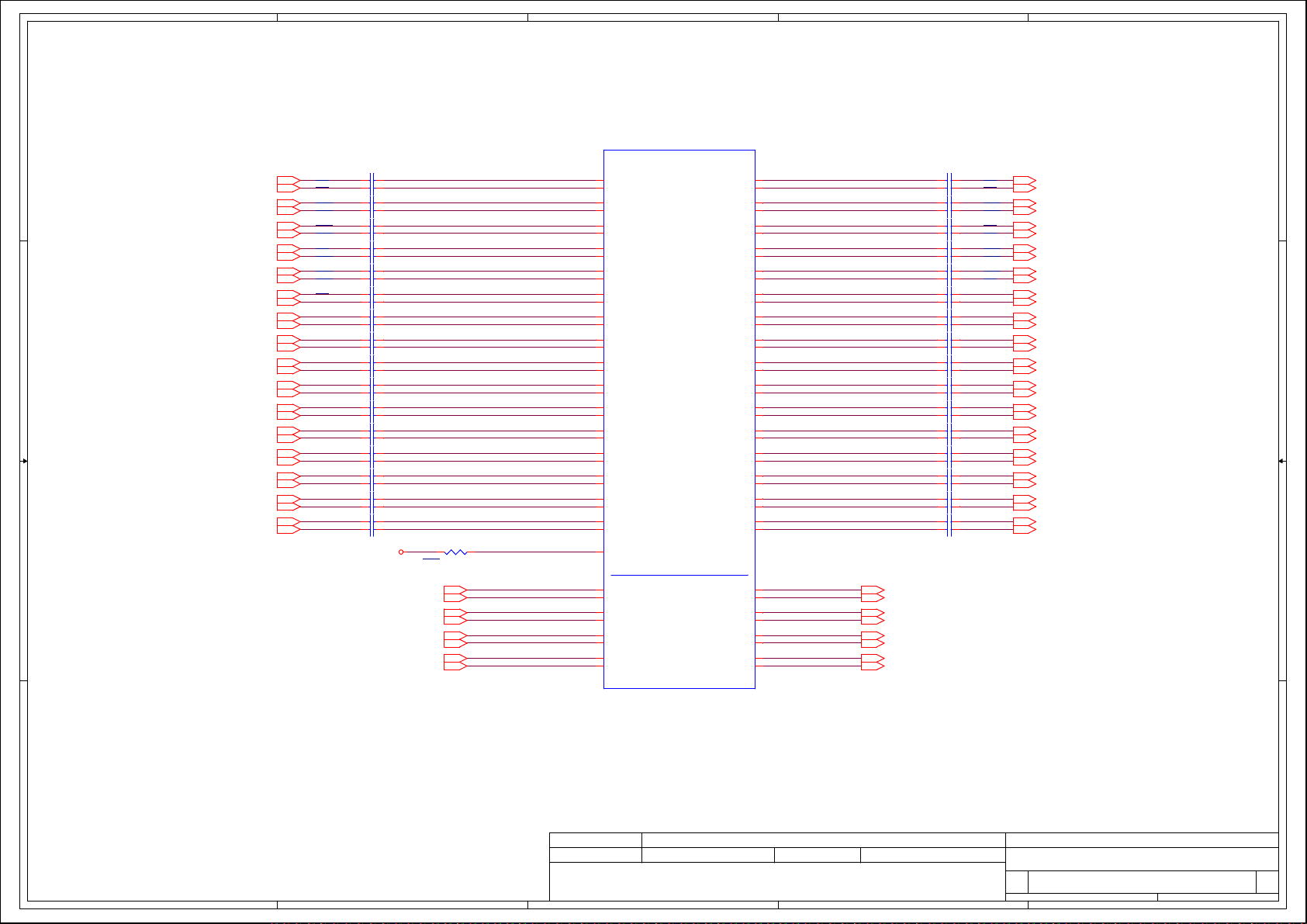

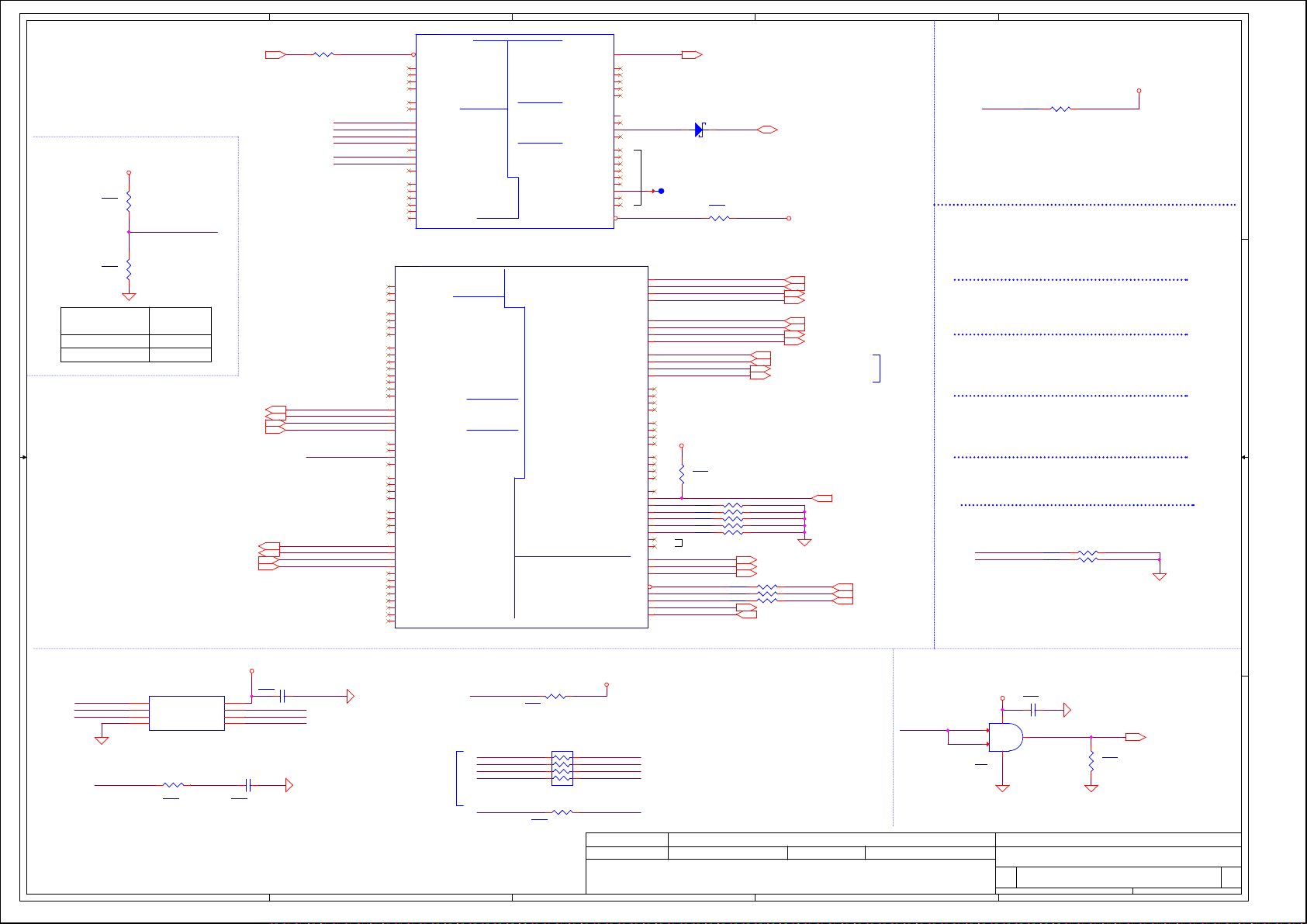

Acer Predator Helios 300 G3-571 Schematic

A

1 1

2 2

B

C

D

E

Compal Confidential

C5PRH MB Schematic Document

LA-E921P

3 3

Rev:1.A

2017.03.29

4 4

Security Classification

Security Classification

Security Classification

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2016/12/15 2017/12/15

2016/12/15 2017/12/15

2016/12/15 2017/12/15

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Title

Title

Title

Cover&Sheet

Cover&Sheet

Cover&Sheet

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

C5PRH M/B LA-E921P

C5PRH M/B LA-E921P

C5PRH M/B LA-E921P

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

173Friday, March 31, 2017

173Friday, March 31, 2017

173Friday, March 31, 2017

E

1.A

1.A

1.A

A

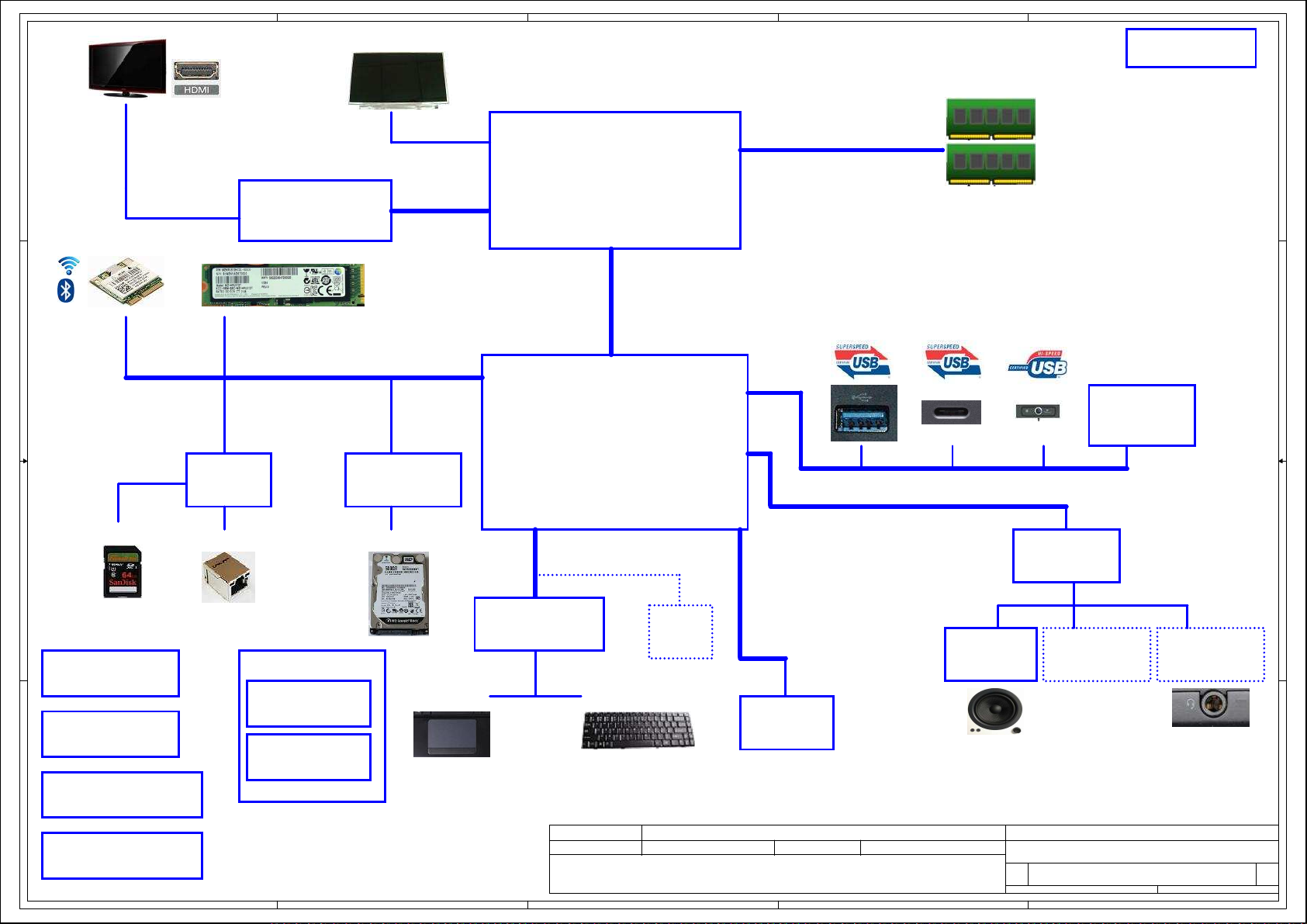

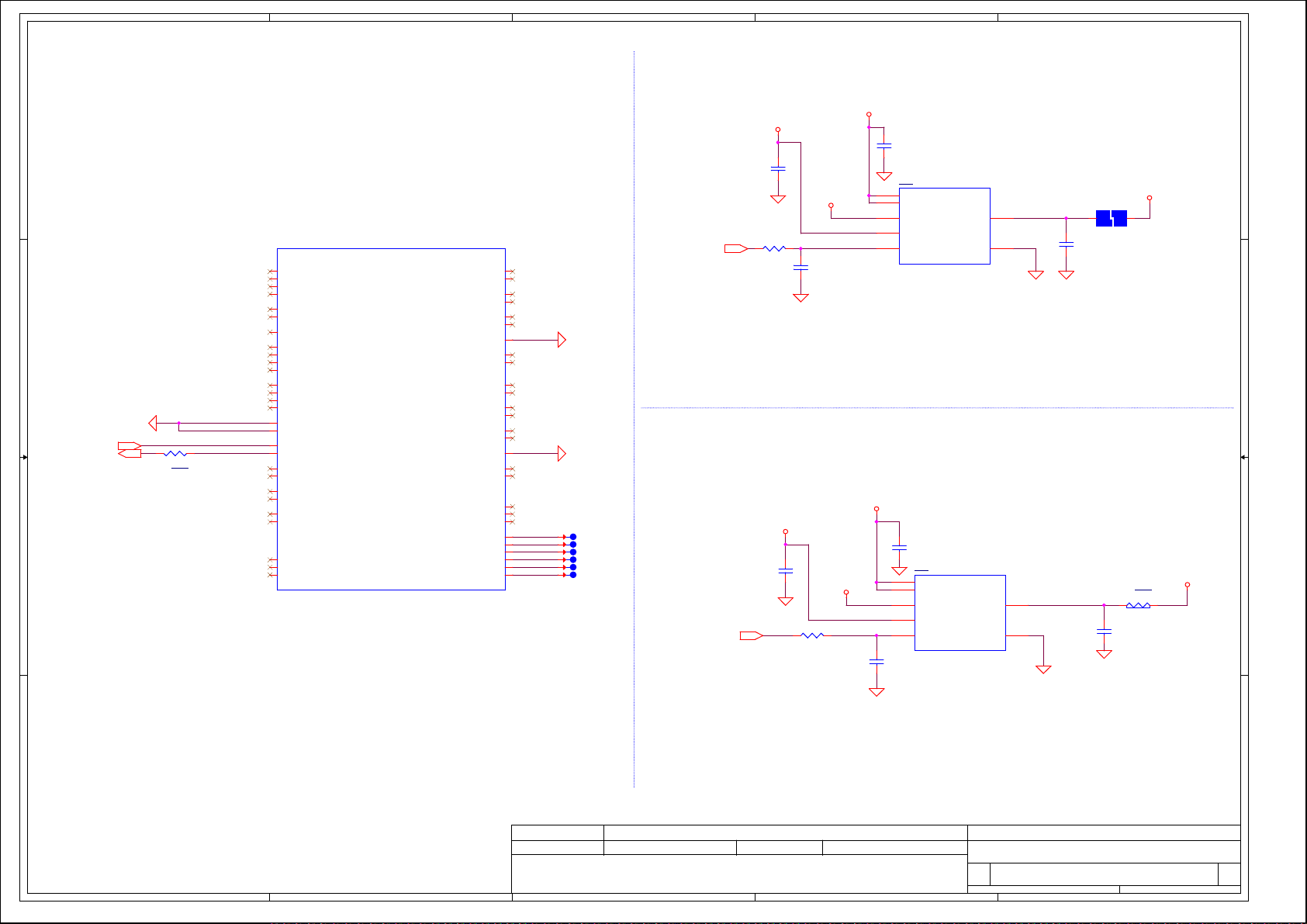

HDMI Conn.

eDP

B

C

D

E

Fan Control*2

page 42

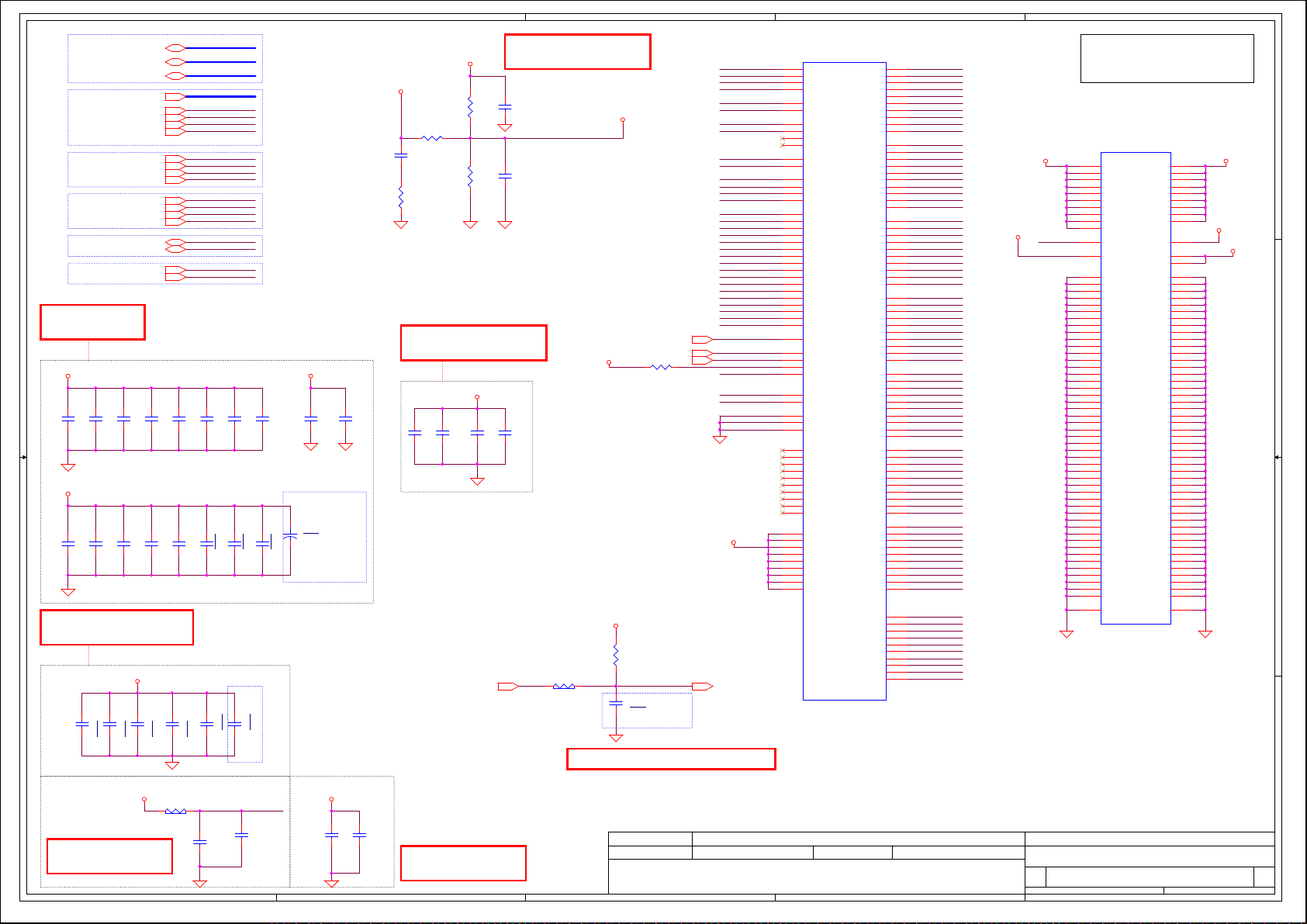

Interleaved Memory

page 30

1 1

eDP

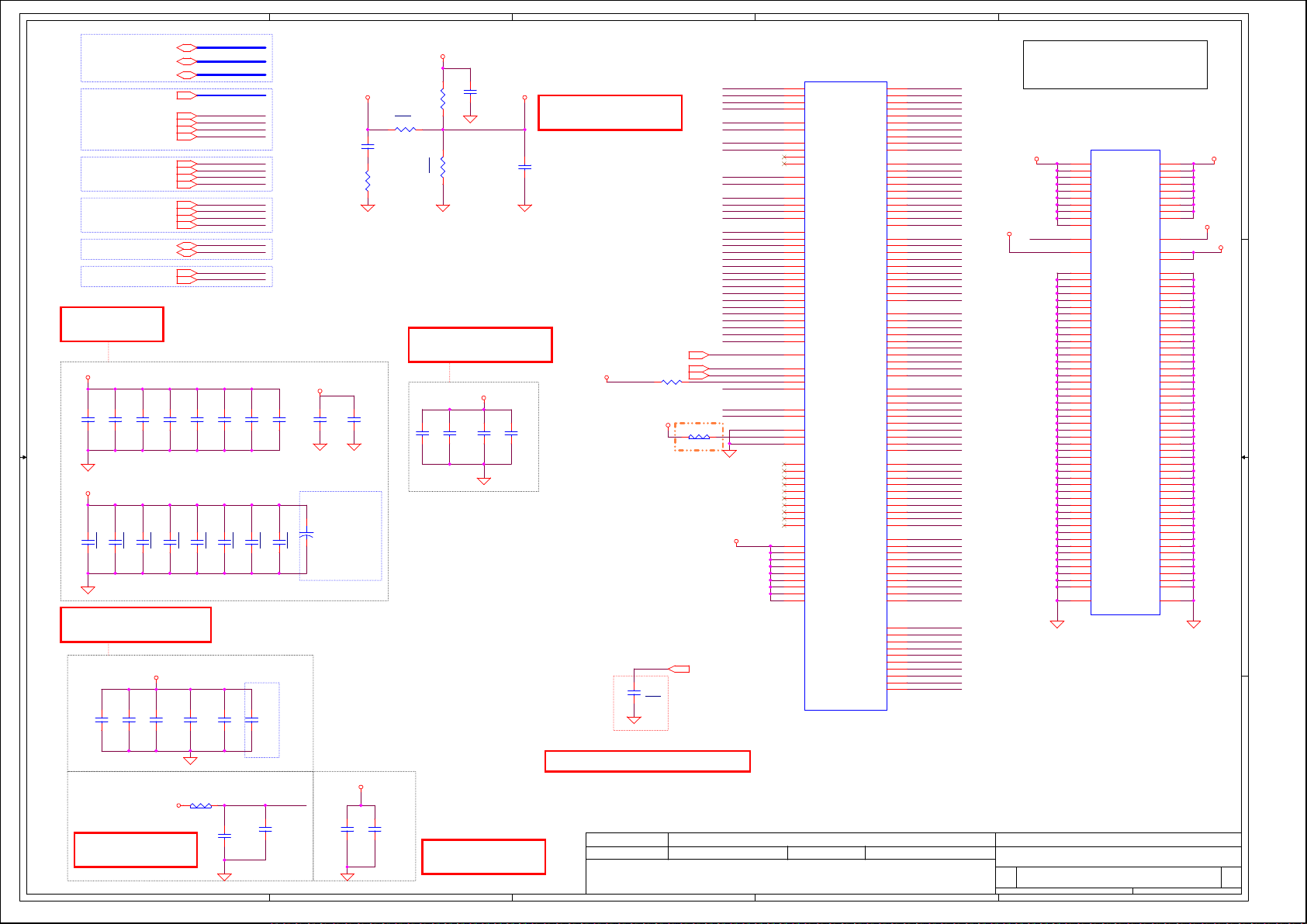

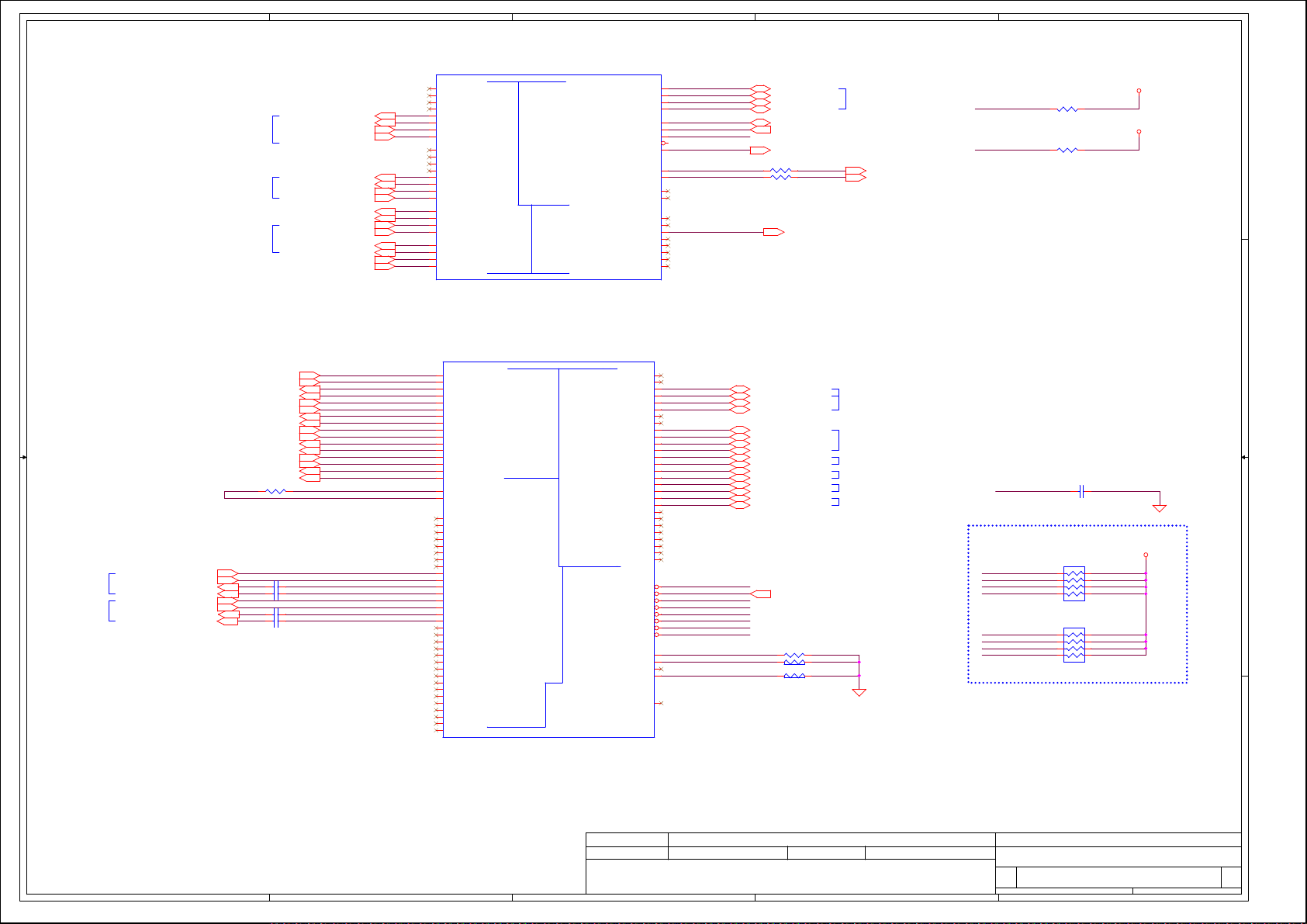

Kabylake H PROCESSOR

BGA1440

HDMI x 4 lanes

Nvidia N17E-G1

with gDDR5 x6

page 23 ~34

PEG x16

8GT/s

(42X28) (SKL-H_4+2)

Processor

page 06 ~13

Memory BUS

Dual Channel

1.2V DDR4 1333/1600

260 pin DDR4-SO-DIMM X1

BANK 0, 1, 2, 3

page 14

260pin DDR4-SO-DIMM X1

BANK 4, 5, 6, 7

page 15

NGFF

WLAN

USB port 7

2 2

page 37

PCIE 2.0

5GT/s

port 3

Card Reader

3 3

page 34

PCIE 3.0 x4

8GT/s

Port 9-12

page 32

PCIE 2.0

5GT/s

port 4

LAN(GbE)

Realtek 8411B

RJ45 conn.

page 32.

SATA Re-Driver

PARADE PS8527

SATA HDD Conn.

page 38

Flexible IO

page 38

SATA3.0

6.0 Gb/s

port 3

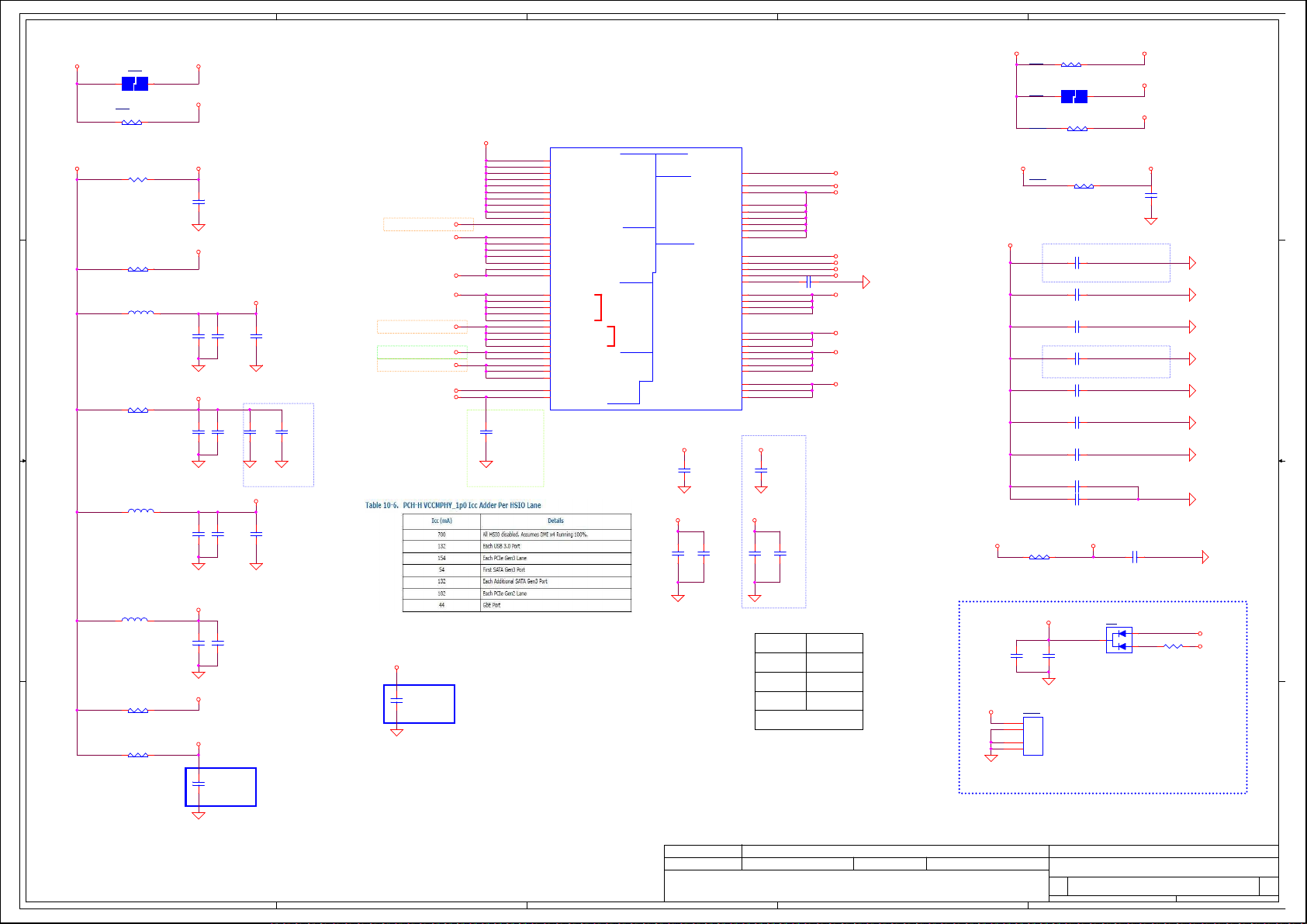

Skylake PCH - H

FCBGA(23X23)

837pin FCBGA

LPC/eSPI BUS

CLK= 24 MH z

ENE

KB9022/9032

page 39

X4 DMI

TPM

USBx8

HD Audio

page 16 ~22

page 41

USB 3.0

conn x1

USB (port 1,2)

48MH z

page 36 page 30

3.3V 24MHz

SPI

RTC CKT.

page 21

Power On/Off CKT.

page 41

DC/DC Interface CKT.

4 4

page 43

Power Circuit DC/DC

page 44 ~61

A

Sub Board

LS-E921P

HS/B

LS-E922P

USB2/B

page 33

page 33

Touch Pad Int.KBD

PS2 / I2C

Issued D ate

Issued D ate

Issued D ate

page 41

page 41

Security Classification

Security Classification

Security Classification

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

SPI ROM x1

page 17

Compal Secret Data

Compal Secret Data

2016/12/15 2017/12/15

2016/12/15 2017/12/15

2016/12/15 2017/12/15

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

USB 3.0

Type-C x1

USB/B

D

(port 3)

page 35

Int. Speaker

CMOS

Camera

USB (port 9)

Finger_Print

USB (port 11)

page 31

HDA Codec

ALC255

page 40

Int. DMIC

page 40

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

on Sub/B

page 33 page 33

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

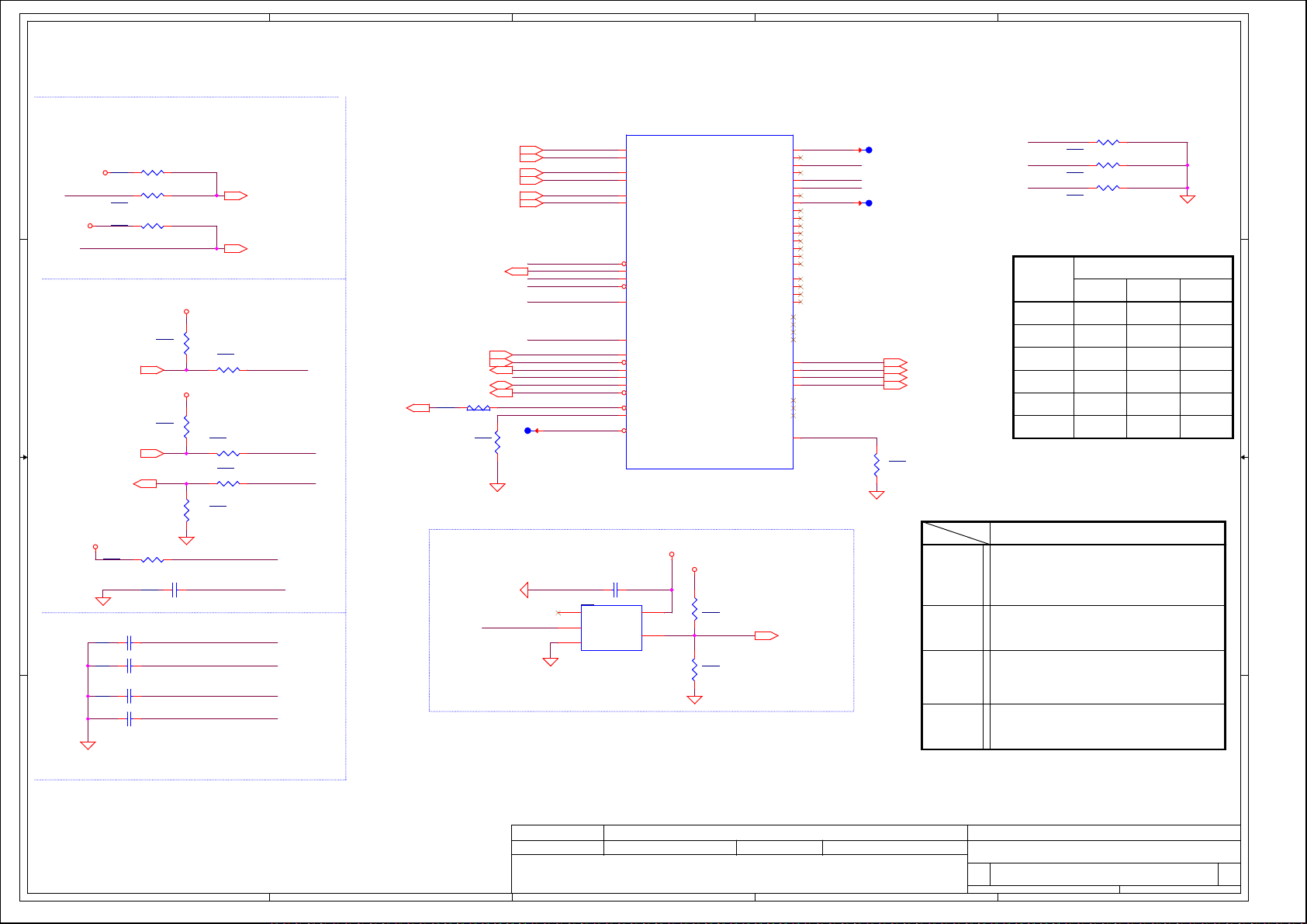

Block Diagrams

Block Diagrams

Block Diagrams

C5PRH M/B LA-E921P

C5PRH M/B LA-E921P

C5PRH M/B LA-E921P

UAJ

on Sub/B

E

273Friday, March 31, 2017

273Friday, March 31, 2017

273Friday, March 31, 2017

of

of

of

1.A

1.A

1.A

A

1 1

B

C

D

E

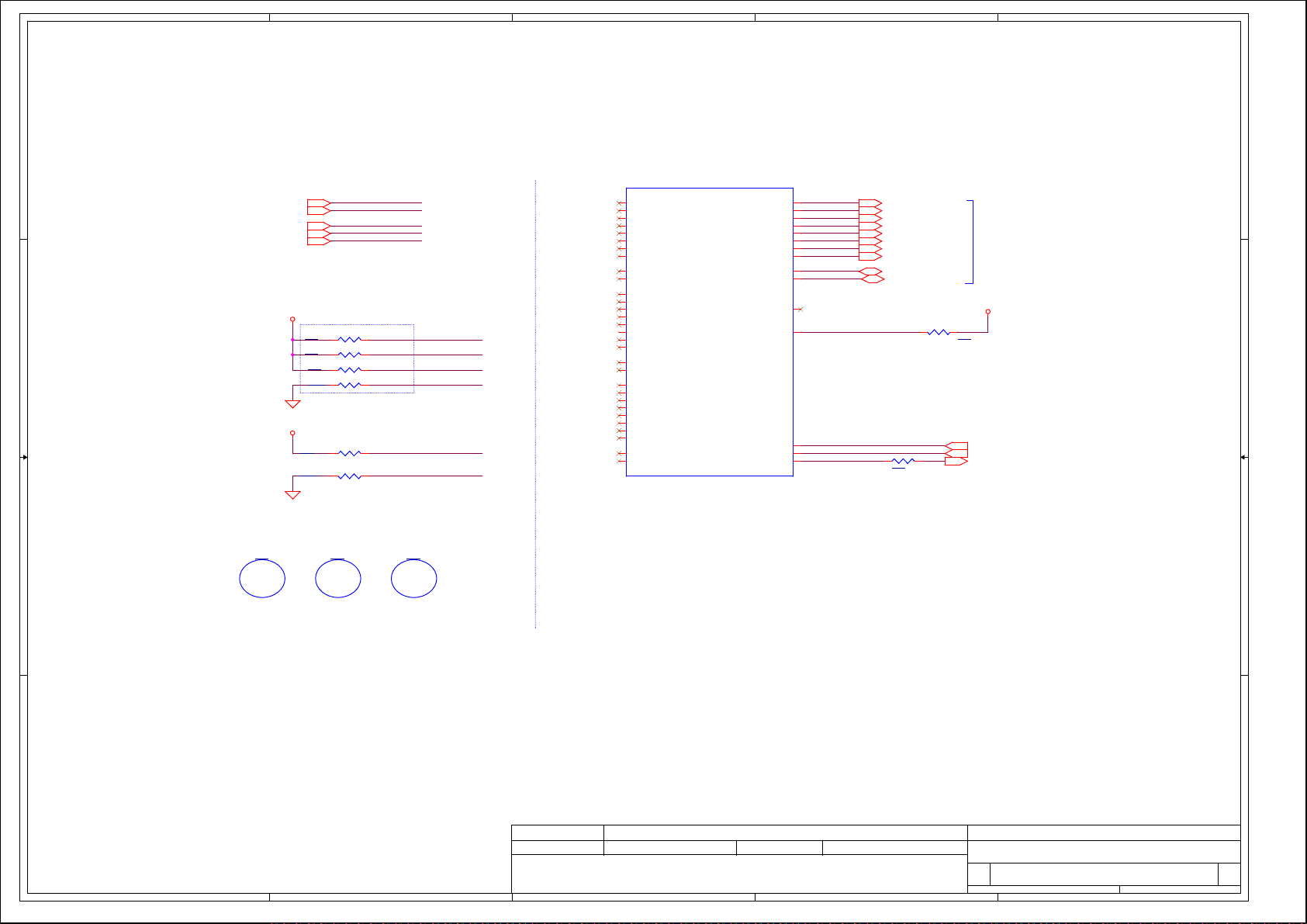

REV = 1

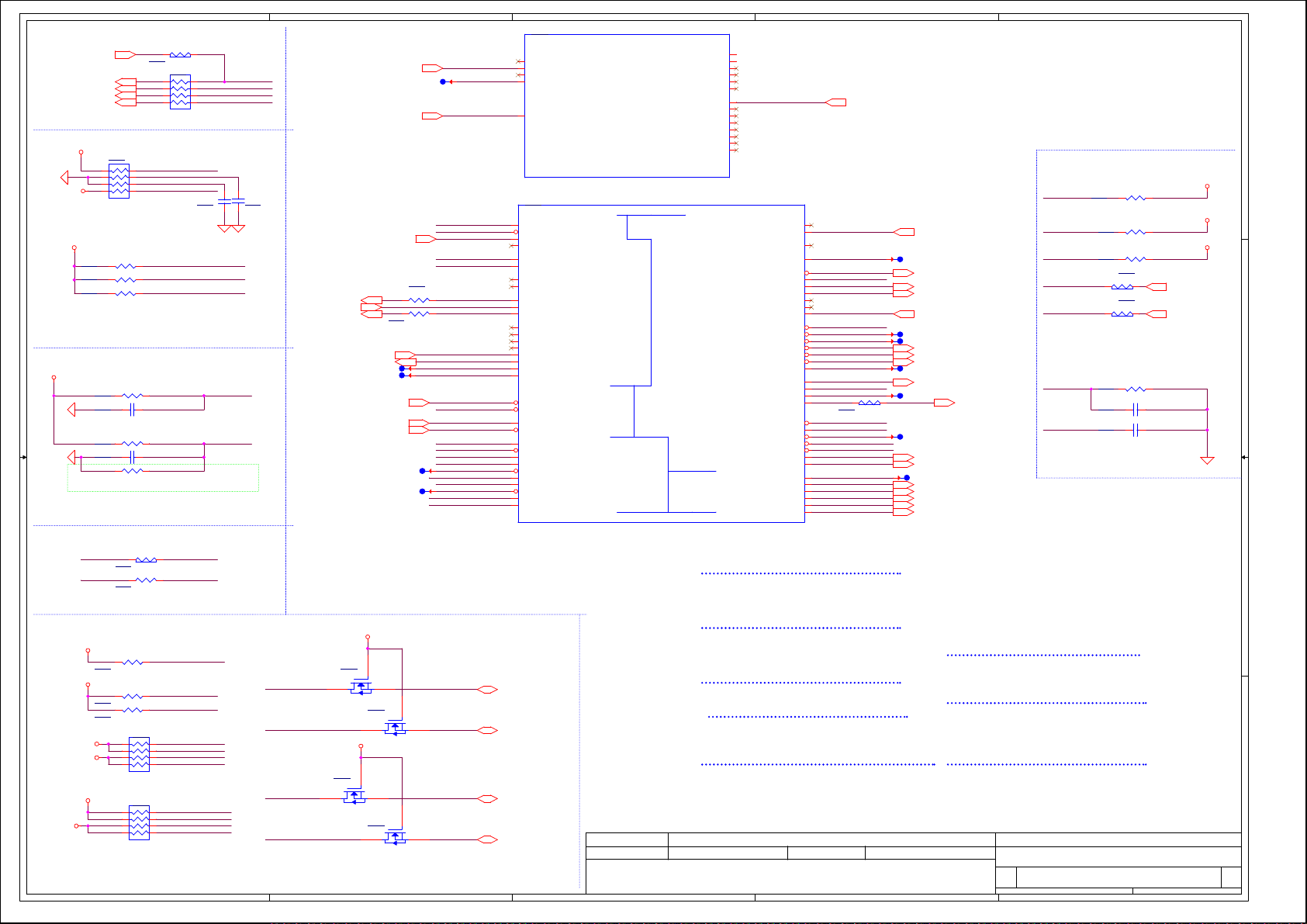

SKYLAKE_H ALO

BGA1 440

4 OF 14

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

D29

E29

F28

E28

B29

A29

B28

C28

C26

B26

A33

EDP_COMP

D37

CAD note:

Trace width=20 mils,Spa cing=25mil,Max length=100mils

G27

G25

CPU_DISPA_SDI

G29

EDP_TXP0 <36>

EDP_TXN0 <36>

EDP_TXP1 <36>

EDP_TXN1 <36>

EDP_TXN2 <36>

EDP_TXP2 <36>

EDP_TXN3 <36>

EDP_TXP3 <36>

EDP_AUXP <36>

EDP_AUXN <36>

RC2

20_0402_5%

<eDP>

+1.0VS_VCCIO

12

RC124.9_0402_1%

CPU_DISPA_BCLK <19 >

12

CPU_DISPA_SDO <19 >

CPU_DISPA_SDI_R <19>

Close to CPU

CPU_XDP_TMS<10,19>

CPU_XDP_TDI<10,19>

CPU_XDP_TDO<10,19>

CPU_XDP_TCK0<10,19>

PCH_JTAG_TCK1<19>

CPU_XDP_TMS

CPU_XDP_TDI

CPU_XDP_TDO

CPU_XDP_TCK0

PCH_JTAG_TCK1

If need debug from usb port. this cmc@ need pop

+1.0VS_VCCSTG

TMS/TDI pin CPU on-die termination

2 2

Place to PCH side

Place to CPU side

3 3

UC1

SR32S 2.5G

SA0000AD850

RC5 51_0402_5%CMC@

RC6 51_0402_5%CMC@

RC7 100_0402_1%CMC@

RC14 51_0402_5%@

+1.0VS_VCCSTG

RC8 100_0402_1%CMC@

RC13 51_0402_5%CMC@

GL82HM175 SR30W

SA0000ADB30

12

12

1 2

12

1 2

12

UH1

CPU_XDP_TMS

CPU_XDP_TDI

CPU_XDP_TDO

PCH_JTAG_TCK1

CPU_XDP_TDO

CPU_XDP_TCK0

UG1

N17E-G1 R1

SA00009PM10

K36

DDI1_TXP[0]

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

J34

DDI1_TXN[1]

H37

DDI1_TXP[2]

H36

DDI1_TXN[2]

J37

DDI1_TXP[3]

J38

DDI1_TXN[3]

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP[0]

H33

DDI2_TXN[0]

F37

DDI2_TXP[1]

G38

DDI2_TXN[1]

F34

DDI2_TXP[2]

F35

DDI2_TXN[2]

E37

DDI2_TXP[3]

E36

DDI2_TXN[3]

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP[0]

D34

DDI3_TXN[0]

B36

DDI3_TXP[1]

B34

DDI3_TXN[1]

F33

DDI3_TXP[2]

E33

DDI3_TXN[2]

C33

DDI3_TXP[3]

B33

DDI3_TXN[3]

A27

DDI3_AUXP

B27

DDI3_AUXN

SKL-H_BGA1440

@

UC1D

4 4

Security Classification

Security Classification

Security Classification

2016/12/15 2017/12/15

2016/12/15 2017/12/15

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2016/12/15 2017/12/15

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal&Electronics,&Inc.

SKL-H(1/9)DDI,EDP

SKL-H(1/9)DDI,EDP

SKL-H(1/9)DDI,EDP

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

E

1.A

1.A

773Friday, March 31, 2017

773Friday, March 31, 2017

773Friday, March 31, 2017

1.A

of

of

of

A

B

C

D

E

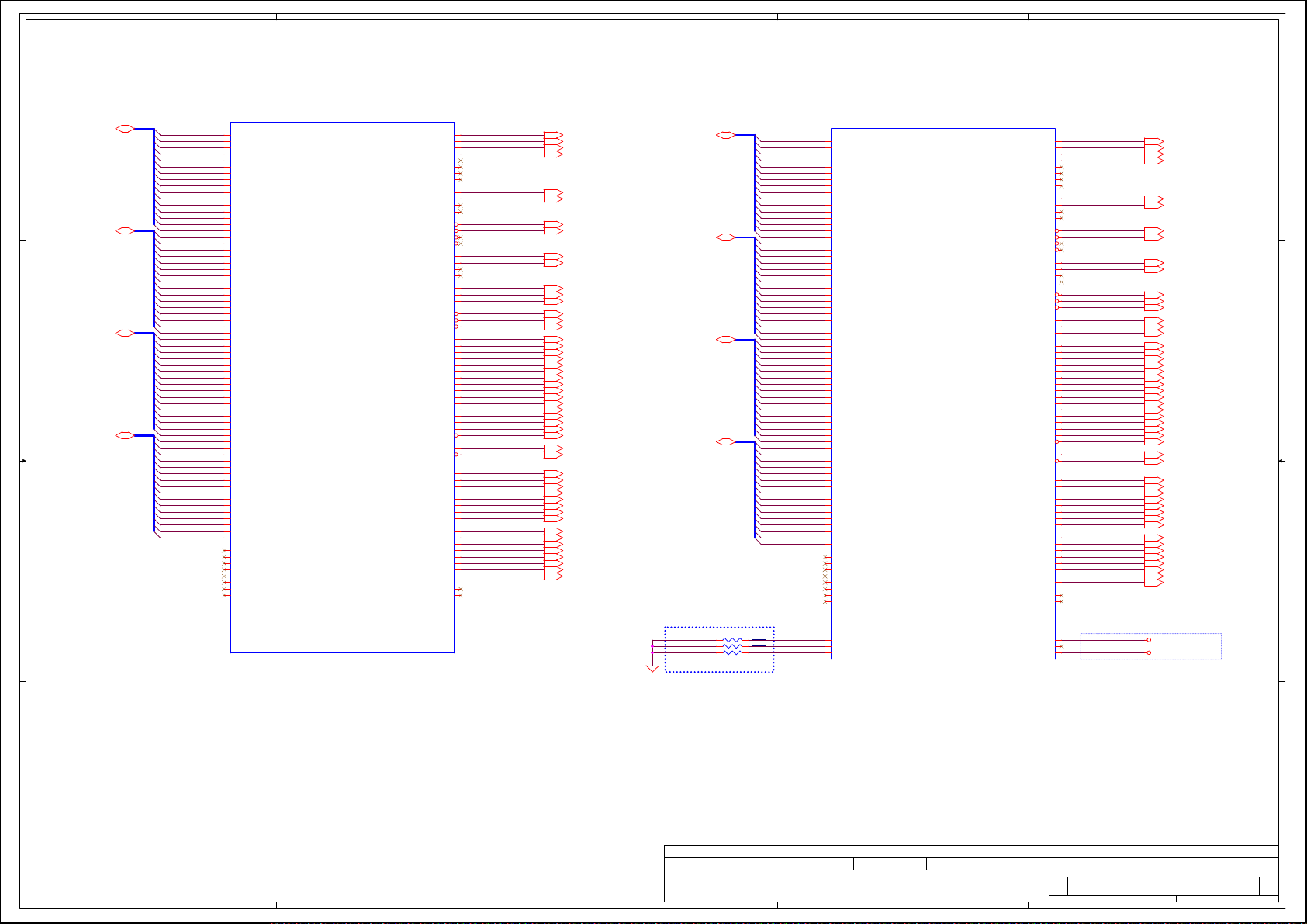

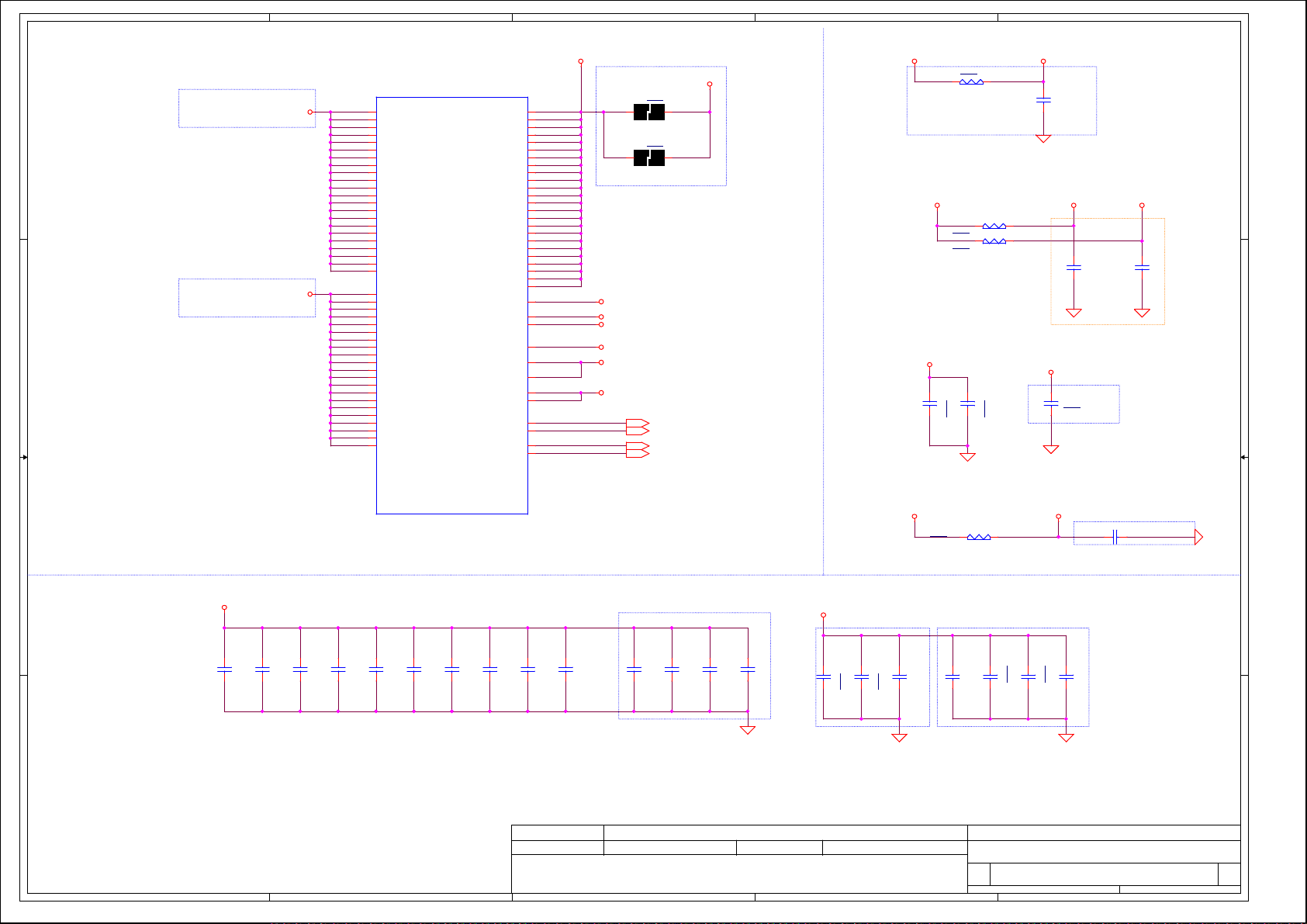

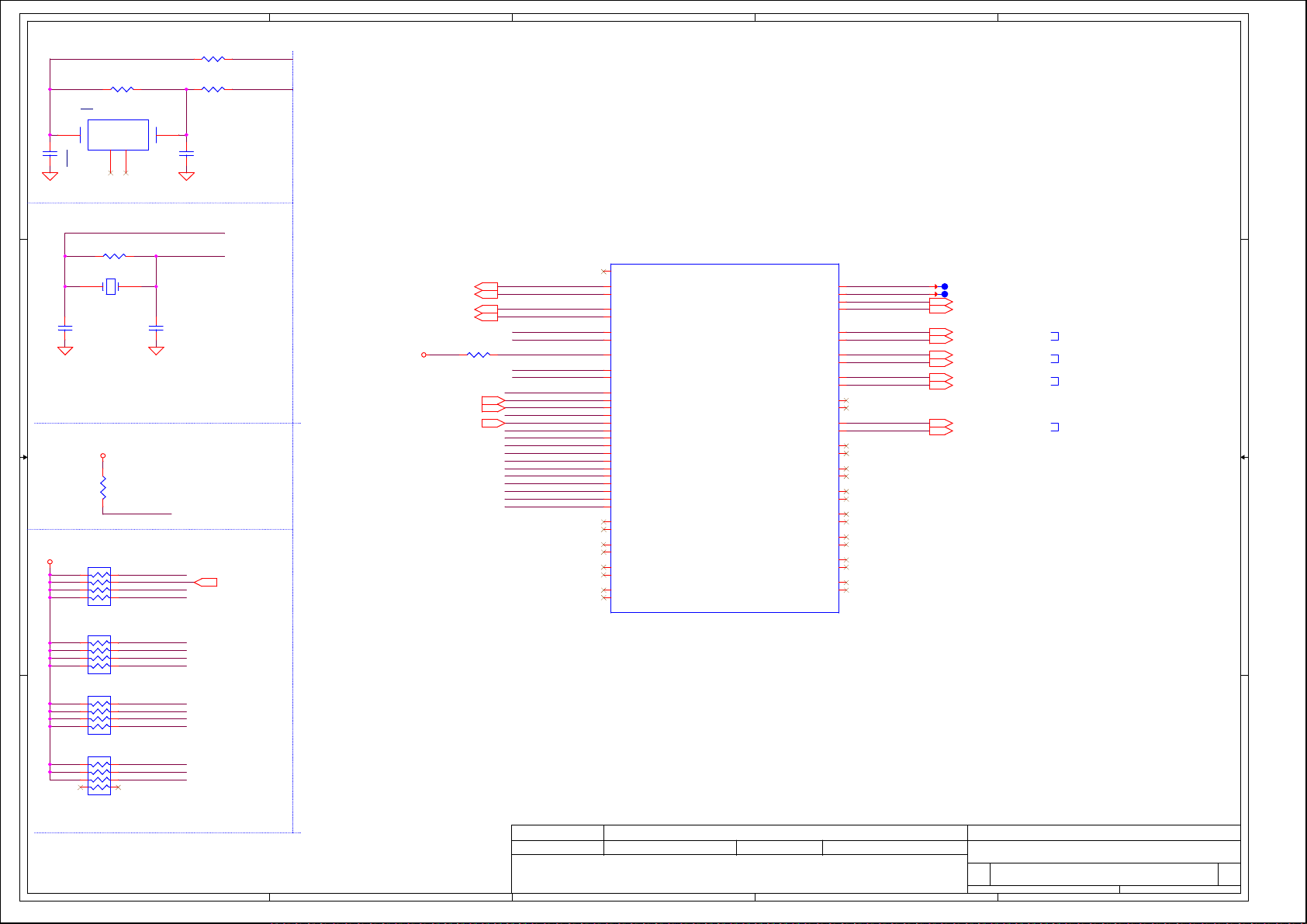

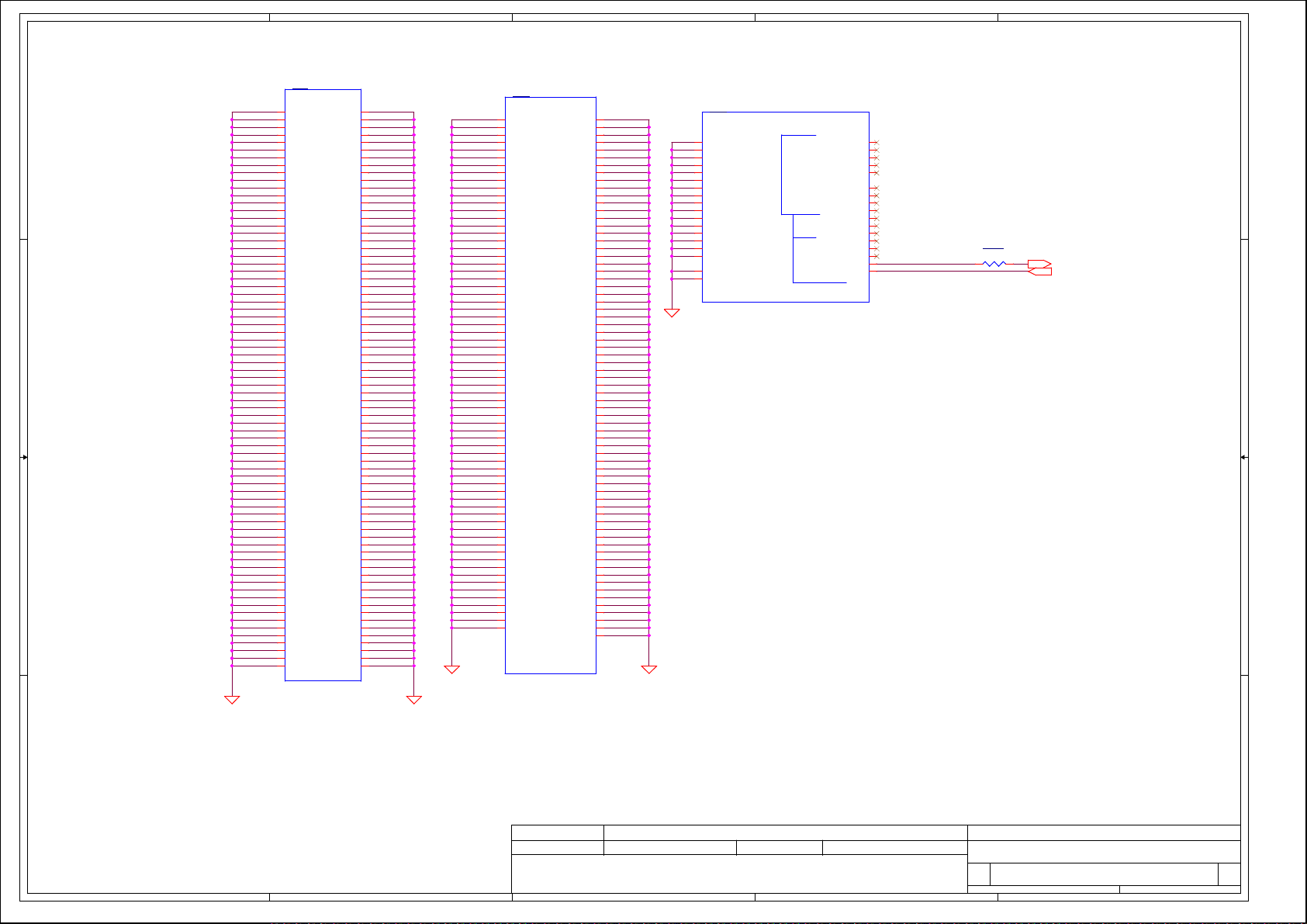

Interleaved Memory

DDR_A_D[0..15]<15>

1 1

DDR_A_D[16..31]<15>

DDR_A_D[32..47]<15>

2 2

DDR_A_D[48..63]<15>

3 3

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10 ]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12 ]

BK5

DDR0_DQ[13 ]

BK1

DDR0_DQ[14 ]

BK2

DDR0_DQ[15 ]

BG4

DDR0_DQ[16] /DDR0_DQ[32]

BG5

DDR0_DQ[17] /DDR0_DQ[33]

BF4

DDR0_DQ[18] /DDR0_DQ[34]

BF5

DDR0_DQ[19] /DDR0_DQ[35]

BG2

DDR0_DQ[20] /DDR0_DQ[36]

BG1

DDR0_DQ[21] /DDR0_DQ[37]

BF1

DDR0_DQ[22] /DDR0_DQ[38]

BF2

DDR0_DQ[23] /DDR0_DQ[39]

BD2

DDR0_DQ[24] /DDR0_DQ[40]

BD1

DDR0_DQ[25] /DDR0_DQ[41]

BC4

DDR0_DQ[26] /DDR0_DQ[42]

BC5

DDR0_DQ[27] /DDR0_DQ[43]

BD5

DDR0_DQ[28] /DDR0_DQ[44]

BD4

DDR0_DQ[29] /DDR0_DQ[45]

BC1

DDR0_DQ[30] /DDR0_DQ[46]

BC2

DDR0_DQ[31] /DDR0_DQ[47]

AB1

DDR0_DQ[32] /DDR1_DQ[0]

AB2

DDR0_DQ[33] /DDR1_DQ[1]

AA4

DDR0_DQ[34] /DDR1_DQ[2]

AA5

DDR0_DQ[35] /DDR1_DQ[3]

AB5

DDR0_DQ[36] /DDR1_DQ[4]

AB4

DDR0_DQ[37] /DDR1_DQ[5]

AA2

DDR0_DQ[38] /DDR1_DQ[6]

AA1

DDR0_DQ[39] /DDR1_DQ[7]

V5

DDR0_DQ[40] /DDR1_DQ[8]

V2

DDR0_DQ[41] /DDR1_DQ[9]

U1

DDR0_DQ[42] /DDR1_DQ[10]

U2

DDR0_DQ[43 ]/DDR1_DQ[11]

V1

DDR0_DQ[44] /DDR1_DQ[12]

V4

DDR0_DQ[45] /DDR1_DQ[13]

U5

DDR0_DQ[46] /DDR1_DQ[14]

U4

DDR0_DQ[47] /DDR1_DQ[15]

R2

DDR0_DQ[48] /DDR1_DQ[32]

P5

DDR0_DQ[49] /DDR1_DQ[33]

R4

DDR0_DQ[50] /DDR1_DQ[34]

P4

DDR0_DQ[51] /DDR1_DQ[35]

R5

DDR0_DQ[52] /DDR1_DQ[36]

P2

DDR0_DQ[53] /DDR1_DQ[37]

R1

DDR0_DQ[54] /DDR1_DQ[38]

P1

DDR0_DQ[55] /DDR1_DQ[39]

M4

DDR0_DQ[56] /DDR1_DQ[40]

M1

DDR0_DQ[57] /DDR1_DQ[41]

L4

DDR0_DQ[58] /DDR1_DQ[42]

L2

DDR0_DQ[59] /DDR1_DQ[43]

M5

DDR0_DQ[60] /DDR1_DQ[44]

M2

DDR0_DQ[61] /DDR1_DQ[45]

L5

DDR0_DQ[62] /DDR1_DQ[46]

L1

DDR0_DQ[63] /DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

SKL-H_BGA1440

REV = 1

@

SKYLAKE_HAL O

BGA1440

DDR0_BA[0]/D DR0_CAB[4]/DDR0 _BA[0]

DDR0_BA[1]/D DR0_CAB[6]/DDR0 _BA[1]

DDR0_BA[2]/D DR0_CAA[5]/DDR0 _BG[0]

DDR0_RAS#/DD R0_CAB[3]/DDR0 _MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DD R0_CAB[1]/DDR0 _MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/ DDR0_CAA[8]/DDR0 _ACT#

DDR0_DQSN[2]/D DR0_DQSN[4]

DDR0_DQSN[3]/D DR0_DQSN[5]

DDR0_DQSP[4]/D DR1_DQSP[0]

DDR0_DQSP[5]/D DR1_DQSP[1]

DDR0_DQSP[6]/D DR1_DQSP[4]

DDR0_DQSP[7]/D DR1_DQSP[5]

DDR0_DQSP[2]/D DR0_DQSP[4]

DDR0_DQSP[3]/D DR0_DQSP[5]

DDR0_DQSN[4]/D DR1_DQSN[0]

DDR0_DQSN[5]/D DR1_DQSN[1]

DDR0_DQSN[6]/D DR1_DQSN[4]

DDR0_DQSN[7]/D DR1_DQSN[5]

1 OF 14

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

?

AG1

AG2

AK1

AK2

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AB3

V3

R3

M3

BP5

BK3

BF3

BC3

AA3

U3

P3

L3

AY3

BA3

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDR_A_MA16

DDR_A_MA14

DDR_A_MA15

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_BG1

DDR_A_ACT#

DDR_A_PARITY

DDR_A_ALERT#

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_CLK0 <15>

DDR_A_CLK#0 <15>

DDR_A_CLK#1 <15>

DDR_A_CLK1 <15>

DDR_A_CKE0 <15>

DDR_A_CKE1 <15>

DDR_A_CS#0 <15>

DDR_A_CS#1 <15>

DDR_A_ODT0 <15>

DDR_A_ODT1 <15>

DDR_A_BA0 <15>

DDR_A_BA1 <15>

DDR_A_BG0 < 15>

DDR_A_MA16 <15>

DDR_A_MA14 <15>

DDR_A_MA15 <15>

DDR_A_MA0 <15>

DDR_A_MA1 <15>

DDR_A_MA2 <15>

DDR_A_MA3 <15>

DDR_A_MA4 <15>

DDR_A_MA5 <15>

DDR_A_MA6 <15>

DDR_A_MA7 <15>

DDR_A_MA8 <15>

DDR_A_MA9 <15>

DDR_A_MA10 <15>

DDR_A_MA11 <15>

DDR_A_MA12 <15>

DDR_A_MA13 <15>

DDR_A_BG1 < 15>

DDR_A_ACT# <15>

DDR_A_PARITY <15>

DDR_A_ALERT# <15>

DDR_A_DQS#0 <15>

DDR_A_DQS#1 <15>

DDR_A_DQS#2 <15>

DDR_A_DQS#3 <15>

DDR_A_DQS4 <15>

DDR_A_DQS5 <15>

DDR_A_DQS6 <15>

DDR_A_DQS7 <15>

DDR_A_DQS0 <15>

DDR_A_DQS1 <15>

DDR_A_DQS2 <15>

DDR_A_DQS3 <15>

DDR_A_DQS#4 <15>

DDR_A_DQS#5 <15>

DDR_A_DQS#6 <15>

DDR_A_DQS#7 <15>

DDR_B_D[0..15]<16>

DDR_B_D[16..31]<16>

DDR_B_D[32..47]<16>

DDR_B_D[48..63]<16>

close to CPU

DDR CHANNEL B

SKYLAKE_HAL O

BGA1440

DDR1_RAS#/DD R1_CAB[3]/DDR1 _MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DD R1_CAB[1]/DDR1 _MA[15]

DDR1_BA[0]/D DR1_CAB[4]/DDR1 _BA[0]

DDR1_BA[1]/D DR1_CAB[6]/DDR1 _BA[1]

DDR1_BA[2]/D DR1_CAA[5]/DDR1 _BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/ DDR1_CAA[8]/DDR1 _ACT#

DDR1_DQSN[0]/D DR0_DQSN[2]

DDR1_DQSN[1]/D DR0_DQSN[3]

DDR1_DQSN[2]/D DR0_DQSN[6]

DDR1_DQSN[3]/D DR0_DQSN[7]

DDR1_DQSN[4]/D DR1_DQSN[2]

DDR1_DQSN[5]/D DR1_DQSN[3]

DDR1_DQSP[0]/D DR0_DQSP[2]

DDR1_DQSP[1]/D DR0_DQSP[3]

DDR1_DQSP[2]/D DR0_DQSP[6]

DDR1_DQSP[3]/D DR0_DQSP[7]

DDR1_DQSP[4]/D DR1_DQSP[2]

DDR1_DQSP[5]/D DR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA16

DDR_B_MA14

DDR_B_MA15

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_PARITY

DDR_B_ALERT#

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

+0.6V_VREFCA

+0.6V_B_VREFDQ

DDR_B_CLK0 <16>

DDR_B_CLK#0 <16>

DDR_B_CLK#1 <16>

DDR_B_CLK1 <16>

DDR_B_CKE0 <16>

DDR_B_CKE1 <16>

DDR_B_CS#0 <16>

DDR_B_CS#1 <16>

DDR_B_ODT0 <16>

DDR_B_ODT1 <16>

DDR_B_MA16 <16>

DDR_B_MA14 <16>

DDR_B_MA15 <16>

DDR_B_BA0 <16>

DDR_B_BA1 <16>

DDR_B_BG0 <16>

DDR_B_MA0 <16>

DDR_B_MA1 <16>

DDR_B_MA2 <16>

DDR_B_MA3 <16>

DDR_B_MA4 <16>

DDR_B_MA5 <16>

DDR_B_MA6 <16>

DDR_B_MA7 <16>

DDR_B_MA8 <16>

DDR_B_MA9 <16>

DDR_B_MA10 <16>

DDR_B_MA11 <16>

DDR_B_MA12 <16>

DDR_B_MA13 <16>

DDR_B_BG1 <16>

DDR_B_ACT# <16>

DDR_B_PARITY <16>

DDR_B_ALERT# <16>

DDR_B_DQS#0 <16>

DDR_B_DQS#1 <16>

DDR_B_DQS#2 <16>

DDR_B_DQS#3 <16>

DDR_B_DQS#4 <16>

DDR_B_DQS#5 <16>

DDR_B_DQS#6 <16>

DDR_B_DQS#7 <16>

DDR_B_DQS0 <16>

DDR_B_DQS1 <16>

DDR_B_DQS2 <16>

DDR_B_DQS3 <16>

DDR_B_DQS4 <16>

DDR_B_DQS5 <16>

DDR_B_DQS6 <16>

DDR_B_DQS7 <16>

+0.6V_VREFCA

+0.6V_B_VREFDQ

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

SM_RCOMP0

RC17121_0402_1% 12

SM_RCOMP1

12

RC1875_0402_1%

SM_RCOMP2

RC19100_0402_1% 12

UC1B

BT11

DDR1_DQ[0]/ DDR0_DQ[16]

BR11

DDR1_DQ[1]/ DDR0_DQ[17]

BT8

DDR1_DQ[2]/ DDR0_DQ[18]

BR8

DDR1_DQ[3]/ DDR0_DQ[19]

BP11

DDR1_DQ[4]/ DDR0_DQ[20]

BN11

DDR1_DQ[5]/ DDR0_DQ[21]

BP8

DDR1_DQ[6]/ DDR0_DQ[22]

BN8

DDR1_DQ[7]/ DDR0_DQ[23]

BL12

DDR1_DQ[8]/ DDR0_DQ[24]

BL11

DDR1_DQ[9]/ DDR0_DQ[25]

BL8

DDR1_DQ[10] /DDR0_DQ[26]

BJ8

DDR1_DQ[11]/ DDR0_DQ[27]

BJ11

DDR1_DQ[12] /DDR0_DQ[28]

BJ10

DDR1_DQ[13] /DDR0_DQ[29]

BL7

DDR1_DQ[14] /DDR0_DQ[30]

BJ7

DDR1_DQ[15] /DDR0_DQ[31]

BG11

DDR1_DQ[16] /DDR0_DQ[48]

BG10

DDR1_DQ[17] /DDR0_DQ[49]

BG8

DDR1_DQ[18] /DDR0_DQ[50]

BF8

DDR1_DQ[19] /DDR0_DQ[51]

BF11

DDR1_DQ[20] /DDR0_DQ[52]

BF10

DDR1_DQ[21] /DDR0_DQ[53]

BG7

DDR1_DQ[22] /DDR0_DQ[54]

BF7

DDR1_DQ[23] /DDR0_DQ[55]

BB11

DDR1_DQ[24] /DDR0_DQ[56]

BC11

DDR1_DQ[25] /DDR0_DQ[57]

BB8

DDR1_DQ[26] /DDR0_DQ[58]

BC8

DDR1_DQ[27] /DDR0_DQ[59]

BC10

DDR1_DQ[28] /DDR0_DQ[60]

BB10

DDR1_DQ[29] /DDR0_DQ[61]

BC7

DDR1_DQ[30] /DDR0_DQ[62]

BB7

DDR1_DQ[31] /DDR0_DQ[63]

AA11

DDR1_DQ[32] /DDR1_DQ[16]

AA10

DDR1_DQ[33] /DDR1_DQ[17]

AC11

DDR1_DQ[34] /DDR1_DQ[18]

AC10

DDR1_DQ[35] /DDR1_DQ[19]

AA7

DDR1_DQ[36] /DDR1_DQ[20]

AA8

DDR1_DQ[37] /DDR1_DQ[21]

AC8

DDR1_DQ[38] /DDR1_DQ[22]

AC7

DDR1_DQ[39] /DDR1_DQ[23]

W8

DDR1_DQ[40] /DDR1_DQ[24]

W7

DDR1_DQ[41] /DDR1_DQ[25]

V10

DDR1_DQ[42] /DDR1_DQ[26]

V11

DDR1_DQ[43] /DDR1_DQ[27]

W11

DDR1_DQ[44] /DDR1_DQ[28]

W10

DDR1_DQ[45] /DDR1_DQ[29]

V7

DDR1_DQ[46] /DDR1_DQ[30]

V8

DDR1_DQ[47] /DDR1_DQ[31]

R11

DDR1_DQ[48 ]

P11

DDR1_DQ[49 ]

P7

DDR1_DQ[50 ]

R8

DDR1_DQ[51 ]

R10

DDR1_DQ[52 ]

P10

DDR1_DQ[53 ]

R7

DDR1_DQ[54 ]

P8

DDR1_DQ[55 ]

L11

DDR1_DQ[56 ]

M11

DDR1_DQ[57 ]

L7

DDR1_DQ[58 ]

M8

DDR1_DQ[59 ]

L10

DDR1_DQ[60 ]

M10

DDR1_DQ[61 ]

M7

DDR1_DQ[62 ]

L8

DDR1_DQ[63 ]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL-H_BGA1440

REV = 1 ?

@

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET O F ENGINEERING DRAWING IS THE PRO PRIETARY PRO PERTY O F COMPAL ELECTRO NICS, IN C. AND C ONTAINS CONF IDENTIAL

THIS SHEET O F ENGINEERING DRAWING IS THE PRO PRIETARY PRO PERTY O F COMPAL ELECTRO NICS, IN C. AND C ONTAINS CONF IDENTIAL

THIS SHEET O F ENGINEERING DRAWING IS THE PRO PRIETARY PRO PERTY O F COMPAL ELECTRO NICS, IN C. AND C ONTAINS CONF IDENTIAL

AND TRADE SECRET INFO RMATION. TH IS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

AND TRADE SECRET INFO RMATION. TH IS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

AND TRADE SECRET INFO RMATION. TH IS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS , INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS , INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS , INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISC LOSED TO AN Y THIRD PARTY W ITHOUT PRIOR WRITTEN CON SENT OF C OMPAL ELECTRO NICS, INC .

MAY BE USE D BY OR DISC LOSED TO AN Y THIRD PARTY W ITHOUT PRIOR WRITTEN CON SENT OF C OMPAL ELECTRO NICS, INC .

A

B

MAY BE USE D BY OR DISC LOSED TO AN Y THIRD PARTY W ITHOUT PRIOR WRITTEN CON SENT OF C OMPAL ELECTRO NICS, INC .

C

2016/12/15 2017/12/15

2016/12/15 2017/12/15

2016/12/15 2017/12/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Tit le

Tit le

Tit le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

SKL-H(2/9)DDRIII

SKL-H(2/9)DDRIII

SKL-H(2/9)DDRIII

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

Friday, March 31 , 2 017

Friday, March 31 , 2 017

Friday, March 31 , 2 017

1.A

1.A

1.A

73

73

73

8

8

8

of

of

E

of

A

B

C

D

E

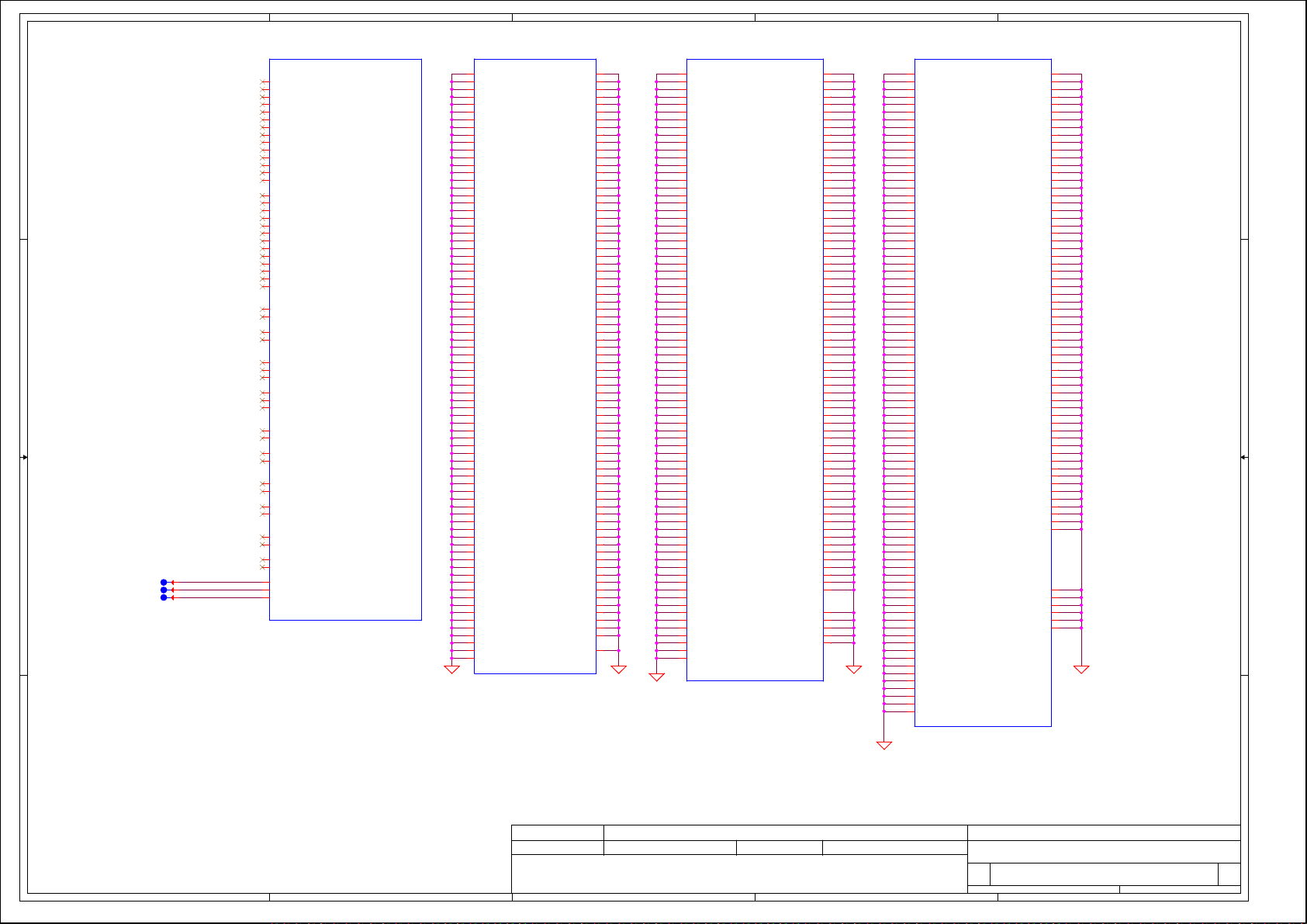

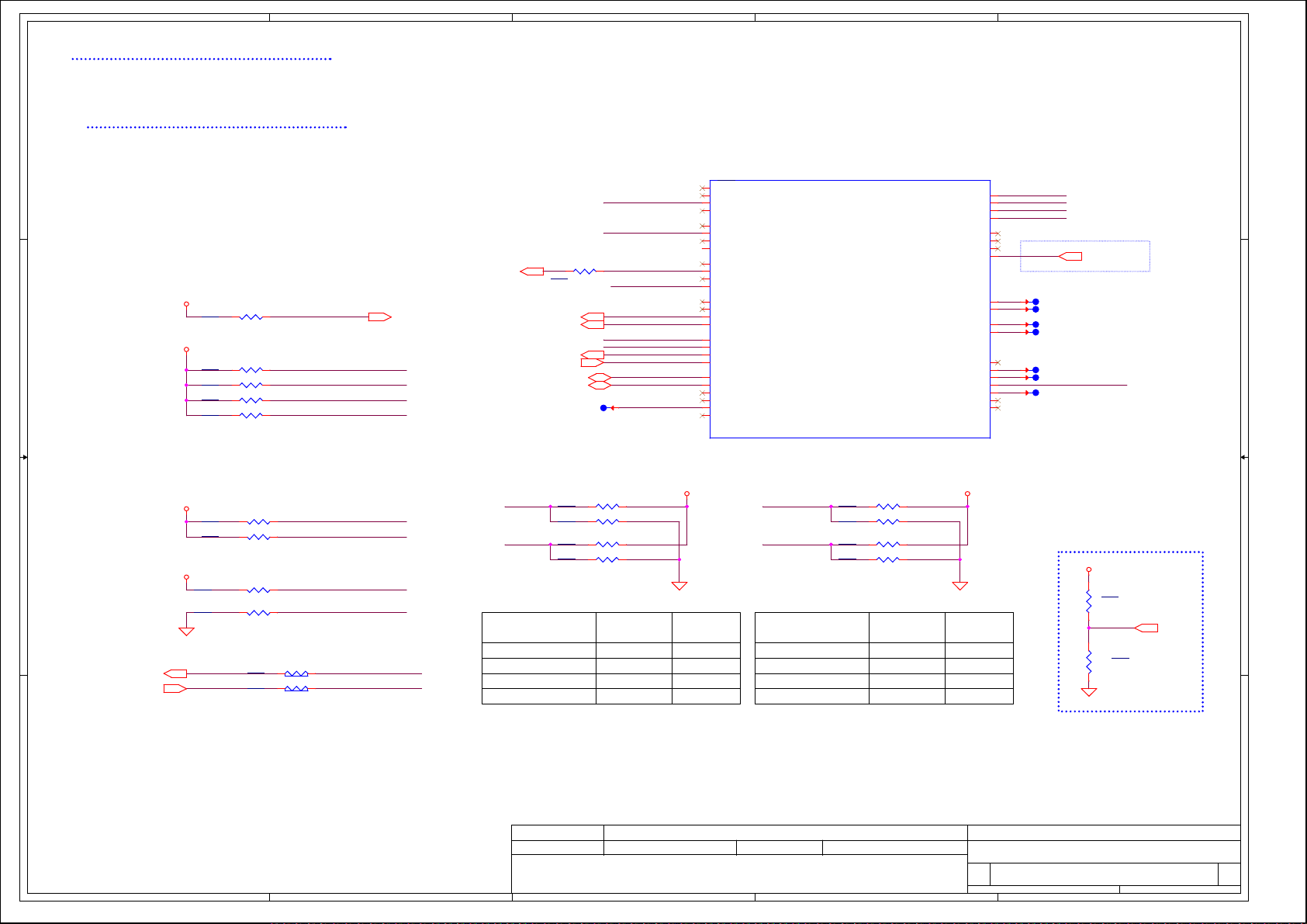

1 1

1 2

PEG_GTX_HRX_P15<24>

PEG_GTX_HRX_N15<24>

PEG_GTX_HRX_P14<24>

PEG_GTX_HRX_N14<24>

PEG_GTX_HRX_P13<24>

PEG_GTX_HRX_N13<24>

PEG_GTX_HRX_P12<24>

PEG_GTX_HRX_N12<24>

PEG_GTX_HRX_P11<24>

PEG_GTX_HRX_N11<24>

PEG_GTX_HRX_P10<24>

PEG_GTX_HRX_N10<24>

PEG_GTX_HRX_P9<24>

PEG_GTX_HRX_N9<24>

PEG_GTX_HRX_P8<24>

2 2

3 3

PEG_GTX_HRX_N8<24>

PEG_GTX_HRX_P7<24>

PEG_GTX_HRX_N7<24>

PEG_GTX_HRX_P6<24>

PEG_GTX_HRX_N6<24>

PEG_GTX_HRX_P5<24>

PEG_GTX_HRX_N5<24>

PEG_GTX_HRX_P4<24>

PEG_GTX_HRX_N4<24>

PEG_GTX_HRX_P3<24>

PEG_GTX_HRX_N3<24>

PEG_GTX_HRX_P2<24>

PEG_GTX_HRX_N2<24>

PEG_GTX_HRX_P1<24>

PEG_GTX_HRX_N1<24>

PEG_GTX_HRX_P0<24>

PEG_GTX_HRX_N0<24>

CC6 0.22U_0201_6.3V6KVGA@

1 2

CC8 0.22U_0201_6.3V6KVGA@

1 2

CC10 0.22U_0201_6.3V6KVGA@

1 2

CC12 0.22U_0201_6.3V6KVGA@

1 2

CC14 0.22U_0201_6.3V6KVGA@

1 2

CC15 0.22U_0201_6.3V6KVGA@

1 2

CC3 0.22U_0201_6.3V6KVGA@

1 2

CC17 0.22U_0201_6.3V6KVGA@

1 2

CC19 0.22U_0201_6.3V6KVGA@

1 2

CC21 0.22U_0201_6.3V6KVGA@

1 2

CC5 0.22U_0201_6.3V6KVGA@

1 2

CC23 0.22U_0201_6.3V6KVGA@

1 2

CC25 0.22U_0201_6.3V6KVGA@

1 2

CC27 0.22U_0201_6.3V6KVGA@

1 2

CC29 0.22U_0201_6.3V6KVGA@

1 2

CC31 0.22U_0201_6.3V6KVGA@

1 2

CC33 0.22U_0201_6.3V6KVGA@

1 2

CC35 0.22U_0201_6.3V6KVGA@

1 2

CC37 0.22U_0201_6.3V6KVGA@

1 2

CC39 0.22U_0201_6.3V6KVGA@

1 2

CC41 0.22U_0201_6.3V6KVGA@

1 2

CC43 0.22U_0201_6.3V6KVGA@

1 2

CC45 0.22U_0201_6.3V6KVGA@

1 2

CC47 0.22U_0201_6.3V6KVGA@

1 2

CC49 0.22U_0201_6.3V6KVGA@

1 2

CC51 0.22U_0201_6.3V6KVGA@

1 2

CC53 0.22U_0201_6.3V6KVGA@

1 2

CC55 0.22U_0201_6.3V6KVGA@

1 2

CC57 0.22U_0201_6.3V6KVGA@

1 2

CC59 0.22U_0201_6.3V6KVGA@

1 2

CC61 0.22U_0201_6.3V6KVGA@

1 2

CC63 0.22U_0201_6.3V6KVGA@

+1.0VS_VCCIO

CAD n ote:

Trace width=12 mils,Spacing=15mil,Max length=400mils

DMI_CRX_PTX_P0<17>

DMI_CRX_PTX_N0<17>

DMI_CRX_PTX_P1<17>

DMI_CRX_PTX_N1<17>

DMI_CRX_PTX_P2<17>

DMI_CRX_PTX_N2<17>

DMI_CRX_PTX_P3<17>

DMI_CRX_PTX_N3<17>

1 2

RC20 24.9_0402_1%

PEG_GTX_C_HRX_P15

PEG_GTX_C_HRX_N15

PEG_GTX_C_HRX_P14

PEG_GTX_C_HRX_N14

PEG_GTX_C_HRX_P13

PEG_GTX_C_HRX_N13

PEG_GTX_C_HRX_P12

PEG_GTX_C_HRX_N12

PEG_GTX_C_HRX_P11

PEG_GTX_C_HRX_N11

PEG_GTX_C_HRX_P10

PEG_GTX_C_HRX_N10

PEG_GTX_C_HRX_P9

PEG_GTX_C_HRX_N9

PEG_GTX_C_HRX_P8

PEG_GTX_C_HRX_N8

PEG_GTX_C_HRX_P7

PEG_GTX_C_HRX_N7

PEG_GTX_C_HRX_P6

PEG_GTX_C_HRX_N6

PEG_GTX_C_HRX_P5

PEG_GTX_C_HRX_N5

PEG_GTX_C_HRX_P4

PEG_GTX_C_HRX_N4

PEG_GTX_C_HRX_P3

PEG_GTX_C_HRX_N3

PEG_GTX_C_HRX_P2

PEG_GTX_C_HRX_N2

PEG_GTX_C_HRX_P1

PEG_GTX_C_HRX_N1

PEG_GTX_C_HRX_P0

PEG_GTX_C_HRX_N0

PEG_RCOMP

DMI_CRX_PTX_P0

DMI_CRX_PTX_N0

DMI_CRX_PTX_P1

DMI_CRX_PTX_N1

DMI_CRX_PTX_P2

DMI_CRX_PTX_N2

DMI_CRX_PTX_P3

DMI_CRX_PTX_N3

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

UC1C

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

SKL-H_BGA1440

REV = 1

@

SKYLAKE_H ALO

BGA1 440

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

?

PEG_HTX_GRX_P15

PEG_HTX_GRX_N15

PEG_HTX_GRX_P14

PEG_HTX_GRX_N14

PEG_HTX_GRX_P13

PEG_HTX_GRX_N13

PEG_HTX_GRX_P12

PEG_HTX_GRX_N12

PEG_HTX_GRX_P11

PEG_HTX_GRX_N11

PEG_HTX_GRX_P10

PEG_HTX_GRX_N10

PEG_HTX_GRX_P9

PEG_HTX_GRX_N9

PEG_HTX_GRX_P8

PEG_HTX_GRX_N8

PEG_HTX_GRX_P7

PEG_HTX_GRX_N7

PEG_HTX_GRX_P6

PEG_HTX_GRX_N6

PEG_HTX_GRX_P5

PEG_HTX_GRX_N5

PEG_HTX_GRX_P4

PEG_HTX_GRX_N4

PEG_HTX_GRX_P3

PEG_HTX_GRX_N3

PEG_HTX_GRX_P2

PEG_HTX_GRX_N2

PEG_HTX_GRX_P1

PEG_HTX_GRX_N1

PEG_HTX_GRX_P0

PEG_HTX_GRX_N0

DMI_CTX_PRX_P0

DMI_CTX_PRX_N0

DMI_CTX_PRX_P1

DMI_CTX_PRX_N1

DMI_CTX_PRX_P2

DMI_CTX_PRX_N2

DMI_CTX_PRX_P3

DMI_CTX_PRX_N3

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

DMI_CTX_PRX_P0 <17>

DMI_CTX_PRX_N0 <17>

DMI_CTX_PRX_P1 <17>

DMI_CTX_PRX_N1 <17>

DMI_CTX_PRX_P2 <17>

DMI_CTX_PRX_N2 <17>

DMI_CTX_PRX_P3 <17>

DMI_CTX_PRX_N3 <17>

CC70.22U_0201_6.3V6K VGA@

CC90.22U_0201_6.3V6K VGA@

CC110.22U_0201_6.3V6K VGA@

CC130.22U_0201_6.3V6K VGA@

CC10.22U_0201_6.3V6K VGA@

CC20.22U_0201_6.3V6K VGA@

CC160.22U_0201_6.3V6K VGA@

CC180.22U_0201_6.3V6K VGA@

CC200.22U_0201_6.3V6K VGA@

CC40.22U_0201_6.3V6K VGA@

CC220.22U_0201_6.3V6K VGA@

CC240.22U_0201_6.3V6K VGA@

CC260.22U_0201_6.3V6K VGA@

CC280.22U_0201_6.3V6K VGA@

CC300.22U_0201_6.3V6K VGA@

CC320.22U_0201_6.3V6K VGA@

CC340.22U_0201_6.3V6K VGA@

CC360.22U_0201_6.3V6K VGA@

CC380.22U_0201_6.3V6K VGA@

CC400.22U_0201_6.3V6K VGA@

CC420.22U_0201_6.3V6K VGA@

CC440.22U_0201_6.3V6K VGA@

CC460.22U_0201_6.3V6K VGA@

CC480.22U_0201_6.3V6K VGA@

CC500.22U_0201_6.3V6K VGA@

CC520.22U_0201_6.3V6K VGA@

CC540.22U_0201_6.3V6K VGA@

CC560.22U_0201_6.3V6K VGA@

CC580.22U_0201_6.3V6K VGA@

CC600.22U_0201_6.3V6K VGA@

CC620.22U_0201_6.3V6K VGA@

CC640.22U_0201_6.3V6K VGA@

PEG_HTX_C_GRX_P15 <24>

PEG_HTX_C_GRX_N15 <24>

PEG_HTX_C_GRX_P14 <24>

PEG_HTX_C_GRX_N14 <24>

PEG_HTX_C_GRX_P13 <24>

PEG_HTX_C_GRX_N13 <24>

PEG_HTX_C_GRX_P12 <24>

PEG_HTX_C_GRX_N12 <24>

PEG_HTX_C_GRX_P11 <24>

PEG_HTX_C_GRX_N11 <24>

PEG_HTX_C_GRX_P10 <24>

PEG_HTX_C_GRX_N10 <24>

PEG_HTX_C_GRX_P9 <24 >

PEG_HTX_C_GRX_N9 <24>

PEG_HTX_C_GRX_P8 <24 >

PEG_HTX_C_GRX_N8 <24>

PEG_HTX_C_GRX_P7 <24 >

PEG_HTX_C_GRX_N7 <24>

PEG_HTX_C_GRX_P6 <24 >

PEG_HTX_C_GRX_N6 <24>

PEG_HTX_C_GRX_P5 <24 >

PEG_HTX_C_GRX_N5 <24>

PEG_HTX_C_GRX_P4 <24 >

PEG_HTX_C_GRX_N4 <24>

PEG_HTX_C_GRX_P3 <24 >

PEG_HTX_C_GRX_N3 <24>

PEG_HTX_C_GRX_P2 <24 >

PEG_HTX_C_GRX_N2 <24>

PEG_HTX_C_GRX_P1 <24 >

PEG_HTX_C_GRX_N1 <24>

PEG_HTX_C_GRX_P0 <24 >

PEG_HTX_C_GRX_N0 <24>

4 4

Security Classification

Security Classification

Security Classification

2016/12/15 2017/12/15

2016/12/15 2017/12/15

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2016/12/15 2017/12/15

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Title

Title

Title

SKL-H(3/9) PEG,DMI

SKL-H(3/9) PEG,DMI

SKL-H(3/9) PEG,DMI

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

Date: Sheet

Date: Sheet

D

Date: Sheet

973Friday, March 31, 2017

973Friday, March 31, 2017

973Friday, March 31, 2017

E

1.A

1.A

1.A

of

of

of

A

B

C

D

E

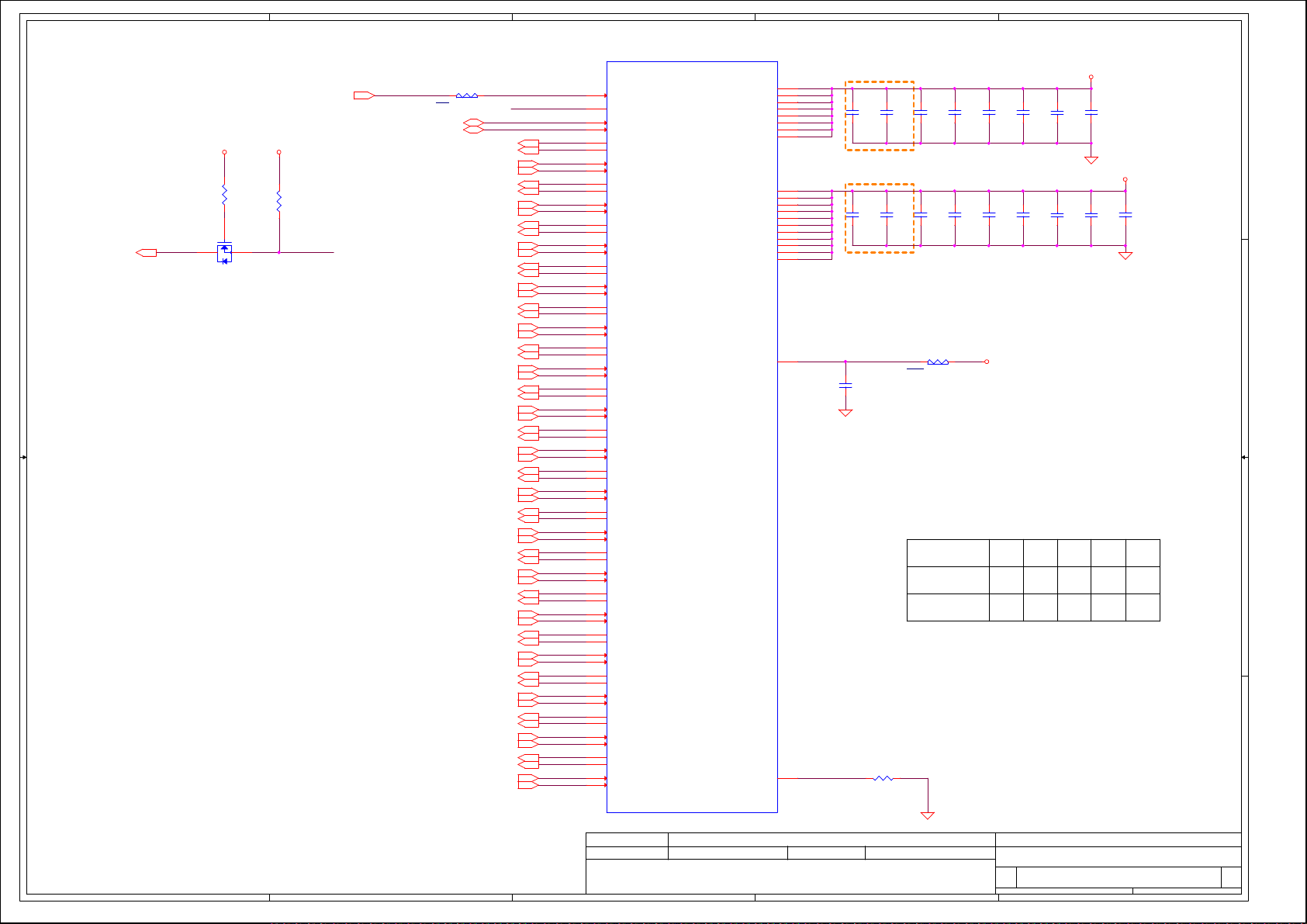

SVID Alert / Data

1 1

Place the PU resistors close to CPU

1 2

+1.0V_VCCST

+1.0V_VCCST

2 2

3 3

RC34 56_0402_5%

CPU_SVID_ALERT#

CPU_SVID_DAT

1 2

RC36 220_0402_5%

1 2

RC38 100_0402_1%

From EC(open-drain)

RC31

1K_0402_5%

H_PROCHOT#<45,52>

+1.0V_VCCST

RC27

From EC OD output

EC_VCCST_PG_R<45,49>

PM_DOWN_R<18>

+1.0V_VCCST

1K_0402_5%

1 2

RC28 1K_0402_5%

XESD@

1 2

CH65 .1U_0402_16V7K

XESD@

1 2

CH1 .1U_0402_16V7K

XESD@

1 2

CH3 .1U_0402_16V7K

ESD@

1 2

CH2 1000P_0402_50V7K

ESD@

1 2

CH67 1000P_0402_50V7 K

+1.0VS_VCCSTG

12

499_0402_1%

1 2

12

RC29

60.4_0402_1%

1 2

20_0402_1%

@

RC32

1K_0402_5%

1 2

(To VR)

CPU_SVID_ALERT#_R <58>

(To VR)

CPU_SVID_DAT <58>

RC33

H_PROCHOT#_R

EC_VCCST_PG

RC30

12

THERMTRIP#

H_PECI

H_CPUPWRGD

THERMTRIP#

H_PROCHOT#_R

EC_VCCST_PG

PM_DOWN

H_SKTOCC#<19>

CPU_BCLK<20>

CPU_BCLK#<20>

CPU_PCIBCLK<20>

CPU_PCIBCLK#<20>

CPU_24M<20>

CPU_24M#<20>

CPU_SVID_CLK<58>

H_CPUPWRGD<19>

PLTRST_CPU#<18 >

H_PM_SYNC<18>

H_PECI<18,45>

THERMTRIP#<18>

1 2

RC21 0_0402_5%@

RC22

@

0_0402_5%

FLOAT FOR SKL

GND FOR CNL

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18 )

DDR_PG_CTRL

P/N: SA00007UR00 ( S IC

SN74AUP1G07DCKR SC70 5P BUFFER)

1 2

CPU_SVID_ALERT#

CPU_SVID_CLK

CPU_SVID_DAT

H_PROCHOT#_R

DDR_PG_CTRL

EC_VCCST_PG

H_CPUPWRGD

PLTRST_CPU#

H_PM_SYNC

PM_DOWN

H_PECI

THERMTRIP#

H_SKTOCC#_R

SKL_CNL_N

@

T3 PAD

CPU_BCLK

CPU_BCLK#

CPU_PCIBCLK

CPU_PCIBCLK#

CPU_24M

CPU_24M#

H_CATERR#

UC2

NC1VCC

2

A

3

GND

74AUP1G07GW_TSS OP5

B31

A32

D35

C36

E31

D31

BH31

BH32

BH29

BR30

BT13

H13

BT31

BP35

BM34

BP31

BT34

BR33

BN1

BM30

J31

UC1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRG D

PROCPWRG D

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

SKL-H_BGA1440

@

12

Y

REV = 1

+1.2V_VDDQ

CC650.1U_0201_10V6K

5

4

SKYLAKE_H ALO

BGA1 440

5 OF 14

+3VS

12

RC35

220K_0402_5%

RC37

2M_0402_5%@

1 2

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

BN25

CFG0

BN27

BN26

CFG2

BN28

BR20

CFG4

BM20

CFG5

BT20

BP20

CFG7

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

CPU_XDP_TDO

BT28

CPU_XDP_TDI

BL32

CPU_XDP_TMS

BP28

CPU_XDP_TCK0

BR28

BP30

BL30

BP27

CFG_RCOMP

BT25

SM_PG_CTRL <54>

@

T1PAD

@

T2PAD

12

RC24

49.9_0402_1%

1 2

RC23 1K_0402_1%

1 2

RC25 1K_0402_1%@

1 2

RC26 1K_0402_1%

Config. Signals

111

*

11

11

1

0

00

00

000

CPU_XDP_TDO <7,19>

CPU_XDP_TDI <7,19>

CPU_XDP_TMS <7,1 9>

CPU_XDP_TCK0 <7,19>

CFG4

CFG5

CFG2

PCIE

pore

assig n

1 x 16

1 x 16

rever se

2 x 8

2 x 8

rever se

1 x 8

+ 2 x 4

1x8+2 x4

rever se

Reference SKL EDS 0.85 Table 6-8

CFG signals internal PH default value = 1

Desc ri ption

Stall reset sequence after PCU PLL

CFG[0 ]

CFG[4 ]

CFG[7 ]

CFG[1 ]

CFG[3 ]

lock until de-asserted

— 1 = (Default) Normal Operation;

*

No stall.

— 0 = Stall.

Enable eDP

— 1 = Disabled.

— 0 = Enabled.

*

PEG Training:

— 1 = (default) PEG Train immediately

*

following RESET# de asserti on.

— 0 = PEG Wait for BIOS for training

Reserved configuration lane.

CFG[2 ]CFG[5 ]CFG[6 ]

0

1

CFG[8:1 9]

ESD Reserve ,pleace close to cpu

4 4

Security Classification

Security Classification

Security Classification

2016/12/15 2017/12/15

2016/12/15 2017/12/15

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2016/12/15 2017/12/15

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Title

Title

Title

SKL-H(4/9)CLK,GPIO

SKL-H(4/9)CLK,GPIO

SKL-H(4/9)CLK,GPIO

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

Date: Sheet

Date: Sheet

D

Date: Sheet

10 73Friday, March 31, 2017

10 73Friday, March 31, 2017

10 73Friday, March 31, 2017

E

1.A

1.A

1.A

of

of

of

A

B

C

D

E

+VCC_CORE +VCC_CORE

1 1

2 2

3 3

4 4

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

SKYLAKE_H ALO

UC1G

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKL-H_BGA1440

REV = 1 ?

@

BGA1 440

7 OF 14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

Trace Length < 25 mils

AG37

AG38

PH/PL on pwr side

H-4+2/68 A H-4+2/55 A

+VCC_GT +VCC_GT

SKYLAKE_H ALO

UC1H

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BGA1440

@

BGA1 440

REV = 1

8 OF 14

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCSENSE <58>

VSSSENSE <58>

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

?

EDS:Rail is unconnected for Processors without GT3/4.

+VCC_GT

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

UC1N

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BGA1440

SKYLAKE_H ALO

BGA1 440

@

14 OF 14

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGT_SENSE

VSSGTX_SENSE

VSSGT_SENSE

VCCGTX_SENSE

?

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

AH38

AH35

AH37

AH36

VCCGT_SENSE

VSSGT_SENSE

Trace Length < 25 mils

VCCGT_SENSE <58>

VSSGT_SENSE <58>

Security Classification

Security Classification

Security Classification

2016/12/15 2017/12/15

2016/12/15 2017/12/15

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2016/12/15 2017/12/15

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

SKL-H(5/9)Power,SVID

SKL-H(5/9)Power,SVID

SKL-H(5/9)Power,SVID

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

E

1.A

1.A

11 73Friday, March 31, 2017

11 73Friday, March 31, 2017

11 73Friday, March 31, 2017

1.A

of

of

of

A

B

C

D

E

+1.2V_VDDQ_CPU

For Power consumption

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

Measurement

JUMP_43X118

JUMP_43X118

+VDDQ_CLK

+VCCSFR_OC_1

+VCCSFR_OC_2

+1.0V_VCCST

+1.0VS_VCCSTG

+1.0V_VCCSFR

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCPLL_OC

VCCPLL_OC

VCCST

VCCSTG

VCCSTG

VCCPLL

VCCPLL

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

DDR4/2.8 A

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

?

20mA

150mA

SKYLAKE_H ALO

K29

K30

K31

K32

K33

K34

K35

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J30

L31

L32

L35

L36

L37

L38

J15

J16

J17

J19

J20

J21

J26

J27

UC1I

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

SKL-H_BGA1440

REV = 1

@

BGA1 440

9 OF 14

RVP11 47u*1,10u*7,1u*3

CAP place on PWR side.

1 1

RVP11

PWR NEED PROVIDE

0.95V FOR VCCIO

+VCC_SA

H-4+2/11. 1A

+1.0VS_VCCIO

H /5.5A

2 2

+1.2V_VDDQ

JPC1

12

@

JPC2

12

@

130mA

VCCSA_SENSE <58>

VSSSA_SENSE <58>

VCCIO_SENSE <57>

VSSIO_SENSE <57>

NOTE:

VCCPLL_OC is allowed to be turned off

during S3 & DS3 if it is not powered

directly from VDDQ

+1.2V_VDDQ_CPU

Place at Back Side

+1.2V_VDDQ

+1.0VS_VCCSTG

1U_0402_6.3V6K

1

2

+1.0V_VCCST

RC39 0_0402_5%@

RC40

1 2

@

0_0603_5%

1 2

RC41 0_0402_5%

1 2

RC42 0_0402_5%

(1.0VS )

1U_0402_6.3V6K

1

CC68

2

1 2

+VDDQ_CLK

BSC Side

10U_0603_6.3V6M

1

CC70

2

+VCCSFR_OC_1

@

@

1

2

1U_0402_6.3V6K

CC71

+VCCSFR_OC_2

1U_0402_6.3V6K

1

2

CC72

Place at Back Side

+1.0V_VCCST

CC69

1

CC67

1U_0402_6.3V6K

2

Place at Back Side

+1.0V_VCCSFR

1 2

CC66 1U_0402_6.3V6K

3 3

+1.2V_VDDQ_CPU

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC73

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

CC74

1

1

CC75

2

1

CC76

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

CC77

10U_0603_6.3V6M

1

CC78

2

10U_0603_6.3V6M

1

CC79

2

1

1

CC80

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC82

CC81

2

22U_0603_6.3V6M

CC83

1

1

2

2

22U_0603_6.3V6M

22U_0603_6.3V6M

CC84

22U_0603_6.3V6M

CC85

1

1

2

2

Place at Back Side

+1.2V_VDDQ_CPU : 10UF/6.3V/0603 *10

22UF/6.3V/0603 * 4

update CRB cap QTY

4 4

A

CPU_CORE/VCCGT/VCCSA decoupling capacitor place to PWR side

Security Classification

Security Classification

Security Classification

2016/12/15 2017/12/15

2016/12/15 2017/12/15

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERI NG DR AWING IS TH E P ROPRIETAR Y PROP ERTY OF COMPAL ELECTRONICS, INC. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEI THER THIS SHEET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

2016/12/15 2017/12/15

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.0VS_VCCIO

CC86

Place at Back Side

22U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC91

2

1

CC92

2

2

1

CC89

2

22U_0603_6.3V6M

CC87

CC90

1

1

2

2

22U_0603_6.3V6M

22U_0603_6.3V6M

CC88

CC93

1

2

Follow ORB 3/20

Compal&Electronics,&Inc.

Compal&Electronics,&Inc.

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal&Electronics,&Inc.

SKL-H(6/9)POWER

SKL-H(6/9)POWER

SKL-H(6/9)POWER

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

C5PRH&M/B&LA-E921P

12 73Friday, March 31, 2017

12 73Friday, March 31, 2017

12 73Friday, March 31, 2017

E

1.A

1.A

1.A

of

of

of

A

B

C

D

E

BM9

BM6

BM2

C17

C13

BT9

BT5

BR7

BP7

BN9

BN7

BN4

BN2

BH9

BH8

BH5

BH4

BH1

BE6

BD9

C9

SKYLAKE_H ALO

UC1L

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL-H_BGA1440

REV = 1

@

BGA1 440

12 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

C25

C23

C21

C19

C15

C11

C8

C5

BM29

BM25

BM18

BM11

BM8

BM7

BM5

BM3

BL38

BL35

BL13

BL6

BK25

BK22

BK13

BK6

BJ30

BJ29

BJ15

BJ12

BH11

BH10

BH7

BH6

BH3

BH2

BG37

BG14

BG6

BF34

BF6

BE30

BE5

BE4

BE3

BE2

BE1

BD38

BD37

BD12

BD11

BD10

BD8

BD7

BD6

BC33

BC14

BC13

BC6

BB30

BB29

BB6

BB5

C2

BT36

BT35

BT4

BT3

BR38

?

Y38

Y37

Y14

Y13

Y11

Y10

W34

W33

W12

V30

V29

V12

U38

U37

T34

T33

T14

T13

T12

T11

T10

R30

R29

R12

P38

P37

P12

N34

N33

N12

N11

N10

M14

M13

M12

L34

L33

L30

L29

K38

K11

K10

Y9

Y8

Y7

W5

W4

W3

W2

W1

V6

U6

T9

T8

T7

T4

T3

T2

T1

P6

N9

N8

N7

N6

N5

N4

N3

N2

N1

M6

K9

K8

K7

K5

K4

K3

K2

T5

SKL-H_BGA1440

@

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

UC1F

SKYLAKE_H ALO

BGA1 440

6 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

UC1M

SKYLAKE_H ALO

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL-H_BGA1440

REV = 1

@

BGA1 440

13 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

AK30

AK29

AK4

AJ38

AJ37

AJ6

AJ5

AJ4

AJ3

AJ2

AJ1

AH34

AH33

AH12

AH6

AG30

AG29

AG11

AG10

AG8

AG7

AG6

AF14

AF13

AF12

AF4

AF3

AF2

AF1

AE34

AE33

AE6

AD30

AD29

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AC38

AC37

AC12

AC6

AC5

AC4

AC3

AC2

AC1

AB34

AB33

AB6

AA30

AA29

AA12

A30

A28

A26

A24

A22

A20

A18

A16

A14