Acer ORTA SA 1212-1 Schematics

5

4

3

2

1

PCB Layer Stackup

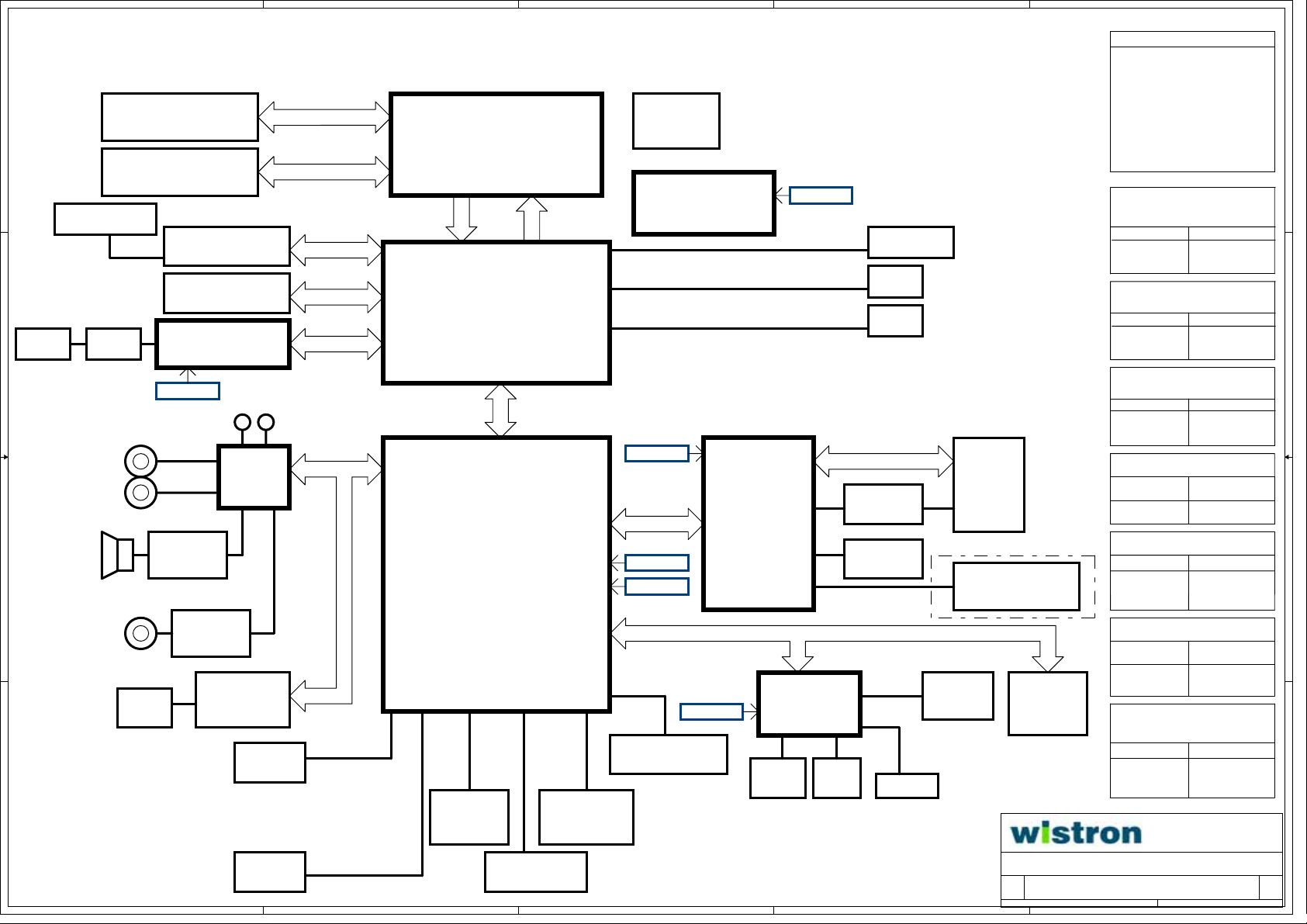

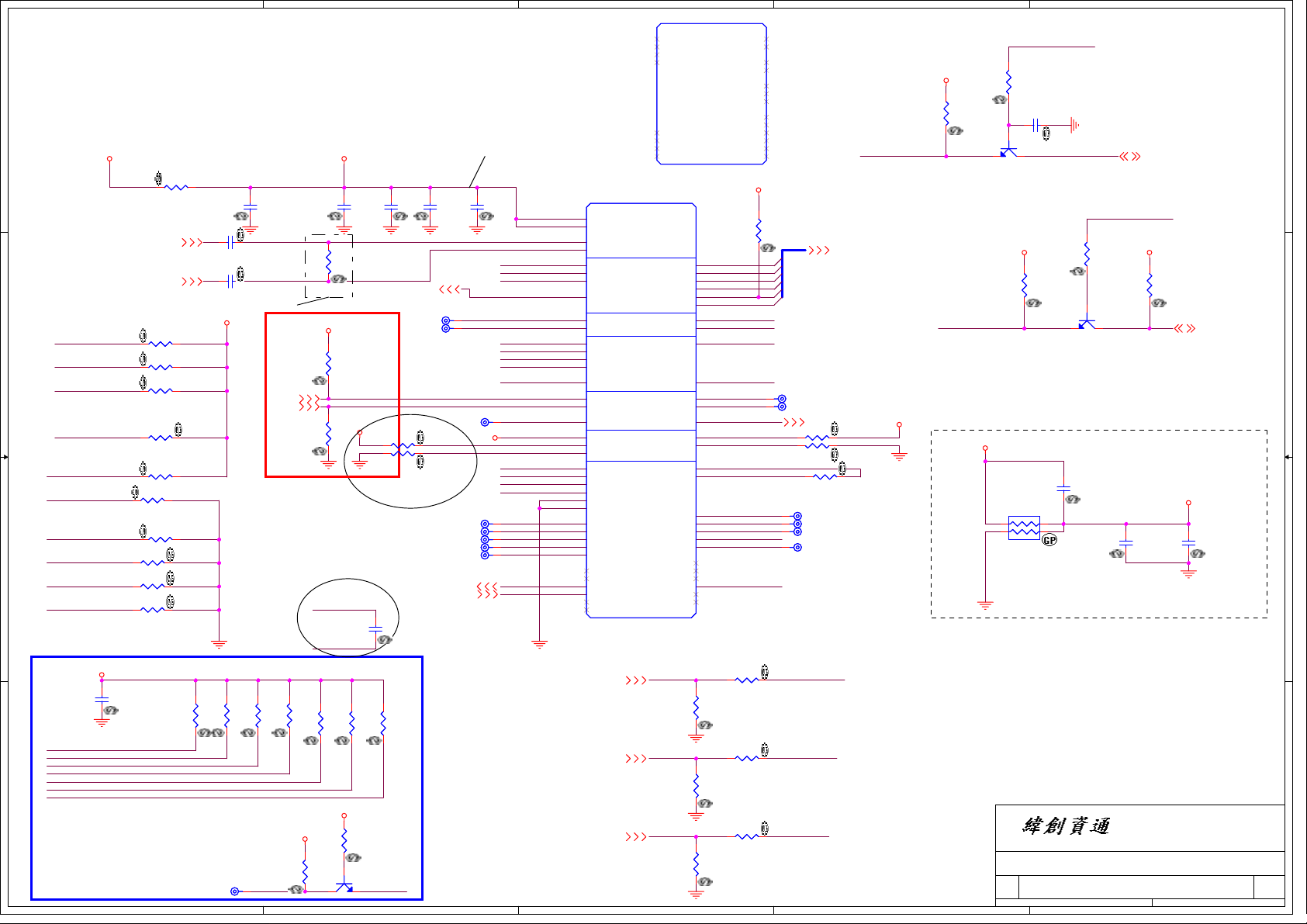

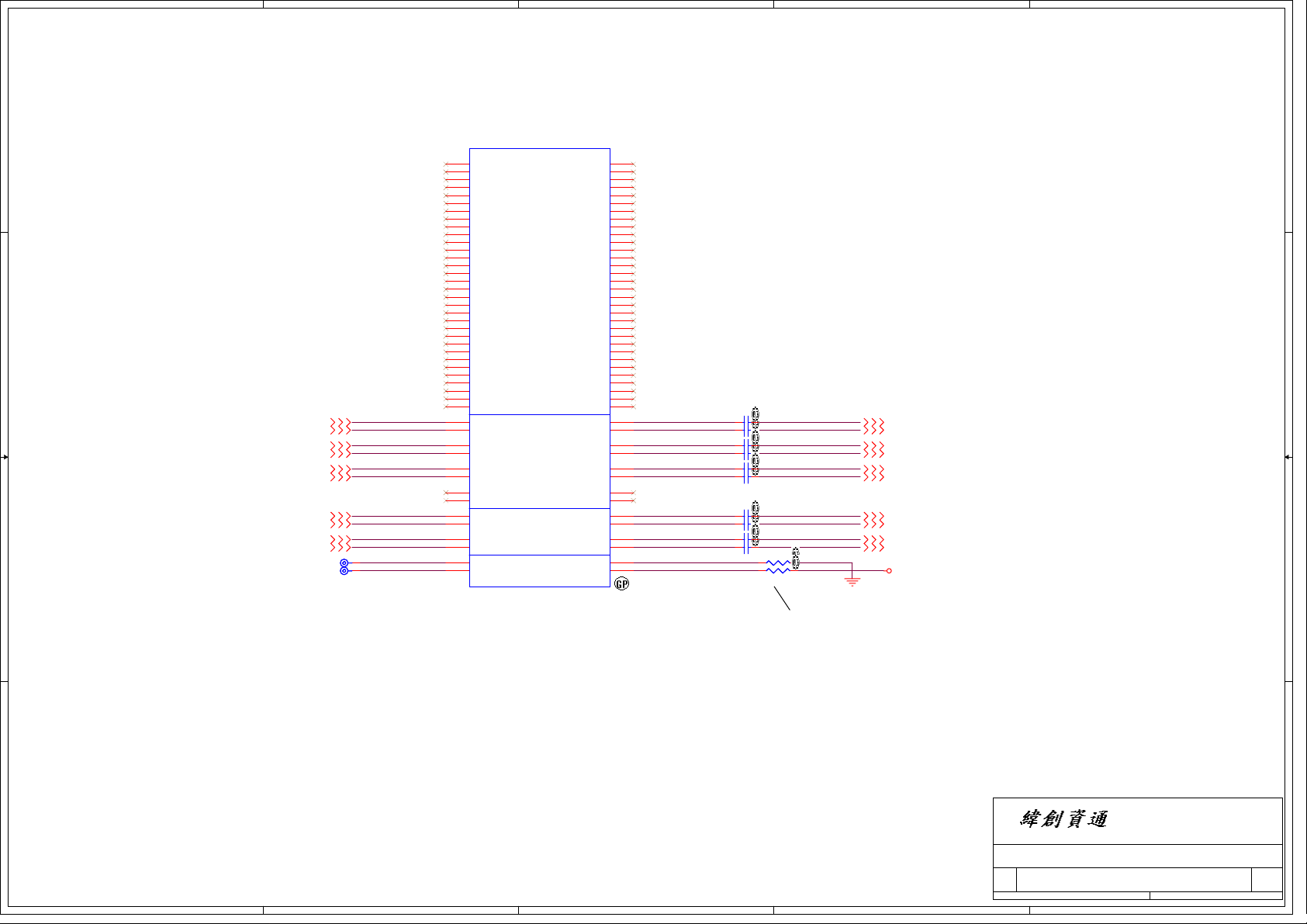

Orta Block Diagram

D D

DIMM1

8,9

DDR2 SODIMM

DDR2 SODIMM

Power Switch

P2231NFC1

DIMM2

28

8,9

New card

Mini Card

802.11a/b/g/n

C C

TXFMRJ45

2424

LAN

10/100/1000

BCM5787M

25MHz

INT. MIC Array

DDR II 533/667/800

DDR II 533/667/800

HyperTransport

PCI-E x 1

28

PCI-E x 1

28

PCI-E x 1

23

AMD

K8 Rev.G

S1g1 Socket

16x16

OUT

IN

ATI

RS690M

10,11,12,13

PCI-E x 4

4,5,

6,7

G792

36

CLK GEN.

ICS 9LPRS502

(RTM875T-605)

Line In

30

30

MIC In

Codec

ALC268

AZALIA

29

ATI

AMP

G1432Q

B B

30

30

INT.SPKR

30

Line Out

AMP

G1410Q

30

AZALIA

SB600

24.576MHz

PCI BUS

25MHz

32.768KHz

O2

OZ711

1394

Cardbus

Cardreader

(No-SPDIF)

USB

CCD .3M/1.3M

USB

32.768KHz

14

3

RJ11

22

MODEM

MDC Card

22

16,17,18,19,20

SATA

HDD

A A

21

USB x 4

USB

4 Port

CDROM

5

PATA

21

4

USB

MINI USB

22 22

Finger print

BlueTooth

22

Project code: 91.4U101.001

PCB P/N : 48.4U101.0SA

REVISION : 06245-SA

14.318MHz

3

S-Vedio

CRT

LCD

PCMCIA I/F

PWR SW

CP2211F

13

14

25

13

PCMCIA

SLOT

Support

TypeII

1394

25,26

KBC

Winbond

WPC8768L

Touch

Pad

32 32

CONN

LPC BUS

31

INT.

KB

27

SPI I/F

FIR

2

MS/MS Pro/xD/

MMC/SD/SDIO

BIOS

W25X80-VSS

31

33

6 in 1

27

27

LPC

DEBUG

CONN.

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Orta

Orta

Orta

33

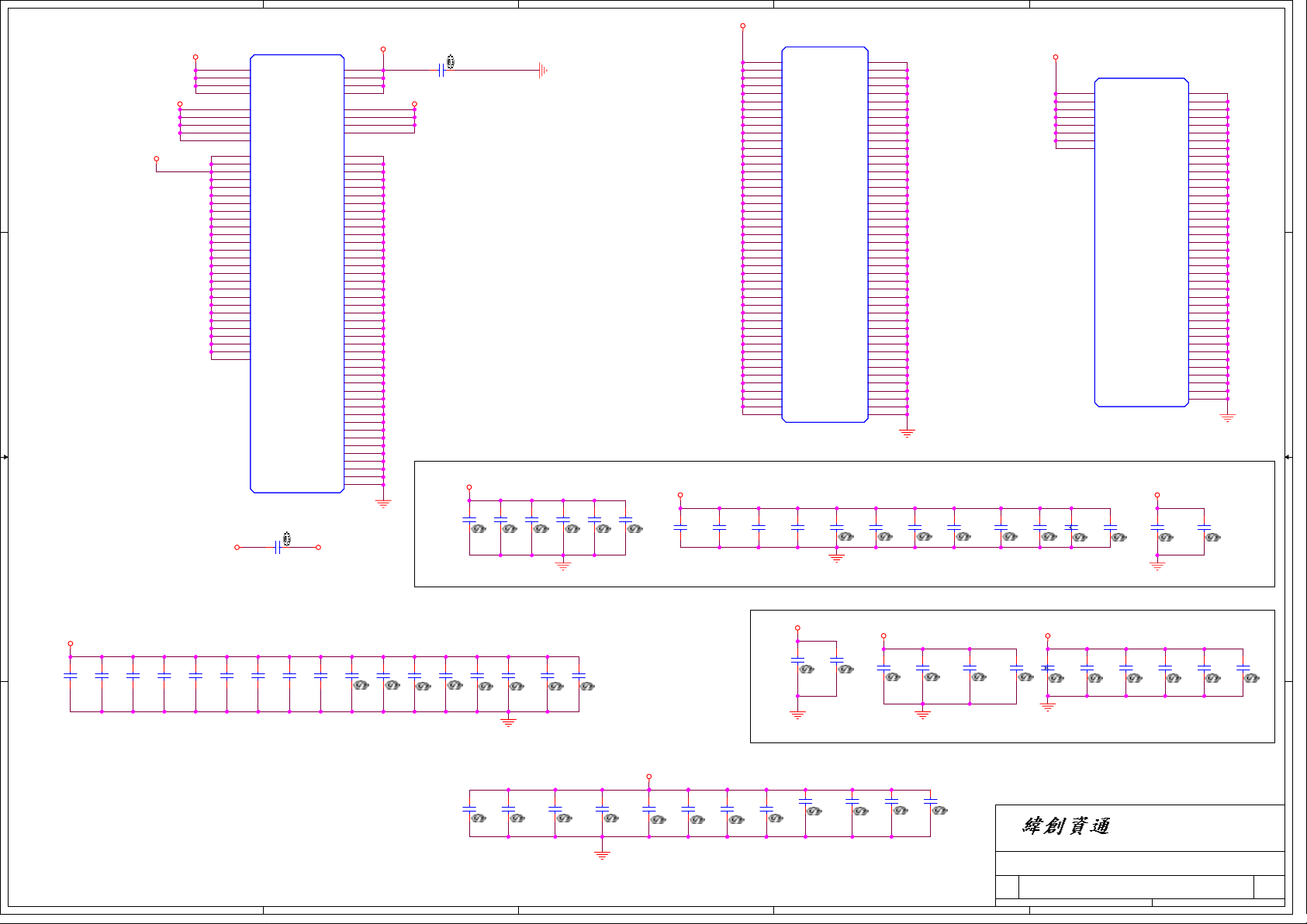

L1: Signal 1

L2: VCC

L3: Inner Signal 2

L4: Inner Signal 3

L5: GND

L6: Signal 4

CPU V_CORE

INPUT

DCBATOUT

SYSTEM DC/DC

INPUT

DCBATOUT

SYSTEM DC/DC

INPUT

DCBATOUT 5V_S5

SYSTEM LDO

INPUT

1D8V_S3

SYSTEM LDO

INPUT

3D3V_S5

3D3V_S0

3D3V_S0

SYSTEM LDO

INPUT

DCBATOUT

Battery Charger

INPUTS

AD+

BAT+

1

OUTPUT

VCC_CORE_S0

OUTPUT

1D2V_S0

1D8V_S3

OUTPUT

3D3V_S5

OUTPUT

0D9V_S3

OUTPUT

1D2V_S5

2D5V_S0

1D5V_S0

OUTPUT

5V_AUX_S5

3D3V_AUX_S5

OUTPUTS

DCBATOUT

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

of

146Tuesday, December 12, 2006

of

146Tuesday, December 12, 2006

of

146Tuesday, December 12, 2006

SA

SA

SA

5

4

3

2

1

SA: 07/31/06 Start

D D

SB change

power team

1.change L7, L9 to 68.1R510.10D

2.changge U12 to 84.04706.037

3.change R66 to 10K ohm

C C

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CHANGE HISTORY

CHANGE HISTORY

CHANGE HISTORY

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet

Orta

Orta

Orta

of

246Tuesday, December 12, 2006

246Tuesday, December 12, 2006

246Tuesday, December 12, 2006

1

SA

SA

SA

5

4

3

2

1

3D3V_S0

1 2

0R3-0-U-GP

0R3-0-U-GP

D D

3D3V_S0

1- PLACE ALL SERIAL TERMINATION

RESISTORS CLOSE TO U800

2- PUT DECOUPLING CAPS CLOSE TO U800

POWER PIN

3D3V_S0

C C

3D3V_S0

12

DY

DY

10KR2J-3-GP

10KR2J-3-GP

R184

R184

R1860R2J-2-GP

NEWCARD_CLKREQ#28

B B

1 2

R1860R2J-2-GP

DY

DY

Check SLGO EXT CLK XSL84606 (56 Pin) or XSL84605 (64 Pin) pin to pin compatable with ICS951464

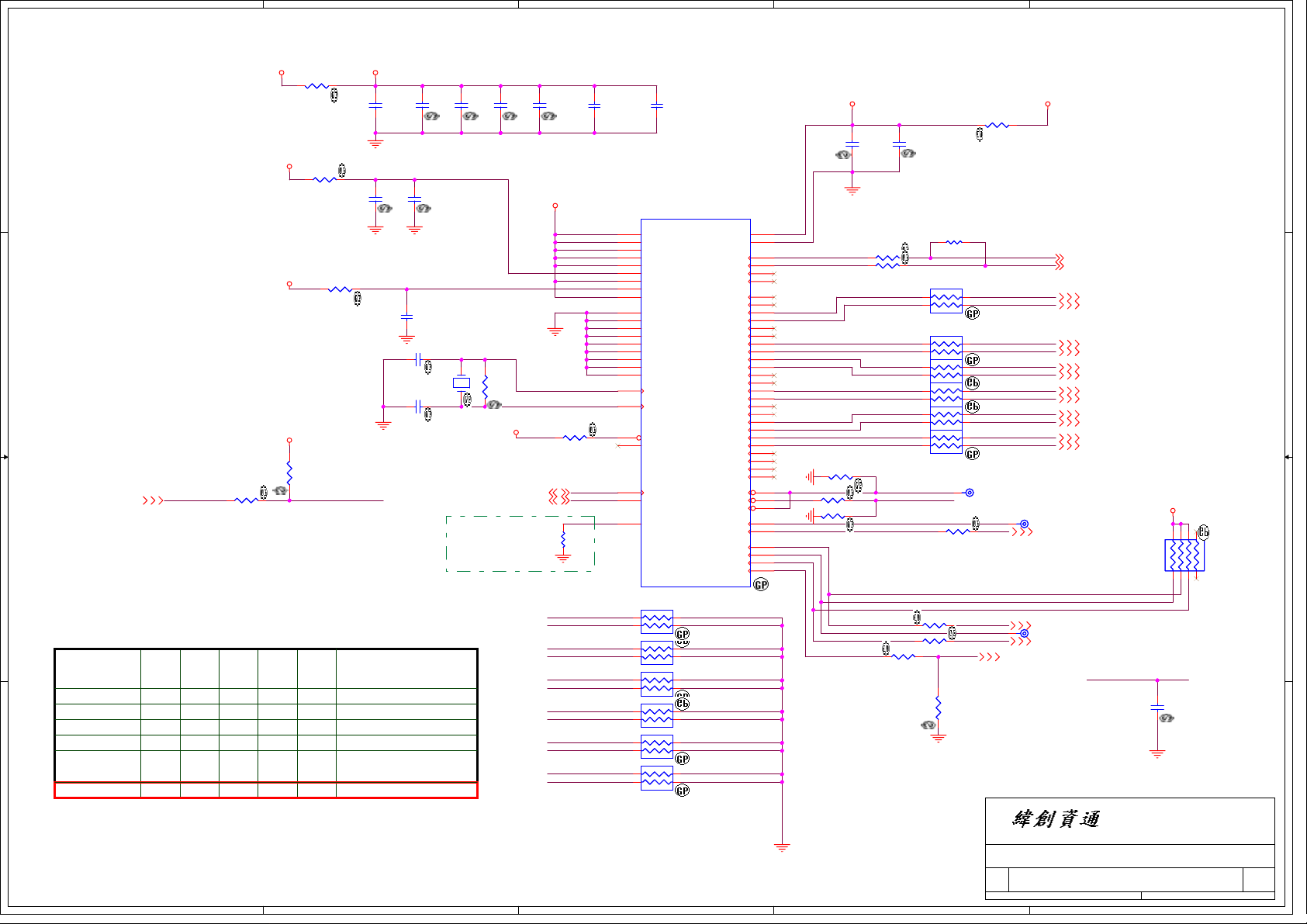

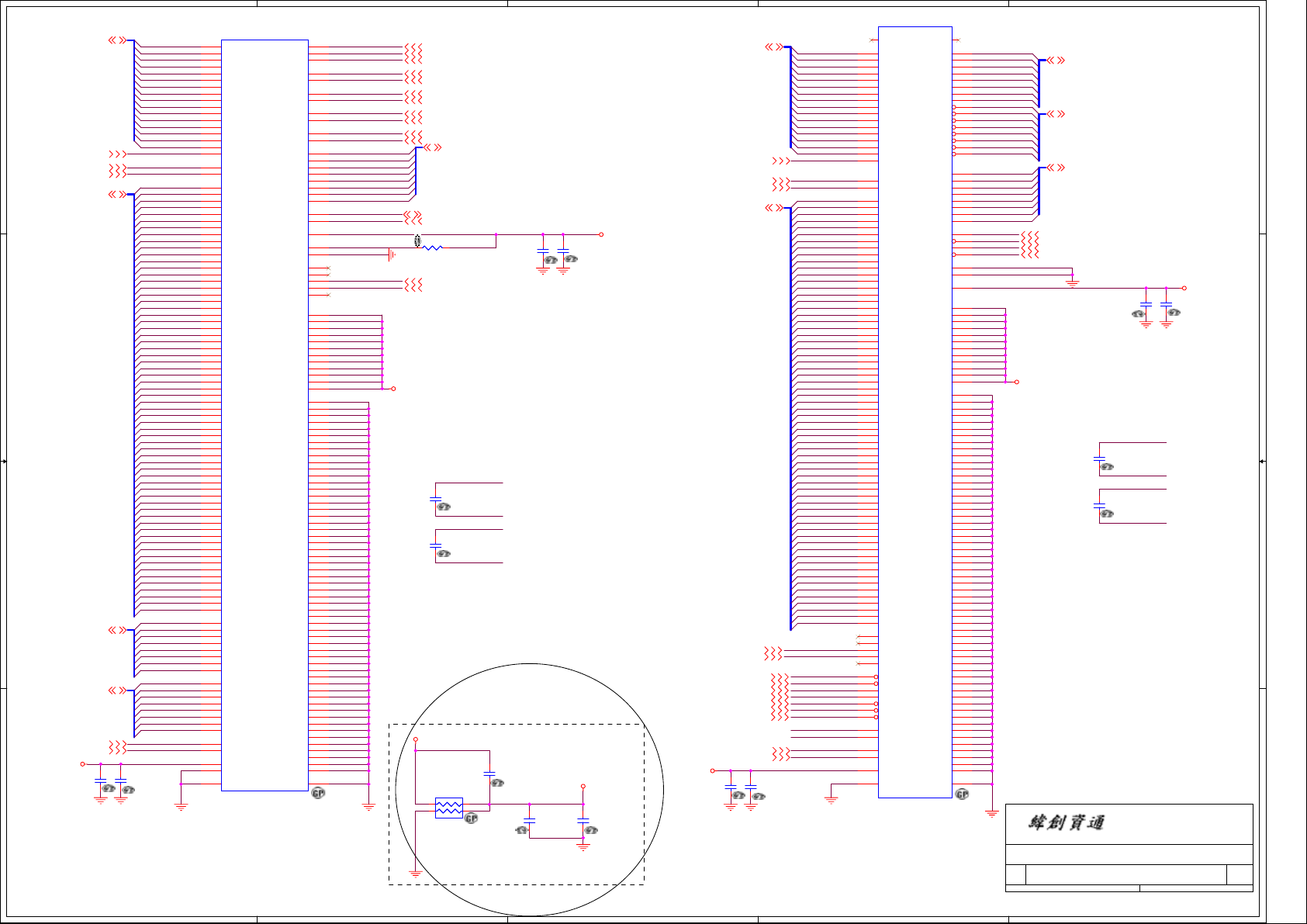

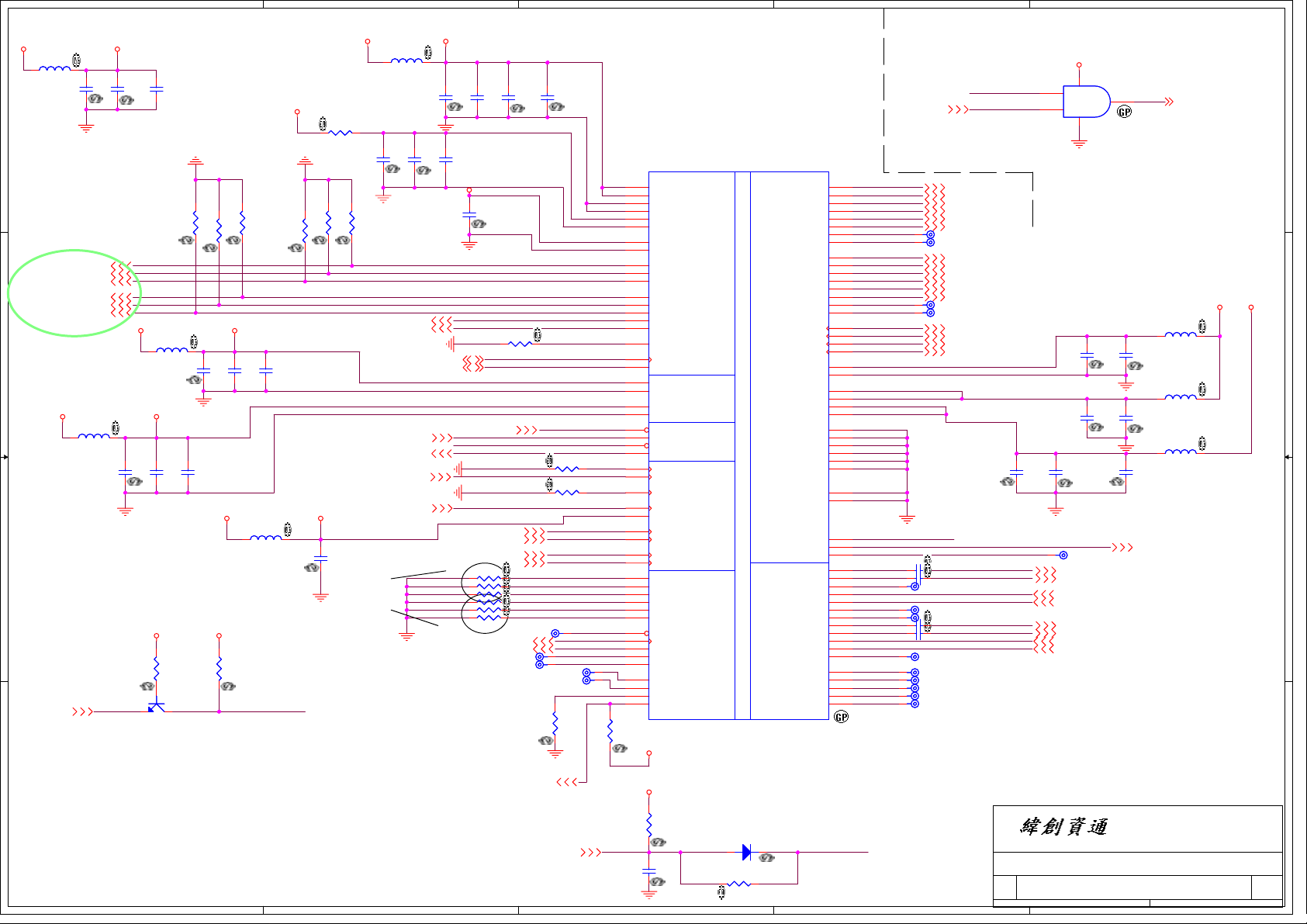

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FS2

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 1

A A

5

CPUFS1

Hi-Z

X

180.00

220.00

100.00

133.33

200.00

SRCCLK

[2:1]

100.00

100.00

100.00

100.00

100.00

100.00

HTTFS0 PCI

Hi-Z Hi-Z100.00 Reserved

X/6X/3

30.0060.00

36.56 73.12

66.66 33.33

66.66 33.33

66.66 33.33 Normal ATHLON64 operation

3D3V_CLK_VDD

R162

R162

R181

R181

2D2R2J-GP

1 2

2D2R2J-GP

3000mA.80ohm

R182

R182

1 2

0R3-0-U-GP

0R3-0-U-GP

CLK_REQB#

USB

COMMENT

48.00

48.00

Reserved

Reserved

48.00

48.00

Reserved

48.00

Reserved

48.00

Reserved

48.00

12

C279

C279

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C304

C304

DY

DY

SC1U16V3ZY-GP

SC1U16V3ZY-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C303

C303

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

Parallel Resonance Crystal

C294 SC18P50V2JN-1-GPC294 SC18P50V2JN-1-GP

1 2

X-14D31818M-44GP

X-14D31818M-44GP

C283 SC18P50V2JN-1-GPC283 SC18P50V2JN-1-GP

1 2

12

12

C301

C301

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_48MPWR_S0

C305

C305

12

X3

X3

Ioh = 5 * Iref

(2.32mA)

12

C302

C302

C280

C280

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

R172

R172

DY

DY

1MR2J-L2-GP

1MR2J-L2-GP

3D3V_S0

SMBC0_SB9,19

SMBD0_SB9,19

Voh = 0.71V @ 60 ohm

4

12

C282

C282

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

3D3V_CLK_VDD

R180

R180

1 2

10KR2J-3-GP

10KR2J-3-GP

R171

R171

475R2F-L1-GP

475R2F-L1-GP

1%

CLK_PCIE_NEW#

CLK_PCIE_NEW

SBLINK_CLK#

SBLINK_CLK

SBSRC_CLK#

SBSRC_CLK

NBSRC_CLK#

NBSRC_CLK

CLK_PCIE_MINI1#

CLK_PCIE_MINI1

CLK_PCIE_LAN

CLK_PCIE_LAN#

C273

C273

54

14

23

28

44

5

39

2

60

53

15

22

29

45

8

38

1

58

3

4

11

61

9

10

48

1

2 3

2 3

1

1

2 3

2 3

1

1

2 3

1

2 3

C306

C306

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

U32

U32

VDDCPU

VDDSRC

VDDSRC

VDDSRC

VDDSRC

VDD48

VDDATIG

VDDREF

VDDHTT

GNDCPU

GNDSRC

GNDSRC

GNDSRC

GNDSRC

GND48

GNDATIG

GNDREF

GNDHTT

X1

X2

RESET_IN#

NC#61

SMBCLK

SMBDAT

IREF

ICS951462YGLFT-GP

ICS951462YGLFT-GP

RN45 SRN49D9F-GPRN45 SRN49D9F-GP

RN36 SRN49D9F-GPRN36 SRN49D9F-GP

RN46 SRN49D9F-GPRN46 SRN49D9F-GP

RN35 SRN49D9F-GPRN35 SRN49D9F-GP

RN44 SRN49D9F-GPRN44 SRN49D9F-GP

RN34 SRN49D9F-GPRN34 SRN49D9F-GP

3

4

4

4

4

4

4

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

SRCCLKT6

SRCCLKC6

ATIGCLKT0

ATIGCLKC0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT2

ATIGCLKC2

ATIGCLKT3

ATIGCLKC3

SRCCLKT5

SRCCLKC5

SRCCLKT4

SRCCLKC4

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT0

SRCCLKC0

SRCCLKT1

SRCCLKC1

SRCCLKT7

SRCCLKC7

CLKREQA#

CLKREQB#

CLKREQC#

48MHZ_1

48MHZ_0

FS1/REF1

FS0/REF0

FS2/REF2

HTTCLK0

VDDA

GNDA

50

49

56

55

52

51

16

17

41

40

37

36

35

34

30

31

18

19

20

21

24

25

26

27

47

46

43

42

12

13

57

32

33

7

6

63

64

62

59

CPUCLK_R

CPUCLK#_R

C274

C274

NBSRC_CLK_R

NBSRC_CLK#_R

SBLINK_CLK_R

SBLINK_CLK#_R

SBSRC_CLK_R

SBSRC_CLK#_R

CLK_PCIE_MINI_R

CLK_PCIE_MINI#_R

CLK_PCIE_NEW_R

CLK_PCIE_NEW#_R

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

R168

R168

1 2

DY

DY

1 2

DY

DY

0R2J-2-GP

0R2J-2-GP

R183

R183

1 2

DY

DY

HTREF_CLK_R

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

R169 47D5R2F-1-GPR169 47D5R2F-1-GP

R170 47D5R2F-1-GPR170 47D5R2F-1-GP

10KR2J-3-GP

10KR2J-3-GP

10KR2J-3-GP

10KR2J-3-GP

12

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

1 2

1 2

CLK_REQA#

CLK_REQB#

R178

R178

CLK48_USB_R

C281

C281

R163 261R2F-GPR163 261R2F-GP

1

RN38

RN38

2 3

1

RN39

RN39

2 3

2 3

RN43

RN43

1

2 3

RN41

RN41

1

2 3

RN42

RN42

1

1

RN37

RN37

2 3

1 2

33R2J-2-GP

33R2J-2-GP

06/05/2006

06/09/2006

FS1

R165 33R2F-3-GPR165 33R2F-3-GP

FS0

FS2

R166 33R2J-2-GPR166 33R2J-2-GP

33R2F-3-GP

33R2F-3-GP

49D9R2F-GP

49D9R2F-GP

2

1 2

12

R161

R161

12

R167

R167

3D3V_S03D3V_CLK_VDDA

R159

R159

12

0R3-0-U-GP

0R3-0-U-GP

CPUCLK 6

CPUCLK# 6

SRN33J-5-GP-U

SRN33J-5-GP-U

4

SRN33J-5-GP-U

SRN33J-5-GP-U

4

4

4

4

4

TP33

TP33

1

R179

R179

12

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN33J-5-GP-U

SRN33J-5-GP-U

TPAD28

TPAD28

HTREF_CLK 12

TP40 TPAD30TP40 TPAD30

CLK48_USB 19

SB_OSC_CLK 19

TP32TPAD30TP32TPAD30

NB_OSC 12

NBSRC_CLK 12

NBSRC_CLK# 12

SBLINK_CLK 12

SBLINK_CLK# 12

SBSRC_CLK 16

SBSRC_CLK# 16

CLK_PCIE_MINI1 28

CLK_PCIE_MINI1# 28

CLK_PCIE_NEW 28

CLK_PCIE_NEW# 28

CLK_PCIE_LAN 23

CLK_PCIE_LAN# 23

CLK48_USB

DY

DY

3D3V_CLK_VDD

123

12

EC61

EC61

EMI REQUEST

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CLKGEN_ICS951412

CLKGEN_ICS951412

CLKGEN_ICS951412

Orta

Orta

Orta

1

346Tuesday, December 12, 2006

346Tuesday, December 12, 2006

346Tuesday, December 12, 2006

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

678

4 5

of

of

of

RN33

RN33

SRN10KJ-6-GP

SRN10KJ-6-GP

SA

SA

SA

5

D D

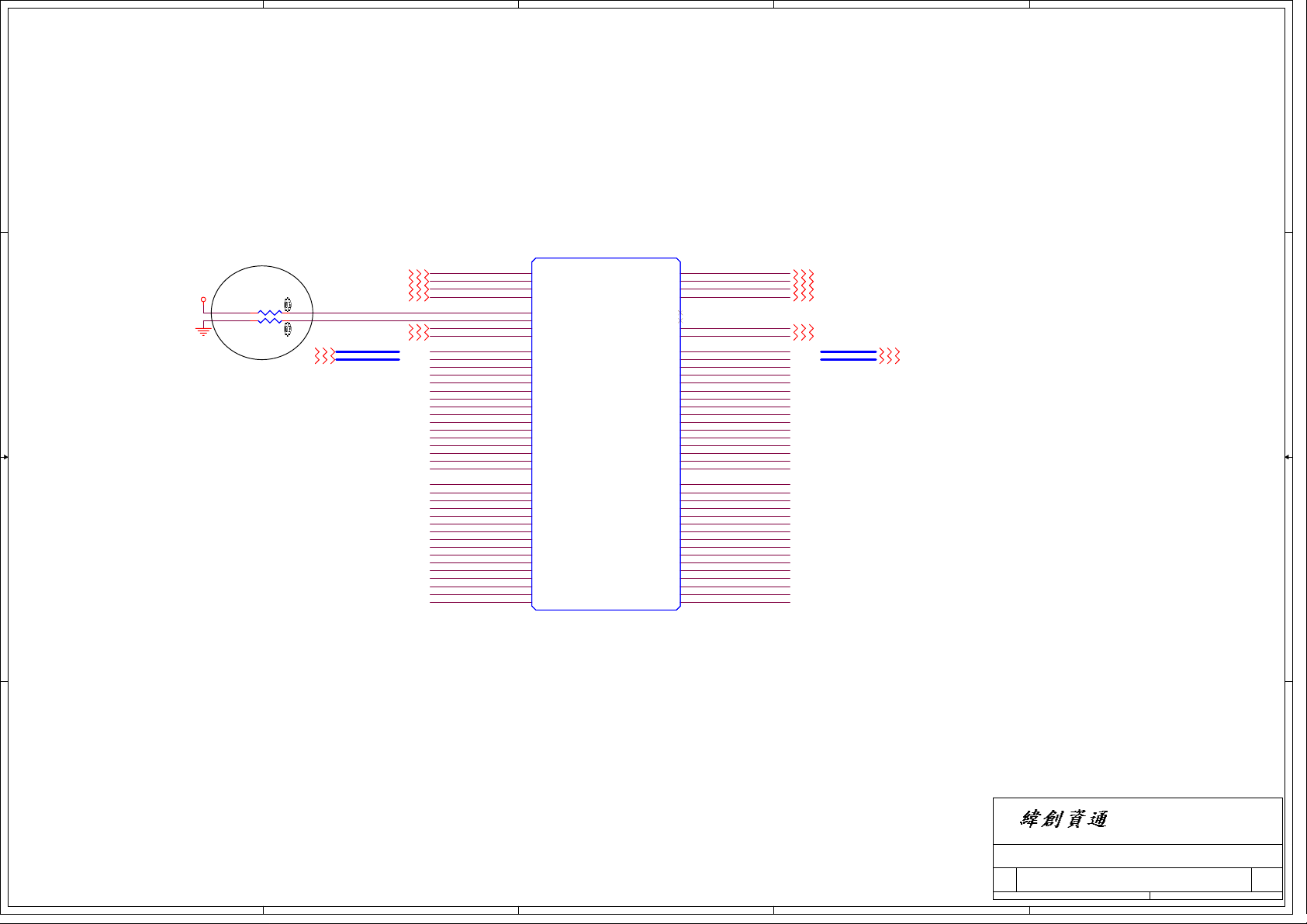

NB0HTTCLKOUT110

R144

1D2V_LDO_S0

C C

B B

R144

51R2J-2-GP

51R2J-2-GP

1 2

1 2

51R2J-2-GP

51R2J-2-GP

R141

R141

NB0CADOUT[15..0]10

NB0CADOUTJ[15..0]10

NB0HTTCLKOUTJ110

NB0HTTCLKOUT010

NB0HTTCLKOUTJ010

NB0HTTCTLOUT10

NB0HTTCTLOUTJ10

4

NB0HTTCLKOUT1

NB0HTTCLKOUTJ1

NB0HTTCLKOUT0

NB0HTTCLKOUTJ0

CPUHTTCTLIN1

CPUHTTCTLINJ1

NB0HTTCTLOUT

NB0HTTCTLOUTJ

NB0CADOUT15

NB0CADOUTJ15

NB0CADOUT14

NB0CADOUTJ14

NB0CADOUT13

NB0CADOUTJ13

NB0CADOUT12

NB0CADOUTJ12

NB0CADOUT11

NB0CADOUTJ11

NB0CADOUT10

NB0CADOUTJ10

NB0CADOUT9

NB0CADOUTJ9

NB0CADOUT8

NB0CADOUTJ8

NB0CADOUT7

NB0CADOUTJ7

NB0CADOUT6

NB0CADOUTJ6

NB0CADOUT5

NB0CADOUTJ5

NB0CADOUT4

NB0CADOUTJ4

NB0CADOUT3

NB0CADOUTJ3

NB0CADOUT2

NB0CADOUTJ2

NB0CADOUT1

NB0CADOUTJ1

NB0CADOUT0

NB0CADOUTJ0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

62.10055.111

62.10055.111

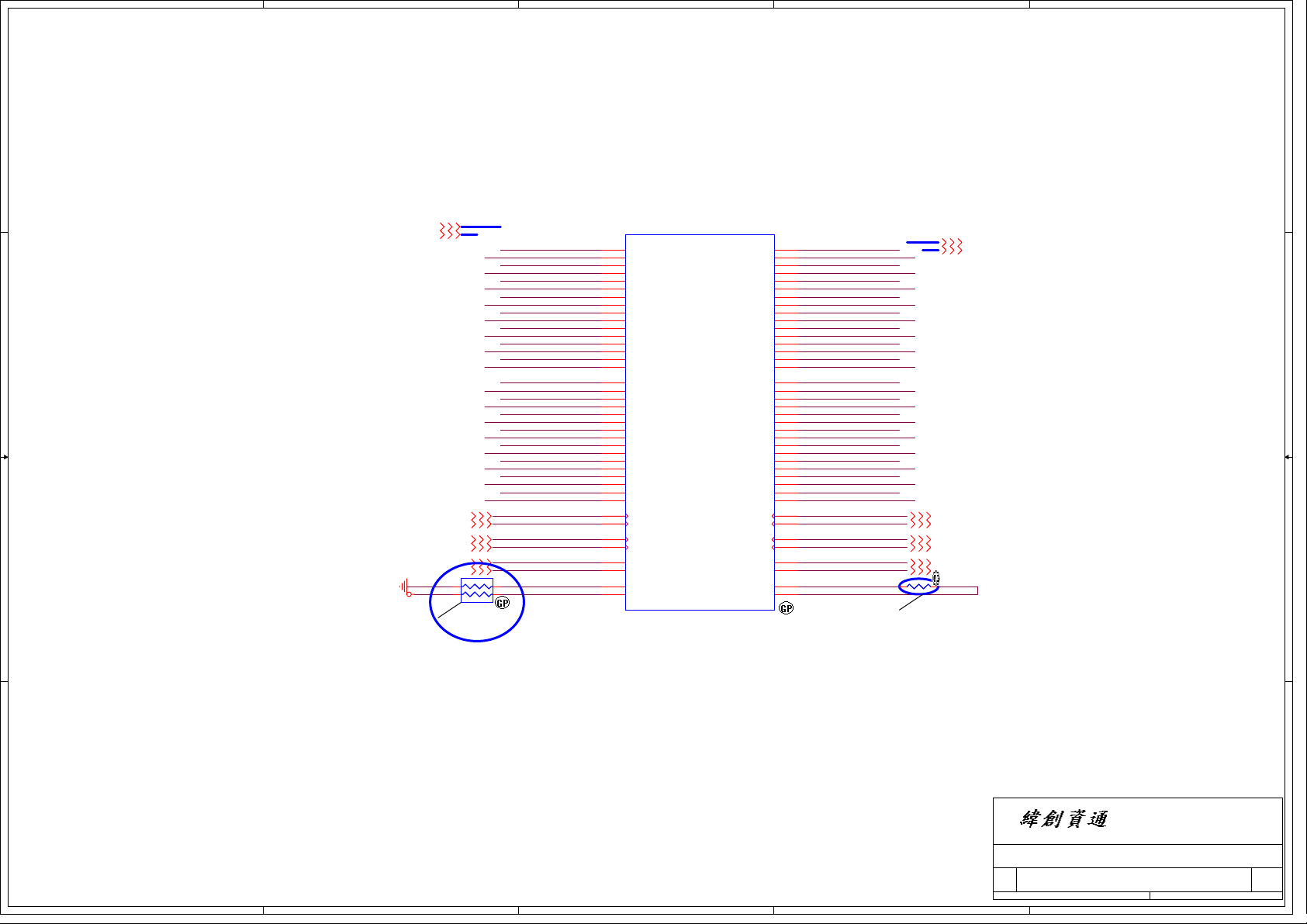

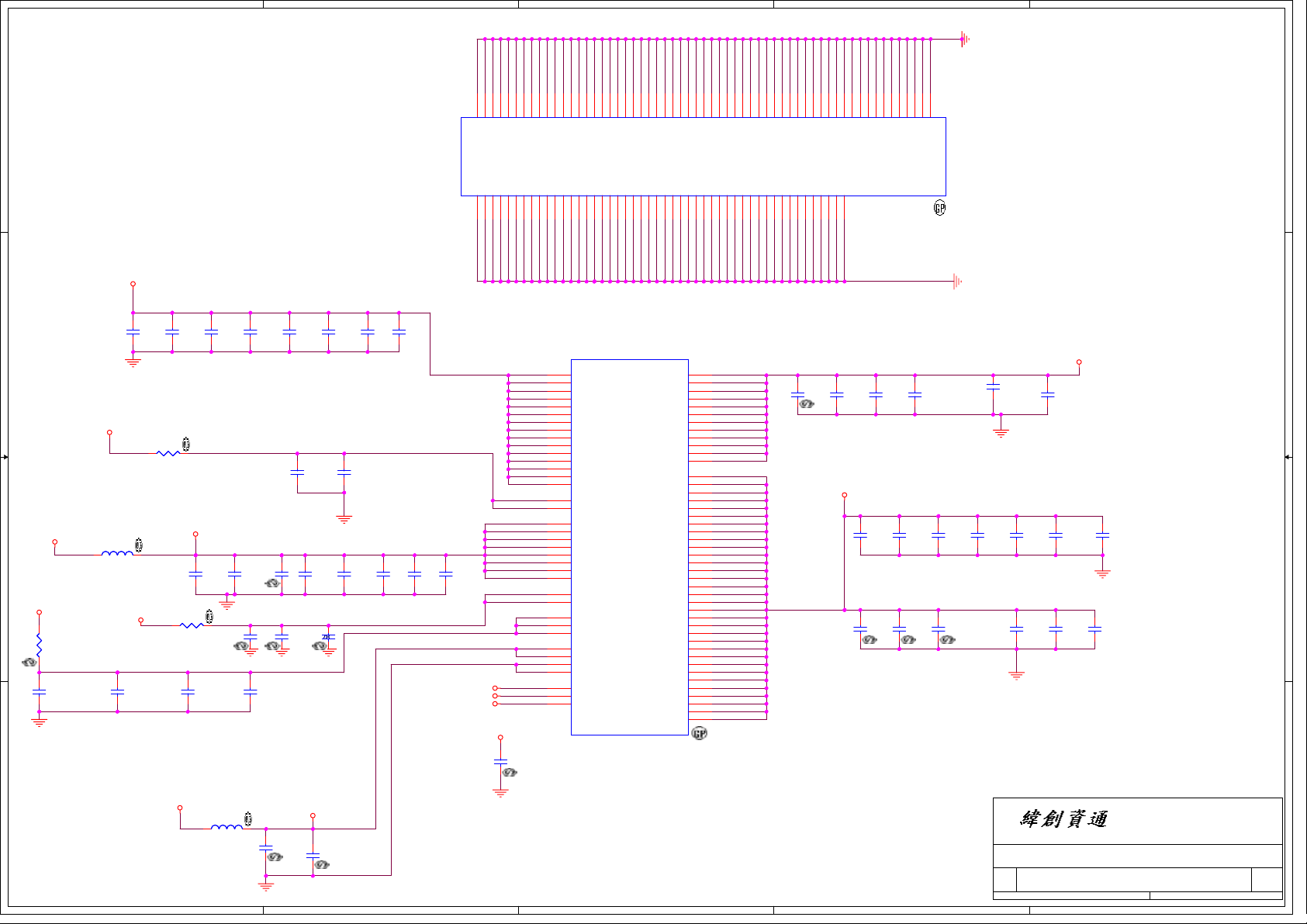

HYPERTRANSPORT

HYPERTRANSPORT

3

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

U52A

U52A

CPUHTTCLKOUT1

Y4

CPUHTTCLKOUTJ1

Y3

CPUHTTCLKOUT0

Y1

CPUHTTCLKOUTJ0

W1

T5

R5

CPUHTTCTLOUT0

R2

CPUHTTCTLOUTJ0

R3

CPUCADOUT15

T4

CPUCADOUTJ15

T3

CPUCADOUT14

V5

CPUCADOUTJ14

U5

CPUCADOUT13

V4

CPUCADOUTJ13

V3

CPUCADOUT12

Y5

CPUCADOUTJ12

W5

CPUCADOUT11

AB5

CPUCADOUTJ11

AA5

CPUCADOUT10

AB4

CPUCADOUTJ10

AB3

CPUCADOUT9

AD5

CPUCADOUTJ9

AC5

CPUCADOUT8

AD4

CPUCADOUTJ8

AD3

CPUCADOUT7

T1

CPUCADOUTJ7

R1

CPUCADOUT6

U2

CPUCADOUTJ6

U3

CPUCADOUT5

V1

CPUCADOUTJ5

U1

CPUCADOUT4

W2

CPUCADOUTJ4

W3

CPUCADOUT3

AA2

CPUCADOUTJ3

AA3

CPUCADOUT2

AB1

CPUCADOUTJ2

AA1

CPUCADOUT1

AC2

CPUCADOUTJ1

AC3

CPUCADOUT0

AD1

CPUCADOUTJ0

AC1

CPUHTTCLKOUT1 10

CPUHTTCLKOUTJ1 10

CPUHTTCLKOUT0 10

CPUHTTCLKOUTJ0 10

CPUHTTCTLOUT0 10

CPUHTTCTLOUTJ0 10

2

CPUCADOUT[15..0] 10

CPUCADOUTJ[15..0] 10

1

<Core Design>

<Core Design>

A A

5

4

3

2

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU(1/4)_HyperTransport I/F

CPU(1/4)_HyperTransport I/F

CPU(1/4)_HyperTransport I/F

Orta

Orta

Orta

1

of

446Tuesday, December 12, 2006

of

446Tuesday, December 12, 2006

of

446Tuesday, December 12, 2006

SA

SA

SA

5

D D

U52B

U52B

MEMORY

MEMORY

INTERFACE

INTERFACE

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA_DQS_H7

MA_DQS_H6

MA_DQS_H5

MA_DQS_H4

MA_DQS_H3

MA_DQS_H2

MA_DQS_H1

MA_DQS_H0

M_A_DQ[63..0]9

C C

B B

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

AA12

AB12

AA14

AB14

W11

AD13

AB13

AD15

AB15

AB17

W14

W16

AD17

AD19

AD21

AB21

AB18

AA18

AA20

AA22

W21

W22

AA21

AB22

AB24

H22

H20

E22

E21

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y12

Y17

Y14

Y18

Y20

Y22

Y24

J19

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_L7

MA_DQS_L6

MA_DQS_L5

MA_DQS_L4

MA_DQS_L3

MA_DQS_L2

MA_DQS_L1

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

4

M_B_DQ[63..0]9

Y16

AA16

E16

F16

V19

J22

V22

T19

V20

U19

U20

U21

T20

K22

R20

T22

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

Y13

AB16

Y19

AC24

F24

E19

C15

E12

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_CLK_DDR2 9

M_A_CLK_DDR2# 9

M_A_CLK_DDR1 9

M_A_CLK_DDR1# 9

M_A_CS3# 8,9

M_A_CS2# 8,9

M_A_CS1# 8,9

M_A_CS0# 8,9

M_A_ODT1 8,9

M_A_ODT0 8,9

M_A_CAS# 8,9

M_A_WE# 8,9

M_A_RAS# 8,9

M_A_BS#2 8,9

M_A_BS#1 8,9

M_A_BS#0 8,9

M_A_CKE1 8,9

M_A_CKE0 8,9

M_A_DQS[7..0] 9

M_A_DQS#[7..0] 9

M_A_DM[7..0] 9

M_A_A[15..0] 8,9

3

U52C

U52C

M_B_DQ63

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

MEMORY

MEMORY

INTERFACE

INTERFACE

2

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB0_ODT1

MB0_ODT0

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

AF18

AF17

A17

A18

Y26

J24

W24

U23

W23

W26

V26

U22

U24

K26

T26

U26

H26

J23

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

F26

E26

A24

A23

D16

C16

C12

B12

AD12

AC16

AE22

AB26

E25

A22

B16

A12

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_CLK_DDR2 9

M_B_CLK_DDR2# 9

M_B_CLK_DDR1 9

M_B_CLK_DDR1# 9

M_B_CS3# 8,9

M_B_CS2# 8,9

M_B_CS1# 8,9

M_B_CS0# 8,9

M_B_ODT1 8,9

M_B_ODT0 8,9

M_B_CAS# 8,9

M_B_WE# 8,9

M_B_RAS# 8,9

M_B_BS#2 8,9

M_B_BS#1 8,9

M_B_BS#0 8,9

M_B_CKE1 8,9

M_B_CKE0 8,9

M_B_A[15..0] 8,9

M_B_DQS[7..0] 9

M_B_DQS#[7..0] 9

M_B_DM[7..0] 9

1

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

CPU(2/4)_DDR

CPU(2/4)_DDR

CPU(2/4)_DDR

Orta

Orta

Orta

of

546Tuesday, December 12, 2006

546Tuesday, December 12, 2006

546Tuesday, December 12, 2006

1

SA

SA

SA

5

D D

IF 0 ohm IS NOT GOOD ENOUGH, TRY 68.00082.491

12

0R3-0-U-GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

CPUCLK3

CPUCLK#3

DY

DY

300R2J-4-GP

300R2J-4-GP

DY

DY

300R2J-4-GP

300R2J-4-GP

DY

DY

300R2J-4-GP

300R2J-4-GP

510R2F-L-GP

510R2F-L-GP

300R2J-4-GP

300R2J-4-GP

12

300R2J-4-GP

300R2J-4-GP

0R3-0-U-GP

R314

R314

12

R102

R102

12

R317

R317

12

R363

R363

12

R319

R319

C453

C453

C451

C451

1 2

SC3900P50V2KX-2GP

SC3900P50V2KX-2GP

C450

C450

1 2

SC3900P50V2KX-2GP

SC3900P50V2KX-2GP

Near To CPU

1D8V_S3

Remove

these

resistor

12

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

100R3J-4-GP

100R3J-4-GP

COREFB37

COREFB#37

100R3J-4-GP

100R3J-4-GP

R325

R325

?

?

?

?

?

LDT_PWROK

LDT_STP#_CPU

LDT_RST#_CPU

CPU_TEST25_H

CPU_TEST26

CPU_TEST18

R316

R316

1 2

C C

2D5V_VDDA_S02D5V_S0

12

C165

C165

12

R321

R321

169R2F-GP

169R2F-GP

VCC_CORE_S0

12

R131

R131

20061031 for Power Test

12

R114

R114

1D8V_S3

when using

TP11TPAD30 TP11TPAD30

EVT CPU

Change;Add

H_THERMDA

H_THERMDC

12

12

R154

R154

DY

DY

220R2F-GP

220R2F-GP

R103

R103

10KR2J-3-GP

10KR2J-3-GP

HDT_RST# LDT_RST#

1

R152

R152

DY

DY

3D3V_S0

12

R153

R153

DY

DY

220R2F-GP

220R2F-GP

12

DY

DY

DY

DY

DY

DY

12

R100

R100

220R2F-GP

220R2F-GP

DY

DY

220R2F-GP

220R2F-GP

1D8V_S3

12

312

Q5

Q5

CPU_TEST19

?

CPU_TEST21

?

B B

A A

CPU_TEST25_L

CPU_SIC

DY

DY

DBREQJ

DBRDY

TMS

TRST_L

TCK

TDI

TDO

1D8V_S3

12

C267

C267

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1 2

1 2

1 2

300R2J-4-GP

300R2J-4-GP

300R2J-4-GP

300R2J-4-GP

510R2F-L-GP

510R2F-L-GP

300R2J-4-GP

300R2J-4-GP

R101

R101

0R2J-2-GP

0R2J-2-GP

12

DY

DY

R122

R122

R155

R155

R120

R120

R362

R362

12

HDT Connectors

5

4

LYAOUT:ROUTE VDDA TRACE APPROX.

50mils WIDE(USE 2X25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

12

12

C146

C146

SC3300P50V2KX-1GP

SC3300P50V2KX-1GP

SC10U10V5ZY-1GP

CLKCPU_IN

CLKCPU#_IN

CPU_PRESENT#37

COREFB

COREFB#

1 2

R366 39D2R2F-L-GPR366 39D2R2F-L-GP

1 2

R365 39D2R2F-L-GPR365 39D2R2F-L-GP

12

12

12

R151

R151

220R2F-GP

220R2F-GP

R99

R99

4K7R2J-2-GP

4K7R2J-2-GP

DY

DY

MMBT3904-U1

MMBT3904-U1

SC10U10V5ZY-1GP

TP77TPAD30 TP77TPAD30

TP78TPAD30 TP78TPAD30

VREF_DDR_CLAW

H_THERMDC35

H_THERMDA35

C232

C232

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

R150

R150

0R2J-2-GP

0R2J-2-GP

DY

DY

4

C153

C153

TP21TPAD30 TP21TPAD30

TP13TPAD30 TP13TPAD30

TP14TPAD30 TP14TPAD30

TP15TPAD30 TP15TPAD30

TP12TPAD30 TP12TPAD30

TP24TPAD30 TP24TPAD30

1

1

CPU_SIC

CPU_SID

12

C456

C456

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

LDT_PWROK

LDT_STP#_CPU

LDT_RST#_CPU

CPU_PRESENT#

TDI

TRST_L

TCK

TMS

DBREQJ

VTT_SENSE

1

MEMZN

MEMZP

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST19

CPU_TEST18

CPU_TEST17

1

CPU_TEST16

1

CPU_TEST15

1

CPU_TEST14

1

CPU_TEST12

1

SB_CPUPWRGD16

AC6

AF4

AF5

AF9

AD9

AC9

AA9

W17

AE10

AF10

H10

AA7

AC8

AA6

AB6

F10

E10

Y10

F8

F9

A9

A8

A7

B7

F6

E6

E9

E8

G9

C2

D7

E7

F7

C7

C3

W7

W8

Y6

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

LDT_RST#16

LDT_STP#12,16

3

P20

P19

N20

N19

R26

R25

P22

R22

THERMTRIP_L

PROCHOT_L

MISC

MISC

VDDIO_FB_H

VDDIO_FB_L

TEST29_H

TEST28_H

3

TEST29_L

TEST28_L

RSVD_MA0_CLK_H3

RSVD_MA_RESET_L

RSVD_MA0_CLK_L3

RSVD_MB_RESET_L

RSVD_MA0_CLK_H0

RSVD_MA0_CLK_L0

RSVD_VIDSTRB1

RSVD_VIDSTRB0

RSVD_VDDNB_FB_H

RSVD_VDDNB_FB_L

RSVD_CORE_TYPE

MISC

MISC

INTERNAL

INTERNAL

RSVD_MB0_CLK_H3

RSVD_MB0_CLK_L3

RSVD_MB0_CLK_H0

RSVD_MB0_CLK_L0

U52D

U52D

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

AF6

AC7

AE9

TDO

G10

DBRDY

W9

Y9

A3

PSI_L

CPU_HTREF1

P6

HTREF1

HTREF0

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST26

TEST10

TEST8

R6

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

12

R307

R307

10KR2F-2-GP

10KR2F-2-GP

12

R309

R309

10KR2F-2-GP

10KR2F-2-GP

12

R312

R312

10KR2F-2-GP

10KR2F-2-GP

CPU_HTREF0

U52E

U52E

H16

B18

B3

C1

H6

G6

D5

R24

FREE5

W18

FREE6

R23

FREE4

AA8

FREE1

H18

FREE2

H19

FREE3

1D8V_S3

12

R315

R315

300R2J-4-GP

300R2J-4-GP

TP20 TPAD30TP20 TPAD30

TP22 TPAD30TP22 TPAD30

PSI# 37

1 2

1 2

1 2

TP72 TPAD30TP72 TPAD30

TP27 TPAD30TP27 TPAD30

TP73 TPAD30TP73 TPAD30

TP70 TPAD30TP70 TPAD30

VID[5..0] 37

80D6R2F-L-GP

80D6R2F-L-GP

VID5

VID4

VID3

VID2

VID1

VID0

THERMTRIP#

PROCHOT#

TDO

DBRDY

VDDIO_FB

1

VDDIO_FB#

1

PSI#

R147 44D2R2F-GPR147 44D2R2F-GP

R146 44D2R2F-GPR146 44D2R2F-GP

CPU_TEST29H

CPU_TEST29L

LAYOUT: Route FBCLKOUT_H/L

CPU_TEST24

CPU_TEST23

CPU_TEST22

CPU_TEST21

CPU_TEST20

CPU_TEST26

1 2

R308

R308

1 2

R318

R318

1 2

R313

R313

R112

R112

differentially impedance 80

1

1

1

1

LDT_RST#_CPU

0R2J-2-GP

0R2J-2-GP

LDT_STP#_CPU

0R2J-2-GP

0R2J-2-GP

LDT_PWROK

0R2J-2-GP

0R2J-2-GP

2

300R2J-4-GP

300R2J-4-GP

THERMTRIP#

1D2V_LDO_S0

2

R367

R367

LDT_PWROK

1D8V_S3

12

2K2R2J-2-GP

2K2R2J-2-GP

PROCHOT#

12

R371

R371

C550

C550

1 2

1

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3

2

MMBT3904-U1

MMBT3904-U1

Q16

Q16

1D8V_S3 3D3V_S0

R364

R364

300R2J-4-GP

300R2J-4-GP

12

R370

R370

2K2R2J-2-GP

2K2R2J-2-GP

MMBT3904-U1

MMBT3904-U1

2

LDT_PWROK

12

DY

DY

1

Q15

Q15

DY

DY

CPU_THERMTRIP# 35

12

3

VREF_DDR_CLAW

1D8V_S3

12

C544

C544

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

RN58

RN58

1

4

2 3

SRN1KJ-7-GP

SRN1KJ-7-GP

LAYOUT: Locate close to CPU.

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

CPU(3/4)_Control & Debug

CPU(3/4)_Control & Debug

CPU(3/4)_Control & Debug

12

C542

C542

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Orta

Orta

Orta

1

R369

R369

4K7R2J-2-GP

4K7R2J-2-GP

ALERT# 17,35

VREF_DDR_CLAW

12

C543

C543

646Tuesday, December 12, 2006

646Tuesday, December 12, 2006

646Tuesday, December 12, 2006

1

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SA

SA

SA

of

5

1D2V_LDO_S0

D4

VLDT_A4

D3

VLDT_A3

D2

VLDT_A2

D1

0D9V_S3

D D

1D8V_S3

C C

0D9V_S3 1D8V_S3

B B

VLDT_A1

D10

VTT8

C10

VTT7

B10

VTT6

AD10

VTT5

W10

VTT9

H25

VDDIO23

J17

VDDIO1

K18

VDDIO2

K21

VDDIO3

K23

VDDIO4

K25

VDDIO5

L17

VDDIO6

M18

VDDIO7

M21

VDDIO8

M23

VDDIO9

M25

VDDIO10

N17

VDDIO11

P18

VDDIO12

P21

VDDIO13

P23

VDDIO14

P25

VDDIO15

R17

VDDIO16

T18

VDDIO17

T21

VDDIO18

T23

VDDIO19

T25

VDDIO20

U17

VDDIO21

V18

VDDIO22

V21

VDDIO24

V23

VDDIO25

V25

VDDIO26

Y25

VDDIO27

1 2

C559

C559

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

I O

I O

POWER

POWER

VLDT_B4

VLDT_B3

VLDT_B2

VLDT_B1

VTT4

VTT3

VTT2

VTT1

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

U52H

U52H

LAYOUT: Place on backside of processor.

VCC_CORE_S0

12

C216

C216

12

C173

C173

10u x 9

12

C169

C169

0.22u x 2

12

12

12

12

12

C213

C213

C195

C195

C182

C182

C215

C215

C170

C170

12

C244

C244

1D2V_LDO_S0

AE5

AE4

AE3

AE2

AC10

AB10

AA10

A10

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

12

C166

C166

4

12

C199

C199

1 2

0D9V_S3

0.01u x 2

12

C218

C218

C254

C254

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

1D8V_S3

12

C219

C219

12

12

C228

C228

C163

C163

0.22u X 6

12

C191

C191

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

180p x 4

12

C214

C214

3

1D8V_S3

12

C181

C181

12

C140

C140

C238

C238

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

12

12

C164

C164

C177

C177

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

12

12

C196

C196

VCC_CORE_S0

U52F

U52F

AC4

VDD1

AD2

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

VDD17

M6

VDD18

M8

VDD19

M10

VDD20

N7

VDD21

N9

VDD22

N11

VDD23

P8

VDD24

P10

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

R11

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

T10

VDD33

T12

VDD34

T14

VDD35

U7

VDD36

U9

VDD37

U11

VDD38

U13

VDD39

V6

VDD40

V8

VDD41

V10

VDD42

V12

VDD43

V14

VDD44

W4

VDD45

Y2

VDD46

10u x 4

12

12

C240

C240

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C241

C241

12

12

C138

C138

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

0D9V_S3

12

VDD

VDD

12

C139

C139

0.22u X 4

12

C541

C541

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

4.7u x 6

C113

C113

C546

C546

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

AA4

AA11

AA13

AA15

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

12

0D9V_S3

12

C239

C239

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

C452

C452

2

VCC_CORE_S0

J15

VDD47

K16

VDD48

L15

VDD49

M16

VDD50

P16

VDD51

T16

VDD52

U15

VDD53

V16

VDD54

180P x 2 0.01u X 2

12

C137

C137

12

12

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

4.7u x 4

C125

C125

C269

C269

12

12

12

C104

C104

C253

C253

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

C558

C558

12

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

0D9V_S3

12

C268

C268

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

C245

C245

12

12

C204

C204

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

C255

C255

1

U52G

U52G

M17

VSS91

N4

VSS92

N8

VSS93

N10

VSS94

N16

VSS95

N18

VSS96

P2

VSS97

P7

VSS98

P9

VSS99

P11

VSS100

P17

VSS101

R8

VSS102

R10

VSS103

R16

VSS104

R18

VSS105

VDD

VDD

1D8V_S3

C209

C209

SC180P50V2JN-1GP

SC180P50V2JN-1GP

Place near to CPU

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS130

VSS131

VSS132

VSS133

12

C145

C145

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

12

C230

C230

SCD01U50V2ZY-1GP

SCD01U50V2ZY-1GP

SCD01U50V2ZY-1GP

SCD01U50V2ZY-1GP

180P x 6

12

12

12

C454

C454

C131

C131

C251

C251

12

C118

C118

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

A A

5

SC10U10V5ZY-1GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

SCD01U50V2ZY-1GP

SCD01U50V2ZY-1GP

4

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

12

12

C261

C261

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

C262

C262

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

4.7u x 4

12

C260

C260

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

1D2V_LDO_S0

C460

C460

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

0.1u x 3 0.22u X 2

12

12

C126

C126

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3

C128

C128

12

C127

C127

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C471

C471

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

180p x 2

12

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

C257

C257

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

12

12

C259

C259

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

12

C465

C465

C123

C123

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

2

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

SCD22U16V3ZY-GP

SCD22U16V3ZY-GP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

CPU(4/4)_Power

CPU(4/4)_Power

CPU(4/4)_Power

Orta

Orta

Orta

SC180P50V2JN-1GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SA

SA

of

746Tuesday, December 12, 2006

746Tuesday, December 12, 2006

746Tuesday, December 12, 2006

1

SA

5

4

3

2

1

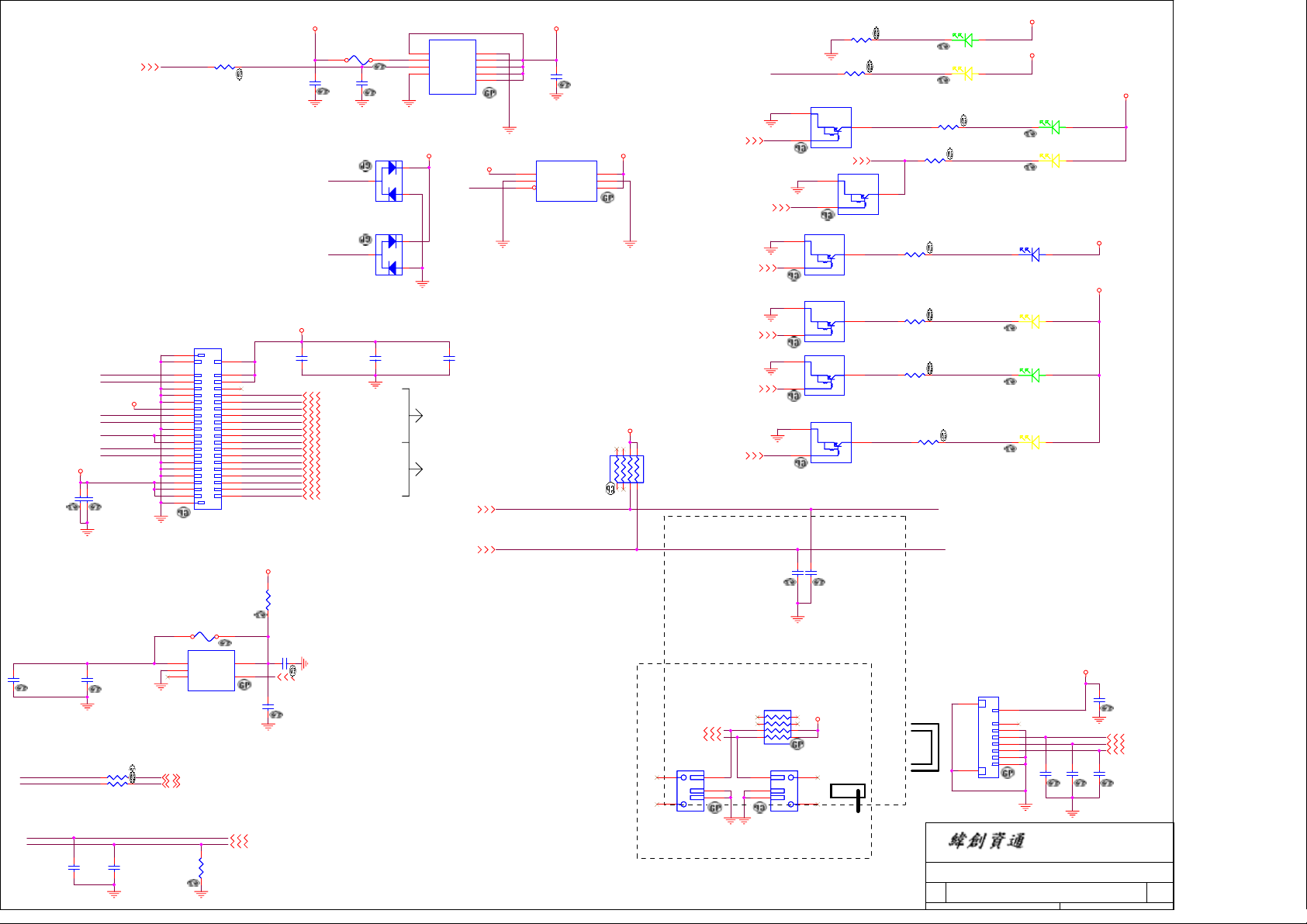

PARALLEL TERMINATION

Decoupling Capacitor

Put decap near power(0.9V) and pull-up resistor

0D9V_S3

RN55

RN55

1

2

3

D D

C C

B B

A A

4 5

SRN47J-4-GP

SRN47J-4-GP

RN24

RN24

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN30

RN30

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN27

RN27

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN18

RN18

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN23

RN23

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN57

RN57

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN56

RN56

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN19

RN19

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN21

RN21

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN25

RN25

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN17

RN17

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

M_A_A2

M_A_A4

M_A_A6

M_A_A7

M_A_A10

M_A_BS#0

M_A_A1

M_A_WE#

M_B_A12

M_B_A9

M_B_A8

M_B_A10

M_B_A1

M_B_A3

M_B_A5

M_A_A5

M_A_A3

M_A_A9

M_A_A8

M_B_A7

M_B_A6

M_B_A4

M_B_A2

M_B_A15

M_B_A14

M_B_A11

5

RN28

RN28

1

2 3

SRN47J-7-GP

SRN47J-7-GP

RN16

RN16

1

2 3

SRN47J-7-GP

SRN47J-7-GP

M_A_BS#0 5,9

M_A_WE# 5,9

M_A_ODT1 5,9

M_A_CS1#

4

M_A_CAS#

4

M_B_CS1# 5,9

M_B_WE# 5,9

M_B_CAS# 5,9

M_B_BS#0 5,9

M_B_CS2# 5,9

M_A_CS3# 5,9

M_A_A13 5,9

M_A_ODT0 5,9

M_A_CS0# 5,9

M_A_RAS# 5,9

M_A_BS#1 5,9

M_A_A0 5,9

M_B_RAS# 5,9

M_B_CS0# 5,9

M_B_CKE1 5,9

0D9V_S3

M_A_A[15..0] 5,9

M_B_A[15..0] 5,9

M_A_CS1# 5,9

M_A_CAS# 5,9

M_B_BS#2 5,9

M_B_CKE0 5,9

RN15

RN15

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN54

RN54

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN29

RN29

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

8

7

6

8

7

6

8

7

6

M_A_BS#2

M_A_A12

M_A_CS2#

M_A_CKE0

M_A_A11

M_A_A14

M_A_A15

M_A_CKE1

M_B_A13M_B_A0

4

M_A_BS#2 5,9

M_A_CS2# 5,9

M_A_CKE0 5,9

M_A_CKE1 5,9

M_B_ODT0 5,9

M_B_CS3# 5,9

M_B_ODT1 5,9M_B_BS#1 5,9

0D9V_S3

1D8V_S3

1D8V_S3

12

12

12

12

C524

C524

C516

C516

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Put decap near power(0.9V)

and pull-up resistor

12

C526

C526

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C511

C511

SC1000P50V3JN-GP

SC1000P50V3JN-GP

12

C135

C135

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C175

C175

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

12

C176

C176

12

C187

C187

12

C498

C498

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C141

C141

SC1000P50V3JN-GP

SC1000P50V3JN-GP

12

C518

C518

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C505

C505

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C147

C147

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

C189

C189

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C223

C223

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3

C235

C235

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C226

C226

SC1000P50V3JN-GP

SC1000P50V3JN-GP

Place these Caps near DM1

12

C512

C512

Place these Caps near DM2

12

C168

C168

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

Place these Caps near PARALLEL TERMINATION

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C222

C222

12

12

12

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

12

C522

C522

12

C519

C519

12

C134

C134

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C171

C171

SC1000P50V3JN-GP

SC1000P50V3JN-GP

C499

C499

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C188

C188

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C201

C201

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

C136

C136

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C197

C197

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C207

C207

C152

C152

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C178

C178

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C510

C510

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C202

C202

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C190

C190

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C184

C184

C500

C500

SC10P50V2JN-4GP

SC10P50V2JN-4GP

12

C520

C520

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C142

C142

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C203

C203

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C236

C236

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C210

C210

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C217

C217

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C158

C158

DY

DY

2

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C234

C234

12

12

C502

C502

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C208

C208

12

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

SC10P50V2JN-4GP

SC10P50V2JN-4GP

C161

C161

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

1D8V_S3

1D8V_S30D9V_S3

C162

C162

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

SC10P50V2JN-4GP

SC10P50V2JN-4GP

C192

C192

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

C167

C167

C194

C194

12

C508

C508

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C521

C521

SC680P50V2KX-2GP

SC680P50V2KX-2GP

12

C515

C515

SC680P50V2KX-2GP

SC680P50V2KX-2GP

12

C523

C523

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C243

C243

DY

DY

SC10P50V2JN-4GP

SC10P50V2JN-4GP

12

C211

C211

SC680P50V2KX-2GP

SC680P50V2KX-2GP

Cross Moat Cap

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

DDR DAMPING & TERMINATION

DDR DAMPING & TERMINATION

DDR DAMPING & TERMINATION

Orta

Orta

Orta

1

of

of

of

846Tuesday, December 12, 2006

846Tuesday, December 12, 2006

846Tuesday, December 12, 2006

SA

SA

SA

5

DM1

M_B_A[15..0]5,8

D D

M_B_BS#25,8

M_B_BS#05,8

M_B_BS#15,8

M_B_DQ[63..0]5

C C

B B

M_B_DQS#[7..0]5

M_B_DQS[7..0]5

M_B_ODT05,8

VREF_DDR_MEM

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

A A

M_B_ODT15,8

12

C97

C97

12

C96

C96

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

DM1

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16/BA2

107

BA0

106

BA1

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

11

/DQS0

29

/DQS1

49

/DQS2

68

/DQS3

129

/DQS4

146

/DQS5

167

/DQS6

186

/DQS7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

114

ODT0

119

ODT1

1

VREF

2

VSS

202

GND

DDR2-200P-22-GP-U1

DDR2-200P-22-GP-U1

108

/RAS

109

/WE

113

/CAS

110

/CS0

115

/CS1

79

CKE0

80

CKE1

30

CK0

32

/CK0

164

CK1

166

/CK1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

195

SDA

197

SCL

199

VDDSPD

198

SA0

200

SA1

50

NC#50

69

NC#69

83

NC#83

120

NC#120

NC#163/TEST

62.10017.A61

62.10017.A61

163

81

VDD

82

VDD

87

VDD

88

VDD

95

VDD

96

VDD

103

VDD

104

VDD

111

VDD

112

VDD

117

VDD

118

VDD

3

VSS

8

VSS

9

VSS

12

VSS

15

VSS

18

VSS

21

VSS

24

VSS

27

VSS

28

VSS

33

VSS

34

VSS

39

VSS

40

VSS

41

VSS

42

VSS

47

VSS

48

VSS

53

VSS

54

VSS

59

NORMAL TYPE

VSS

60

VSS

65

VSS

66

VSS

71

VSS

72

VSS

77

VSS

78

VSS

121

VSS

122

VSS

127

VSS

128

VSS

132

VSS

133

VSS

138

VSS

139

VSS

144

VSS

145

VSS

149

VSS

150

VSS

155

VSS

156

VSS

161

VSS

162

VSS

165

VSS

168

VSS

171

VSS

172

VSS

177

VSS

178

VSS

183

VSS

184

VSS

187

VSS

190

VSS

193

VSS

196

VSS

201

GND

High 9.2mm

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

DIMM2_SA0

4

M_B_CS0# 5,8

M_B_CS1# 5,8

M_B_CKE0 5,8

M_B_CKE1 5,8

SMBC0_SB 3,19

R156

R156

10KR2J-3-GP

10KR2J-3-GP

M_B_CS2# 5,8

M_B_CS3# 5,8

1D8V_S3

Place near CPU

1D8V_S3

M_B_RAS# 5,8

M_B_WE# 5,8

M_B_CAS# 5,8

M_B_CLK_DDR1 5

M_B_CLK_DDR1# 5

M_B_CLK_DDR2 5

M_B_CLK_DDR2# 5

M_B_DM[7..0] 5

SMBD0_SB 3,19

12

M_B_CLK_DDR1

12

C119

C119

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

M_B_CLK_DDR1#

M_B_CLK_DDR2

12

C263

C263

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

M_B_CLK_DDR2#

C561

C561

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

?

DDR_VREF

12

C110

C110

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

RN13

RN13

1

4

2 3

SRN1KJ-7-GP

SRN1KJ-7-GP

C100

C100

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

C562

C562

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

VREF_DDR_MEM

12

C108

C108

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

3D3V_S0

3

VREF_DDR_MEM

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

2

DM2

DM2

MH1

M_A_A[15..0]5,8

M_A_BS#25,8

M_A_BS#05,8

M_A_BS#15,8

M_A_DQ[63..0]5

M_A_CS2#5,8

M_A_CS3#5,8

M_A_CS0#5,8

M_A_CS1#5,8

M_A_CKE05,8

M_A_CKE15,8

M_A_RAS#5,8

M_A_CAS#5,8

M_A_WE#5,8

M_A_ODT05,8

M_A_ODT15,8

12

12

C101

C99

C99

C101

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

SMBC0_SB

SMBD0_SB

MH1

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC#50

69

NC#69

83

NC#83

120

NC#120

163

NC#163/TEST

110

CS0#

115

CS1#

79

CKE0

80

CKE1

108

RAS#

113

CAS#

109

WE#

197

SCL

195

SDA

114

ODT0

119

ODT1

1

VREF

201

GND

SKT-SODIMM20020U3GP

SKT-SODIMM20020U3GP

62.10017.661

62.10017.661

Hi 9.2 mm

Main Source: 62.10017.A61

High 5.2mm

MH2

MH2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

CK0

CK0#

CK1

CK1#

SA0

SA1

VDD_SPD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NORMAL TYPE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

M_A_DQS0

13

M_A_DQS1

31

M_A_DQS2

51

M_A_DQS3

70

M_A_DQS4

131

M_A_DQS5

148

M_A_DQS6

169

M_A_DQS7

188

M_A_DQS#0

11

M_A_DQS#1

29

M_A_DQS#2

49

M_A_DQS#3

68

M_A_DQS#4

129

M_A_DQS#5

146

M_A_DQS#6

167

M_A_DQS#7

186

M_A_DM0

10

M_A_DM1

26

M_A_DM2

52

M_A_DM3

67

M_A_DM4

130

M_A_DM5

147

M_A_DM6

170

M_A_DM7

185

30

32

164

166

198

200

199

81

82

87

88

95

96

103

104

111

112

117

118

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

59

60

65

66

71

72

77

78

121

122

127

128

132

133

138

139

144

145

149

150

155

156

161

162

165

168

171

172

177

178

183

184

187

190

193

196

202

1D8V_S3

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet

Date: Sheet

M_A_DQS[7..0] 5

M_A_DQS#[7..0] 5

M_A_DM[7..0] 5

M_A_CLK_DDR1 5

M_A_CLK_DDR1# 5

M_A_CLK_DDR2 5

M_A_CLK_DDR2# 5

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Place near CPU

DDR SO-DIMM SKT

DDR SO-DIMM SKT

DDR SO-DIMM SKT

Orta

Orta

Orta

1

3D3V_S0

12

C271

C271

M_A_CLK_DDR1

12

C132

C132

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

M_A_CLK_DDR1#

M_A_CLK_DDR2

12

C237

C237

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

M_A_CLK_DDR2#

12

C270

C270

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

946Tuesday, December 12, 2006

946Tuesday, December 12, 2006

946Tuesday, December 12, 2006

SA

SA

SA

of

of

LAYOUT: Locate close to DIMM

5

4

3

2

1

5

D D

4

3

2

1

CLAW HAMMER TO NB NB TO CLAW HAMMER