Acer Nitro 5 Schematics

A

1 1

B

C

D

E

Compal Confidential

2 2

C5V08/C5V09/D5PR8 Schematics Document

AMD Bristol Ridge/Stoney Ridge Platform

APU 15W/35W + Radeon R17M-P1-50/70/G1-70 25W/40W/50W

3 3

LA-E903P REV:1.A

2017-04-18

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

COVER PAGE

COVER PAGE

COVER PAGE

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

1 50Tuesday, May 02, 2017

1 50Tuesday, May 02, 2017

1 50Tuesday, May 02, 2017

E

1.A

1.A

1.A

A

Compal Confidential

Model Name : Wartortle_BS

B

C

D

E

(Channel A)

1 1

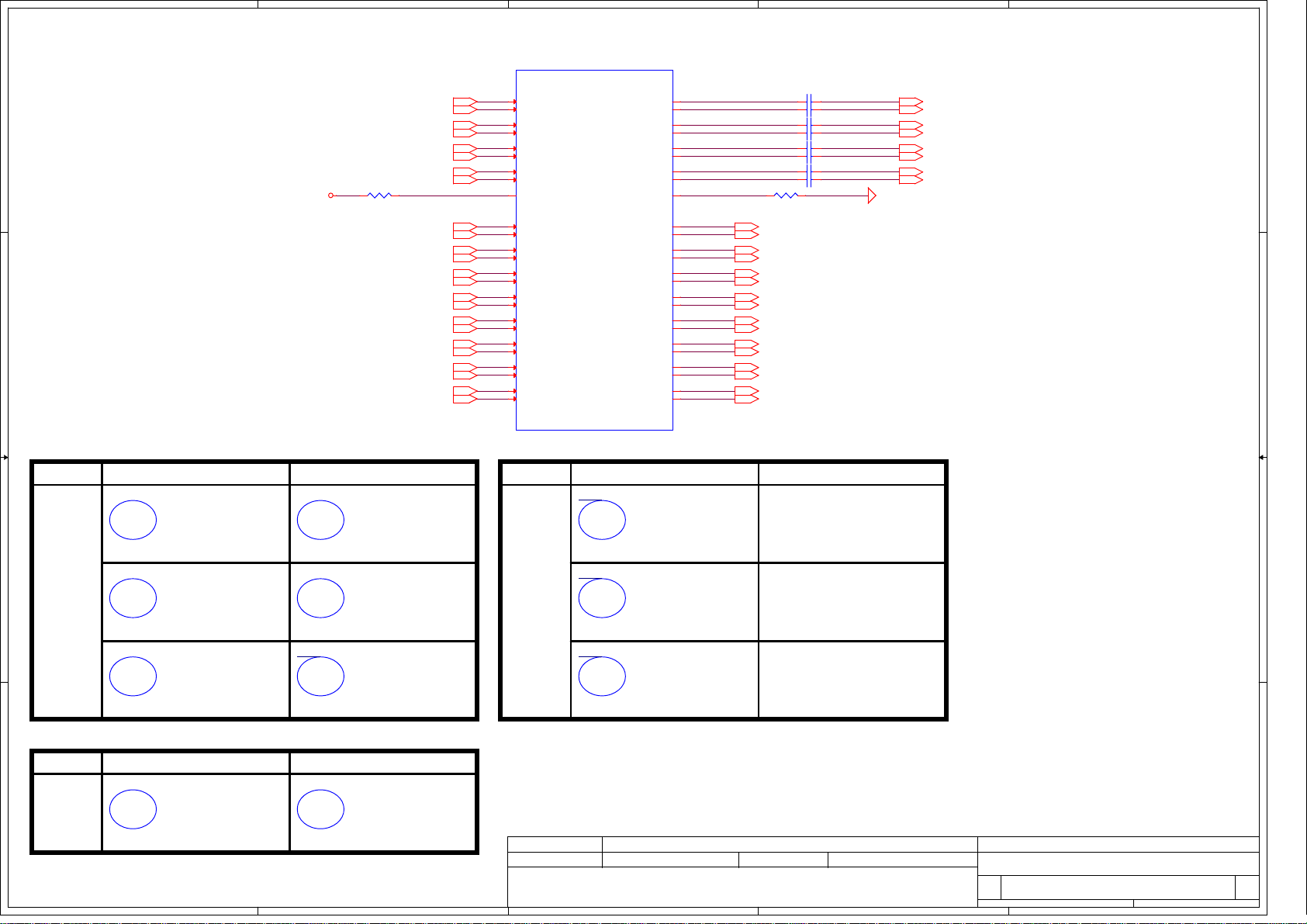

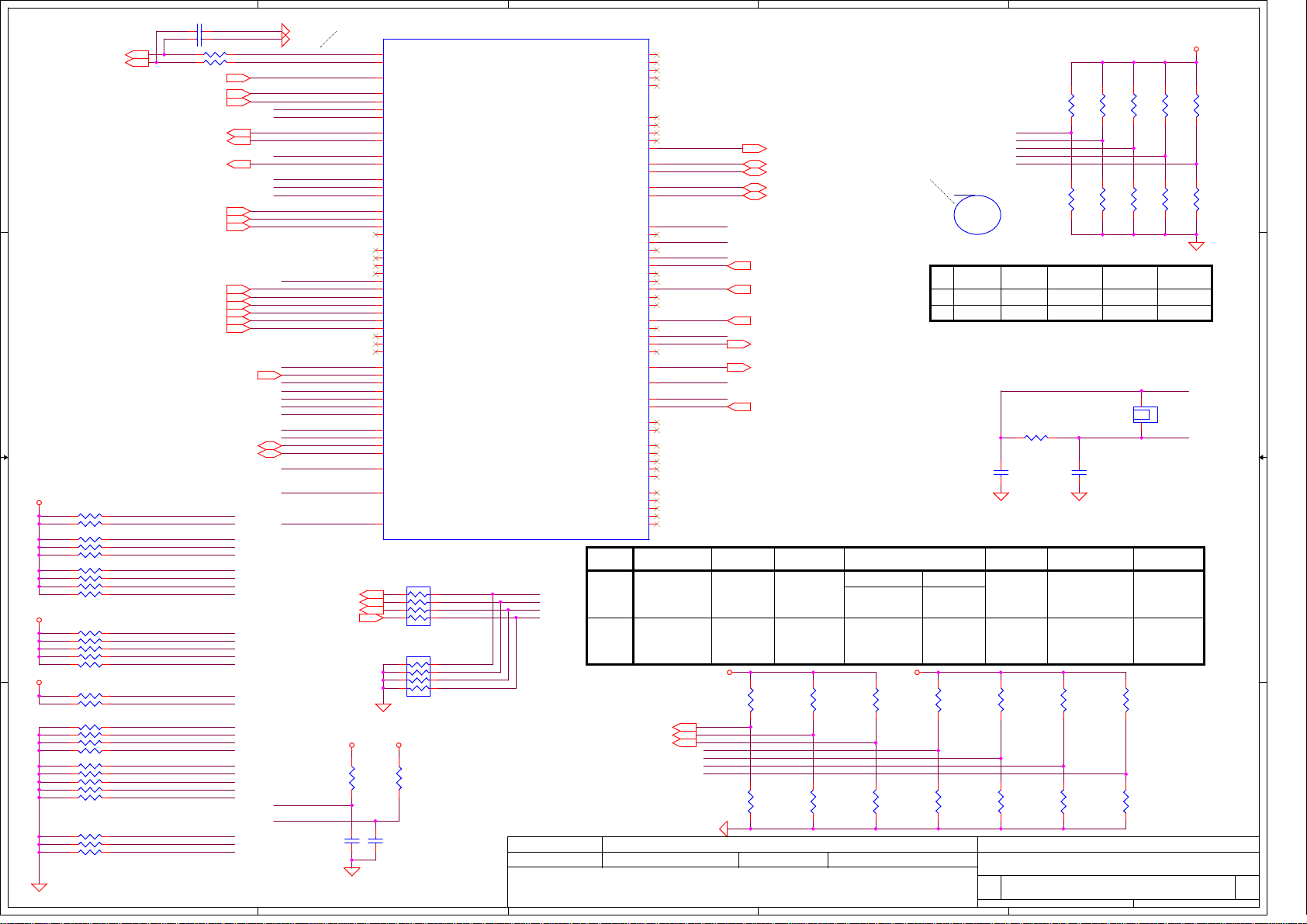

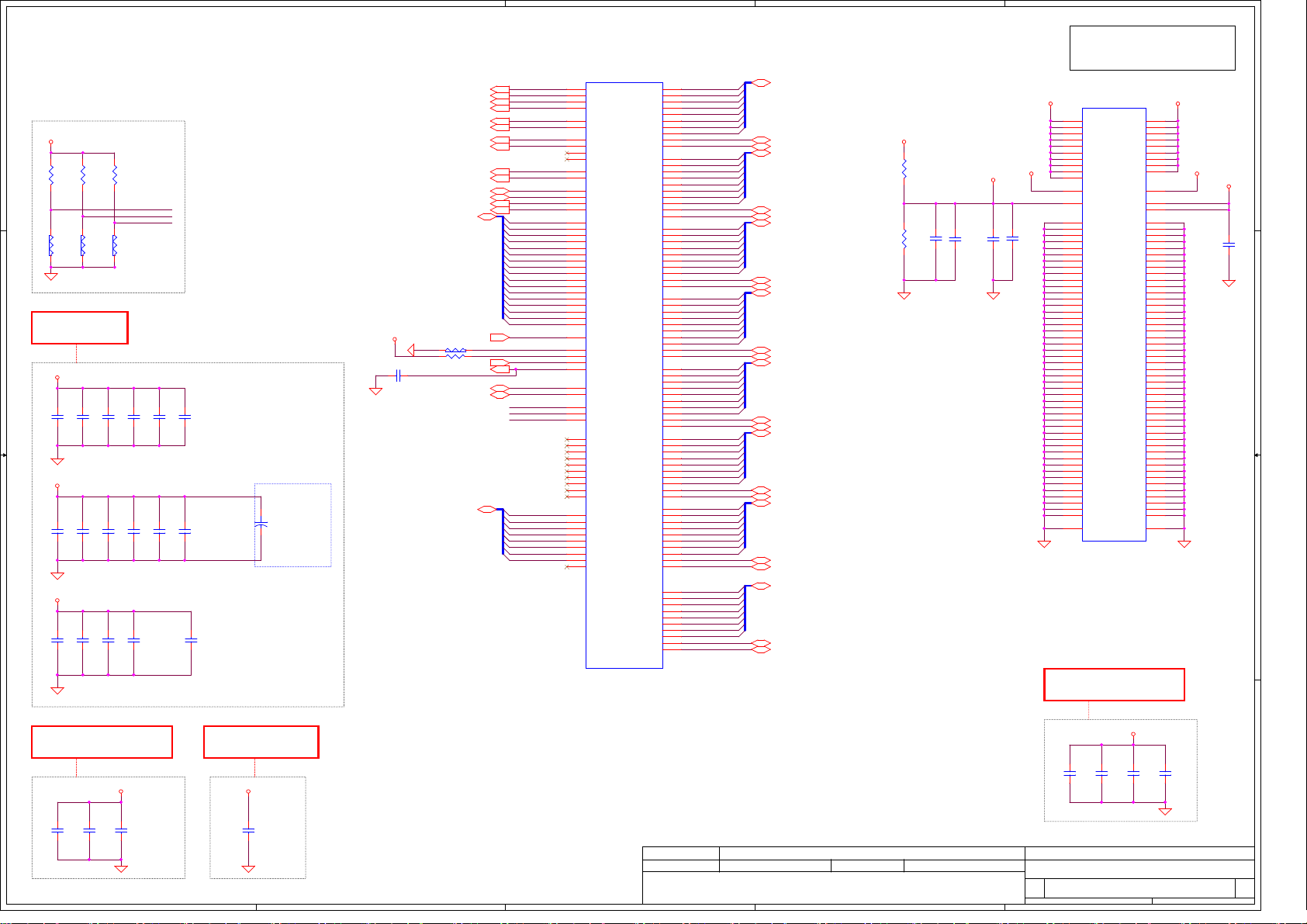

GPU

S4 Package

PEG x8

RX540 : R17M-P1-50

RX550 : R17M-P1-70

RX560 : R17M-G1-70

page 15~23

Display Port

USB2 .0

eDP Conn.

page 27 page 26

Port 3

2 2

Port 1Port 0

HDMI Conn.

AMD

BRISTOL RIDGE

STONEY RIDGE

Co-Lay

Memory BUS(DDR4)

1.2V DDRIV

1866Mhz

USB2 .0

S/B

2.0 Conn.

USB3 .0

260pin DDRIV SO-DIMM

Port 1

page 31 page 31

S/B

2.0 Conn.

page 13

Port 2Port 0

WLAN/BT

Combo

page 29

Port 1,2

page 32

Type-C

3.0 Conn.

AMD FP4 APU

PCIE

BGA 968-balls

Port 2, 3

page 30

SSD

NGFF Conn.

Port 0

LAN+CR

RTL8411

page 28

USB2 .0

Port 2

Transformer

RJ45

page 28 page 28

3 3

Fan Control

page 35

Card Reader

Conn.

Port 1

WLAN/BT

NGFF Conn.

page 29

page 10

BIOS (8M)

SPI

page 33

Discrete TPM

page 6~12

LPC

ENE

KBC9022

page 24 page 30

PS2

page 33

HD Audio(AZ)

SATA III

I2C

Port 1

G-Sensor

(Reserve)

Port 3

PTP

(BR/SR)

HDD

Conn.

page 33

Port 0

page 30

Port 1

SSD

NGFF Conn.

page 30

(Channel B) *SR only Ch B

260pin DDRIV SO-DIMM

Port 3

Camera

page 27

Port 3

page 31

M/B

3.0 Conn.

Port 5

Audio

ALC255

page 27

Int. DMIC

on Camera

Int. Speaker

Conn.

Port 7

page 34

page 34

page 14

page 31

UAJ

on Sub/B

Int.KBD

RTC CKT.

page 11

Power On/Off CKT.

DC/DC Interface CKT.

4 4

Power Circuit DC/DC

VRAM Config Table

page 33

page 25

page 38~51

page 23

A

Sub Board

LS-E901 USB2.0/B

LS-E892 Hall Sensor/B

page 31

page 33

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

D

Date : Sheet of

Compal Electronics, Inc.

BLOCK DIAGRAMS

BLOCK DIAGRAMS

BLOCK DIAGRAMS

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

E

2 50Tuesday, May 02, 2017

2 50Tuesday, May 02, 2017

2 50Tuesday, May 02, 2017

1.A

1.A

1.A

5

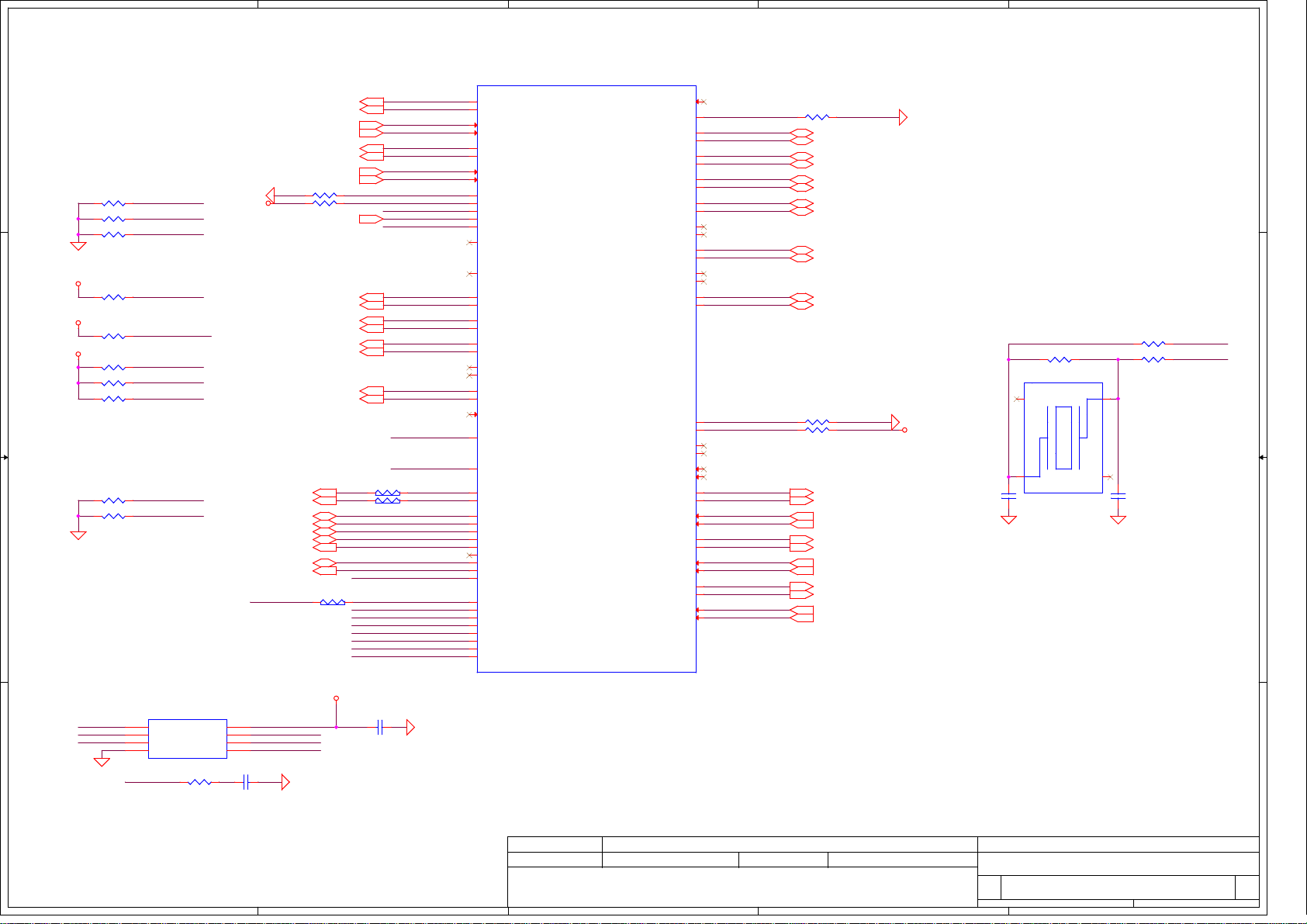

PJP101

AC-IN

PU301

20493mA

+19V B

5416mA

2843mA

449m A

514m A

2311mA

+19V _VIN

+17. 4V_BA TT

D D

PJP201

DC-IN

C C

PU801

PU901

PU501

PU601

PU401

+APU _CORE

+APU _CORE_ NB

+APU _GFX

6500mA

+1.2 V

1200mA

+0.6 VS

9300mA

+0.9 5VALW

(+1. 05VAL W)

+3VL P

KB9022

B B

14000mA3685mA 6500mA

+INV PWR_B +

+5VA LW

Panel BackLight

PU401

1500mA

2969mA

L11

379m A

427m A

A A

To VGA

+VGA _CORE

+VDD CI/VDD _08

+1.3 5VSDG PU

13305mA

4

+3VA LW

1753mA

212m A

7285mA

PU602

PU902

+1.8 VALW

3213mA

+0.7 75VAL W

U2

+3VS

+5VS

8500mA

1700mA

304m A

To VGA

1013mA

JRTC1

PU502

U2606

U1302

10mA

JUSB3

+0.9 5VS

U4

To VGA

+1.8 VS

U3

U102

RM9

RL2

R463

U13

R212

U8

RW2

RW1

U45

R110

RS10

JPA8

U25

RO3

RF1/RF7

JPA1

U73

3

+RTC _APU_ R

+2.5 V

55000mA

17000mA

45000mA

200m A

1500mA

1500mA +0.9 5VS_G FX

7000mA

3000mA

200m A

500m A

200m A

800m A

900m A

45mA

400m A

3500mA

1200mA

125m A

3500mA

1400mA

200m A

1500mA

1500mA

50mA

1mA

200m A

290m A

250m A

3000mA

2000mA

2500mA

2000mA

2000mA

1500mA

1000mA

+VCC _FAN1

+APU _CORE

+APU _CORE_ NB

+APU _GFX

+3VS

+1.8 VS

+0.9 5VS

+1.2 V

+3VA LW

+1.8 VALW

+1.8 VS

+0.9 5VALW

+APU _CORE_ FCH

+RTC _APU_ R

+2.5 V

+1.2 V

+0.6 VS

+3VS _SSD_N GFF

+3V_ LAN

+TP_ VCC

+3VS _WLAN

+LCD VDD

+3VS _TPM

+3VA LW_TP M

+3VS _CAM

+1.2 V_HDM I

+3VA LW_CC

+5VA LW_CC

+USB 3_VCC A

+5VS _HDD

+VCC _FAN2

+VDD A

+5VS _DISP

2

APU Power Rail

VDDCR_CPU @0.75-1.5V

VDDCR_NB @0.75-1.2V

VDDCR_GFX @0.75-1.2V

VDD_33 @0.2A

VDD_18 @1.5A

VDDP_GFX @1.5A

VDDP @7.0A

VDDIO_MEM_S3 @3A

VDD_33_S5 @0.2A

VDD_18_S5 @0.5A

VDDIO_AUDIO @0.2A

VDDP_S5 @0.8A

VDDCR_FCH_S5 @0.9A

VDDBT_RTC_G @0.045A

DDR4 SO-DIMM/MEM-DOWN

+2.5V

+1.2V

+0.6VS

SATA Redriver

SSD

LAN RTL8411

Touch Pad

WLAN

Panel Logic

TPM

Camera

HDMI Redriver

Type C

USB3.0

USB/B

HDD

FAN1/FAN 2

Audio

HDMI Logic

Group C, S0 domain

Group B, S0 domain

Group B, S3 domain

Group A, S5 domain

R17M-P1-50/70

2969mA

+19V B

427m A

+19V B

10mA

+3VS

1013mA

+1.8 VALW

PU1401

PU1402

PU1001

UV7

UV8

6000mA

47000mA

10mA

1013mA

+VGA _CORE

+VDD CI+19V B 8000mA379m A

2000mA

+1.3 5VSDG PU

+3VS DGPU

+1.8 VSDGP U

4000mA

+1.3 5VSDG PU

1

GPU Power Rail

VDDC @47A

@1.2V

VDDCI+VDD_08 @8A

VMEMIO @2A

VDD_GPIO33 @0.01A

VDD_18 @1A

TSVDD @13mA

VRAM x4pcs

@0.8~0.9 V

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHE ET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHE ET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHE ET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

POWER MAP

POWER MAP

POWER MAP

Document Number Re v

Document Number Re v

Document Number Re v

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

1

3 50Tuesday, May 02, 2017

3 50Tuesday, May 02, 2017

3 50Tuesday, May 02, 2017

1.A

1.A

1.A

5

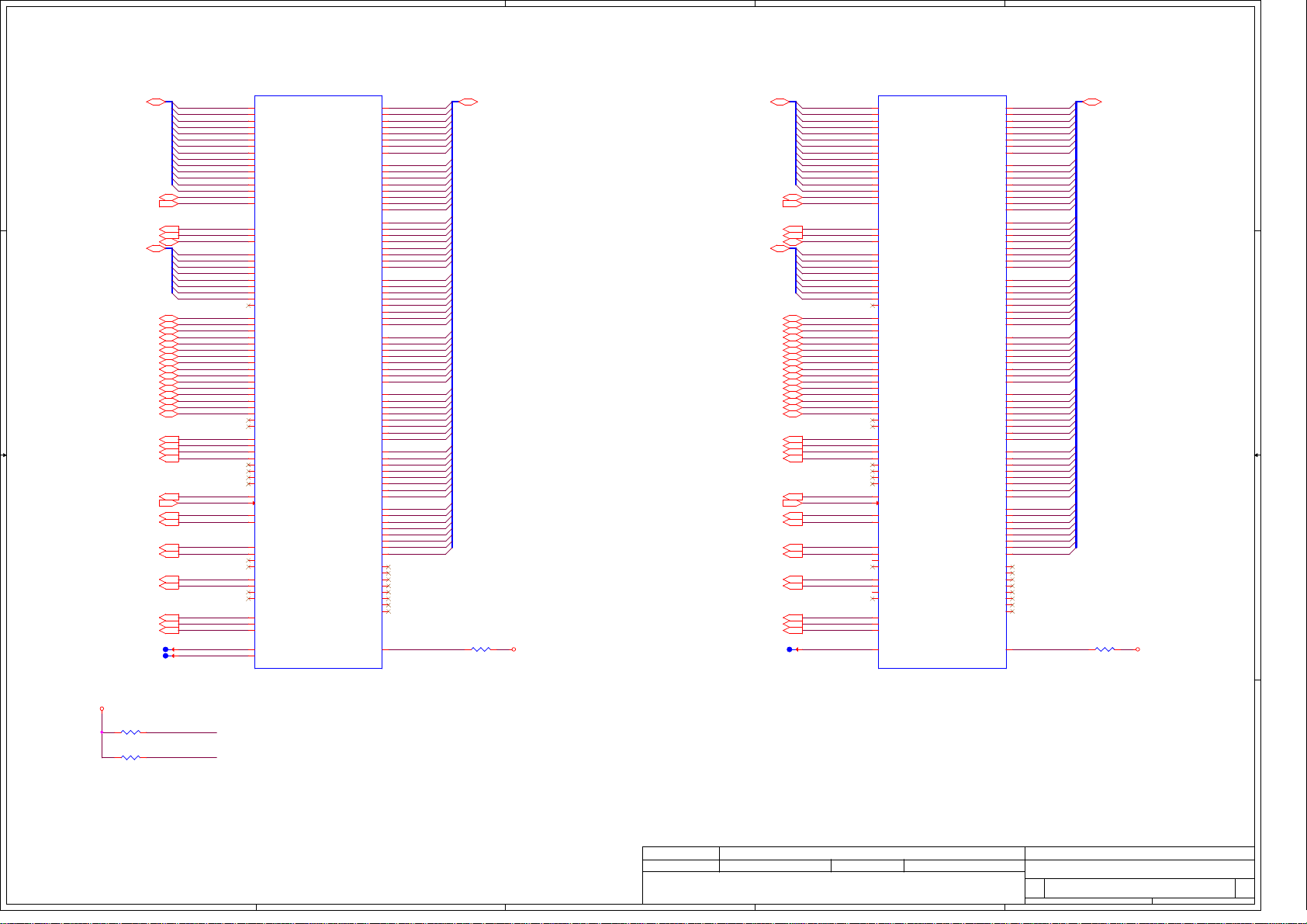

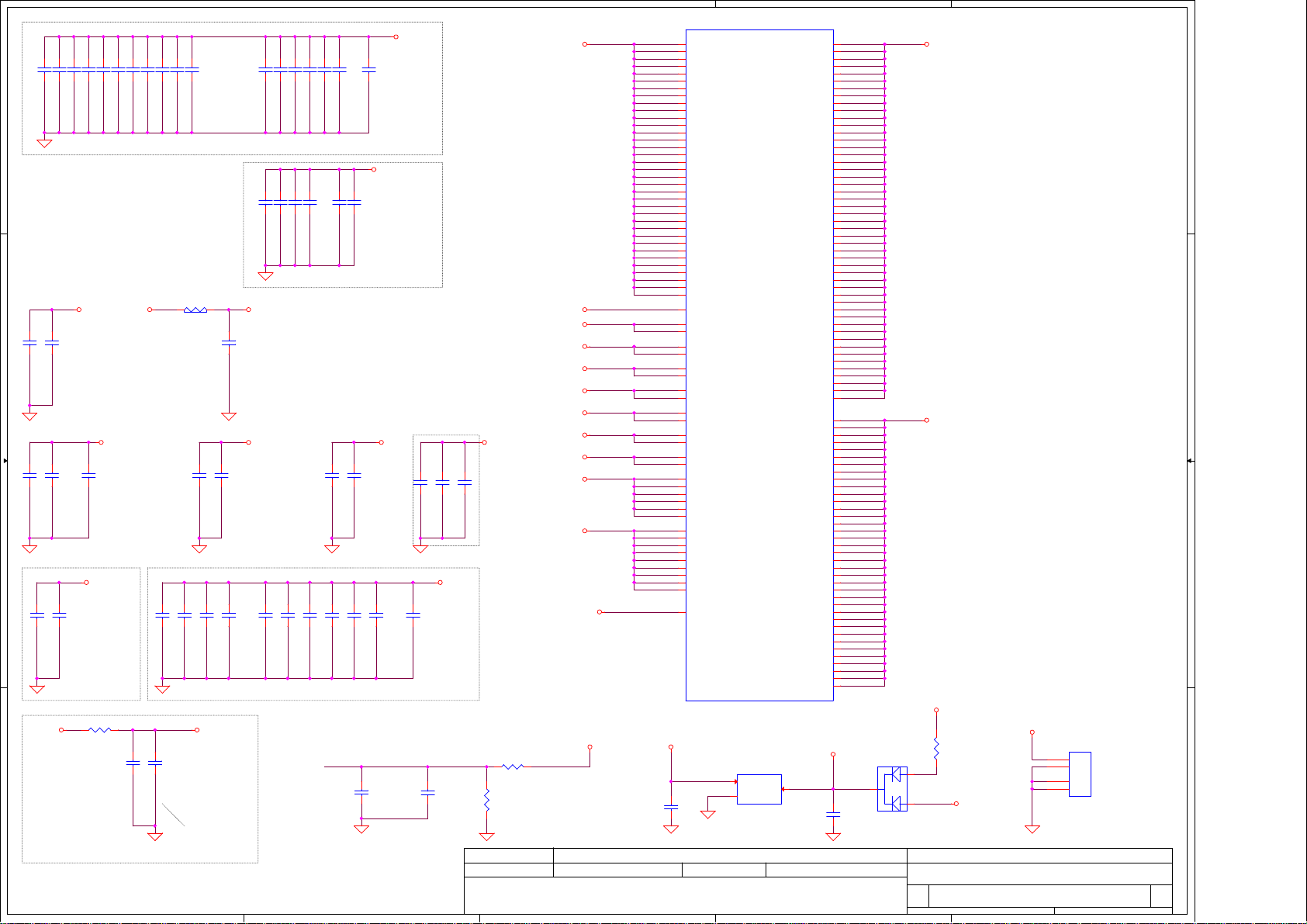

Bristol/Stoney Platform Power Sequence

4

3

2

1

AC-IN G3 --> S0

+3VLP

D D

ACIN

EC_ON

+5VALW

ON/OFFBTN#

3V_EN

+3VALW

+0.775VALW

0.95_1.8VALW_PWREN

+1.8VALW

+0.95VALW

PBTN_OUT#

EC_RSMRST#

SLP_S5#

SLP_S3#

SYSON

+1.2V

C C

+2.5V

SUSP#

+5VS

+3VS

+1.8VS

+0.6VS

KBRST#

0.95VS_PWR_EN#

+0.95VS

VR_ON

+APU_CORE

+APU_CORE_NB

+APU_GFX

VGATE

SYS_PWRGD_EC

APU_PWROK

LPC_RST#

B B

APU_PCIE_RST#

APU_RST#

VGA Sequence

PE_GPIO1

VGA_ON

+3VSDGPU

+1.8VSDGPU

VGA_ON_B

+VGA_CORE

+VDDCI

DGPU_PWROK

+1.35VSDGPU

PE_GPIO0

PLT_RST_VGA#

14.82us

227us

3.348ms, Tr = 637us

4.32us

91ms

91ms

160ms

1.033ms, Tr = 670us

1.108ms, Tr = 364us

2.385ms, Tr = 691us

841us, Tr = 382us

7ms

114ms

100ms

120us

120us

120ms

807us, Tr = 239us

1.456ms, Tr = 1.025ms

20ms

770us, Tr = 616us

823us, Tr = 599us

290us, Tr = 193us

20ms

19.97ms

317us, Tr = 146us 307us, Tr = 138us139us, Tf = 1.419ms 133us, Tf = 955us

20.2ms

1.089ms, Tr = 293us

1.103, Tr = 320us

1.112ms, Tr = 318us

1.254ms

39.81ms

14.61ms

13.38ms

1.005ms

6.709ms

228ms

1.399ms

2.769ms, Tr = 1.598ms 2.782ms, Tr = 1.598ms

6.571ms

5.880ms, Tr = 37.32us

5.943ms, Tr = 35.7us Tf = 16.42ms

5.976ms

Tr = 325us Tr = 257usTf = 8.199ms Tf = 9.667ms

206ms

1.008ns

S0 --> S3 S3 --> S0

57.1ms

Tf = 13.95ms

Tf = 21.44ms

Tf = 8.428ms

57.1ms

58.11ms

88.45ms

Tf = 4.119ms

Tf = 817us

Tf = 807us

28ms

1.418ms

2.06ms

108us

13.51ns

3.145ms

6.158ms

Tf = 754us

Tf = 3.864ms

10.6us

Tf = 5.215ms

395ns

16.7ns

6.871ns

14.88ms

733us, Tr = 575us

789us, Tr = 551us

282us, Tr = 174us

8.25us, Tr = 6.9us10.14us, Tr = 9.399us Tf = 662us Tf = 677us

19.98ms

20.22ms

21.37ms

1.098ms, Tr = 301us

1.083, Tr = 300us

1.108ms, Tr = 306us

1.249ms

39.61ms

14.6ms

13.4ms

1.004ms

6.708ms

113.9ms

1.404ms

3.568ms, Tr = 918us3.553ms, Tr = 917us

6.545ms

5.840ms, Tr = 37.84us

5.932ms, Tr = 35.6us

5.976ms

197.2ms

7.374ns

S0 --> S5

61ms

Tf = 1.135ms

Tf = 11.64ms

53.3ms

Tf = 14.83ms

Tf = 23.94ms

Tf = 8.909ms

53.27ms

53.3ms

83.5ms

Tf = 5.572ms

Tf = 698us

Tf = 803us

23.17ms

1.416ms

2.072ms

97us

36.63ns

3.001ms

6.039ms

Tf = 685us

Tf = 3.659ms

13.21us

Tf = 5.215ms

Tf = 16.42ms

390.7ns

17.79ns

8.908ns

8.532s

8.542s

Tf = 19.35ms

Tf = 9.193ms

Tf = 3.951ms

Tf = 14.24mss

9.041s

9.042s

+3VLP

ACIN

EC_ON

+5VALW

ON/OFFBTN#

3V_EN

+3VALW

+0.775VALW

0.95_1.8VALW_PWREN

+1.8VALW

+0.95VALW

PBTN_OUT#

EC_RSMRST#

SLP_S5#

SLP_S3#

SYSON

+1.2V

+2.5V

SUSP#

+5VS

+3VS

+1.8VS

+0.6VS

KBRST#

0.95VS_PWR_EN#

+0.95VS

VR_ON

+APU_CORE

+APU_CORE_NB

+APU_GFX

VGATE

SYS_PWRGD_EC

APU_PWROK

LPC_RST#

APU_PCIE_RST#

APU_RST#

VGA Sequence

PE_GPIO1

VGA_ON

+3VSDGPU

+1.8VSDGPU

VGA_ON_B

+VGA_CORE

+VDDCI

DGPU_PWROK

+1.35VSDGPU

PE_GPIO0

PLT_RST_VGA#

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

Document Number Re v

Document Number Rev

Document Number Rev

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

1

4 50Tuesday, May 02, 2017

4 50Tuesday, May 02, 2017

4 50Tuesday, May 02, 2017

1.A

1.A

1.A

A

B

C

D

E

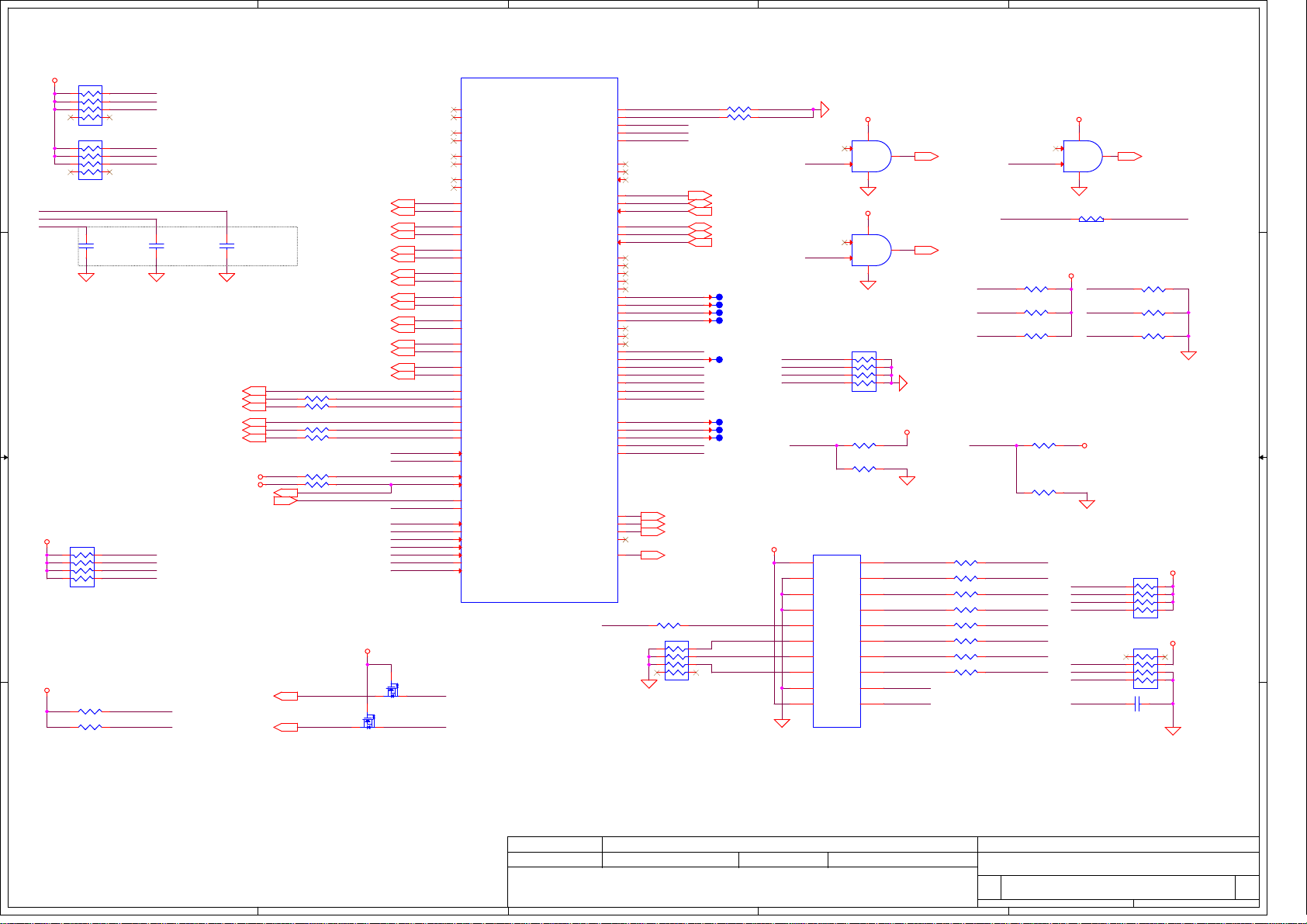

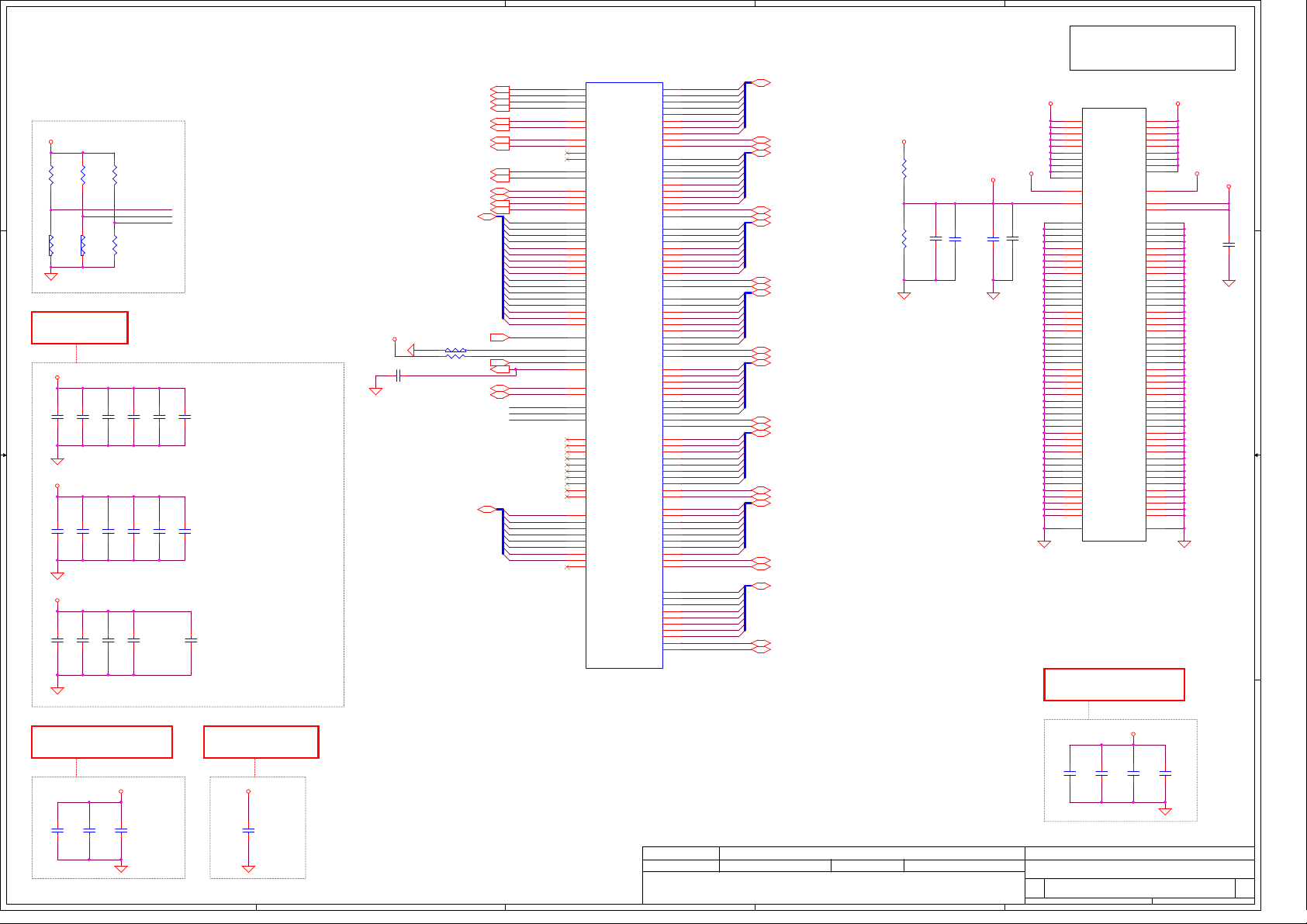

Voltage Rails

Power Plane

+19V_VIN

+19VB

+APU_CORE

1 1

2 2

+APU_CORE_GFX

+APU_CORE_FCH

+0.95VALW

+0.95VS

+1.8VALW

+1.8VS

+2.5V

+1.2V

+0.6VS

+3VALW

+3VS

+5VALW

+5VS

+RTC_APU

+3VSDGPU

+1.8VSDGPU

+VDDCI

+VGA_CORE

APU SMBus/I2C Address Table

Master

I2C Port 0

(+1.8VS)

I2C Port 1

(+1.8VS)

I2C Port 2

(+3VS)

SBMus Port 0

3 3

(+3VS)

I2C Port 3

(+3VALW)

SMBus Port 1

(+3VALW)

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for APU

Voltage for On-die VGA of APU

Voltage for GFX

Fusion Controller Hub Power Supply

0.95V always on power rail

0.95V switched power rail

1.8V always on power rail

1.8V switched power rail

2.5V power rail for APU and DDR

1.2V power rail for APU and DDR

0.6V switched power rail for DDR terminator

0.775V always on power rail+0.775VALW

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

VGA power

VGA power

VGA power

VGA power

Device

G-Sensor

(Reserver)

JDIMM1

JDIMM2

PTP

(Synaptics)

PTP

(ELAN)

Address[7:1]

0001 1000b

18h

0101 0000b

50h

0101 0001b

51h

0010 1100b

2Ch

0001 1111b

15h

Address [7:0]

Write

0011 0000b

30h

1010 0000b

A0h

1010 0010b

A2h

0101 1000b

58h

0011 1110b

3Eh

ON

ON

ON+APU_CORE_NB

ON

ON

ON

ON

ON ON

ON

ON ON

ON

ON

ON

ON

ON

ON

ON

S5S3S0

ONONON

ON ON

OFF

OFF

OFF

OFF

OFF OFF

ONONON

OFF

ONON

OFF OFF

OFF

ON

OFF OFF

OFF

OFF

ONON

OFF OFF

OFF

OFF

ONON

OFF OFF

AC:ON

ON

DC:OFF

OFF OFF

ONONON

OFF OFF

OFFOFF

OFFOFF

OFFOFF

Read

0011 0001b

31h

1010 0001b

A1h

1010 0011b

A3h

0101 1001b

59h

0011 1111b

3Fh

EC SMBus Address Table

SMBus Port 1

(+3VALW)

4 4

SMBus Port 2

(+3VS)

Smart Battery

Charger IC

(BQ24735)

APU Temp.

(TSI)

GPU Temp.

A

0000 1011b

0Bh

0000 1001b

09h

0100 1100b

4Ch

0100 0001b

41h

0001 0110b

16h

0001 0010b

12h

1001 1000b

98h

1000 0010b

82h

0001 0111b

17h

0001 0011b

13h

1001 1001b

99h

1000 0011b

83h

B

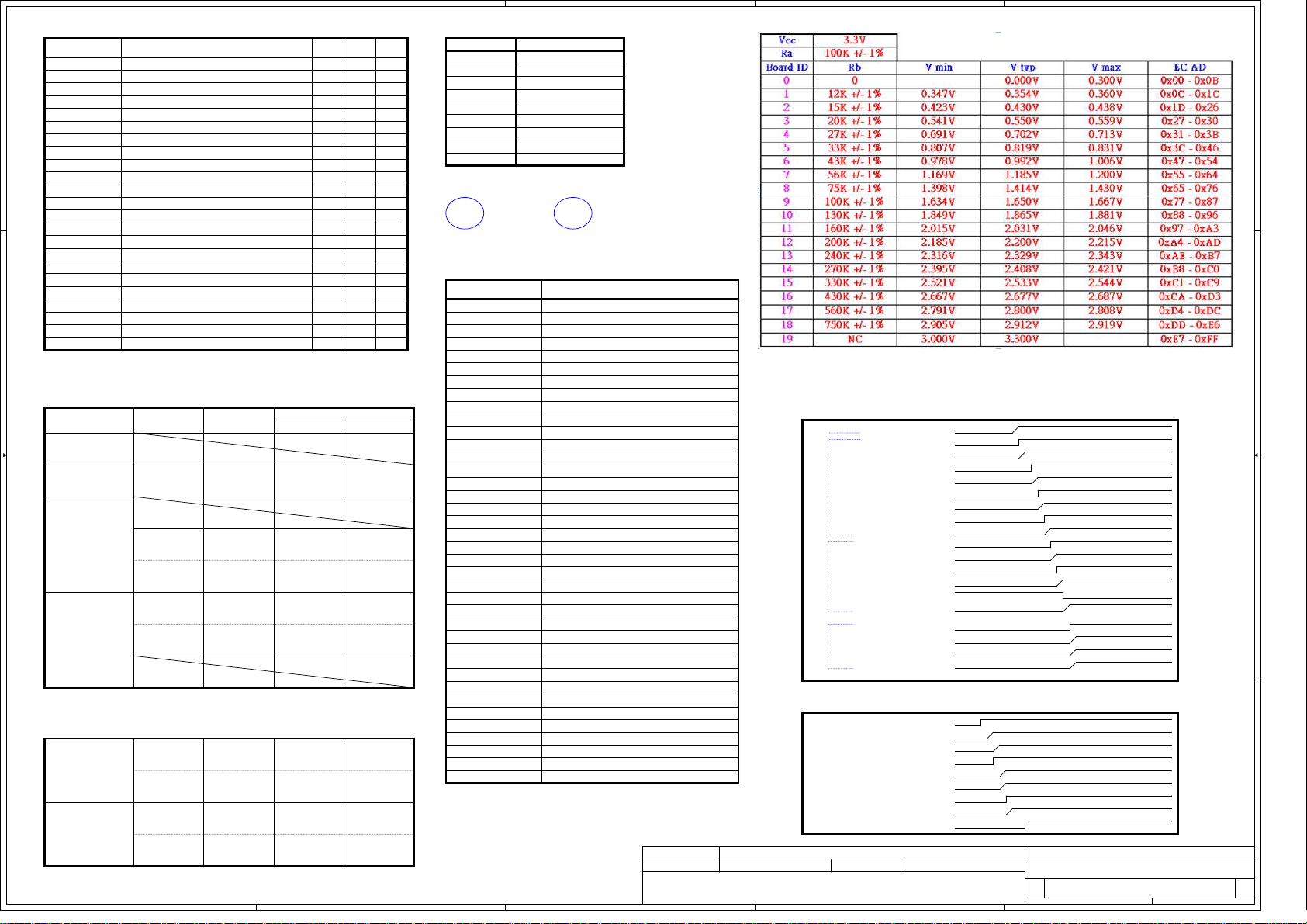

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

8

ZZZ

PCB

DA8001C0010

PCB 218 LA-E903P REV1 MB 2

@

PCB Revision

C5V08 EVT

C5V08 DVT

C5V08 PVT

C5V08 MP

D5PR8 DVT

D5PR8 PVT

D5PR8 MP

D5PR8_PVT_32P

D5PR8_MP_32P

ZZZ

PCB

DAZ21800201

PCB C5V08 LA-E903P LS-E901P/E892P

BOM Structure Table

BTO ItemBOM Structure

@

@EMC@

EMC@

45@

CONN@

JP@

RS@

TP@

TPM@

PCIE@

SATA@

T1@

T3@

GS@

LDO@

SWR@

2D@

PAR@

TI@

EVT@

CHG@

NCHG@

UMA@

EA@

VX@

DIS@

V2G_S@

V2G_H@

V2G_M@

RX540@

RX550@

RX560@

Unpop

EMI/ESD Unpop

EMI/ESD pop

HDMI Royalty

ME Connector

Jump

R-Short

Test Point

TPM Pop

PCIE SSD Device

SATA SSD Device

Bristol Pop

Stoney Pop

G-Sensor Circuits

RTL8411 LDO mode

RTL8411 Switching mode

For 2 SO-DIMM use

SATA Redriver PARADE solution

SATA Redriver TI solution

Only use on EVT

USB Charger

Non-USB Charger

UMA Config

CPU PN Refer p.6

EA Series

VX Series

VGA Circuits Pop

VRAM use SAMSUNG

VRAM use HYNIX

VRAM use MICRON

GPU PN Refer p.23

R17M-P1-50 GPU

R17M-P1-70 GPU

R17M-G1-70 GPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Board ID / SKU ID Table for AD channel

POWER SEQUENCE

G-A

G-B

G-C

G-D

+RTC BATT

EC_O N

+5VA LW

3V_E N

+3VA LW/+ 0.775VALW

0.95 _1.8VALW_PWRE N

+1.8 VALW /+0.95VAL W

S5_M UX_CTRL

+APU _COR E_FC H

SYSO N

+1.2 V/+2 .5V

SUSP #

+5VS /+3V S/+1.8VS/ +0.6 VS

0.95 VS_PWR_EN#

+0.9 5VS

VR_O N

+APU _COR E

+APU _COR E_NB

+APU _GFX

VGA POWER SEQUENCE

PE_G PIO1/VGA_ON

+3VS DGPU

+1.8 VSDG PU

VGA_ ON_B

+VGA _COR E

+VDD CI

DGPU _PWROK

+1.3 5VSD GPU

PE_G PIO0

Compal Secret Data

Compal Secret Data

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

NOTES LIST

NOTES LIST

NOTES LIST

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

E

5 50Tuesday, May 02, 2017

5 50Tuesday, May 02, 2017

5 50Tuesday, May 02, 2017

1.A

1.A

1.A

5

D D

R542 196_0402_1%

+0.95VS

4

PCIE_ARX_DTX_P0<28>

PCIE_ARX_DTX_N0<28>

PCIE_ARX_DTX_P1<29>

PCIE_ARX_DTX_N1<29>

PCIE_ARX_DTX_P2<30>

PCIE_ARX_DTX_N2<30>

PCIE_ARX_DTX_P3<30>

PCIE_ARX_DTX_N3<30>

1 2

U10

U9

T6

T5

T9

T8

P7

P6

U7

UAPU1B

P_GPP_RXP[0]

P_GPP_RXN[0]

P_GPP_RXP[1]

P_GPP_RXN[1]

P_GPP_RXP[2]

P_GPP_RXN[2]

P_GPP_RXP[3]

P_GPP_RXN[3]

P_ZVDDP

3

@

PCIE

PCIE_ATX_DRX_P0

LAN + CR

WLAN

PCIE SSD

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]

P_GPP_TXN[2]

P_GPP_TXP[3]

P_GPP_TXN[3]

P_ZVSS/P_RX_ZVDDP

R1

PCIE_ATX_DRX_N0

R2

PCIE_ATX_DRX_P1

R4

PCIE_ATX_DRX_N1

R3

PCIE_ATX_DRX_P2

N1

PCIE_ATX_DRX_N2

N2

PCIE_ATX_DRX_P3

N4

PCIE_ATX_DRX_N3

N3

U6

P_ZVSSP_ZVDDP

R541 196_0402_1%

1 2

C19 .1U_0402_16V7K

1 2

C20 .1U_0402_16V7K

1 2

C17 .1U_0402_16V7K

1 2

C18 .1U_0402_16V7K

1 2

C2702 .1U_0402_16V7K

1 2

C2701 .1U_0402_16V7K

1 2

C2704 .1U_0402_16V7K

1 2

C2703 .1U_0402_16V7K

1 2

2

PCIE_ATX_C_DRX_P0 <28>

PCIE_ATX_C_DRX_N0 <28>

PCIE_ATX_C_DRX_P1 <29>

PCIE_ATX_C_DRX_N1 <29>

PCIE_ATX_C_DRX_P2 <30>

PCIE_ATX_C_DRX_N2 <30>

PCIE_ATX_C_DRX_P3 <30>

PCIE_ATX_C_DRX_N3 <30>

1

P10

PEG_GTX_C_HRX_P0<15>

PEG_GTX_C_HRX_N0<15>

PEG_GTX_C_HRX_P1<15>

PEG_GTX_C_HRX_N1<15>

PEG_GTX_C_HRX_P2<15>

PEG_GTX_C_HRX_N2<15>

PEG_GTX_C_HRX_P3<15>

PEG_GTX_C_HRX_N3<15>

PEG_GTX_C_HRX_N4<15>

C C

PEG_GTX_C_HRX_P5<15>

PEG_GTX_C_HRX_N6<15>

PEG_GTX_C_HRX_P7<15>

CPU PN Table

CPU Platform

UAPU1 BR_A10@

S IC A10-9620P AM962PADY44AB 2.5G BGA 968P AP

SA0000AK010

B B

Brist ol

15W

UAPU1 BR_A12@

S IC A12-9720P AM972PADY44AB 2.7G BGA 968P APU

SA0000AJY10

UAPU1 BR_FX@

PN R3(ABO!)PN R1(ROH)

UAPU1 BR_A10R3@

S IC A10-9620P AM962PADY44AB 2.5G ABO!

SA0000AK020

UAPU1 BR_A12R3@

S IC A12-9720P AM972PADY44AB 2.7G ABO!

SA0000AJY20

UAPU1 BR_FXR3@

P_GFX_RXP[0]

P9

P_GFX_RXN[0]

N6

P_GFX_RXP[1]

N5

P_GFX_RXN[1]

N9

P_GFX_RXP[2]

N8

P_GFX_RXN[2]

L7

P_GFX_RXP[3]

L6

P_GFX_RXN[3]

L10

P_GFX_RXP[4]

L9

P_GFX_RXN[4]

K6

P_GFX_RXP[5]

K5

P_GFX_RXN[5]

K9

P_GFX_RXP[6]

K8

P_GFX_RXN[6]

J7

P_GFX_RXP[7]

J6

P_GFX_RXN[7]

CPU PN Table

CPU Platform

Brist ol

35W

FP4 REV 0.93

FP4_BGA968

UAPU1 BR_35WA10@

S IC A10-9630P AM963PAEY44AB 2.6G BGA968

SA0000AOQ00

UAPU1 BR_35WA12@

S IC A12-9730P AM973PAEY44AB 2.8G BGA968

SA0000AOR00

UAPU1 BR_35WFX@

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

M2

M1

L1

L2

L4

L3

J1

J2

J4

J3

H2

H1

G1

G2

G4

G3

PEG_HTX_C_GRX_P0 <15>

PEG_HTX_C_GRX_N0 <15>

PEG_HTX_C_GRX_P1 <15>

PEG_HTX_C_GRX_N1 <15>

PEG_HTX_C_GRX_P2 <15>

PEG_HTX_C_GRX_N2 <15>

PEG_HTX_C_GRX_P3 <15>

PEG_HTX_C_GRX_N3 <15>

PEG_HTX_C_GRX_P4 <15>PEG_GTX_C_HRX_P4<15>

PEG_HTX_C_GRX_N4 <15>

PEG_HTX_C_GRX_P5 <15>

PEG_HTX_C_GRX_N5 <15>PEG_GTX_C_HRX_N5<15>

PEG_HTX_C_GRX_P6 <15>PEG_GTX_C_HRX_P6<15>

PEG_HTX_C_GRX_N6 <15>

PEG_HTX_C_GRX_P7 <15>

PEG_HTX_C_GRX_N7 <15>PEG_GTX_C_HRX_N7<15>

PN R3(ABO!)PN R1(ROH)

S IC FX-9800P FM980PADY44AB 2.7G BGA 968P APU

SA00009LB00

S IC FX-9800P FM980PADY44AB 2.7G ABO!

SA00009LB40

S IC FX-9830P FM983PAEY44AB 3G BGA 968P

SA0000AOS00

CPU PN Table

CPU Platform

A A

Stone y

UAPU1 SR_A6@

S IC A6-9220 AM9220AVY23AC 2.5G BGA 968P

SA0000ALL00

5

PN R3(ABO!)PN R1(ROH)

UAPU1 SR_A6R3@

S IC A6-9220 AM9220AVY23AC 2.5G BGA ABO!

SA0000ALL10

4

Security Classification

Security Classification

Security Classification

2017/04/18 2019/04/18

2017/04/18 2019/04/18

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/04/18 2019/04/18

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

FP4 PCIE

FP4 PCIE

FP4 PCIE

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

6 50Tuesday, May 02, 2017

6 50Tuesday, May 02, 2017

6 50Tuesday, May 02, 2017

1

1.A

1.A

1.A

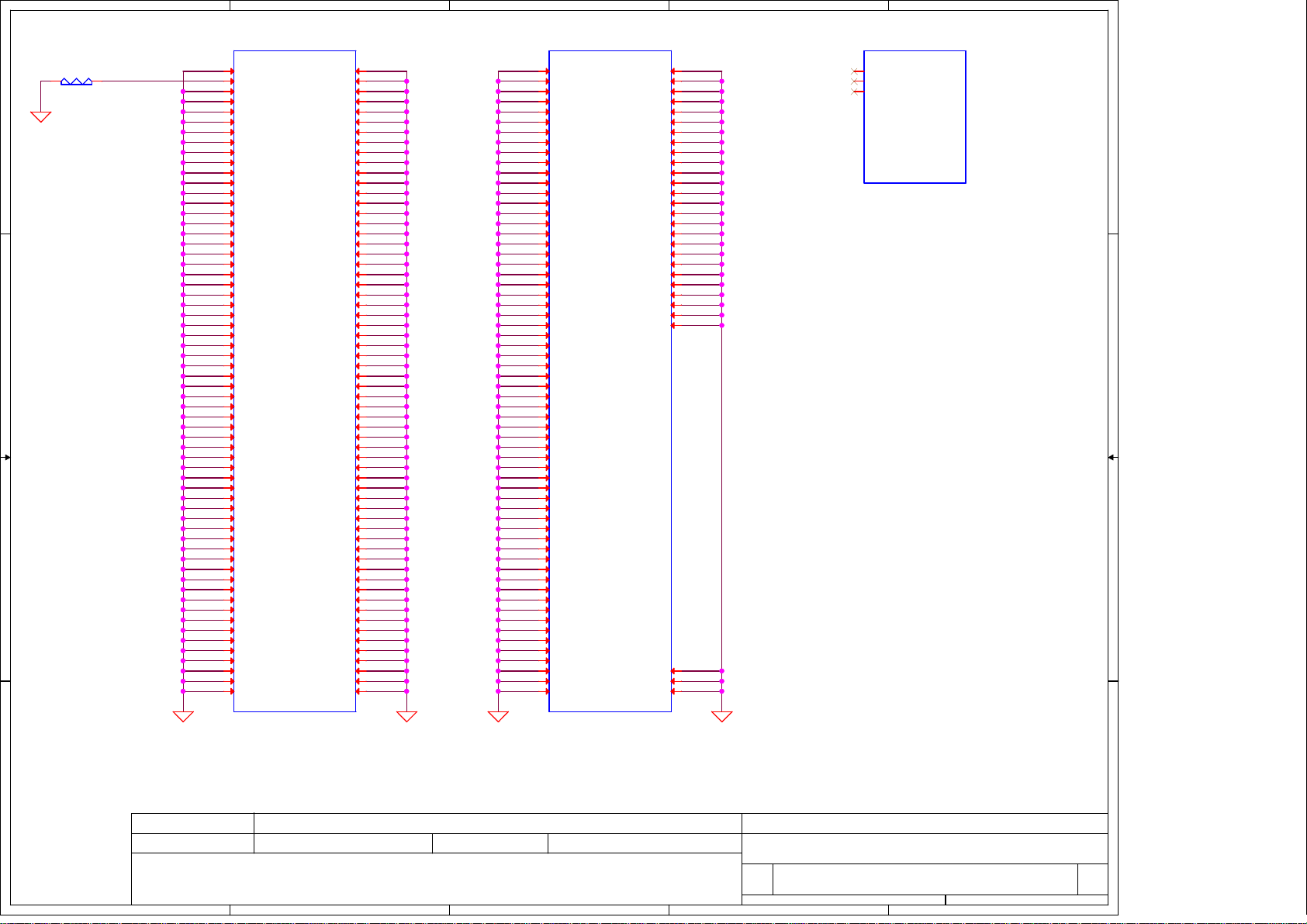

5

4

3

2

1

@

DDRA_SMA[13..0]<13>

D D

DDRA_BG1<13>

MEM_MA_ACT#<13> MEM_MB_ACT#<14>

DDRA_SBS0#<13>

DDRA_SBS1#<13>

DDRA_BG0<13>

DDRA_SDM[7..0]<13>

DDRA_SDQS0<13>

DDRA_SDQS0#<13>

DDRA_SDQS1<13>

DDRA_SDQS1#<13>

C C

B B

DDRA_SDQS2<13>

DDRA_SDQS2#<13>

DDRA_SDQS3<13>

DDRA_SDQS3#<13>

DDRA_SDQS4<13>

DDRA_SDQS4#<13>

DDRA_SDQS5<13>

DDRA_SDQS5#<13>

DDRA_SDQS6<13>

DDRA_SDQS6#<13>

DDRA_SDQS7<13>

DDRA_SDQS7#<13>

DDRA_CLK0<13>

DDRA_CLK0#<13>

DDRA_CLK1<13>

DDRA_CLK1#<13>

MEM_MA_RST#<13>

MEM_MA_EVENT#<13>

DDRA_CKE0<13>

DDRA_CKE1<13>

DDRA_ODT0<13>

DDRA_ODT1<13>

DDRA_SCS0#<13>

DDRA_SCS1#<13>

DDRA_SMA16<13>

DDRA_SMA15<13>

DDRA_SMA14<13>

T80

T4957

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_BG1

MEM_MA_ACT#

DDRA_SBS0#

DDRA_SBS1#

DDRA_BG0

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

MEM_MA_RST#

MEM_MA_EVENT#

DDRA_CKE0

DDRA_CKE1

DDRA_ODT0

DDRA_ODT1

DDRA_SCS0#

DDRA_SCS1#

DDRA_SMA16

DDRA_SMA15

DDRA_SMA14

MA_VREFDQ

M_VREF

UAPU1A

AE28

MA_ADD[0]

Y27

MA_ADD[1]

Y29

MA_ADD[2]

Y26

MA_ADD[3]

W28

MA_ADD[4]

W29

MA_ADD[5]

W26

MA_ADD[6]

U29

MA_ADD[7]

W25

MA_ADD[8]

U26

MA_ADD[9]

AG29

MA_ADD[10]

U27

MA_ADD[11]

T28

MA_ADD[12]

AK26

MA_ADD[13]

T26

MA_ADD[14]/MA_BG[1]

T25

MA_ADD[15]/MA_ACT_L

AG26

MA_BANK[0]

AG27

MA_BANK[1]

T29

MA_BANK[2]/MA_BG[0]

E19

MA_DM[0]

D21

MA_DM[1]

K21

MA_DM[2]

F29

MA_DM[3]

AP28

MA_DM[4]

AV26

MA_DM[5]

AR22

MA_DM[6]

BC22

MA_DM[7]

K29

MA_DM[8]

H19

MA_DQS_H[0]

G19

MA_DQS_L[0]

B22

MA_DQS_H[1]

A22

MA_DQS_L[1]

F23

MA_DQS_H[2]

E23

MA_DQS_L[2]

G27

MA_DQS_H[3]

F27

MA_DQS_L[3]

AP25

MA_DQS_H[4]

AP26

MA_DQS_L[4]

AW27

MA_DQS_H[5]

AV27

MA_DQS_L[5]

AV22

MA_DQS_H[6]

AU22

MA_DQS_L[6]

BA21

MA_DQS_H[7]

AY21

MA_DQS_L[7]

L27

MA_DQS_H[8]

L26

MA_DQS_L[8]

AE25

MA_CLK_H[0]

AE26

MA_CLK_L[0]

AD26

MA_CLK_H[1]

AD27

MA_CLK_L[1]

AB28

MA_CLK_H[2]

AB29

MA_CLK_L[2]

AB25

MA_CLK_H[3]

AB26

MA_CLK_L[3]

N29

MA_RESET_L

AE29

MA_EVENT_L

P27

MA_CKE0

P29

MA_CKE1

AK27

MA0_ODT[0]

AL26

MA0_ODT[1]

AH25

MA1_ODT[0]

AL25

MA1_ODT[1]

AH26

MA0_CS_L[0]

AL29

MA0_CS_L[1]

AH29

MA1_CS_L[0]

AL28

MA1_CS_L[1]

AG24

MA_RAS_L/MA_RAS_L_ADD[16]

AK29

MA_CAS_L/MA_CAS_L_ADD[15]

AH28

MA_WE_L/MA_WE_L_ADD[14]

B19

MA_VREFDQ

T32

M_VREF

MEMORY A

FP4 REV 0.93

FP4_BGA968

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

MA_CHECK[0]

MA_CHECK[1]

MA_CHECK[2]

MA_CHECK[3]

MA_CHECK[4]

MA_CHECK[5]

MA_CHECK[6]

MA_CHECK[7]

MA_ZVDDIO_MEM_S

H17

J17

F20

H20

E17

F17

K18

E20

A21

C21

C23

D23

B20

B21

B23

A23

G22

H22

E25

G25

J20

E22

H23

J23

F26

E27

J26

J27

H25

E26

G28

G29

AN26

AP29

AR26

AP24

AN29

AN27

AR29

AR27

AU26

AV29

AU25

AW25

AU29

AU28

AW26

AT25

AV23

AW23

AV20

AW20

AR23

AT23

AR20

AT20

BB23

BB22

BB20

AY19

BA23

BC23

BC21

BB21

K26

K28

N26

N28

J29

K25

L29

N25

AD29

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

MEM_MA_ZVDDIO

DDRA_SDQ[63..0] <13>

R74

39.2_0402_1%

1 2

T1@

+1.2V

DDRB_SMA[13..0]<14>

DDRB_BG1<14>

DDRB_SBS0#<14>

DDRB_SBS1#<14>

DDRB_BG0<14>

DDRB_SDM[7..0]<14>

DDRB_SDQS0<14>

DDRB_SDQS0#<14>

DDRB_SDQS1<14>

DDRB_SDQS1#<14>

DDRB_SDQS2<14>

DDRB_SDQS2#<14>

DDRB_SDQS3<14>

DDRB_SDQS3#<14>

DDRB_SDQS4<14>

DDRB_SDQS4#<14>

DDRB_SDQS5<14>

DDRB_SDQS5#<14>

DDRB_SDQS6<14>

DDRB_SDQS6#<14>

DDRB_SDQS7<14>

DDRB_SDQS7#<14>

DDRB_CLK0<14>

DDRB_CLK0#<14>

DDRB_CLK1<14>

DDRB_CLK1#<14>

MEM_MB_RST#<14>

MEM_MB_EVENT#<14>

DDRB_CKE0<14>

DDRB_CKE1<14>

DDRB_ODT0<14>

DDRB_ODT1<14>

DDRB_SCS0#<14>

DDRB_SCS1#<14>

DDRB_SMA16<14>

DDRB_SMA15<14>

DDRB_SMA14<14>

T45

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SMA13

DDRB_BG1

MEM_MB_ACT#

DDRB_SBS0#

DDRB_SBS1#

DDRB_BG0

DDRB_SDM0

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS7

DDRB_SDQS7#

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

MEM_MB_RST#

MEM_MB_EVENT#

DDRB_CKE0

DDRB_CKE1

DDRB_ODT0

DDRB_ODT1

DDRB_SCS0#

DDRB_SCS1#

DDRB_SMA16

DDRB_SMA15

DDRB_SMA14

MB_VREFDQ

UAPU1I

AG31

MB_ADD[0]

AC30

MB_ADD[1]

AC31

MB_ADD[2]

AB32

MB_ADD[3]

AA32

MB_ADD[4]

AA33

MB_ADD[5]

AA31

MB_ADD[6]

Y33

MB_ADD[7]

AA30

MB_ADD[8]

W32

MB_ADD[9]

AG32

MB_ADD[10]

Y32

MB_ADD[11]

W33

MB_ADD[12]

AL31

MB_ADD[13]

W30

MB_ADD[14]/MB_BG[1]

V32

MB_ADD[15]/MB_ACT_L

AH32

MB_BANK[0]

AG33

MB_BANK[1]

W31

MB_BANK[2]/MB_BG[0]

D25

MB_DM[0]

D29

MB_DM[1]

E33

MB_DM[2]

J33

MB_DM[3]

AR30

MB_DM[4]

AW30

MB_DM[5]

BC30

MB_DM[6]

BC26

MB_DM[7]

N33

MB_DM[8]

B26

MB_DQS_H[0]

A26

MB_DQS_L[0]

B30

MB_DQS_H[1]

A30

MB_DQS_L[1]

F32

MB_DQS_H[2]

E32

MB_DQS_L[2]

K32

MB_DQS_H[3]

J32

MB_DQS_L[3]

AR32

MB_DQS_H[4]

AR33

MB_DQS_L[4]

AW32

MB_DQS_H[5]

AW33

MB_DQS_L[5]

BA29

MB_DQS_H[6]

AY29

MB_DQS_L[6]

BA25

MB_DQS_H[7]

AY25

MB_DQS_L[7]

P32

MB_DQS_H[8]

N32

MB_DQS_L[8]

AE33

MB_CLK_H[0]

AE32

MB_CLK_L[0]

AE30

MB_CLK_H[1]

AE31

MB_CLK_L[1]

AD32

MB_CLK_H[2]

AD33

MB_CLK_L[2]

AC33

MB_CLK_H[3]

AC32

MB_CLK_L[3]

T33

MB_RESET_L

AG30

MB_EVENT_L

U32

MB_CKE0

U33

MB_CKE1

AL30

MB0_ODT[0]

AM32

MB0_ODT[1]

AJ32

MB1_ODT[0]

AM33

MB1_ODT[1]

AJ33

MB0_CS_L[0]

AL32

MB0_CS_L[1]

AJ30

MB1_CS_L[0]

AL33

MB1_CS_L[1]

AH33

MB_RAS_L/MB_RAS_L_ADD[16]

AK32

MB_CAS_L/MB_CAS_L_ADD[15]

AJ31

MB_WE_L/MB_WE_L_ADD[14]

A19

MB_VREFDQ

@

MEMORY B

FP4 REV 0.93

FP4_BGA968

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

MB_ZVDDIO_MEM_S

A25

C25

C27

D27

B24

B25

B27

A27

A29

C29

B32

D32

B28

B29

A31

C31

E30

E31

G33

G32

C33

D33

G30

G31

J30

J31

L33

L32

H32

H33

L30

L31

AN31

AP32

AT32

AU32

AN33

AN32

AR31

AT33

AU30

AV32

BA33

AY32

AU33

AU31

AW31

AY33

BC31

BB30

BB28

AY27

BB32

BA31

BC29

BB29

BB27

BB26

BB24

AY23

BA27

BC27

BC25

BB25

N30

N31

R33

R32

M32

M33

R30

R31

AF32

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

MEM_MB_ZVDDIO

DDRB_SDQ[63..0] <14>

R75

39.2_0402_1%

1 2

+1.2V

+1.2V

R3979

2D@

1K_0402_5%

MEM_MA_EVENT#

12

R3994

1K_0402_5%

MEM_MB_EVENT#

12

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS C ONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

Compal Electronics, Inc.

FP4 MEMORY INTERFACE

FP4 MEMORY INTERFACE

FP4 MEMORY INTERFACE

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

1

7 50Tuesday, May 02, 2017

7 50Tuesday, May 02, 2017

7 50Tuesday, May 02, 2017

1.A

1.A

1.A

A

B

C

D

E

+1.8VS

RP14

@

APU_SVT_R

18

APU_SVC

27

APU_SVD

36

1 1

45

1K_0804_8P4R_5%

RP17

@

GFX_SVC

18

GFX_SVD

27

GFX_SVT_R

36

45

1K_0804_8P4R_5%

1 2

1 2

1 2

1 2

1 2

1 2

APU_DP1_P0<26>

APU_DP1_N0<26>

APU_DP1_P1<26>

APU_DP1_N1<26>

APU_DP1_P2<26>

APU_DP1_N2<26>

APU_DP1_P3<26>

APU_DP1_N3<26>

EDP_TXP0<27>

EDP_TXN0<27>

EDP_TXP1<27>

EDP_TXN1<27>

EDP_TXP2<27>

EDP_TXN2<27>

EDP_TXP3<27>

EDP_TXN3<27>

APU_SVT_R

APU_SVC_R

APU_SVD_R

GFX_SVT_R

GFX_SVC_R

GFX_SVD_R

APU_SIC

APU_SID

APU_RST#

APU_PW ROK

APU_PROCHOT#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

C15

D17

D19

B15

B16

A18

B18

C17

D15

C19

A15

B17

H15

H14

D13

G15

C13

A11

J14

APU_PROCHOT#

APU_RST#

APU_PW ROK

2 2

+1.8VS

3 3

RP25

1

EMC@

C2647

33P_0402_50V8J

2

APU_PROCHOT#

18

APU_SID

27

APU_ALERT#

36

APU_SIC

45

1

EMC@

C2648

33P_0402_50V8J

2

APU_SVT_R<44>

APU_SVC<44>

APU_SVD<44>

GFX_SVT_R<45>

GFX_SVC<45>

GFX_SVD<45>

APU_PROCHOT#<16,24,44,45>

Close to APU

1

@EMC@

C2649

.1U_0402_16V7K

2

R2612 0_0402_5%

R2613 0_0402_5%

R2614 0_0402_5%T1@

R2615 0_0402_5%T1@

R80 300_0402_5%

+1.8VS

R82 300_0402_5%

+1.8VS

APU_PW ROK<44,45>

1K_0804_8P4R_5%

+1.8VS

+3VS

1 2

R3969 2.2K_0402_5%

1 2

R3970 2.2K_0402_5%

EC_SMB_CK2

EC_SMB_DA2

EC_SMB_CK2<16,24>

EC_SMB_DA2<16,24>

EC_SMB_CK2

EC_SMB_DA2

5

3 4

SGD

Q79A

2

DMN63D8LDW_SOT363-6

G

6 1

S

D

Q79B

DMN63D8LDW_SOT363-6

VGS,on = 0.8~1.5V

APU_SIC

APU_SID

B6

A6

D7

C7

A7

B7

D9

C9

A2

A3

B4

A4

D5

C5

A5

B5

E2

E1

E3

E4

D1

D2

C1

B1

UAPU1C

DP2_TXP[0]

DP2_TXN[0]

DP2_TXP[1]

DP2_TXN[1]

DP2_TXP[2]

DP2_TXN[2]

DP2_TXP[3]

DP2_TXN[3]

DP1_TXP[0]

DP1_TXN[0]

DP1_TXP[1]

DP1_TXN[1]

DP1_TXP[2]

DP1_TXN[2]

DP1_TXP[3]

DP1_TXN[3]

DP0_TXP[0]

DP0_TXN[0]

DP0_TXP[1]

DP0_TXN[1]

DP0_TXP[2]

DP0_TXN[2]

DP0_TXP[3]

DP0_TXN[3]

SVT0

SVC0

SVD0

SVT1

SVC1

SVD1

SIC

SID

RESET_L

PWROK

PROCHOT_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

@

DISPLAY/SVI2 /JTAG/TEST

FP4 REV 0.93

FP4_BGA968

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

RSVD_1

TEMPIN0

TEMPIN1

TEMPIN2

TEMPINRETURN

TEST410

TEST411

TEST28_H

TEST28_L

DP_STEREOSYNC/TEST36

VDDCR_GFX_SENSE

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDP_SENSE

VSS_SENSE

A9

B9

G5

G6

F11

H9

G9

E9

F7

E7

F5

F8

E8

G8

K24

E15

E14

E12

F14

AK24

AL24

P24

TEST4

N24

TEST5

AN24

TEST6

AB8

TEST9

Y9

TEST10

B10

TEST14

D11

TEST15

A10

TEST16

C11

TEST17

B11

TEST11

A14

TEST18

B14

TEST19

A13

B13

P26

TEST31

E11

A17

TEST37

H11

J12

G12

AY18

H12

APU_TRST#

DP_ZVSS

DP_AUX_ZVSS

ENBKL_R

ENVDD_R

INVTPWM_R

APU_TEST410

APU_TEST411

APU_TEST4

APU_TEST5

1 2

R400 2K_0402_1%

1 2

R401 150_0402_1%

HDMI_SCLK <26>

HDMI_SDATA <26>

HDMI_HPD <26>

EDP_AUXP <27>

EDP_AUXN <27>

EDP_HPD <27>

TP@

T32

TP@

T33

TP@

T34

TP@

T35

ENVDD_R

ENBKL_R

+1.8VALW

5

U64

1

P

NC

2

A

G

NL17SZ07DFT2G_SC70-5

3

SA00004BV00

+1.8VALW

5

U2610

1

P

NC

2

A

G

NL17SZ07DFT2G_SC70-5

3

SA00004BV00

4

Y

@

Y

ENVDD <27>

4

ENBKL <24>

ENVDD

INVTPWM

ENBKL

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST11

APU_TEST18

APU_TEST19

APU_TEST28_H

APU_TEST28_L

APU_TEST31

APU_TEST36 APU_TEST36

APU_TEST37

APU_COREGFX_SEN_H <45>

APU_CORENB_SEN_H <44>

APU_CORE_SEN_H <44>

T40

T43

T42

T41

APU_VSS_SEN_L <44,45>

TP@

TP@

TP@

TP@

+1.8VS

APU_TEST11

APU_TEST17

APU_TEST16

APU_TEST14

APU_TEST37

1

3

5

7

1 2

R671 33_0402_5%

1 8

2 7

3 6

4 5

APU_TRST#_R

RP29

10K_0804_8P4R_5%

HDT_P11

HDT_P13

HDT_P15

9

11

13

15

17

19

1 2

1 2

HDT+

JHDT1

@

1

3

5

7

9

11

13

15

17

19

RP30

@

18

27

36

45

1K_0804_8P4R_5%

@

R117

1K_0402_5%

@

R118

1K_0402_5%

APU_TCK_R

2

2

APU_TMS_R

4

4

APU_TDI_R

6

6

APU_TDO_R

8

8

APU_PW ROK_R

10

10

APU_RST#_R

12

12

APU_DBRDY_R

14

14

APU_DBREQ#_R

16

16

APU_TEST19

18

18

APU_TEST18

20

20

+1.8VS

1 2

@

R706 0_0402_5%

1 2

@

R694 0_0402_5%

1 2

@

R705 0_0402_5%

1 2

@

R704 0_0402_5%

1 2

@

R682 0_0402_5%

1 2

@

R707 0_0402_5%

1 2

@

R708 0_0402_5%

1 2

R672 33_0402_5%

SAMTE_ASP-136446-07-B

INVTPWM_R

ENVDD_R

1 2

@

R1160

4.7K_0402_5%

1 2

R1161

4.7K_0402_5%

1 2

R3905

4.7K_0402_5%

1 2

R155

1K_0402_5%

1 2

R154

1K_0402_5%

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PW ROK

APU_RST#

APU_DBRDY

APU_DBREQ#

+1.8VALW

5

1

P

NC

2

A

G

3

1 2

R683 0_0402_5%RS@

+3VS

@

APU_DBREQ#

APU_TDI

APU_TMS

APU_TCK

APU_TRST#

APU_TEST19

APU_TEST18

APU_TRST#

U2611

4

Y

NL17SZ07DFT2G_SC70-5

SA00004BV00

ENVDD_R

INVTPWM_R

ENBKL_R

INVTPWM <27>

1 2

R3847

100K_0402_5%

1 2

@

R3835

100K_0402_5%

1 2

R3906

100K_0402_5%

+1.8VS

RP28

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

RP27

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

1 2

C141

0.01U_0402_16V7K

ENVDD

+1.8VS

+1.8VS

4 4

Security Classification

Security Classification

Security Classification

2017/04/18 2019/04/18

2017/04/18 2019/04/18

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2017/04/18 2019/04/18

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

FP4 DISP/MISC/HDT

FP4 DISP/MISC/HDT

FP4 DISP/MISC/HDT

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

8 50Tuesday, May 02, 2017

8 50Tuesday, May 02, 2017

8 50Tuesday, May 02, 2017

E

1.A

1.A

1.A

A

1 2

C912 150P_0402_50V8J

1 2

C615 150P_0402_50V8J

1 2

LPC_RST#<24,33>

APU_PCIE_RST#<15,28,29,30>

1 1

2 2

+3VALW

1 2

R930 10K_0402_5%@

1 2

R905 100K_0402_5%@

1 2

R3927 10K_0402_5%

1 2

R685 10K_0402_5%@

1 2

R686 10K_0402_5%@

1 2

R2616 2.2K_0402_5%@

3 3

4 4

1 2

R2618 1K_0402_5%@

1 2

R2617 2.2K_0402_5%@

1 2

R3948 10K_0402_5%

+3VS

1 2

R676 2.2K_0402_5%

1 2

R677 2.2K_0402_5%

1 2

R3863 10K_0402_5%@

1 2

R3864 10K_0402_5%@

1 2

R3975 10K_0402_5%@

+1.8VS

1 2

R3946 10K_0402_5%

1 2

R3947 10K_0402_5%

1 2

R3945 10K_0402_5%@

1 2

R3929 10K_0402_5%

1 2

R3928 10K_0402_5%

1 2

R3954 10K_0402_5%@

1 2

R3850 10K_0402_5%

1 2

R3879 0_0402_5%@

1 2

R40 15K_0402_5%

1 2

R41 15K_0402_5%

1 2

R42 15K_0402_5%

1 2

R3949 10K_0402_5%

1 2

R3950 10K_0402_5%

1 2

R3961 10K_0402_5%T3@

R602 33_0402_5%

R907 33_0402_5%

EC_RSMRST#<24>

PBTN_OUT#<24>

SYS_PWRGD_EC<24>

SLP_S3#<24>

SLP_S5#<24>

S5_MUX_CTRL<25>

KBRST#<24>

GATEA20<24>

EC_SCI#<24>

LAN_CLKREQ#<28>

WLAN_CLKREQ#<29>

DGPU_PW ROK<47,48>

SSD_CLKREQ#<30>

PEG_CLKREQ#<16>

USB_OC0#<31>

APU_PCIE_WAKE#

USB_OC0#

EC_SCI#

APU_I2C3_SCL

APU_I2C3_SDA

APU_TEST0

APU_TEST1

APU_TEST2

AGPIO8

APU_SMB_CLK0

APU_SMB_DATA0

LAN_CLKREQ#

WLAN_CLKREQ#

SSD_CLKREQ#

APU_I2C1_SCL

APU_I2C1_SDA

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_BITCLK

PEG_CLKREQ#

HVB

APU_TEST0

APU_TEST1

APU_TEST2

APU_I2C0_SCL

APU_I2C0_SDA

VDDGFX_PWRGD

A

1 2

HDA_SDIN0<34>

APU_I2C1_SCL<30>

APU_I2C1_SDA<30>

1U_0402_6.3V6K

Length<1.0"

LPC_RST_A#

APU_PCIE_RST#_R

EC_RSMRST#

PBTN_OUT#

SYS_PWRGD_EC

SYS_RST#

APU_PCIE_WAKE#

SLP_S3#

SLP_S5#

AGPIO10

APU_TEST0

APU_TEST1

APU_TEST2

KBRST#

GATEA20

EC_SCI#

AGPIO12

LAN_CLKREQ#

WLAN_CLKREQ#

DGPU_PW ROK

SSD_CLKREQ#

PEG_CLKREQ#

USB_OC0#

HDA_BITCLK

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_RST#

HDA_SYNC

HDA_SDOUT

APU_I2C0_SCL

APU_I2C0_SDA

APU_I2C1_SCL

APU_I2C1_SDA

RTC_CLK

32K_X1

32K_X2

HDA_BITCLK_AUDIO<34>

HDA_SDOUT_AUDIO<34>

HDA_SYNC_AUDIO<34>

HDA_RST#_AUDIO<34>

+1.8VALW +3VS

R346

22K_0402_1%

EC_RSMRST#

SYS_PWRGD_EC

C999

B

@

UAPU1D

BB12

LPC_RST_L

AN7

PCIE_RST_L/EGPIO26

AE4

RSMRST_L

AE1

PWR_BTN_L/AGPIO0

BC9

PWR_GOOD

AF2

SYS_RESET_L/AGPIO1

AG2

WAKE_L/AGPIO2

AK7

SLP_S3_L

AH5

SLP_S5_L

AE8

S0A3_GPIO/AGPIO10

AH8

S5_MUX_CTRL/EGPIO42

AH6

TEST0

AK8

TEST1/TMS

AE3

TEST2

AY15

ESPI_RESET_L/KBRST_L/AGPIO129

BC19

GA20IN/AGPIO126

AD7

LPC_PME_L/AGPIO22

BB13

LPC_SMI_L/AGPIO86

AG3

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AD5

IR_TX0/USB_OC5_L/AGPIO13

AL8

IR_TX1/USB_OC6_L/AGPIO14

AN8

IR_RX1/AGPIO15

AE2

IR_LED_L/LLB_L/AGPIO12

BC15

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

BB17

CLK_REQ1_L/AGPIO115

BC17

CLK_REQ2_L/AGPIO116

BB18

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

BB16

CLK_REQG_L/OSCIN/EGPIO132

AH9

USB_OC0_L/TRST_L/AGPIO16

AG1

USB_OC1_L/TDI/AGPIO17

AH2

USB_OC2_L/TCK/AGPIO18

AL9

USB_OC3_L/TDO/AGPIO24

AU6

AZ_BITCLK/I2S_BCLK_MIC

AR8

AZ_SDIN0/I2S_DATA_MIC[0]

AP6

AZ_SDIN1/I2S_LR_PLAYBACK

AR5

AZ_SDIN2/I2S_DATA_MIC[1]

AU9

AZ_RST_L/I2S_LR_MIC

AT9

AZ_SYNC/I2S_BCLK_PLAYBACK

AR7

AZ_SDOUT/I2S_DATA_PLAYBACK

BB10

I2C0_SCL/EGPIO145

BB9

I2C0_SDA/EGPIO146

BB7

I2C1_SCL/EGPIO147

BC7

I2C1_SDA/EGPIO148

AG7

RTCCLK

AT1

X32K_X1

AT2

X32K_X2

EMC@

RP13

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

T1@

RP68

1K_0804_8P4R_5%

12

12

R348

4.7K_0402_5%

2

2

C1000

0.22U_0402_16V7K

1

1

B

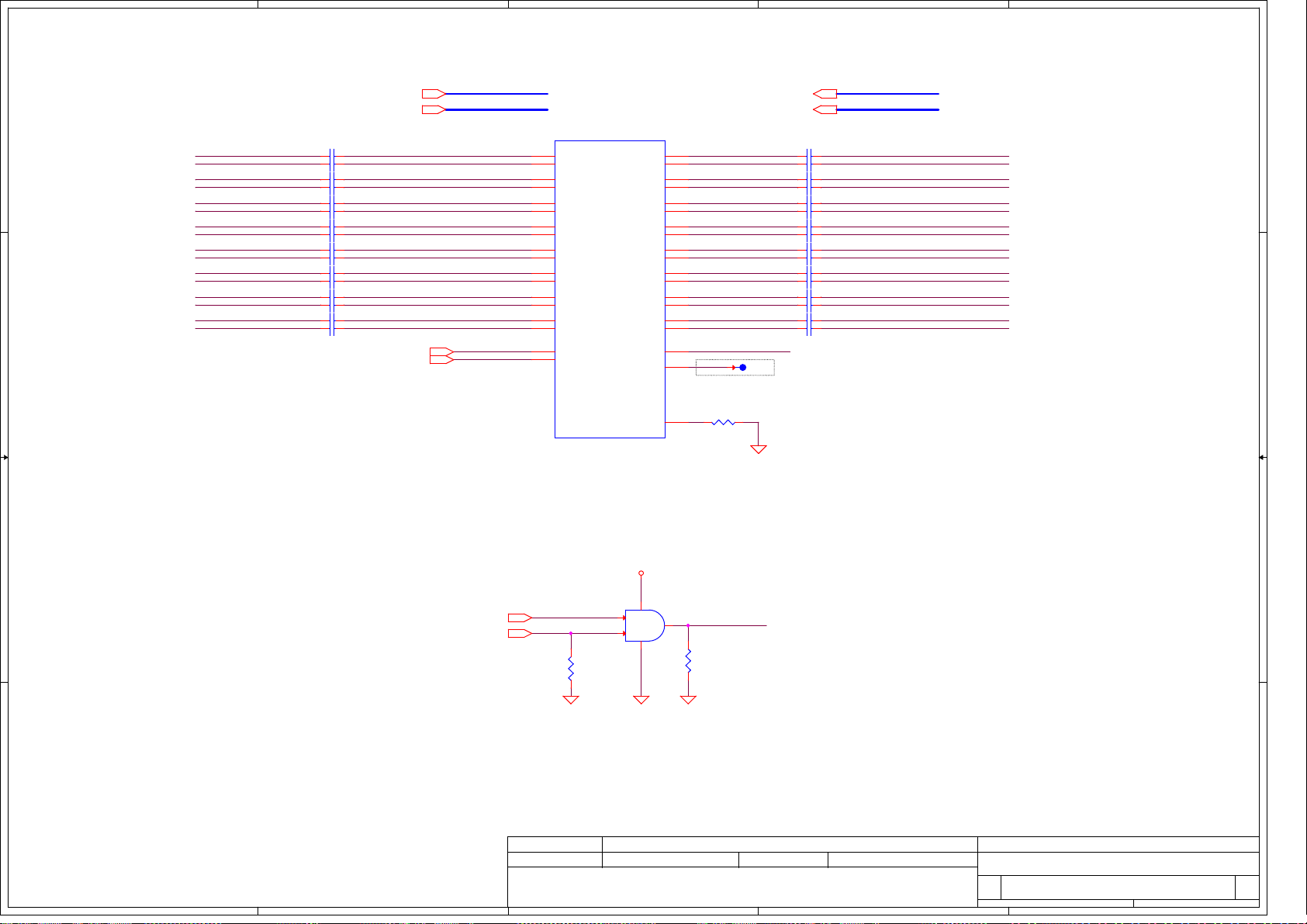

ACPI/SD/AZ/GPIO/RTC/I2C/ UART/MISC

HDA_BITCLK

HDA_SDOUT

HDA_SYNC

HDA_RST#

18

27

36

45

C

SD0_WP/EGPIO101

SD0_PWR_CTRL/AGPIO102

SD0_CLK/EGPIO95

SD0_CMD/EGPIO96

SD0_DATA0/EGPIO97

SD0_DATA1/EGPIO98

SD0_DATA2/EGPIO99

SD0_DATA3/EGPIO100

SD0_LED/EGPIO93

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO6/LDT_RST

AGPIO7/LDT_PWROK

VDDGFX_PD/AGPIO39

AGPIO66/SHUTDOWN_L

AGPIO68/SGPIO_CLK

AGPIO69/SGPIO_LOAD

AGPIO71/SGPIO_DATAOUT

AGPIO72/SGPIO_DATAIN

BLINK/USB_OC7_L/AGPIO11

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

FANOUT0/AGPIO85

UART0_CTS_L/EGPIO135

UART0_RXD/EGPIO136

UART0_RTS_L/EGPIO137

UART0_TXD/EGPIO138

UART0_INTR/AGPIO139

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

UART1_RXD/BT_I2S_SDI/EGPIO141

UART1_RTS_L/EGPIO142

UART1_TXD/BT_I2S_SDO/EGPIO143

FP4 REV 0.93

FP4_BGA968

UART1_INTR/BT_I2S_LRCLK/AGPIO144

H

L

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

BB2

BB5

BC2

SD0_CD/AGPIO25

BB4

AY5

BC3

BA3

BC5

BA5

PE_GPIO1

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

AGPIO64

AGPIO65

SPKR/AGPIO91

FANIN0/AGPIO84

BB6

APU_SMB_CLK0

BA15

APU_SMB_DATA0

AY17

APU_I2C3_SCL

AG5

APU_I2C3_SDA

AG4

AL5

AGPIO3

AL6

AJ1

AGPIO5

AJ3

AH1

AGPIO7

AJ4

AGPIO8

AK5

AD8

VDDGFX_PWRGD

AG8

AW15

AU15

G_INT#_APU

AT15

AU12

AT14

AGPIO69

PE_GPIO0

AR14

BC13

APU_SPKR

BA17

AN5

AGPIO11

BB14

HVB

TP_I2C_INT#_APU

BA19

BC18

BB19

AY9

AW8

AV5

AV8

AW9

AV11

AU7

AT11

AR11

AP9

PE_GPIO1 <25>

APU_SMB_CLK0 <13,14>

APU_SMB_DATA0 <13,14>

APU_I2C3_SCL <33>

APU_I2C3_SDA <33>

AGPIO8 <30>

VDDGFX_PWRGD <45>

G_INT#_APU <30>

PE_GPIO0 <15>

APU_SPKR <34>

TP_I2C_INT#_APU <33>

LPC_FRAME#LPC_CLK0_EC LPC_CLK1

BOOT FAIL

TIMER

ENABLED

BOOT FAIL

TIMER

DISABLED

(DEFAULT)

LPC_FRAME#<10,24,33>

LPC_CLK0_EC<10,24>

LPC_CLK1<10,33>

2017/04/18 2019/04/18

2017/04/18 2019/04/18

2017/04/18 2019/04/18

C

CLKGEN

ENABLE

(DEFAULT)

CLKGEN

DISABLED

+3VS

12

R902

10K_0402_5%

AGPIO3

RTC_CLK

SYS_RST#

AGPIO11

12

@

R903

2K_0402_5%

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SPI ROM

(DEFAULT)

LPC ROM

12

12

@

R904

10K_0402_5%

R926

2K_0402_5%

MEM_VOLT_SEL/AGPIO3

<INT PU>

CZL CZ

1.8V SPI ROM

3.3V SPI ROM

(Default)

12

12

D

If no use, need Config Low

H

L

ENHANCED

RESET

(DEFAULT)

TRADITION

RESET

+3VALW

R925

10K_0402_5%

@

R927

2K_0402_5%

D

12

R928

10K_0402_5%

12

@

R929

2K_0402_5%

E

T1@

VX@

R3978

R3953

10K_0402_5%

10K_0402_5%

1 2

1 2

T3@

EA@

R936

R3952

10K_0402_5%

10K_0402_5%

1 2

1 2

VX

EASR

UMA

DIS

R4002

UMA@

10K_0402_5%

SD028100280

AGPIO5

RX550xRX560

RX540

RX550@

RX560@

AGPIO5

AGPIO7

AGPIO10

AGPIO12

AGPIO69

R4001

10K_0402_5%

1 2

RX540@

R4002

10K_0402_5%

1 2

R3892

R3999

10K_0402_5%

1 2

@

R2624

R4000

10K_0402_5%

1 2

AGPIO7 AGPIO10 AGPIO12 AGPIO69

BR

32.768KMHz CRYSTAL

32K_X1

12

1

C682

22P_0402_50V8J

2

Y3

12

R954

10K_0402_5%

12

@

R2621

2K_0402_5%

E

32K_X2

SYS_RST#

<INT PU>

NORMAL

RESET MODE

(DEFAULT)

SHORT RST

MODE

9 50Tuesday, May 02, 2017

9 50Tuesday, May 02, 2017

9 50Tuesday, May 02, 2017

32.768KHZ_12.5PF_Q13FC135000040

12

R914

20M_0402_5%

1

C686

18P_0402_50V8J

2

RTC_CLK

<INT PU>

COIN BATT

ON BOARD

(DEFAULT)

COIN BATT

NOT ON

BOARD

12

12

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

BLINK/AGPIO11

<INT PU>

LDT_RST#/PG

OUTPUT TO

APU

(DEFAULT)

OUTPUT

TO PADS

12

R949

10K_0402_5%

@

R2619

2K_0402_5%

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

C5V08/D5PR8_LA-E903PR1A

R951

10K_0402_5%

12

@

R2620

2K_0402_5%

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

FP4 GPIO/AZ/MISC/STRAPS

FP4 GPIO/AZ/MISC/STRAPS

FP4 GPIO/AZ/MISC/STRAPS

+3VALW

UMA@

10K_0402_5%

1 2

DIS@

10K_0402_5%

1 2

1.A

1.A

1.A

A

SATA_ATX_DRX_P0<30>

1 1

HDD

SSD

12

12

12

DEVSLP0

DEVSLP1

AGPIO130

R3852 10K_0402_5%

R3853 10K_0402_5%

R3882 10K_0402_5%

SATA_ATX_DRX_N0<30>

SATA_ARX_DTX_N0<30>

SATA_ARX_DTX_P0<30>

SATA_ATX_DRX_P1<30>

SATA_ATX_DRX_N1<30>

SATA_ARX_DTX_N1<30>

SATA_ARX_DTX_P1<30>

R90 1K_0402_1%

R96 1K_0402_1%

+0.95VS

DEVSLP1<30>

+3VS

12

@

R3872 10K_0402_5%

+3VALW

R3873 10K_0402_5%

2 2

+1.8VS

R634 10K_0402_5%

R635 10K_0402_5%

R636 10K_0402_5%

R637 10K_0402_5%

R638 10K_0402_5%

3 3

CLKRUN#

12

LPCPD#

APU_SPI_HOLD#

12

APU_SPI_W P#

12

APU_SPI_CS1#

12

APU_SPI_CS2#

12

APU_SPI_TPMCS#

12

VGA

LAN+CR

WLAN

PCIE_SSD

CLK_PEG_VGA<15>

CLK_PEG_VGA#<15>

CLK_PCIE_LAN<28>

CLK_PCIE_LAN#<28>

CLK_PCIE_WLAN<29>

CLK_PCIE_WLAN#<29>

CLK_PCIE_SSD<30>

CLK_PCIE_SSD#<30>

LPC_CLK0_EC<9,24>

LPC_CLK1<9,33>

LPC_AD0<24,33>

LPC_AD1<24,33>

LPC_AD2<24,33>

LPC_AD3<24,33>

LPC_FRAME#<9,24,33>

SERIRQ<24,33>

CLKRUN#<33>

APU_SPI_CLK APU_SPI_CLK_R

1 2

RS@

R106

0_0402_5%

8MB SPI ROM

12

12

1 2

R107 0_0402_5%RS@

1 2

R108 0_0402_5%RS@

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

SERIRQ

CLKRUN#

LPCPD#

APU_SPI_CS1#

APU_SPI_CS2#

APU_SPI_MISO

APU_SPI_MOSI

APU_SPI_W P#

APU_SPI_HOLD#

APU_SPI_TPMCS#

B

SATA_ATX_DRX_P0

SATA_ATX_DRX_N0

SATA_ARX_DTX_N0

SATA_ARX_DTX_P0

SATA_ATX_DRX_P1

SATA_ATX_DRX_N1

SATA_ARX_DTX_N1

SATA_ARX_DTX_P1

SATA_ZVSS

SATA_ZVDD

DEVSLP0

DEVSLP1

AGPIO130

CLK_PEG_VGA

CLK_PEG_VGA#

CLK_PCIE_LAN

CLK_PCIE_LAN#

CLK_PCIE_WLAN

CLK_PCIE_WLAN#

CLK_PCIE_SSD

CLK_PCIE_SSD#

48M_X1

48M_X2

UAPU1E

AU3

SATA_TX0P

AU4

SATA_TX0N

AV1

SATA_RX0N

AV2

SATA_RX0P

AY2

SATA_TX1P

AY1

SATA_TX1N

AW4

SATA_RX1N

AW3

SATA_RX1P

AW1

SATA_ZVSS

AW2

SATA_ZVDDP

AT17

DEVSLP[0]/EGPIO67

AT12

DEVSLP[1]/EGPIO70

BB15

SATA_ACT_L/AGPIO130

AU2

SATA_X1

AU1

SATA_X2

U4

GFX_CLKP

U3

GFX_CLKN

U1

GPP_CLK0P

U2

GPP_CLK0N

W4

GPP_CLK1P

W3

GPP_CLK1N

W1

GPP_CLK2P