Acer LA 4921P Diagram

A

1 1

B

C

D

E

Compal Confidential

2 2

KBLG0 Schematics Document

AMD Puma : Griffin Processor with RS780MN/SB700/M92-M2 XT

Tigris : Caspian Processor with RS880M/SB710/M92-M2 XT

3 3

2009-03-11

REV:1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

E

0.1

0.1

1 57Wednesday, March 11, 2009

1 57Wednesday, March 11, 2009

1 57Wednesday, March 11, 2009

0.1

A

Compal Confidential

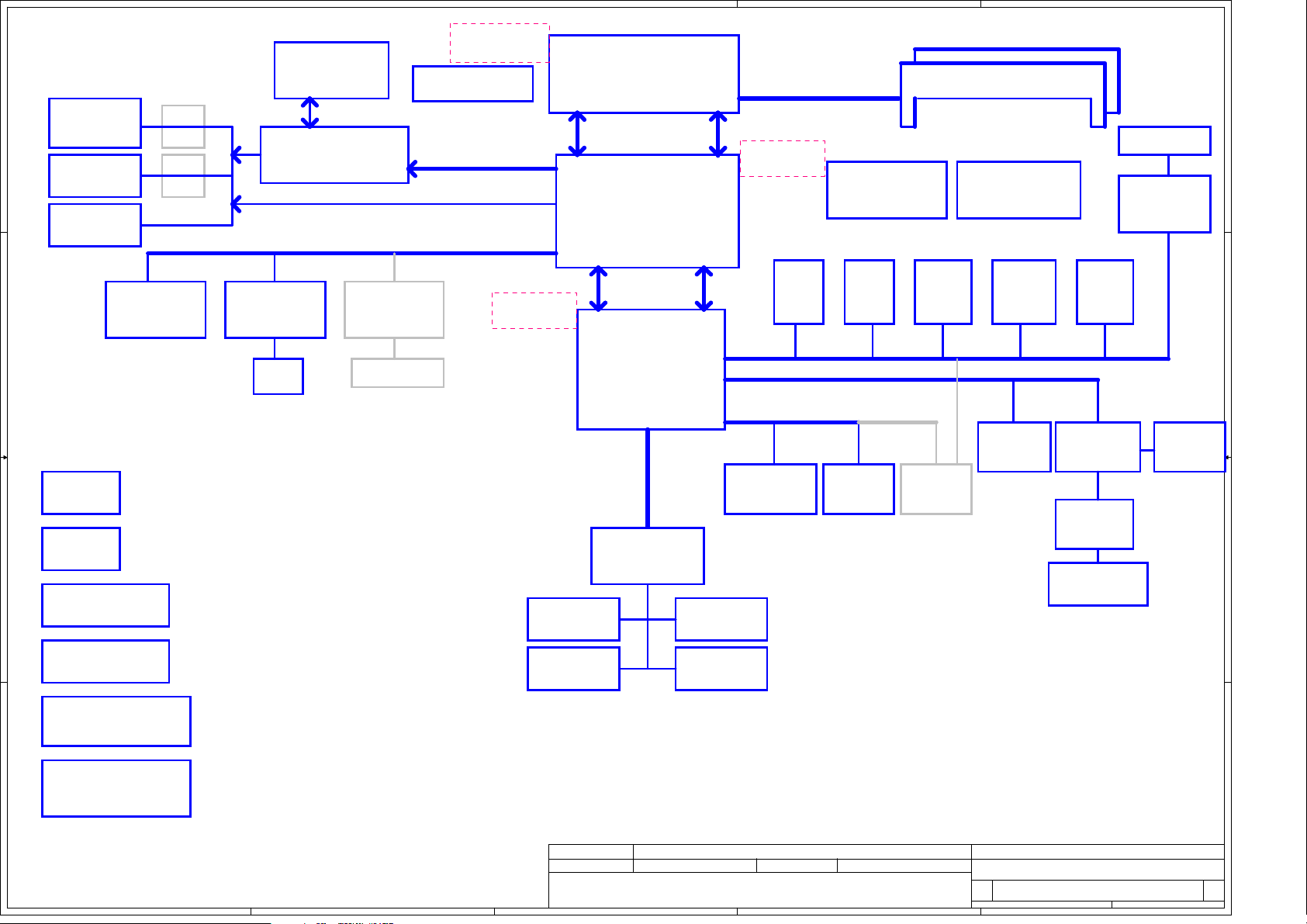

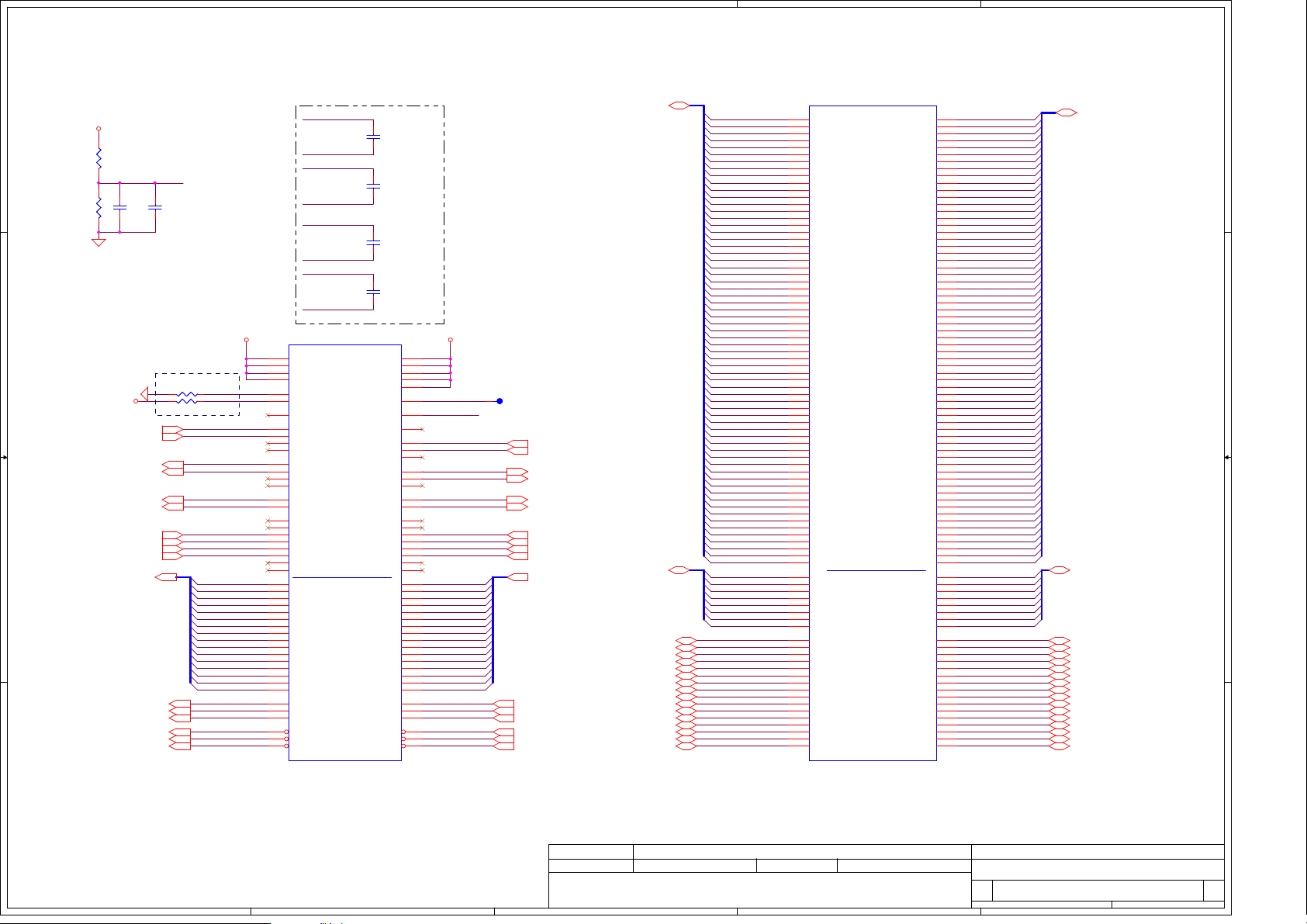

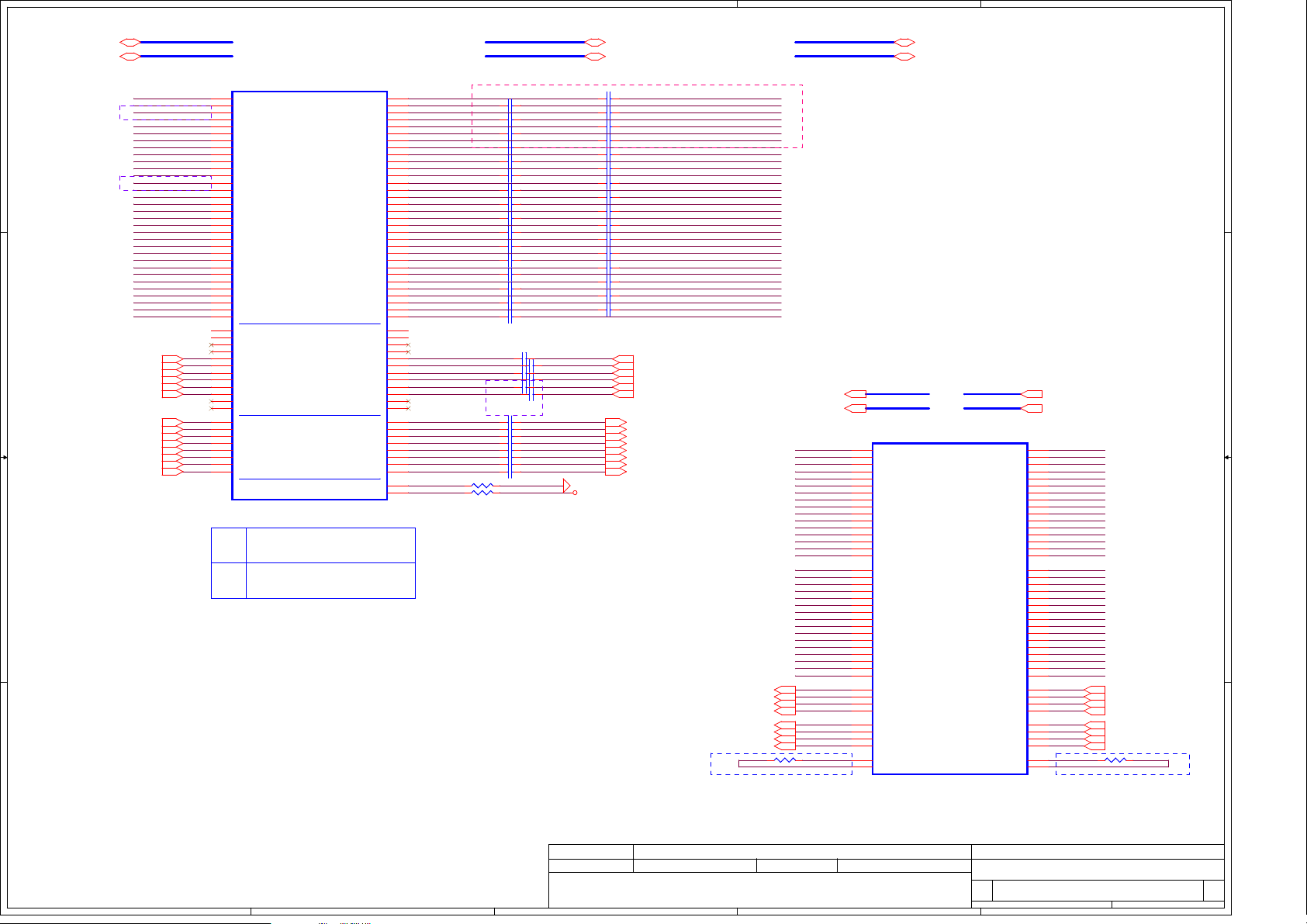

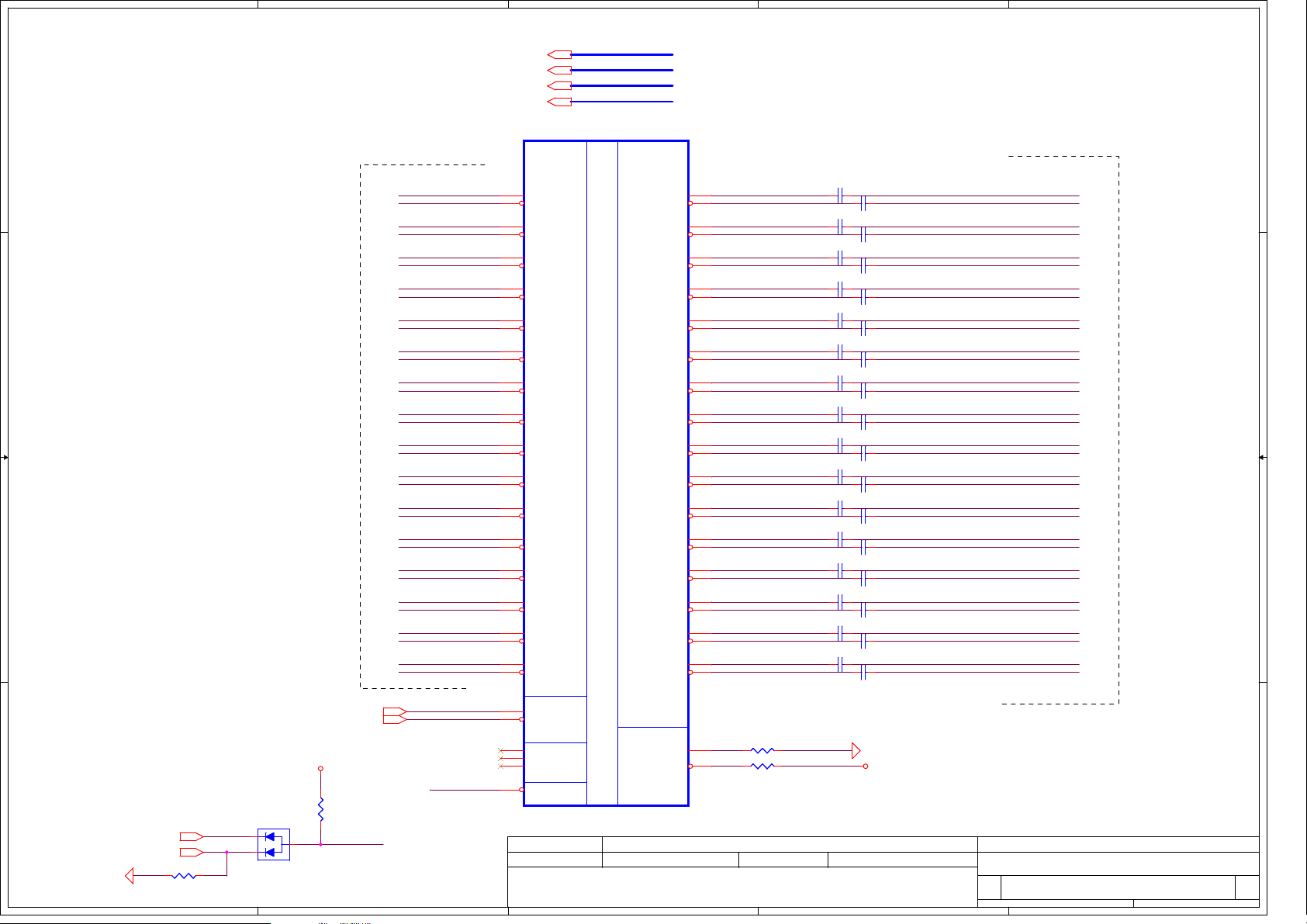

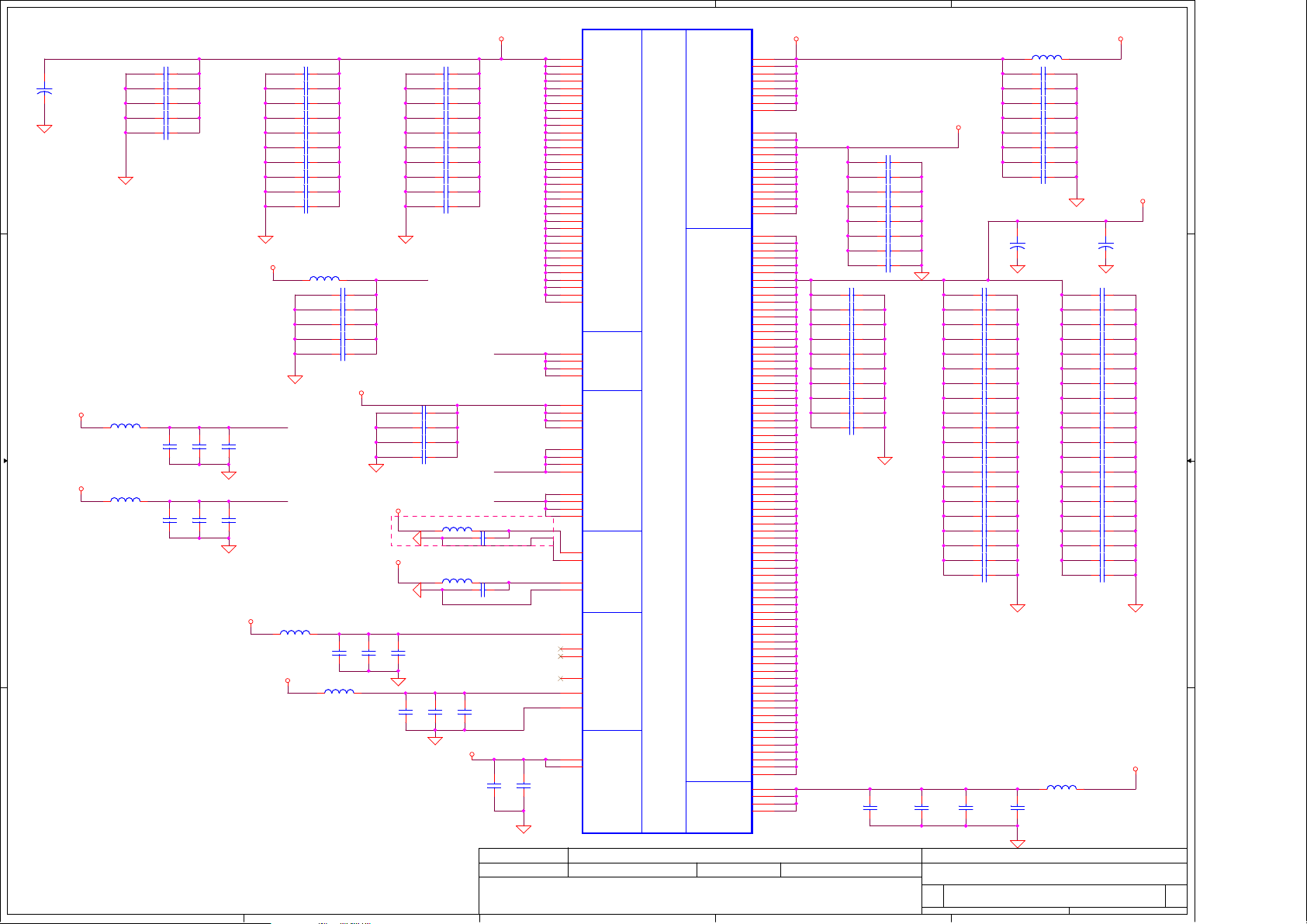

Model Name : KBLG0

PowerXpress (MUX)

1 1

2 2

3 3

LCD (LED BL)

page 24

CRT

page 26

HDMI Conn.

page 25

MINI Card x1

WLAN

page 36

LED

page 40

RTC CKT.

page 26

LID SW / MEDIA/B

page 39

MUX

(1:2)

MUX

(1:2)

Atheros AR8131

port 3port 2

VRAM 512MB

64M16 x 4

page 19, 20

DDR2 500MHz

ATI M92-M2 XT

uFCBGA-962

Page 14,15,16,17,18,21,22

LAN(GbE) Card Reader

page 34

RJ45

page 35

B

PCI-Express 1x

option2

JMB385

page 33

port 4

5 in 1 socket

page 33

Tigris

AMD S1G3 Processor

uPGA-638 Package

Caspian

Fan Control

page 44

PCI-Express 16x

Gen2

ATI SB710

uFCBGA-528

C

Puma

AMD S1G2 Processor

uPGA-638 Package

Griffin

Hyper Transport Link

16 x 16

page 4,5,6,7

ATI RS780MN

uFCBGA-528

page 10,11,12,13

A link Express2

ATI SB700

uFCBGA-528

page 27,28,29,30,31

LPC BUS

ENE KB926

page 38

Touch Pad

page 39

Int.KBD

Memory BUS(DDRII)

Dual Channel

1.8V DDRII 667/800

ATI RS880M

uFCBGA-528

page 36,37 page 27 page 37 page 36 page 36

USB

conn

X 2

USB port 0,6

3.3V 48MHz

3.3V 24.576MHz/48Mhz

S-ATA

USB

SATA HDD

Conn.

page 32

port 0

page 39

D

200pin DDRII-SO-DIMM X2

BANK 0, 1, 2, 3

Thermal Sensor

ADM1032

page 6 page 23

CMOS

Camera

Bluetooth

Conn

Clock Generator

SLG8SP626VTR

USB port 3 USB port 12 USB port 13 USB port 8

HD Audio

USB port 1

MDC 1.5

Conn

CDROM

Conn.

page 32

port 1

ESATA

Conn.

page 37

port 2

page 8,9

Finger

printer

AES1610

page 41

Mini

card

(WL)X1

HDA Codec

ALC888

Audio AMP

Phone Jack x3

E

page 42

page 43

page 43

5 in 1 socket

page 33

Card Reader

RTS5159

page 33

option1

USB port 4

Digital MIC

page 42

Power On/Off CKT.

page 41

EC I/O Buffer

page 38

BIOS

page 39

DC/DC Interface CKT.

page 45

Power Circuit

4 4

page 46,47,48,49,50,51

52,53,54

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

E

0.1

0.1

2 57Wednesday, March 11, 2009

2 57Wednesday, March 11, 2009

2 57Wednesday, March 11, 2009

0.1

A

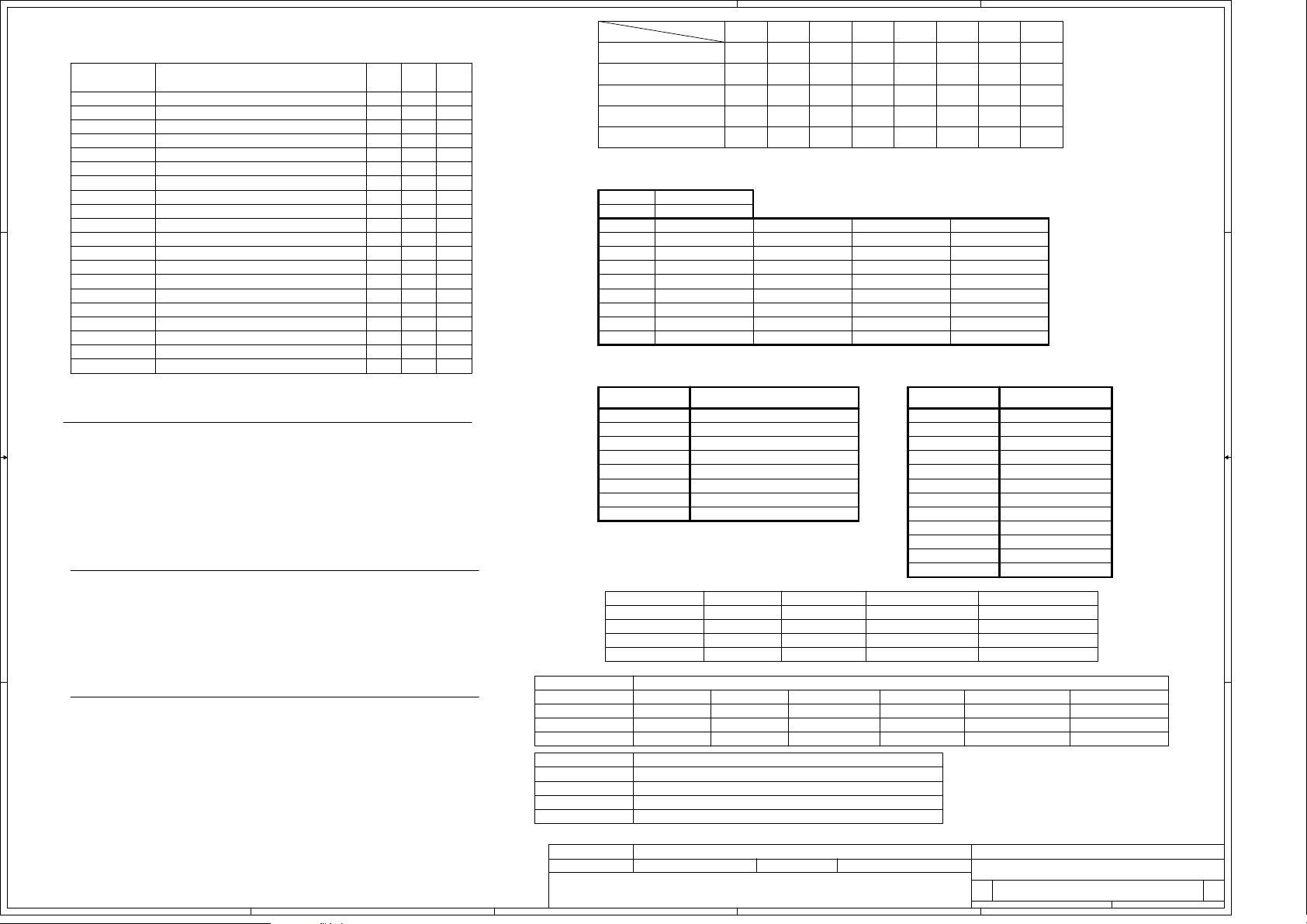

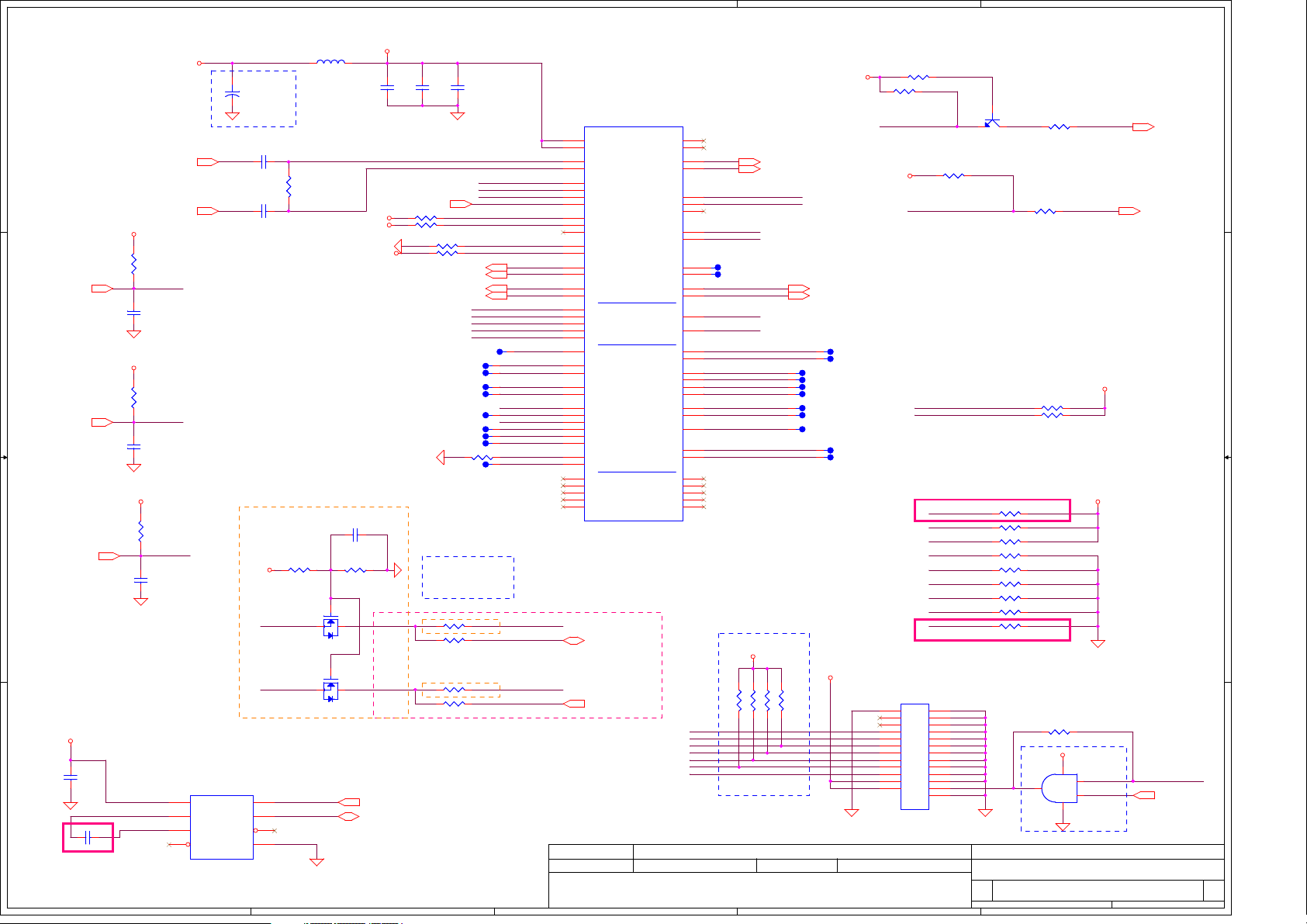

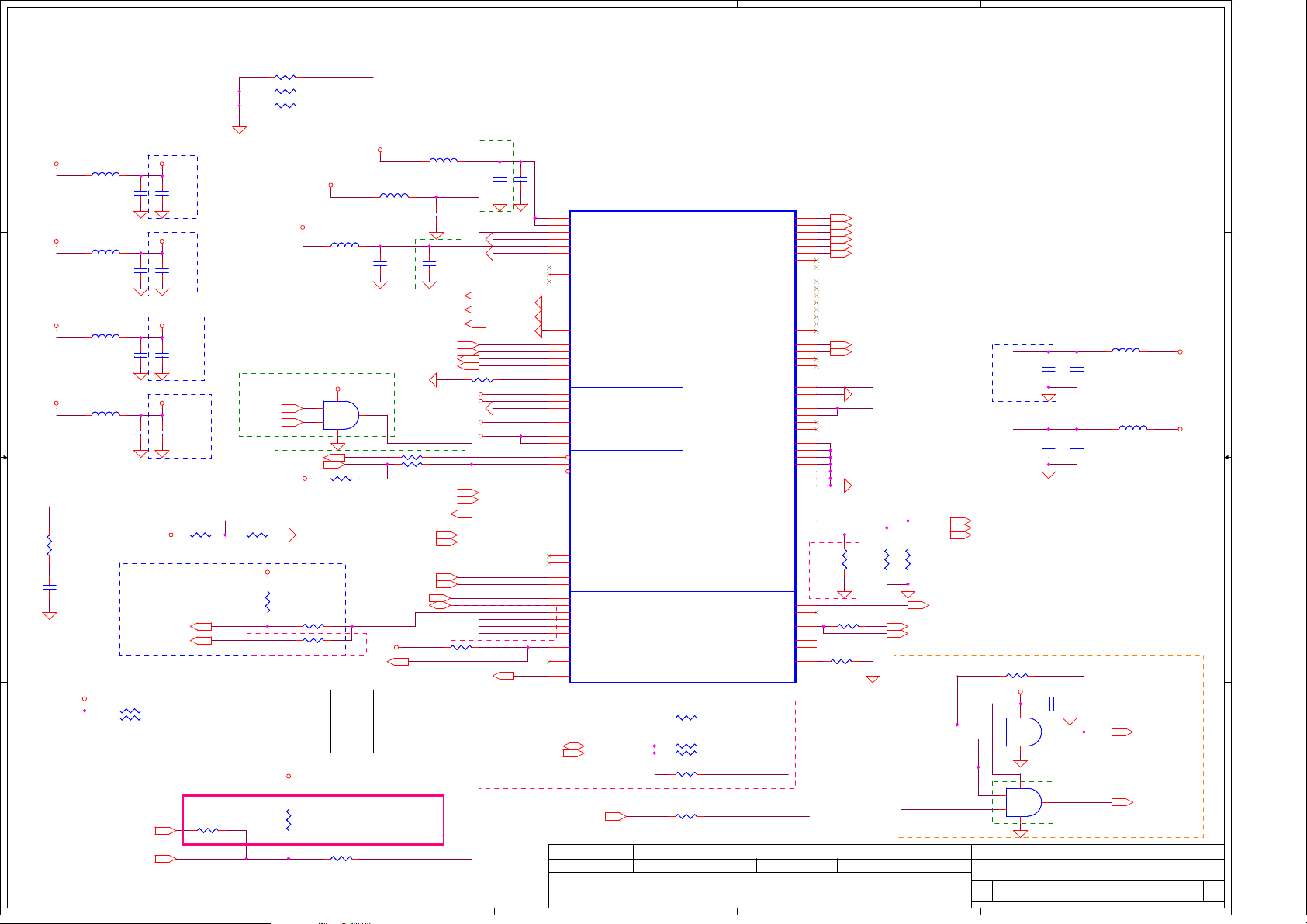

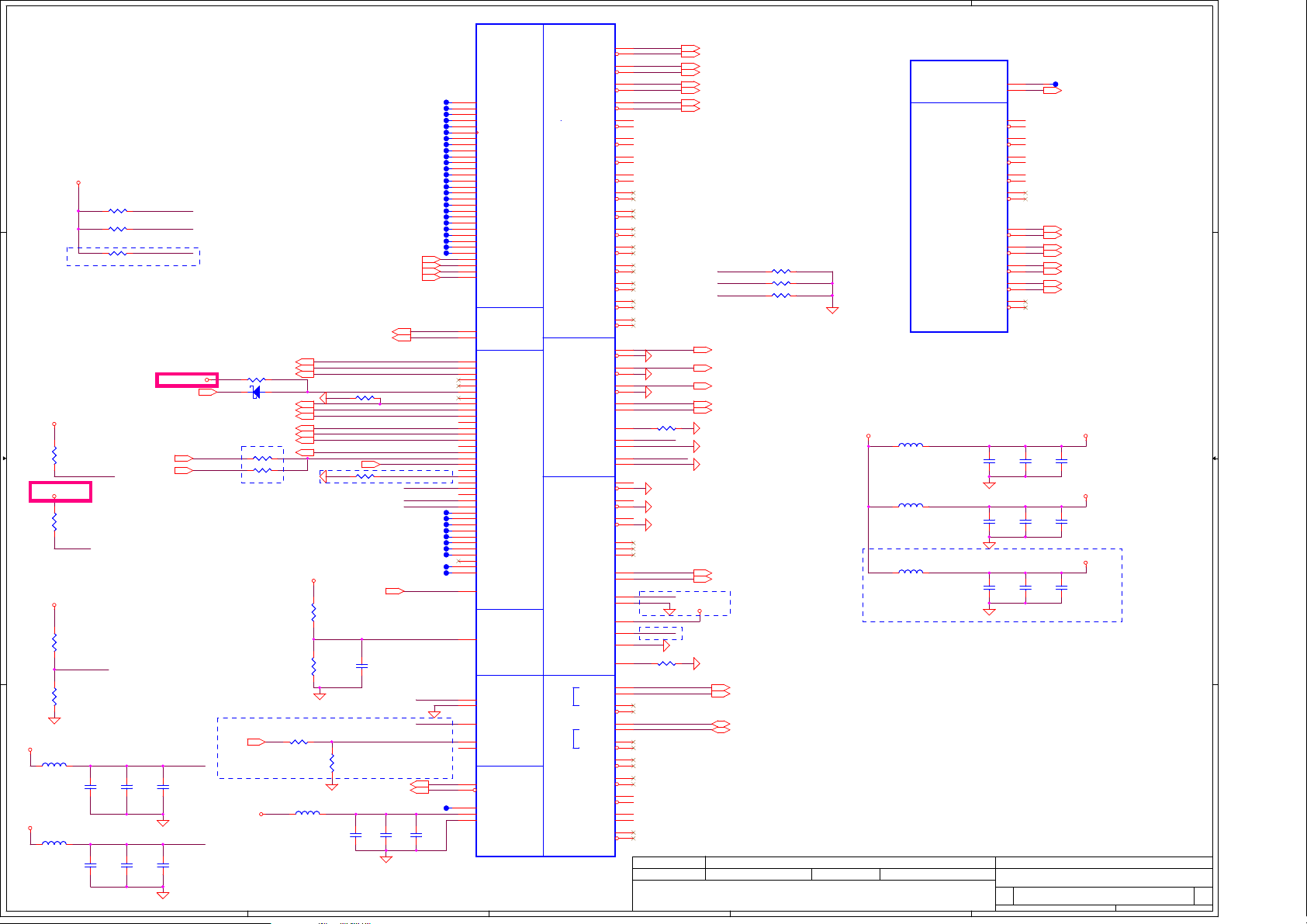

Voltage Rails

Power Plane Description

VIN

1 1

2 2

B+

+CPU_CORE_0

+CPU_CORE_1 Core voltage for CPU (0.7-1.2V)

+CPU_CORE_NB Voltage for On-die Northbridge of CPU(0.8-1.1V)

+0.9V 0.9V switched power rail for DDR terminator

+1.1VS

+1.2V_HT 1.2V switched power rail ON OFF OFF

+VGA_CORE OFFOFFON

+1.5VS

+1.8V

+1.8VS 1.8V switched power rail

+2.5VS

+3VALW

+3V_LAN 3.3V power rail for LAN ON ON ON

+3VS

+5VALW

+5VS

+VSB VSB always on power rail ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU (0.7-1.2V)

1.1V switched power rail for NB VDDC & VGA

0.95-1.2V switched power rail

1.5V power rail for PCIE Card

1.8V power rail for CPU VDDIO and DDR

2.5V for CPU_VDDA

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

External PCI Devices

Device IDSEL#

REQ#/GNT#

B

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON OFF OFF

OFF OFF

ON

ON

ON

OFF

ON

OFF

ON

ON ON*

ON

OFF

ON

ON

ON

OFF

ON

ON

Interrupts

N/AN/AN/A

OFF

OFF

OFF

OFF

OFF

OFF

ON*

OFFON

ONON

C

STATE

SIGNAL

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

D

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON ON

ON

ON

ON

ON

ON

OFF

ON

ON

OFF

OFF

OFF

OFF

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

V typ

AD_BID

V

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

max

BOARD ID Table BTO Option Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

0.2

0.3

0.4

1.0

BTO Item BOM Structure

Discrete

UMA UMA@

VRAM STRAP VRAM@

LAN 8121 8121@

LAN 8131 8131@

HDT debug HDT@

JMB385 CR JMB385@

E

LOW

OFF

OFF

OFF

VGA@

M92@M92-M2 XT

RTS5159 CR RTS5159@

FOR PUMA PUMA@

3 3

EC SM Bus1 address

Device

Smart Battery

Address Address

HEX

16H

SB700

SM Bus 0 address

Device

Clock Generator

(SILEGO SLG8SP626)

DDR DIMM1

DDR DIMM2

Mini card

4 4

Address

1101 001Xb

1001 000Xb

1001 010Xb

HEX

D2

90

94

EC SM Bus2 address

Device

ADI ADM1032 (CPU)

GMT G781-1 (GPU)

SB-Temp Sensor

1001 100X b0001 011X b

1001 101X b

SB700

SM Bus 1 address

Device Address

New card

HEX

98H

9AH

9CH

IGP only mode

PowerXpress mode

IGP only mode

PowerXpress mode

PX_GPIO0

IGP only mode

PX_GPIO1

Enable +1.1VS_PXFunction Description

H : Enable Reserved H : Enable

Trigger from SB to Enable (PX_GPIO1/PX_+3VS/PX_+1.8VS/PX_+VGA_CORE)Function Description

dGPU_ResetFunction Description

PX MODE SWITCH

XX

KB926

PX_GPIO1_SB

X

H : Enable

PX_GPIO1

dGPU_PWR_Enable

XX

H : EnableH : Enable

KB926

PX_+3VSPX_GPIO2

Enable +3VS_DELAY

X

L : iGPU(DC) / H : dGPU(AC)

FOR TIGRIS TIGRIS@

FOR TEST UB@

RS780MNSB700 SB700

PX_GPIO2

PX Mode Switch

X

PX_+1.8VS

Enable +1.8VS_PX

X

H : Enable

PX_+VGA_CORE

Enable +VGA_CORE

DISPLAY OUTPUT

LVDS / CRTPowerXpress mode

X

H : Enable

PX_GPIO2_NB

Trigger from SB

X

Reserved

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

E

0.1

0.1

3 57Wednesday, March 11, 2009

3 57Wednesday, March 11, 2009

3 57Wednesday, March 11, 2009

0.1

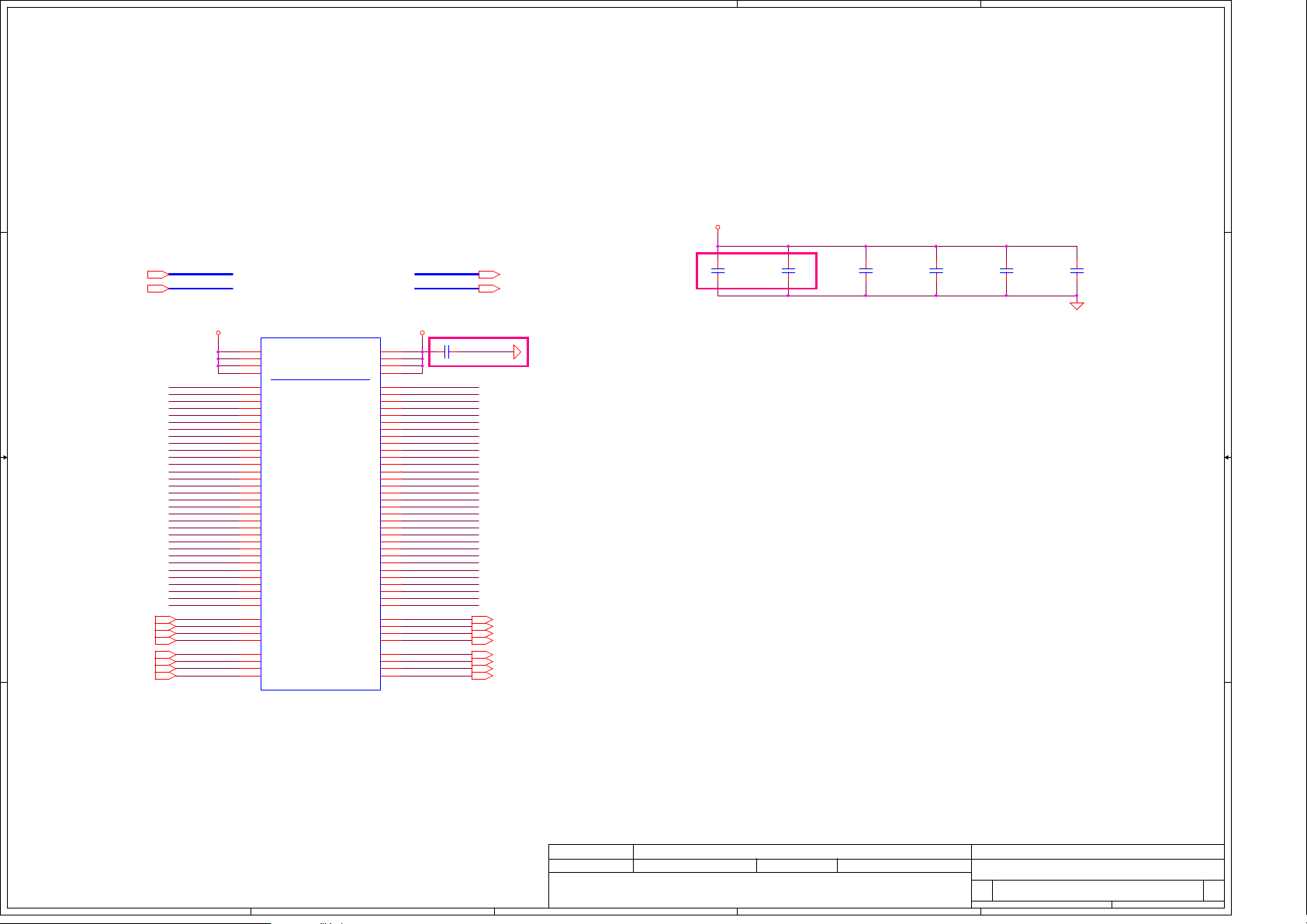

A

1 1

B

C

D

E

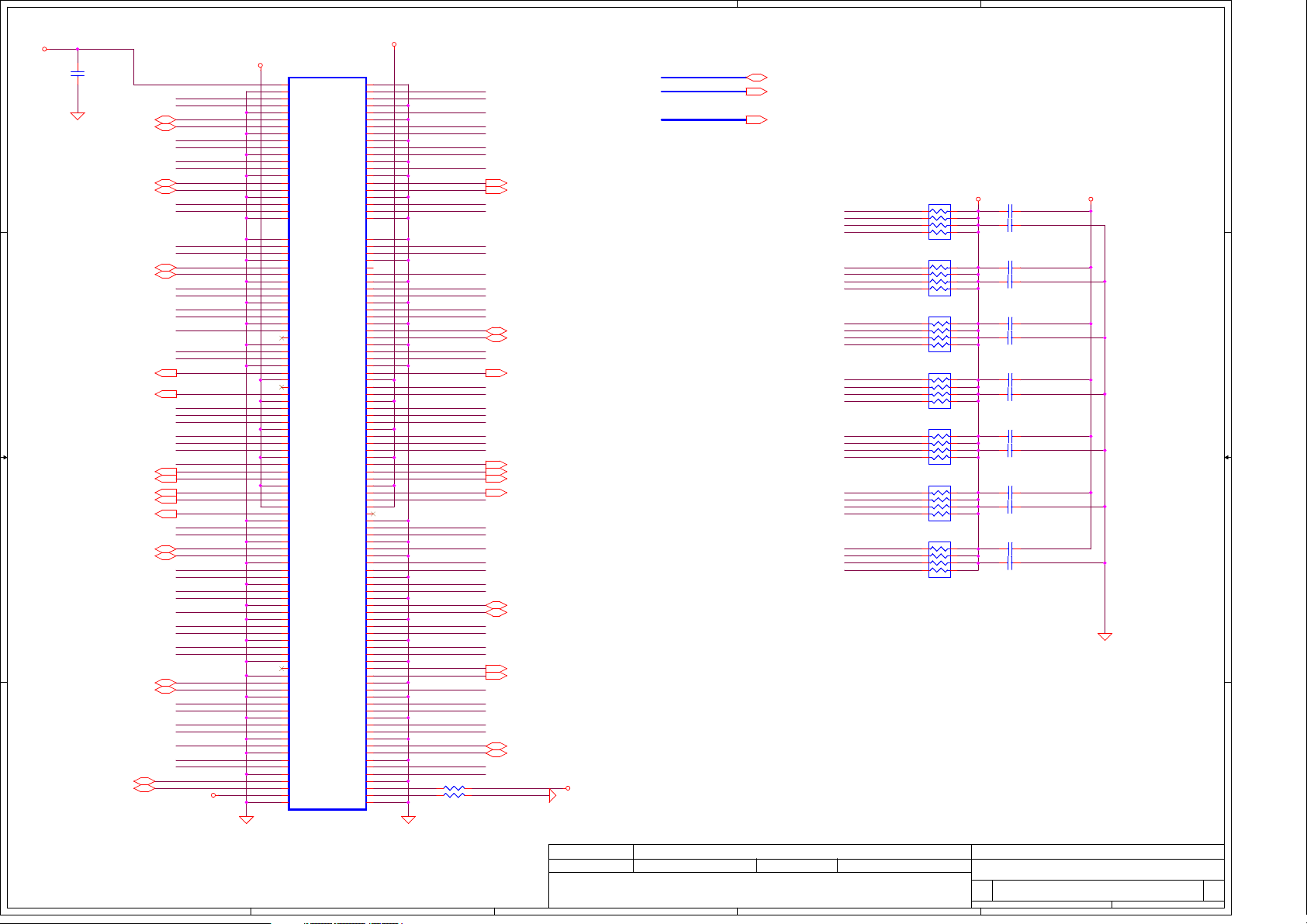

+1.2V_HT

250 mil

1

C727

C727

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

PUMA@

PUMA@

Change as 10U

for Tigris

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

+1.2V_HT

H_CADOP[0..15]

H_CADON[0..15]

Change as 10U

for Tigris

PUMA@

PUMA@

1 2

C664 4.7U_0805_10V4Z

C664 4.7U_0805_10V4Z

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

H_CADOP[0..15] 10

H_CADON[0..15] 10H_CADIN[0..15]10

H_CLKOP0 10

H_CLKON0 10

H_CLKOP1 10

H_CLKON1 10

H_CTLOP0 10

H_CTLON0 10H_CTLIN010

H_CTLON1 10

H_CADIP[0..15]10

2 2

3 3

H_CLKIP010

H_CLKIN010

H_CLKIP110

H_CLKIN110

H_CTLIP010

H_CTLIP110 H_CTLOP1 10

H_CTLIN110

H_CADIP[0..15]

H_CADIN[0..15]

VLDT=1.5A

+1.2V_HT

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

D1

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

6090022100G_B

6090022100G_B

JCPU1A

JCPU1A

HT LINK

HT LINK

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

conn@

conn@

1

C666

C666

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

PUMA@

PUMA@

VLDT CAP.

1

C725

C725

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

Near CPU Socket

1

2

C726

C726

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

C722

C722

180P_0402_50V8J

180P_0402_50V8J

2

1

C668

C668

180P_0402_50V8J

180P_0402_50V8J

2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

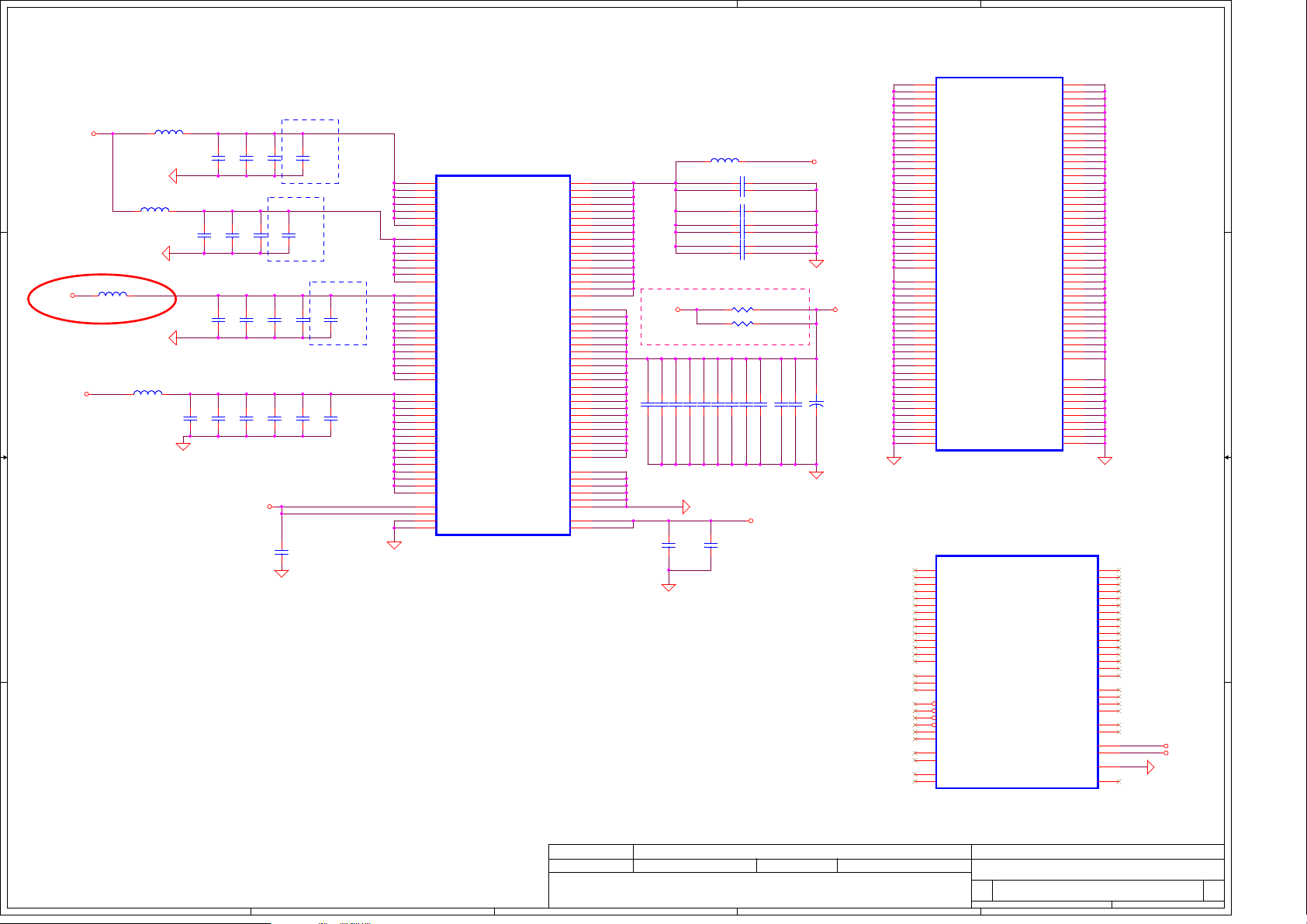

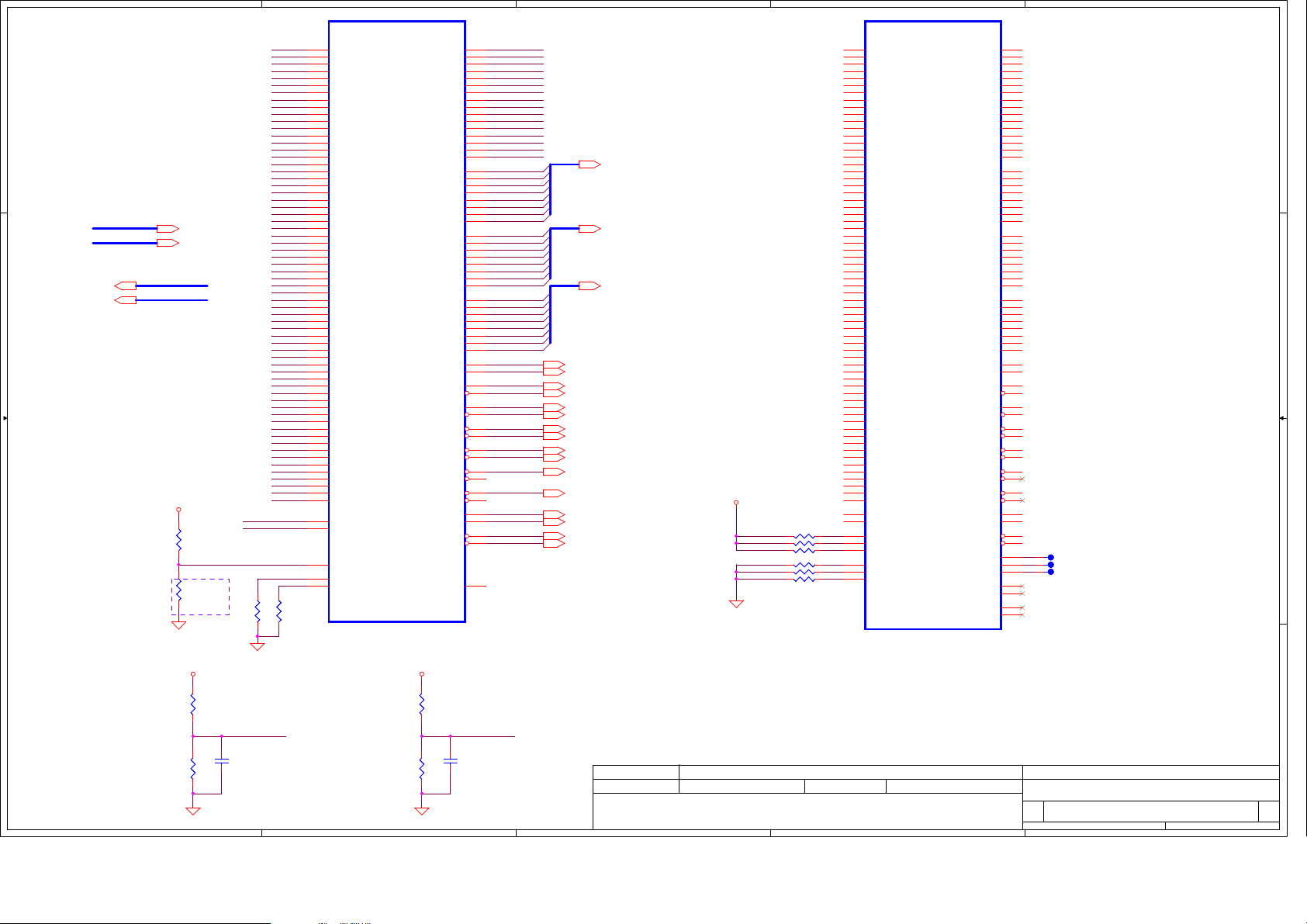

AMD CPU S1G2 HT I/F

AMD CPU S1G2 HT I/F

AMD CPU S1G2 HT I/F

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

4 57Wednesday, March 11, 2009

4 57Wednesday, March 11, 2009

4 57Wednesday, March 11, 2009

E

0.1

0.1

0.1

A

B

C

D

E

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

AD10

AF10

AE10

AA16

D10

C10

B10

H16

T19

V22

U21

V19

T20

U19

U20

V20

N19

N20

E16

F16

Y16

P19

P20

N21

M20

N22

M19

M22

M24

K22

R21

K20

V24

K24

K19

R20

R23

R19

T22

T24

J22

J20

L20

L21

L19

L22

J21

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

VTT1

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

VTT2

VTT3

VTT4

MEMZP

MEMZN

RSVD_M1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CLK_H2

MA_CLK_L2

MA_CLK_H3

MA_CLK_L3

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

6090022100G_B

6090022100G_B

conn@

conn@

JCPU1B

JCPU1B

1

2

1

2

1

2

1

2

VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

C379

C379

1.5P_0402_50V9C

1.5P_0402_50V9C

C111

C111

1.5P_0402_50V9C

1.5P_0402_50V9C

C380

C380

1.5P_0402_50V9C

1.5P_0402_50V9C

C112

C112

1.5P_0402_50V9C

1.5P_0402_50V9C

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

+0.9V+0.9V

VTT_SENSE

+MCH_REF

DDRB_ODT0

DDRB_ODT1

DDRB_SCS1#

DDRB_CKE0

DDRB_CKE1

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#DDRA_CLK1#

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SMA13

DDRB_SMA14

DDRB_SMA15

DDRB_SBS0#

DDRB_SBS1#

DDRB_SBS2#

DDRB_SRAS#

DDRB_SCAS#

DDRB_SWE#

T4PAD T4PAD

DDRB_ODT0 9

DDRB_ODT1 9

DDRB_SCS1# 9

DDRB_CKE0 9

DDRB_CKE1 9

DDRB_CLK0 9

DDRB_CLK0# 9

DDRB_CLK1 9

DDRB_CLK1# 9

DDRB_SBS0# 9

DDRB_SBS1# 9

DDRB_SBS2# 9

DDRB_SRAS# 9

DDRB_SCAS# 9

DDRB_SWE# 9

1 1

2 2

3 3

4 4

+1.8V

R78

R78

1K_0402_1%

1K_0402_1%

1 2

+MCH_REF

1

R79

R79

1K_0402_1%

1K_0402_1%

1 2

Place them clos e to CPU within 1"

DDRA_SMA[15..0]8 DDRB_SMA[15..0] 9

1

C178

C178

C177

2

C177

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1000P_0402_25V8J

1000P_0402_25V8J

VTT=0.75A

R77 39.2_0402_1%R77 39.2_0402_1%

1 2

+1.8V

DDRA_ODT08

DDRA_ODT18

DDRA_SCS0#8

DDRA_SCS1#8 DDRB_SCS0# 9

DDRA_CKE08

DDRA_CKE18

DDRA_CLK08

DDRA_CLK0#8

DDRA_CLK18

DDRA_CLK1#8

DDRA_SBS0#8

DDRA_SBS1#8

DDRA_SBS2#8

DDRA_SRAS#8

DDRA_SCAS#8

DDRA_SWE#8

1 2

R76 39.2_0402_1%R76 39.2_0402_1%

DDRA_ODT0

DDRA_ODT1

DDRA_SCS0#

DDRA_SCS1# DDRB_SCS0#

DDRA_CKE0

DDRA_CKE1

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SMA15

DDRA_SBS0#

DDRA_SBS1#

DDRA_SBS2#

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

DDRB_SDQ[63..0]9

DDRB_SDM[7..0]9 DDRA_SDM[7..0] 8

DDRB_SDQS09

DDRB_SDQS0#9

DDRB_SDQS19

DDRB_SDQS1#9

DDRB_SDQS29

DDRB_SDQS2#9

DDRB_SDQS39

DDRB_SDQS3#9

DDRB_SDQS49

DDRB_SDQS4#9

DDRB_SDQS59

DDRB_SDQS5#9

DDRB_SDQS69

DDRB_SDQS6#9

DDRB_SDQS79

DDRB_SDQS7#9

Processor DDR2 Memory Interface

JCPU1C

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

DDRB_SDM0

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS7

DDRB_SDQS7#

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

JCPU1C

6090022100G_B

6090022100G_B

conn@

conn@

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MEM:DATA

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_SDQ[63..0] 8

DDRA_SDQS0 8

DDRA_SDQS0# 8

DDRA_SDQS1 8

DDRA_SDQS1# 8

DDRA_SDQS2 8

DDRA_SDQS2# 8

DDRA_SDQS3 8

DDRA_SDQS3# 8

DDRA_SDQS4 8

DDRA_SDQS4# 8

DDRA_SDQS5 8

DDRA_SDQS5# 8

DDRA_SDQS6 8

DDRA_SDQS6# 8

DDRA_SDQS7 8

DDRA_SDQS7# 8

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

AMD CPU S1G2 DDRII I/F

AMD CPU S1G2 DDRII I/F

AMD CPU S1G2 DDRII I/F

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

5 57Thursday, February 19, 2009

5 57Thursday, February 19, 2009

5 57Thursday, February 19, 2009

E

0.1

0.1

0.1

A

B

C

D

E

1 2

C92 0.1U_0402_16V4Z@C92 0.1U_0402_16V4Z@

R53

R53

34.8K_0402_1%

34.8K_0402_1%

@

@

2

13

D

D

2

13

D

D

+2.5VDDA

3300P_0402_50V7K

3300P_0402_50V7K

1

1

C3854.7U_0805_10V4Z C3854.7U_0805_10V4Z

2

2

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_LDT_REQ#11

R70 2.2K_0402_5%R70 2.2K_0402_5%

+1.8V

+1.8V

R71 2.2K_0402_5%R71 2.2K_0402_5%

R82 44.2_0402_1%R82 44.2_0402_1%

R89 44.2_0402_1%R89 44.2_0402_1%

+1.2V_HT

12

EC_SMB_DA

DVT

EC_SMB_CK

EC_SMB_CK2 22,38

EC_SMB_DA2 22,38

B

VDDA=0.25A

1

C384

C384

C319

C319

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

LDT_RST#

H_PWRGD

LDT_STOP#

12

12

1 2

1 2

CPU_VDD0_FB_H53

CPU_VDD0_FB_L53

CPU_VDD1_FB_H53

CPU_VDD1_FB_L53

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

T44 PADT44 PAD

T25 PADT25 PAD

T26 PADT26 PAD

T37 PADT37 PAD

T33 PADT33 PAD

T43 PADT43 PAD

T42 PADT42 PAD

T3 PADT3 PAD

T41 PADT41 PAD

R330 0_0402_5%R 330 0_0402_5 %

1 2

T2 PADT2 PAD

FDV301N, the Vgs is:

min = 0.65V

Typ = 0.85V

Max = 1.5V

2.09V for Gate

@

@

1 2

R479 0_0402_5%

R479 0_0402_5%

@

@

1 2

R484 0_0402_5%

R484 0_0402_5%

@

@

1 2

R480 0_0402_5%

R480 0_0402_5%

@

@

1 2

R485 0_0402_5%

R485 0_0402_5%

JCPU1D

JCPU1D

CPU_SIC

CPU_SID

CPU_HTREF0

CPU_HTREF1

CPU_VDD0_FB_H

CPU_VDD0_FB_L

CPU_VDD1_FB_H

CPU_VDD1_FB_L

CPU_TEST23

CPU_TEST18

CPU_TEST19

CPU_TEST25H

CPU_TEST25L

CPU_TEST21

CPU_TEST20

CPU_TEST24

CPU_TEST22

CPU_TEST12

CPU_TEST27

CPU_TEST6

EC_SMB_DA2

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_CK1

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

AB6

VDD1_FB_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

6090022100G_B

6090022100G_B

conn@

conn@

EC_SMB_DA1 38,47

EC_SMB_CK1 38,47

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

KEY1

KEY2

SVC

SVD

MEMHOT_L

THERMDC

THERMDA

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

M11

W18

CPU_SVC

A6

CPU_SVD

A4

CPU_THERMTRIP#_R

AF6

H_PROCHOT#

AC7

AA8

THERMDC_CPU

W7

THERMDA_CPU

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

T6PAD T6PAD

T5PAD T5PAD

CPU_VDDNB_FB_H

CPU_VDDNB_FB_L

CPU_DBREQ#

CPU_TDO

CPU_TEST28_H_PLLCHRZ _P

CPU_TEST28_L_PLLCHRZ_N

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST7

CPU_TEST10

CPU_TEST8

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

+1.8V

R117220_0402_5%

R117220_0402_5%

12

CPU_DBREQ#

CPU_DBRDY

HDT@

HDT@

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

CPU_SVC 53

CPU_SVD 53

R119220_0402_5%

R119220_0402_5%

R118220_0402_5%

R118220_0402_5%

12

12

HDT@

HDT@

HDT@

HDT@

CPU_VDDNB_FB_H 53

CPU_VDDNB_FB_L 53

R120220_0402_5%

R120220_0402_5%

12

HDT@

HDT@

+1.8V

MP(Remove)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.8V

T24PAD T24PAD

T21PAD T21PAD

T34PAD T34PAD

T36PAD T36PAD

T32PAD T32PAD

T38PAD T38PAD

T31PAD T31PAD

T18PAD T18PAD

T67PAD T67PAD

T39PAD T39PAD

T35PAD T35PAD

For Tigris

For Tigris

CONN@ SAMTEC_ASP-68200-07

CONN@

D

1 2

R66 10K_0402_5%R66 10K_0402_5%

1 2

R67 30 0_0402_5%R67 30 0_0402_5%

CPU_THERMTRIP#_R

1 2

+1.8V

R69 30 0_0402_5%R69 30 0_0402_5%

H_PROCHOT#

CPU_SVC

CPU_SVD

CPU_TEST25H

CPU_TEST25L

CPU_DBREQ#

CPU_TEST21

CPU_TEST24

CPU_TEST20

CPU_TEST23

CPU_TEST25H

CPU_TEST25L

JP1

JP1

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

MP(mask)

B

B

2

Q9

Q9

E

E

3 1

C

C

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

TIGRIS@

TIGRIS@

1 2

R144 300_0402_5%

R144 300_0402_5%

1 2

R143 300_0402_5%R143 300_0402_5%

1 2

R327 300_0402_5%R327 300_0402_5%

1 2

R75 30 0_0402_5%R75 30 0_0402_5%

1 2

R74 30 0_0402_5%R74 30 0_0402_5%

1 2

R73 30 0_0402_5%R73 30 0_0402_5%

1 2

R72 30 0_0402_5%R72 30 0_0402_5%

1 2

R136 300_0402_5%R136 300_0402_5%

1 2

R135 300_0402_5%

R135 300_0402_5%

TIGRIS@

TIGRIS@

HDT_RST#

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

R65

R65

1 2

0_0402_5%

0_0402_5%

R68

R68

1 2

0_0402_5%

0_0402_5%

+1.8V

1 2

R328 1K_0402_5%R328 1K_0402_5%

1 2

R329 1K_0402_5%R329 1K_0402_5%

+1.8V

R140

R140

1 2

0_0402_5%@

0_0402_5%@

+3VS

MP(Remove)

5

U15

U15

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

AMD CPU S1G2 CTRL

AMD CPU S1G2 CTRL

AMD CPU S1G2 CTRL

2

P

B

Y

1

A

G

NC7SZ08P5X_NL_SC70-5

NC7SZ08P5X_NL_SC70-5

3

HDT@

HDT@

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

E

H_THERMTRIP# 28

H_PROCHOT_R# 27

LDT_RST#

SB_PWRGD 11,28,41

6 57Wednesday, March 11, 2009

6 57Wednesday, March 11, 2009

6 57Wednesday, March 11, 2009

0.1

0.1

0.1

L35

+2.5VS

1

+

+

C391

C391

150U_B2_6.3VM

150U_B2_6.3VM

1 1

CLK_CPU_BCLK23

CLK_CPU_BCLK#23

+1.8VS

R339

R339

300_0402_5%

300_0402_5%

1 2

LDT_RST#27

2 2

H_PWRGD27

LDT_STOP#11,27

3 3

+3VS

1

C206

C206

4 4

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C194

C194

1 2

2200P_0402_50V7K

2200P_0402_50V7K

PUMA@

PUMA@

Change as 3300pF

For Tigris

LDT_RST#

1

C721

C721

0.01U_0402_25V4Z

0.01U_0402_25V4Z

@

@

2

+1.8VS

R338

R338

300_0402_5%

300_0402_5%

1 2

H_PWRGD

1

C720

C720

0.01U_0402_25V4Z

0.01U_0402_25V4Z

@

@

2

+1.8VS

R337

R337

300_0402_5%

300_0402_5%

1 2

LDT_STOP#

1

C719

C719

0.01U_0402_25V4Z

0.01U_0402_25V4Z

@

@

2

THERMDA_CPU

THERMDC_CPU

A

1

2

3

Address

2

C723

C723

C724 3900P_0402_50V7KC724 3900P_0402_50V7K

DVT2

+3VS

U11

U11

VDD

SCLK

D+

SDATA

ALERT#

D-

THERM#4GND

ADM1032ARMZ_MSOP8

ADM1032ARMZ_MSOP8

1001 100X b

1 2

1 2

8

7

6

5

20K_0402_5%

20K_0402_5%

L35

1 2

FBM_L11_201209_300L_0805

FBM_L11_201209_300L_0805

3900P_0402_50V7K

3900P_0402_50V7K

12

R325

R325

169_0402_1%

169_0402_1%

CPU internal thermal sensor

R52

R52

12

@

@

G

G

CPU_SID

S

S

Q7 FDV301N_NL_SOT23-3@

Q7 FDV301N_NL_SOT23-3@

G

G

CPU_SIC

S

S

Q8 FDV301N_NL_SOT23-3@

Q8 FDV301N_NL_SOT23-3@

EC_SMB_CK2

EC_SMB_DA2

A

VDD(+CPU_CORE) decoupling.

+CPU_CORE_0

1

+

+

C106

1 1

C106

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

+

+

C661

C661

330U_X_2VM_R6M

330U_X_2VM_R6M

2

Near CPU Socket

+CPU_CORE_0

1

C280

C280

22U_0805_6.3V6M

22U_0805_6.3V6M

2

+CPU_CORE_0

1

C253

C253

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

2 2

1

C281

C281

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C276

C276

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

1

C273

C273

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C290

C290

180P_0402_50V8J

180P_0402_50V8J

2

1

C257

C257

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Under CPU Socket

VDDIO decoupling.

+1.8V

1

C195

C195

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C228

C228

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Under CPU Socket

1

C222

C222

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C294

C294

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

B

+CPU_CORE_1

+CPU_CORE_1

1

C214

C214

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C295

C295

180P_0402_50V8J

180P_0402_50V8J

2

1

+

+

C96

C96

330U_X_2VM_R6M

330U_X_2VM_R6M

2

+CPU_CORE_1

1

C274

C274

180P_0402_50V8J

180P_0402_50V8J

2

1

C238

C238

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C244

C244

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

C

VDD0 = 18A VDD1 =18A

JCPU1E

M10

M16

M18

M21

M23

M25

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

N7

N9

N11

K16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

N17

JCPU1E

VDD0_1

VDD0_2

VDD0_3

VDD0_4

VDD0_5

VDD0_6

VDD0_7

VDD0_8

VDD0_9

VDD0_10

VDD0_11

VDD0_12

VDD0_13

VDD0_14

VDD0_15

VDD0_16

VDD0_17

VDD0_18

VDD0_19

VDD0_20

VDD0_21

VDD0_22

VDD0_23

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

6090022100G_B

6090022100G_B

Athlon 64 S1

Processor Socket

conn@

conn@

1

+

+

C643

C643

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

C227

C227

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C184

C184

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

1

C215

C215

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C230

C230

180P_0402_50V8J

180P_0402_50V8J

2

+CPU_CORE_0

VDDNB=4A

(For Tigris)

VDDNB=3A

+CPU_CORE_NB

+1.8V

VDDIO=3A

+CPU_CORE_NB decoupling.

+CPU_CORE_NB

1

C207

C207

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C186

C186

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C249

C249

22U_0805_6.3V6M

22U_0805_6.3V6M

2

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

D

JCPU1F

JCPU1F

AA4

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

+CPU_CORE_1

+1.8V

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AB2

AB7

AB9

AD6

AD8

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

H21

H23

B4

B6

B8

B9

D6

D8

D9

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

J4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

6090022100G_B

6090022100G_B

Athlon 64 S1

Processor Socket

conn@

conn@

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

E

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3 3

4 4

+1.8V

1

C301

C301

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

+1.8V +1.8V

1

C309

C309

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

+1.8V

1

2

Between CPU Socket and DIMM

1

C303

C303

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

180PF Qt'y foll ow the distance between

CPU socket and DIMM0. <2.5inch >

1

C218

C218

180P_0402_50V8J

180P_0402_50V8J

2

1

C208

C208

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

C211

C211

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

C302

C302

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C307

C307

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

1

C209

C209

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C300

C300

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C308

C308

180P_0402_50V8J

180P_0402_50V8J

2

A: Add C165 and C176

to follow AMD L ayout

review recomman d for

EMI

1

C210

C210

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C310

C310

180P_0402_50V8J

180P_0402_50V8J

2

1

C: Change to NB O CAP

+

+

C226

C226

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

C219

C219

180P_0402_50V8J

180P_0402_50V8J

2

VTT decoupling.

220U_D2_4VM_R15

220U_D2_4VM_R15

+0.9V

1

C163

C163

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

+0.9V

1

C387

C387

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C164

C164

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

Near CPU Socket Right side.

1

C386

C386

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C109

C109

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C383

C383

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

+0.9V

Near Power Supply

1

C107

C107

C: Change to NB O CAP

+

+

2

1

C110

C110

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C382

C382

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C113

C113

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C190

C190

1000P_0402_25V8J

1000P_0402_25V8J

2

1

C718

C718

1000P_0402_25V8J

1000P_0402_25V8J

2

1

C191

C191

1000P_0402_25V8J

1000P_0402_25V8J

2

1

C717

C717

1000P_0402_25V8J

1000P_0402_25V8J

2

1

C189

C189

180P_0402_50V8J

180P_0402_50V8J

2

1

C716

C716

180P_0402_50V8J

180P_0402_50V8J

2

1

C173

C173

180P_0402_50V8J

180P_0402_50V8J

2

1

C715

C715

180P_0402_50V8J

180P_0402_50V8J

2

Near CPU Socket Left side.

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

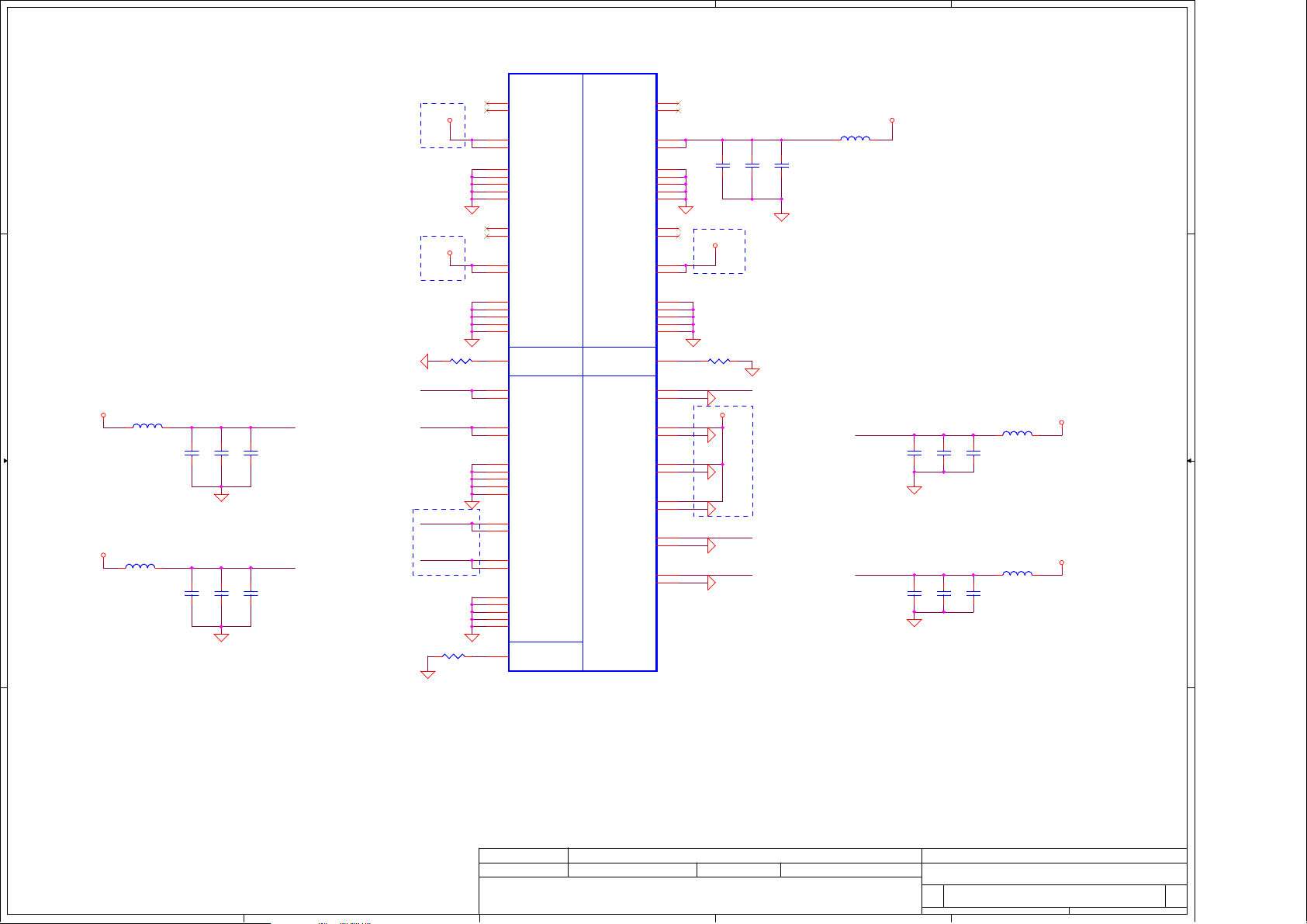

Compal Electronics, Inc.

AMD CPU S1G2 PWR & GND

AMD CPU S1G2 PWR & GND

AMD CPU S1G2 PWR & GND

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

7 57Thursday, January 15, 2009

7 57Thursday, January 15, 2009

7 57Thursday, January 15, 2009

E

0.1

0.1

0.1

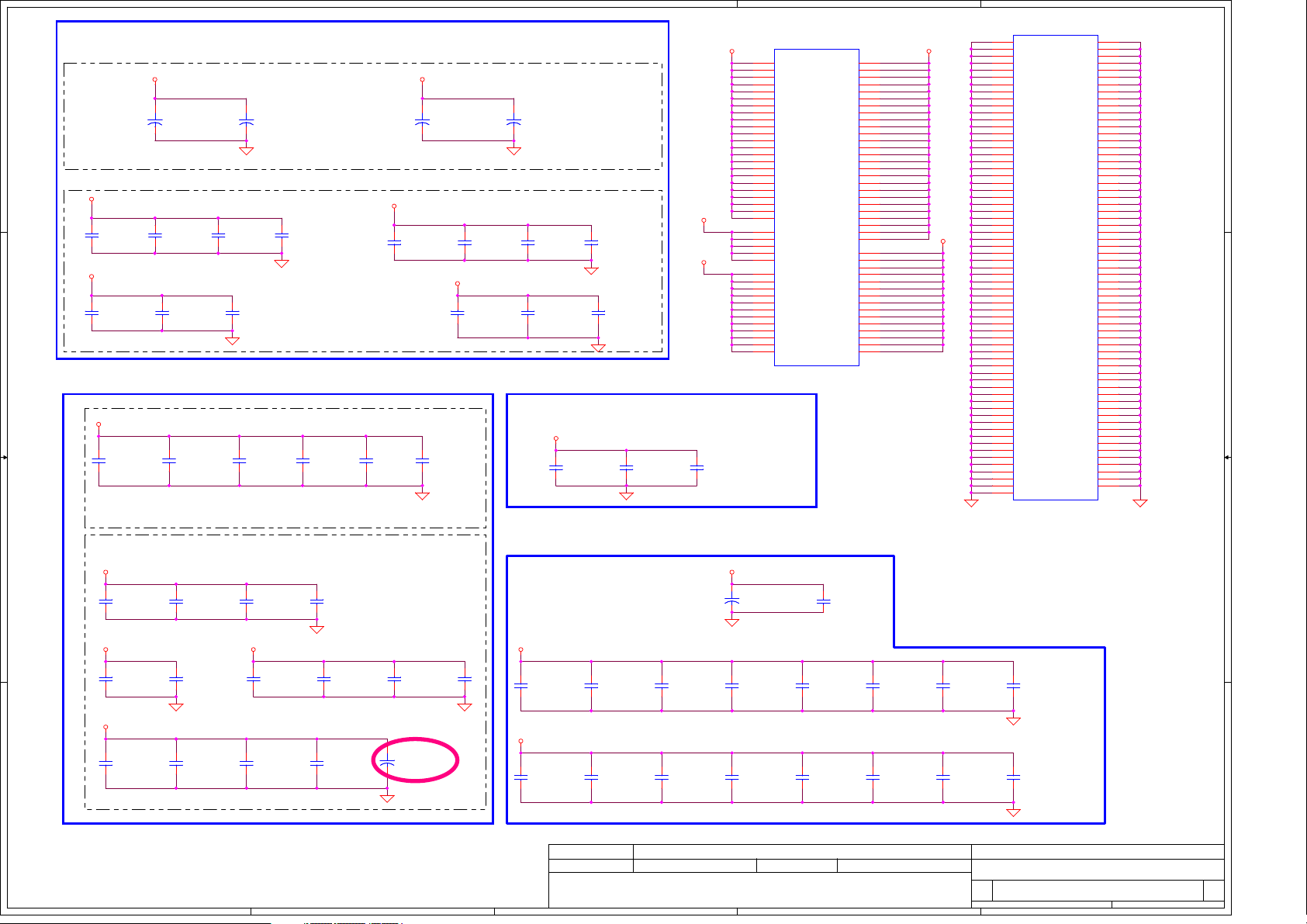

A

+1.8V +1.8V

JDIMM1

JDIMM1

+V_DDR_MCH_REF

DDRA_SDQS0#5

1 1

2 2

3 3

4 4

DDRA_SDQS05

DDRA_SDQS1#5

DDRA_SDQS15

DDRA_SDQS2#5

DDRA_SDQS25

DDRA_CKE05

DDRA_SBS2#5

DDRA_SBS0#5

DDRA_SWE#5

DDRA_SCAS#5

DDRA_SCS1#5

DDRA_ODT15

DDRA_SDQS4#5

DDRA_SDQS45

DDRA_SDQS6#5

DDRA_SDQS65

ICH_SMBDATA09,23,28,36

ICH_SMBCLK09,23,28,36

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQS0#

DDRA_SDQS0

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25 DDRA_SDQ29

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ27

DDRA_SBS2#

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_SMA10

DDRA_SBS0#

DDRA_SWE#

DDRA_SCAS#

DDRA_SCS1#

DDRA_ODT1

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQS4#

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQS6#

DDRA_SDQS6

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ58

DDRA_SDQ59

ICH_SMBDATA0

ICH_SMBCLK0

+3VS

+3VS

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

203

GND

FOX_AS0A426-M2RN-7F

FOX_AS0A426-M2RN-7F

CONN@

CONN@

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0#

VSS

DQ14

DQ15

VSS

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

VDD

VDD

RAS#

VDD

ODT0

NC/A13

VDD

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SAO

GND

CK0

BA1

CK1

SA1

B

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

NC

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

A11

92

A7

94

A6

96

98

A4

100

A2

102

A0

104

106

108

110

S0#

112

114

116

118

120

NC

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

204

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDM0

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDM1

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDM2

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ28

DDRA_SDQS3#

DDRA_SDQS3

DDRA_SDQ30

DDRA_SDQ31

DDRA_CKE1DDRA_CKE0

DDRA_SMA15

DDRA_SMA14

DDRA_SMA11

DDRA_SMA7

DDRA_SMA6

DDRA_SMA4

DDRA_SMA2

DDRA_SMA0

DDRA_SBS1#

DDRA_SRAS#

DDRA_SCS0#

DDRA_ODT0

DDRA_SMA13

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDM4

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQS5#

DDRA_SDQS5

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDM6

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQS7#

DDRA_SDQS7

DDRA_SDQ62

DDRA_SDQ63

R39 10K_0402_5%R39 10K_0402_5%

1 2

R36 10K_0402_5%R36 10K_0402_5%

1 2

DDRA_CLK0 5

DDRA_CLK0# 5

DDRA_SDQS3# 5

DDRA_SDQS3 5

DDRA_CKE1 5

DDRA_SBS1# 5

DDRA_SRAS# 5

DDRA_SCS0# 5

DDRA_ODT0 5

DDRA_SDQS5# 5

DDRA_SDQS5 5

DDRA_CLK1 5

DDRA_CLK1# 5

DDRA_SDQS7# 5

DDRA_SDQS7 5

C

DDRA_SDQ[0..63]

DDRA_SDM[0..7]

DDRA_SMA[0..15]

+V_DDR_MCH_REF

1

C392

C392

2

1000P_0402_25V8J

1000P_0402_25V8J

1

C394

C394

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

DDRA_SDQ[0..63] 5

DDRA_SDM[0..7] 5

DDRA_SMA[0..15] 5

+1.8V

R147

R147

1K_0402_1%

1K_0402_1%

1 2

R148

R148

1K_0402_1%

1K_0402_1%

1 2

+V_DDR_MCH_REF

D

DDRA_SMA6

DDRA_SMA7

DDRA_SMA11

DDRA_SMA15

DDRA_CKE0

DDRA_SBS2#

DDRA_SMA14

DDRA_CKE1

DDRA_SBS1#

DDRA_SMA0

DDRA_SMA2

DDRA_SMA4

DDRA_SMA5

DDRA_SMA8

DDRA_SMA9

DDRA_SMA12

DDRA_SBS0#

DDRA_SMA10

DDRA_SMA1

DDRA_SMA3

DDRA_SCS1#

DDRA_ODT1

DDRA_SWE#

DDRA_SCAS#

DDRA_SMA13

DDRA_ODT0

DDRA_SCS0#

DDRA_SRAS#

RP10

RP10

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

47_0804_8P4R_5%

RP13

RP13

47_0804_8P4R_5%

47_0804_8P4R_5%

RP8

RP8

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

47_0804_8P4R_5%

RP9

RP9

47_0804_8P4R_5%

47_0804_8P4R_5%

RP7

RP7

47_0804_8P4R_5%

47_0804_8P4R_5%

RP4

RP4

47_0804_8P4R_5%

47_0804_8P4R_5%

RP3

RP3

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

47_0804_8P4R_5%

DVT(EMI)

+1.8V

C174 0.1U_0402_16V4ZC174 0.1U_0402_16V4Z

C175 0.1U_0402_16V4ZC175 0.1U_0402_16V4Z

C176 0.1U_0402_16V4ZC176 0.1U_0402_16V4Z

+0.9V

C182 0.1U_0402_16V4ZC182 0.1U_0402_16V4Z

C198 0.1U_0402_16V4ZC198 0.1U_0402_16V4Z

18

C225 0.1U_0402_16V4ZC225 0.1U_0402_16V4Z

27

36

C223 0.1U_0402_16V4ZC223 0.1U_0402_16V4Z

45

C159 0.1U_0402_16V4ZC159 0.1U_0402_16V4Z

C167 0.1U_0402_16V4ZC167 0.1U_0402_16V4Z

18

C179 0.1U_0402_16V4ZC179 0.1U_0402_16V4Z

27

36

C185 0.1U_0402_16V4ZC185 0.1U_0402_16V4Z

45

18

C169 0.1U_0402_16V4ZC169 0.1U_0402_16V4Z

27

36

C161 0.1U_0402_16V4ZC161 0.1U_0402_16V4Z

45

18

C157 0.1U_0402_16V4ZC157 0.1U_0402_16V4Z

27

36

C142 0.1U_0402_16V4ZC142 0.1U_0402_16V4Z

45

C145 0.1U_0402_16V4ZC145 0.1U_0402_16V4Z

C135 0.1U_0402_16V4ZC135 0.1U_0402_16V4Z

1 2

1 2

1 2

E

+1.8V

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1

C67

C67

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2.2U_0805_10V6K

2.2U_0805_10V6K

A

1

C63

C63

2

DIMM1 REV H:5.2mm (BOT)

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

DDRII SO-DIMM 1

DDRII SO-DIMM 1

DDRII SO-DIMM 1

KBLG0 LA-4921P

KBLG0 LA-4921P

KBLG0 LA-4921P

E

8 57Thursday, February 19, 2009

8 57Thursday, February 19, 2009

8 57Thursday, February 19, 2009

0.1

0.1

0.1

A

B

C

D

E

+V_DDR_MCH_REF

1

C390

C390

2

2.2U_0603_6.3V4Z

2.2U_0603_6.3V4Z

1 1

2 2

3 3

4 4

DDRB_SDQS0#5

DDRB_SDQS05

DDRB_SDQS1#5

DDRB_SDQS15

DDRB_SDQS2#5

DDRB_SDQS25

DDRB_CKE05

DDRB_SBS2#5

DDRB_SBS0#5

DDRB_SWE#5

DDRB_SCAS#5

DDRB_SCS1#5

DDRB_ODT15

DDRB_SDQS4#5

DDRB_SDQS45

DDRB_SDQS6#5

DDRB_SDQS65

ICH_SMBDATA08,23,28,36

ICH_SMBCLK08,23,28,36

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQS0#

DDRB_SDQS0

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQS1#

DDRB_SDQS1

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQS2#

DDRB_SDQS2

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDM3