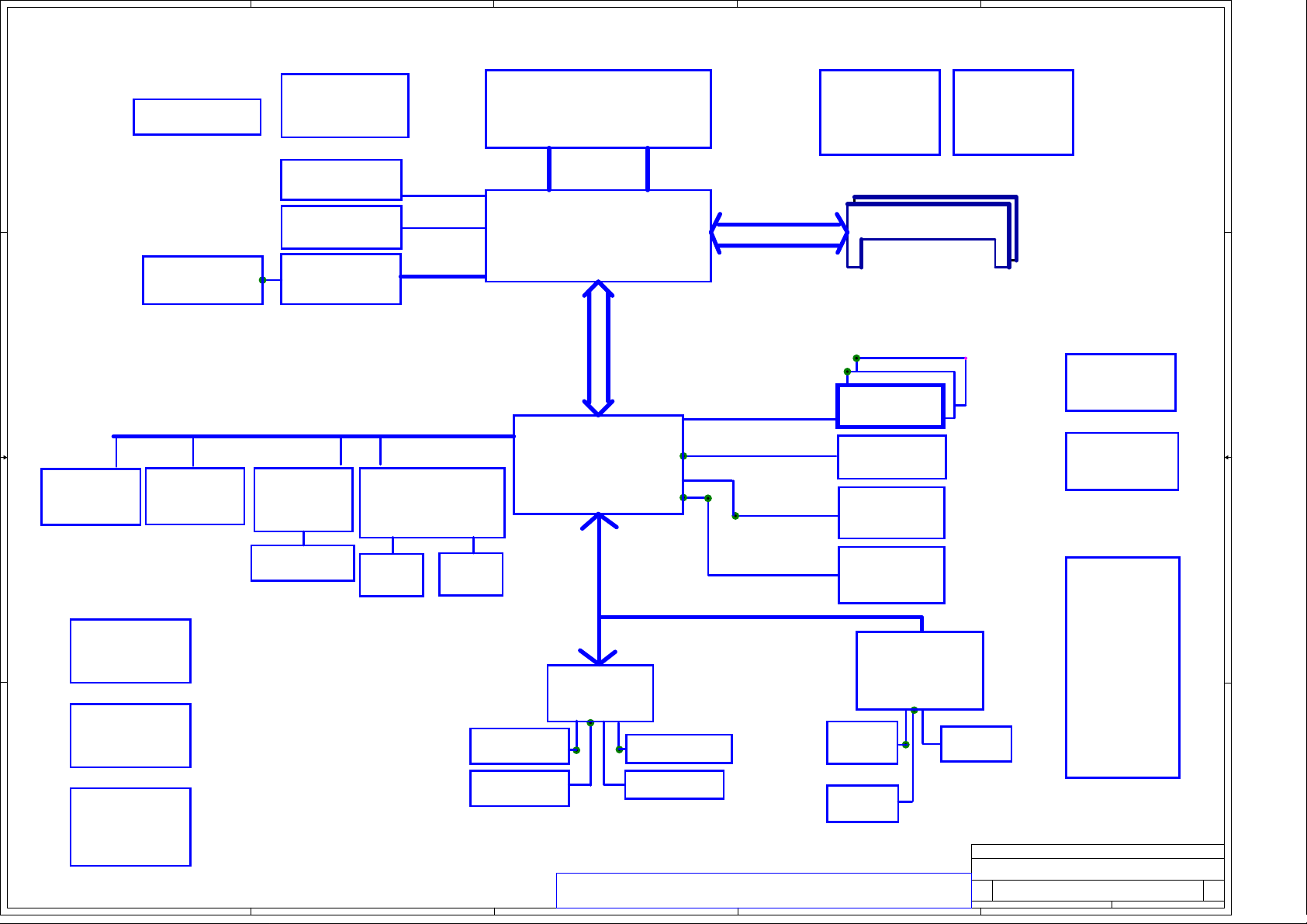

Acer LA-1571P Schematics

A

1 1

B

C

D

E

Compal confidential

2 2

Schematics Document

Mobile P4 uFCBGA/uFCPGA with INTEL

MONTARA-GML/ICH4-M core logic

2002-02-10

3 3

4 4

A

B

REV:1.0

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

Date: Sheet

401238

星期一

Compal Electronics, Inc.

SCHEMATIC M/B LA-1571

21, 2004

六月

E

3B

of

138,

A

Compal confidential

File Name : LA-1571

B

C

D

E

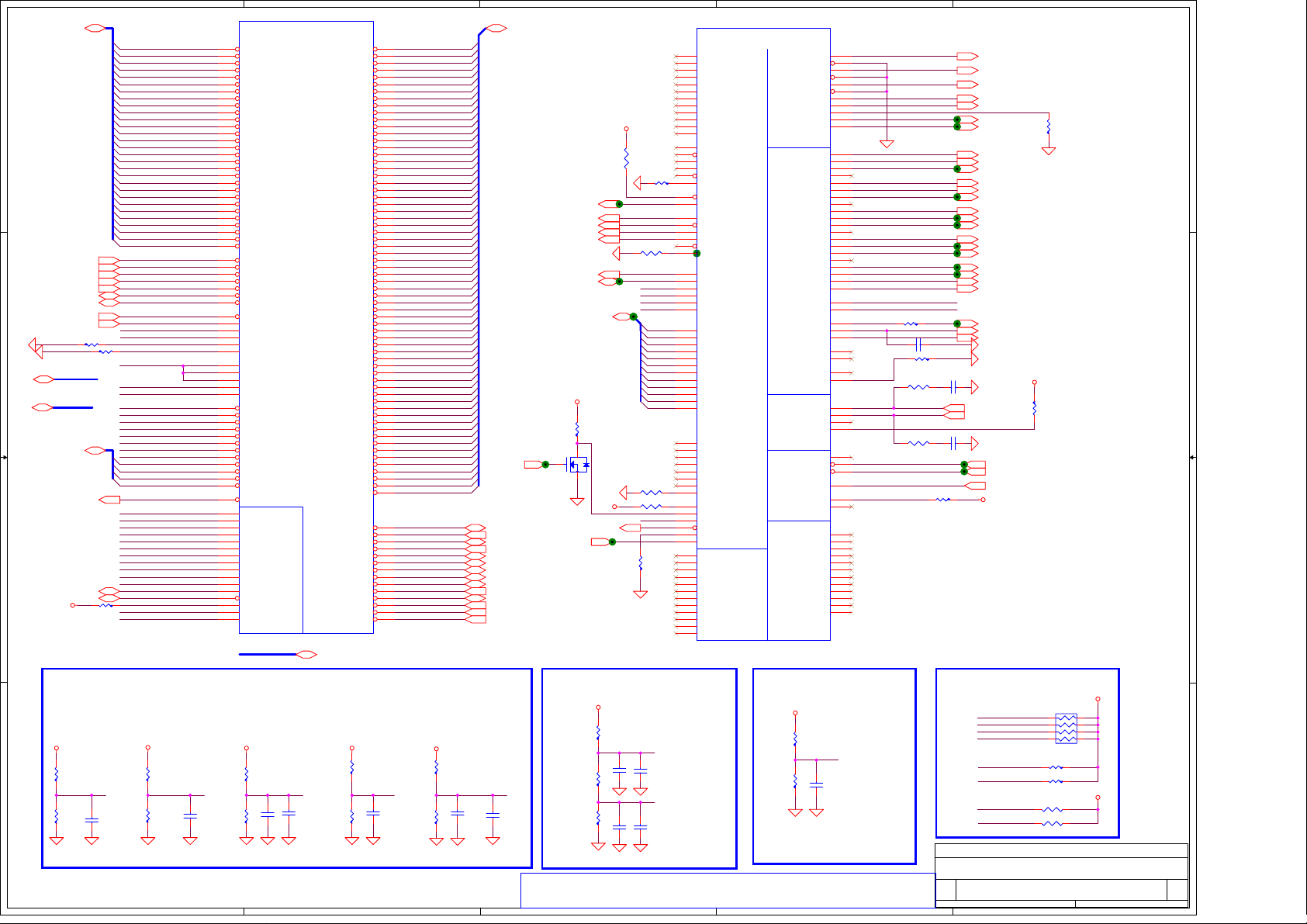

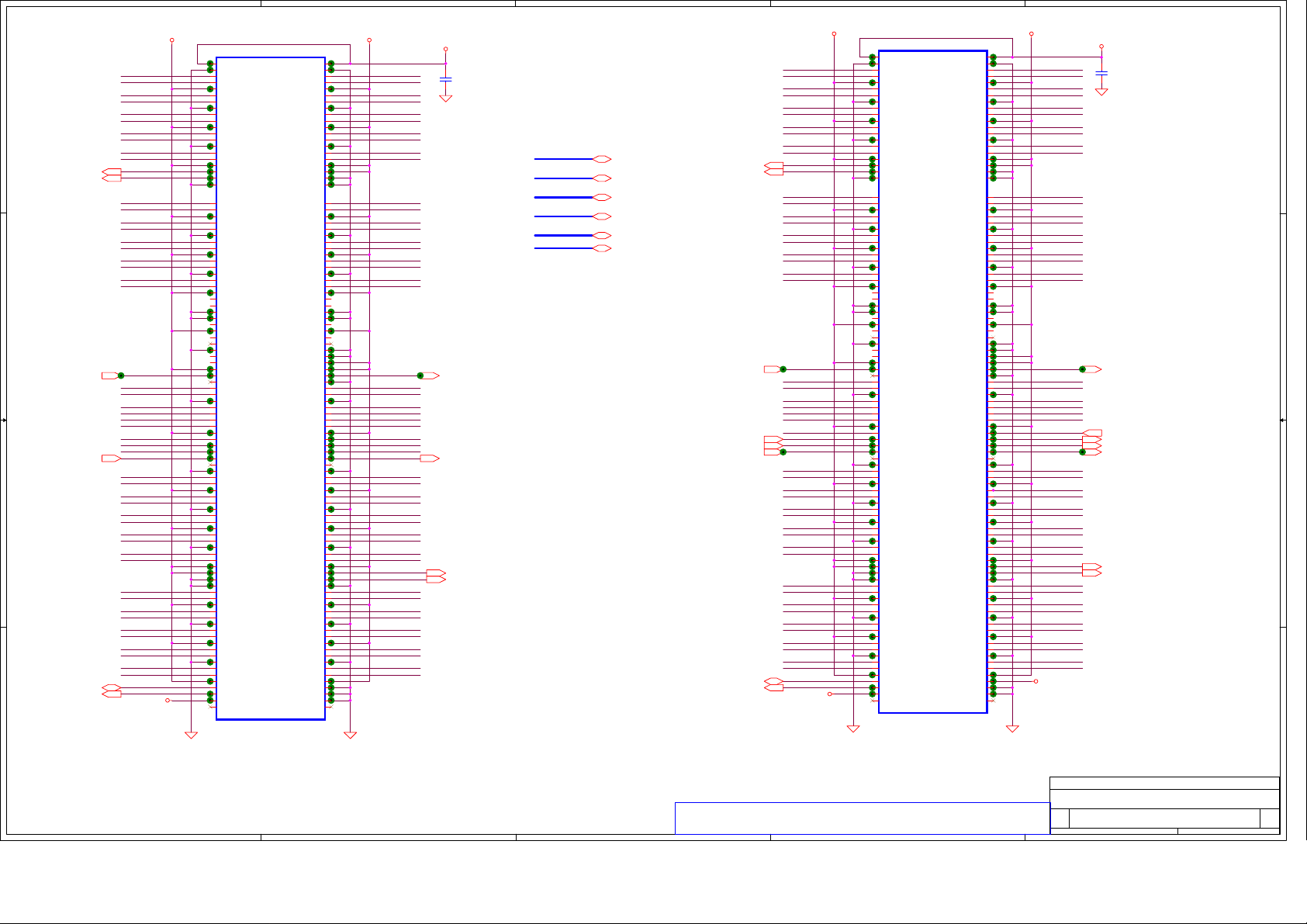

Block Diagram

CPU Bypass

1 1

Fan Control

page 3

TV-OUT Conn

page 14

2 2

& CPUVID

page 5

CRT Conn

page 14

LCD Conn

page 13

TV ENCODER

CH7011

page 11

uFCBGA-479/uFCPGA-478 CPU

HA#(3..31)

MONTARA-GML

DVOC

Mobile P4

page 3,4,5

System Bus

400MHz

VGA Embeded

732 pin u-FCBGA

page6,7,8

HUB LINK 1.5

HD#(0..63)

Thermal Sensor

ADM1032AR

Memory BUS(DDR)

2.5V DDR- 200/266

page 3

DDR-SO-DIMM X2

BANK 0, 1, 2, 3

page 9,10

Clock Generator

CY28346

page 12

5 IN 1

CARDREADER

3.3V 33 MHz

IDSEL:AD19

(PIRQD#,GNT#3,REQ#3)

IEEE 1394

VT6307L

page 20

IDSEL:AD16

(PIRQA#,GNT#0,REQ#0)

3 3

Mini PCI

socket

page 24

IDSEL:AD22/23

(PIRQG/H#,GNT#1/4,REQ#1/4)

LAN

RTL 8100BL

page 19

RJ45/11 CONN

page 19

CardBus Controller

PCI BUS

IDSEL:AD20

(PIRQE/F#,GNT#2,REQ#2)

ENE CB1420

page 21

Slot 1

page 22

Slot 0

page 22

ICH4-M

BGA 421 pin

page 15,16,17

LPC BUS

USB

AC-LINK

Primary IDE

Secondary IDE

USB conn

page 29

AC-LINK CONN

page 23

HDD

Connector

page 18

CDROM

Connector

page 18

Power On/Off

Reset & RTC

page 30

EC

NS87591L

DC/DC Interface

Suspend

page 31

Touch Pad

page 26

EC I/O Bu ffer

4 4

Power Circuit

page 28

DC/DC

page

32,33,34,35,36,37

A

B

page 27

Int.KBD

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

BIOS

page 26

page 28

PARALLEL

SMsC

LPC47N227

LPC to X-BUS

Super I/O

page 25

FIR

page 25

D

page 25

FDD

page 26

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

401238

星期一 六月

page 26

MDC/BT

CONN

page 23

SPR

CONN

page 29

*RJ45/11 CONN

*PS2 x2 CONN

*CRT CONN

*LINE IN JACK

*LINE OUT JACK

*MIC JACK

*DC JACK

*TVOUT CONN

*PRINTER PORT

*COM PORT

*USB CONN x1

SCHEMATIC M/B LA-1571

238, 21, 2004

E

1.0

of

A

FERR#

FERR# 15

A20M# 15

INIT# 15

INTR 15

NMI 15

IGNNE# 15

SMI# 15

CPUSLP# 15

STPCLK# 15

ADS# 6

HASTB0# 6

HASTB1# 6

BNR# 6

DBSY# 6

DEFER# 6

DRDY# 6

HIT# 6

HITM# 6

HTRDY# 6

BPRI# 6

BREQ0# 6

HLOCK# 6

HREQ0# 6

HREQ1# 6

HREQ2# 6

HREQ3# 6

HREQ4# 6

H_RS#0 6

H_RS#1 6

H_RS#2 6

CLK_CPU_BCLK 12

CLK_CPU_BCLK# 12

R18 0_0402

R19 0_0402

CPURST# 6

CPUPWRGD 15

Trace width :

25 mil

R32

1 2

0_0402

R28 0_0402

TCK 4

TDI 4

TDO 4

TMS 4

TRST# 4

CLK_CPU_ITP# 12

CLK_CPU_ITP 12

PULL UP

HTEST0

HTEST1

HTEST2

HTEST3

HTEST4

HTEST5

ITPCLKOUT0

ITPCLKOUT1

HTEST8

HTEST9

HTEST10

GHI#

PROCHOT#

CPUPWRGD

FERR#

IERR#

BREQ0#

CPURST#

THERMTRIP#

ITP_CLK#

ITP_CLK

CPU_COMP0

CPU_COMP1

R4 56_0402

R5 56_0402

R6 56_0402

R7 300_0402

R11 300_0402

R12 56_0402

R13 56_0402

R14 220_0402

R15 51_0402

R34 @56_0402

R24

R25

+CPU_CORE

R2 56_0402

R3 56_0402

R10 56_0402

R20 49.9_1%_0402

R22 49.9_1%_0402

51.1_1%_0603

51.1_1%_0603

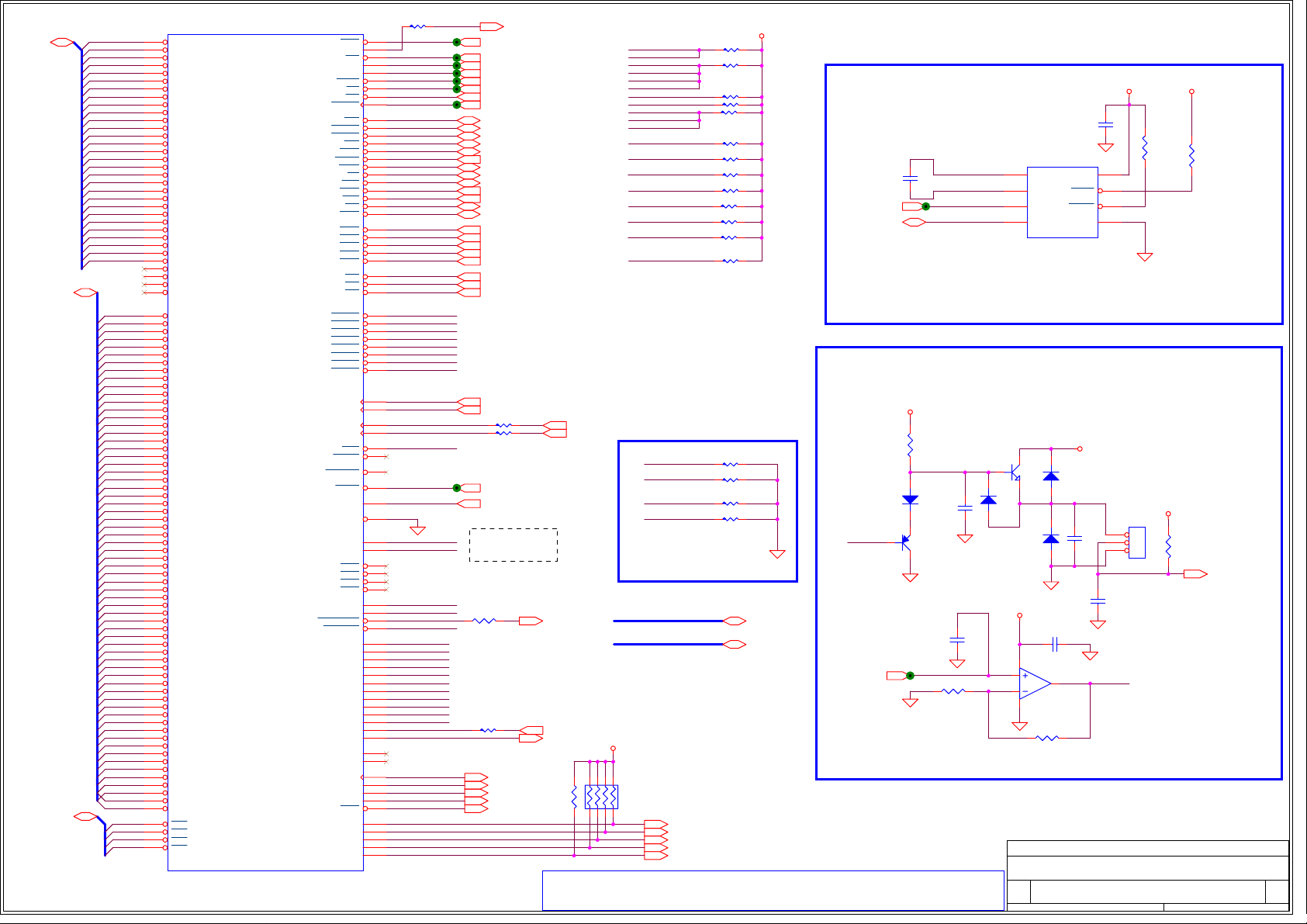

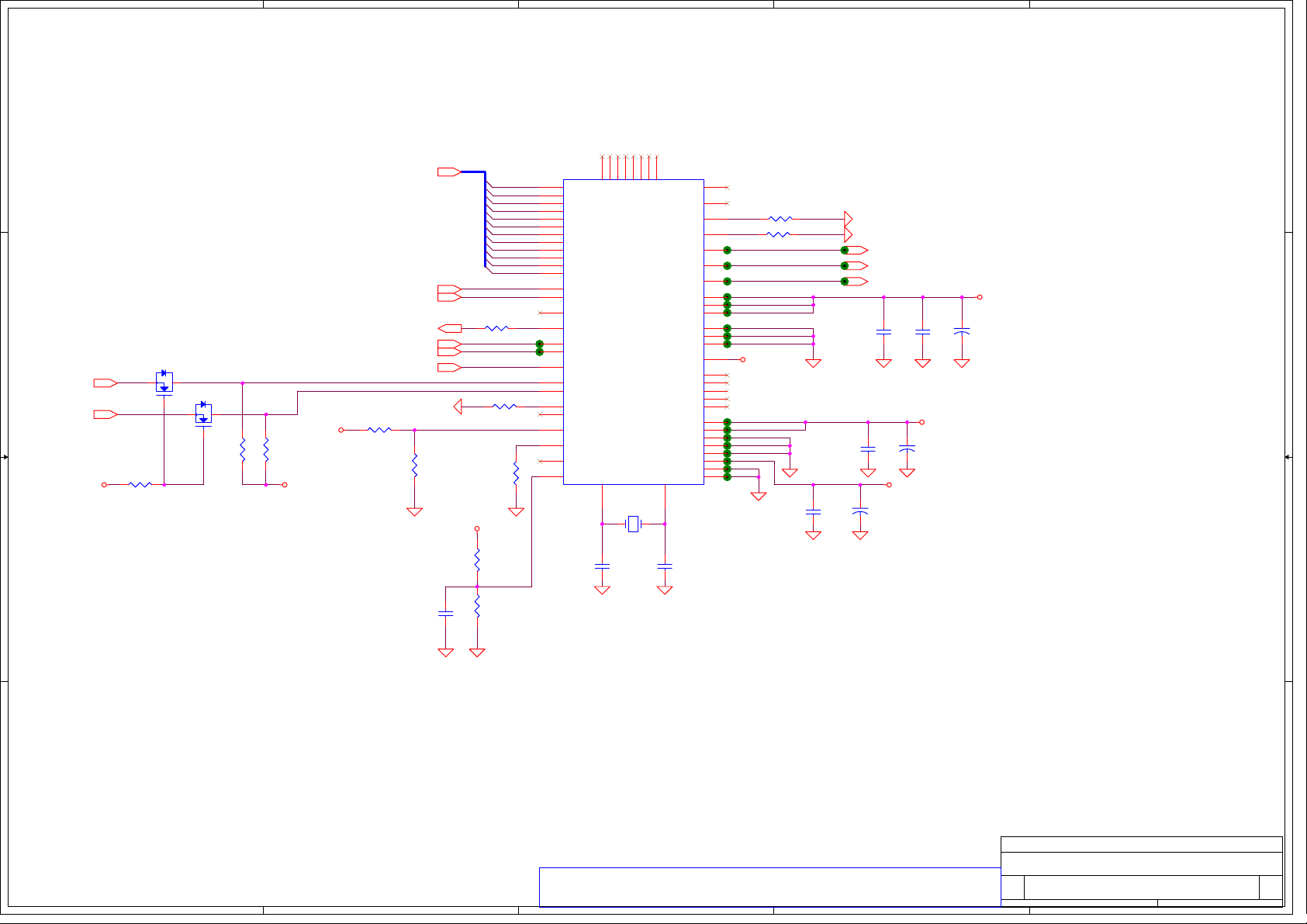

Thermal Sensor

ADM1032AR

12

2200PF_0402

EC_SMC227

EC_SMD227

3.48K_1%_0603

1N4148

FAN1

C2

+12VS

R17

D2

2

H_THERMDA

H_THERMDC

1 2

21

2.2UF_16V_0805

31

Q2

2SA1036K

CB1

FMMT619

1 2

Q1

D3

@1SS355

2 1

2

3

8

7

2

Address:1001_100X

3 1

PULL DOWN

+5VS

VCC

1

3

VEE

2 5

R27

Title

Size Document Number Rev

Date: Sheet of

45

HDSTBP#[0..3]

HDSTBN#[0..3]

+3VS

182736

RP1

8P4R_1K_0804

A

CPU_VID0 37

CPU_VID1 37

CPU_VID2 37

CPU_VID3 37

CPU_VID4 37

SB_THERMTRIP# 16

CPUPERF# 16

DPSLP# 6,15

12

R29

1K_0402

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

HDSTBP#[0..3] 6

HDSTBN#[0..3] 6

12

C6

.1UF_0402

EN_FAN127

1 2

R26

13K_1%_0603

+3VALW+5VALW

W=15mil

C1

.1UF_0402

U2

VDD1

D+

ALERT

D-

THERM

SCLK

SDATA

GND

ADM1032AR_SOP-8

1 2

1 2

1

6

4

5

R9

1K_0402

12

R8

10K_0402

Fan Control circuit

+5VS

D1

1SS355

2 1

+5VFAN1

D4

C3

1000PF_0402

1N4148

2 1

C4

1000PF_0402

.1UF_0402

1 2

C5

4

U3

LMV321_SOT23-5

1 2

7.32K_1%_0603

FAN1

Compal Electronics, Inc.

SCHEMATIC M /B LA- 1571

401238

,

星期一

21, 2004

六月

+3VS

JP1

12

1

R23

2

10K_0402

3

53398-0310

C3,C4 Close

to JP1

FANSPEED1 27

3

3B

38

HA#[3..31] 6

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HD#[0..63]6

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

1 1

DBI#[0..3]6

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

DBI#0

DBI#1

DBI#2

DBI#3

U1A

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

B21

D#0

B22

D#1

A23

D#2

A25

D#3

C21

D#4

D22

D#5

B24

D#6

C23

D#7

C24

D#8

B25

D#9

G22

D#10

H21

D#11

C26

D#12

D23

D#13

J21

D#14

D25

D#15

H22

D#16

E24

D#17

G23

D#18

F23

D#19

F24

D#20

E25

D#21

F26

D#22

D26

D#23

L21

D#24

G26

D#25

H24

D#26

M21

D#27

L22

D#28

J24

D#29

K23

D#30

H25

D#31

M23

D#32

N22

D#33

P21

D#34

M24

D#35

N23

D#36

M26

D#37

N26

D#38

N25

D#39

R21

D#40

P24

D#41

R25

D#42

R24

D#43

T26

D#44

T25

D#45

T22

D#46

T23

D#47

U26

D#48

U24

D#49

U23

D#50

V25

D#51

U21

D#52

V22

D#53

V24

D#54

W26

D#55

Y26

D#56

W25

D#57

Y23

D#58

Y24

D#59

Y21

D#60

AA25

D#61

AA22

D#62

AA24

D#63

E21

DBI0

G25

DBI1

P26

DBI2

V21

DBI3

ZIF_SOCKET478_478P

A20M

FERR

INIT

LINT0

LINT1

IGNNE

SMI

SLP

STPCLK

ADS

ADSTB0

ADSTB1

BNR

DBSY

DEFER

DRDY

HITM

TRDY

BPRI

BR0

LOCK

REQ0

REQ1

REQ2

REQ3

REQ4

RS0

RS1

RS2

DSTBP0

DSTBN0

DSTBP1

DSTBN1

DSTBP2

DSTBN2

DSTBP3

DSTBN3

BCLK0

BCLK1

ITP_CLK1

ITP_CLK0

IERR

MCERR

DBRESET

RESET

PWRGOOD

VSS75

COMP0

COMP1

DEP0

DEP1

DEP2

DEP3

THERMDA

THERMDC

THERMTRIP

PROCHOT

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6/ITPCLKOUT0

TESTHI7/ITPCLKOUT1

TESTHI8

TESTHI9

TESTHI10

TESTHI11/GHI#

TESTHI12/DPSLP#

BSEL0

BSEL1

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

HIT

TDI

C6

B6

W5

D1

E5

B2

B5

AB26

Y4

G1

L5

R5

G2

H5

E2

H2

F3

E3

J6

D2

H6

G4

J1

K5

J4

J3

H3

F1

G5

F4

F21

E22

J23

K22

P23

R22

W23

W22

AF22

AF23

AD26

AC26

AC3

V6

AE25

AB25

AB23

AF26

L24

P1

J26

K25

K26

L25

B3

C4

A2

C3

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

AD6

AD5

D4

C1

D5

F7

E6

AE5

AE4

AE3

AE2

AE1

R1 0_0402

A20M#

INIT#

INTR

NMI

IGNNE#

SMI#

CPUSLP#

STPCLK#

BREQ0#

HDSTBP#0

HDSTBN#0

HDSTBP#1

HDSTBN#1

HDSTBP#2

HDSTBN#2

HDSTBP#3

HDSTBN#3

CPU_CLK

CPU_CLK#

ITP_CLK#

ITP_CLK

IERR#

CPURST#

CPUPWRGD

CPU_COMP0

CPU_COMP1

H_THERMDA

H_THERMDC

THERMTRIP#

PROCHOT#

HTEST0

HTEST1

HTEST2

HTEST3

HTEST4

HTEST5

ITPCLKOUT0

ITPCLKOUT1

HTEST8

HTEST9

HTEST10

GHI#

DPSLP#

TCK

TDI

TDO

TMS

TRST#

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

A

+CPU_CORE

A12

A14

A16

A18

A20

AA10

AA12

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

E13

E15

E17

AA14

AA16

VCC_COREA8VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

GND

E19

E23

E26

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF16

GND

AF18

AF9

VCC_CORE

GND

GND

AF6

AF20

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

B10

B12

AF8

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

B14

B16

B18

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

B20

B23

B26

U1B

4 4

3 3

2 2

1 1

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

E10

E12

E14

E16

E18

E20

F11

F13

F15

F17

F19

D10

K21

K24

L23

L26

M22

M25

N21

N24

P22

P25

R23

R26

D12

D14

D16

D18

D20

D24

D21

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

B7

B9

C8

D7

D9

E8

F9

D8

D6

D3

J2

J22

J25

J5

K3

K6

L1

L4

M2

M5

N3

N6

P2

P5

R1

E1

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC_CORE

VCC_CORE

VCC_CORE

GND

GNDB4GNDB8GND

C11

A10

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

C13

C15

C17

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GNDC2GND

E11

C19

AA18

AA8

AB11

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

GNDE4GNDE7GNDE9GND

F10

B

+CPU_CORE

AB13

AB15

AB17

AB19

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

F18

F12

F14

F16

AB7

AB9

AC10

VCC_CORE

VCC_CORE

VCC_CORE

GND

GNDF2GND

F22

F25

R30

@54.9_1%_0402

AC12

AC14

AC16

VCC_CORE

VCC_CORE

VCC_CORE

GND

GNDF5GND

F8

G21

AC18

AC8

AD11

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GNDG3GNDG6GND

G24

VCORE_SENSE

AD13

AD15

AD17

AD19

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

GNDC9GNDY5GND

Y25

C22

AD9

AE10

AE12

VCC_CORE

VCC_CORE

VCC_CORE

GND

GNDY2GNDW6GNDW3GND

Y22

AD7

A5

VCC_CORE

VCC_SENSE

GND

W24

W21

AB2

RSP

GNDV4GND

V26

AC1

AP0

GND

V23

V5

AC6

AP1

BPM0

GNDV1GNDU5GND

AB5

BPM1

U25

AC4

U22

AA5

AB4

BPM2

BPM3Y6BPM4

GND

GNDU2GNDT6GNDT3GND

C

AF3

AF4

AA3

BINIT

BPM5

VCCVID

GTLREF

VCCVIDPRG

GTLREF

GTLREF

GTLREF

VCCIOPLL

VSS_SENSE

GND

GND

ZIF_SOCKET478_478P

R4

T24

T21

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

VCCA

VSSA

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AA21

AA6

F20

F6

AD20

AD22

AE23

A4

C7

C5

H1

H4

H23

H26

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

C25

+1.2VPP

CB2

1UF_10V_0603

GTLREF

C7

220PF_0402

1UF_10V_0603

VCORE_PLL

VSS_PLL

VIO_PLL

VSS_SENSE

R35

@54.9_1%_0402

CB3

+CPU_CORE

R31

49.9_1%_0603

2/3VCORE

R33

100_1%_0603

12

CB4

+

33UF_D2_16V

CB6

+

33UF_D2_16V

1 2

L1 4.7UH_80mA

1 2

1 2

L2 4.7UH_80mA

D

+1.2VPP

+1.2VPP

CB5

10UF_10V_1206

CB7

10UF_10V_1206

P4-M + Montara

ITP PULL UP/DOWN

TMS3

TDO3

TDI3

TRST#3

TCK3

TMS

TDO

TDI

BPM#4

BPM#5

BPM#1

BPM#0

BPM#3

BPM#2

TRST#

TCK

R38

R39

R40

RP2

R41

R42

R43

R44

27.4_1%_0603

39.2_1%_0603

75_0603

150_0603

18

27

36

45

8P4R-51_0804

51.1_1%_0603

51.1_1%_0603

680_0603

E

+CPU_CORE

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

D

SCHEMATIC M /B LA- 1571

Size Document Number Rev

401238

Date: Sheet of

Compal Electronics, Inc.

,

星期一

21, 2004

六月

438

E

3B

A

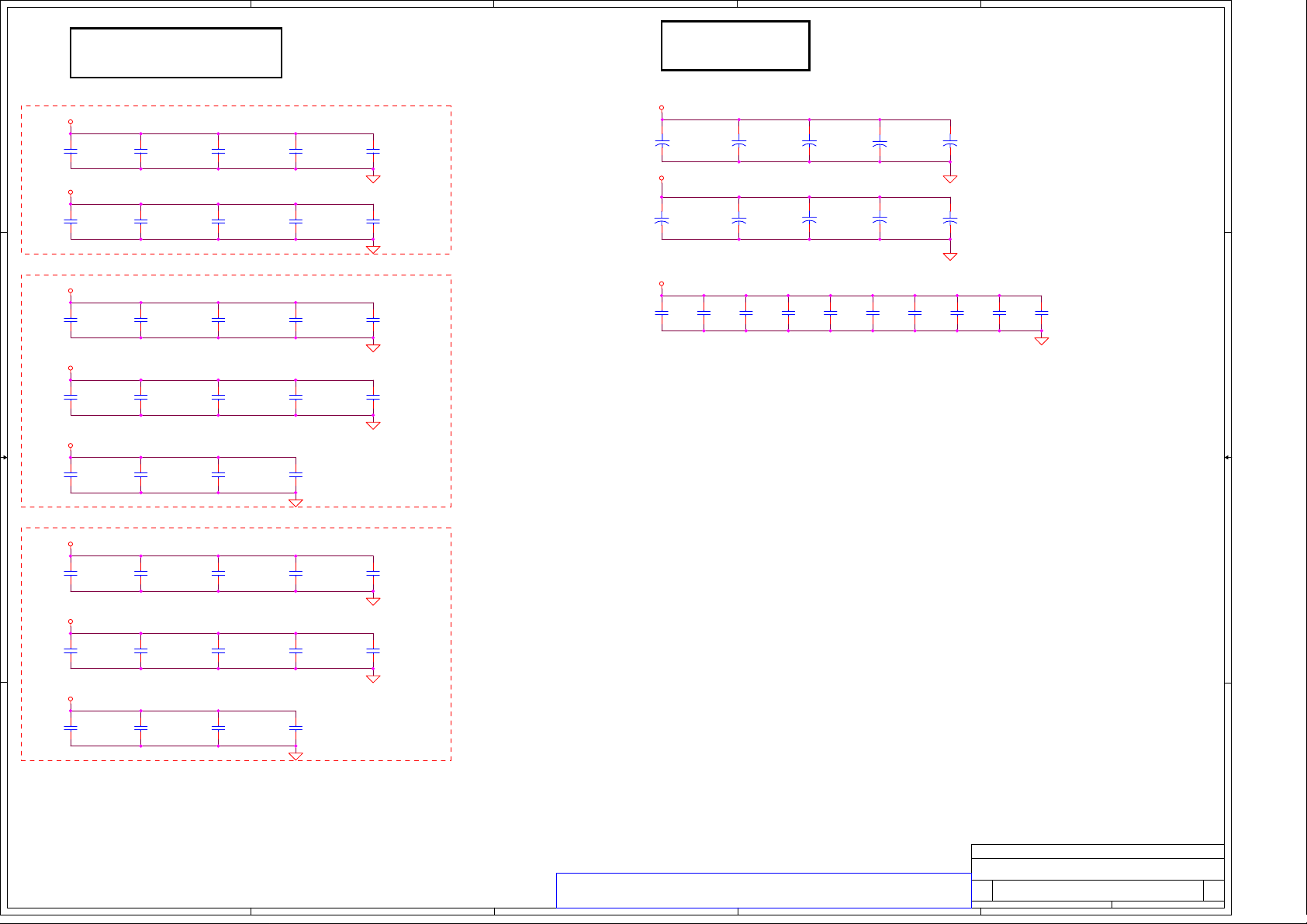

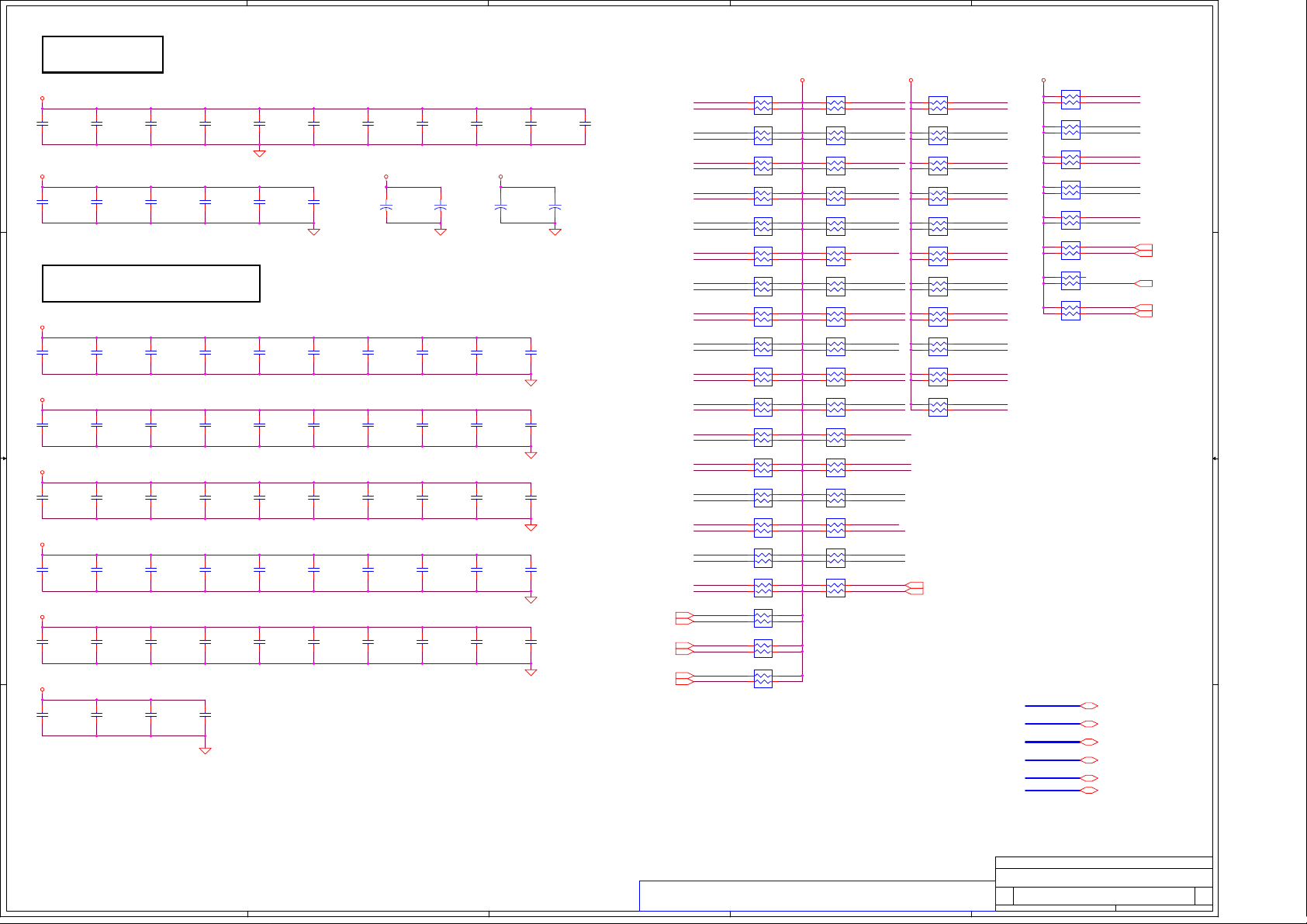

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

B

C

D

E

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

Please place these cap in the socket cavity area

+CPU_CORE

1 1

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

CB8

CB13

12

CB9

10UF_6.3V_1206

12

CB14

10UF_6.3V_1206

12

CB10

10UF_6.3V_1206

12

CB15

10UF_6.3V_1206

12

CB11

10UF_6.3V_1206

12

CB16

10UF_6.3V_1206

12

CB12

10UF_6.3V_1206

12

CB17

10UF_6.3V_1206

Please place these cap on the socket north side

+CPU_CORE

12

CB18

10UF_6.3V_1206

2 2

+CPU_CORE

12

CB23

10UF_6.3V_1206

+CPU_CORE

12

CB28

10UF_6.3V_1206

12

CB19

10UF_6.3V_1206

12

CB24

10UF_6.3V_1206

12

CB29

10UF_6.3V_1206

12

CB20

10UF_6.3V_1206

12

CB25

10UF_6.3V_1206

12

CB30

10UF_6.3V_1206

12

CB21

10UF_6.3V_1206

12

CB26

10UF_6.3V_1206

12

CB31

10UF_6.3V_1206

12

CB22

10UF_6.3V_1206

12

CB27

10UF_6.3V_1206

+CPU_CORE

12

+

+CPU_CORE

12

+

+CPU_CORE

12

CE1

220UF_D2_4V_25m

CE8

220UF_D2_4V_25m

C9

0.22UF_0603

Used ESR 25m ohm cap total ESR=2.5m ohm

12

C10

0.22UF_0603

12

CE2

+

220UF_D2_4V_25m

12

CE9

+

220UF_D2_4V_25m

12

C11

0.22UF_0603

+

+

12

C12

0.22UF_0603

12

12

CE3

220UF_D2_4V_25m

CE6

@220UF_D2_4V_25m

12

C13

0.22UF_0603

12

CE5

+

220UF_D2_4V_25m

12

CE7

+

220UF_D2_4V_25m

12

C14

0.22UF_0603

12

C15

0.22UF_0603

12

CE4

+

220UF_D2_4V_25m

12

CE10

+

220UF_D2_4V_25m

12

C16

0.22UF_0603

12

C17

0.22UF_0603

12

C18

0.22UF_0603

Please place these cap on the socket south side

+CPU_CORE

3 3

4 4

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

CB32

CB37

CB42

12

12

12

A

CB33

10UF_6.3V_1206

CB38

10UF_6.3V_1206

CB43

10UF_6.3V_1206

12

CB34

10UF_6.3V_1206

12

CB39

10UF_6.3V_1206

12

CB44

10UF_6.3V_1206

12

CB35

10UF_6.3V_1206

12

CB40

10UF_6.3V_1206

12

CB45

10UF_6.3V_1206

12

CB36

10UF_6.3V_1206

12

CB41

10UF_6.3V_1206

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

SCHEMATIC M /B LA- 1571

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

401238

星期一 六月

of

538, 21, 2004

E

3B

5

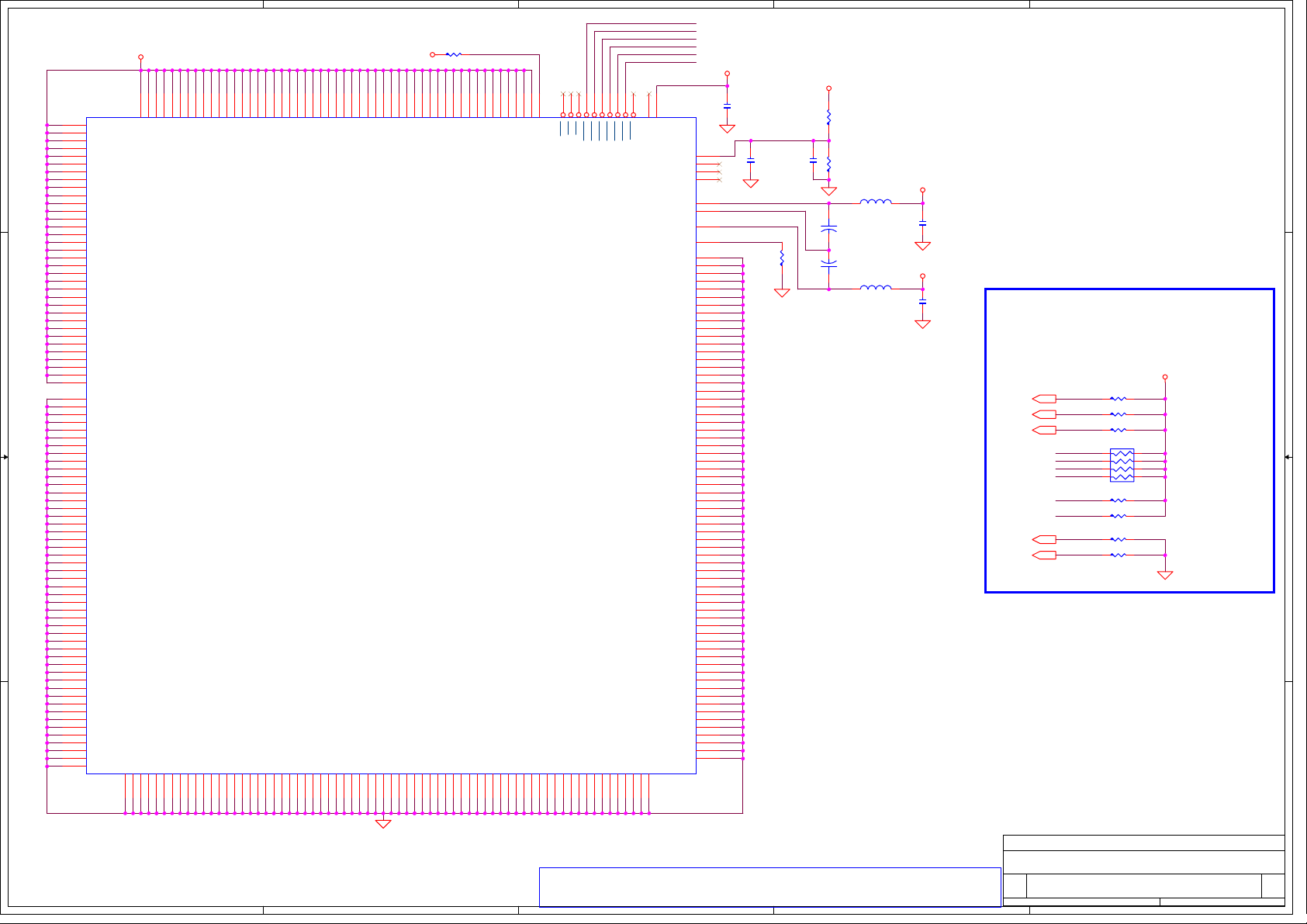

HA#[3..31]3

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

D D

HREQ0#3

HREQ1#3

HREQ2#3

HREQ3#3

HREQ4#3

HASTB0#3

HASTB1#3

CLK_MCH_BCLK#12

CLK_MCH_BCLK12

27.4_1%_0402

C C

B B

R55

R56

27.4_1%_0402

HDSTBP#[0..3]

HDSTBP#[0..3] 3

HDSTBN#[0..3]

HDSTBN#[0..3]

DBI#[0..3]3

CPURST#3

HI_PSTRB15

HI_PSTRB#15

+1.2VS

27.4_1%_0402

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HYSWING

HXSWING

HYRCOMP

HXRCOMP

HDVREF

HCCVREF

HAVREF

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DBI#0

DBI#1

DBI#2

DBI#3

CPURST#

HI_D0

HI_D1

HI_D2

HI_D3

HI_D4

HI_D5

HI_D6

HI_D7

HI_D8

HI_D9

HI_D10

HI_PSTRB

HI_PSTRB#

NB_HI_VSWING

R67

NB_HI_VREF

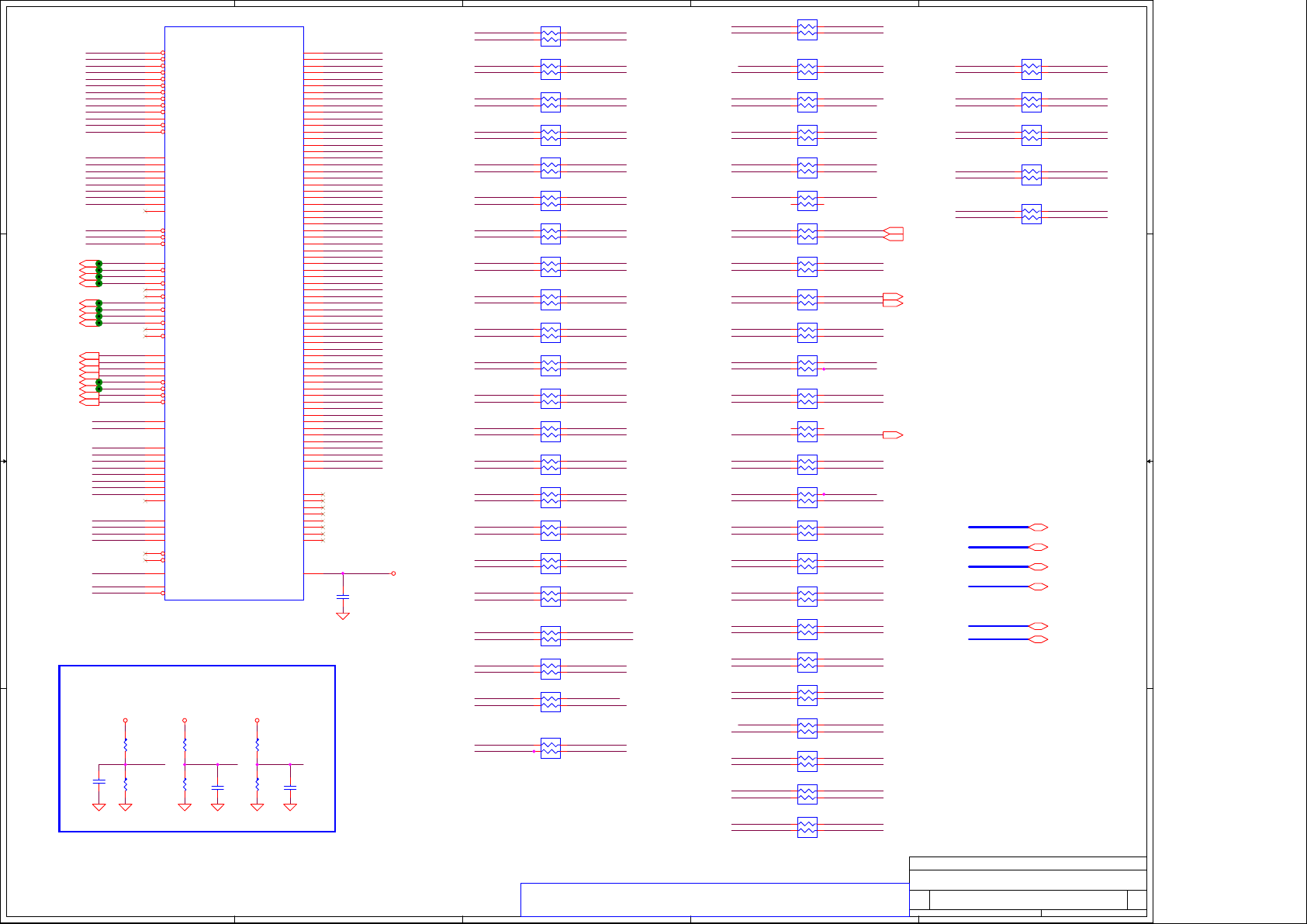

U4A

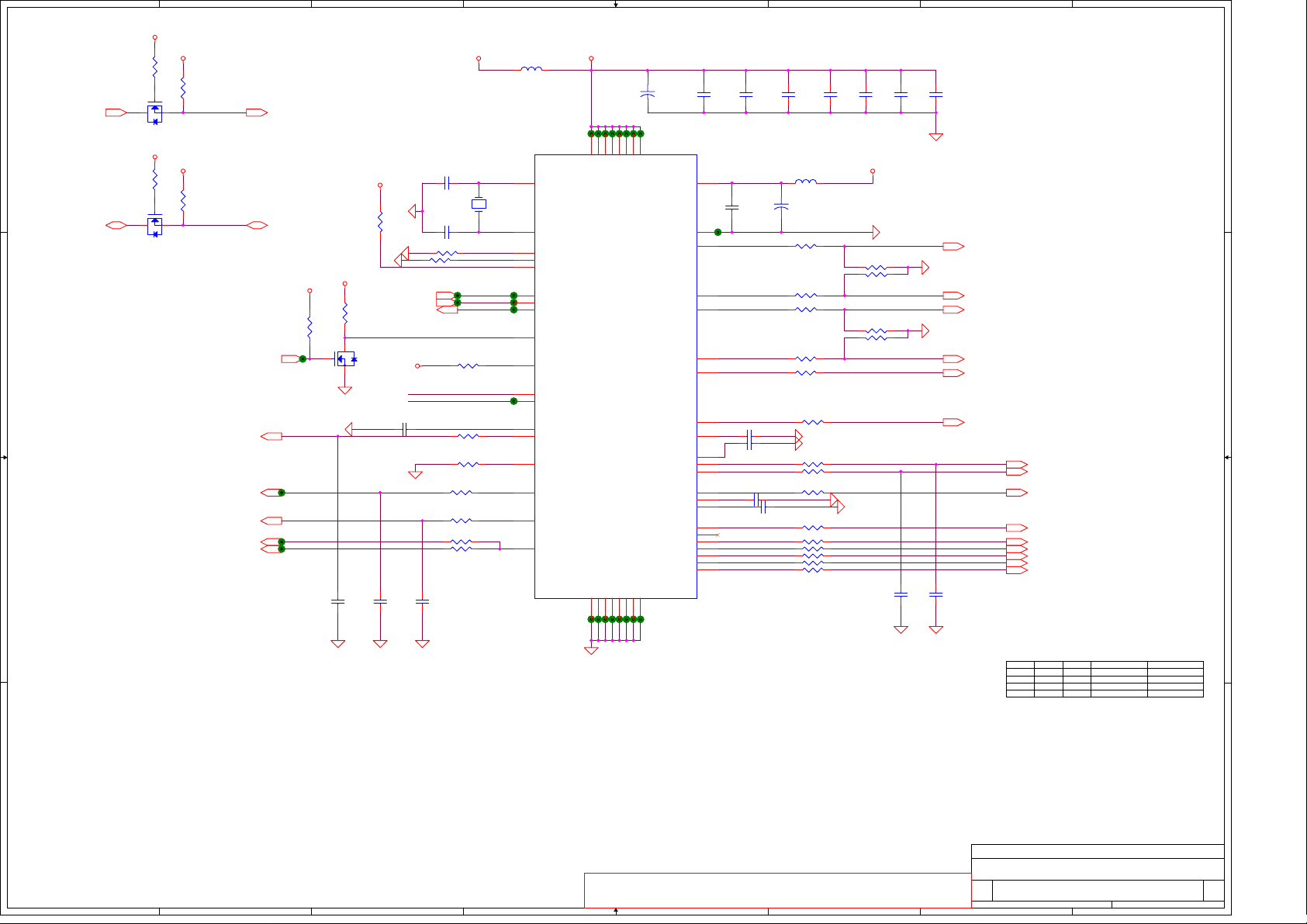

Montara-GM(L)

P23

HA#3

T25

HA#4

T28

HA#5

R27

HA#6

U23

HA7#

U24

HA#8

R24

HA#9

U28

HA#10

V28

HA#11

U27

HA#12

T27

HA#13

V27

HA#14

U25

HA#15

V26

HA#16

Y24

HA#17

V25

HA#18

V23

HA#19

W25

HA#20

Y25

HA#21

AA27

HA#22

W24

HA#23

W23

HA#24

W27

HA#25

Y27

HA#26

AA28

HA#27

W28

HA#28

AB27

HA#29

Y26

HA#30

AB28

HA#31

R28

HREQ#0

P25

HREQ#1

R23

HREQ#2

R25

HREQ#3

T23

AA26

AD29

AE29

K28

B18

H28

B20

K21

Y28

Y22

C27

E22

D18

K27

D26

E21

E18

E25

B25

G19

T26

J21

J17

J28

J25

F15

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

HREQ#4

HADSTB#0

HADSTB#1

BCLK#

BCLK

HYSWING

HXSWING

HYRCOMP

HXRCOMP

HVREF0

HVREF1

HVREF2

HCCVREF

HAVREF

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DINV0#

DINV1#

DINV2#

DINV3#

CPURST#

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HLSTB

HLSTB#

HLRCOMP

PSWING

HLVREF

MONTARA-GM(L)

HI_D[0..10]

HOST

HUB I/F

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HTRDY#

DRDY#

DEFER#

HITM#

HLOCK#

BREQ0#

DBSY#

HI_D[0..10] 15

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

ADS#

HIT#

BNR#

BPRI#

RS#0

RS#1

RS#2

4

HD#[0..63] 3

HD#0

K22

HD#1

H27

HD#2

K25

HD#3

L24

HD#4

J27

HD#5

G28

HD#6

L27

HD#7

L23

HD#8

L25

HD#9

J24

HD#10

H25

HD#11

K23

HD#12

G27

HD#13

K26

HD#14

J23

HD#15

H26

HD#16

F25

HD#17

F26

HD#18

B27

HD#19

H23

HD#20

E27

HD#21

G25

HD#22

F28

HD#23

D27

HD#24

G24

HD#25

C28

HD#26

B26

HD#27

G22

HD#28

C26

HD#29

E26

HD#30

G23

HD#31

B28

HD#32

B21

HD#33

G21

HD#34

C24

HD#35

C23

HD#36

D22

HD#37

C25

HD#38

E24

HD#39

D24

HD#40

G20

HD#41

E23

HD#42

B22

HD#43

B23

HD#44

F23

HD#45

F21

HD#46

C20

HD#47

C21

HD#48

G18

HD#49

E19

HD#50

E20

HD#51

G17

HD#52

D20

HD#53

F19

HD#54

C19

HD#55

C17

HD#56

F17

HD#57

B19

HD#58

G16

HD#59

E16

HD#60

C16

HD#61

E17

HD#62

D16

HD#63

C18

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

RTCCLK16

ADS# 3

HTRDY# 3

DRDY# 3

DEFER# 3

HITM# 3

HIT# 3

HLOCK# 3

BREQ0# 3

BNR# 3

BPRI# 3

DBSY# 3

H_RS#0 3

H_RS#1 3

H_RS#2 3

DVOBC_CLKINT11

DVOC_CLK11

DVOC_CLK#11

DVOC_HSYNC11

DVOC_VSYNC11

MI2CCLK11

MI2CDATA11

10K_1%_0402

CLK_MCH_66M12

3

U4B

Montara-GM(L)

R3

DVOBD0/(NC)

R5

DVOBD1/(NC)

R6

DVOBD2/(NC)

R4

DVOBD3/(NC)

P6

DVOBD4/(NC)

P5

DVOBD5/(NC)

N5

DVOBD6/(NC)

P2

DVOBD7/(NC)

N2

DVOBD8/(NC)

N3

DVOC_D0

DVOC_D1

DVOC_D2

DVOC_D3

DVOC_D4

DVOC_D5

DVOC_D6

DVOC_D7

DVOC_D8

DVOC_D9

DVOC_D10

DVOC_D11

GVREF

DVOBD9/(NC)

M1

DVOBD10/(NC)

M5

DVOBD11/(NC)

P3

DVOBCLK/(NC)

P4

DVOBCLK#/(NC)

T6

DVOBHSYNC/(NC)

T5

DVOBVSYNC/(NC)

L2

DVOBBLANK#/(NC)

M2

DVOBFLDSTL/(NC)

G2

DVOBCINTR#

M3

DVOBCCLKINT

J3

DVOCCLK

J2

DVOCCLK#

K6

DVOCHSYNC

L5

DVOCVSYNC

L3

DVOCBLANK#

H5

DVOCFLDSTL

K7

MI2CCLK

N6

MI2CDATA

N7

MDVICLK

M6

MDVIDATA

P7

MDDCCLK

T7

MDDCDATA

K5

DVOCD0

K1

DVOCD1

K3

DVOCD2

K2

DVOCD3

J6

DVOCD4

J5

DVOCD5

H2

DVOCD6

H1

DVOCD7

H3

DVOCD8

H4

DVOCD9

H6

DVOCD10

G3

DVOCD11

E5

ADDID0

F5

ADDID1

E3

ADDID2

E2

ADDID3

G5

ADDID4

F4

ADDID5

G6

ADDID6

F6

ADDID7

L7

DVODETECT

D5

DPMS

F1

GVREF

F7

AGPBUSY#

D1

DVORCOMP

Y3

GCLKIN

AA5

RVSD0

F2

RVSD1

F3

RVSD2

B2

RVSD3

B3

RVSD4

C2

RVSD5

C3

GST[1]

C4

GST[0]

D2

RVSD8

D3

RVSD9

D7

RVSD10

L4

RVSD11

MONTARA-GM(L)

DAC

DVO

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

CLKS

MISCNC

MCHDETECTVSS

+1.5VS

R406

1K_1%_0402

1 2

R52

100K_0402

DVOBC_CLKINT

DVOC_CLK

DVOC_CLK#

DVOC_HSYNC

DVOC_VSYNC

R410

1 2

100K_0402

MI2CCLK

MI2CDATA

MDVICLK

MDVIDATA

MDDCCLK

R394 1K_0402

1 2

R405

1 2

1K_0402

40.2_1%_0402

MDDCDATA

DVORCOMP

R66

DVOC_D[0..11]11

+1.5VS

R62

Q8

13

D

BSN20

2

G

S

+1.5VS

AGP_BUSY#16

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

HSYNC

VSYNC

REFSET

DDCACLK

DDCADATA

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM3

IYBP0

IYBP1

IYBP2

IYBP3

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

LVDS

LVREFH

LVREFL

LVBG

LIBG

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

DPWR#/(NC)

DPSLP#

RSTIN#

PWROK

EXTTS0

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

2

C9

D9

C8

D8

A7

A8

H10

J9

E8

B6

G9

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

B4

C5

G8

F8

A5

D12

F12

B12

A10

B7

B17

H9

C6

AA22

Y23

AD28

J11

D6

AJ1

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

REFSET

EXTTS

LCD_DC2

LCD_DD2

R54

@0_0402

1 2

C430 22PF_0402

R57 1.5K_1%_0402

R60

1 2

@33_0402

LCLKCTLB

R63

1 2

@33_0402

PCIRST#

@22PF_0402

R64

10K_1%_0402

BLUE 14

GREEN 14

RED 14

HSYNC 14

VSYNC 14

DDCCLK 14

DDCDATA 14

TXA0- 13

TXA1- 13

TXA2- 13

TXA0+ 13

TXA1+ 13

TXA2+ 13

TXB0- 13

TXB1- 13

TXB2- 13

TXB0+ 13

TXB1+ 13

TXB2+ 13

TXACLK- 13

TXACLK+ 13

TXBCLK- 13

TXBCLK+ 13

INVT_PWM 13,27

ENABLT 13,27

ENAVDD 13

C19

1 2

@22PF_0402

CLK_MCH_48M 12

CLK_SSC_66M 12

C20

1 2

DPSLP# 3,15

PCIRST# 11,15,18,19,20,21,24,25,27

VCCcore_POK 12,30,37

+3VS

+3VS

R50

137_1%_0402

R58

510_0402

1

HOST

REF

VOLTAGE

5

+CPU_CORE

R71

301_1%_0402

R80

150_1%_0402

C30

.1UF_0402

1 2

+CPU_CORE +CPU_CORE

R72

49.9_1%_0402

R81

100_1%_0402

HCCVREF

C26

1UF_0402

1 2

C27

1 2

.1UF_0402

49.9_1%_0402

100_1%_0402

R74

HAVREF

C32

R83

.1UF_0402

1 2

4

+CPU_CORE

R75

49.9_1%_0402

R84

100_1%_0402

HDVREFHYSWINGHXSWING

C28

1UF_0402

1 2

C29

.1UF_0402

1 2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+CPU_CORE

R73

301_1%_0402

A A

R82

C31

150_1%_0402

.1UF_0402

1 2

+1.5VS

R68

80.6_1%_0402

R77

51.1_1%_0402

R85

40.2_1%_0402

NB_HI_VSWING

C23

.1UF_0402

1 2

NB_HI_VREF

C33

.1UF_0402

1 2

3

HUB I/F

REF

VOLTAGE

C24

1 2

0.01UF

C34

1 2

0.01UF_0402

+1.5VS

R69

1K_1%_0402

R76

1K_1%_0402

DVO REF

VOLTAGE

GVREF

C25

.1UF_0402

1 2

2

I2C BUS PULL UP

MDVICLK

MDVIDATA

MDDCCLK

MDDCDATA

MI2CCLK

MI2CDATA

LCD_DC2

LCD_DD2

Compal Electronics, Inc.

Title

SCHEMATIC M /B LA-1571

Size Document Number Rev

Custom

401238

Date: Sheet

星期一 六月

8P4R-2.2K_0804

R70

R78 2.2K_0402

R79

R86

RP3

2.2K_0402

2.2K_0402

2.2K_0402

1

+1.5VS

18

27

36

45

+3VS

of

638, 21, 2004

1.0

5

U4C

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

D D

DDR_CLK09

DDR_CLK0#9

DDR_CLK19

DDR_CLK1#9

DDR_CLK39

DDR_CLK3#9

DDR_CLK49

DDR_CLK4#9

C C

DDR_CKE09,10

DDR_CKE19,10

DDR_CKE29,10

DDR_CKE39,10

DDR_SCS#09,10

DDR_SCS#19,10

DDR_SCS#29,10

DDR_SCS#39,10

B B

DDR_SMA11

DDR_SMA12

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SWE#

DDR_SRAS#

DDR_SCAS#

DDR_SBS0

DDR_SBS1

DDR_SDM0

DDR_SDM1

DDR_SDM2

DDR_SDM3

DDR_SDM4

DDR_SDM5

DDR_SDM6

DDR_SDM7

DDR_SMA_B1

DDR_SMA_B2

DDR_SMA_B4

DDR_SMA_B5

MRCOMP

MVSWINGL

MVSWINGH

Montara-GM(L)

AC18

SMA0

AD14

SMA1

AD13

SMA2

AD17

SMA3

AD11

SMA4

AC13

SMA5

AD8

SMA6

AD7

SMA7

AC6

SMA8

AC5

SMA9

AC19

SMA10

AD5

SMA11

AB5

SMA12

AG2

SDQS0

AH5

SDQS1

AH8

SDQS2

AE12

SDQS3

AH17

SDQS4

AE21

SDQS5

AH24

SDQS6

AH27

SDQS7

AD15

SDQS8

AD25

SWE#

AC21

SRAS#

AC24

SCAS#

AB2

SCK0

AA2

SCK0#

AC26

SCK1

AB25

SCK1#

AC3

SCK2

AD4

SCK2#

AC2

SCK3

AD2

SCK3#

AB23

SCK4

AB24

SCK4#

AA3

SCK5

AB4

SCK5#

AC7

SCKE0

AB7

SCKE1

AC9

SCKE2

AC10

SCKE3

AD23

SCS#0

AD26

SCS#1

AC22

SCS#2

AC25

SCS#3

AD22

SBA0

AD20

SBA1

AE5

SDM0

AE6

SDM1

AE9

SDM2

AH12

SDM3

AD19

SDM4

AD21

SDM5

AD24

SDM6

AH28

SDM7

AH15

SDM8

AD16

SMA_B1

AC12

SMA_B2

AF11

SMA_B4

AD10

SMA_B5

AC15

RCVENOUT#

AC16

RCVENIN#

AB1

SMRCOMP

AJ22

SMVSWINGL

AJ19

SMVSWINGH

MONTARA-GM(L)

MEMORY

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

SMVREF0

DDR REF & SWING VOLTAGE

+2.5V +2.5V +2.5V

R88

60.4_1%_0603

MRCOMP

C37

R91

.1UF_0402

1 2

A A

60.4_1%_0603

R89

604_1%_0603

MVSWINGL

R92

150_1%_0603

C38

.1UF_0402

1 2

R90

150_1%_0603

MVSWINGH

R93

C39

604_1%_0603

.1UF_0402

1 2

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ24

4

DDR_SDQ0

DDR_SDQ1

DDR_SDQ2

DDR_SDQ3

DDR_SDQ4

DDR_SDQ5

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ10

DDR_SDQ11

DDR_SDQ12

DDR_SDQ13

DDR_SDQ14

DDR_SDQ15

DDR_SDQ16

DDR_SDQ17

DDR_SDQ18

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ22

DDR_SDQ23

DDR_SDQ24

DDR_SDQ25

DDR_SDQ26

DDR_SDQ27

DDR_SDQ28

DDR_SDQ29

DDR_SDQ30

DDR_SDQ31

DDR_SDQ32

DDR_SDQ33

DDR_SDQ34

DDR_SDQ35

DDR_SDQ36

DDR_SDQ37

DDR_SDQ38

DDR_SDQ39

DDR_SDQ40

DDR_SDQ41

DDR_SDQ42

DDR_SDQ43

DDR_SDQ44

DDR_SDQ45

DDR_SDQ46

DDR_SDQ47

DDR_SDQ48

DDR_SDQ49

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ53

DDR_SDQ54

DDR_SDQ55

DDR_SDQ56

DDR_SDQ57

DDR_SDQ58

DDR_SDQ59

DDR_SDQ60

DDR_SDQ61

DDR_SDQ62

DDR_SDQ63

C36

.1UF_0402

1 2

SDREF

DDR_SDQ5

DDR_SDQ4

DDR_SDQ0

DDR_SDQ2

DDR_SDQ1

DDR_SDQ6

DDR_SDQS0

DDR_SDQ7

DDR_SDQ3

DDR_SDM0

DDR_SDQ8

DDR_SDM1

DDR_SDQ12

DDR_SDQ13

DDR_SDQS1

DDR_SDQ11

DDR_SDQ9

DDR_SDQ15

DDR_SDQ10

DDR_SDQ14

DDR_SDQ21

DDR_SDQ20

DDR_SDM2

DDR_SDQ17

DDR_SDQS2

DDR_SDQ16

DDR_SDQ22

DDR_SDQ18

DDR_SDQ23

DDR_SDQ19

DDR_SDQ24

DDR_SDQ28

DDR_SDQ25

DDR_SDQ29

DDR_SDQ30

DDR_SDQ26

DDR_SDQ31

DDR_SDQ27

DDR_SMA9

DDR_SMA_B4

DDR_SMA4

DDR_SMA_B5

DDR_SMA5

DDR_SMA_B2

RP4 4P2R_10

1 4

2 3

RP7 4P2R_10

1 4

2 3

RP10 4P2R_10

1 4

2 3

RP13 4P2R_10

1 4

2 3

RP16 4P2R_10

1 4

2 3

RP19 4P2R_10

1 4

2 3

RP22 4P2R_10

1 4

2 3

RP24 4P2R_10

1 4

2 3

RP26 4P2R_10

1 4

2 3

RP28 4P2R_10

1 4

2 3

RP30 4P2R_10

1 4

2 3

RP32 4P2R_10

1 4

2 3

RP34 4P2R_10

1 4

2 3

RP36 4P2R_10

1 4

2 3

RP38 4P2R_10

1 4

2 3

RP40 4P2R_10

1 4

2 3

RP42 4P2R_10

1 4

2 3

RP44 4P2R_10

1 4

2 3

RP47 4P2R_10

1 4

2 3

RP49 4P2R_10

1 4

2 3

RP51 4P2R_10

1 4

2 3

RP5 4P2R_10

1 4

2 3

3

DDR_DQ5

DDR_DQ4

DDR_DQ0

DDR_DQ2

DDR_DQ1

DDR_DQ6

DDR_DQS0

DDR_DQ7

DDR_DQ3

DDR_DM0

DDR_DQ8

DDR_DM1

DDR_DQ12

DDR_DQ13

DDR_DQS1

DDR_DQ11

DDR_DQ9

DDR_DQ15

DDR_DQ10

DDR_DQ14

DDR_DQ21

DDR_DQ20

DDR_DM2

DDR_DQ17

DDR_DQS2

DDR_DQ16

DDR_DQ22

DDR_DQ18

DDR_DQ23

DDR_DQ19

DDR_DQ24

DDR_DQ28

DDR_DQ25

DDR_DQ29

DDR_DQ30

DDR_DQ26

DDR_DQ31

DDR_DQ27

DDR_MA9

DDR_MA_B4

DDR_MA4

DDR_MA_B5

DDR_MA5

DDR_MA_B2

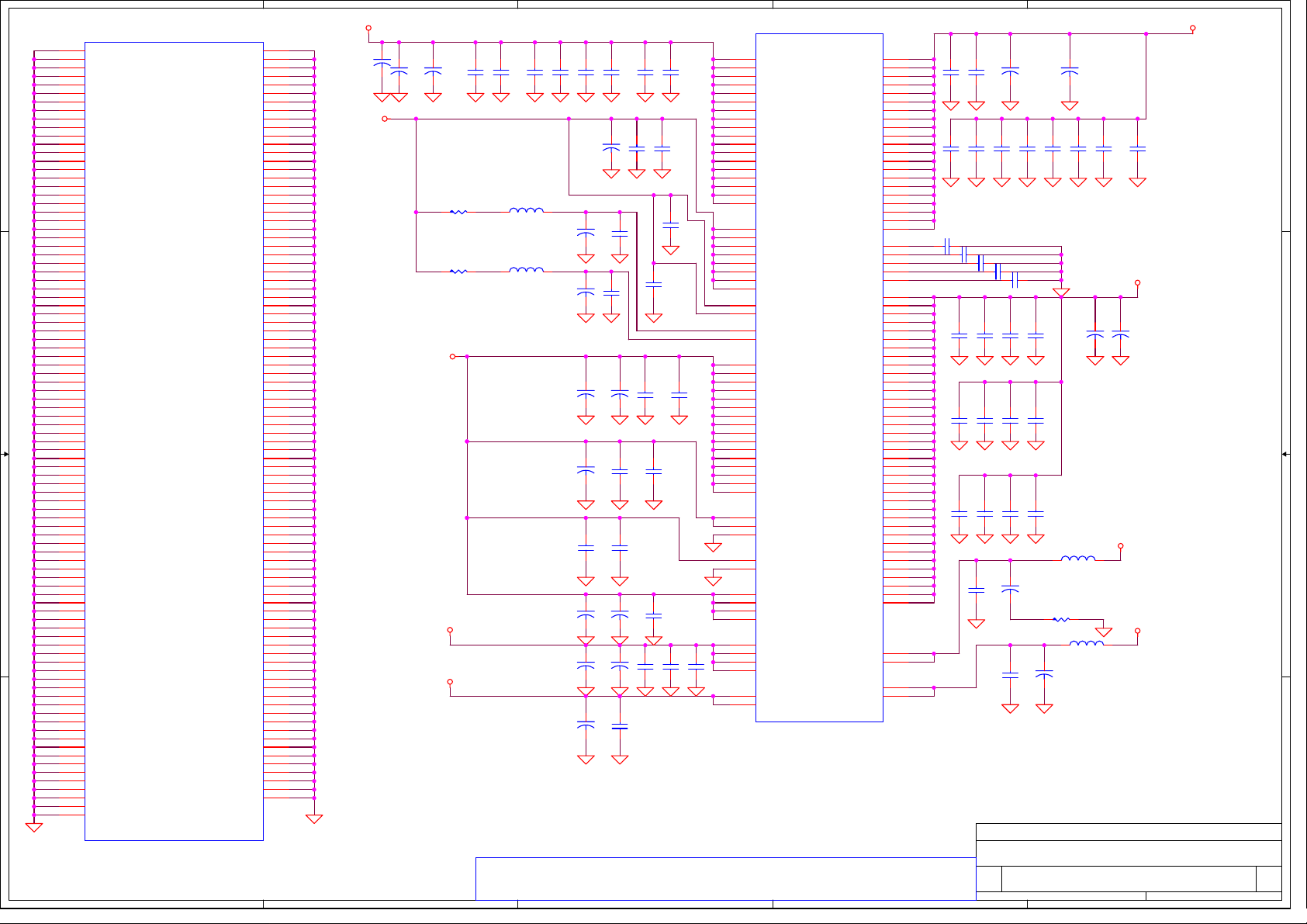

Layout note

Place these resistor

closely DIMM0,

all trace length

Max=0.75"

2

DDR_SMA1

RP6 4P2R_10

1 4

2 3

RP8 4P2R_10

1 4

2 3

RP11

4P2R_10

1 4

2 3

RP14 4P2R_10

1 4

2 3

RP23 4P2R_10

1 4

2 3

RP25 4P2R_10

1 4

2 3

RP17 4P2R_10

1 4

2 3

RP20 4P2R_10

1 4

2 3

RP27 4P2R_10

1 4

2 3

RP29 4P2R_10

1 4

2 3

RP31 4P2R_10

1 4

2 3

RP33 4P2R_10

1 4

2 3

RP35 4P2R_10

1 4

2 3

RP37 4P2R_10

1 4

2 3

RP39 4P2R_10

1 4

2 3

RP41 4P2R_10

1 4

2 3

RP43 4P2R_10

1 4

2 3

RP45 4P2R_10

1 4

2 3

RP46 4P2R_10

1 4

2 3

RP48 4P2R_10

1 4

2 3

RP50 4P2R_10

1 4

2 3

RP52 4P2R_10

1 4

2 3

RP53 4P2R_10

1 4

2 3

RP54 4P2R_10

1 4

2 3

RP55 4P2R_10

1 4

2 3

DDR_MA_B1

DDR_MA2

DDR_MA1

DDR_MA6

DDR_MA7

DDR_MA8

DDR_MA3

DDR_MA0

DDR_MA10

DDR_MA11

DDR_MA12

DDR_BS1

DDR_BS0

DDR_DQ32

DDR_DQ34DDR_SDQ34

DDR_RAS#

DDR_WE#

DDR_DQ33

DDR_DQ38

DDR_DQS4

DDR_DQ37

DDR_DQ36

DDR_DQ39

DDR_CAS#

DDR_DQ35

DDR_DM5

DDR_DQ45

DDR_DQ40

DDR_DQ41

DDR_DQ44

DDR_DQS5

DDR_DQ46

DDR_DQ47

DDR_DQ43

DDR_DQ42

DDR_DQ48

DDR_DQ49

DDR_DQ53

DDR_DQS6

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ54

DDR_DQ55

DDR_DQ60

DDR_DM6

DDR_SMA_B1

DDR_SMA2

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA3

DDR_SMA0

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SBS1

DDR_SBS0

DDR_SDQ32

DDR_SRAS#

DDR_SWE#

DDR_SDQ33

DDR_SDQ38

DDR_SDQS4

DDR_SDQ37

DDR_SDQ36

DDR_SDQ39

DDR_SCAS#

DDR_SDM4 DDR_DM4

DDR_SDQ35

DDR_SDM5

DDR_SDQ45

DDR_SDQ40

DDR_SDQ41

DDR_SDQ44

DDR_SDQS5

DDR_SDQ46

DDR_SDQ47

DDR_SDQ43

DDR_SDQ42

DDR_SDQ48

DDR_SDQ49

DDR_SDQ53

DDR_SDQS6

DDR_SDM6

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ54

DDR_SDQ55

DDR_SDQ60

DDR_SDQ57 DDR_DQ57

DDR_BS1 9,10

DDR_BS0 9,10

DDR_RAS# 9,10

DDR_WE# 9,10

DDR_CAS# 9,10

1

DDR_DM[0..7]

DDR_DQ[0..63]

DDR_DQS[0..8]

DDR_MA[0..12]

DDR_MA_B[1..2]

DDR_MA_B[4..5]

RP9 4P2R_10

1 4

2 3

RP12 4P2R_10

1 4

2 3

RP15 4P2R_10

1 4

2 3

RP18 4P2R_10

1 4

2 3

RP21 4P2R_10

1 4

2 3

DDR_SDQ56

DDR_SDQS7

DDR_SDQ61

DDR_SDQ63

DDR_SDM7

DDR_SDQ59 DDR_DQ59

DDR_SDQ62

DDR_SDQ58

DDR_SDQS3

DDR_DQ56

DDR_DQS7

DDR_DQ61

DDR_DQ63

DDR_DM7

DDR_DQ62

DDR_DQ58

DDR_DQS3

DDR_DM3DDR_SDM3

DDR_DM[0..7] 9,10

DDR_DQ[0..63] 9,10

DDR_DQS[0..8] 9,10

DDR_MA[0..12] 9,10

DDR_MA_B[1..2] 9,10

DDR_MA_B[4..5] 9,10

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

5

4

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

SCHEMATIC M/B LA-1571

Size Document Number Rev

Custom

401238

星

, 21, 2004

期一 六月

Date: Sheet

1

of

738

3B

5

U4D

C1

VSS0

G1

VSS1

L1

VSS2

U1

VSS3

AA1

VSS4

AE1

VSS5

R2

VSS6

AG3

VSS7

AJ3

AA4

AC4

AE4

AG6

AA7

AE7

AJ7

AC8

AB9

AG9

C10

J10

AA10

AE10

D11

F11

H11

AB11

AC11

AJ11

J12

AA12

AG12

A13

D13

F13

H13

N13

R13

U13

AB13

AE13

J14

P14

T14

AA14

AC14

D15

H15

N15

R15

U15

AB15

AG15

F16

J16

P16

T16

AA16

AE16

A17

D17

H17

N17

D4

G4

K4

N4

T4

W4

B5

U5

Y5

Y6

C7

E7

G7

J7

M7

R7

H8

K8

P8

T8

V8

Y8

E9

L9

N9

R9

U9

W9

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

MONTARA-GM(L)

Montara-GM(L)

5

D D

C C

B B

A A

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

W29

AA29

AJ10

AJ12

AJ18

AJ20

C22

D28

E28

L6

T9

AJ26

150UF_10V_E

150UF_10V_E

+1.2VS

CE11

+1.2VS

4

CE12

10UF_10V_1206

+1.5VS

4

CB46

+2.5VS

+3VS

3

Montara-GM(L)

J15

C44

C40

C41

.1UF_0402

.1UF_0402

1 2

1 2

R399

1_0603

R400

1_0603

0_0805

0_0805

@220UF_D2_4V_25m

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C43

C42

.1UF_0402

.1UF_0402

1 2

1 2

10UF_10V_1206

FB1

CE14

220UF_D2_4V_25m

FB2

CE15

220UF_D2_4V_25m

CE18

150UF_10V_E

CE19

CE20

47UF_D2

CE22

47UF_D2

CB51

10UF_10V_1206

C45

.1UF_0402

.1UF_0402

1 2

1 2

CB48

C61

.1UF_0402

1 2

C68

.1UF_0402

1 2

CB49

10UF_10V_1206

C79

.1UF_0402

1 2

C85

C86

.1UF_0402

0.01UF_0402

1 2

1 2

CE21

10UF_16V_1206

CE23

10UF_16V_1206

C93

.1UF_0402

1 2

C46

.1UF_0402

1 2

C50

C51

.1UF_0402

.1UF_0402

1 2

1 2

C67

.1UF_0402

1 2

C73

.1UF_0402

1 2

C80

0.01UF_0402

1 2

C88

.1UF_0402

1 2

C89

.1UF_0402

1 2

3

C47

.1UF_0402

1 2

C60

.1UF_0402

1 2

C74

.1UF_0402

1 2

C90

C91

.1UF_0402

.1UF_0402

1 2

1 2

P13

T13

N14

R14

U14

P15

T15

AA15

N16

R16

U16

P17

T17

AA17

AA19

W21

H14

V1

Y1

W5

U6

U8

W8

V7

V9

D29

Y2

A6

B16

E1

J1

N1

E4

J4

M4

E6

H7

J8

L8

M8

N8

R8

K9

M9

P9

A9

B9

B8

A11

B11

G13

B14

J13

B15

F9

B10

D10

A12

A3

A4

MONTARA-GM(L)

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCCHL0

VCCHL1

VCCHL2

VCCHL3

VCCHL4

VCCHL5

VCCHL6

VCCHL7

VCCAHPLL

VCCAGPLL

VCCADPLLA

VCCADPLLB

VCCDVO_0

VCCDVO_1

VCCDVO_2

VCCDVO_3

VCCDVO_4

VCCDVO_5

VCCDVO_6

VCCDVO_7

VCCDVO_8

VCCDVO_9

VCCDVO_10

VCCDVO_11

VCCDVO_12

VCCDVO_13

VCCDVO_14

VCCDVO_15

VCCADAC0

VCCADAC1

VSSADAC

VCCALVDS

VSSALVDS

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCDLVDS3

VCCTXLVDS0

VCCTXLVDS1

VCCTXLVDS2

VCCTXLVDS3

VCCGPIO_0

VCCGPIO_1

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

POWER

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCASM1

2

U4E

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

C62 .1U F_0402

A22

A24

H29

M29

V29

AC1

AG1

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

AJ6

AJ8

AD1

AF1

2

C48

C49

.1UF_0402

.1UF_0402

1 2

1 2

10UF_10V_1206

C55

C56

C52

.1UF_0402

1 2

.1UF_0402

C63 .1UF_0402

C64 .1UF_0402

.1UF_0402

1 2

1 2

12

12

12

C65 .1U F_0402

C69

.1UF_0402

1 2

C75

.1UF_0402

1 2

C81

.1UF_0402

1 2

12

C66 .1UF_0402

C71

C70

.1UF_0402

.1UF_0402

1 2

1 2

C77

C76

.1UF_0402

.1UF_0402

1 2

1 2

C82

C83

.1UF_0402

.1UF_0402

1 2

1 2

C87

.1UF_0402

1 2

C92

.1UF_0402

1 2

Compal Electronics, Inc.

Title

SCHEMATIC M/B LA-1571

Size Document Number Rev

Custom

Date: Sheet

CB47

C58

C57

.1UF_0402

.1UF_0402

1 2

1 2

12

C72

.1UF_0402

1 2

C78

.1UF_0402

1 2

C84

.1UF_0402

1 2

星期

R99

一六月

0_0805

CE24

47UF_D2

, 21, 2004

CB50

4.7UF_10V_0805

1

+CPU_CORE

CE13

150UF_10V_E

C59

C53

.1UF_0402

1 2

CE16

150UF_10V_E

FB4

1_0603

FB5

0_0805

C54

.1UF_0402

.1UF_0402

1 2

1 2

+2.5V

CE17

150UF_10V_E

+2.5V

+1.2VS

401238 3B

838

1

of

5

+2.5V

JP4

1

VREF

3

DDR_DQ0

DDR_DQ3

DDR_DQS0

DDR_DQ5

D D

DDR_CLK07

DDR_CLK0#7

C C

DDR_CKE17,10

DDR_SCS#07,10 DDR_SCS#1 7,10

B B

DIMM_SMD12

DIMM_SMC12

A A

DDR_DQ1

DDR_DQ8

DDR_DQ13

DDR_DQS1

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ20

DDR_DQS2

DDR_DQ22

DDR_DQ18

DDR_DQ24

DDR_DQ25

DDR_DQS3

DDR_DQ26

DDR_DQ27

DDR_CKE1

DDR_MA12

DDR_MA9

DDR_MA7

DDR_MA5

DDR_MA3

DDR_MA1

DDR_MA10

DDR_BS0

DDR_WE#

DDR_SCS#0

DDR_DQ32

DDR_DQ37

DDR_DQS4

DDR_DQ38

DDR_DQ34

DDR_DQ44

DDR_DQ40

DDR_DQS5

DDR_DQ43

DDR_DQ42

DDR_DQ52

DDR_DQ49

DDR_DQS6

DDR_DQ55

DDR_DQ50

DDR_DQ63

DDR_DQ58

DDR_DQS7

DDR_DQ56

DDR_DQ62

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

AMP1565711-1_STANDARD 4.0

VREF

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ31

DU/RESET#

CKE0

DU/BA2

RAS#

CAS#

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQ46

DQ47

CK1#

DQ52

DQ53

DQ54

DQ55

DQ60

DQ61

DQ62

DQ63

2

4

VSS

6

DQ4

8

DQ5

10

VDD

12

DM0

14

DQ6

16

VSS

18

DQ7

20

22

VDD

24

26

DM1

28

VSS

30

32

34

VDD

36

VDD

38

VSS

40

VSS

42

44

46

VDD

48

DM2

50

52

VSS

54

56

58

VDD

60

62

DM3

64

VSS

66

68

70

VDD

72

CB4

74

CB5

76

VSS

78

DM8

80

CB6

82

VDD

84

CB7

86

88

VSS

90

VSS

92

VDD

94

VDD

96

98

100

A11

102

A8

104

VSS

106

A6

108

A4

110

A2

112

A0

114

VDD

116

BA1

118

120

122

S1#

124

DU

126

VSS

128

130

132

VDD

134

DM4

136

138

VSS

140

142

144

VDD

146

148

DM5

150

VSS

152

154

156

VDD

158

160

CK1

162

VSS

164

166

168

VDD

170

DM6

172

174

VSS

176

178

180

VDD

182

184

DM7

186

VSS

188

190

192

VDD

194

SA0

196

SA1

198

SA2

200

DU

DIMM0

TOP SIDE

5

+2.5V

4

DDR_DQ2

DDR_DQ7

DDR_DM0

DDR_DQ4

DDR_DQ6

DDR_DQ9

DDR_DQ12

DDR_DM1

DDR_DQ11

DDR_DQ10

DDR_DQ17

DDR_DQ21

DDR_DM2

DDR_DQ19

DDR_DQ23

DDR_DQ28

DDR_DQ29

DDR_DM3

DDR_DQ30

DDR_DQ31

DDR_CKE0

DDR_MA11

DDR_MA8

DDR_MA6

DDR_MA4

DDR_MA2

DDR_MA0

DDR_BS1

DDR_RAS#

DDR_CAS#

DDR_SCS#1

DDR_DQ36

DDR_DQ33

DDR_DM4

DDR_DQ39

DDR_DQ35

DDR_DQ41

DDR_DQ45

DDR_DM5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ53

DDR_DM6

DDR_DQ54

DDR_DQ51

DDR_DQ59

DDR_DQ57

DDR_DM7

DDR_DQ61

DDR_DQ60

4

SDREF

12

C95

.1UF_0402

DDR_CKE0 7,10

DDR_CLK1# 7

DDR_CLK1 7

DDR_DM[0..8]

DDR_DQ[0..63]

DDR_DQS[0..8]

DDR_MA[0..12]

DDR_MA_B[1..2]

DDR_MA_B[4..5]

3

DDR_DM[0..8] 7,10

DDR_DQ[0..63] 7,10

DDR_DQS[0..8] 7,10

DDR_MA[0..12] 7,10

DDR_MA_B[1..2] 7,10

DDR_MA_B[4..5] 7,10

3

2

+2.5V

JP3

1

VREF

3

DDR_DQ2

DDR_DQ7

DDR_DQS0

DDR_DQ4

DDR_DQ6

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ11

DDR_DQ10

DDR_CLK37

DDR_CLK3#7

DDR_DQ17

DDR_DQ21

DDR_DQS2

DDR_DQ19

DDR_DQ23

DDR_DQ28

DDR_DQ29

DDR_DQS3

DDR_DQ30

DDR_DQ31

DDR_CKE37,10

DDR_BS07,10

DDR_SCS#27,10

DIMM_SMD12

DIMM_SMC12

DDR_CKE3

DDR_MA12

DDR_MA9

DDR_MA7 DDR_MA6

DDR_MA_B5

DDR_MA3

DDR_MA_B1

DDR_MA10

DDR_BS0

DDR_WE#

DDR_SCS#2

DDR_DQ36

DDR_DQ33

DDR_DQS4

DDR_DQ39

DDR_DQ35

DDR_DQ41

DDR_DQ45

DDR_DQS5

DDR_DQ47

DDR_DQ46

DDR_DQ48

DDR_DQ53

DDR_DQS6

DDR_DQ54

DDR_DQ51

DDR_DQ59

DDR_DQ57

DDR_DQS7

DDR_DQ61

DDR_DQ60

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

AMP1565619_REVERSE 5.2

VREF

DQ4

DQ5

VDD

DM0

DQ6

DQ7

DQ12

VDD

DQ13

DM1

DQ14

DQ15

VDD

VDD

DQ20

DQ21

VDD

DM2

DQ22

DQ23

DQ28

VDD

DQ29

DM3

DQ30

DQ31

VDD

DM8

VDD

DU/RESET#

VDD

VDD

CKE0

DU/BA2

VDD

RAS#

CAS#

DQ36

DQ37

VDD

DM4

DQ38

DQ39

DQ44

VDD

DQ45

DM5

DQ46

DQ47

VDD

CK1#

DQ52

DQ53

VDD

DM6

DQ54

DQ55

DQ60

VDD

DQ61

DM7

DQ62

DQ63

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CB4

CB5

VSS

CB6

CB7

VSS

VSS

A11

A8

VSS

A6

A4

A2

A0

BA1

S1#

DU

VSS

VSS

VSS

CK1

VSS

VSS

VSS

SA0

SA1

SA2

DU

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_DQ0

DDR_DQ3

DDR_DM0

DDR_DQ5

DDR_DQ1

DDR_DQ8

DDR_DQ13

DDR_DM1

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ20

DDR_DM2

DDR_DQ22

DDR_DQ18

DDR_DQ24

DDR_DQ25

DDR_DM3

DDR_DQ26

DDR_DQ27

DDR_CKE2

DDR_MA11

DDR_MA8

DDR_MA_B4

DDR_MA_B2

DDR_MA0

DDR_BS1

DDR_RAS#

DDR_CAS#

DDR_SCS#3

DDR_DQ32

DDR_DQ37

DDR_DM4

DDR_DQ38

DDR_DQ34

DDR_DQ44

DDR_DQ40

DDR_DM5

DDR_DQ43

DDR_DQ42

DDR_DQ52

DDR_DQ49

DDR_DM6

DDR_DQ55

DDR_DQ50

DDR_DQ63

DDR_DQ58

DDR_DM7

DDR_DQ56

DDR_DQ62

+3VS

DIMM1

BOTTOM SIDE

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL,INC. AND CONTAINS CONFIDENTIAL AND TRADE

SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF COMPETENT DIVISION OF R&D DEPARTMENT

EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR

DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Title

Size Document Number Rev

Custom

Date: Sheet

1

SDREF

12

C94

.1UF_0402

DDR_CKE2 7,10

DDR_BS1 7,10

DDR_RAS# 7,10

DDR_CAS# 7,10DDR_WE#7,10

DDR_SCS#3 7,10

DDR_CLK4# 7

DDR_CLK4 7

SCHEMATIC M/B LA-1571

401238 3B

薑六月

1

of

938星@, 21, 2004

5

Layout note :

Distribute as close as possible

to DDR-SODIMM.

+2.5V

12

D D

C96

.1UF_0402_X5R

+2.5V

12

C107

.1UF_0402_X5R

Layout note :

Place one cap close to every 2 pull up resistors termination to

+1.25V

+1.25VS

12

C C

C117

.1UF_0402_X5R

+1.25VS

12

C127

.1UF_0402_X5R

+1.25VS

12

C137

.1UF_0402_X5R

+1.25VS

12

C147

B B

.1UF_0402_X5R

+1.25VS

12

C157

.1UF_0402_X5R

+1.25VS

12

C167

.1UF_0402_X5R

A A

12

C97

.1UF_0402_X5R

12

C108

.1UF_0402_X5R

12

C118

.1UF_0402_X5R

12

C128

.1UF_0402_X5R

12

C138

.1UF_0402_X5R

12

C148

.1UF_0402_X5R

12

C158

.1UF_0402_X5R

12

C168

.1UF_0402_X5R

12

C98

.1UF_0402_X5R

12

C109

.1UF_0402_X5R

12

C119

.1UF_0402_X5R

12

C129

.1UF_0402_X5R

12

C139

.1UF_0402_X5R

12

C149

.1UF_0402_X5R

12

C159

.1UF_0402_X5R

12

C169

.1UF_0402_X5R

12

C99

.1UF_0402_X5R

12

C110

.1UF_0402_X5R

12

C120

.1UF_0402_X5R

12

C130

.1UF_0402_X5R

12

C140

.1UF_0402_X5R

12

C150

.1UF_0402_X5R