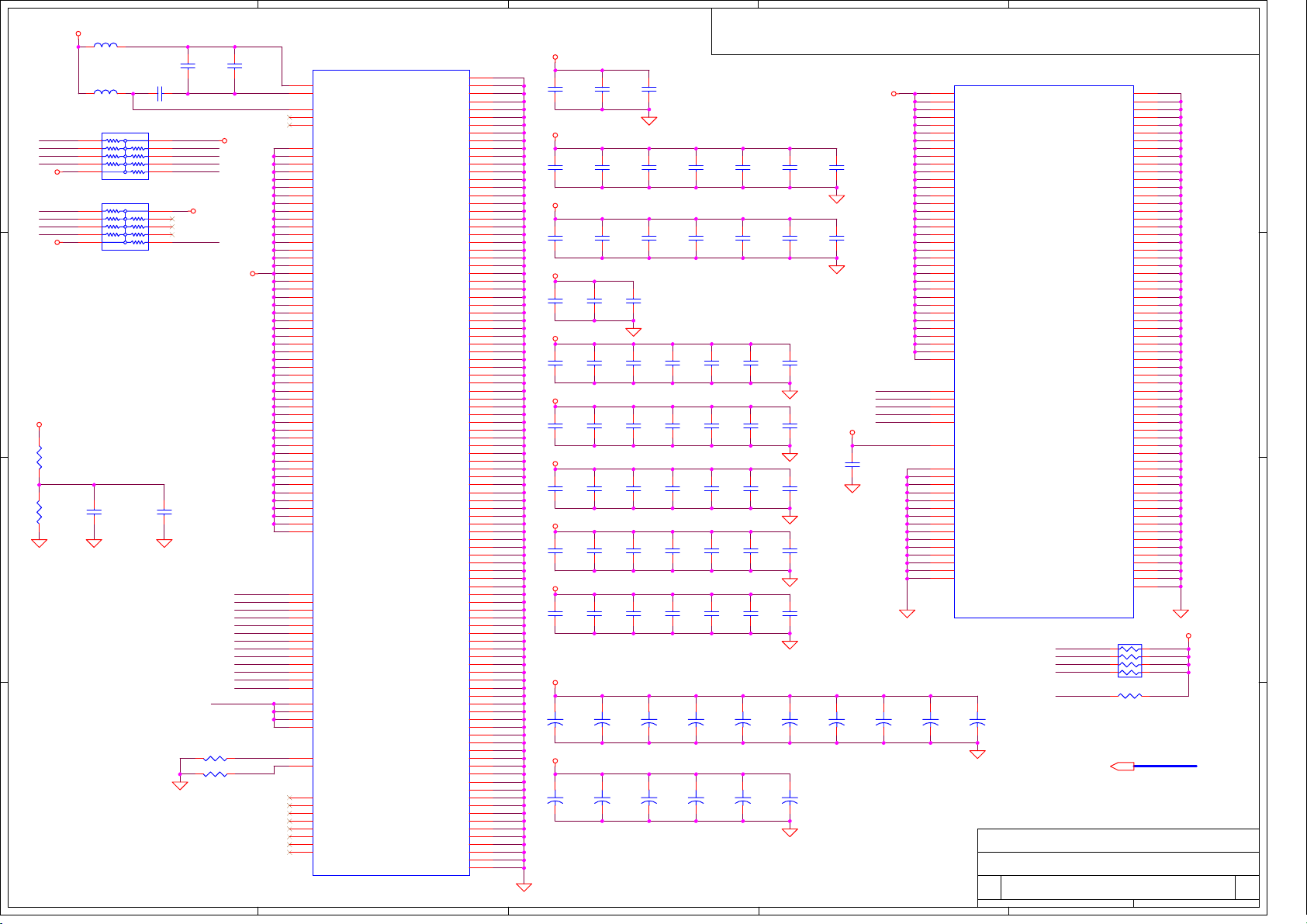

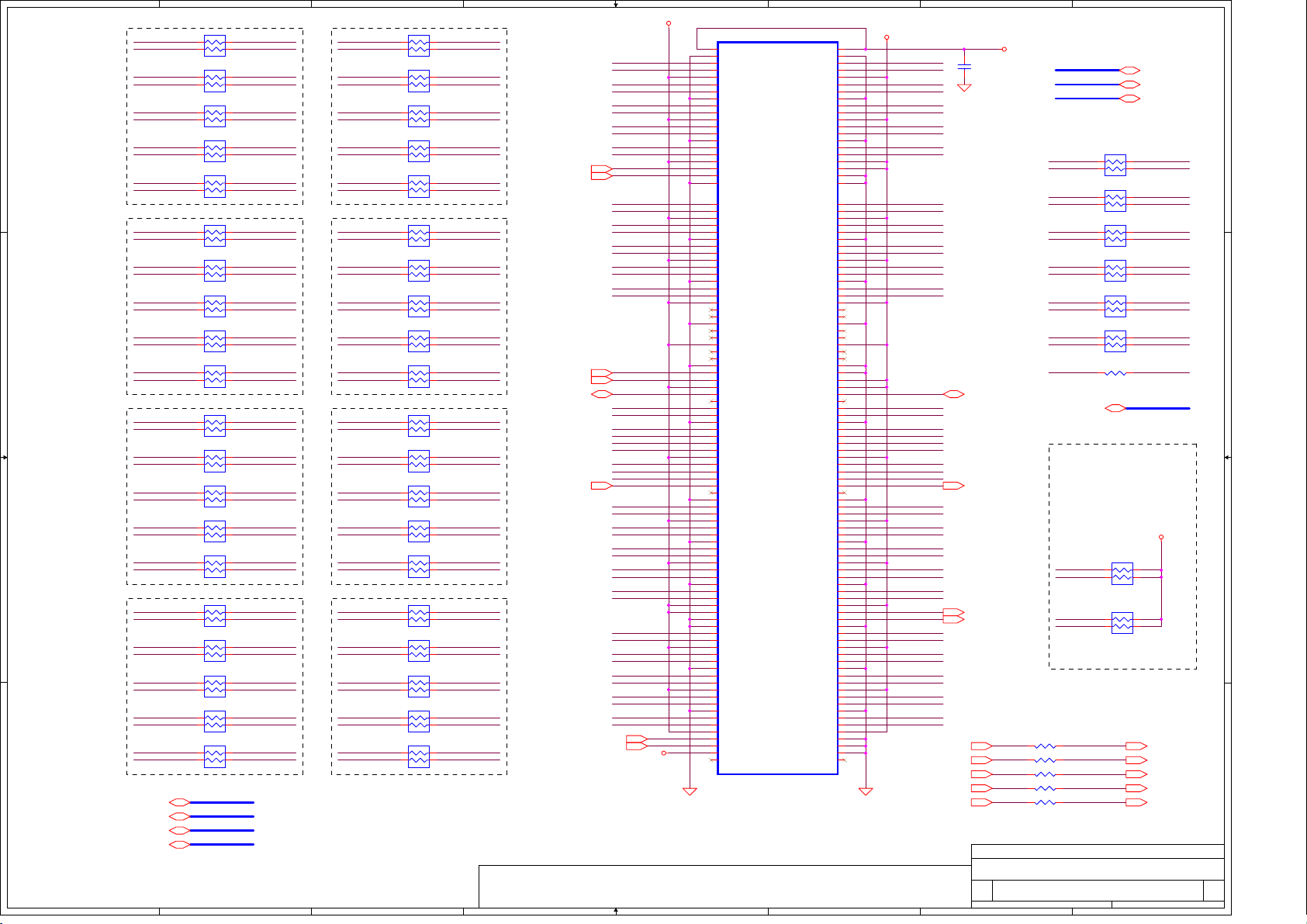

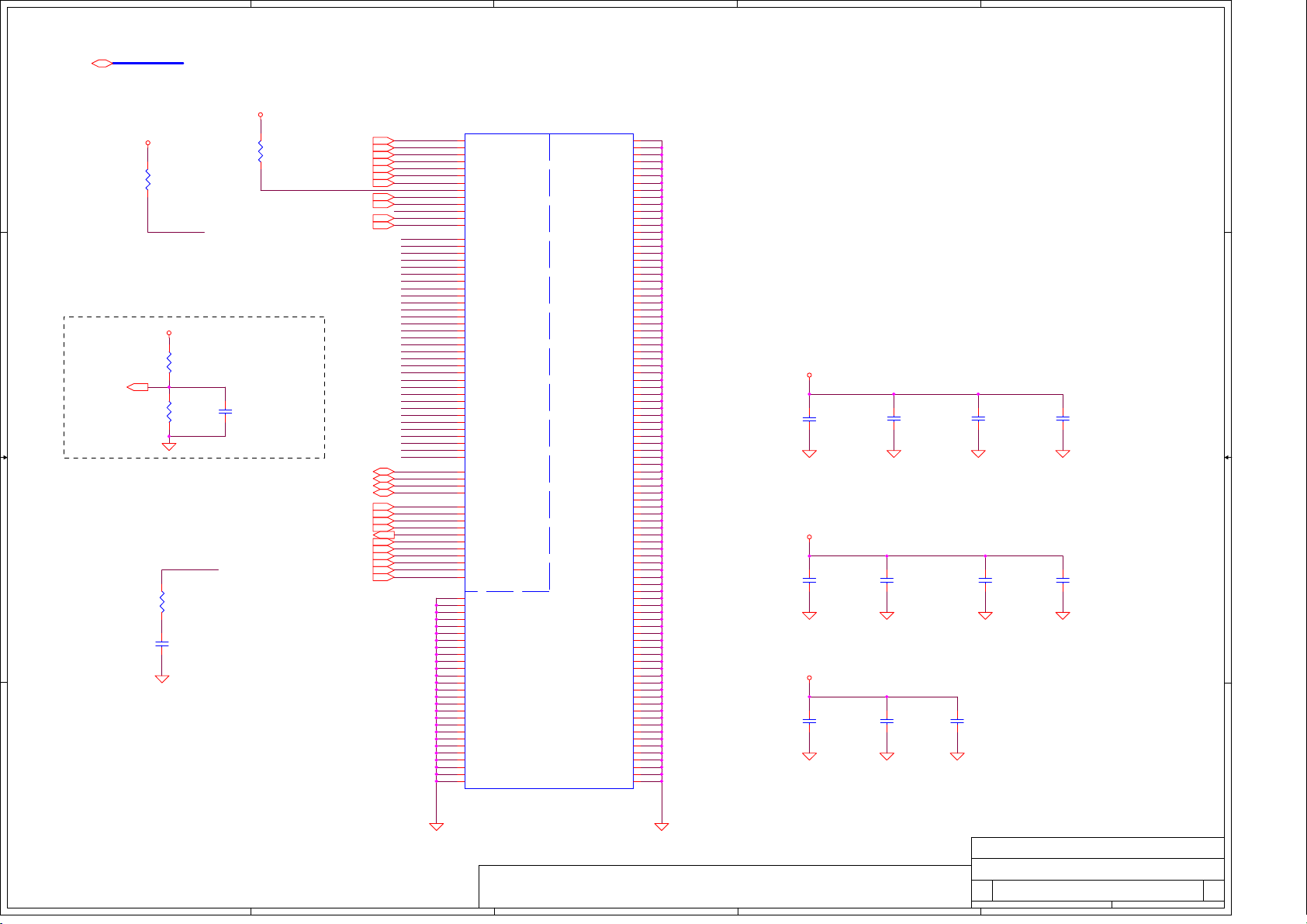

Acer LA-1541 Schematics

A

1 1

2 2

B

C

D

E

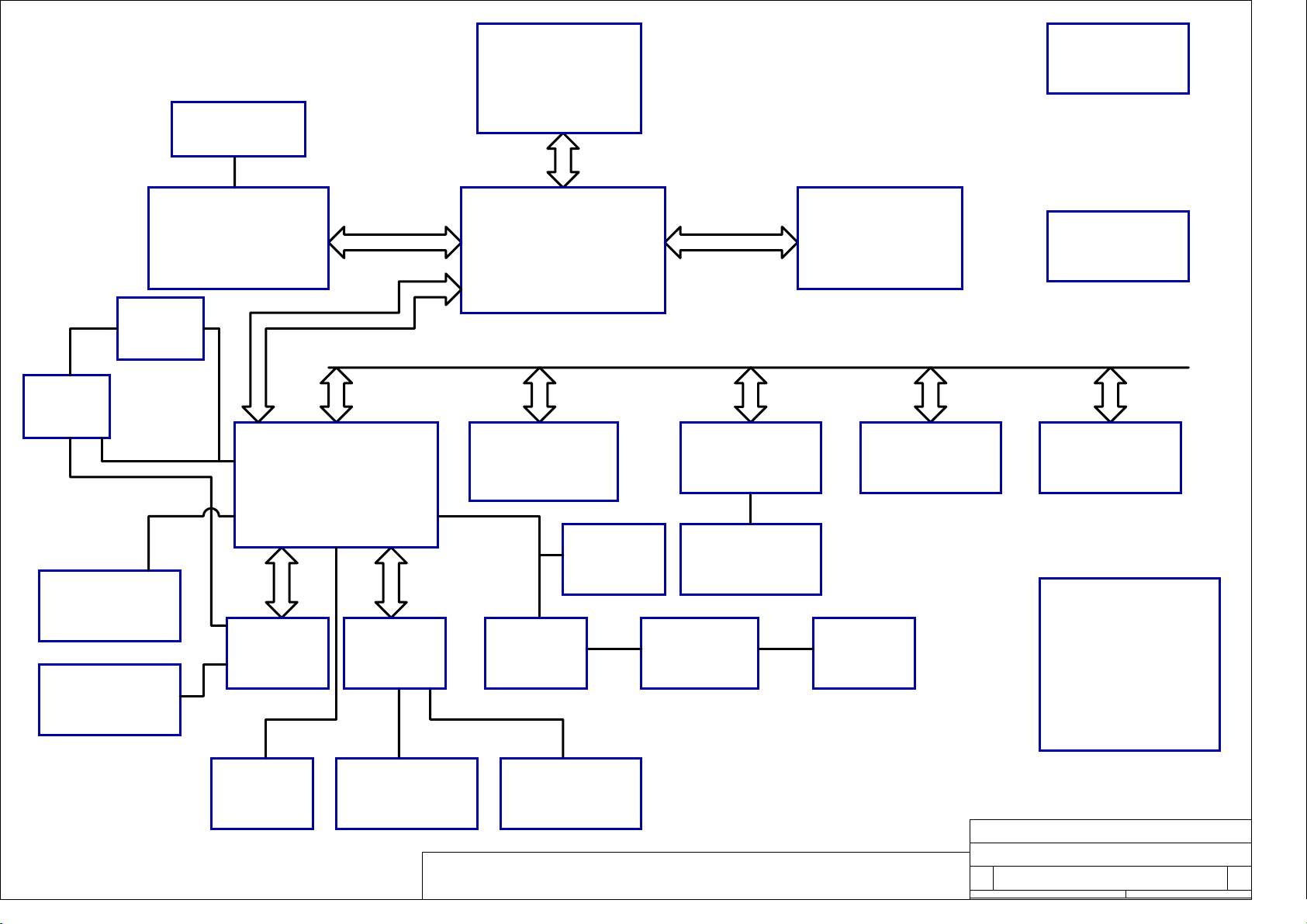

BTS88 LA-1541 REV0.3 Schematics Document

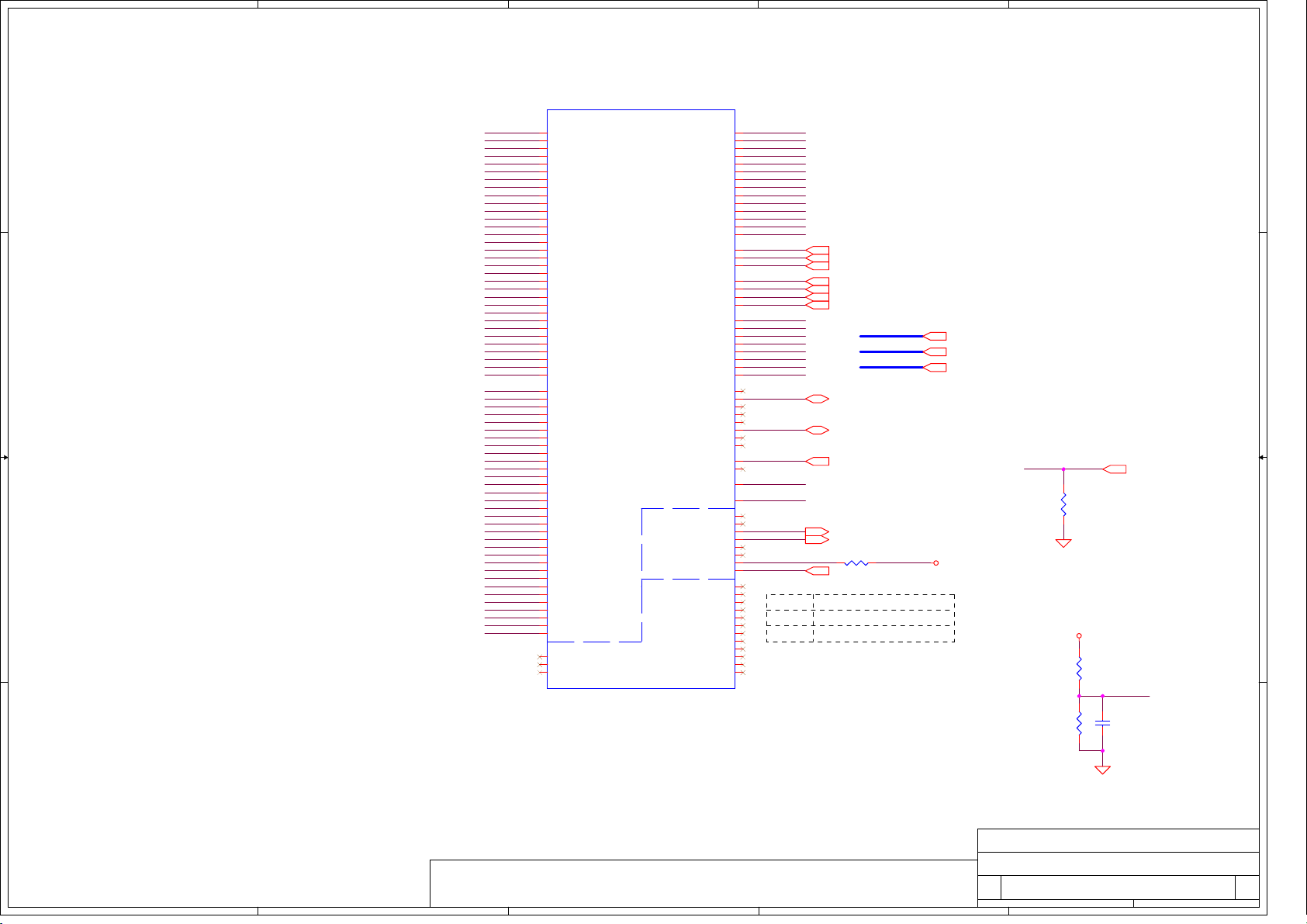

Intel Pentium 4 Processor in the 478-pin Package

with 845PE / ICH4 / NVIDIA SQ17 chipset

2002-10-26-A

3 3

4 4

A

B

C

For B2-Test

Compal Electronics, Ltd.

Title

BTS88 Cover Sheet

Size Document Number Re v

B

LA1541

Date: Sheet of

星期二

29, 2002

D

十月

148,

E

0.3

COMPAL CONFIDENTIAL

MODEL NAME :BTS88

REV:0.3

CRT & TV-OUT

LCD

PAGE 18

Pentium4/Northwood

mPGA478 CPU

PAGE 4,5

PSB

CLOCK

ICS950810

PAGE 12

INTERNAL IDE

IDE/CD

/FDD

PAGE 28

USB/BlueTooth

/FIR

LPT PORT

MDC

NVIDIA SQ17_A5

16MB DDR SDRAM

PIRQA#

Direct CD

Play-OZ168

PAGE 27

PAGE 31

LPC 47N227

PAGE 29

PAGE 13,14,15,

16,17

HUB Link

ICH4

FUNC 0: LAN, HUB-TO-PCI ,

PCI-TO-LPC BRIDGE

FUNC 1: IDE Controller

FUNC 2: USB Controller #1

FUNC 3: SM BUS Controller

FUNC 4: USB Controller #2

FUNC 5: AC97 Audio Controller

FUNC 5: AC97 Modem Controller

LPC

SIO

PAGE 30

PAGE 19,20,21

EC/KBC

PC87591

PCI BUS

LPC

PAGE 36

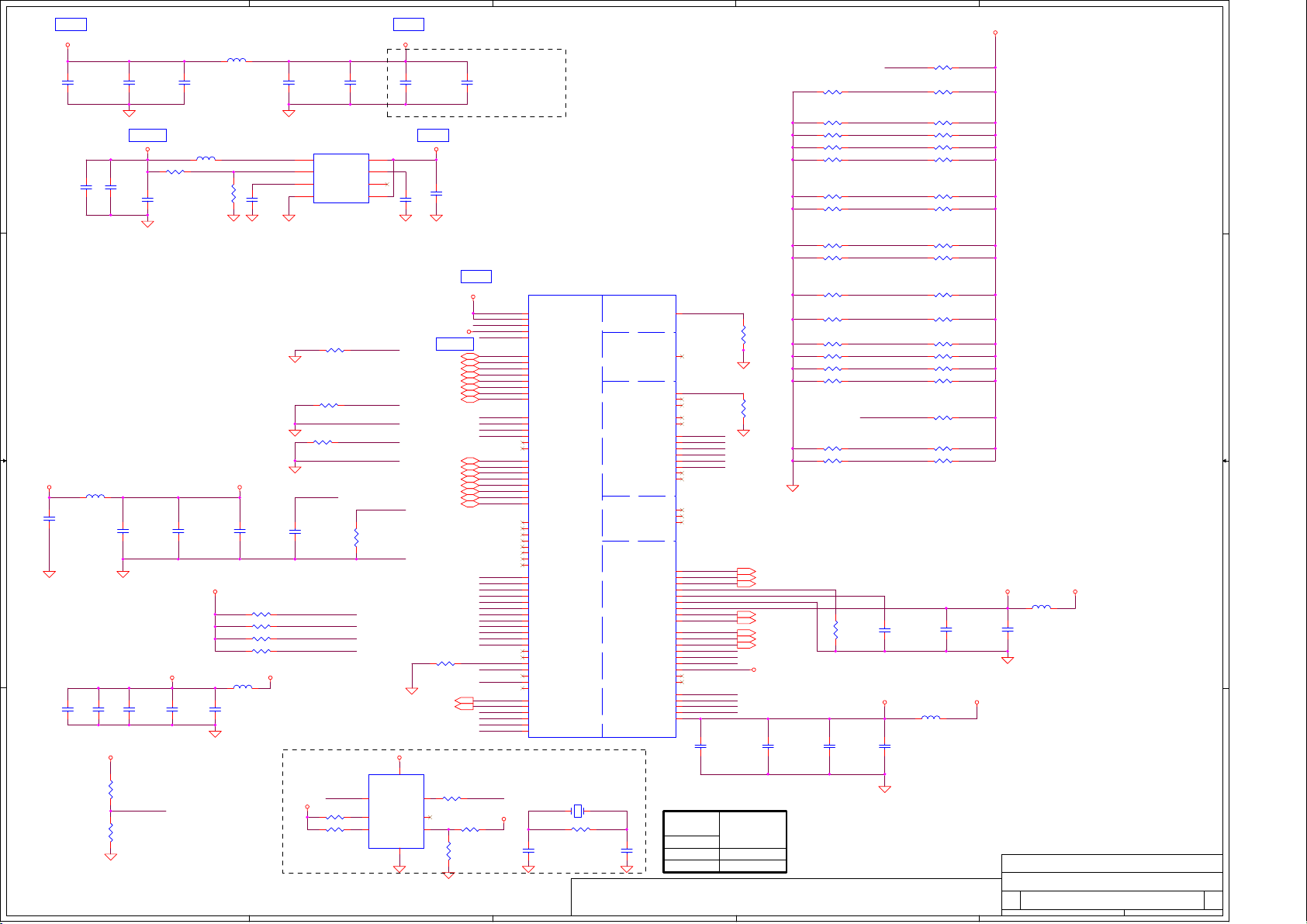

Brookdale-E MCH

845PE

Host-AGP Bridge

DRAM controller

Hub interface

1394 Controller

TAB43AB21

AC LINK

AC97 Codec

ALC202

PAGE 32 PAGE 33

IDSEL: AD16

MASTER 0

PIRQA#

PAGE 7,8,9

PAGE 22

MDC

Connector

PAGE 29

MEMORY BUSAGP BUS

CARDBUS

OZ6933

PCMCIA

SOCKET

AUDIO

HARDWARE

EQ

DDR DIMM*2

IDSEL: AD20

MASTER 2

PIRQA#, PIRQB#

SIRQ

PAGE 23

PAGE 24

AMP &

Audio

Jack

PAGE 9,10,11

IDSEL: AD17

MASTER 3

PIRQB#

LAN Controller

RTL8100BL

PAGE 25

PAGE 34

POWER

INTERFACE

PAGE 38

IDSEL: AD18

MASTER 1

PIRQC#, PIRQD#

Mini PCI

Connector

PAGE 26

DC/DC POWER

+GPU_CORE POWER (+1.2V)

+1.25VS POWER

+1.5VALW POWER

+2.5V POWER

+3VALW POWER

+5VALW POWER

+12VALW POWER

+CPU_CORE POWER

PAGE 41,42,43,44,45,46,47

SD

W83L518D

PAGE 35

BIOS

EC BUFFER

PAGE 37 PAGE 39

PROPRIETARY NOTE

Switchs &

Connectors

FAN

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Size Document Number Re v

B

Date: Sheet of

BTS88 BLOCK DIAGRAM

LA1541

星期二

29, 2002

十月

0.3

248,

A

B

C

D

E

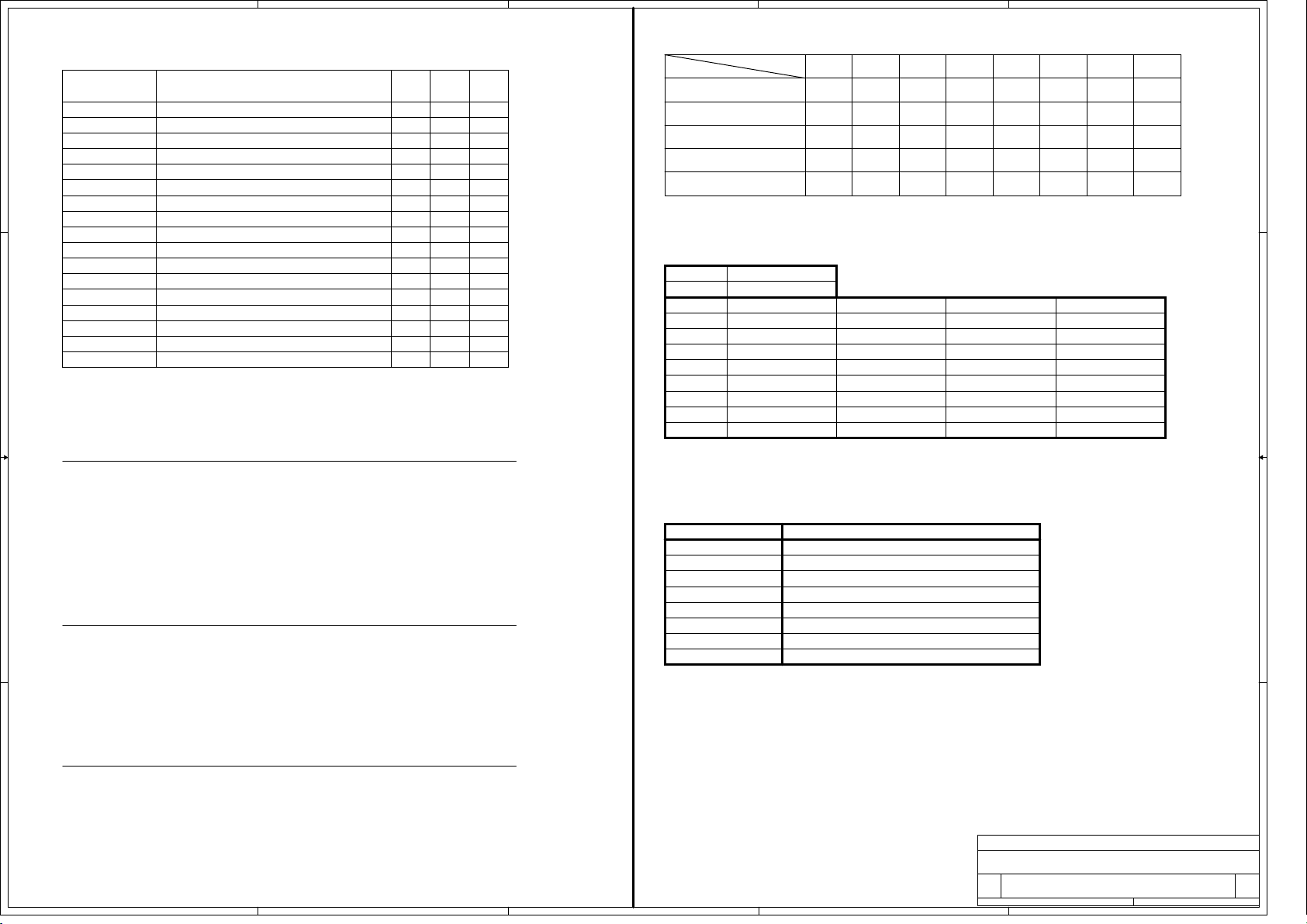

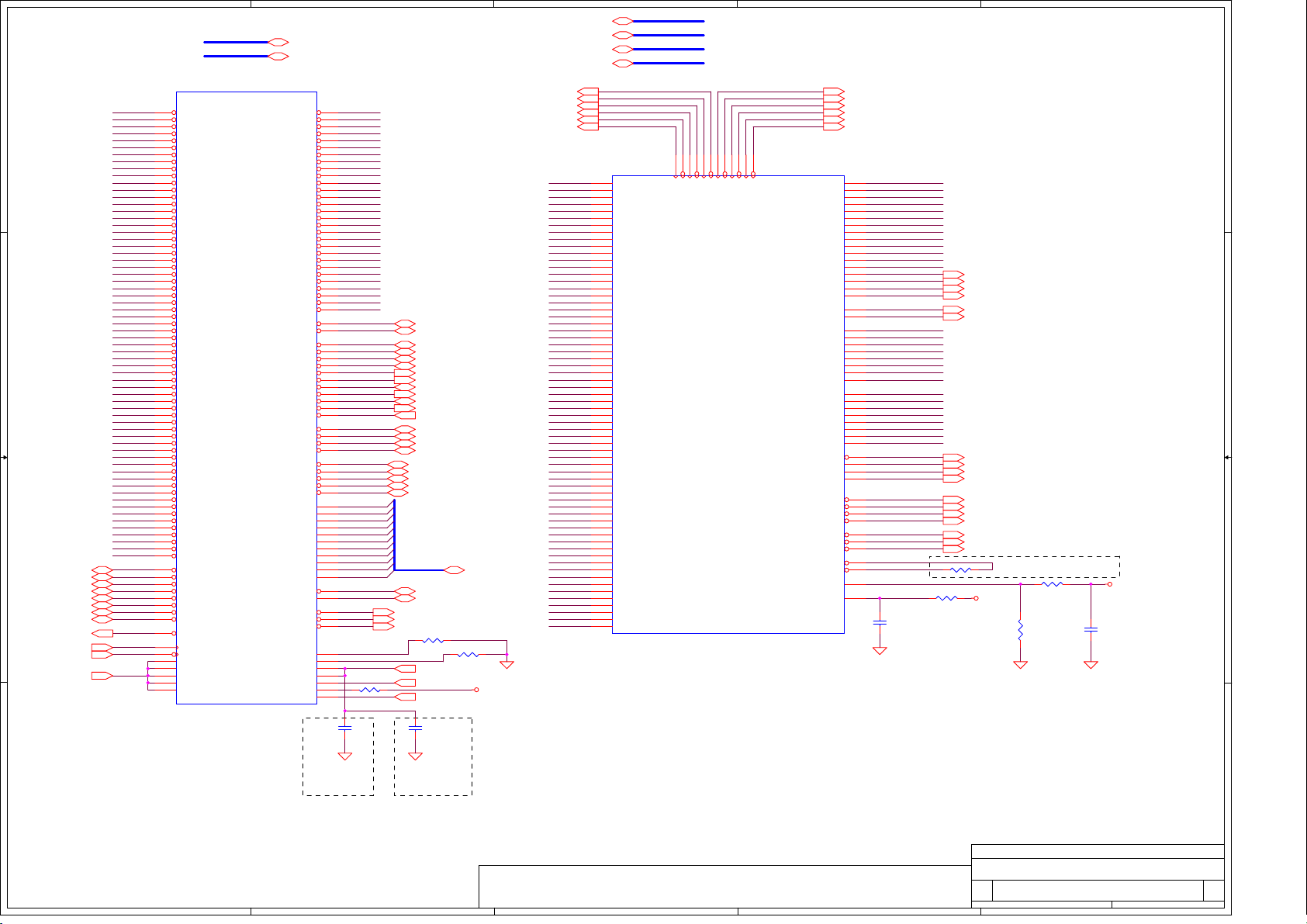

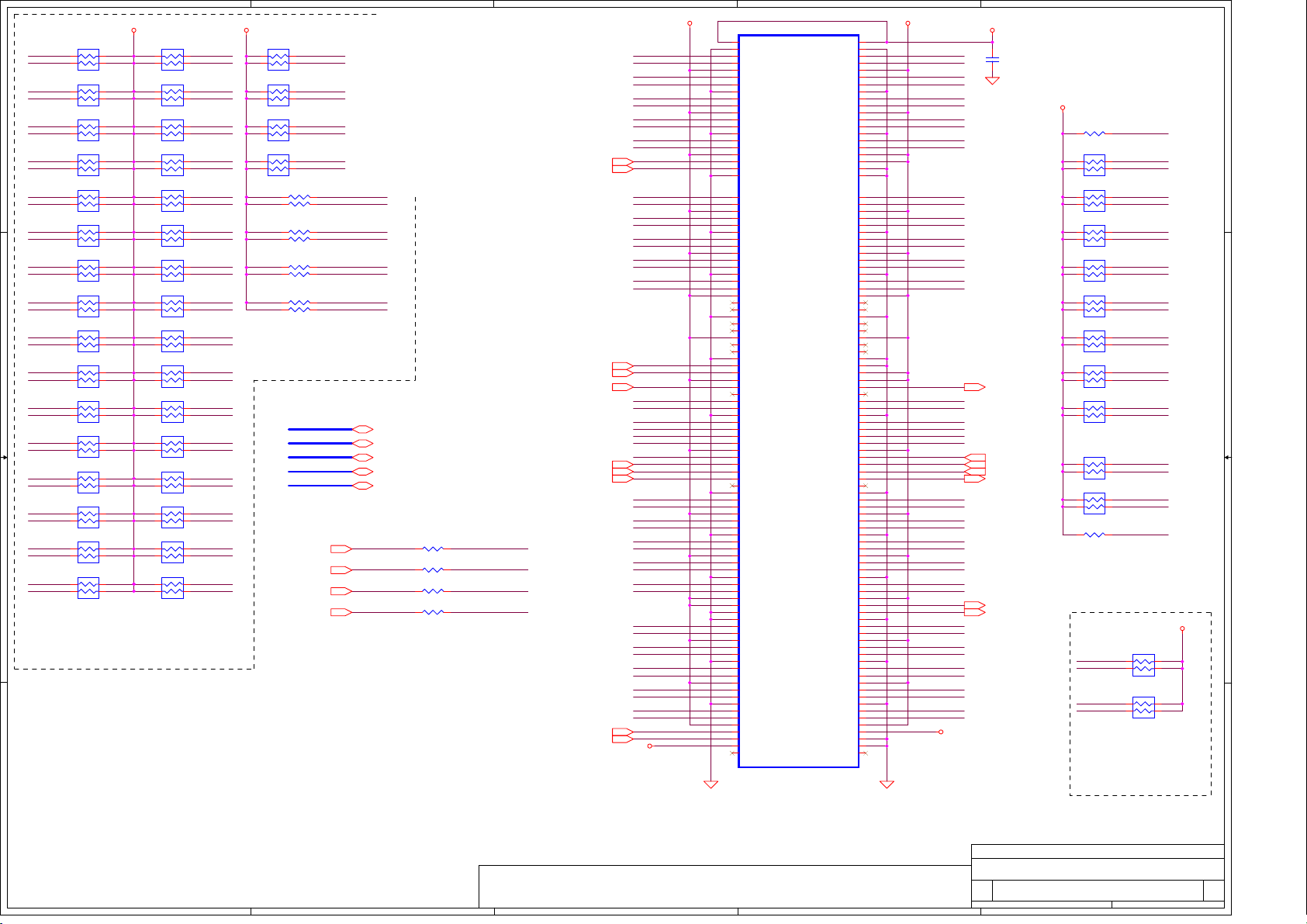

Voltage Rails

STATE

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+1.2VP

+1.25VS 1.25V switched power rail

+1.5VALW 1.5V always on power rail ON ON ON*

+2.5V

+2.5VS 2.5V switched power rail

+3VALW

+3V

+3VS

+5VALW

+5V

+5VS

RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

AGP 4 X ON OFF OFF+1.5VS

2.5V power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

N/A N/A N/A

N/AN/AN/A

ON OFF

ON OFF

ON OFF OFF

ON

ON

ON

ON

ON

ON

ON ON

ON

ON+12VALW

ON

OFF

OFF

OFF

ON

OFF

OFF

ON ON *

OFF

ON

OFF

OFF

ON

ON*

OFF

OFF

OFF

ON

ON*

ON

ON

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW

AD_BID

0 V

HIGH

LOWLOWLOW

ON

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

Vtyp

AD_BID

0 V 0 V

ON

ON

ON

OFF

OFF

V

AD_BID

ON ON

ON

OFF

OFF

OFF

max

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

3.300 V

LOW

OFF

OFF

OFF

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

VGA

CardBus

LAN

Mini-PCI

1394

3 3

AD20

AD17

AD18

AD16 0

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

0001 011X b

1010 000X b

1011 000Xb

2

3PIRQB

1/4

EC SM Bus2 address

Device

MAX1617MEE

OZ168

Smart Battery

Docking

DOT Board

PIRQA

PIRQA/PIRQB

PIRQC/PIRQD

PIRQA

1001 110X b

0011 0100 b

0001 011X b

0011 011X b

XXXX XXXXb

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

0.2

0.3

ICH4 SM Bus address

Device

4 4

Clock Generator (

ICS950810)

DDR DIMM0

DDR DIMM1

A

Address

1101 001Xb

1001 000Xb

1001 001Xb

Compal Electronics, Ltd.

Title

BTS88 Notes

Size Document Number Re v

B

B

C

D

Date: Sheet of

LA1541

星期二

29, 2002

十月

348,

E

0.3

A

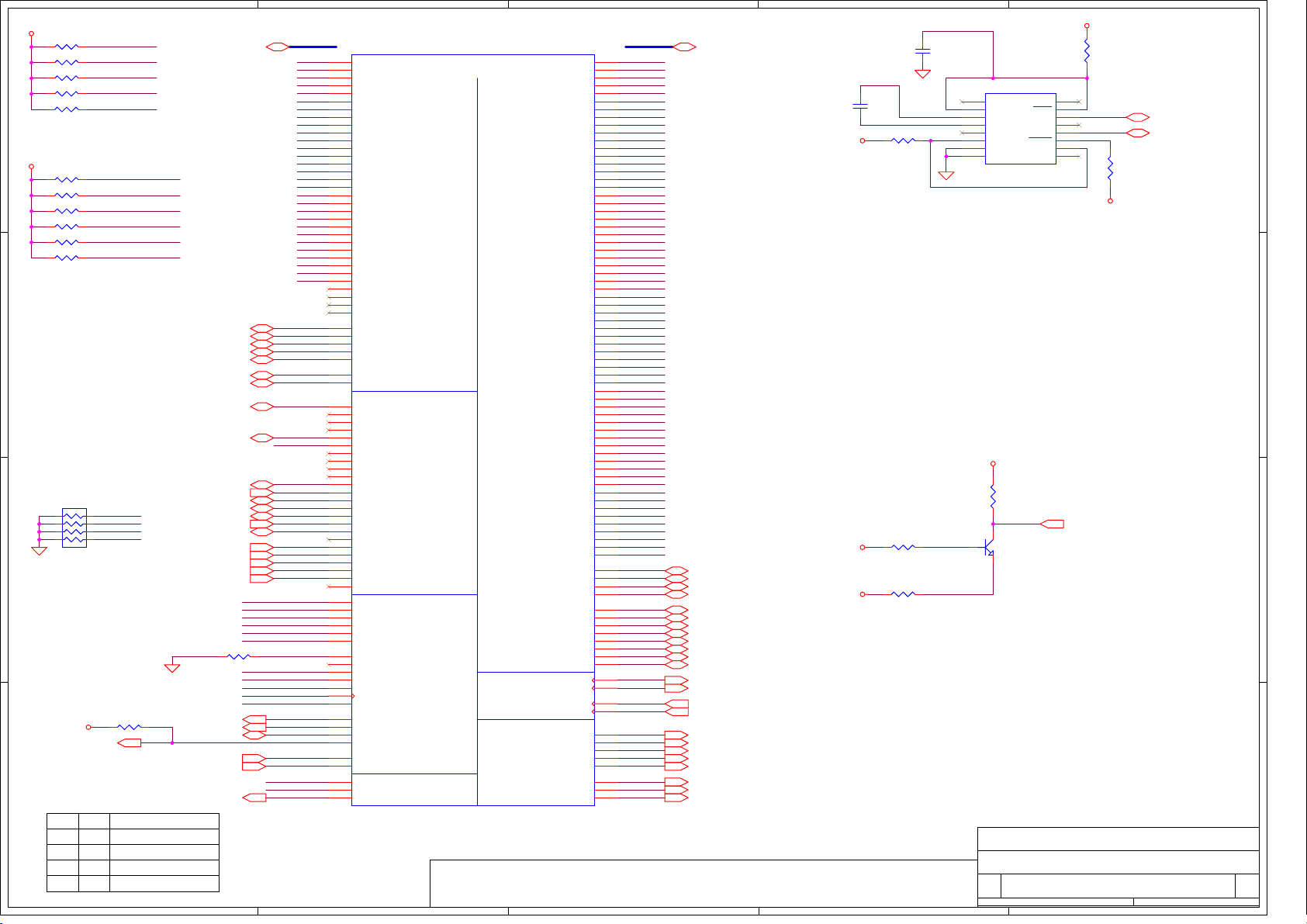

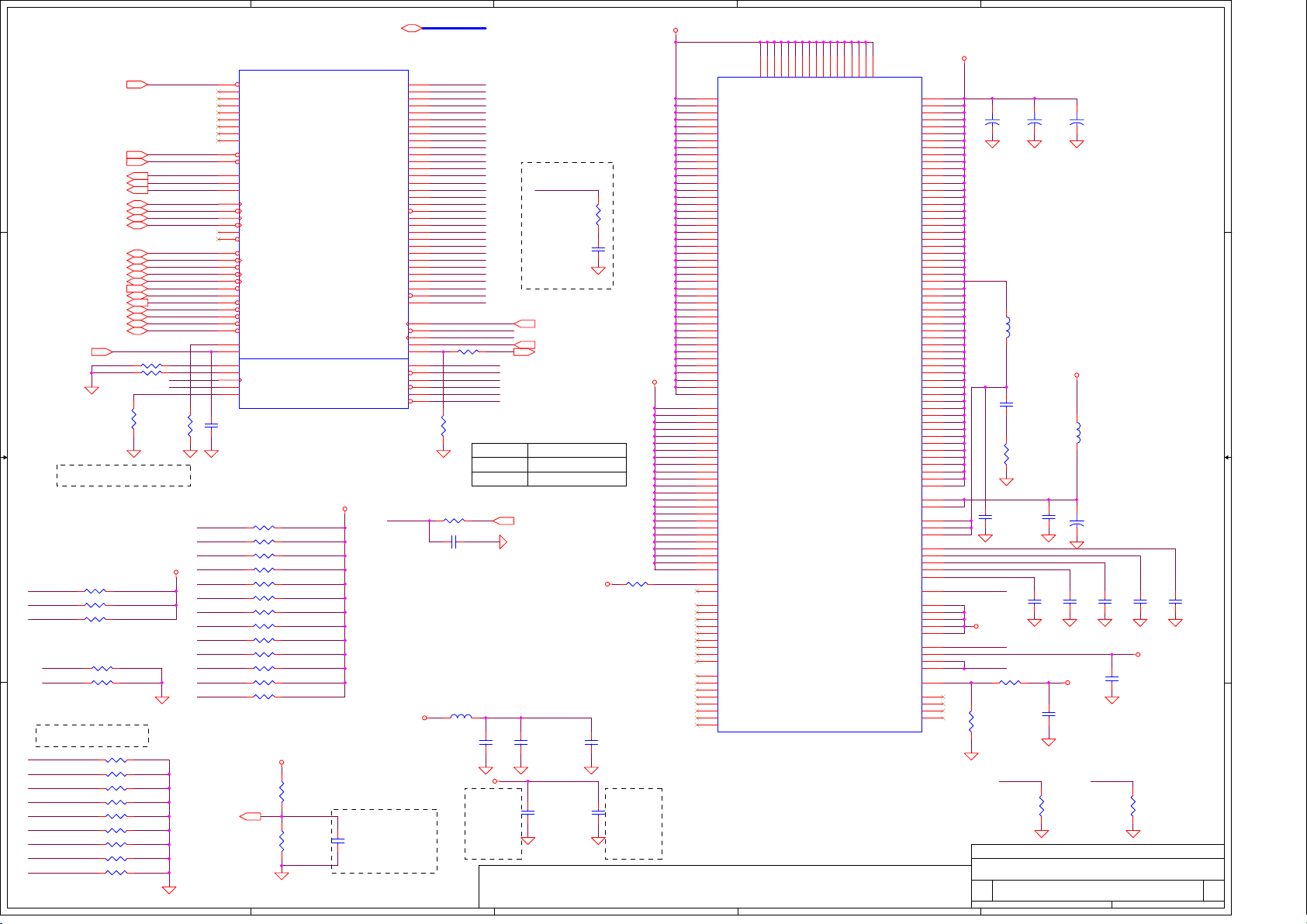

+CPU_CORE

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

W1

62_0402_5%

62_0402_5%

CPURST#

H_FERR#

H_PWRGD

BREQ0#

IERR#

H_BPM0#

H_BPM1#

H_BPM2#

H_BPM3#

H_BPM4_PRDY#

H_BPM5_PREQ#

Near ICH trace:10mils

R88 51_0603_1%

1 2

R24

R57 300_0603_1%

R40 200_0603_1%

1 2

R14

4 4

+CPU_CORE

1 2

R39 51_0603_1%

1 2

R38 51_0603_1%

1 2

R35 51_0603_1%

1 2

R37 51_0603_1%

1 2

R36 51_0603_1%

1 2

R34 51_0603_1%

HA#[3..31]6

W2

AB1

HREQ#06

HREQ#16

3 3

RP2

1 8

2 7

3 6

4 5

2 2

+3VALW

1 1

BSEL1 BSEL0

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_TDI

1.5K_8P4R _1206_5%

1 2

R67 150_0402_5%

ITP_DBRESET#20

SYSTEM BUS FREQUENCY

LLL

LH

HHH

100MHz

133MHz

RESERVED

RESERVED

A

HREQ#26

HREQ#36

HREQ#46

HADSTB0#6

HADSTB1#6

ADS#6

BNR#6

BREQ0#6

BPRI#6

HLOCK#6

HIT#6

HITM#6

DEFER#6

DRDY#6

CPURST#6

HTRDY#6

RS#06

RS#16

RS#26

R73 33_0402_5%

1 2

H_BSEL07,12

H_BSEL112

DBSY#6

H_PWRGD19

H_CPUSLP#19

IERR#

BREQ0#

CPURST#

H_BPM0#

H_BPM1#

H_BPM2#

H_BPM3#

H_BPM4_PRDY#

H_BPM5_PREQ#

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

PRO_CHOT#

BSEL0

H_PWRGD

H_CPUSLP#

THERMDA

THERMDC

THERTRIP#

AC1

AA3

AC3

K25

K26

L25

AB25

AB2

AC6

AB5

AC4

AA5

AB4

AF26

AD6

AD5

AE25

AB23

AB26

J26

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

T5

U4

V3

Y1

J1

K5

J4

J3

H3

L5

R5

G1

V5

G2

H6

D2

G4

F3

E3

E2

H2

V6

J6

F1

G5

F4

Y6

D5

C1

F7

E6

D4

C3

H5

B3

C4

A2

U39A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

ADSTB1#

ADS#

AP0#

AP1#

BINIT#

BNR#

IERR#

DP0#

DP1#

DP2#

DP3#

BREQ0#

BPRI#

LOCK#

HIT#

HITM#

DEFER#

DRDY#

MCERR#

RESET#

TRDY#

RS0#

RS1#

RS2#

RSP#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

SKTOCC#

TDO

TDI

TMS

TRST#

TCK

PROCHOT#

BSEL0

BSEL1

DBSY#

DBR#

PWRGOOD

SLP#

THERMDA

THERMDC

THERMTRIP#

mPGA478

B

ADDR GROUP

CONTROL GROUP

THERMAL DIODE

B

Northwood

MISC

PROPRIETARY NOTE

C

HD#[0..63]

HD#0

B21

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

DATA GROUP

HOST CLK

LEGACY CPU

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI0#

DBI1#

DBI2#

DBI3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

BCLK0

BCLK1

ITPCLK0

ITPCLK1

A20M#

FERR#

IGNNE#

INTR/LINT0

NMI/LINT1

INIT#

STPCLK#

SMI#

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

E21

G25

P26

V21

E22

K22

R22

W22

F21

J23

P23

W23

AF22

AF23

AC26

AD26

C6

B6

B2

D1

E5

W5

Y4

B5

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_A20M#

H_FERR#

H_IGNNE#

H_INTR

H_NMI

C

HD#[0..63] 6

DBI0# 6

DBI1# 6

DBI2# 6

DBI3# 6

DSTBN0# 6

DSTBN1# 6

DSTBN2# 6

DSTBN3# 6

DSTBP0# 6

DSTBP1# 6

DSTBP2# 6

DSTBP3# 6

CLK_HCLK 12

CLK_HCLK# 12

CLK_ITP_BCLK 12

CLK_ITP_BCLK# 12

H_A20M# 19

H_FERR# 19

H_IGNNE# 19

H_INTR 19

H_NMI 19

H_INIT# 19

H_STPCLK# 19

H_SMI# 19THERTRIP#20

space:10mils

2200P_0402_25V7K

+CPU_CORE

+CPU_CORE

C55

1 2

+5VS

1 2

R774 62_0402_5%

1 2

R15 62_0402_5%

D

R51

D

C45

0.1U_0402_10V6K

THERMDA

THERMDC

1K_0402_5%

10K_0402_5%

R773

2

B

PRO_CHOT#

E

+5VS

R45

200_0402_5%

1617VCC

U4

1

NC

2

VCC

3

DXP

4

DXN

5

NC

SMBDATA

6

ADD1

7

GND

8

GND

NE1618DS/MAX6654

STBY

SMBCLK

ALERT

ADD0

1 2

16

NC

15

14

13

NC

12

ATF#

11

10

9

NC

EC_SMC2 27,36

EC_SMD2 27,36

R46

1K_0402_5%

1 2

+5VS

+3VS

1 2

1

C

Q54

2SC2411K_SOT23

E

3

PROCHOT# 36

Compal Electronics, Inc.

Title

Pentium 4/Northwood Processor in mPGA478

Size Document Number Re v

B

LA1541

Date: Sheet of

星期二

29, 2002

十月

448,

E

0.3

A

+CPU_CORE

1 2

L4

LQG21N4R7K 10_0805

22U_1206_16V4Z_V1

1 2

LQG21N4R7K 10_0805

4 4

TESTHI0

TESTHI1

TESTHI2

TESTHI3

+CPU_CORE

TESTHI8

TESTHI9

TESTHI10

TESTHI11

+CPU_CORE

3 3

+CPU_CORE

12

R52

49.9_0603_1%

CPU_GTLREF

R56

100_0603_1%

1 2

2 2

1 1

C91 22U_1206_16V4Z_V1

L6

RP65

1

2

3

4

5

4.7K_10P8R_1206_5%

RP3

1

2

3

4

5

4.7K_10P8R_1206_5%

C71

1U_0603_10V6K

A

C66

10

TESTHI7

9

TESTHI6

8

TESTHI5

7

TESTHI4

6

10

9

8

7

6

C56

220P_0402_50V8K

+VCCA

VSSA

+CPU_CORE

TESTHI12

+CPU_CORE

1 2

R87

1 2

R11

VCCIOPLL

+CPU_CORE

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

CPU_GTLREF

COMP0

51.1_0603_1%

COMP1

51.1_0603_1%

C79

1U_0603_10V6K

AD20

AD22

AE23

AA10

AA12

AA14

AA16

AA18

AB11

AB13

AB15

AB17

AB19

AC10

AC12

AC14

AC16

AC18

AD11

AD13

AD15

AD17

AD19

AE10

AE12

AE14

AE16

AE18

AE20

AF11

AF13

AF15

AF17

AF19

AF21

AD24

AC21

AC20

AC24

AC23

AA20

AB22

AD25

AA21

AE21

AF24

AF25

A10

A12

A14

A16

A18

A20

AA8

AB7

AB9

AC8

AD7

AD9

AE6

AE8

AF2

AF5

AF7

AA2

AA6

F20

L24

A22

AD2

AD3

AF3

A5

A4

A8

U6

W4

Y3

A6

F6

P1

A7

U39B

VCCA

VSSA

VCCIOPLL

VCCSENSE

VSSSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

GTLREF

GTLREF

GTLREF

GTLREF

COMP0

COMP1

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

mPGA478

B

PLL ANALOG VOLTAGE

Northwood

POWER,

GROUND,

RESERVED

SIGNALS

B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D10

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

B4

B8

C11

C13

C15

C17

C19

C2

C22

C25

C5

C7

C9

D12

D14

D16

D18

D20

D21

D24

D3

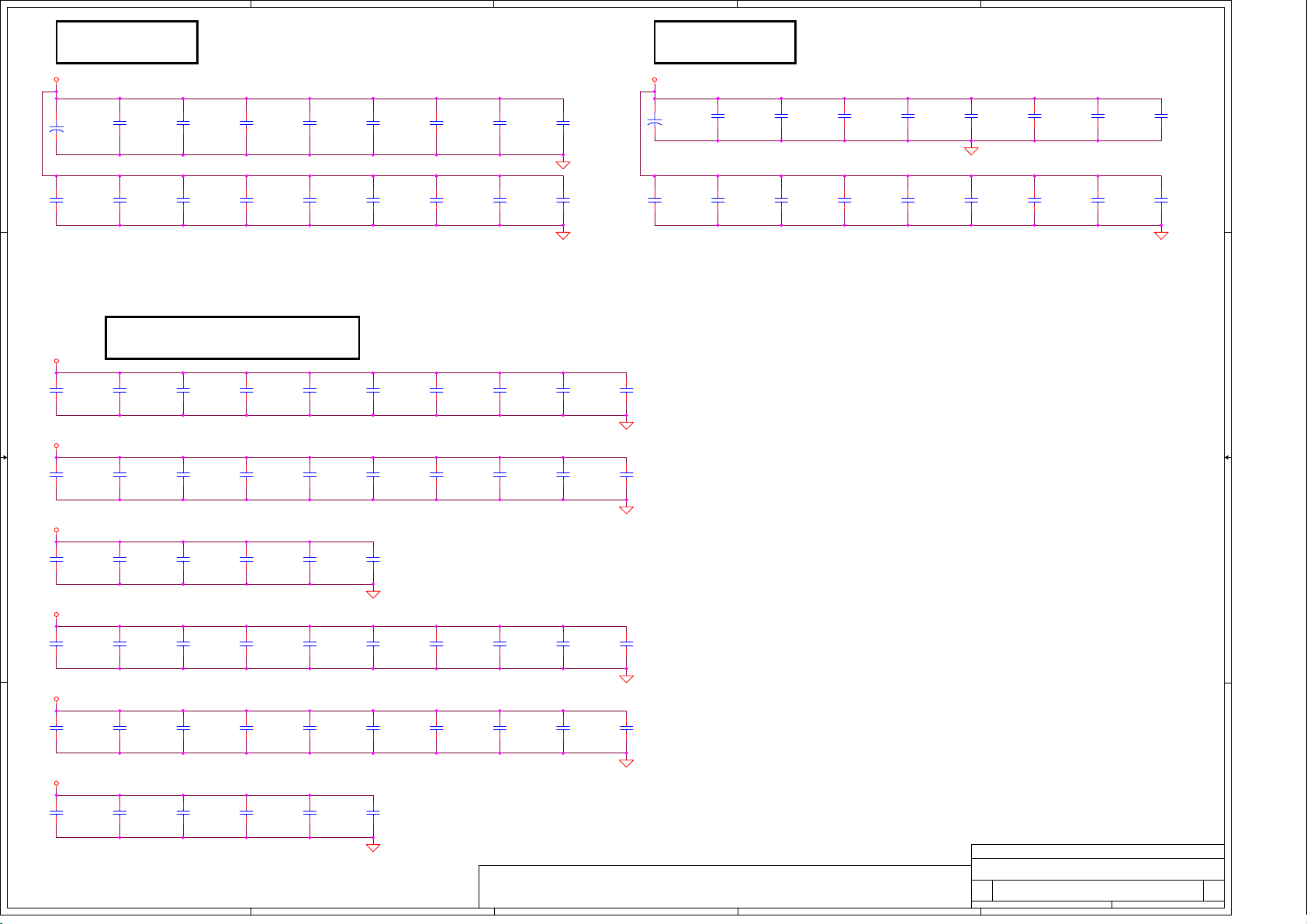

+CPU_CORE

C423

0.1U_0402_10V6K

+CPU_CORE

C436

0.1U_0402_10V6K

+CPU_CORE

C444

1U_0603_10V6K

+CPU_CORE

10U_1206_6.3V6M

C508

10U_1206_6.3V6M

+CPU_CORE

C505

10U_1206_6.3V6M

+CPU_CORE

C454

10U_1206_6.3V6M

+CPU_CORE

C453

10U_1206_6.3V6M

+CPU_CORE

C435

10U_1206_6.3V6M

+CPU_CORE

C476

10U_1206_6.3V6M

+CPU_CORE

12

C365

+

470U_D_2.5VM

+CPU_CORE

12

C457

+

470U_D_2.5VM

0.1U_0402_10V6K

C429

0.1U_0402_10V6K

C439

1U_0603_10V6K

C415

C507

10U_1206_6.3V6M

C504

10U_1206_6.3V6M

10U_1206_6.3V6M

C402

10U_1206_6.3V6M

10U_1206_6.3V6M

C393

10U_1206_6.3V6M

10U_1206_6.3V6M

C441

10U_1206_6.3V6M

10U_1206_6.3V6M

C498

10U_1206_6.3V6M

470U_D_2.5VM

12

C364

+

470U_D_2.5VM

12

C466

+

C

C433

0.1U_0402_10V6K

0.1U_0402_10V6K

C424

0.1U_0402_10V6K

C406

1U_0603_10V6K

C506

10U_1206_6.3V6M

10U_1206_6.3V6M

C502

C503

10U_1206_6.3V6M

C403

C404

10U_1206_6.3V6M

C396

C401

10U_1206_6.3V6M

C448

C456

10U_1206_6.3V6M

C497

C496

12

C366

+

470U_D_2.5VM

12

C8

+

470U_D_2.5VM

C

PROPRIETARY NOTE

C430

0.1U_0402_10V6K

1U_0603_10V6K

C450

C501

10U_1206_6.3V6M

C405

10U_1206_6.3V6M

C414

10U_1206_6.3V6M

C459

10U_1206_6.3V6M

C495

10U_1206_6.3V6M

470U_D_2.5VM

12

C367

+

470U_D_2.5VM

12

C9

+

0.1U_0402_10V6K

C434

1U_0603_10V6K

C447

1U_0603_10V6K

10U_1206_6.3V6M

C500

10U_1206_6.3V6M

C451

10U_1206_6.3V6M

10U_1206_6.3V6M

C426

10U_1206_6.3V6M

10U_1206_6.3V6M

C464

10U_1206_6.3V6M

10U_1206_6.3V6M

C494

10U_1206_6.3V6M

12

C515

+

330U_D_2.5VM

12

C10

+

470U_D_2.5VM

+CPU_CORE

C440

0.1U_0402_10V6K

C407

1U_0603_10V6K

+1.2VP

C24

1U_0603_10V6K

C408

+

D

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

12

C431

+

470U_D_2.5VM

D

U39C

AF9

VCC

B11

VCC

B13

VCC

B15

VCC

B17

VCC

B19

VCC

B7

VCC

B9

VCC

C10

VCC

C12

VCC

C14

VCC

C16

VCC

C18

VCC

C20

VCC

C8

VCC

D11

VCC

D13

VCC

D15

VCC

D17

VCC

D19

VCC

D7

VCC

D9

VCC

E10

VCC

E12

VCC

E14

VCC

E16

VCC

E18

VCC

E20

VCC

E8

VCC

F11

VCC

F13

VCC

F15

VCC

F17

VCC

F19

VCC

F9

VCC

AE5

VID0

AE4

VID1

AE3

VID2

AE2

VID3

AE1

VID4

AF4

VCCVID

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

mPGA478

470U_D_2.5VM

12

C442

+

Northwood

POWER, GROUND AND NC

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID[0..4]47

29, 2002

十月

CPU_VID4

12

C514

+

330U_D_2.5VM

Compal Electronics, Inc.

Title

Pentium 4/Northwood Processor in mPGA478

Size Document Number Re v

B

LA1541

Date: Sheet of

星期二

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C437

C416

C499

10U_1206_6.3V6M

C452

C492

C468

C493

470U_D_2.5VM

12

470U_D_2.5VM

12

C395

+

C513

+

330U_D_2.5VM

12

E

D6

VSS

D8

VSS

E1

VSS

E11

VSS

E13

VSS

E15

VSS

E17

VSS

E19

VSS

E23

VSS

E26

VSS

E4

VSS

E7

VSS

E9

VSS

F10

VSS

F12

VSS

F14

VSS

F16

VSS

F18

VSS

F2

VSS

F22

VSS

F25

VSS

F5

VSS

F8

VSS

G21

VSS

G24

VSS

G3

VSS

G6

VSS

H1

VSS

H23

VSS

H26

VSS

H4

VSS

J2

VSS

J22

VSS

J25

VSS

J5

VSS

K21

VSS

K24

VSS

K3

VSS

K6

VSS

L1

VSS

L23

VSS

L26

VSS

L4

VSS

M2

VSS

M22

VSS

M25

VSS

M5

VSS

N21

VSS

N24

VSS

N3

VSS

N6

VSS

P2

VSS

P22

VSS

P25

VSS

P5

VSS

R1

VSS

R23

VSS

R26

VSS

R4

VSS

T21

VSS

T24

VSS

T3

VSS

T6

VSS

U2

VSS

RP1

1 8

2 7

3 6

4 5

1K_8P4R_1206_5%

1 2

R1 1K_0402_5%

CPU_VID[0..4]

E

+3VS

0.3

548,

5

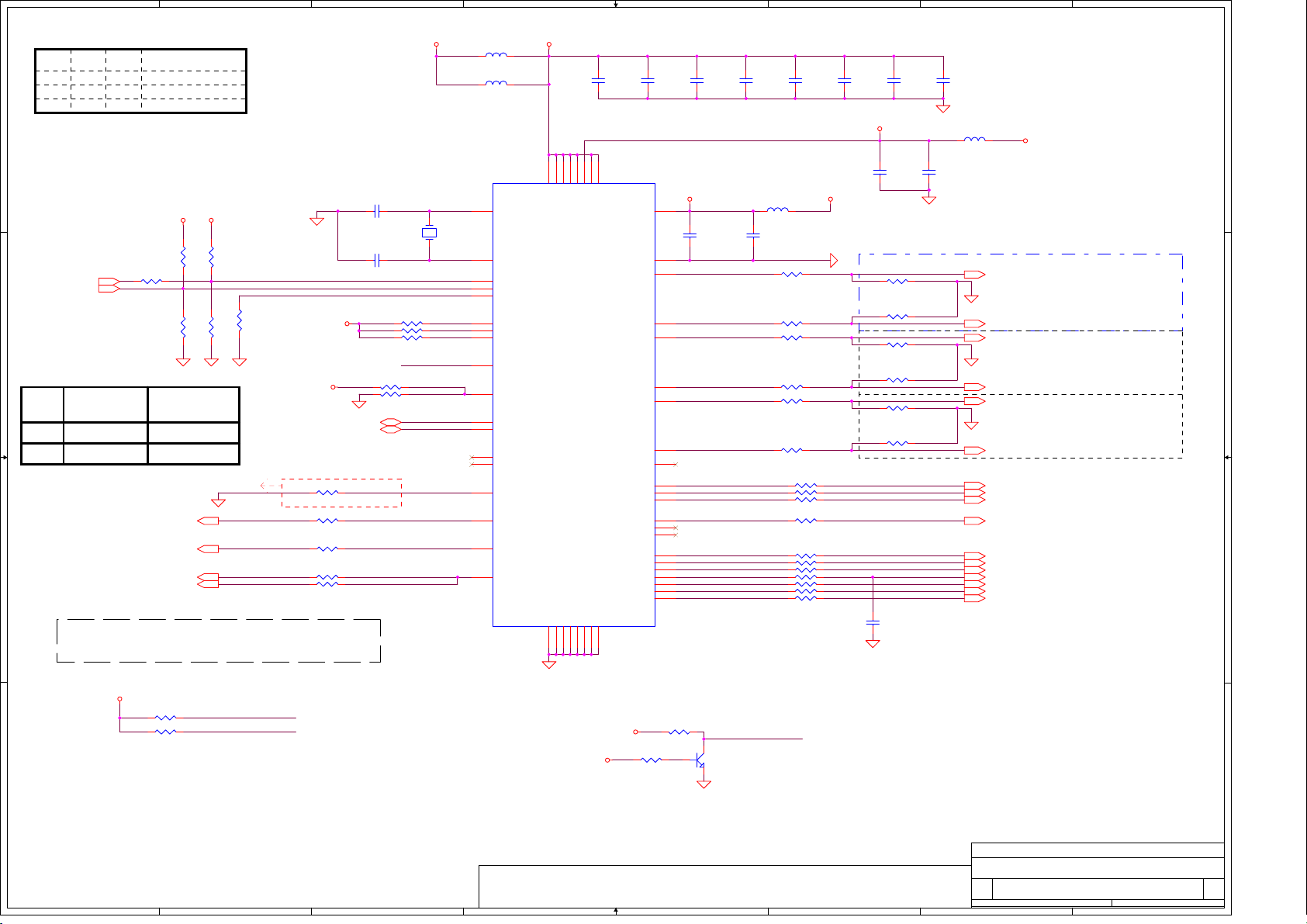

HD#[0..63]

HA#[3..31]

U23A

HD#0

D D

C C

B B

DSTBP0#4

DSTBP1#4

DSTBP2#4

DSTBP3#4

DSTBN0#4

DSTBN1#4

DSTBN2#4

DSTBN3#4

CPURST#4

CLK_GHT12

CLK_GHT#12

MCH_GTLREF8

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

BROOKDALE-GL/PE

T30

HD#0

R33

HD#1

R34

HD#2

N34

HD#3

R31

HD#4

L33

HD#5

L36

HD#6

P35

HD#7

J36

HD#8

K34

HD#9

K36

HD#10

M30

HD#11

M35

HD#12

L34

HD#13

K35

HD#14

H36

HD#15

G34

HD#16

G36

HD#17

J33

HD#18

D35

HD#19

F36

HD#20

F34

HD#21

E36

HD#22

H34

HD#23

F35

HD#24

D36

HD#25

H35

HD#26

E33

HD#27

E34

HD#28

B35

HD#29

G31

HD#30

C36

HD#31

D33

HD#32

D30

HD#33

D29

HD#34

E31

HD#35

D32

HD#36

C34

HD#37

B34

HD#38

D31

HD#39

G29

HD#40

C32

HD#41

B31

HD#42

B32

HD#43

B30

HD#44

B29

HD#45

E27

HD#46

C28

HD#47

B27

HD#48

D26

HD#49

D28

HD#50

B26

HD#51

G27

HD#52

H26

HD#53

B25

HD#54

C24

HD#55

B23

HD#56

B24

HD#57

E23

HD#58

C22

HD#59

G25

HD#60

B22

HD#61

D24

HD#62

G23

HD#63

L31

HDSTBP0#

J34

HDSTBP1#

E29

HDSTBP2#

E25

HDSTBP3#

N31

HDSTBN0#

G33

HDSTBN1#

C30

HDSTBN2#

D25

HDSTBN3#

D22

CPURST#

K30

HCLK

J31

HCLK#

D27

HD_VREF2

H24

HD_VREF1

H30

HD_VREF0

AD30

HA_VREF

P30

HCC_VREF

BROOKDALE-GL /PE_760P

HOST,HUB

HD#[0..63] 4

HA#[3..31] 4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB0#

HADSTB1#

HIT#

HITM#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HTRDY#

HLOCK#

DINV3

DINV2

DINV1

DINV0

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HI10

HI_STBS

HI_STBF

RS2#

RS1#

RS0#

HX_RCOMP

HY_RCOMP

HX_SWING

HY_SWING

HI_VREF

HI_RCOMP

HI_SWING

W31

AA33

AB30

V34

Y36

AC33

Y35

AA36

AC34

AB34

Y34

AB36

AC36

AC31

AF35

AD36

AD35

AE34

AD34

AE36

AF36

AE33

AF34

AG34

AG36

AE31

AH35

AG33

AG31

AB35

AF30

P36

M36

T36

T34

M34

U33

U31

N36

U36

V30

T35

C26

B33

C35

N33

V36

AA31

W33

AA34

W35

AF2

AE2

HI9

AF3

HI8

AE5

HI7

AE4

HI6

AF4

HI5

AD8

HI4

AC5

HI3

AC7

HI2

AB8

HI1

AA7

HI0

AD4

AC4

P34

U34

R36

B28

V35

H28

Y30

AD3

AC2

AD2

4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HUB_PD10

HUB_PD9

HUB_PD8

HUB_PD7

HUB_PD6

HUB_PD5

HUB_PD4

HUB_PD3

HUB_PD2

HUB_PD1

HUB_PD0

RS2#

RS1#

RS0#

HX_RCOMP

HY_RCOMP

R540

1 2

68_0603_1%

12

C570

0.1U_0402_10V6K

HREQ#0 4

HREQ#1 4

HREQ#2 4

HREQ#3 4

HREQ#4 4

HUB_PD[0..10]

RS#2 4

RS#1 4

RS#0 4

10 mil

10 mil

1 2

24.9_0603_1%

12

HADSTB0# 4

HADSTB1# 4

HIT# 4

HITM# 4

ADS# 4

BNR# 4

BPRI# 4

BREQ0# 4

DBSY# 4

DEFER# 4

DRDY# 4

HTRDY# 4

HLOCK# 4

DBI3# 4

DBI2# 4

DBI1# 4

DBI0# 4

HUB_PD[0..10] 19

HUB_PSTRB 19

HUB_PSTRB# 19

R418

R397

1 2

24.9_0603_1%

H_XY_SWING 8

MCH_HUB_VREF 8

MCH_HUB_VSWING 8

C578

0.1U_0402_10V6K

+1.5VS

3

DDR_SDQ[0..63]9

DDR_SDQS[0..7]9

DDR_SDM[0..7]9

DDR_SMA[0..12]9

DDR_CLK2#9

DDR_CLK29 DDR_CLK3# 10

DDR_CLK1#9

DDR_CLK19

DDR_CLK0#9

DDR_CLK09

DDR_SDQ0

AN4

DDR_SDQ1

AP2

DDR_SDQ2

AT3

DDR_SDQ3

AP5

DDR_SDQ4

AN2

DDR_SDQ5

AP3

DDR_SDQ6

AR4

DDR_SDQ7

AT4

DDR_SDQ8

AT5

DDR_SDQ9

AR6

DDR_SDQ10

AT9

DDR_SDQ11

AR10

DDR_SDQ12

AT6

DDR_SDQ13

AP6

DDR_SDQ14

AT8

DDR_SDQ15

AP8

DDR_SDQ16

AP10

DDR_SDQ17

AT11

DDR_SDQ18

AT13

DDR_SDQ19

AT14

DDR_SDQ20

AT10

DDR_SDQ21

AR12

DDR_SDQ22

AR14

DDR_SDQ23

AP14

DDR_SDQ24

AT15

DDR_SDQ25

AP16

DDR_SDQ26

AT18

DDR_SDQ27

AT19

DDR_SDQ28

AR16

DDR_SDQ29

AT16

DDR_SDQ30

AP18

DDR_SDQ31

AR20

DDR_SDQ32

AR22

DDR_SDQ33

AP22

DDR_SDQ34

AP24

DDR_SDQ35

AT26

DDR_SDQ36

AT22

DDR_SDQ37

AT23

DDR_SDQ38

AT25

DDR_SDQ39

AR26

DDR_SDQ40

AP26

DDR_SDQ41

AT28

DDR_SDQ42

AR30

DDR_SDQ43

AP30

DDR_SDQ44

AT27

DDR_SDQ45

AR28

DDR_SDQ46

AT30

DDR_SDQ47

AT31

DDR_SDQ48

AR32

DDR_SDQ49

AT32

DDR_SDQ50

AR36

DDR_SDQ51

AP35

DDR_SDQ52

AP32

DDR_SDQ53

AT33

DDR_SDQ54

AP34

DDR_SDQ55

AT35

DDR_SDQ56

AN36

DDR_SDQ57

AM36

DDR_SDQ58

AK36

DDR_SDQ59

AJ36

DDR_SDQ60

AP36

DDR_SDQ61

AM35

DDR_SDQ62

AK35

DDR_SDQ63

AK34

DDR_SDQ[0..63]

DDR_SDQS[0..7]

DDR_SDM[0..7]

DDR_SMA[0..12]

U23B

SDQ_0

SDQ_1

SDQ_2

SDQ_3

SDQ_4

SDQ_5

SDQ_6

SDQ_7

SDQ_8

SDQ_9

SDQ_10

SDQ_11

SDQ_12

SDQ_13

SDQ_14

SDQ_15

SDQ_16

SDQ_17

SDQ_18

SDQ_19

SDQ_20

SDQ_21

SDQ_22

SDQ_23

SDQ_24

SDQ_25

SDQ_26

SDQ_27

SDQ_28

SDQ_29

SDQ_30

SDQ_31

SDQ_32

SDQ_33

SDQ_34

SDQ_35

SDQ_36

SDQ_37

SDQ_38

SDQ_39

SDQ_40

SDQ_41

SDQ_42

SDQ_43

SDQ_44

SDQ_45

SDQ_46

SDQ_47

SDQ_48

SDQ_49

SDQ_50

SDQ_51

SDQ_52

SDQ_53

SDQ_54

SDQ_55

SDQ_56

SDQ_57

SDQ_58

SDQ_59

SDQ_60

SDQ_61

SDQ_62

SDQ_63

BROOKDALE-GL /PE_760P

AL21

SCMD_CLK0

AK22

AP11

AL33

AN21

AN9

AN11

AM34

SCMD_CLK1

SCMD_CLK0#

SCMD_CLK1#

AN34

AP21

AP9

AP33

SCMD_CLK2

SCMD_CLK3

SCMD_CLK4

SCMD_CLK5

SCMD_CLK2#

SCMD_CLK3#

SCMD_CLK4#

SCMD_CLK5#

BROOKDALE-GL/PE

DDR

SMAA12/BS0

SMAA11/DQS8

SMAA10/DQ31

SMAA9/SMA3

SMAA8/SMA4

SMAA7/SMA6

SMAA6/SDQ29

SMAA5/SMA8

SMAA4/SMA11

SMAA3/SMA7

SMAA2/SMA9

SMAA1/SDQ19

SMAA0/SMA12

SCKE3/SCK#5

SCKE2/RSVD

SCKE1/SDQ58

SCKE0/RSVD

SCS#0/SCKE2

SCS#1/RSVD

SCS#2/SCK#2

SCS#3/SCAS#

SRAS#/SCKE0

SCAS#/RSVD

SWE#/SDQ5

SRCVEN_OUT#

SRCVEN_IN#

SMY_RCOMP

SM_VREF

SMAB5

SMAB4

SMAB2

SMAB1

SBA1

SBA0

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

2

DDR_CLK3 10

DDR_CLK4 10

DDR_CLK4# 10

DDR_CLK5 10

DDR_CLK5# 10

AN15

AL15

AK26

AK16

AN17

AP17

AP19

AL17

AL19

AK20

AP23

AN25

AL25

AK18

AN19

AN23

AP25

AP27

AN27

AR2

AT7

AT12

AT17

AR24

AT29

AT34

AL36

AP4

AR8

AP12

AR18

AT24

AP28

AR34

AL34

AL13

AK14

AN13

AP13

AL29

AP31

AK30

AN31

AK28

AN29

AP29

AK24

AL23

AJ34

AM2

DDR_SMA12

DDR_SMA11

DDR_SMA10

DDR_SMA9

DDR_SMA8

DDR_SMA7

DDR_SMA6

DDR_SMA5

DDR_SMA4

DDR_SMA3

DDR_SMA2

DDR_SMA1

DDR_SMA0

DDR_SMAB5

DDR_SMAB4

DDR_SMAB2

DDR_SMAB1

DDR_SBS1

DDR_SBS0

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SDM0

DDR_SDM1

DDR_SDM2

DDR_SDM3

DDR_SDM4

DDR_SDM5

DDR_SDM6

DDR_SDM7

DDR_CKE3

DDR_CKE2

DDR_CKE1

DDR_CKE0

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

DDR_SRAS#

DDR_SCAS#

DDR_SWE#

RDCLKO

RDCLKI

SMY_RCOMP

SM_VREF

12

C751

0.1U_0402_10V6K

DDR_SMAB5 10

DDR_SMAB4 10

DDR_SMAB2 10

DDR_SMAB1 10

DDR_SBS1 9

DDR_SBS0 9

DDR_CKE3 10

DDR_CKE2 10

DDR_CKE1 9

DDR_CKE0 9

DDR_SCS#0 9

DDR_SCS#1 9

DDR_SCS#2 10

DDR_SCS#3 10

DDR_SRAS# 9

DDR_SCAS# 9

DDR_SWE# 9

12

R434 @0_0603_5%

1 2

R552

0_0603_5%

+SDREF

RDCLKI & RDCLKO 100mils

LENGTH 5mils WIDTH

12

R393

60.4_0603_1%

R394

60.4_0603_1%

12

12

C527

0.1U_0402_10V6K

1

+2.5V

Close to H28 Close to Y30

A A

5

Layout note :

1. HX_RCOM P, HY_RCOMP Trace width 10 mil.

2. Terminator Max 500 mil.

PROPRIETARY NOTE

4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Compal Electronics, Inc.

Title

Brookdale-GL/PE(1/3)

Size Document Number R ev

Custom

LA1541

Date: Sheet

星期二 十月

1

of

648, 29, 2002

0.3

A

U23C

R515

12

40.2_0603_1%

12

12

12

A

AGP_PIPE#

WBF#

RBF#

AGP_ST0

AGP_ST1

AGP_ST2

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

GFRAME#

GIRDY#

GTRDY#

GSTOP#

GDEVSEL#

GREQ#

GPAR

GGNT#

GC/BE#3

GC/BE#2

GC/BE#1

GC/BE#0

@0_0402_5%

12

12

R542

+1.5VS

AGP_PIPE#13

A A

WBF#13

RBF#13

ST013

ST113

ST213

AD_STB013

AD_STB0#13

AD_STB113

AD_STB1#13

GFRAME#13

GIRDY#13

GTRDY#13

GSTOP#13

GDEVSEL#13

GREQ#13

GPAR13

GGNT#13

GC/BE#313

GC/BE#213

GC/BE#113

GC/BE#013

B B

C C

D D

NB_AGPREF13

0_0603_5%

845PE R565 = 0_0603_5%

*

845GL R565 = 137_0603_1%

AGP_ST0

R528 6. 8K_0402_5%

AGP_ST1

R523 6. 8K_0402_5%

AGP_ST2

R531 6. 8K_0402_5%

AD_STB0#

R504 6. 8K_0402_5%

AD_STB1#

R505 6. 8K_0402_5%

Populated for 845PE

*

DREFCLK

DDCA_CLK

DDCA_DATA

INTCRT_B

INTCRT_B#

INTCRT_G

INTCRT_G#

INTCRT_R

INTCRT_R#

R492 0_0402_5%

R517 0_0402_5%

R514 0_0402_5%

R502 0_0402_5%

R508 0_0402_5%

R501 0_0402_5%

R491 0_0402_5%

R479 0_0402_5%

R485 0_0402_5%

R509

@0_0402_5%

R470

12

12

12

12

12

1 2

1 2

1 2

1 2

1 2

1 2

DDCA_CLK

DDCA_DATA

12

12

AD_STB0

AD_STB1

GDEVSEL#

GFRAME#

GGNT#

GIRDY#

GPAR

AGP_PIPE#

GREQ#

GSTOP#

GTRDY#

RBF#

WBF#

VGA_AGPREF13

H8

GPIPE#

C3

GSBA0/ADDIN0

C2

GSBA1/ADDIN1

D3

GSBA2/ADDIN2

D2

GSBA3/ADDIN3

E4

GSBA4/ADDIN4

E2

GSBA5/ADDIN5

F3

GSBA6/ADDIN6

F2

GSBA7/ADDIN7

G5

GWBF#

G7

GRBF#

BROOKDALE-GL/PE

C4

GST0

B4

GST1

B3

GST2

V8

GAD_STB0/DVOBCLK

U7

GAD_STB0#/DVOBCLK#

M8

GAD_STB1/DVOCCLK

L7

GAD_STB1#/DVOCCLK#

F4

GSBSTB

E5

GSBSTB#

M4

G_FRAME#/MDVI DATA

N7

G_IRDY#/MI2C CLK

N5

G_TRDY#/MDVI CLK

P2

G_STOP#/MDDC DATA

N2

G_DEVSEL#/MI2C DATA

D5

G_REQ#

P4

G_PAR/ADD_DETECT

B5

G_GNT#

H2

GCBE3#/DVOCD5

M2

GCBE2#

N4

GCBE1#/DVOBBLANK#

R4

GCBE0#/DVOBD7

L2

AGP RCOMP/DVOBCRCOMP

W2

AGP_VREF

B7

HSYNC

C6

VSYNC

D7

DDCA_CLK

C7

DDCA_DATA

B16

REFSET

BROOKDALE-GL /PE_760P

C763

0.1U_0402_10V6K

R503 6.8 K_0402_5%

R490 6.8 K_0402_5%

R527 6.8 K_0402_5%

R520 6.8 K_0402_5%

R524 6.8 K_0402_5%

R510 6.8 K_0402_5%

R519 6.8 K_0402_5%

R506 6.8 K_0402_5%

R513 6.8 K_0402_5%

R541 6.8 K_0402_5%

R511 6.8 K_0402_5%

R512 6.8 K_0402_5%

R521 6.8 K_0402_5%

AGP/DVO

ANALOG DISPLAY

12

12

12

12

12

12

12

12

12

12

12

12

12

+1.5VS

12

R539

1K_0603_1%

12

R548

1K_0603_1%

B

GAD[0..31]13

GAD0/DVOBHSYNC

GAD1/DVOBVSYNC

GAD2/DVOBD1

GAD3/DVOBD0

GAD4/DVOBD3

GAD5/DVOBD2

GAD6/DVOBD5

GAD7/DVOBD4

GAD8/DVOBD6

GAD9/DVOBD9

GAD10/DVOBD8

GAD11/DVOBD11

GAD12/DVOBD10

GAD13/DVOBCCLKINT#

GAD14/DVOBFLDSTL

GAD15/MDDC CLK

GAD16/DVOCVSYNC

GAD17/DVOCHSYNC

GAD18/DVOCBLANK#

GAD19/DVOCD0

GAD20/DVOCD1

GAD21/DVOCD2

GAD22/DVOCD3

GAD23/DVOCD4

GAD24/DVOCD7

GAD25/DVOCD6

GAD26/DVOCD9

GAD27/DVOCD8

GAD28/DVOCD11

GAD29/DVOCD10

GAD30/DVOBCINTR#

GAD31/DVOCFLDSTL

GCLKIN

RSTIN#

DREFCLK

PWROK

PSBSEL

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

+1.5VS

RSTIN#

PLACE COLSE TO MCH

C781

0.1U_0402_10V6K

B

GAD[0..31]

GAD0

V4

GAD1

V2

GAD2

W4

GAD3

W5

GAD4

U5

GAD5

U4

GAD6

U2

GAD7

V3

GAD8

T2

GAD9

T3

GAD10

T4

GAD11

R2

GAD12

R5

GAD13

R7

GAD14

T8

GAD15

P3

GAD16

P8

GAD17

K4

GAD18

K2

GAD19

J2

GAD20

M3

GAD21

L5

GAD22

L4

GAD23

H4

GAD24

G2

GAD25

K3

GAD26

J4

GAD27

J5

GAD28

J7

GAD29

H3

GAD30

K8

GAD31

G4

CLK_AGP_MCH

AE7

RSTIN#

AJ31

DREFCLK

D14

E7

Y3

1 2

R477 8.2K_0402_5%

INTCRT_B

G15

INTCRT_B#

H16

INTCRT_G

E15

INTCRT_G#

F16

INTCRT_R

C15

INTCRT_R#

D16

12

R483

8.2K_0402_5%

R398 0_0402_5%

C562

1 2

15P_0402_50V8J

L50

KC FBM-L11-201209-221LMAT_0805

1 2

+1.5VS

C655

0.1U_0402_10V6K

Place close to pin AE7

CLK_AGP_MCH

10_0402_5%

10P_0402_50V8K

CLK_AGP_MCH 12

SYS_PWROK 20,40

H_BSEL0 4,12

PSBSEL FSB FREQUENCY

0

1

*

12

VCCA_FSB

12

+1.5VS

C755

0.1U_0402_10V6K

400 MHZ

533 MHZ

PCIRST# 13,19,22,23,24,25,26,28,30,35,36

C647

22U_1206_16V4Z_V1

12

NEAR AA1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

PROPRIETARY NOTE

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

R484

C679

+1.5VS

12

C

12

1

2

+CPU_CORE

R530

1.5K_0402_5%

C644

0.1U_0402_10V6K

12

C754

0.1U_0402_10V6K

NEAR AE1

C

D

+1.5VS

+2.5V

U23D

Y19

VCC1

AA19

VCC2

W20

U21

W21

AA21

A9

B9

C9

D9

E9

B10

C10

D10

F10

H10

A11

B11

C11

D11

E11

G11

J11

B12

C12

D12

F12

H12

G13

J13

H14

J15

AA17

W17

U17

W18

V19

U19

K10

K12

K14

K16

W19

B18

C18

D18

H18

B19

C19

D19

E19

G19

J19

B20

C20

D20

F20

H20

F18

K18

K20

K22

K26

M28

T28

Y28

AD28

AU37

AU36

AT37

AU2

AU1

AJ35

AH34

AB2

Y2

A37

AB3

AA2

AA3

AA4

AA5

Y4

Y8

W7

AT1

12

VCCAGP0A3VCCAGP1A7VCCAGP2C1VCCAGP3D4VCCAGP4D6VCCAGP5G1VCCAGP6K6VCCAGP7L1VCCAGP8L9VCCAGP9

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VTTFSB0

VTTFSB1

VTTFSB2

VTTFSB3

VTTFSB4

VTTFSB5

VTTFSB6

VTTFSB7

VTTFSB8

VTTFSB9

VTTFSB10

VTTFSB11

VTTFSB12

VTTFSB13

VTTFSB14

VTTFSB15

VTTFSB16

VTTFSB17

VTTFSB18

VTTFSB19

VTTFSB20

VTTFSB21

VTTFSB22

VTTFSB23

TESTIN#

MEM_SEL

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

NC

NC

NC

NC

NC

NC

NC

NC

BROOKDALE-GL /PE_760P

BROOKDALE-GL/PE

P6

VCCAGP10R1VCCAGP11R9VCCAGP12W9VCCAGP13

POWER

V6

P10

VCCAGP14

D

V10

AB10

VCCAGP15

VCCAGP16

VCCA_SM0

VCCA_SM1

VTTDECAP0

VTTDECAP1

VTTDECAP2

VTTDECAP3

VTTDECAP4

VCCA_DPLL

VCCA_DAC0

VCCA_DAC1

SMX_RCOMP

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCQSM0

VCCQSM1

VCCQSM2

VCCA_FSB

VCCA_HI

VCCHI0

VCCHI1

VCCHI2

VCCHI3

VCCGPIO

AH8

AK8

AG9

AJ9

AL9

AM22

AJ23

AL37

AU9

AK10

AJ11

AL11

AU25

AM26

AU13

AM14

AJ27

AJ1

AL1

AJ15

AP15

AU29

AH2

AJ2

AK2

AL2

AM30

AH3

AJ3

AK3

AL3

AH4

AJ4

AK4

AL4

AU17

AJ5

AL5

AU5

AM18

AJ19

AK32

AU33

AH6

AK6

AP20

AG7

AJ7

AL7

AP7

AH10

AH12

AH14

AH18

AH22

AH26

AG1

AG2

AT20

AT21

AU21

A31

AC37

R37

L37

G37

A17

AD10

AD6

AC9

AC1

AE3

A13

B6

B14

A15

AF10

A2

NC

A36

NC

B37

NC

B1

NC

12

12

C528

+

150U_D2_6.3VM

12

C614

0.1U_0402_10V6K

VCCA_FSB

+1.5VS

VCCA_DPLL

VCCA_DAC

R467

60.4_0603_1%

12

R468

60.4_0603_1%

Compal Electronics, Inc.

Title

Size Document Number R ev

Custom

Date: Sheet

C768

+

150U_D2_6.3VM

12

L49

KC FBM-L11-201209-221LMAT_0805

12

C620

4.7U_0805_10V4Z

12

R438

1_0402_5%

0.1U_0402_10V6K

12

C753

0.1U_0402_10V6K

12

C548

0.1U_0402_10V6K

12

12

C696

0.1U_0402_10V6K

VCCA_DPLL

12

R486

0_0402_5%

BROOKDALE-GL/PE (2/3)

LA1541

星期二 十月

E

12

C767

+

150U_D2_6.3VM

+1.5VS

12

L52

KC FBM-L11-201209-221LMAT_0805

12

C795

+

150U_D2_6.3VM

0.1U_0402_10V6K

12

12

C547

C546

0.1U_0402_10V6K

12

+2.5V

C730

0.1U_0402_10V6K

VCCA_DAC

E

12

12

C545

0.1U_0402_10V6K

+3VS

R478

0_0402_5%

748, 29, 2002

12

C563

0.3

of

5

U23E

AM10

VSS0

AR23

D D

C C

B B

A A

VSS1

AU23

VSS2

F24

VSS3

AM24

VSS4

A25

VSS5

C16

VSS6

N37

VSS7

U18

VSS8

V18

VSS9

Y18

VSS10

AA18

VSS11

AL31

VSS12

AR31

VSS13

AU31

VSS14

F32

VSS15

H32

VSS16

K32

VSS17

M32

VSS18

P32

VSS19

T32

VSS20

V32

VSS21

Y32

VSS22

AB32

VSS23

AD32

VSS24

AF32

VSS25

AH32

VSS26

AM4

VSS27

A5

VSS28

C5

VSS29

AG5

VSS30

AN5

VSS31

AR5

VSS32

AR19

VSS33

AM32

VSS34

A33

VSS35

C33

VSS36

AJ33

VSS37

AN33

VSS38

AR33

VSS39

F6

VSS40

H6

VSS41

M6

VSS42

T6

VSS43

Y6

VSS44

AB6

VSS45

AF6

VSS46

AM6

VSS47

U20

VSS48

V20

VSS49

Y20

VSS50

AA20

VSS51

AM20

VSS52

A21

VSS53

B21

VSS54

C21

VSS55

D21

VSS56

E21

VSS57

G21

VSS58

J21

VSS59

D34

VSS60

W34

VSS61

A35

VSS62

E35

VSS63

G35

VSS64

J35

VSS65

L35

VSS66

AN7

VSS67

AR7

VSS68

AU7

VSS69

B8

VSS70

C8

VSS71

D8

VSS72

F8

VSS73

V21

VSS74

Y21

VSS75

AJ21

VSS76

AR21

VSS77

F22

VSS78

H22

VSS79

M10

VSS80

T10

VSS81

Y10

VSS82

AH16

VSS83

AH20

VSS84

AH24

VSS85

BROOKDALE-GL /PE_760P

AR9

AR17

AJ17

Y17

AG4

AB4

AU3

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

BROOKDALE-GL/PE

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

N35

R35

U35

AL35

AA35

AE35

AC35

AN35

AR35

AG35

VSS117

VSS95

AR3

VSS118

VSS

VSS96

AU35

AN3

AM3

AG3

AC3

C31

AH30

V17

J17

G17

E17

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS97

VSS98

VSS99

VSS100

VSS101G9VSS102J9VSS103N9VSS104U9VSS105

VSS106

VSS107

VSS108

VSS109

B36

AF8

W36

AM8

J23

A23

C23

D23

AA9

AE9

4

R538 226_0603_1%

+1.5VS

C17

VSS129

B17

VSS130

AM16

VSS131

W3

VSS132

U3

VSS133

R3

VSS134

D17

VSS135

N3

VSS136

L3

VSS137

J3

VSS138

G3

VSS139

E3

VSS140

AT2

VSS141

F30

VSS142

AR29

VSS143

AJ29

VSS144

AG29

VSS145

AE29

VSS146

AC29

VSS147

AA29

VSS148

W29

VSS149

R29

VSS150

U29

VSS151

N29

VSS152

L29

VSS153

J29

VSS154

C29

VSS155

A29

VSS156

AU15

VSS157

AR15

VSS158

D15

VSS159

B2

VSS160

AR1

VSS161

AN1

VSS162

AE1

VSS163

AA1

VSS164

U1

VSS165

N1

VSS166

J1

VSS167

E1

VSS168

AM28

VSS169

F28

VSS170

AU27

VSS171

AR27

VSS172

AL27

VSS173

F14

VSS174

AR13

VSS175

AJ13

VSS176

J27

VSS177

C27

VSS178

A27

VSS179

E13

VSS180

D13

VSS181

C13

VSS182

B13

VSS183

AM12

VSS184

AK12

VSS185

F26

VSS186

AR25

VSS187

AJ25

VSS188

J25

VSS189

AU11

VSS190

AR11

VSS191

AR37

VSS192

AN37

VSS193

C25

VSS194

AJ37

VSS195

AG37

VSS196

AE37

VSS197

AA37

VSS198

U37

VSS199

AH28

VSS200

AF28

VSS201

AB28

VSS202

V28

VSS203

P28

VSS204

K28

VSS205

K24

VSS206

J37

VSS207

E37

VSS208

C37

VSS209

AT36

VSS210

AH36

VSS211

VSSA_DAC0

VSSA_DAC1

VSS110

B15

C14

1 2

+CPU_CORE

10U_1206_6.3V6M

12

0.1U_0402_10V6K

+2.5V

12

C634

0.1U_0402_10V6K

12

C631

0.1U_0402_10V6K

+1.5VS

12

C615

0.1U_0402_10V6K

12

C677

0.1U_0402_10V6K

C617

C576

0.1U_0402_10V6K

10U_1206_6.3V6M

C629

0.1U_0402_10V6K

12

C575

0.1U_0402_10V6K

12

C664

0.1U_0402_10V6K

12

C662

0.1U_0402_10V6K

12

C625

12

C680

0.1U_0402_10V6K

3

0.01U_0402_25V4Z

C769

NEAR MCH

FSB DECOUPLING

12

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

C701

0.1U_0402_10V6K

12

C688

0.1U_0402_10V6K

12

C616

0.1U_0402_10V6K

12

C690

R553 100_0603_1%

1 2

12

0.1U_0402_10V6K

C618

0.1U_0402_10V6K

C574

12

C775

0.1U_0402_10V6K

12

C608

0.1U_0402_10V6K

12

C619

PLACE NOTE:

CAP PLACE

NEAR MCH

AD2 & AD3

12

12

SYSTEM MEMORY DECOUPLING

0.1U_0402_10V6K

C612

0.1U_0402_10V6K

C700

12

C588

12

C708

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

GMCH DECOUPLING

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

C626

0.1U_0402_10V6K

C728

0.1U_0402_10V6K

12

C643

12

C729

0.1U_0402_10V6K

C635

C633

0.1U_0402_10V6K

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

12

R551

100_0603_1%

12

C589

C601

0.1U_0402_10V6K

C731

0.1U_0402_10V6K

C642

0.1U_0402_10V6K

C756

0.1U_0402_10V6K

2

12

C780

0.1U_0402_10V6K

12

C577

0.1U_0402_10V6K

0.1U_0402_10V6K

12

C624

12

C734

0.1U_0402_10V6K

12

C663

0.1U_0402_10V6K

12

C757

12

C657

0.1U_0402_10V6K

12

C699

12

C694

12

C758

0.1U_0402_10V6K

12

C774

0.01U_0402_25V4Z

NEAR MCH

Within 250milWithin 250mil

+CPU_CORE

+CPU_CORE

12

C692

0.1U_0402_10V6K

12

C670

0.1U_0402_10V6K

12

C703

0.1U_0402_10V6K

12

C759

MCH_HUB_VSWING 6

10 mil Trace,

7mil Space

MCH_HUB_VREF 6

R423 49.9_0603_1%

0.1U_0402_10V6K

12

C583

0.1U_0402_10V6K

12

C641

0.1U_0402_10V6K

12

C704

0.1U_0402_10V6K

12

C705

1 2

100_0603_1%

NEAR MCH

R430

12

301_0603_1%

R431

150_0603_1%

12

C721

0.1U_0402_10V6K

12

C707

0.1U_0402_10V6K

12

0.1U_0402_10V6K

12

0.1U_0402_10V6K

10 mil Trace,

7mil Space

12

R433

1 2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

C693

C740

1

1

C569

0.1U_0402_10V6K

2

10 mil Trace,

7mil Space

12

C590

0.01U_0402_25V4Z

12

C568

0.1U_0402_10V6K

12

C559

0.1U_0402_10V6K

12

C658

MCH_GTLREF 6

H_XY_SWING 6

0.1U_0402_10V6K

12

C587

12

C539

C609

12

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

PROPRIETARY NOTE

5

4

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

BROOKDALE-GL/PE (3/3)

Size Document Number R ev

Custom

LA1541

Date: Sheet

星期二 十月

1

of

848, 29, 2002

0.3

A

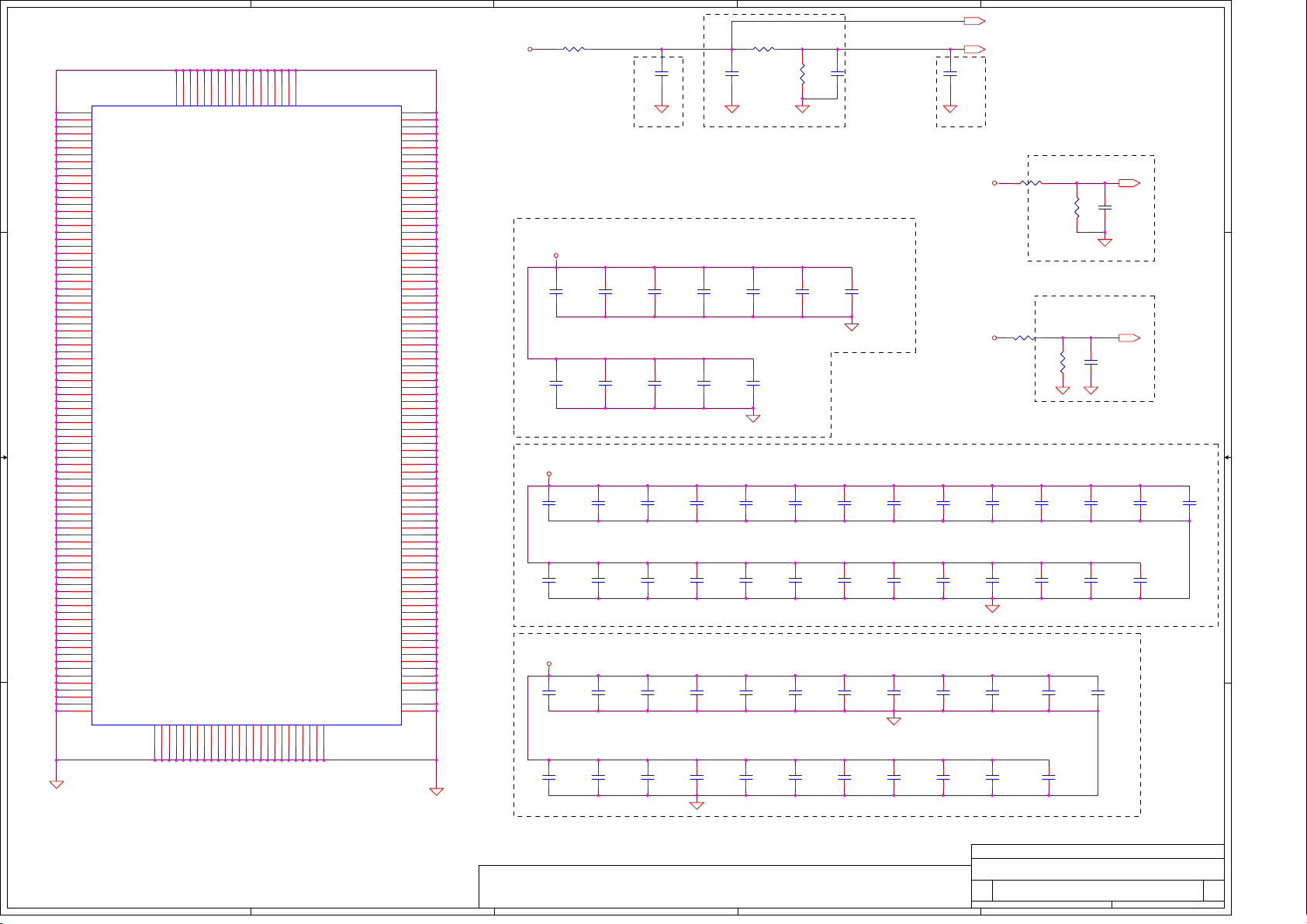

DDR_SDQ0

DDR_SDQ5

DDR_SDQ4

DDR_SDQ1

DDR_SDQS0

1 1

2 2

3 3

4 4

A

DDR_SDM0

DDR_SDQ2

DDR_SDQ6

DDR_SDQ7

DDR_SDQ3

DDR_SDQ8

DDR_SDQ13

DDR_SDQ12

DDR_SDQ9

DDR_SDQS1 DDR_DQS1

DDR_SDM1 DDR_DM1

DDR_SDQ14 DDR_DQ14

DDR_SDQ15 DDR_DQ15

DDR_SDQ10

DDR_SDQ11

DDR_SDQ20

DDR_SDQ16

DDR_SDQ21 DDR_DQ21

DDR_SDQS2 DDR_DQS2

DDR_SDM2 DDR_DM2

DDR_SDQ18 DDR_DQ18

DDR_SDQ23

DDR_SDQ24 DDR_DQ24

DDR_SDQ25

DDR_SDQ29 DDR_DQ29

DDR_SDQS3

DDR_SDM3

DDR_SDQ26 DDR_DQ26

DDR_SDQ30 DDR_DQ30

DDR_SDQ27

DDR_SDQ31

DDR_SDQ[0..63]6

DDR_SDQS[0..7]6

DDR_SMA[0..12]6

DDR_SDM[0..7]6

B

RP118 10_0402_4P2R_5%

1 4

2 3

RP117 10_0402_4P2R_5%

1 4

2 3

RP116 10_0402_4P2R_5%

1 4

2 3

RP115 10_0402_4P2R_5%

1 4

2 3

RP114 10_0402_4P2R_5%

1 4

2 3

RP113 10_0402_4P2R_5%

1 4

2 3

RP112 10_0402_4P2R_5%

1 4

2 3

RP109 10_0402_4P2R_5%

1 4

2 3

RP108 10_0402_4P2R_5%

1 4

2 3

RP107 10_0402_4P2R_5%

1 4

2 3

RP106 10_0402_4P2R_5%

1 4

2 3

RP105 10_0402_4P2R_5%

1 4

2 3

RP103 10_0402_4P2R_5%

1 4

2 3

RP102 10_0402_4P2R_5%

1 4

2 3

RP101 10_0402_4P2R_5%

1 4

2 3

RP100 10_0402_4P2R_5%

1 4

2 3

RP99 10_0402_4P2R_5%

1 4

2 3

RP98 10_0402_4P2R_5%

1 4

2 3

RP96 10_0402_4P2R_5%

1 4

2 3

RP95 10_0402_4P2R_5%

1 4

2 3

DDR_SDQ[0..63]

DDR_SDQS[0..7]

DDR_SMA[0..12]

DDR_SDM[0..7]

B

DDR_DQ0

DDR_DQ5

DDR_DQ4

DDR_DQ1

DDR_DQS0

DDR_DM0

DDR_DQ2

DDR_DQ6

DDR_DQ7

DDR_DQ3

DDR_DQ8

DDR_DQ13

DDR_DQ12

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ20

DDR_DQ16

DDR_DQ17DDR_SDQ17

DDR_DQ23

DDR_DQ19DDR_SDQ19

DDR_DQ22DDR_SDQ22

DDR_DQ25

DDR_DQ28DDR_SDQ28

DDR_DQS3

DDR_DM3

DDR_DQ27

DDR_DQ31

C

DDR_SDQ33 DDR_DQ33

DDR_SDQ32

DDR_SDQ36 DDR_DQ36

DDR_SDQ37

DDR_SDQS4

DDR_SDM4 DDR_DM4

DDR_SDQ34

DDR_SDQ38

DDR_SDQ39

DDR_SDQ35

DDR_SDQ40

DDR_SDQ44

DDR_SDQ45

DDR_SDQ41

DDR_SDM5

DDR_SDQS5 DDR_DQS5

DDR_SDQ43

DDR_SDQ42 DDR_DQ42

DDR_SDQ47

DDR_SDQ52

DDR_SDQ49

DDR_SDQ48

DDR_SDQ53

DDR_SDM6

DDR_SDQS6

DDR_SDQ54

DDR_SDQ55

DDR_SDQ51 DDR_DQ51

DDR_SDQ60

DDR_SDQ56 DDR_DQ56

DDR_SDQ61 DDR_DQ61

DDR_SDQ57

DDR_SDM7

DDR_SDQS7

DDR_SDQ63

DDR_SDQ62 DDR_DQ62

DDR_SDQ58 DDR_DQ58

DDR_SDQ59

RP94 10_0402_4P2R_5%

1 4

2 3

RP93 10_0402_4P2R_5%

1 4

2 3

RP91 10_0402_4P2R_5%

1 4

2 3

RP90 10_0402_4P2R_5%

1 4

2 3

RP89 10_0402_4P2R_5%

1 4

2 3

RP86 10_0402_4P2R_5%

1 4

2 3

RP83 10_0402_4P2R_5%

1 4

2 3

RP82 10_0402_4P2R_5%

1 4

2 3

RP80 10_0402_4P2R_5%

1 4

2 3

RP77 10_0402_4P2R_5%

1 4

2 3

RP76 10_0402_4P2R_5%

1 4

2 3

RP74 10_0402_4P2R_5%

1 4

2 3

RP73 10_0402_4P2R_5%

1 4

2 3

RP72 10_0402_4P2R_5%

1 4

2 3

RP71 10_0402_4P2R_5%

1 4

2 3

RP70 10_0402_4P2R_5%

1 4

2 3

RP69 10_0402_4P2R_5%

1 4

2 3

RP68 10_0402_4P2R_5%

1 4

2 3

RP67 10_0402_4P2R_5%

1 4

2 3

RP66 10_0402_4P2R_5%

1 4

2 3

C

DDR_DQ32

DDR_DQ37

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ39

DDR_DQ35

DDR_DQ40

DDR_DQ44

DDR_DQ45

DDR_DQ41

DDR_DM5

DDR_DQ43

DDR_DQ46DDR_SDQ46

DDR_DQ47

DDR_DQ52

DDR_DQ49

DDR_DQ48

DDR_DQ53

DDR_DM6

DDR_DQS6

DDR_DQ54

DDR_DQ55

DDR_DQ50DDR_SDQ50

DDR_DQ60

DDR_DQ57

DDR_DM7

DDR_DQS7

DDR_DQ63

DDR_DQ59

PROPRIETARY NOTE

D

DDR_DQ0

DDR_DQ5

DDR_DQS0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ13

DDR_DQS1

DDR_DQ10

DDR_DQ11

DDR_CLK16

DDR_CLK1#6

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ18

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQS3

DDR_DQ26

DDR_DQ30

DDR_CLK06

DDR_CLK0#6

DDR_CKE16 DDR_CKE0 6

Layout note

Place these resistors

close to DIMM0,

all trace length<500 mil

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

DDR_CKE1 DDR_CKE0

DDR_F_SMA12

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA5

DDR_F_SMA3

DDR_F_SMA1

DDR_F_SMA10

DDR_F_SBS0

DDR_F_SWE#

DDR_SCS#0 DDR_SCS#1

DDR_DQ32

DDR_DQS4

DDR_DQ34

DDR_DQ38

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ43

DDR_DQ46

DDR_DQ52

DDR_DQ49

DDR_DQS6

DDR_DQ51

DDR_DQ50

DDR_DQ61

DDR_DQ57

DDR_DQS7

DDR_DQ63

DDR_DQ62

SMB_DATA10,12,19

SMB_CLK10,12,19

+3VS

+2.5V

E

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

E

JP22

VREF

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

CK0#

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

CK2#

VDD

CKE1

DU/A13

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

WE#

S0#

DU

VSS

DQ32

DQ33

VDD

DQS4

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

VSS

DQ58

DQ59

VDD

SDA

SCL

VDD_SPD

VDD_ID

QTC_C106A-092SFP11-01

Bottom-1

DIMM0

VREF

DM0

DQ12

DQ13

DM1

DQ14

DQ15

DQ20

DQ21

DM2

DQ22

DQ23

DQ28

DQ29

DM3

DQ30

DQ31

DM8

DU/RESET#

CKE0

DU/BA2

RAS#

CAS#

DQ36

DQ37

DM4

DQ38

DQ39

DQ44

DQ45

DM5

DQ46

DQ47

CK1#

DQ52

DQ53

DM6

DQ54

DQ55

DQ60

DQ61

DM7

DQ62

DQ63

VSS

DQ4

DQ5

VDD

DQ6

VSS

DQ7

VDD

VSS

VDD

VDD

VSS

VSS

VDD

VSS

VDD

VSS

VDD

CB4

CB5

VSS

CB6

VDD

CB7

VSS

VSS

VDD

VDD

VSS

VDD

BA1

VSS

VDD

VSS

VDD

VSS

VDD

CK1

VSS

VDD

VSS

VDD

VSS

VDD

SA0

SA1

SA2

F

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

F

20mil

DDR_DQ4

DDR_DQ1

DDR_DM0

DDR_DQ7

DDR_DQ3

DDR_DQ12

DDR_DQ9

DDR_DM1

DDR_DQ14

DDR_DQ15

DDR_DQ17

DDR_DQ21

DDR_DM2

DDR_DQ19

DDR_DQ22

DDR_DQ29

DDR_DQ28

DDR_DM3

DDR_DQ27

DDR_DQ31

DDR_F_SMA11

DDR_F_SMA8

DDR_F_SMA6

DDR_F_SMA4

DDR_F_SMA2

DDR_F_SMA0

DDR_F_SBS1

DDR_F_SRAS#

DDR_F_SCAS#

DDR_DQ36DDR_DQ33

DDR_DQ37

DDR_DM4

DDR_DQ39

DDR_DQ35

DDR_DQ45

DDR_DQ41

DDR_DM5

DDR_DQ42

DDR_DQ47

DDR_DQ48

DDR_DQ53

DDR_DM6

DDR_DQ54

DDR_DQ55

DDR_DQ60

DDR_DQ56

DDR_DM7

DDR_DQ58

DDR_DQ59

DDR_SWE#6

DDR_SCAS#6

DDR_SRAS#6

DDR_SBS06

G

12

C329

0.1U_0402_16V4Z

+SDREF

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

RP121 10_0402_4P2R_5%

DDR_SMA9

1 4

DDR_SMA7

2 3

RP122 10_0402_4P2R_5%

DDR_SMA11

1 4

DDR_SMA12

2 3

RP123 10_0402_4P2R_5%

DDR_SMA8

1 4

DDR_SMA5

2 3

RP124 10_0402_4P2R_5%

DDR_SMA6

1 4

DDR_SMA4

2 3

RP125 10_0402_4P2R_5%

DDR_SMA3

1 4

DDR_SMA2

2 3

RP126 10_0402_4P2R_5%

DDR_SMA0

1 4

DDR_SMA1

2 3

DDR_SMA10 DDR_F_SMA10

R731 10_0402_5%

DDR_F_SMA[0..12]10

H

DDR_DQ[0..63] 10

DDR_DQS[0..7] 10

DDR_DM[0..7] 10

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA11

DDR_F_SMA12

DDR_F_SMA8

DDR_F_SMA5

DDR_F_SMA6

DDR_F_SMA4

DDR_F_SMA3

DDR_F_SMA2

DDR_F_SMA0

DDR_F_SMA1

DDR_F_SMA[0..12]

Layout note

Place these resistor

DDR_SCS#1 6DDR_SCS#06

DDR_CLK2# 6

DDR_CLK2 6

Title

Size Document Number R ev

B

LA1541

Date: Sheet

星期二 十月

G

close by DIMM0,

all trace length

Max=1.4"

DDR_CKE1

DDR_CKE0

DDR_SCS#0

DDR_SCS#1

DDR_F_SBS1

12

R732 10_0402_5%

R740 10_0402_5%

R733 10_0402_5%

R734 10_0402_5%

R735 10_0402_5%

12

12

12

12

DDR_F_SBS0

DDR_F_SWE#

DDR_F_SCAS#

DDR_F_SRAS#

Compal Electronics, Inc.

DDR-SODIMM SLOT0

+1.25VS

RP92 56_0402_4P2R_5%

1 4

2 3

RP87 56_0402_4P2R_5%

1 4

2 3

DDR_F_SBS1 10DDR_SBS16

DDR_F_SBS0 10

DDR_F_SWE# 10

DDR_F_SCAS# 10

DDR_F_SRAS# 10

of

948, 29, 2002

H

0.3

A

+1.25VS +1.25VS

RP57 56_0402_4P2R_5%

DDR_DQ0

1 4

DDR_DQ4

2 3

RP56 56_0402_4P2R_5%

DDR_DQ5

1 4

DDR_DQ1

2 3

DDR_DQ6

DDR_DQS0

DDR_DQ2

DDR_DQ3

DDR_DQ8

DDR_DQ7

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ13

DDR_DQ10

DDR_DQ14

DDR_DQ11

DDR_DQ15

DDR_DQ16

DDR_DQ20

DDR_DQ21

DDR_DQ17

DDR_DQ18

DDR_DQS2

DDR_DQ22

DDR_DQ19

DDR_DQ24

DDR_DQ23

DDR_DQ25

DDR_DQ28

DDR_DQS3

DDR_DQ29

RP54 56_0402_4P2R_5%

1 4

2 3

RP53 56_0402_4P2R_5%

1 4

2 3

RP55 56_0402_4P2R_5%

1 4

2 3

RP52 56_0402_4P2R_5%

1 4

2 3

RP50 56_0402_4P2R_5%

1 4

2 3

RP49 56_0402_4P2R_5%

1 4

2 3

RP48 56_0402_4P2R_5%

1 4

2 3

RP47 56_0402_4P2R_5%

1 4

2 3

RP46 56_0402_4P2R_5%

1 4

2 3

RP45 56_0402_4P2R_5%

1 4

2 3

RP44 56_0402_4P2R_5%

1 4