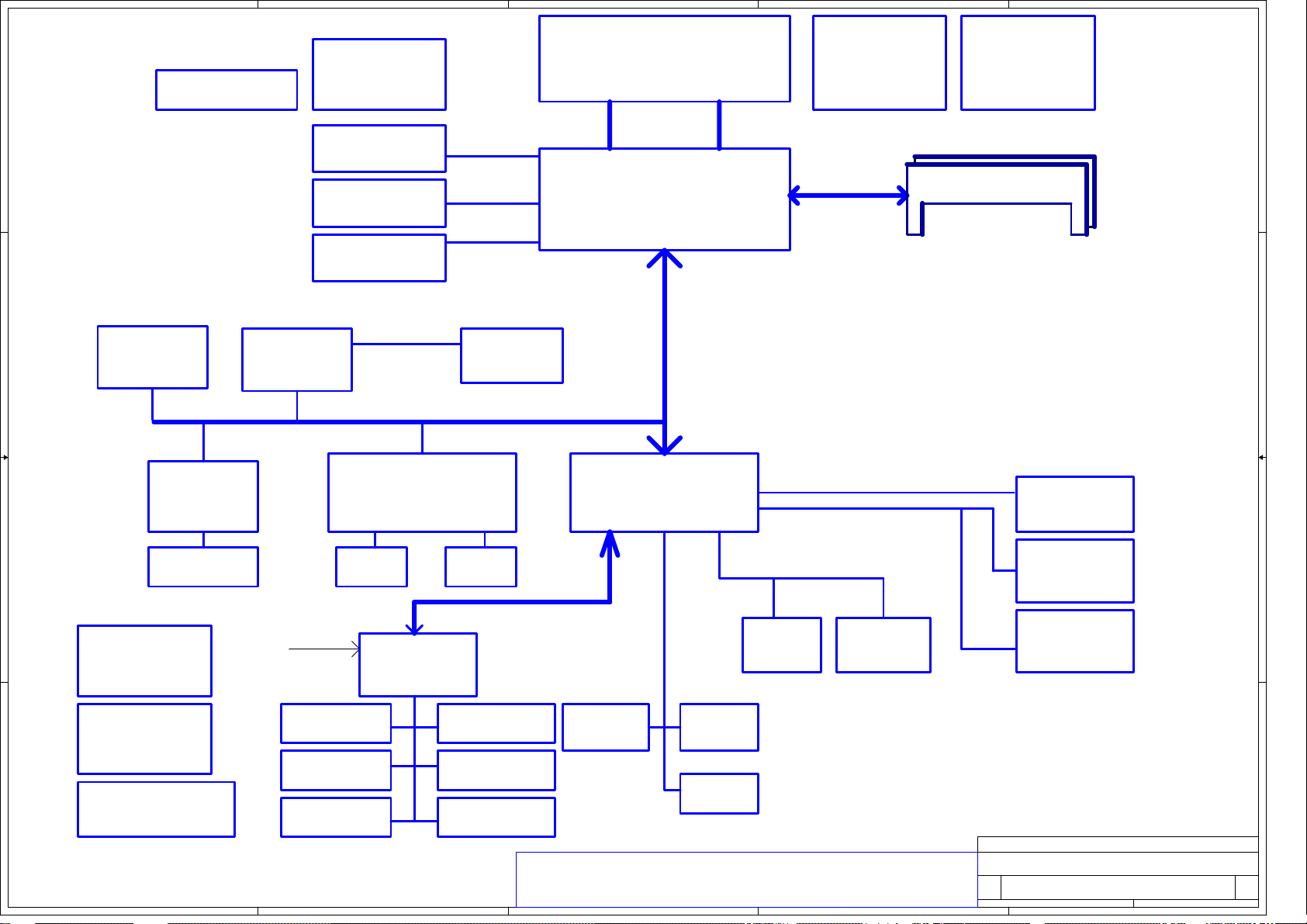

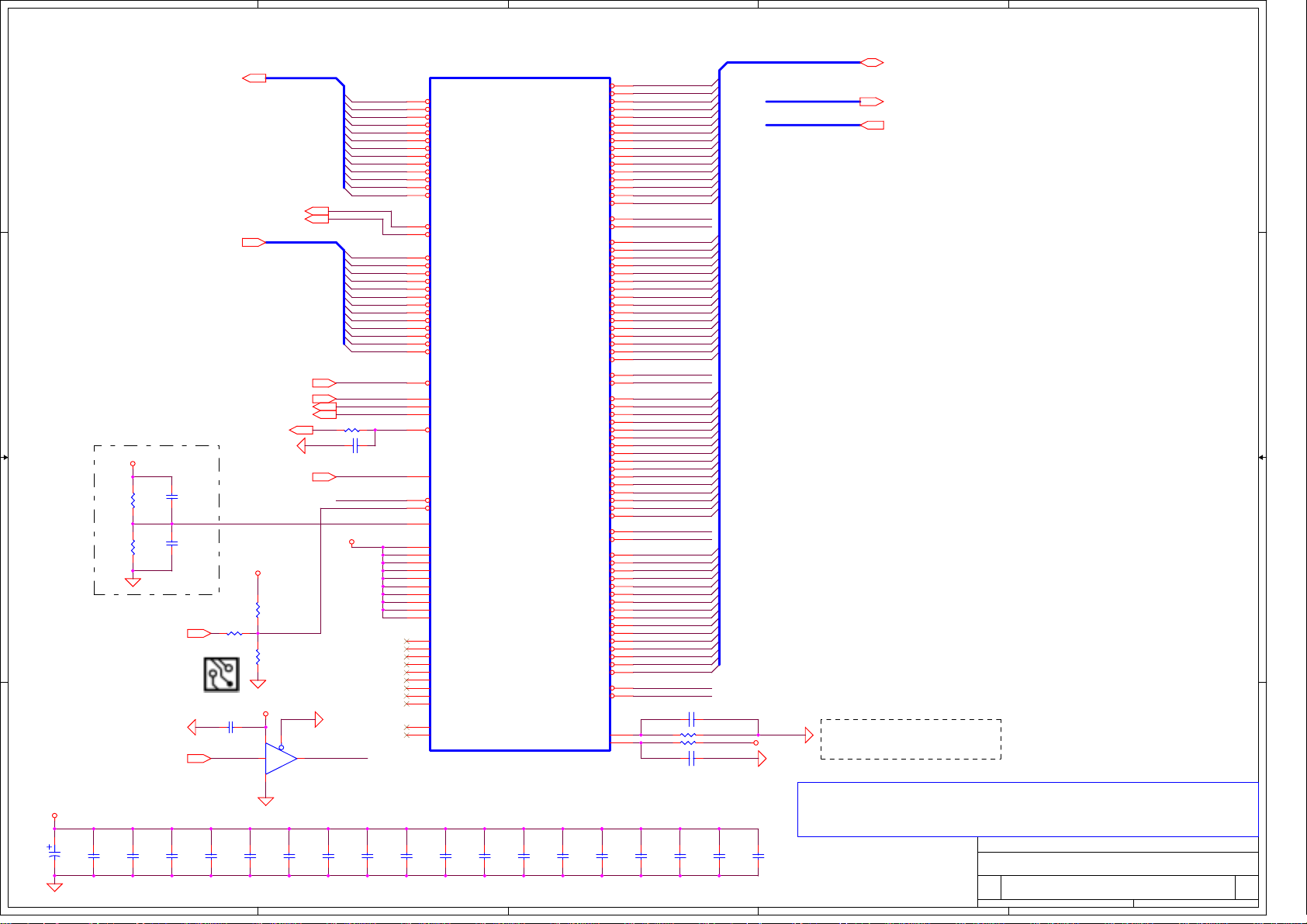

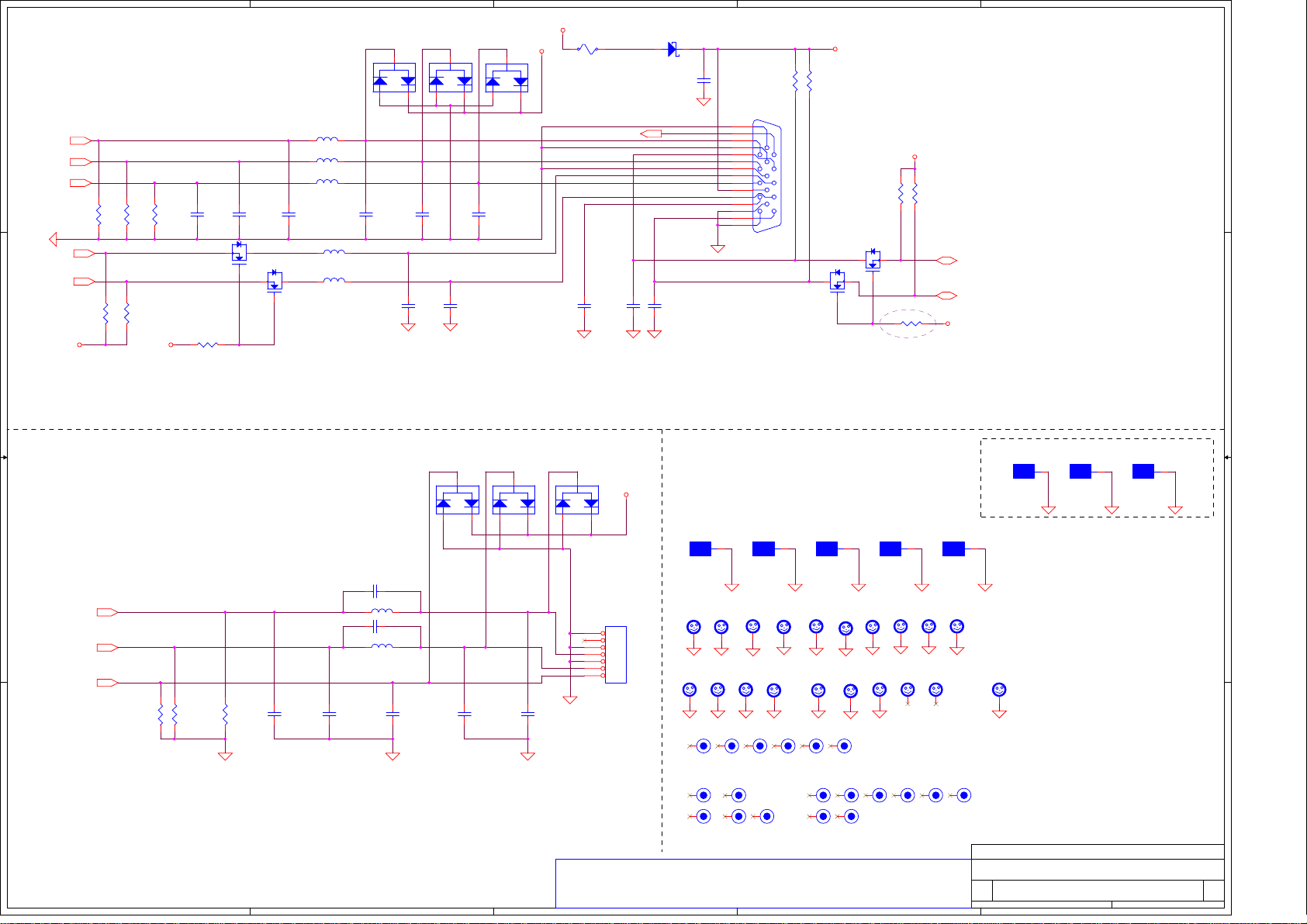

Acer LA-1481 Schematics

A

4 4

B

C

D

E

Confidential

3 3

Schematics

Document

Mobile AMD Athlon XP with ATI

MOBILITY-U1 /ALI 1535+ core logic chip

2 2

2002-08-12

REV: 0.5

1 1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

A

B

C

D

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

COVER SHEET

LA-1481 M/B

!"#, $%

14, 2002

147

E

0.5

of

A

File Name : LA-1481 M/B

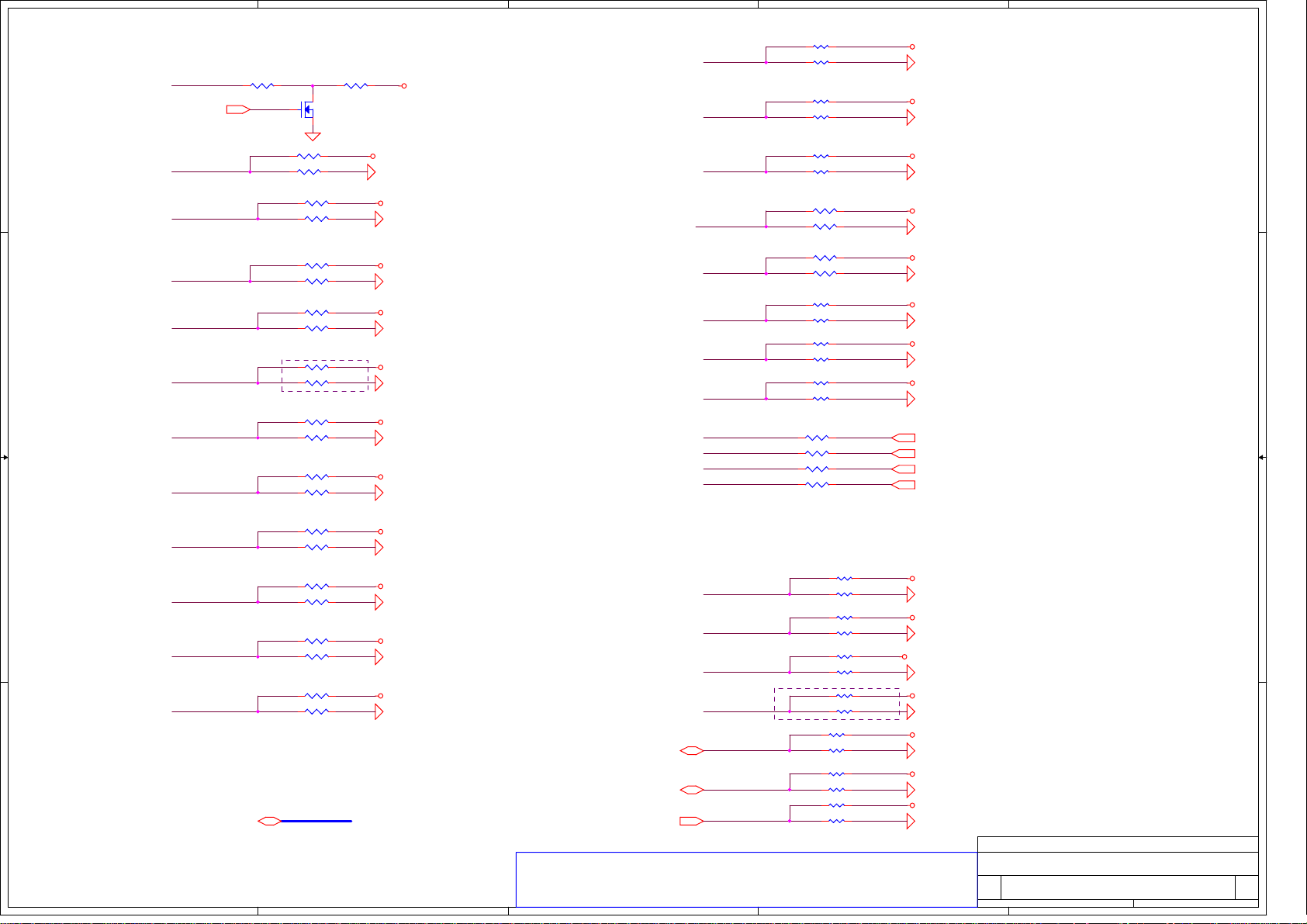

CPU Bypass &

Fan Control

4 4

page 4

CPUFID/VID

TV-OUT Conn

B

page 5,32,33

CRT Conn

page 14

page 14

C

Mobile AMD AthlonXP

Model-8 OPGA

CPU SOCKET

page 3,4

System Bus

400MHz

HD#(0..63)HA#(3..31)

ATI MOBILITY-U1

596 Graphics embedded

BGA

page6,7,8,9,10

Thermal Sensor

NE1617 ICS951403

Memory

BUS(DDR)

2.5V DDR 200/266 MHz

D

Clock Generator

page 3

DDR-SO - D IMM X 2

BANK 0, 1, 2, 3

E

Block Diagram

page 13

page 11,12

LCD Conn

page 15

IDSEL:AD16

(PIRQC#,GNT#0,REQ#0)

3 3

IEEE 1394

VT6306

page 21

Mini PCI

port

page 25

IDSEL:AD31

(PIRQB#,GNT#1,REQ#1)

RJ11

Conn.&Jack

page 25

PCI BUS

IDSEL:AD17

(PIRQC#,GNT#3,REQ#3)

LAN CTRL

RTL 8100BL

page 20

2 2

RJ45 Jack

page 25

Power On/Off

Reset & RTC

page 26,30,18

DC/DC Interface

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

CardBus Controller

ENE CB1420

Slot 1

page 23

14M_5V

EC NS87591L

Touch Pad

page 24

page 27

Suspend

page 31

1 1

Power Circuit DC/DC

page 34,35,36,37,38,39

A

EC I/O Buffer

page 28

BIOS

page 28 page 30

B

3.3V 33MHz

page 22

Slot 0

page 23

S/W BD conn

Int.KBD

page 26

page 26

PS/2 conn

AC-LINK

+5VALW

USB

Port 2

page 29

LPC BUS

3.3V 33MHz

ALI 1535+

page 16,17

3.3V 48MHz

+5VALW

Port 0,1

page 29

3.3V 24.576MHz

3.3V ATA100

USB

SERIALPARALLEL

page 29 page 29

FDD

page 26

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

AC-LINK

CONN

page 24

HDD IDE

Connector

page 19

CDROM IDE

Connector

page 19

Compal Electronics, Inc.

Title

Block Diagram

Size Document Number Rev

LA-1481 M/B

!"#, $%

Date: Sheet

14, 2002

247

E

of

0.3

A

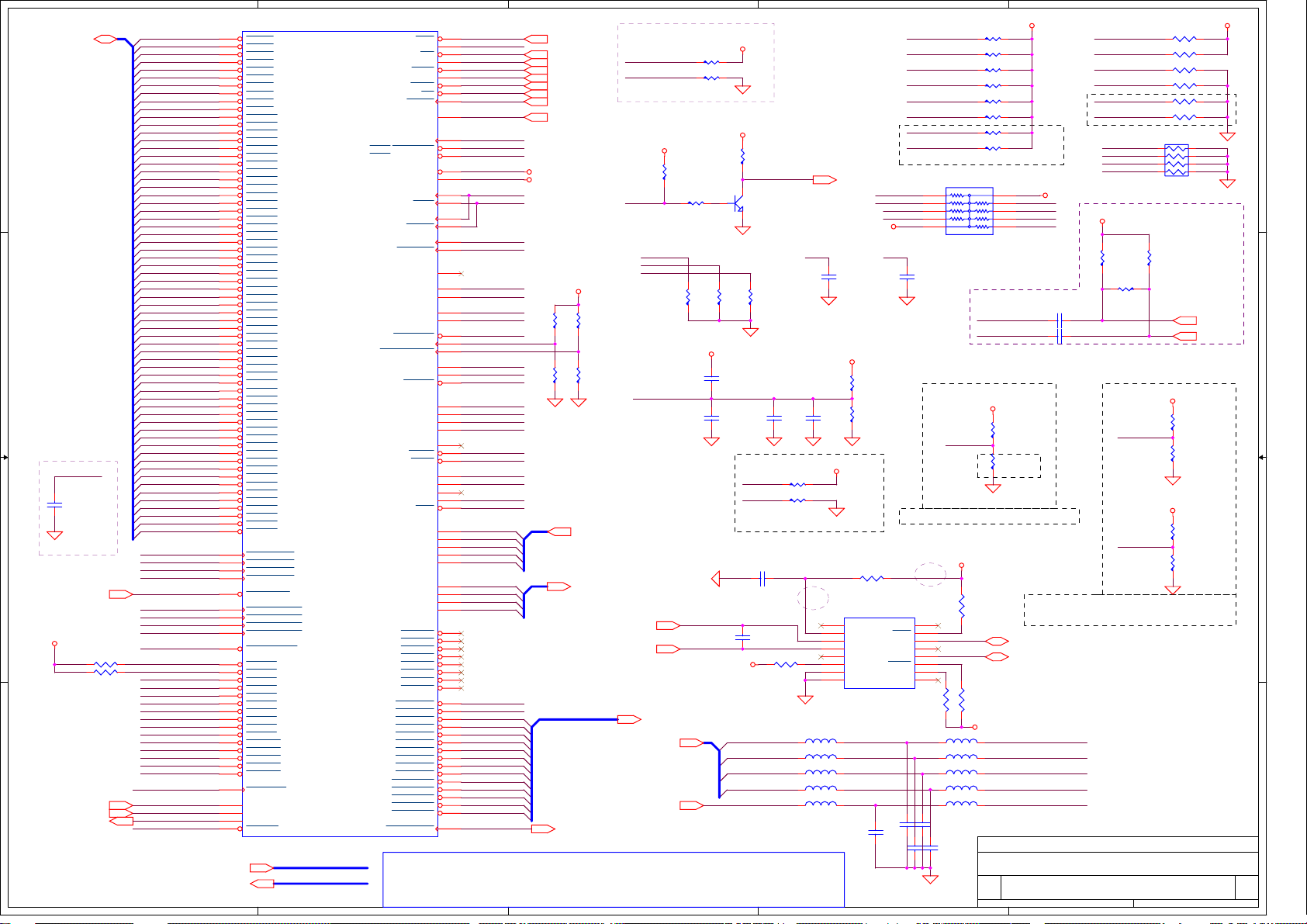

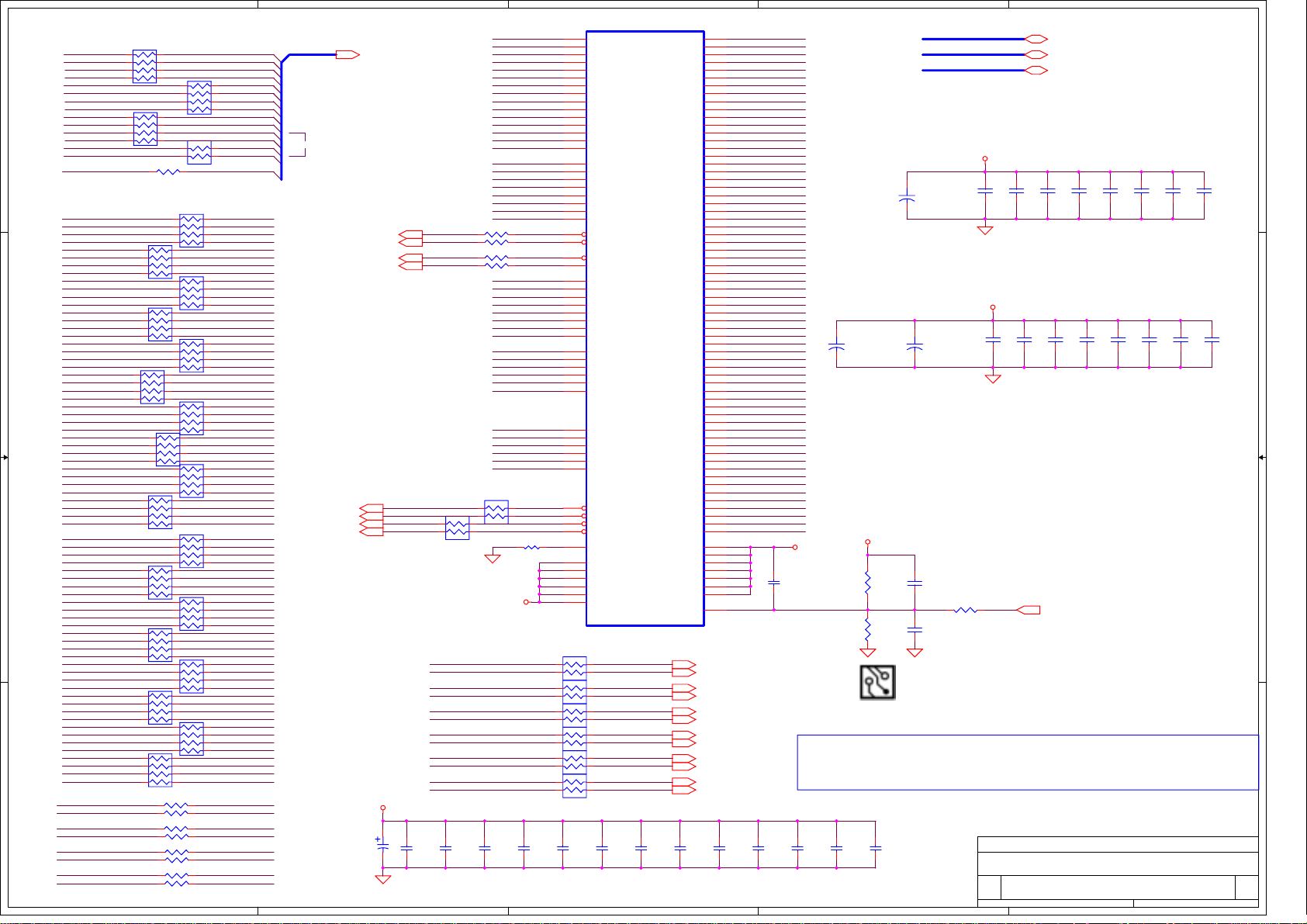

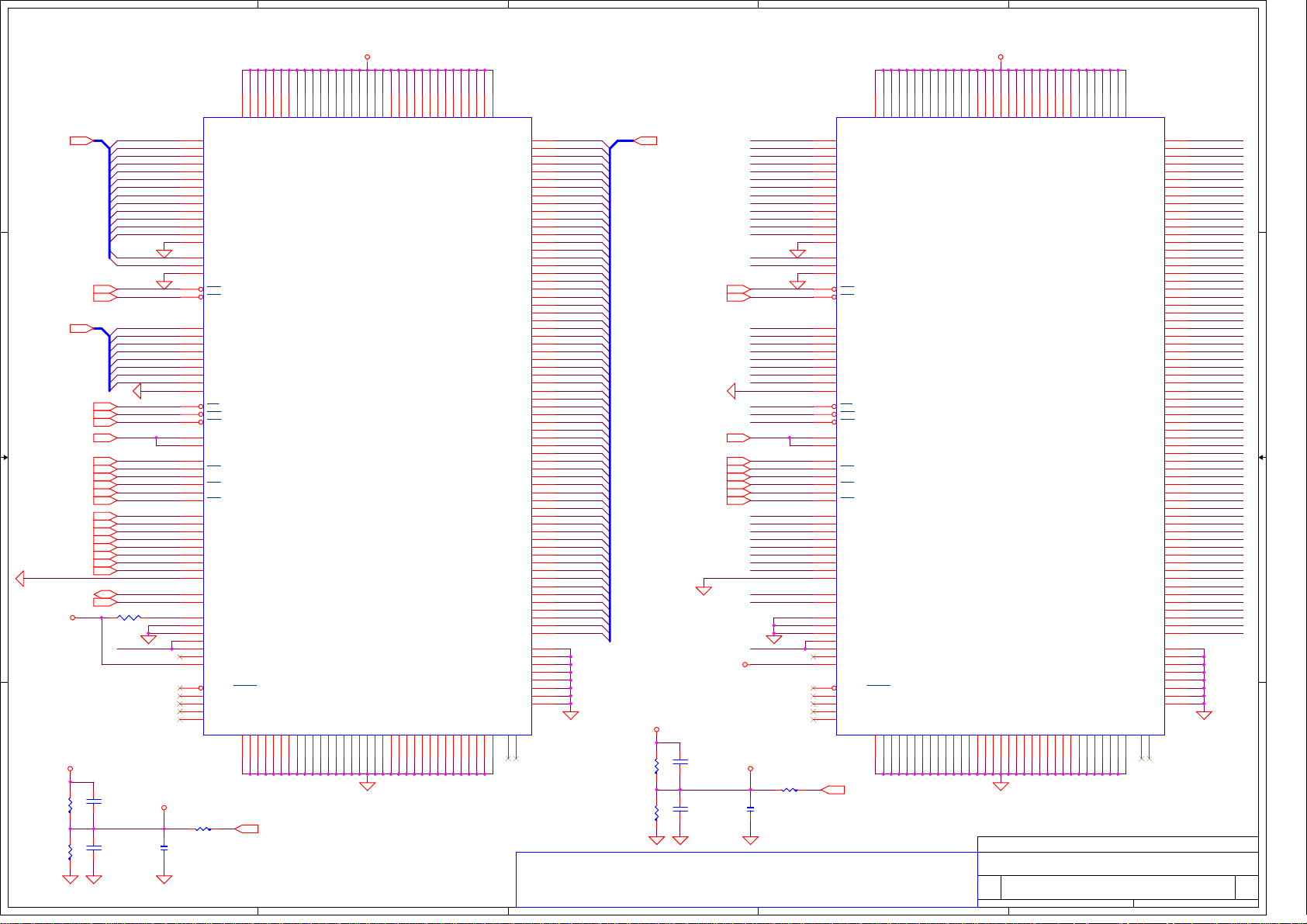

SDATA#[0..63]6

4 4

3 3

SDATAINVAL#

C517

@20PF

1 2

Just for A-TEST

2 2

SDATAINVAL#6

+CPU_CORE

R35 820

1 2

R36 820

1 2

1 1

CLKFWDRST6

CONNECT6

PROCRDY6

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

SDATAIN_CLK#0

SDATAIN_CLK#1

SDATAIN_CLK#2

SDATAIN_CLK#3

SDATAINVAL#

SDATAOUTCLK#0

SDATAOUTCLK#1

SDATAOUTCLK#2

SDATAOUTCLK#3

DOVAL#

SADDIN#0

SADDIN#1

SADDIN#2

SADDIN#3

SADDIN#4

SADDIN#5

SADDIN#6

SADDIN#7

SADDIN#8

SADDIN#9

SADDIN#10

SADDIN#11

SADDIN#12

SADDIN#13

SADDIN#14

SADDIN_CLK#

CONNECT

PROCRDY

FILVAL#

A

SADDIN#[2..14]6

SDATAOUTCLK#[0..3]6

U27A

AA35

SDATA0

W37

SDATA1

W35

SDATA2

Y35

SDATA3

U35

SDATA4

U33

SDATA5

S37

SDATA6

S33

SDATA7

AA33

SDATA8

AE37

SDATA9

AC33

SDATA10

AC37

SDATA11

Y37

SDATA12

AA37

SDATA13

AC35

SDATA14

S35

SDATA15

Q37

SDATA16

Q35

SDATA17

N37

SDATA18

J33

SDATA19

G33

SDATA20

G37

SDATA21

E37

SDATA22

G35

SDATA23

Q33

SDATA24

N33

SDATA25

L33

SDATA26

N35

SDATA27

L37

SDATA28

J37

SDATA29

A37

SDATA30

E35

SDATA31

E31

SDATA32

E29

SDATA33

A27

SDATA34

A25

SDATA35

E21

SDATA36

C23

SDATA37

C27

SDATA38

A23

SDATA39

A35

SDATA40

C35

SDATA41

C33

SDATA42

C31

SDATA43

A29

SDATA44

C29

SDATA45

E23

SDATA46

C25

SDATA47

E17

SDATA48

E13

SDATA49

E11

SDATA50

C15

SDATA51

E9

SDATA52

A13

SDATA53

C9

SDATA54

A9

SDATA55

C21

SDATA56

A21

SDATA57

E19

SDATA58

C19

SDATA59

C17

SDATA60

A11

SDATA61

A17

SDATA62

A15

SDATA63

W33

SDATAINCLK0

J35

SDATAINCLK1

E27

SDATAINCLK2

E15

SDATAINCLK3

AN33

SDATAINVAL

AE35

SDATAOUTCLK0

C37

SDATAOUTCLK1

A33

SDATAOUTCLK2

C11

SDATAOUTCLK3

AL31

SDTATOUTVAL

AJ29

SADDIN0

AL29

SADDIN1

AG33

SADDIN2

AJ37

SADDIN3

AL35

SADDIN4

AE33

SADDIN5

AJ35

SADDIN6

AG37

SADDIN7

AL33

SADDIN8

AN37

SADDIN9

AL37

SADDIN10

AG35

SADDIN11

AN29

SADDIN12

AN35

SADDIN13

AN31

SADDIN14

AJ33

SADDINCLK

AJ21

CLKFWDRST

AL23

CONNECT

AN23

PROCRDY

AJ31

SFILLVAL

CPU_SOCKET_OPGA_462

SADDIN#[2..14]

SDATAOUTCLK#[0..3]

B

A20M#

AE1

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

ZN

ZP

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

B

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

FERR

INIT#

INTR

IGNNE#

NMI

CPURST#

SMI#

STPCLK#

APICCLK0

APICD0

APICD1

COREFBCOREFB+

CPUCK

CPUCK#

CLKOUT

CLKOUT#

VREFMODE

VREF_SYS

ZN

ZP

PLLBP#

PLLCLK

PLLCLK#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBREQ#

FLUSH#

TCK

TDI

TMS

TRST#

PVID0

PVID1

PVID2

PVID3

PVID4

FID0

FID1

FID2

FID3

SADDOUT#0

SADDOUT#1

SADDOUT#2

SADDOUT#3

SADDOUT#4

SADDOUT#5

SADDOUT#6

SADDOUT#7

SADDOUT#8

SADDOUT#9

SADDOUT#10

SADDOUT#11

SADDOUT#12

SADDOUT#13

SADDOUT#14

SADDOUTCLK#

COREFBCOREFB+

R129

100_1%

15mil

15mil

100_1%

A20M# 16

INIT# 16

INTR 16

IGNNE# 16

NMI 16

CPURST# 6,16

SMI# 16

STPCLK# 16

CPU_PWROK 30

+CPU_CORE

R131

100_1%

R130

R132

100_1%

PVID[0..4] 33

FID[0..3] 32

SADDOUT#[2..14]

SADDOUTCLK# 6

C

Near socket-A

COREFB+

COREFB-

AMD RECOMEND

+CPU_CORE

R187

510

FERR

R530 75

APICCLK0

APICD0

APICD1

0.047UF_0603

VREF_SYS

close to CPU socket

@1UF_0603

THERMDA4

THERMDC4

SADDOUT#[2..14] 6

SDATAINCLK#[0..3]6

SADDINCLK#6

Place these component near middle of

trace.

C

+CPU_CORE

R157 10K

R151 10K

+3VS

R451

510

Q17

2

MMBT2222A

3 1

R190

R450

1K

1K

+CPU_CORE

12

C518

VREF_SYS is set at 50%

of VCC_CORE to CPU

12

C519

10 Miles

10 Miles

C149

0.047UF

ZN

ZP

Change Value by tunning

close to CPU socket

C377 0.1UF

C385

2200PF

1 2

+3VS

AMD recommend

SDATAINCLK#0

SDATAINCLK#1 SDATAIN_CLK#1

SDATAINCLK#2

SDATAINCLK#3

SADDINCLK# SADDIN_CLK#

R140

1K

15mil

FERR#

15mil

12

R192 40.2_1%_0603

R191 40.2_1%_0603

12

R422

1 2

1K

FERR# 16

+CPU_CORE

SMI#

C528

@560PF

Reduce NMI

noise for

C3

+CPU_CORE

12

C147

@0.1UF

+CPU_CORE

R552 150

1 2

15mil

U26

1

NC

2

VCC

3

DXP

4

DXN

5

NC

6

ADD1

7

GND

8 9

GND NC

NE1617DS

RESERVE FOR MOBILE K7

10nH

L23 NL252018T-010J

L27 NL252018T-010J

L32 NL252018T-010J

L35 NL252018T-010J

L20 0_0805

C40

@5PF

D

NMI

Reduce NMI

noise for

C3

R441

60.4_1%

R442

60.4_1%

SMBCLK

SMBDATA

C46

12

C57

D

+CPU_CORE +CPU_CORE

A20M#

IGNNE#

INIT#

DBREQ#

TCK

TMS

TDI

TRST#

PLLTEST#

FLUSH#

PLLBP#

C145

@560PF

RP24

1

2

3

4

5

10P8R_820

AMD recomend

R146 820

R448 820

R449 820

R185 820

R443 820

R445 820

R173 820

R75 820

10

9

8

7

6

INTRCPURST#

NMI

SMI#

STPCLK#

Near socket-A U1

CPUCK

CPUCK#

+CPU_CORE

R446

VREFMODE

close to CPU socket

@1K

15mil

R447

@1.5K

VREFMODE=Low=No voltage scaling

+3VS

15mil

12

R419

10K

12

12

R421

10K

+3VS

L24 NL252018T-010J

L28 NL252018T-010J

L33 NL252018T-010J

L36 NL252018T-010J

L21 0_0805

C91

5PF

12

C108

5PF

Title

Size Document Number Rev

Date: Sheet

EC_SMC2 27

EC_SMD2 27

SDATAIN_CLK#0

SDATAIN_CLK#2

SDATAIN_CLK#3

Compal Electronics, Inc.

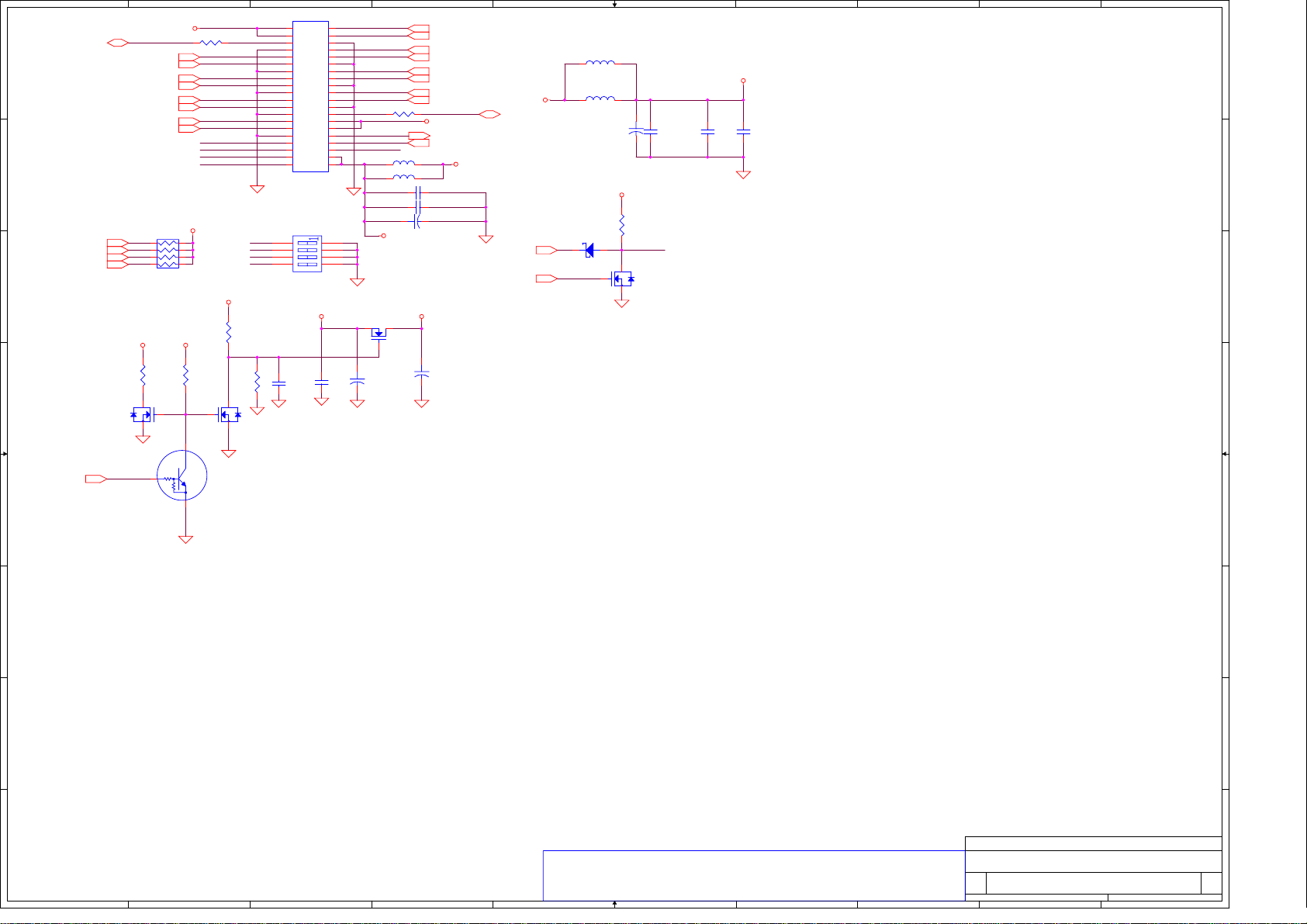

AMD AthlonXP SOCKET_ A-1

LA-1481 M/B

!"#, $%

STBY

ALERT

ADD0

5PF

5PF

16

NC

15

14

13

NC

12

11

10

R423

1K

12

12

12

E

PLLMON1

PLLMON2

SADDOUT#0

SADDOUT#1

FILVAL#

DOVAL#

+CPU_CORE

+CPU_CORE

C116 680PF

C112 680PF

Trace lengths of CLKOUT and CLKOUT#

are between 2" and 3"

14, 2002

R138 56

R139 56

R452 @1K

R444 @1K

R23 820

R24 820

SSHIFTEN

SINTVAL

SCANCLK2

SCANCLK1

8P4R_1.5K_0804

R127

60.4_1%

R115

301_1%

CLKOUT

close to CPU socket

CLKOUT#

E

RP25

1 8

2 7

3 6

4 5

R112

60.4_1%

CPUCLK 13

CPUCLK# 13

+CPU_CORE

R91

100_1%

15mil

R92

100_1%

+CPU_CORE

R98

100_1%

15mil

R97

100_1%

347

of

0.3

+12VS

R195

3.48K_1%_0603

FAN1

1 2

21

D13

1N4148

31

2

Q18 2SA1036K

Located at Socket-A Cap

0.22UF(0603) X 22

1000PF(0402) X 4

0.1UF(0402) X 4

0.01UF(0402) X 4

1UF(0603) X 8

10UF(1206) X 30

39PF(0402) X 29

330UF(D2_2.5V_15m) X 8

SVID[0..4]33

SVID0

SVID4

SVID2

SVID3

SVID1

Fan1 Control circuit

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

H10

H28

H30

H32

K30

AJ7

AL7

AN7

G25

G17

AG7

AG15

AG29

AA7

AG9

AG17

AG27

G15

G23

AH6

F8

H6

H8

K8

G9

N7

Y7

G7

Q7

D15 @1SS355

CB41

1 2

2.2UF_16V_0805

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

KEY

KEY

KEY

KEY

KEY

KEY

KEY

KEY

AMD

VSS1

VSS2

VSS3

VSS4

H14

H18

H22

H26

FMMT619

2

21

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VSS5

VSS6

VSS7

VSS8

M30P8R30T8V30X8Z30

Q19

D14

1N4148

VCC_CORE9

VCC_CORE10

VSS9

VSS10

D33

C17

1SS355

VCC_CORE14

VSS14

40mil

AF22

AF26

VCC_CORE15

VSS15

AF20

AF24

C446

1000PF

AM34

VCC_CORE16

VCC_CORE17

VSS16

VSS17

AM36

@1000PF

+5VFAN1

AK36

AK34

AK30

VCC_CORE18

VCC_CORE19

VSS18

VSS19

AK32

AK28

AK24

VCC_CORE20

VSS20

2 1

3 1

2 1

AF14

AF18

VCC_CORE11

VCC_CORE12

VCC_CORE13

VSS11

VSS12

VSS13

AB8

AF12

AF16

+5VS

JP21

1

2

3

53398-0310

Layout:C3 & C988 must

close to JP1

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

AH22

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

AK20

AK16

AK12

AK4

AK2

AH36

AM32

AH34

AH32

+3VS

12

R456

10K

FANSPEED1 27

C219

1000PF

AH18

AH14

AH10

AH4

AH2

AF36

AF34

AD6

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VSS31

VSS32

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

AH28

AH24

AH20

AH16

AH12

AF4

AF2

AD36

EN_FAN127

AM26

AD4

AD2

AB36

AB34

AB32Z6Z4Z2X36

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

AD34

AD32

AB6

AB4

AB2

Z36

Z34

VCC_CORE44

VCC_CORE45

VCC_CORE46

VSS46

VSS47

VSS48

Z32X6AM28X4X2

VCC_CORE47

VSS49

X34

VCC_CORE48

VSS50

12

AM22

X32V6V4V2T36

VCC_CORE49

VCC_CORE50

VSS51

VSS52

V36

C444

0.1UF

1 2

R455

13K_1%_0603

VCC_CORE51

VCC_CORE52

VCC_CORE53

VSS53

VSS54

VSS55

V34

V32T6T4T2R36

T34

VCC_CORE54

VCC_CORE55

VSS56

VSS57

T32R6R4R2AM18

VCC_CORE56

VCC_CORE57

VCC_CORE58

VSS58

VSS59

VSS60

R34

AM24

P36

VCC_CORE59

VCC_CORE60

VCC_CORE61

VSS61

VSS62

VSS63

R32P6P4P2M36

+5VS

1

3

P34

P32M4M6M2K36

VCC_CORE62

VCC_CORE63

VSS64

VSS65

VCC

VEE

2 5

R453

M34

0.1UF

1 2

C443

4

U28

LMV321_SOT23-5

1 2

7.32K_1%_0603

K34

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VSS66

VSS67

VSS68

VSS69

VSS70

M32K6K4K2AM20

K32H4H2

VCC_CORE69

VCC_CORE70

VSS71

VSS72

H36

FAN1

AM14

F36

F34

F32

F28

F24

F20

F16

F12

D32

D28

AM10

D24

D20

D16

D12D8D4D2B36

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

H34

F26

F22

F18

F14

F10F6F4F2AM16

D36

D34

D30

D26

D22

D18

D14

D10D6B34

+CPU_CORE

12

12

C71

C103

0.1UF

1000PF

+CPU_CORE

12

C30

10UF_10V_1206

+VCCA2.5+CPU_CORE

B32

AM2

B28

B24

B20

B16

B12B8B4

AJ5

AC7

VCC_Z

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

NC1

NC2

NC3

NC6

NC7

NC8/FSB_Sense

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

AM12

B30

B26

B22

B18

B14

B10B6B2

AM4

AK6

AM6

AE7

OPTION

12

12

C358

C334

1000PF

0.01UF

OPTION

12

C27

10UF_10V_1206

CB106

1 2

4.7UF_10V_0805

>15mil

U27B

CPU_SOCKET_OPGA_462

AJ23

VCC_A

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

ADD for 133/100MHz select 91.03.15.

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

THERMDA

S7

U31

THERMDC

U7

W31

9/04/2000 CHANGE BACK

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

+CPU_CORE

VSS_Z

C31

1UF_10V_0603

12

C143

0.01UF

C28

10UF_10V_1206

1 2

FSB_100/133#

C37

1UF_10V_0603

12

C357

1000PF

THERMDA 3

THERMDC 3

12

C94

0.1UF

12

R11 10K

OPTION

12

C98

0.01UF

12

C29

10UF_10V_1206

+3VS

+CPU_CORE

12

C56

0.1UF

C395

1UF_10V_0603

12

12

C72

C82

1000PF

0.01UF

FSB_100/133# 10,13

12

C33

0.1UF

C384

1UF_10V_0603

AMD Socket-A processors will not

implement a pin at location AH6.

VR_ON27,36,39

CONTROL ON/OFF

+5VS

0.22UF_0603

R221 0

C161

C158

0.1UF

VCCA for cpu internal PLL power source!

U9

8

SD#

4

VIN

1

Cnoise

3

GND

SENSE/ADJ

VOUT

ERROR#

DELAY

SI9182DH-25

5

6

7

2

C526

0.22UF_0603

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

(2.5V Output)

2.5V,if 1GHz need 200mA

@4.7UF_10V_0805

+2.5_A +2.5_B

12

12

C151

C152

39PF

L41 0_0805

>20mil >20mil

1 2

C156

39PF

L40 0_0805

1 2

C160

39PF

+VCCA2.5

>20mil

C155

39PF

+3VALW

Near socket-A

pin AJ23

R74 10

C84

39PF

R292 470K_0603

CPUDET#27

C81

39PF

1 2

C520

39PF

+VCCP2.5

+CPU_CORE

+VCCP2.5 30

Compal Electronics, Inc.

Title

AMD AthlonXP SOCKET_ A-2

Size Document Number Rev

LA-1481 M/B

!"#, $%

Date: Sheet

C35

1UF_10V_0603

14, 2002

OPTION

1UF_10V_0603

C26

C38

1UF_10V_0603

447

of

C39

1UF_10V_0603

0.3

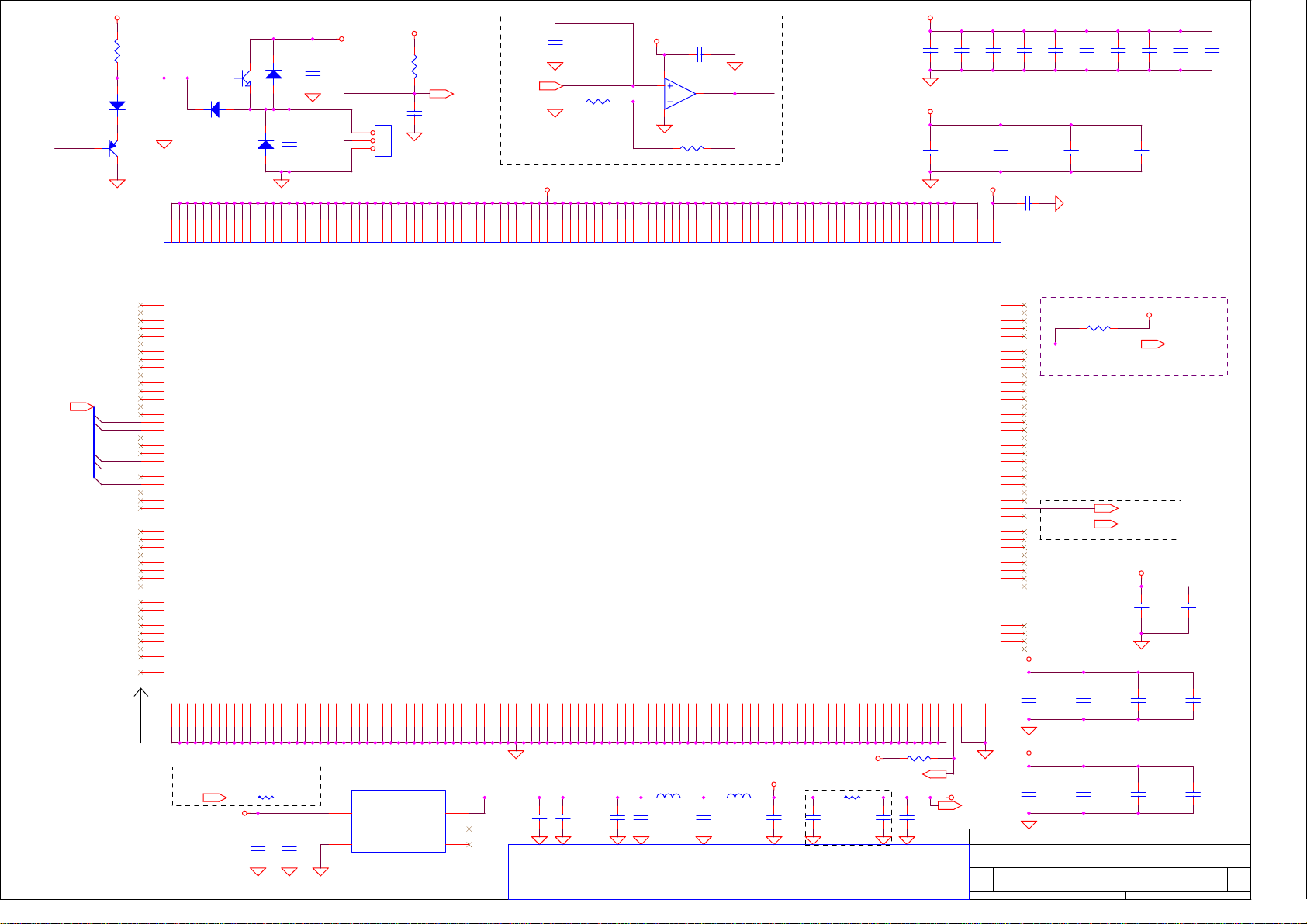

A

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

B

C

D

E

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

Please place these cap in the socket cavity area

1 1

+CPU_CORE

12

option

CB83

10UF_6.3V_1206

Please place these cap on the socket north side

+CPU_CORE

12

CB25

10UF_6.3V_1206

+CPU_CORE

12

2 2

10UF_6.3V_1206

+CPU_CORE

12

CB12

CB31

10UF_6.3V_1206

12

CB10

10UF_6.3V_1206

12

CB26

10UF_6.3V_1206

12

CB34

10UF_6.3V_1206

12

CB30

10UF_6.3V_1206

12

CB36

10UF_6.3V_1206

12

CB28

10UF_6.3V_1206

12

CB37

10UF_6.3V_1206

12

CB9

10UF_6.3V_1206

option

Please place these cap on the socket south side

+CPU_CORE

12

CB40

10UF_6.3V_1206

+CPU_CORE

3 3

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

CB1

CB29

12

CB32

10UF_6.3V_1206

12

CB38

10UF_6.3V_1206

12

CB33

10UF_6.3V_1206

12

CB6

10UF_6.3V_1206

12

CB13

10UF_6.3V_1206

12

CB5

10UF_6.3V_1206

12

CB19

10UF_6.3V_1206

12

CB21

10UF_6.3V_1206

12

CB11

10UF_6.3V_1206

12

CB8

10UF_6.3V_1206

12

CB27

10UF_6.3V_1206

option

+CPU_CORE

12

CE3

+

330UF_D2_2.5V_15m

+CPU_CORE

12

CE11

+

330UF_D2_2.5V_15m

+CPU_CORE +CPU_CORE

12

C114

39PF

+CPU_CORE

12

C111

0.22UF_0603

+CPU_CORE

12

C93

0.22UF_0603

+CPU_CORE

12

C78

0.22UF_0603

+CPU_CORE

12

C45

39PF

Used ESR 15m ohm cap total ESR=1.875m ohm

12

CE16

+

330UF_D2_2.5V_15m

12

CE6

+

330UF_D2_2.5V_15m

12

12

C102

39PF

12

C32

39PF

12

C87

C85

39PF

39PF

12

12

C75

C123

0.22UF_0603

0.22UF_0603

12

12

C117

C131

0.22UF_0603

0.22UF_0603

12

C74

0.22UF_0603

12

12

C137

C361

39PF

39PF

Distribute evenly on approximately

one-inch spacing along the VccCore

plane edge .

12

+

330UF_D2_2.5V_15m

12

+

330UF_D2_2.5V_15m

12

12

C88

39PF

12

C132

0.22UF_0603

12

C76

0.22UF_0603

NOTE: Must put inside

the CPU socket

12

12

C365

C438

39PF

39PF

CE7

CE12

C403

39PF

12

C362

0.22UF_0603

12

C414

0.22UF_0603

12

C415

39PF

12

CE5

+

330UF_D2_2.5V_15m

12

CE15

+

330UF_D2_2.5V_15m

12

12

C416

39PF

12

C405

39PF

12

C392

0.22UF_0603

12

C363

0.22UF_0603

12

C356

39PF

12

C354

39PF

12

C125

0.22UF_0603

12

C378

0.22UF_0603

12

C86

39PF

12

C99

39PF

place close to the bulk

decoupling 330UF CAP per item

C366

39PF

12

C396

0.22UF_0603

12

C387

0.22UF_0603

12

C126

0.22UF_0603

12

C381

0.22UF_0603

12

C77

0.22UF_0603

12

C413

0.22UF_0603

+CPU_CORE

12

12

12

C73

C121

39PF

4 4

39PF

C138

39PF

12

C119

39PF

EMI Clip HOLE for CPU

PT2

1 2

AMD_CPU_EMI_CLIP

A

PT3

1 2

AMD_CPU_EMI_CLIP

PT4

1 2

AMD_CPU_EMI_CLIP

PT5

1 2

AMD_CPU_EMI_CLIP

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

12

12

C355

39PF

DISTRIBUTE EVENLY ON BOTTOMSIDE

OF CPU SOCKET-A

C139

39PF

12

C127

39PF

12

12

C34

C124

39PF

39PF

D

place the

components first

Compal Electronics, Inc.

Title

CPU Bypass Cap.

Size Document Number Rev

LA-1481 M/B

Date: Sheet

!"#, $%

14, 2002

E

547

of

0.3

A

B

C

D

E

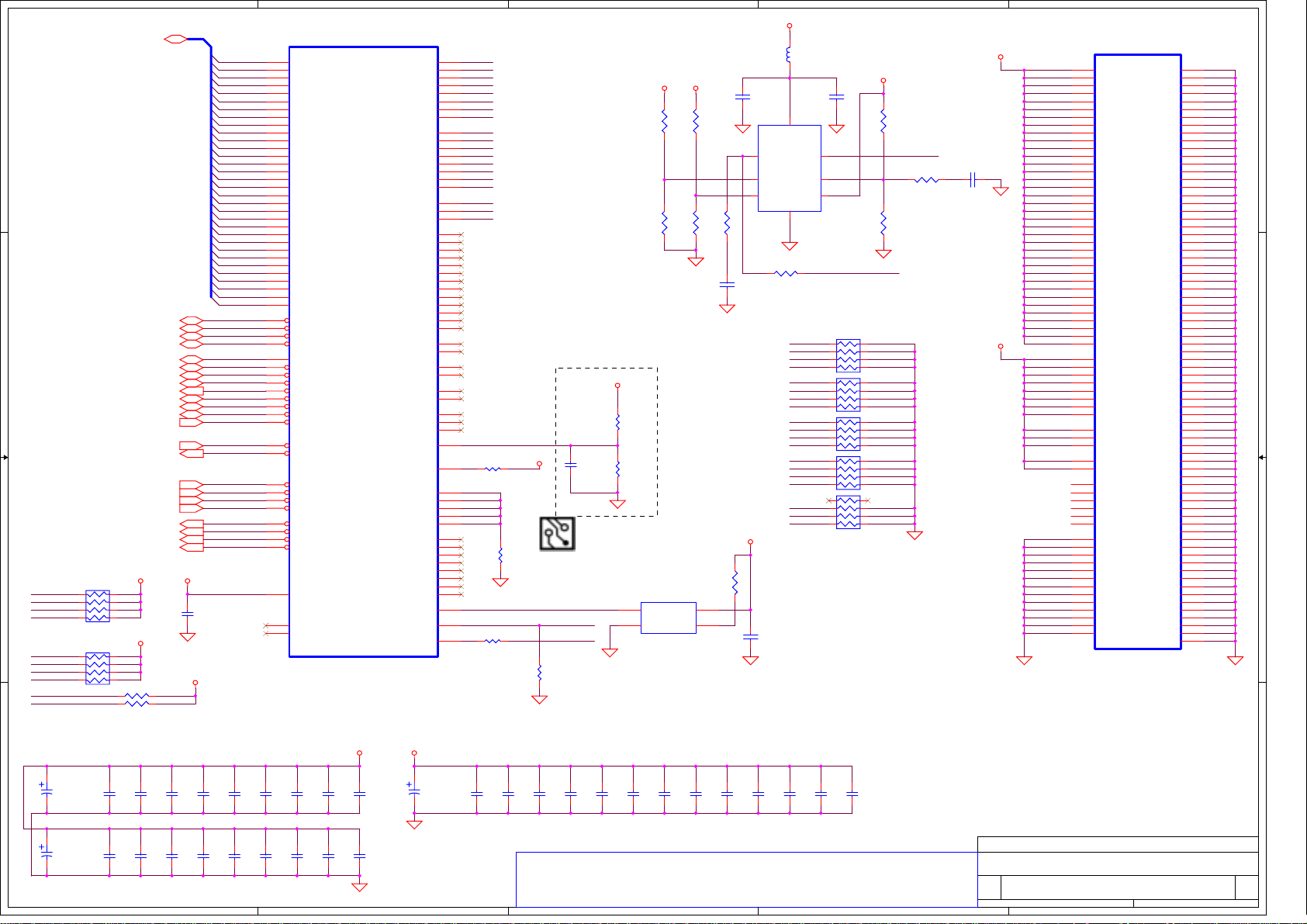

SDATA#[0:63]

SDATAINCLK#[0..3]

SDATAOUTCLK#[0..3]

+CPU_CORE

PA_216U1E1 Product Advisory

Ball A16 = CAL#

Ball B16 = CAL

A21

A20

B19

A22

B20

B21

C18

C17

A19

D21

D20

B18

C21

C19

E19

N26

P24

P25

R24

N25

U25

P26

R26

V25

U26

T25

T26

U24

R25

F20

D19

E20

V26

AC25

AD6

AE6

Y26

C20

G16

G17

G18

H20

H24

M20

N20

P20

D17

D18

E16

E17

E18

F16

F17

F18

F19

W23

V22

U3A

J20

ATI_U1

SADDIN2#

SADDIN3#

SADDIN4#

SADDIN5#

SADDIN6#

SADDIN7#

SADDIN8#

SADDIN9#

SADDIN10#

SADDIN11#

SADDIN12#

SADDIN13#

SADDIN14#

SADDINCLK#

SDATAINVAL#

SADDOUT2#

SADDOUT3#

SADDOUT4#

SADDOUT5#

SADDOUT6#

SADDOUT7#

SADDOUT8#

SADDOUT9#

SADDOUT10#

SADDOUT11#

SADDOUT12#

SADDOUT13#

SADDOUT14#

SADDOUTCLK#

PROCRDY

CLKFWDRST

CONNECT

CPURST#

POWERGOOD

NRSTIN#

DC_STOP#

S2K_VREF

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

K7_NC

K7_NC

K7_NC

K7_NC

K7_NC

K7_NC

K7_NC

K7_NC

K7_NC

THERMALDIODE_P

THERMALDIODE_N

PART 1 OF 5

SDATAOUTCLK0#

SDATAOUTCLK1#

S2K I/F (K7 MOBILE)

SDATAOUTCLK2#

SDATAOUTCLK3#

SDATA0#

SDATA1#

SDATA2#

SDATA3#

SDATA4#

SDATA5#

SDATA6#

SDATA7#

SDATA8#

SDATA9#

SDATA10#

SDATA11#

SDATA12#

SDATA13#

SDATA14#

SDATA15#

SDATAINCLK0#

SDATA16#

SDATA17#

SDATA18#

SDATA19#

SDATA20#

SDATA21#

SDATA22#

SDATA23#

SDATA24#

SDATA25#

SDATA26#

SDATA27#

SDATA28#

SDATA29#

SDATA30#

SDATA31#

SDATAINCLK1#

SDATA32#

SDATA33#

SDATA34#

SDATA35#

SDATA36#

SDATA37#

SDATA38#

SDATA39#

SDATA40#

SDATA41#

SDATA42#

SDATA43#

SDATA44#

SDATA45#

SDATA46#

SDATA47#

SDATAINCLK2#

SDATA48#

SDATA49#

SDATA50#

SDATA51#

SDATA52#

SDATA53#

SDATA54#

SDATA55#

SDATA56#

SDATA57#

SDATA58#

SDATA59#

SDATA60#

SDATA61#

SDATA62#

SDATA63#

SDATAINCLK3#

CAL#

CAL

SDATA#0

A25

SDATA#1

D25

SDATA#2

D26

SDATA#3

C25

SDATA#4

E25

SDATA#5

E24

SDATA#6

F24

SDATA#7

E26

SDATA#8

A23

SDATA#9

B22

SDATA#10

C22

SDATA#11

B23

SDATA#12

C26

SDATA#13

B24

SDATA#14

C23

SDATA#15

F25

SDATAINCLK#0

D24

SDATAOUTCLK#0

A24

SDATA#16

E23

SDATA#17

D22

SDATA#18

G22

SDATA#19

H23

SDATA#20

J23

SDATA#21

J22

SDATA#22

K23

SDATA#23

J21

SDATA#24

E21

SDATA#25

G23

SDATA#26

G21

SDATA#27

F23

SDATA#28

F22

SDATA#29

H22

SDATA#30

L23

SDATA#31

K22

SDATAINCLK#1

H21

SDATAOUTCLK#1

K21

SDATA#32

M21

SDATA#33

N22

SDATA#34

R23

SDATA#35

R21

SDATA#36

U23

SDATA#37

T22

SDATA#38

P21

SDATA#39

T21

SDATA#40

L21

SDATA#41

L22

SDATA#42

M23

SDATA#43

N23

SDATA#44

P23

SDATA#45

N21

SDATA#46

T23

SDATA#47

P22

SDATAINCLK#2

R22

SDATAOUTCLK#2

M22

SDATA#48

H25

SDATA#49

K25

SDATA#50

L24

SDATA#51

J26

SDATA#52

M25

SDATA#53

K26

SDATA#54

M26

SDATA#55

N24

SDATA#56

F26

SDATA#57

G24

SDATA#58

G25

SDATA#59

G26

SDATA#60

H26

SDATA#61

L26

SDATA#62

J24

SDATA#63

J25

SDATAINCLK#3

K24

SDATAOUTCLK#3

L25

C539 0.01UF

R15 30_1%_0603

A16

R14 30_1%_0603

B16

C540 0.01UF

1 2

1 2

SADDIN#[2..14]3

4 4

SADDOUT#[2..14]3

3 3

+CPU_CORE

C533

R150

0.047UF

60.4_1%

C140

R149

0.047UF

60.4_1%

2 2

PLACE CLOSE TO MOBILITY U1

SUS_STAT#17,28

PCIRST#16,19,20,21,22,23,25,26,27

R210

1K

C159 0.1UF

PCIRST# NB_RST#

SADDIN#[2..14]

SADDINCLK#3

SDATAINVAL#3

SADDOUT#[2..14]

SADDOUTCLK#3

PROCRDY3

CLKFWDRST3

CONNECT3

1

U7A

74LVC125

R137 @0

C122

@1UF_10V_0603

CPURST#3,16

NB_PWRGD30

+2.5V

R211

@4.7K

DC_STOP#

R457

1K

NOTE: ROUTE AS DIFF PAIR T O HW M

+3VALW

147

2 3

1 2

+CPU_CORE

SADDIN#2

SADDIN#3

SADDIN#4

SADDIN#5

SADDIN#6

SADDIN#7

SADDIN#8

SADDIN#9

SADDIN#10

SADDIN#11

SADDIN#12

SADDIN#13

SADDIN#14

SADDOUT#2

SADDOUT#3

SADDOUT#4

SADDOUT#5

SADDOUT#6

SADDOUT#7

SADDOUT#8

SADDOUT#9

SADDOUT#10

SADDOUT#11

SADDOUT#12

SADDOUT#13

SADDOUT#14

NB_PWRGD

NB_RST#

NB_VREFSYS

SDATA#[0:63] 3

SDATAINCLK#[0..3] 3

SDATAOUTCLK#[0..3] 3

1 1

+CPU_CORE

CB16

10UF_10V_1206

C442

0.1UF

C340

0.1UF

A

0.1UF

0.1UF

C439

C441

C120

0.1UF

C374

0.1UF

C335

0.1UF

C339

0.1UF

C440

0.1UF

B

C375

0.1UF

C383

0.1UF

0.1UF

C373

C404

0.1UF

C360

0.1UF

C372

0.1UF

C

0.1UF

0.1UF

C412

C367

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C394

0.1UF

D

Compal Electronics, Inc.

Title

ATI MOBILITY U1_S2K BUS

Size Document Number Rev

LA-1481 M/B

!"#, $%

Date: Sheet

14, 2002

E

647

0.3

of

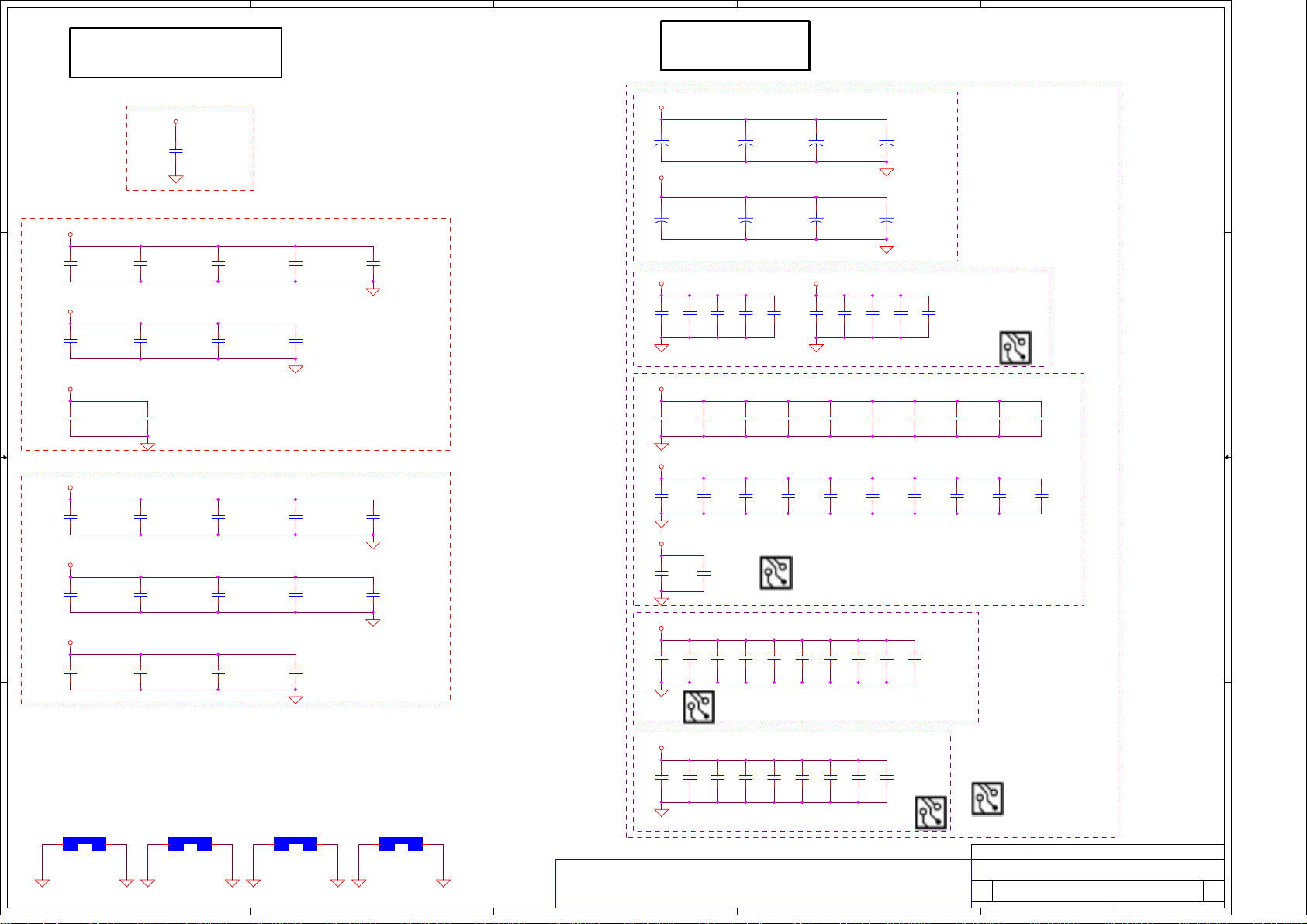

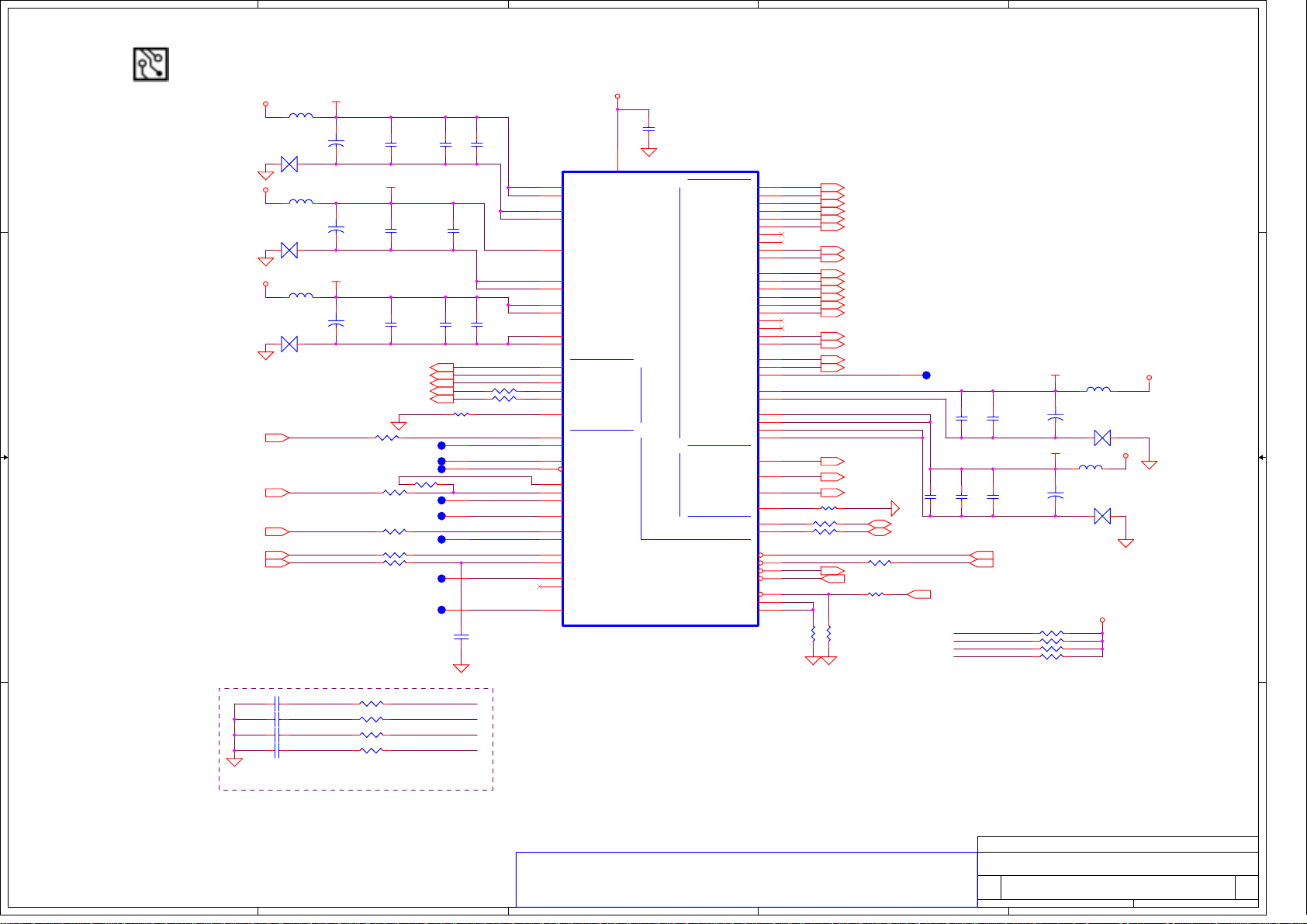

A

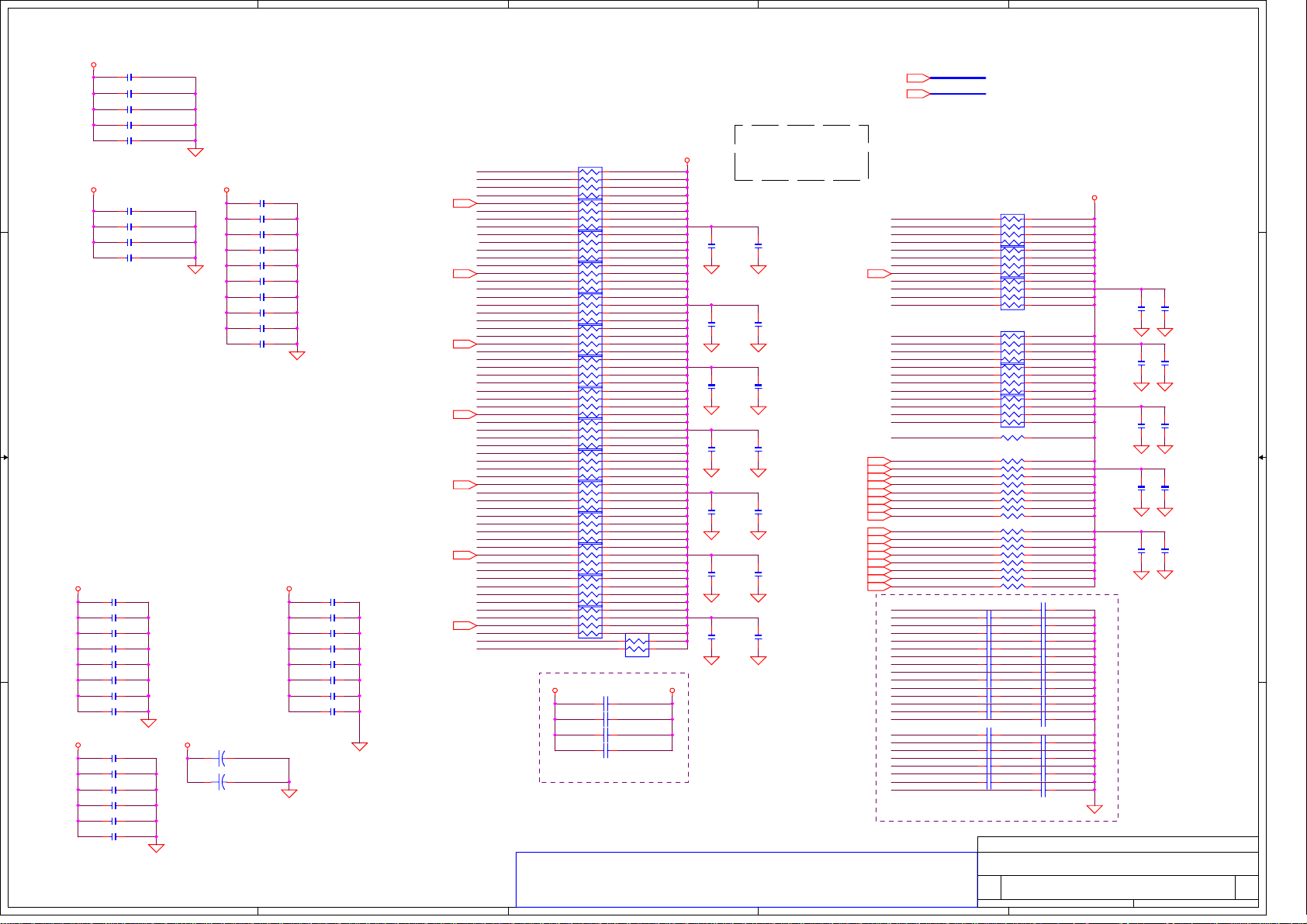

RP* place close to DIMM1

MAA_1 MAA1

MAA_0 MAA0

MAA_3

MAA_2

MAA_5 MAA5

MAA_7

MAA_6

MAA_9 MAA9

4 4

MAA_8 MAA8

MAA_12

MAA_11

MAA_14 MAA12

MAA_10 MAA10

RP93 4P2R_10

RP82

18

8P4R_10_0804

27

36

45

RP94

8P4R_10_0804

18

RP83

27

8P4R_10_0804

36

45

R468 10

MAA[0..14]

MAA3

MAA2

18

MAA4MAA_4

27

MAA7

36

MAA6

45

MAA14

MAA13

14

MAA11MAA_13

23

ATI RECOMEND

RP* PLACE CLOSE TO DIMM

MD4

MD5

MD0

MD1

MD6

RDQS0

MD2

8P4R_22_0804

MD3

MD12

MD8

MD7

MD9

MD13

MD14

MD10

RDQS1

3 3

2 2

1 1

MD11

MD20

MD16

MD15

MD17

RDQS2

MD18

8P4R_22_0804

MD22 MMD22

MD19

MD24

MD28

MD29

MD25

8P4R_22_0804

RDQS3

MD30

MD27

MD31

MD26

MD32

MD37

MD36

8P4R_22_0804

MD33

MD34

MD39

MD38

RDQS4

MD35

MD45

MD44

8P4R_22_0804

MD40

MD42

MD46

MD41

RDQS5

MD48

MD47

MD43

8P4R_22_0804

MD52

MD49

MD54

RDQS6

MD53

MD55

MD60

MD50

8P4R_22_0804

MD51

MD56

MD61

MD57

RDQS7

MD58

MD59

8P4R_22_0804

MD62

MD63

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RP99

8P4R_22_0804

1 8

RP87

2 7

3 6

4 5

8P4R_22_0804

1 8

2 7

3 6

4 5

RP97

8P4R_22_0804

1 8

2 7

3 6

RP85

4 5

8P4R_22_0804

RP95

RP84

8P4R_22_0804

1 8

RP92

2 7

3 6

4 5

RP81

8P4R_22_0804

1 8

RP91

2 7

3 6

4 5

8P4R_22_0804

1 8

RP90

2 7

3 6

4 5

8P4R_22_0804

1 8

RP89

2 7

3 6

4 5

RP78

8P4R_22_0804

RP88

1 8

2 7

3 6

4 5

R471 22

R470 22

R476 22

R475 22

R474 22

R473 22

R469 22

R472 22

A

1 8

2 7

3 6

4 5

1 8

RP98

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

RP96

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

RP80

2 7

3 6

4 5

1 8

RP79

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RP86

8P4R_22_0804

MMD4

MMD5

MMD0

MMD1

MMD6

DQS0

MMD2

MMD3

MMD12

MMD8

MMD7

MMD9

MMD13

MMD14

MMD10

DQS1

MMD11

MMD20

MMD16

MMD15

MMD21MD21

MMD17

DQS2

MMD18

MMD19

MMD23MD23

MMD24

MMD28

MMD29

MMD25

DQS3

MMD30

MMD27

MMD31

MMD26

MMD32

MMD37

MMD36

MMD33

MMD34

MMD39

MMD38

DQS4

MMD35

MMD45

MMD44

MMD40

MMD42

MMD46

MMD41

DQS5

MMD48

MMD47

MMD43

MMD52

MMD49

MMD54

DQS6

MMD53

MMD55

MMD60

MMD50

MMD51

MMD56

MMD61

MMD57

DQS7

MMD58

MMD59

MMD62

MMD63

DQM0RDQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DDR_CS#011,12

DDR_CS#111,12

DDR_CS#211,12

DDR_CS#311,12

10UF_10V_1206

B

MAA[0..14] 11,12

SRAS#11,12

SCAS#11,12

SWE#11,12

CKE11,12

+2.5V

CB92

B

DDR_CS#0

DDR_CS#1

DDR_CS#2

DDR_CS#3

C426

0.1UF

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

R_DDRCLK#0

R_DDRCLK#1

R_DDRCLK#2

R_DDRCLK#3

R_DDRCLK#4

R_DDRCLK#5

R_DDRCLK0

R_DDRCLK1

R_DDRCLK2

R_DDRCLK3

R_DDRCLK4

R_DDRCLK5

R454 10K

+2.5V

4P2R_0

4P2R_0

4P2R_0

4P2R_0

4P2R_0

4P2R_0

C434

0.1UF

RASCAS-

WECKE+

RCS#0

RCS#1

RCS#2

RCS#3

RP28

RP32

RP22

RP31

RP27

RP21

C433

0.1UF

R206 10

SRAS#

R208 10

SCAS#

R207 10

SWE#

R209 10

CKE

RP30 4P2R_10

1 4

2 3

1 4

2 3

RP29 4P2R_10

R_DDRCLK0

R_DDRCLK#0

R_DDRCLK1

R_DDRCLK#1

R_DDRCLK2

R_DDRCLK#2

R_DDRCLK3

R_DDRCLK#3

R_DDRCLK#4 DDRCLK#4

R_DDRCLK5

C437

0.1UF

AC21

AC20

AB20

AA20

AB19

AA19

AC19

AC18

AB18

AA18

AB21

AA17

AA16

AD23

AC22

AF8

AA9

AD12

AA13

AD16

AE20

W21

AA25

AD18

AF24

AE19

AF10

AD8

AC8

AE12

AB12

AE16

AF20

Y23

Y25

AB10

AE23

Y22

AB16

AE26

AB25

AC10

AD22

AA23

AC16

AD25

AC26

AE24

AD26

AF22

AC24

AF23

Y9

Y8

Y7

W20

V20

U20

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

2 3

1 4

1 4

2 3

C436

0.1UF

U3C

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_CKE

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_CK0#

DDR_CK1#

DDR_CK2#

DDR_CK3#

DDR_CK4#

DDR_CK5#

DDR_CK0

DDR_CK1

DDR_CK2

DDR_CK3

DDR_CK4

DDR_CK5

DDR_CS0#

DDR_CS1#

DDR_CS2#

DDR_CS3#

TESTMODE

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

ATI_U1

C421

0.1UF

C

PART 3 OF 5

DDRCLK0

DDRCLK#0

DDRCLK1

DDRCLK#1

DDRCLK2

DDRCLK#2

DDRCLK3

DDRCLK#3

DDRCLK4R_DDRCLK4

DDRCLK5

DDRCLK#5R_DDRCLK#5

C

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR SDRAM I/F (K7 MOBILE)

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

DDR_VREF

C424

0.1UF

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

VDD_MEM

AF6

AF7

AD9

AD10

AE7

AE8

AE9

AF9

AC7

AB9

AB11

AC11

AB8

AA11

AA10

AC9

AF11

AE11

AD13

AE13

AE10

AF12

AF13

AD14

AA12

AC12

AB13

AB14

AC13

AA15

AA14

AC14

AE14

AF15

AF16

AE17

AF14

AE15

AD17

AF17

AE18

AF19

AE21

AF21

AF18

AD19

AD21

AE22

AB23

AA22

V21

V23

W22

Y21

U21

U22

AB24

AA26

W25

V24

AB26

AA24

W26

W24

AD20

AD7

Y24

Y18

Y17

Y14

Y13

AF5

DDRCLK0 11

DDRCLK#0 11

DDRCLK1 11

DDRCLK#1 11

DDRCLK2 11

DDRCLK#2 11

DDRCLK3 11

DDRCLK#3 11

DDRCLK4 11

DDRCLK#4 11

DDRCLK5 11

DDRCLK#5 11

C432

0.1UF

C431

0.1UF

MMD0

MMD1

MMD2

MMD3

MMD4

MMD5

MMD6

MMD7

MMD8

MMD9

MMD10

MMD11

MMD12

MMD13

MMD14

MMD15

MMD16

MMD17

MMD18

MMD19

MMD20

MMD21

MMD22

MMD23

MMD24

MMD25

MMD26

MMD27

MMD28

MMD29

MMD30

MMD31

MMD32

MMD33

MMD34

MMD35

MMD36

MMD37

MMD38

MMD39

MMD40

MMD41

MMD42

MMD43

MMD44

MMD45

MMD46

MMD47

MMD48

MMD49

MMD50

MMD51

MMD52

MMD53

MMD54

MMD55

MMD56

MMD57

MMD58

MMD59

MMD60

MMD61

MMD62

MMD63

D

12

C229

+

150UF_D2_6.3V

CAP-D_E_TAN

MD[0..63]

RDQM[0..7]

RDQS[0..7]

Place near SODIMM1.

+2.5V

12

C231

0.1UF

12

C232

0.1UF

MD[0..63] 11,12

RDQM[0..7] 11,12

RDQS[0..7] 11,12

12

C228

0.1UF

12

C227

0.1UF

E

12

12

C234

C257

0.1UF

0.1UF

Place near SODIMM2

+2.5V

12

12

C230

+

@150UF_D2_6.3V

CAP-D_E_TAN

C435

0.1UF

+2.5V

+2.5V

C150

@0.1UF

NB_DDR_VREF

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C430

C429

0.1UF

0.1UF

12

C163

+

150UF_D2_6.3V

CAP-D_E_TAN

R285

1K_ 1%

R279

1K_ 1%

C190

0.1UF

R280 @0_0603

C183

0.1UF

PLACE RPACKS CLOSE TO

1ST SO-DIMM

C428

0.1UF

D

12

C467

0.1UF

Compal Electronics, Inc.

Title

ATI MOBILITY U1_DDR I/F

Size Document Number Rev

LA-1481 M/B

Date: Sheet

C466

0.1UF

SDREF 11,35

!"#, $%

12

C465

0.1UF

14, 2002

12

C464

0.1UF

12

12

C462

C461

0.1UF

0.1UF

E

12

12

C226

C233

0.1UF

0.1UF

12

12

C463

C468

0.1UF

0.1UF

747

0.5

of

A

AD[0..31]10,16,20,21,22,25,32

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

PCI_ACT_REQ#

PCI_SBREQ#

PCI_SBGNT#

REQ#0

REQ#1

REQ#2

REQ#3

GNT#0

GNT#1

GNT#2

GNT#3

C136

0.1UF

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

4 4

CBE#010,16,20,21,22,25

CBE#116,20,21,22,25

CBE#216,20,21,22,25

DEVSEL#16,20,21,22,25

PCI_ACT_REQ#10,17

PCI_SBREQ#16

PCI_SBGNT#16

+3VS

1 2

1 2

CBE#310,16,20,21,22,25

PAR16,20,21,22,25

FRAME#16,20,21,22,25

IRDY#16,20,21,22,25

TRDY#16,20,21,22,25

PIRQA#16,22

STOP#16,20,21,22,25

SERR#16,20,22,25

REQ#021

REQ#125

REQ#222

REQ#320

GNT#021

GNT#125

GNT#222

GNT#320

+3VS+3VS

+3VS

3 3

2 2

8P4R_8.2K_0804

GNT#3

REQ#3

GNT#2

REQ#2

8P4R_8.2K_0804

GNT#1

REQ#1

REQ#0

GNT#0

PCI_SBGNT#

PCI_SBREQ#

RP77

4 5

3 6

2 7

1 8

RP14

4 5

3 6

2 7

1 8

R424 8.2K

R136 8.2K

U3B

AA7

PCI_AD0

AA8

PCI_AD1

AB7

PCI_AD2

AE5

PCI_AD3

AF4

PCI_AD4

AD5

PCI_AD5

AE4

PCI_AD6

AD4

PCI_AD7

AF3

PCI_AD8

AE1

PCI_AD9

AD2

PCI_AD10

AC3

PCI_AD11

AD1

PCI_AD12

AC6

PCI_AD13

AC5

PCI_AD14

AC2

PCI_AD15

AA2

PCI_AD16

AA1

PCI_AD17

Y2

PCI_AD18

Y6

PCI_AD19

Y5

PCI_AD20

Y4

PCI_AD21

W6

PCI_AD22

W5

PCI_AD23

W4

PCI_AD24

W3

PCI_AD25

W2

PCI_AD26

V6

PCI_AD27

V5

PCI_AD28

V4

PCI_AD29

W1

PCI_AD30

V3

PCI_AD31

AE3

PCI_CBE0#

AC1

PCI_CBE1#

AA3

PCI_CBE2#

Y1

PCI_CBE3#

AB3

PCI_PAR

AB1

PCI_FRAME#

AA4

PCI_IRDY#

AA5

PCI_TRDY#

T5

INTA#

AB4

PCI_DEVSEL#

AB6

PCI_STOP#

AB2

PCI_SERR#

R6

PCI_ACT_REQ#

R2

PCI_SBREQ#

R4

PCI_SBGNT#

V2

PCI_REQ0#

U4

PCI_REQ1#

U6

PCI_REQ2#

T4

PCI_REQ3#/PCI_CLK3

V1

PCI_GNT0#

U5

PCI_GNT1#

T2

PCI_GNT2#

T6

PCI_GNT3#/PCI_CLK4

T1

VDD_5V

AB17

NC

AC15

NC

ATI_U1

B

PART 2 OF 5

VID0/TST_IN0

VID1/TST_IN1

VID2/TST_IN2

VID3/TST_IN3

VID4/TST_IN4

VID5/TST_IN5

VID6/TST_IN6

VID7/TST_IN7

XVID0

XVID1

XVID2

XVID3/TESTCLK1

XVID4

XVID5/TST_ADDR

XVID6/TST_STB

XVID7/TST_WR

VVSYNC/TST_OUT14

VHREF/TST_OUT15

VPCLK0/TST_OUT13

TMDS_D0/TST_OUT12

TMDS_D1/TST_OUT10

TMDS_D2/TST_OUT9

TMDS_D3/TST_OUT8

TMDS_D4/TST_OUT6

TMDS_D5/TST_OUT7

TMDS_D6/TST_OUT5

TMDS_D7/TST_OUT4

TMDS_D8/TST_OUT2

TMDS_D9/TST_OUT3

TMDS_D10/TST_OUT1

TMDS_D11/TST_OUT0

TMDS_DE/TST_OUT11

TMDS_VSYNC/TCK

TMDS_HSYNC/TMS

TMDS_SCL

TMDS_SDA/TDI

PCI/ZV/TMDS (K7 MOBILE)

TMDS_IDCK-

TMDS_IDCK+

TMDS_LCDCNTL0/GPIO8

TMDS_LCDCNTL1/GPIO9

TMDS_LCDCNTL2/GPIO10

TMDS_VREF

TMDS_VOLT_DET

TMDS_HPD

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

CLK27M

LVDS_SSIN

LVDS_SSOUT

NB_VID0

J4

NB_VID1

F4

NB_VID2

E6

NB_VID3

M4

NB_VID4

F5

NB_VID5

G4

NB_VID6

G5

NB_VID7

K5

XVID0

L5

XVID1

J6

XVID2

H6

XVID3

K4

XVID4

K6

XVID5

J5

XVID6

L4

XVID7

G6

VVSYNC

L6

VHREF

M5

VPCLK0

H5

J2

K3

K1

K2

L1

L2

L3

N1

N2

N3

P1

P2

J1

H2

J3

R3

R1

M2

M1

D3

E2

G2

R5

R417 @4.7K

E4

G1

E1

RSV

F3

RSV

F2

RSV

H4

RSV

P3

N4

N6

P4

P6

M6

N5

P5

CLK27M

C1

C2

R414 SS@22

D6

INSTALL IF CLK NOT POPULATED

R418

10K

+3VS

DNI

+3VS

NB_TMDS_VREF

C402

0.1UF

KEEP CLOSE TO TMDS VREF PIN

LVDS_SSIN

LVDS_SSOUT

R77

SS@10K

C

R399

SS@10K

R400

@10K

R426

1K_1%

R425

1K_1%

3

2

+3VS

12

12

SS@10K

X2

OUT

GND

OSC_27MHz

R385

VDD

+3VS

12

12

SS@10

C49

SS@22PF

ST

C60

SS@0.1UF

R398

SS@10K

R32

R34

10K_1%

4

1

12

1

6

1 2

12

+3VS

12

12

+3VS

L22

SS@FBM-L11-201209-221

C50

SS@10UF_10V_0805

2

U25

VDD

X1/CLK

CLK

SDS0

S1

LEE

GND

3

SS@SM560_SO-8

LVDS SPREAD SPECTRUM

R415

1 2

SS@10

Close to U49

XVID7

NB_VID1

NB_VID4

NB_VID2

XVID0

XVID6

NB_VID7

XVID3

VPCLK0

XVID2

NB_VID5

NB_VID6

XVID4

XVID1

NB_VID0

XVID5

VHREF

NB_VID3

VVSYNC

C43

0.1UF_16V

12

4

87

5

LVDS_SSOUT

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

D

+3VS

12

R19

@0

LVDS_SSIN

@10

Close to U49

12

R5

@0

RP5

8P4R_10K_0804

RP12

8P4R_10K_0804

RP10

8P4R_10K_0804

RP11

8P4R_10K_0804

RP13

8P4R_10K_0804

R10

12

C21

1 2

@22PF

+1.8VS

+3VS

K10

K11

K12

K15

K16

K17

L10

L11

L12

L15

L16

L17

M10

M11

M12

M15

M16

M17

R10

R11

R12

R15

R16

R17

T10

T11

T12

T15

T16

T17

U10

U11

U12

U15

U16

U17

G10

G11

W7

B15

C15

D15

E15

F15

G15

T13

T14

T20

T24

U13

U14

Y10

Y11

Y12

Y15

Y16

Y19

Y20

C7

T3

U7

V7

Y3

G7

K7

L7

H3

P7

U3E

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_3.3V

VDD_3.3V

VDD_3.3V

VDD_3.3V

VDD_3.3V

VDD_3.3V

VDD_3.3V

VDD_3.3V

VDD_VID

VDD_VID

VDD_VID

VDD_TMDS

VDD_TMDS

NC

NC

NC

NC

NC

NC

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

ATI_U1

E

PART 5 OF 5

A1

GND

A26

GND

AA6

GND

AA21

GND

AB5

GND

AB15

GND

AB22

GND

AC23

GND

AC4

GND

AC17

GND

AD3

GND

AD11

GND

AD15

GND

AD24

GND

AE2

GND

AE25

GND

AF1

GND

AF2

GND

AF25

GND

AF26

GND

B1

GND

B2

GND

B25

GND

B26

GND

C3

GND

C24

GND

D4

GND

D23

GND

E5

GND

E22

GND

F6

GND

F21

GND

G8

GND

G9

GND

G12

GND

G13

GND

G14

GND

G19

GND

G20

GND

H7

GND

J7

GND

K13

GND

K14

GND

K20

GND

L13

GND

L14

GND

L20

GND

POWER (K7 MOBILE)

M3

GND

M7

GND

M13

GND

M14

GND

M24

GND

N7

GND

N10

GND

N11

GND

N12

GND

N13

GND

N14

GND

N15

GND

N16

GND

N17

GND

P10

GND

P11

GND

P12

GND

P13

GND

P14

GND

P15

GND

P16

GND

P17

GND

R7

GND

R13

GND

R14

GND

R20

GND

T7

GND

+1.8VS

C386

0.1UF

C401

0.1UF

C390

0.1UF

C400

0.1UF

1 1

CB90

10UF_10V_1206

CB91

10UF_10V_1206

C388

0.1UF

C418

0.1UF

A

C389

0.1UF

C391

0.1UF

C411

0.1UF

C398

0.1UF

C420

0.1UF

C407

0.1UF

C409

0.1UF

C397

0.1UF

C410

0.1UF

C399

0.1UF

C422

0.1UF

C408

0.1UF

B

+3VS

CB7

10UF_10V_1206

C419

C427

0.1UF

C425

0.1UF

C417

0.1UF

C369

0.1UF

0.1UF

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C406

C382

C371

C376

0.1UF

C359

0.1UF

C423

@0.1UF

C393

@0.1UF

D

C370

0.1UF

0.1UF

0.1UF

C

0.1UF

Compal Electronics, Inc.

Title

ATI MOBILITY U1_PCI BUS I/F

Size Document Number Rev

LA-1481 M/B

!"#, $%

Date: Sheet

14, 2002

847

E

of

0.3

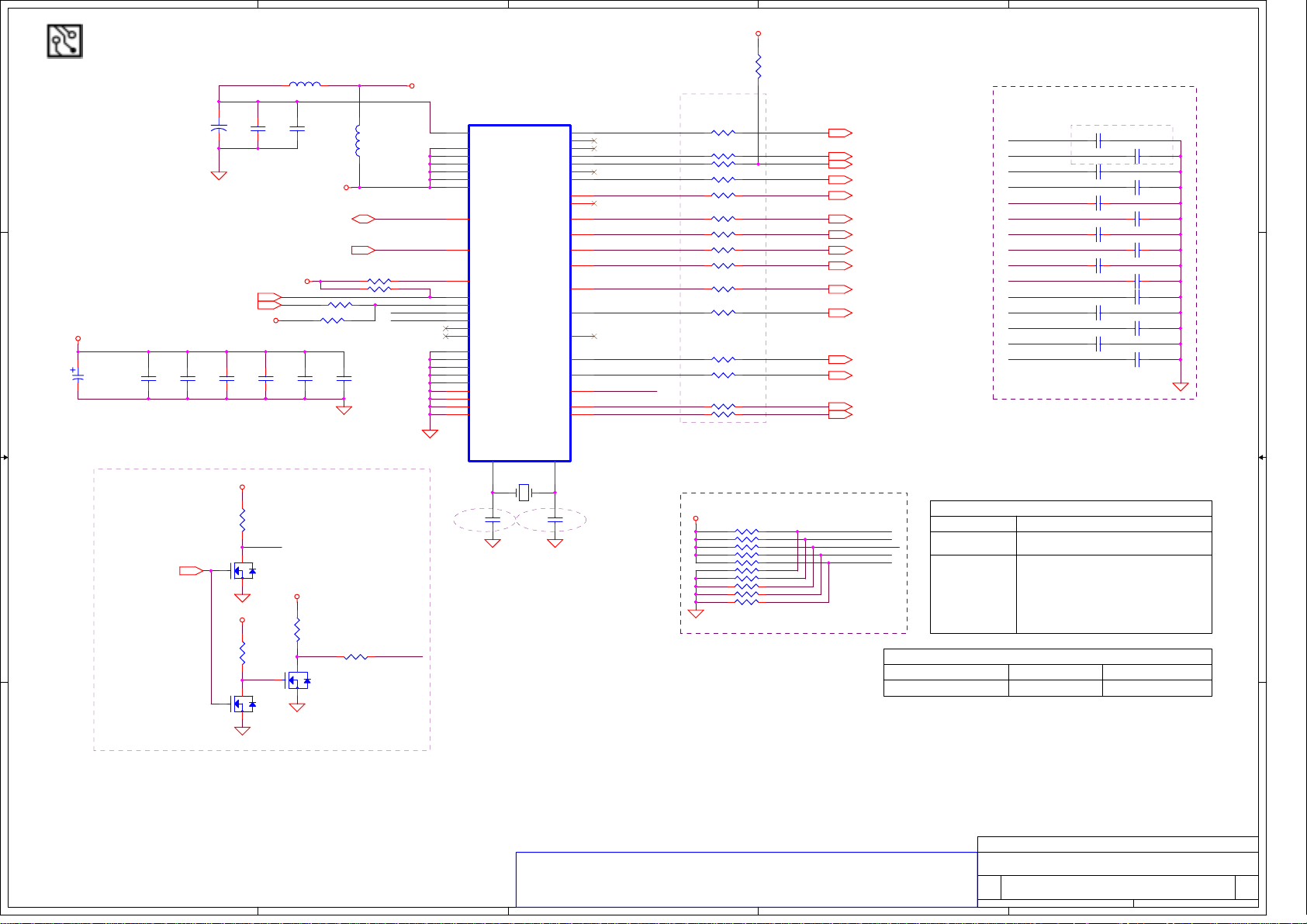

A

B

C

D

E

Note: AVSSQ & AVS SN requ ire separate d irect con nectio ns to G ND plan e ( se p a ra te v i as ).

Note: A2VSSQ & A2VSSN require separate direct connections to GND plane (separate vias).

+1.8VS

4 4

3 3

REFCLK1_NB13

CPUCLK_NB_EXT13

PCLK_NB_EXT13

AGPCLK_EXT13

2 2

SDCLK_NB_EXT13

HB-1M2012-121JT

+2.5VS A2VDD

HB-1M2012-121JT

AVDD

L18

1 2

RED14

BLUE14

R29 499_1%

TP14

TP3

TP2

TP1

TP5

TP12

TP4

TP11

C53

C61

0.1UF

0.1UF

C59

0.1UF

C350

C347

0.1UF

0.1UF

R405 0

1 2

R30 0

1 2

1

TST_CPUCLK

1

TST_CPUCLK#

1

SYS_FBCLKOUT

R409 @22

SYS_FBCLKIN

HCLKOUT

1

PCI_CLKF

1

PCLK_NB_EXT_RPCLK_NB_EXT

PCICLK_BUF

1

SDCLK_NB_EXT_R

TST_UCLK48M

1

TST_REFCLK1_SB

1

12

C346

@100PF

CB15

+

AVSS

A2VSS

PLLVSS

10UF_10V_1206

CB14

+

10UF_10V_1206

PLVDD+1.8VS

CB86

+

10UF_10V_1206

R412 0

R410 0

R406 0

SHORT

JOPEN1

L17

1 2

SHORT

JOPEN2

L47

1 2

5.6_0805

SHORT

JOPEN5

CPUCLK_NB_EXT

AGPCLK_EXT AGPCLK_EXT_R

SDCLK_NB_EXT

1UF_10V_0603

1UF_10V_0603

1 2

R27 0

1 2

R408 0

1 2

1 2

1 2

C48

C47

1UF_10V_0603

C344

GREEN14

VSYNC14

HSYNC14

1 2

B11

C9

B13

F11

C11

A8

D10

C12

E13

D13

F13

A11

A12

A13

D12

E12

B12

OSC_NBREFCLK1_NB

A18

B17

D16

A15

C16

D14

C13

B14

A14

E14

C14

B9

A9

U2

U1

+2.5VS

C55

0.1UF

U3D

AVDD

A2VDDQ

AVSSQ

AVSSN

A2VDD

A2VSSN

A2VSSQ

PLLVDD0

PLLVDD1

PLLVSS0

PLLVSS1

RED

GREEN

BLUE

DACVSYNC

DACHSYNC

RSET

XTLIN

XTLOUT

SYSCLK

SYSCLK#

SYS_FBCLKOUT

SYS_FBCLKIN/HCLKIN

HCLKOUT

PCI_CLKF

PCI_CLK1

PCI_CLK2

AGP_FBCLKIN/AGP_CLKIN

AGP_FBCLKOUT/EXT_MEM_CLK

USBCLK

APICCLK

OSC

ATI_U1

A17

PART 4 OF 5

VDD_2.5V

CRT

CLK.

Remove if testing CLK_RUN# using SB GPIO

CLK, DISPLAY (K7 MOBILE)

GEN.

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXCLK_UN

TXCLK_UP

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

TXCLK_LN

TXCLK_LP

LVDS

LVDS_DIGON/TDO

LVDS_BLON#

LVDS_BIASON

LPVDD

LPVSS

LVDDR

LVDDR

LVSSR

LVSSR

C_R

Y_G

COMP_B

SVID

R2SET

DACSCL

DACSDA

PCICLK_STP#

CPUCLK_STP#

AGP_BUSY#

AGP_STP#

CLK_RUN#

RSV

RSV

WAIT CHECK ATI LVDS EVEN/ODD DEFINE

D7

D8

B7

A7

E8

E9

C8

B8

D9

E10

B3

A3

B4

A4

B5

A5

C5

C6

B6

A6

D1

D2

E3

F9

F10

E7

F7

F8

A2

A10

B10

C10

R413 715_1%_0603

D11

R31 0

E11

R404 0

F12

PCICLK_STP#

U3

CPU_STP#

F14

AGPBUSY#

C4

AGPSTP#

D5

F1

G3

H1

R96

10K

1 2

1 2

TXOUT_U0- 15

TXOUT_U0+ 15

TXOUT_U1- 15

TXOUT_U1+ 15

TXOUT_U2- 15

TXOUT_U2+ 15

TXCLKOUT_U- 15

TXCLKOUT_U+ 15

TXOUT_L0- 15

TXOUT_L0+ 15

TXOUT_L1- 15

TXOUT_L1+ 15

TXOUT_L2- 15

TXOUT_L2+ 15

TXCLKOUT_L- 15

TXCLKOUT_L+ 15

LCD_DIGON 15,27

LVDS_BLON# 15

CRMA 14

LUMA 14

COMPS 14

R403 @0

1 2

AGP_BUSY# 16

AGP_STP# 16

R90 @0

R83

10K

1

TP13

C349

C343

0.1UF

1UF_10V_0603

C352

0.1UF

DDCCLK 14,15

DDCDATA 14,15

CPUCLK_STP#

PM_CLKRUN# 16,18,22,25,27

DNI

Install if testing CLK_RUN# using SB GPIO

AGPBUSY#

AGPSTP#

PCICLK_STP#

CPU_STP#

C351

C353

1UF_10V_0603

0.1UF

PCICLK_STP# 13,17

CPUCLK_STP# 13,17

R416 4.7K

R60 4.7K

R178 10K

R21 10K

LVDD

+

LVDDR

+

1 2

1 2

1 2

1 2

L46

1 2

5.6_0805

CB85

10UF_10V_1206

LVSS

L48

1 2

HB-1M2012-121JT

CB87

10UF_10V_1206

LVSSR

SHORT

JOPEN7

+3VS

JOPEN6

SHORT

+1.8VS

+1.8VS

C341 22PF

1 2

C342 22PF

1 2

C348 22PF

1 2

C345 22PF

1 2

EMI request

R401 @10

1 2

R402 @10

1 2

R411 @10

1 2

R407 @10

1 2

SYS_FBCLKIN

PCLK_NB_EXT_R

AGPCLK_EXT_R

SDCLK_NB_EXT_R

LAYOUT:Close to NB(U5)

1 1

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

A

B

C

D

Title

ATI MOBILITY U1_CLK GEN/LVDS

Size Document Number Rev

LA-1481 M/B

!"#, $%

Date: Sheet

14, 2002

947

E

of

0.3

A

B

C

D

E

R154 @10K_0603

AD15

AD31

R61 3.3K_0603

1 2

4 4

FSB_100/133#4,13

AD30

2

@2N7002

1 2

R40 10K_0603

1 2

R64 @4.7K_0603

AD29

AD28

AD27

3 3

AD26

AD25

AD24

1 2

R37 5.6K_0603

13

Q6

1 2

R39 @10K_0603

1 2

R63 4.7K_0603

1 2

R38 @10K_0603

1 2

R62 4.7K_0603

1 2

R42 @10K_0603

1 2

R66 4.7K_0603

1 2

R43 @10K_0603

1 2

R67 4.7K_0603

R41 @10K_0603

R65 4.7K_0603

R45 10K_0603

R69 @4.7K_0603

ATI 5/27

1 2

1 2

1 2

1 2

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

AD[31..30] : CLK SPEED

DEFAULT

00: 66 MHZ (1:1)

01: 100 MHZ (1.5:1)

10: 166MHZ (2.5:1)

11: 133 MHZ (2:1)

AD29: STRAP SET SELECTION

DEFAULT

0: USE FULL STRAPPING SET

1: USE REDUCED STRAPPING SET

AD28: SPREAD SPECTRUM ENABLE

0: DISABLE

DEFAULT

1: ENABLE

AD[27..26] : CPU S2K BUS LENGTH

DEFAULT

00: SHORT, NON-S2K INTERFACE

01: SINGLE S2K INTERFACE, CLOSE

10: FAR S2K INTERFACE, DUAL CPU

11: FARTHEST S2K INTERFACE, DUAL CPU

AD25: RESERVED

DEFAULT

0: ???

1: ???

AD24: INCLK_DELAY_ENABLE

DEFAULT

0: DISABLE

1: ENABLE

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

R155 4.7K_0603

R437 @10K_0603

R438 4.7K_0603

R435 @10K_0603

R436 4.7K_0603

R160 @10K_0603

1 2

R161 4.7K_0603

1 2

R147 @10K_0603

1 2

R148 4.7K_0603

1 2

R166 @10K_0603

R167 4.7K_0603

R174 @10K_0603

R175 4.7K_0603

R193 10K_0603

R194 @4.7K_0603

R103 10K_0603

1 2

R102 10K_0603

1 2

R117 10K_0603

1 2

R118 10K_0603

1 2

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

PID3 15,28

PID2 15,28

PID1 15,28

PID0 15,28

AD[15..14] :S2K/SLOT1 SELECT & CALIBRATION

DEFAULT

00: S2K INTERFACE (MOBILE)

01: S2K INTERFACE (DESKTOP)

10: SLOT1 INTERFACE (MOBILE)

11: SLOT1 INTERFACE (DESKTOP)

AD13: RESERVED

DEFAULT

0: ???

1: ???

AD[12] : FLAT PANEL ID MSB

ID4

AD11 : INTERAL CLOCK GENERATOR

0: DISABLE

DEFAULT 1: ENABLE

AD[10..9] : RESERVED[4..3]

DEFAULT

0: ???

1: ???

DEFAULT

0: ???

1: ???

AD8: ENABLE K7 OUTCLK DELAY

0: DISABLE

1: ENABLEDEFAULT

AD[7..4] : FLAT PANEL ID

DEBUG MODE ONLY

1 2

AD23

2 2

AD22

AD21

1 1

AD[0..31]8,16,20,21,22,25,32

A

R44 @10K_0603

1 2

R68 4.7K_0603

1 2

R47 @10K_0603

1 2

R71 4.7K_0603

1 2

R48 @10K_0603

1 2

R72 4.7K_0603

1 2

R49 @10K_0603

1 2

R73 4.7K_0603

AD[0..31]

+3VS

+3VS

+3VS

+3VS

B

AD[23..21] : SKEW ADJUST

DEFAULT

AD20: PCICLK EXPANSION

DEFAULT

R439 @10K_0603

000: ??? DETERMINE DURING

BRING-UP & FIX FOR

PRODUCTION

AD3

AD2

R440 4.7K_0603

R431 @10K_0603

R432 4.7K_0603

R429 @10K_0603

AD1

R430 4.7K_0603

R433 @10K_0603

0: REQ/GNT3 USED AS REQ/GNT

1: REQ/GNT3 USED AS PCICLKS

AD0AD20

ATI 6/19

R434 4.7K_0603

R46 10K_0603

CBE#38,16,20,21,22,25

CBE#3

R70 @4.7K_0603

R183 @10K_0603

CBE#08,16,20,21,22,25

PCI_ACT_REQ#8,17

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

CBE#0

PCI_ACT_REQ#

R184 4.7K_0603

R428 @10K_0603

R427 2.2K_0603

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

D

AD3: PCI66 MODE

0: 33MHzDEFAULT

1: 66MHz

AD2: CAL DEFAULTS FOR CPU

0: DISABLEDEFAULT

1: ENABLE

AD1: RESERVED

0: ???DEFAULT

1: ???

AD0 : INTERAL GRAPHICS ENABLE

DEFAULT 0: IF NO EXTERNAL, USE INTERNAL

DEFAULT

DEFAULT

DEFAULT

1: USE INTERNAL BY DEFAULT

PCI_CBE#3 : PRODUCTION TEST

0: SHORT TIMERS FOR PROD TEST

1: NORMAL OPERATION

PCI_CBE#0 : EXTERNAL SIP ROM ENABLE

0: DISABLE

1: ENABLE

PCI_ACT_REQ# : INTERNAL CLOCK GENERATOR(A21 ASIC)

0: DISABLE

1: ENABLE

Compal Electronics, Inc.

Title

ATI MOBILITY U1_STRAP IN PUT

Size Document Number Rev

LA-1481 M/B

!"#, $%

Date: Sheet

14, 2002

E

10 47

of

0.2

A

B

C

D

E

+2.5V

JP23

4 4

MAA_11

MAA_12

MAA_13

MAA_14

DDR_CS#27,12

DDR_CS#37,12

RDQM[0..7]7,12

3 3

SWE#7,12

SCAS#7,12

SRAS#7,12

CKE7,12

DDRCLK37

DDRCLK#37

DDRCLK47

DDRCLK#47

DDRCLK57

DDRCLK#57

RDQS07,12

RDQS17,12

RDQS27,12

RDQS37,12

RDQS47,12

RDQS57,12

RDQS67,12

2 2

RDQS77,12

SMB_CK_DAT13,17

SMB_CK_CLK13,17

+3VS

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA14

MAA11

MAA12

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

SWE#

SCAS#

SRAS#

CKE CKE

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

SMB_CK_DAT

SMB_CK_CLK

R482 4.7K

1 2

MVREF_DIM2

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2