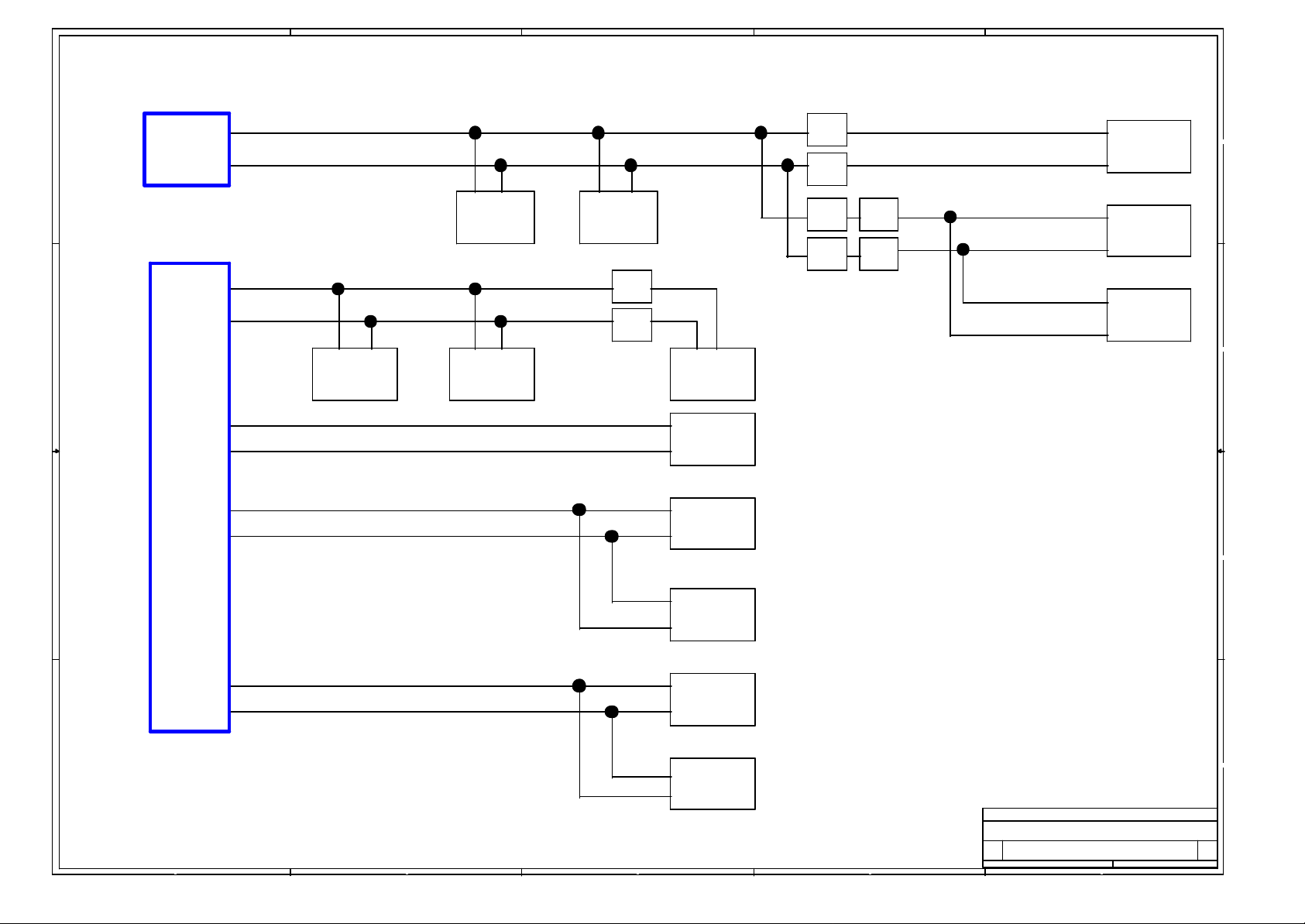

Acer LA-1361 Schematics

5

D D

4

3

2

1

C C

uFCPGA Northwood

2002-10-23

B B

Rev:X025

A A

Lindbergh Schematic Document

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

ADQ00/LA-1351

1 50Wednesday, October 23, 2002

1

X025

5

Compal confidential

4

3

2

1

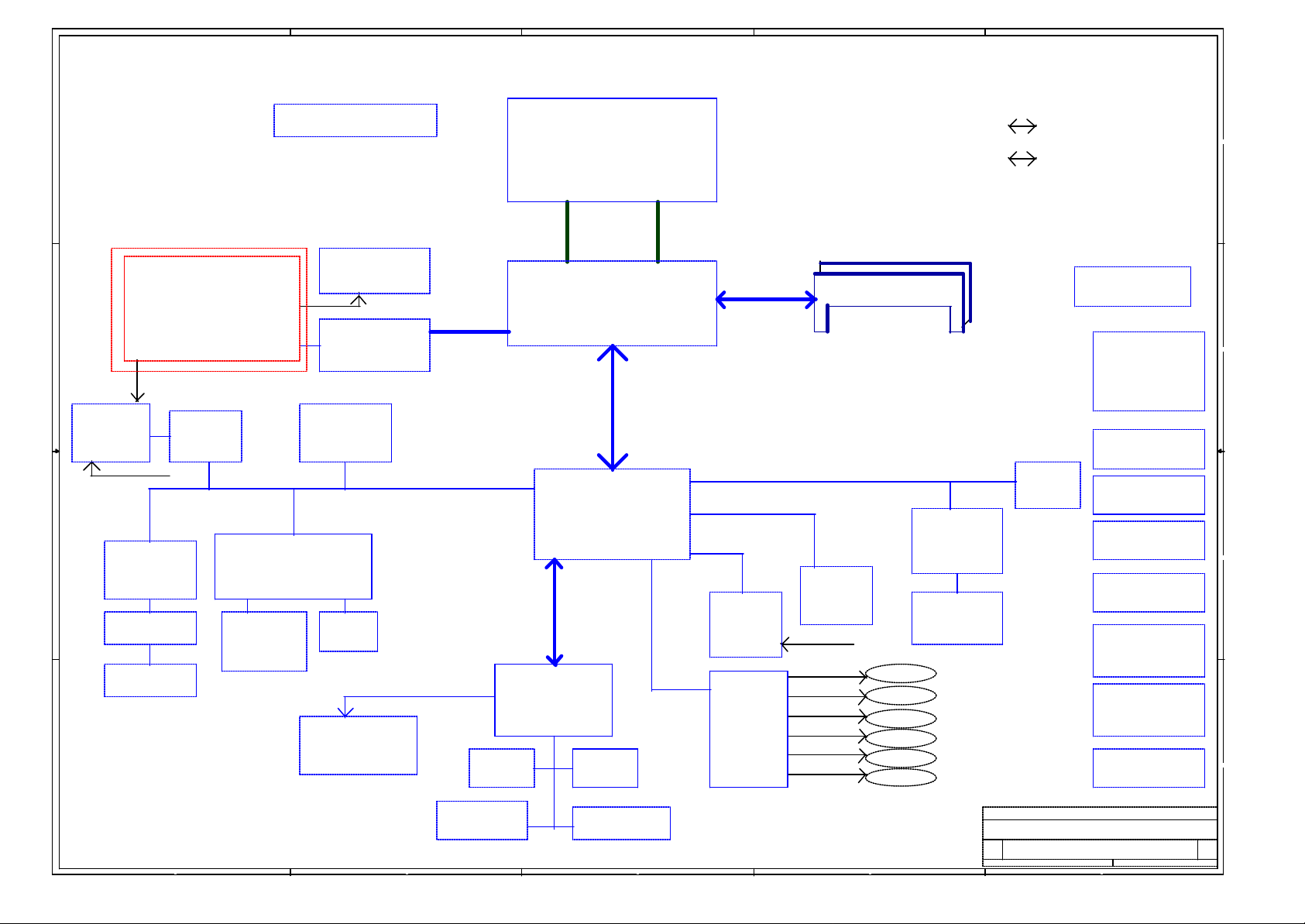

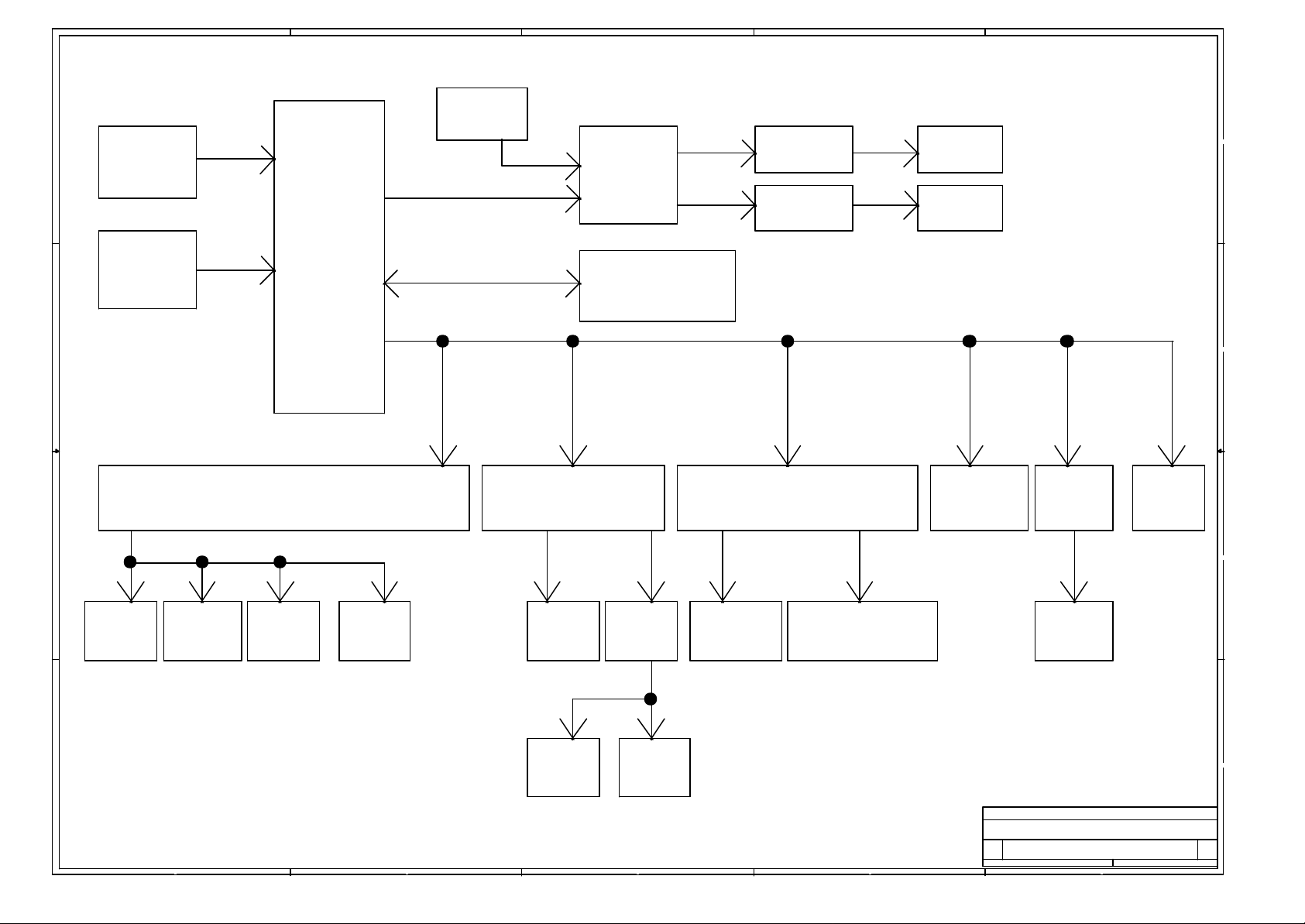

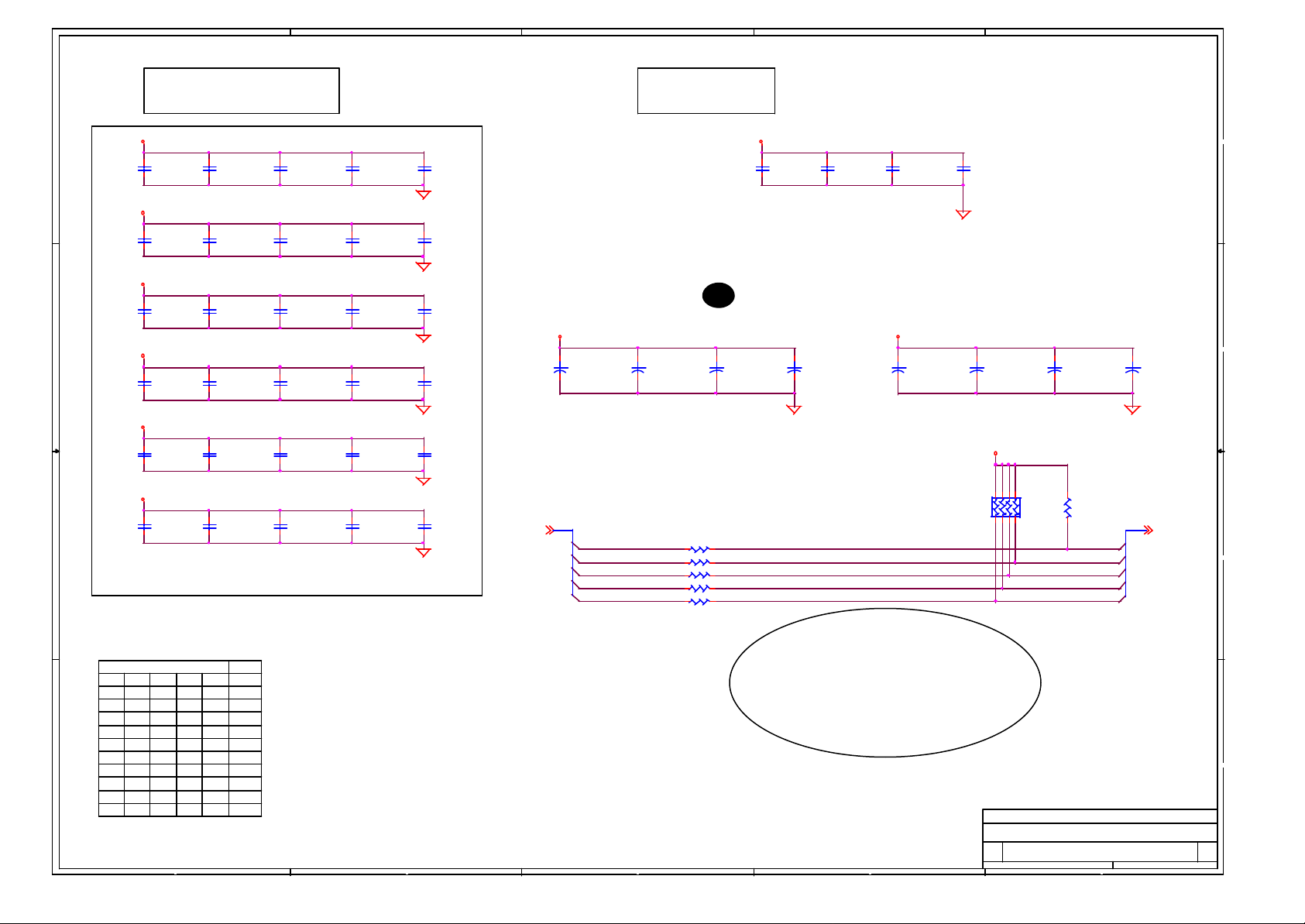

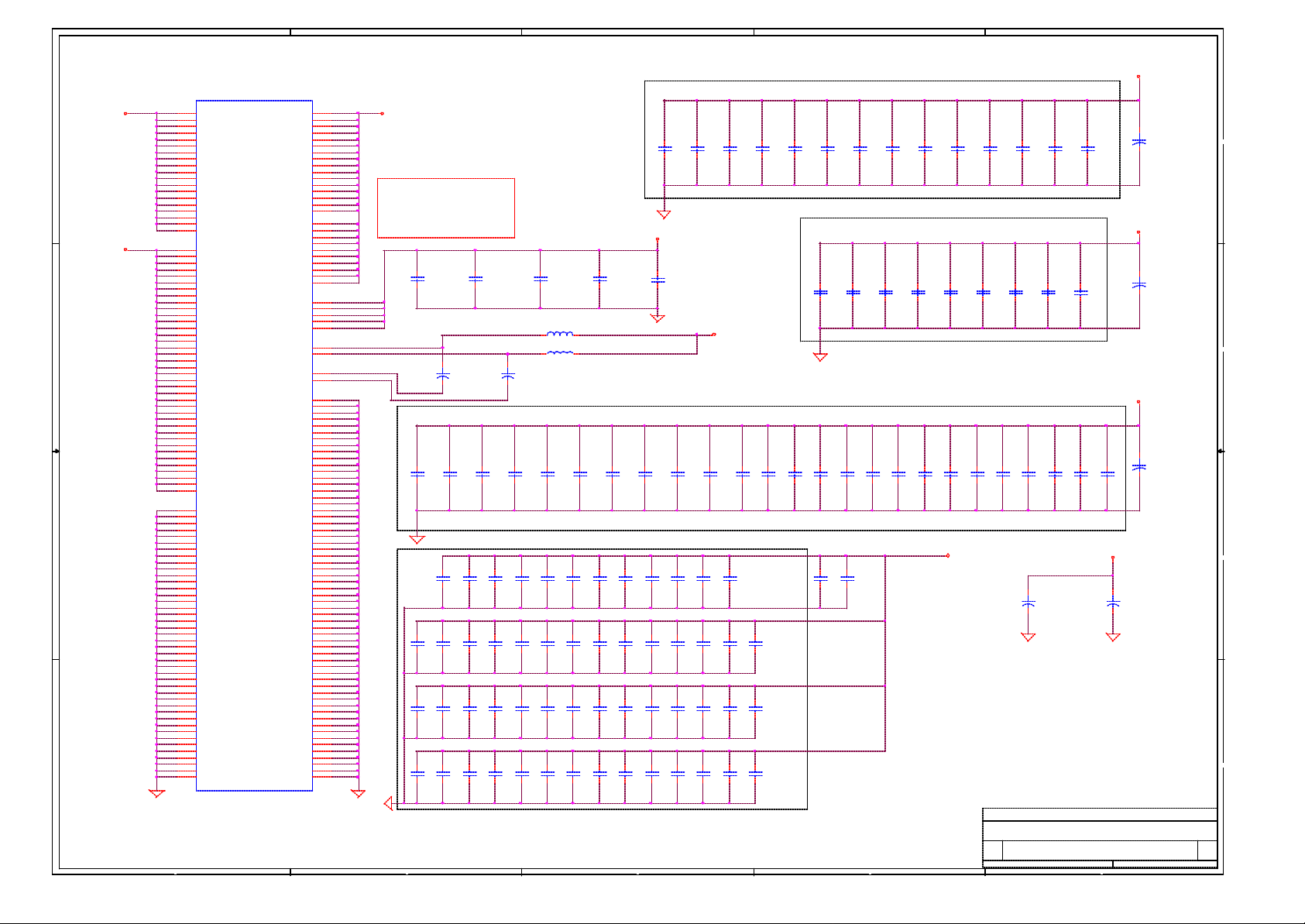

Block Diagram

ADM1032 Thermal sensor

D D

page 7

Mobile Northwood

uFCBGA/uFCPGA CPU

page 7,8

HA#(3..31)

VGA

Board

NV17/ATI M9

C C

CRT CONN.

& TV-OUT

page 17

AGP CONN.

page 16

AGP4X(1.5V)

System Bus

400MHz

Brookdale-M

MCH-M

593 FC-BGA

HD#(0..63)

page

11,12,13,

Memory

BUS(DDR)

DVI port

HUB Link

DOCKING

PORT

PAGE 33

USB

port5

B B

NIC

5705M/4401

DOCKING

BUFFER

PAGE 32

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

page 27

CardBus Controller

PCI4510/PC7510

MINI PCI

page 31

PCI BUS

3.3V 33MHz

page 29

1.8V

66Mhz

266MB/S

ICH4-M

421 BGA

page

18,19,20,21

3.3V 24.576MHz

3.3V ATA100

ATA100

CDROM

LPC BUS

COM

3.3V 33MHz

Macallen

LPC to X-BUS

& Super I/O

page

34,35

LPT

USB

FDD

USB2.0

page 37page 38

Transformer

page 28

RJ45

page 28

1394, Smart

card

page30

Slot 0

page30

X BUS

SST39VF080

A A

page 36

2.5V 266MHz

PC2100

page 21

page 25

page 26

ADQ00(Lindbergh)

ADQ10(Baekland)

SO-DIMM X2

BANK 0, 1, 2, 3

ATA100

HDD

page 21

USB

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

page 14,15

BACK

BT

BACK

DOG

MOD

DOCK

AC-LINK

AC97

Codec

STAC9750

page 23

AMP& Phone

Jack

page 24

Inspiron

Latitude

Fan Control

MDC

page 26

page 10

Clock Generator

CK408

page 6

DC IN

BATT

IN

1.5V/1.8V

1.25V/2.5V

page

42

page

43

page

44

page

45

VCORE

page 46

5V/3.3V

MAX1632

CHARGER

MAX1645

page 47

page

48,49

Touch Pad

page 36

5

4

Int.KBD

page 36

3

Title

Size Document Number Rev

2

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

ADQ00/LA-1351

2 50Wednesday, October 23, 2002

1

X025

5

4

3

2

1

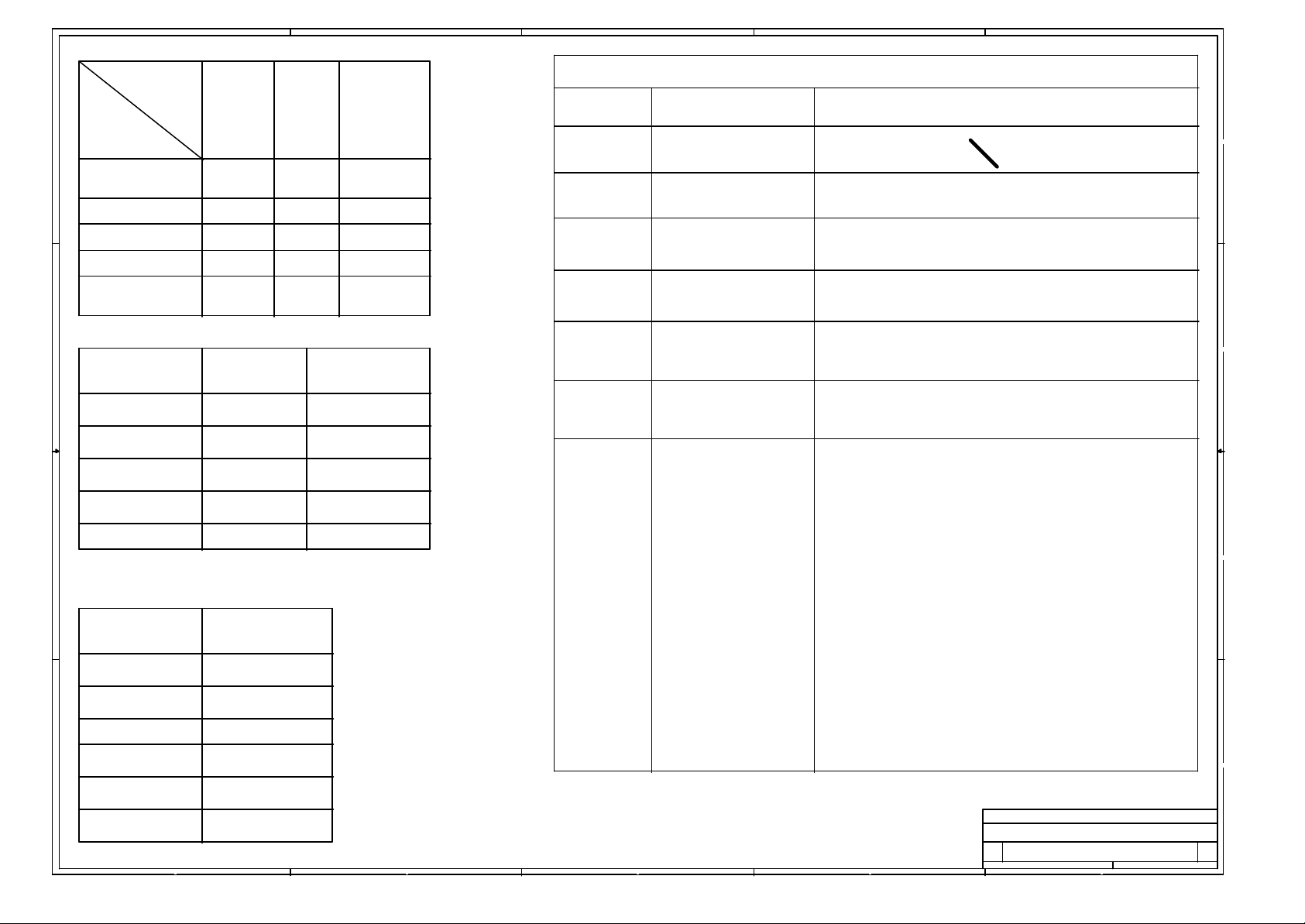

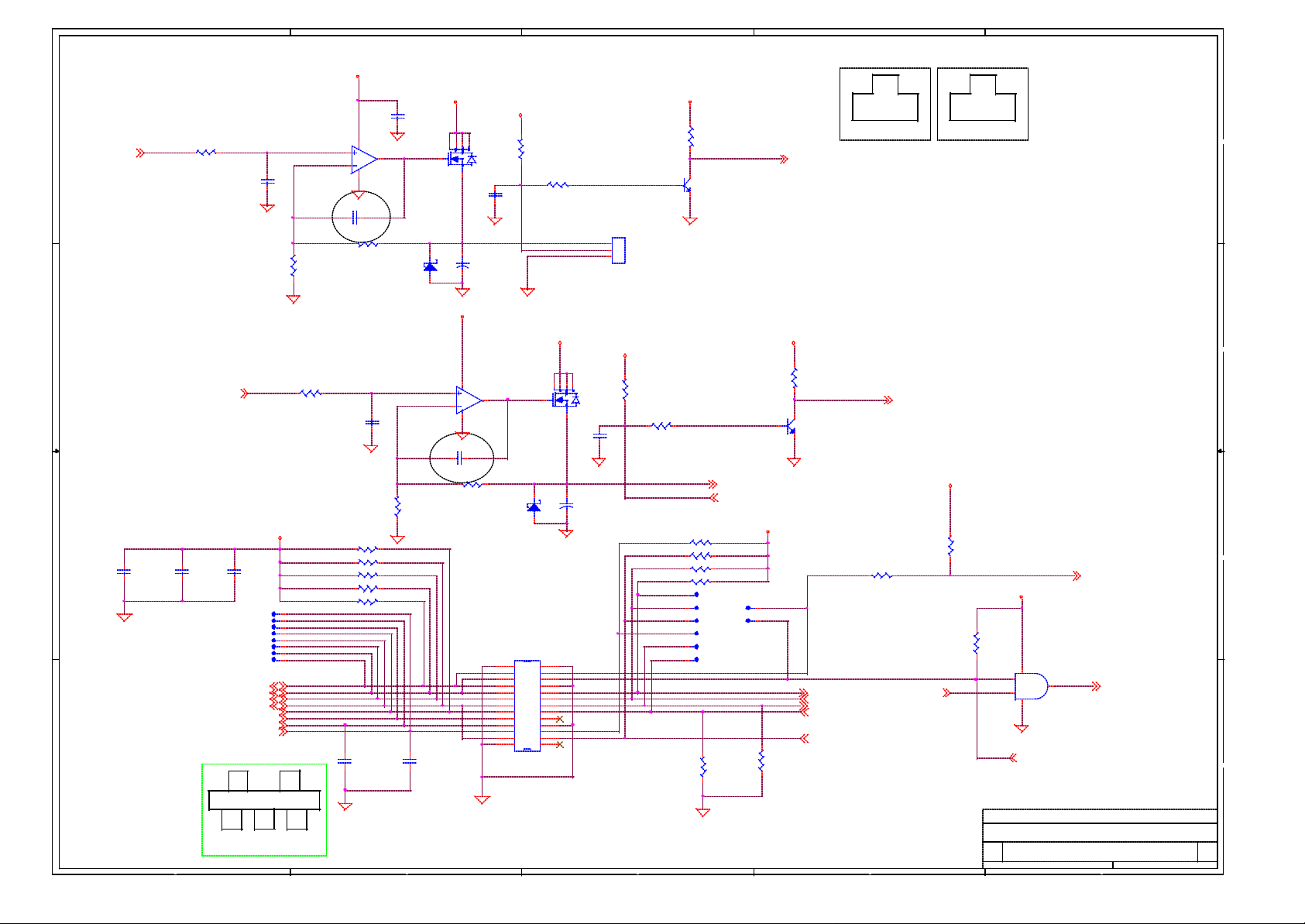

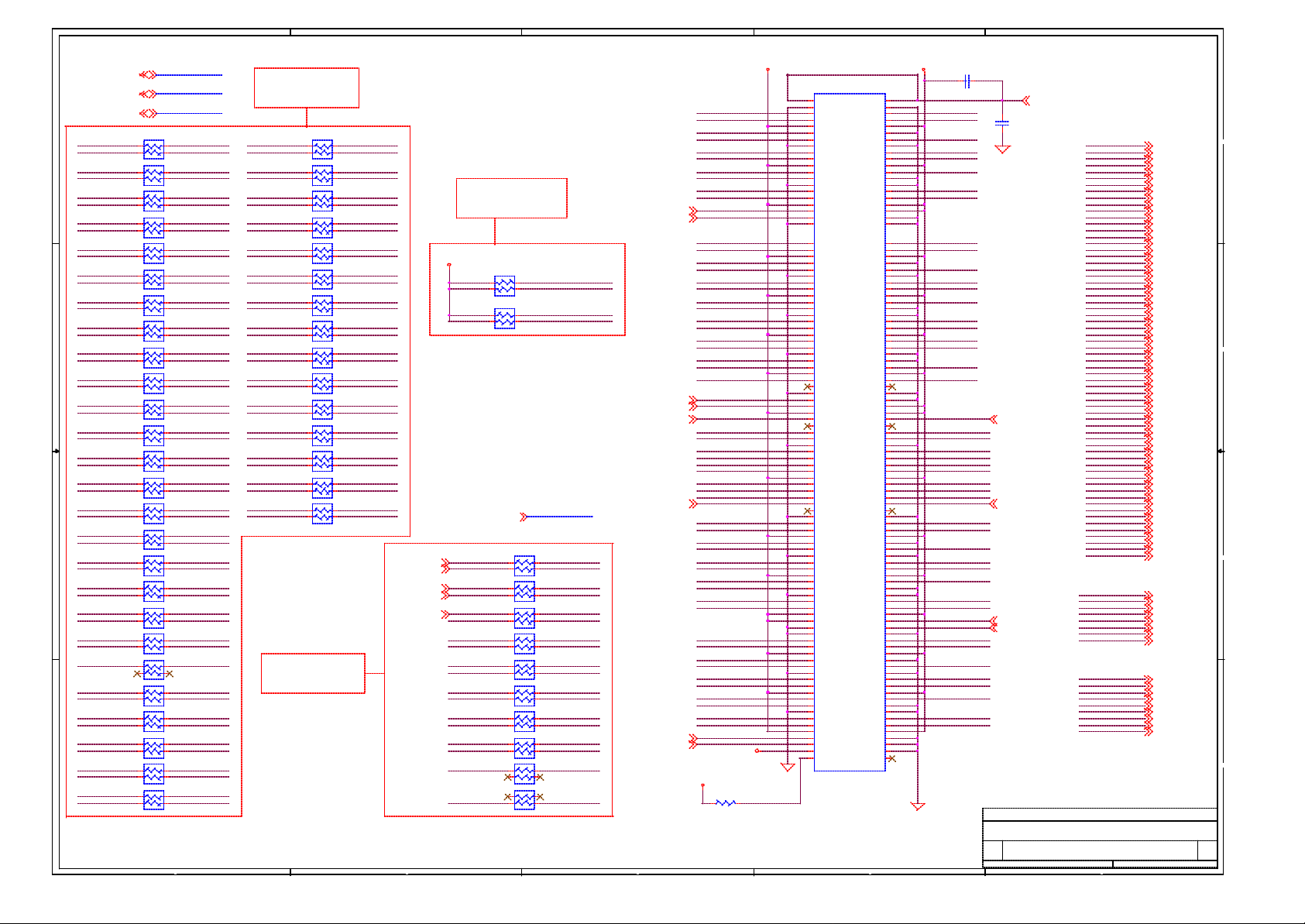

PM TABLE

power

plane

State

D D

S0

+3VALW

+5VALW

ON

+3VSRC

+3VSUS

+5VSUS

+2.5VSUS

+1.8VSUS

+1.5VSUS

+12V

ON

+3VRUN

+5VRUN

+1.8VRUN

+1.5VRUN

+VCC_CORE

ON

BOM Structure

Function Lindbergh Kapalua

Configuration List

Baekland

S1

S3

S5 S4/AC

S5 S4/AC don't exist

TABLE

PCI

C C

PCI DEVICE

CARD BUS

LAN

DOCK

MINI PCI

B B

TABLE

USB

ON

ON

ON

IDSEL

AD17

AD16

AD24

AD19

USB PORT# DESTINATION

ON

ON

OFF

OFF

ON

OFF

OFF

OFFOFF

REQ#/GNT#

1

4

0

3

BOM Structure:

Baekland- 43122231001, with

1@

Lindbergh- 43122231002, with 2@

0

1

2

3

A A

4

5

5

BACK

BLUETOOTH

BACK

DOG

MOD

DOCK

Note:

"@" means all model depop

"?" means Kapalua pop only (ie Lendbergh depop)

"#" means Lindbergh pop only (ie baekland

depop)

4

3

Title

Size Document Number Rev

2

Date: Sheet of

Compal Electronics, Inc.

Index and Config.

ADQ00/LA-1351

3 50Wednesday, October 23, 2002

1

X025

5

4

3

2

1

RBAT

D D

ADAPTER

+RTCSRC

+RTC_PWR

+5VALW

PWR_SRC

+3.3VRTC

+3VALW

BATTERY

DOCK _PWR_SRC

C C

+5VSUS

B B

+5VMOD

VDDA+5VRUN +2.5V_MEM+3VSUS

+3VSRC

V3P3LAN

+2.5VMEMP

V_1P25V_DDR_VTT

+VCC_CORE

+1.5VSUS

+1.5VRUN+5VHDD

+12V

A A

5

4

+1.8VSUS

+3VRUN

3

Title

Size Document Number Rev

2

Date: Sheet of

Compal Electronics, Inc.

Power Rail

ADQ00/LA-1351

4 50Wednesday, October 23, 2002

1

X025

5

4

3

2

1

D D

ICH4-M

ICH_SMBDATA

+3VSUS

ICH_SMBCLK

7002

7002

+3VRUN

CK_SCLK

CLK GEN.

CK_SDATA

V_3P3_LAN

DIMM0

DIMM1

7002

7002

LAN_SMBCLK

NIC

LAN_SMBDATA

7002

CLK_SMB

DAT_SMB

C C

24C05

+3VALW

ADM1032

7002

7002

DH PORT

7002

MPCI

DOCK_SMB_CLK

SIO

DOCK_SMB_DAT

+5VALW

DOCKING

Macallen

SBAT_SMBCLK

SBAT_SMBDAT

B B

+5VALW

2'nd

BATTERY

VGA

Inverter & ADM1032

PBAT_SMBCLK

1'nd

PBAT_SMBDAT

A A

+5VALW

BATTERY

CHARGER

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

SMBUS TOPOLOGY

ADQ00/LA-1351

5 50Wednesday, October 23, 2002

1

X025

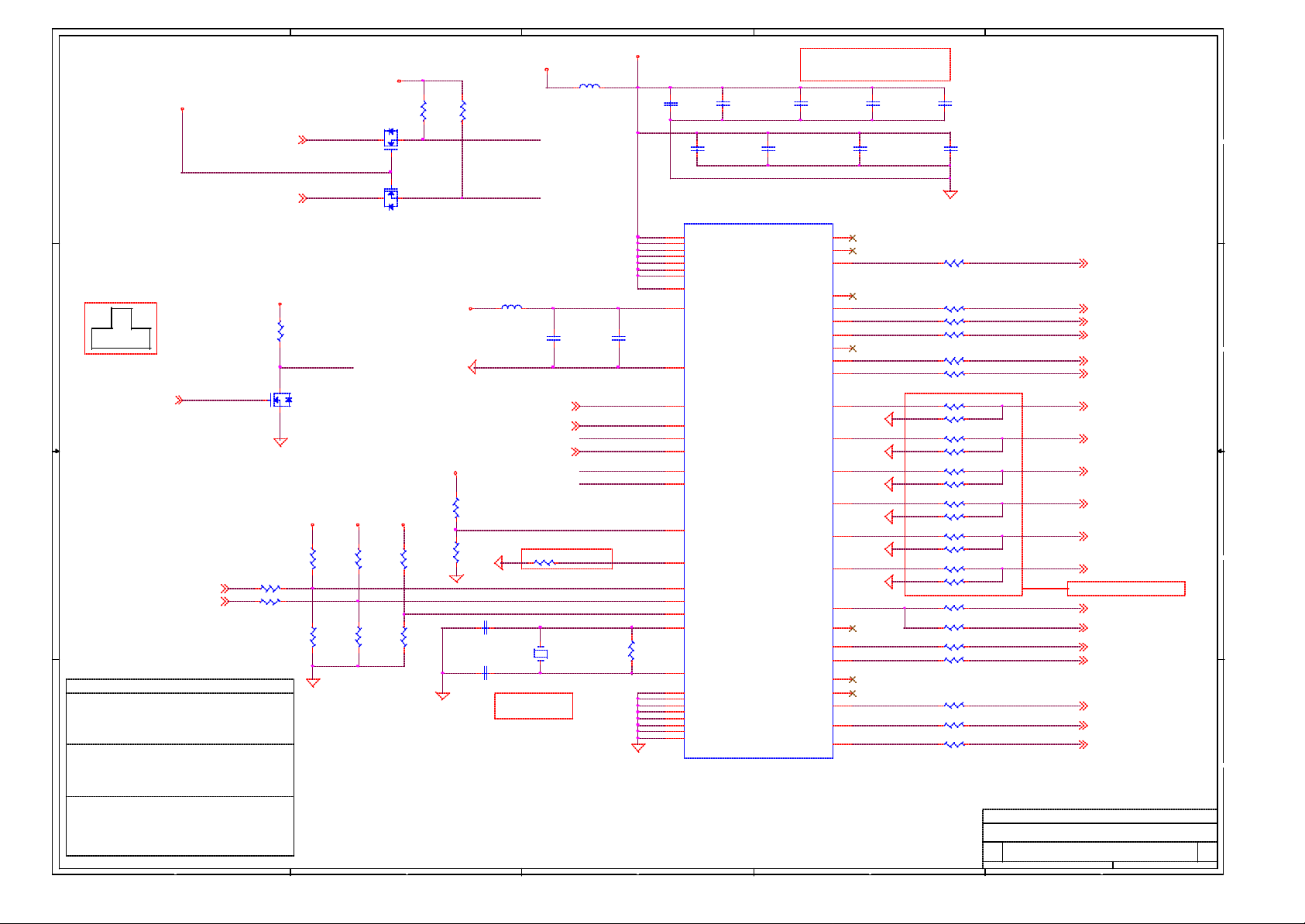

5

+3VRUN

+3VRUN

R56

10K_0402_5%

1 2

13

D

S

R97

12

12

R94

ICH_SMBDATA

ICH_SMBCLK

CK_VTT_PG#

+3VRUN

1K_0402_5%

R96

1 2

@1K_0402_5%

R91

1 2

+3VRUN

1 2

1 2

D D

ICH_SMBDATA14,15,19,31

ICH_SMBCLK14,15,19,31

D

1

G

C C

S

2

2N7002

2N7002_SOT23

Q51

2

G

@0_0402_5%

@0_0402_5%

VCORE_PWRGD20,38,46

B B

VCORE_PWRGD

H_BSEL1#8

H_BSEL0#8,12

S2 S1 S0 CPU 3V66[0..4] 3V66_5/66IN

1 0 0 66 66IN 66 Input

1 0 1 100 66IN 66 Input

1 1 0 200 66IN 66 Input

1 1 1 133 66IN 66 Input

0 0 0 66 66 66 Input

0 0 1 100 66 66 Input

A A

0 1 0 200 66 66 Input

+3VRUN

R57

100K_0402_5%

D

1 3

Q6 2N7002_SOT23

G

2

2

G

1 3

D

Q8 2N7002_SOT23

+3VRUN

@1K_0402_5%

R95

1K_0402_5%

R90

4

12

S

S

@1K_0402_5%

R65

1 2

1K_0402_5%

R66

1 2

12

+3VRUN

CK_VDD_MAIN

12

R76

10K_0402_5%

@1K_0402_5%

R69

1 2

R61

100K_0402_5%

CK_SDATA

CK_SCLK

L29

BLM11A601S_0603

1 2

C81

10U_1206_6.3V7K

R67 475_0603_1%1 2

12

C90

@10P_0402_50V8 J

12

C93

@10P_0402_50V8 J

Place crystal within

500 mils of CK408

+3VRUN

L33

BLM21PG600SN1D_0805

1 2

W=20 mils

CLK_VDD_CORE

12

0.1U_0402_16V4Z

H_STP_CPU#20,46

H_STP_PCI#20

ICH_SLP_S1#20

MULT0

Please closely pin42

CLKSEL0

CLKSEL1

CLKSEL2

CK_XTAL_OUT

12

14.31818MHz_20P_1BX14318CC1A

X1

CK_XTAL_IN

3

CK_VDD_MAIN

CK_VDD_MAIN

1 2

14

19

32

46

50

37

26

12

C80

27

12

R89

@2M_0603_5%

53

34

28

25

30

29

43

42

54

55

40

15

20

31

36

41

47

H_STP_CPU# CK_CPU0

H_STP_PCI#

CK_VTT_PG#

ICH_SLP_S1#

CK_SCLK

CK_SDATA

CLKIREF

10U_1206_6.3V7K

C89

12

C88

0.1U_0402_10V6K

U8

1

VDD_REF

8

VDD_PCI

VDD_PCI

VDD_3V66

VDD_3V66

VDD_CPU

VDD_CPU

VDD_48MHZ

VDD_CORE

GND_CORE

CPU_STOP#

PCI_STOP#

VTT_PWRGD#

PWR_DWN#

SCLK

SDATA

MULT0

IREF

SEL0

SEL1

SEL2

3

XTAL_OUT

2

XTAL_IN

4

GND_REF

9

GND_PCI

GND_PCI

GND_3V66

GND_3V66

GND_48MHZ

GND_IREF

GND_CPU

W320-04_TSSOP56

12

C94

0.1U_0402_10V6K

CK408

Place near each pin

W>40 mil

12

C91

0.1U_0402_10V6K

12

C92

0.1U_0402_10V6K

PCICLK_F0

PCICLK_F1

PCICLK_F2

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2

CPUCLKC2

3V66_0/DRCG

48MHZ_DOT

48MHZ_USB

3V66_1/VCH_CLK

66MHZ_IN/3V66_5

66MHZ_OUT0/3V66_2

66MHZ_OUT1/3V66_3

66MHZ_OUT2/3V66_4

REF

12

5

6

7

10

11

12

13

16

17

18

52

51

49

48

45

44

56

33

38

39

35

24

21

22

23

CK_CPU0#

CK_CPU1

CK_CPU1#

CK_CPU2

CK_CPU2#

CLKREF

CLK48M_OUT1

CLK48M_OUT0

CLK66M_OUT0

CLK66M_OUT2

CLK66M_OUT3

2

12

C87

0.1U_0402_10V6K

C83

0.1U_0402_10V6K

PCICLK_F2

PCICLK1

PCICLK2

PCICLK3

PCICLK5

PCICLK6

12

C85

0.1U_0402_10V6K

12

C82

0.1U_0402_10V6K

1 2

R88 33_0402_5%

1 2

R83 33_0402_5%

1 2

R81 33_0402_5%

1 2

R79 33_0402_5%

1 2

R72 33_0402_5%

1 2

R68 33_0402_5%

1 2

R93 33_0402_5%

1 2

R92 49.9_0402_1%

1 2

R87 33_0402_5%

1 2

R86 49.9_0402_1%

1 2

R85 33_0402_5%

1 2

R84 49.9_0402_1%

1 2

R82 33_0402_5%

1 2

R80 49.9_0402_1%

1 2

R78 33_0402_5%

1 2

R77 49.9_0402_1%

1 2

R71 33_0402_5%

1 2

R70 49.9_0402_1%

1 2

R99 33_0402_5%

1 2

R98 33_0402_5%

1 2

R59 33_0402_5%

1 2

R62 33_0402_5%

1 2

R64 33_0402_5%

1 2

R63 33_0402_5%

1 2

R60 33_0402_5%

CK_33M_ICHPCI

CK_33M_SIOPCI

CK_33M_LANPCI

CK_33M_DOCKPCI

CK_33M_CBPCI

CK_33M_MINIPCI

CK_BCLK

CK_BCLK#

CK_ITP

CK_ITP#

CK_HCLK

CK_HCLK#

CK_14M_ICH

CK_14M_SIO

CK_48M_SCR

CK_48M_ICH

CK_66M_ICH

CK_66M_MCH

CK_66M_AGP

1

CK_33M_ICHPCI 18

CK_33M_SIOPCI 35

CK_33M_LANPCI 27

CK_33M_DOCKPCI 32

CK_33M_CBPCI 29

CK_33M_MINIPCI 31

CK_BCLK 7

CK_BCLK# 7

CK_ITP 8

CK_ITP# 8

CK_HCLK 11

CK_HCLK# 11

Place near CK408

CK_14M_ICH 19

CK_14M_SIO 35

CK_48M_SCR 29

CK_48M_ICH 19

CK_66M_ICH 19

CK_66M_MCH 12

CK_66M_AGP 16

0 1 1 133 66 66 Input

Mid

Mid

0Mid

0

0

13Mid

Hi-z

TCLK/21

Reserve1

0 Reserve

1

Reserve

Hi-z

TCLK/2

Reserve

5

Hi-z

TCLK/2

Reserve

Reserve

Title

Size Document Number Rev

4

3

2

Date: Sheet of

Compal Electronics, Inc.

Clock Generator

ADQ00/LA-1351

6 50Wednesday, October 23, 2002

1

X025

5

+VCC_CORE

4

3

2

1

JCPUA

D D

C C

+VCC_CORE

R360

1K_0402_5%

1 2

B B

Placed near CPU

CK_BCLK

CK_BCLK#

A A

H_A#[3..31]11

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#[0..4]11

H_ADS#11

H_BR0#8,11

H_BPRI#11

H_BNR#11

H_LOCK#11

CK_BCLK6

CK_BCLK#6

H_HIT#11

H_HITM#11

H_DEFER#11

12

C450@2.2P_0402_50V7C

12

C452@2.2P_0402_50V7C

5

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADS#

AC1

CPU_IERR#

H_BR0#

H_BPRI#

H_BNR#

H_LOCK#

CK_BCLK

CK_BCLK#

H_HIT#

H_HITM#

H_DEFER#

AC3

AF22

AF23

JCPU DELL P/N changed to

1M568(mobil socket)

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E12

E14

E16

E18

E20E8F11

F13

F15

F17

F19

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

+3VRUN+3VALW

C36

0.1U_0402_16V4Z

1 2

2

F9

VCC_83

VCC_84

VCC_85

B21

D#0

B22

D#1

A23

D#2

A25

D#3

C21

D#4

D22

D#5

B24

D#6

C23

D#7

C24

D#8

B25

D#9

G22

D#10

H21

D#11

C26

D#12

D23

D#13

J21

D#14

D25

D#15

H22

D#16

E24

D#17

G23

D#18

F23

D#19

F24

D#20

E25

D#21

F26

D#22

D26

D#23

L21

D#24

G26

D#25

H24

D#26

M21

D#27

L22

D#28

J24

D#29

K23

D#30

H25

D#31

M23

D#32

N22

D#33

P21

D#34

M24

D#35

N23

D#36

M26

D#37

N26

D#38

N25

D#39

R21

D#40

P24

D#41

R25

D#42

R24

D#43

T26

D#44

T25

D#45

T22

D#46

T23

D#47

U26

D#48

U24

D#49

U23

D#50

V25

D#51

U21

D#52

V22

D#53

V24

D#54

W26

D#55

Y26

D#56

W25

D#57

Y23

D#58

Y24

D#59

Y21

D#60

AA25

D#61

AA22

D#62

AA24

D#63

AMP_1565030-1_478P

+3VALW

10K_0402_5%

R41

1 2

H_D#[0..63] 11

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

ATF_INT# 34

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

Mobile Northwood (1/2)

ADQ00/LA-1351

7 50Wednesday, October 23, 2002

1

X025

E10

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_74

VCC_75

VCC_76

VCC_77

VSS_50

VSS_51

AD16

AD18

VSS_52

VSS_53

AD21

AD23

VSS_54

AD4

1 2

VCC_73

VSS_55

VSS_56

AD8

@10K_0402_5%

R33

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

J1

REQ#0

K5

REQ#1

J4

REQ#2

J3

REQ#3

H3

REQ#4

G1

ADS#

AP#0

V5

AP#1

AA3

BINIT#

IERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

BCLK0

BCLK1

F3

HIT#

E3

HITM#

E2

DEFER#

VSS_0

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

H1H4H23

H26

A11

A13

A15

A17

A19

A21

A24

A26A3A9

H_THERMDA8

H_THERMDC8

CLK_SMB25,35,36

DAT_SMB25,35,36

H_THERMDA

H_THERMDC

CLK_SMB

DAT_SMB

4

12

2200P_0603_50V7 K

C44

1 2

Mobile

NorthWood

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

CPU Temperature Sensor

1 2

R42

6.8K_0603_5%

R43

6.8K_0603_5%

VSS_25

AB10

AB12

VSS_26

VSS_27

AB14

AB16

3

VSS_28

VSS_29

AB18

AB20

VSS_30

VSS_31

AB21

2

3

8

7

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

AB24

AB3

AB6

AB8

AC11

AC13

AC15

U5

VDD1

D+

ALERT

D-

THERM

SCLK

GND

SDATA

ADM1032AR_SOP-8

VSS_39

AC17

VSS_40

AC19

AC2

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

AC22

AC25

AC5

AC7

AC9

1

6

ADM1032_THERM#

4

5

VSS_46

VSS_47

AD1

AD10

VSS_48

VSS_49

AD12

AD14

+VCC_CORE

R381 51.1_0603_1%

R352 51.1_0603_1%12

R357 51.1_0603_1%12

R355 51.1_0603_1%12

R353 51.1_0603_1%

R356 51.1_0603_1%

D D

12

C364

0.1U_0402_16V4Z

C C

V_1P2V_VCCVID

L32

L30

12

33U_D2_16VM_R70

C685

1U_0603_6.3V6M

CK_ITP_R#10

CK_ITP_R10

CK_ITP6

CK_ITP#6

B B

+VCC_CORE

R48

R46

R349

R354

R405

R403

R49

R350

R47

R44

R378 220_0603_1%

A A

R401

R404 300_0603_5%

R345

R45

R351

5

12

12

C46

0.1U_0402_16V4Z

V_1P2V_VCCVID 46

12

+

RN11

0_0404_4P2R_5%

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

200_0603_5%

12

56_0603_5%

12

12

51.1_0603_1%

12

12

200_0603_5%

12

10K_0402_1%

12

56_0603_5%

12

5

H_BPM0#

H_BPM1#

H_BPM2#

H_BPM3#

H_BPM4#

H_BPM5#

14

23

H_A20M#

H_SMI#

H_IGNNE#

H_STPCLK#

H_CPUSLP#

H_DPSLP#

H_NMI

H_INTR

H_CPUPERF#

H_FERR#

H_BR0#

H_RESET#

H_PWRGOOD

H_INIT#

H_PROCHOT#

H_THERMTRIP#

12

+

12

12

12

+VCC_CORE

C54

0.1U_0402_16V4Z

4.7U_LQM21FN4R7N00L_80M_30%_0805

12

4.7U_LQM21FN4R7N00L_80M_30%_0805

12

C77

Low

ESR

H_RS#[0..2]11

H_TRDY#11

H_A20M#18

H_FERR#18

H_IGNNE#18

H_SMI#18

H_PWRGOOD18

H_STPCLK#18

H_DPSLP#18

H_INTR18

H_NMI18

H_INIT#18

H_RESET#10,11

H_DBSY#11

H_DRDY#11

H_BSEL0#6,12

H_BSEL1#6

H_THERMDA7

H_THERMDC7

H_THERMTRIP#20,38

H_BPM0#10

H_BPM1#10

H_BPM4#10

H_BPM5#10

T16

C84

33U_D2_16VM_R70

Low

ESR

T17

RN10

1 4

2 3

@0_0402_4P2R_5%

R400

51.1_0603_1%

H_BR0# 7,11

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGOOD

H_STPCLK#

H_DPSLP#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_DBSY#

H_DRDY#

H_BSEL0#

H_BSEL1#

H_THERMDA

H_THERMDC

H_THERMTRIP#

H_BPM0#

H_BPM1#

H_BPM2#

H_BPM3#

H_BPM4#

H_BPM5#

H_VCCA

H_VCCIOPLL

H_VCCSENSE

PAD

H_VSSA

H_VSSSENSE

PAD

CPU_CK_ITP

CPU_CK_ITP#

H_COMP0

H_COMP1

51.1_0603_1%

R344

1 2

1 2

Place resistor <100mils from

CPU pin

JCPUB

F1

G5

F4

AB2

J6

C6

B6

B2

B5

AB23

Y4

AD25

D1

E5

W5

AB25

H5

H2

AD6

AD5

B3

C4

A2

AC6

AB5

AC4

Y6

AA5

AB4

AD20

AE23

A5

AD22

A4

AC26

AD26

L24

P1

4

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

VCCA

VCCIOPLL

VCCSENSE

VSSA

VSSSENSE

ITP_CLK0

ITP_CLK1

COMP0

COMP1

4

AE11

AE13

VSS_57

F8

AE15

AE17

VSS_58

VSS_59

VSS_60

VSS_129

VSS_130

VSS_131

G21

G24G3G6J2J22

AE19

AE22

VSS_61

VSS_132

AE24

AE26

VSS_62

VSS_63

VSS_64

VSS_133

VSS_134

VSS_135

AE7

AE9

VSS_65

VSS_66

VSS_136

VSS_137

J25J5K21

AF1

AF10

AF12

AF14

VSS_67

VSS_68

VSS_69

VSS_138

VSS_139

VSS_140

K24K3K6L1L23

AF16

AF18

AF20

VSS_70

VSS_71

VSS_72

VSS_141

VSS_142

VSS_143

L26L4M2

AF26

AF6

VSS_73

VSS_75

SKTOCC#

VSS_144

VSS_145

VSS_146

AF8

B10

VSS_76

VSS_147

M22

M25M5N21

B12

B14

VSS_77

VSS_78

VSS_79

VSS_148

VSS_149

VSS_150

3

B16

B18

B20

B23

B26B4B8

C11

C13

C15

C17

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

Mobile

NorthWood

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

N24N3N6P2P22

P25P5R1

R23

R26R4T21

3

C19C2C22

VSS_90

VSS_91

VSS_92

VSS_161

VSS_162

VSS_163

T24T3T6U2U22

C25C5C7C9D10

VSS_93

VSS_94

VSS_95

VSS_96

VSS_164

VSS_165

VSS_166

VSS_167

U25U5V1

D12

VSS_97

VSS_98

VSS_99

VSS_168

VSS_169

VSS_170

D14

D16

VSS_100

VSS_171

V23

V26V4W21

D18

D20

VSS_101

VSS_102

VSS_103

VSS_172

VSS_173

VSS_174

D21

D24D3D6D8E1

E11

E13

E15

E17

E19

E23

E26E4E7E9F10

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VID0

VID1

VID2

VID3

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

W24W3W6Y2Y22

Y25

Y5

GTL Reference Voltage

Layout note :

1. Place R_A and R_B near CPU.

2. Place decoupling cap 220PF near CPU.(Within

500mils)

VID4

AE5

AE4

AE3

AE2

AE1

220P_0402_50V8 J

F12

VSS_120

VSS_121

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

C362

F14

F16

VSS_122

NC5

AE21

AF24

2

F18F2F22

VSS_123

VSS_124

NC6

1 2

2

F25

F5

VSS_125

VSS_126

VSS_127

VSS_128

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

NC1

NC2

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

GHI#

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

TRST#

TMS

TDO

TDI

TCK

NC8

NC7

NC3

NC4

VCCVID

AMP_1565030-1_478P

AF4

C365

220P_0402_50V8 J

J26

K25

K26

L25

AA21

AA6

F20

F6

A22

A7

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

E6

F7

D5

C1

D4

AF3

AF25

AD2

AD3

V_1P2V_VCCVID

H_VID[0..4] 9

220P_0402_50V8 J

1 2

1

H_GTLREF0_3

TESTHI0_1_PU

TESTHI2_7_PU

TESTHI8_10_PU

H_CPUPERF#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_ADSTB#0

H_ADSTB#1

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_ITP_DBR#

H_PROCHOT#

H_CPUSLP#

H_TRST#

H_TMS

H_TDO

H_TDI

H_TCK

12

C359

0.1U_0402_16V4Z

H_GTLREF0_3

C447

220P_0402_50V8 J

1 2

Title

Size Document Number Rev

Date: Sheet of

R359 1K_0402_5%1 2

R52 1K_0402_5%1 2

R358 1K_0402_5%1 2

H_CPUPERF# 20

H_DSTBN#[0..3] 11

H_DSTBP#[0..3] 11

H_ADSTB#0 11

H_ADSTB#1 11

H_DBI#[0..3] 11

H_ITP_DBR# 10

H_PROCHOT# 18

H_CPUSLP# 18

H_TRST# 10

H_TMS 10

H_TDO 10

H_TDI 10

H_TCK 10

V_1P2V_VCCVID 46

1U_0603_6.3V6M

1 2

C53

1 2

C446

Compal Electronics, Inc.

Mobile Northwood (2/2)

ADQ00/LA-1351

1

+VCC_CORE

49.9_0603_1%

R50

R51

8 50Wednesday, October 23, 2002

+VCC_CORE

12

R_A

R_B

12

100_0603_1%

X025

5

4

3

2

1

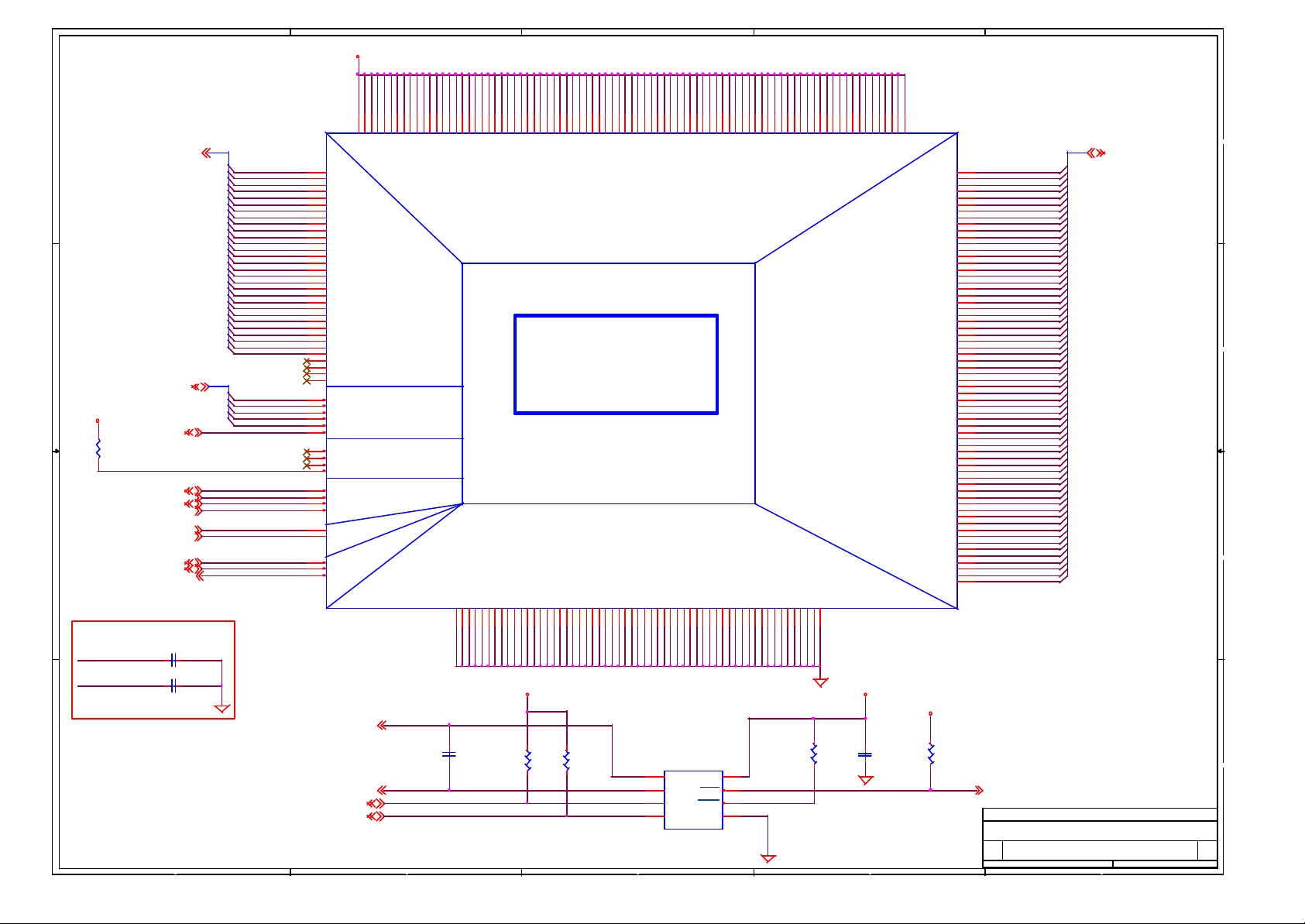

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

D D

C C

B B

+VCC_CORE +VCC_CORE

12

C415

10U_1206_6.3V7K

+VCC_CORE

12

C403

10U_1206_6.3V7K

+VCC_CORE

12

C404

10U_1206_6.3V7K

+VCC_CORE

12

C376

10U_1206_6.3V7K

+VCC_CORE

12

C427

10U_1206_6.3V7K

+VCC_CORE

12

C441

10U_1206_6.3V7K

10uF 1206 X5R -> 85

degree

12

C386

10U_1206_6.3V7K

12

C418

10U_1206_6.3V7K

12

C440

10U_1206_6.3V7K

12

C414

10U_1206_6.3V7K

12

C379

10U_1206_6.3V7K

12

C394

10U_1206_6.3V7K

CPU Bulk

12

C412

10U_1206_6.3V7K

12

C413

10U_1206_6.3V7K

12

C396

10U_1206_6.3V7K

12

C445

10U_1206_6.3V7K

12

C373

10U_1206_6.3V7K

12

C372

10U_1206_6.3V7K

12

12

12

12

12

12

Check X5R

or X7R ?

Quantity?

C406

10U_1206_6.3V7K

C378

10U_1206_6.3V7K

C387

10U_1206_6.3V7K

C398

10U_1206_6.3V7K

C438

10U_1206_6.3V7K

C374

10U_1206_6.3V7K

12

C395

10U_1206_6.3V7K

12

C405

10U_1206_6.3V7K

12

C439

10U_1206_6.3V7K

12

C444

10U_1206_6.3V7K

12

C377

10U_1206_6.3V7K

12

C426

10U_1206_6.3V7K

+VCC_CORE +VCC_CORE

12

+

C671

220U_D_2.5VM_R15

H_VID[0..4]8 VID[0..4] 46

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

12

C57

0.22U_0603_10V7 M

12

C56

0.22U_0603_10V7 M

12

C61

0.22U_0603_10V7 M

12

C60

0.22U_0603_10V7 M

High Frequence Decoupling

To find 2V BULK CAP.

12

+

C672

220U_D_2.5VM_R15

12

+

C673

220U_D_2.5VM_R15

12

+

C674

220U_D_2.5VM_R15

12

+

C675

220U_D_2.5VM_R15

CPU Voltag e ID

R3410_0402_5%

12

H_VID1

H_VID2

H_VID3

H_VID4 VID4

R3370_0402_5%

12

R3380_0402_5%

12

R3390_0402_5%

12

R3400_0402_5%

12

12

+

C676

220U_D_2.5VM_R15

+3VSUS

1 8

2 7

3 6

4 5

12

+

C677

220U_D_2.5VM_R15

12

RN9

10K_1206_8P4R_5%

R333

10K_0402_5%

VID0H_VID0

VID1

VID2

VID3

12

+

C678

220U_D_2.5VM_R15

VID4

A A

V I D

VID2

VID3

1

1

0

0

1 0

1 1

0

1

0

0

1 0

0

1

0

1

1

1

0

VID1

00

0

0

1

1

1

1

0

0

5

Vcore

VID0

0

0

1

1

0

1

1

00

0

V

0

1.350

0

1

1.300

0

1.250

1.200

1.150

0

1.100

1

1

0

1.050

1

1.000

0

0.975

1

0.950

Title

Size Document Number Rev

4

3

2

Date: Sheet of

Compal Electronics, Inc.

CPU bypass and CPU VID

ADQ00/LA-1351

9 50Wednesday, October 23, 2002

1

X025

5

+12V

U49B

D D

FAN1_PWM35

R130

1 2

100K_0402_5%

1U_0805_10V6 K

C128

12

FAN1VREF

FAN1_VFB

1 2

R128

150K_0603_5%

LM358M_SO-8

5

6

2200P_0603_50V7 K

8

4

C127

4

FAN1 Control and Tachometer

C121

0.1U_0402_16V4Z

3

D9

2 1

+5VRUN

12

+12V

65241

+

+5VRUN

Q15

SI3456DV-T1_TSOP-6

12

C476

0.47U_1206_16V7K

FAN1_VOUT

C479

100U_D_10VM_R55

R110

10K_0402_5%

1 2

7

12

R129

100K_0402_5%

RB751V-40

12

FAN1_ON

R109

1 2

1K_0402_5%

FAN1(MAIN FAN)

FAN1_TACH_FB

3

FAN1TACH_ON

JFAN1

1

2

3

FOX_BP26037-H1R_3P

+3VRUN

2

12

R117

10K_0402_5%

Q11

PMBT2222_SOT23

3 1

FAN1_TACH 35

2

C

B

E 3

2

2222 SYMBOL(SOT23-NEW)

1

1

+VCC_CORE

T262 PAD

T266 PAD

1 2

+3VRUN

12

2

3 1

R173

680_0603_5%

R174

10K_0402_5%

Q18

PMBT2222_SOT23

H_TDI 8

H_TMS 8

H_TRST# 8

H_TCK 8

H_TDO 8

FAN2_TACH 35

R133

12

@33_0402_5%

GDRUNPWROK38,47

H_ITP_DBR#

+3VRUN

R132

10K_0402_5%

1 2

R125

10K_0402_5%

1 2

G_AGPBUSY#

+3VSUS

5

1

2

3

H_ITP_DBR# 8

G_AGPBUSY# 16,20

U10

4

TC7SH08FU_SSOP5

DRUNPWROK 20

D10

1

3

5

7

9

11

13

15 16

17 18

19 20

21 22

23 24

25 K

+5VRUN

3

2 1

2

2

4

4

6

6

8

8

10

10

12

12

14

14

65241

Q17

SI3456DV-T1_TSOP-6

C472

0.47U_1206_16V7K

FAN2_5V

12

+

C495

100U_D_10VM_R55

ITP_PWRON

12

+5VRUN

R163

10K_0402_5%

1 2

1 2

FAN2(VGA CARD)

R168

1K_0402_5%

FAN2_TACH_FB

FAN2TACH_ON

FAN2_5V 16

FAN2_TACH_FB 16

R182 1.5K_0603_1%1 2

R186 51.1_0603_1%1 2

1 2

R156 39_0603_1%

1 2

R148 150_0603_1%

T260PAD

T261PAD

T265PAD

T269PAD

T272PAD

T275PAD

H_DBA#

H_TDI

H_TMS

H_TRST#

H_TCK

H_TDO

R180

27.4_0603_1%

1 2

C C

U49A

R437

C193

T263 PAD

T264 PAD

T267 PAD

T268 PAD

T270 PAD

T271 PAD

T273 PAD

T274 PAD

1 2

100K_0402_5%

+VCC_CORE

H_BPM0#

H_BPM1#

H_BPM4#

H_BPM5#

H_RESET#

H_TCK

CK_ITP_R

CK_ITP_R#

4

1U_0805_10V6 K

FAN2_PWM35

B B

A A

12

C184

10U_0805_10V4Z

12

C201

0.1U_0402_16V4Z

12

H_BPM0#8

H_BPM1#8

H_BPM4#8

H_BPM5#8

H_RESET#8,11

H_TCK8

CK_ITP_R8

CK_ITP_R#8

0.1U_0402_16V4Z

5

FAN2VREF

12

C478

12

12

12

@2.2P_0402_50V8C

C189

FAN2_VFB

R435

150K_0603_5%

1 2

R177@51.1_0603_1%

R19551.1_0603_1% 12

R16551.1_0603_1% 12

R14351.1_0603_1% 12

R13851.1_0603_1%

12

8

LM358M_SO-8

3

2

4

C110

2200P_0603_50V7 K

R436

100K_0402_5%

@2.2P_0402_50V8C

C194

FAN2_ON

1

12

RB751V-40

P1

1

3

5

7

9

11

13

15 16

17 18

19 20

21 22

23 24

25 26

@2MM SMT KEY26

single gate TTL

5

2 3

1

ITP Debug Connector

4

3

2

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

ITP Debug CONN. & FAN

ADQ00/LA-1351

10 50Wednesday, October 23, 2002

1

X025

5

4

3

2

1

H_A#[3..31]7

D D

C C

B B

A A

Placed near MCH

CK_HCLK

CK_HCLK#

+1.5VRUN

@1K_0402_5%

R408

1 2

+VCC_CORE

R380

301_0603_1%

1 2

R379

150_0603_1%

1 2

+VCC_CORE

R391

301_0603_1%

1 2

R389

150_0603_1%

1 2

12

C380@2.2P_0402_50V7C

12

C381@2.2P_0402_50V7C

H_ADSTB#08

H_ADSTB#18

H_RESET#8,10

H_TRDY#8

H_DEFER#7

H_BPRI#7

H_LOCK#7

PCIRST_1#18,27

H_DBSY#8

H_DRDY#8

H_HIT#7

H_HITM#7

H_BR0#7,8

H_ADS#7

H_BNR#7

H_RS#[0..2]8

H_REQ#[0..4]7

CK_HCLK6

CK_HCLK#6

H_DBI#[0..3]8

C371

0.01U_0402_16V7K

1 2

24.9_0603_1%

C402

0.01U_0402_16V7K

1 2

GTL Reference Voltage

Layout note :

1. Place R_E and R_F near MCH

2. Place decoupling cap 220PF near MCH pin.(Within

500mils)

R348

1 2

5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28 DDR_D54

H_A#29

H_A#30

H_A#31

H_ADSTB#0

H_ADSTB#1

H_RESET#

H_TRDY#

H_DEFER#

H_BPRI#

H_LOCK#

PCIRST_1#

MCH_TESTIN#

H_DBSY#

H_DRDY#

H_HIT#

H_HITM#

H_BR0#

H_ADS#

H_BNR#

H_RS#0 H_D#50

H_RS#1

H_RS#2

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

CK_HCLK

CK_HCLK#

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_SWNG0

H_SWNG1

GMCHCOMP0

GMCHCOMP1

24.9_0603_1%

R376

1 2

U7A

T4

HA#3

T5

HA#4

T3

HA#5

U3

HA#6

R3

HA#7

P7

HA#8

R2

HA#9

P4

HA#10

R6

HA#11

P5

HA#12

P3

HA#13

N2

HA#14

N7

HA#15

N3

HA#16

K4

HA#17

M4

HA#18

M3

HA#19

L3

HA#20

L5

HA#21

K3

HA#22

J2

HA#23

M5

HA#24

J3

HA#25

L2

HA#26

H4

HA#27

N5

HA#28

G2

HA#29

M6

HA#30

L7

HA#31

R5

HADSTB#0

N6

HADSTB#1

AE17

CPURST#

U7

HTRDY#

Y4

DEFER#

Y7

BPRI#

W5

HLOCK#

J27

RSTIN#

H26

TESTIN#

V5

DBSY#

V4

DRDY#

Y5

HIT#

Y3

HITM#

V7

BREQ#0

V3

ADS#

W3

BNR#

W2

RS#0

W7

RS#1

W6

RS#2

U6

HREQ#0

T7

HREQ#1

R7

HREQ#2

U5

HREQ#3

U2

HREQ#4

J8

BCLK

K8

BCLK#

AD5

DBI#0

AG4

DBI#1

AH9

DBI#2

AD15

DBI#3

AA7

HSWNG0

AD13

HSWNG1

AC2

HRCOMP0

AC13

HRCOMP1

Trace

width>=7mils

12

C385

1U_0603_6.3V6M

12

C367

220P_0402_50V8 J

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HOST

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

RG82845MP_BGA-593

12

C370

220P_0402_50V8 J

4

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AD7

AC7

AC6

AC3

AC8

AE2

AG5

AG2

AE8

AF6

AH2

AF3

AG3

AE5

AH7

AH3

AF4

AG8

AG7

AG6

AF8

AH5

AC11

AC12

AE9

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

AD4

H_DSTBN#0

H_DSTBN#1

AE6

H_DSTBN#2

AE11

AC15

H_DSTBN#3

H_DSTBP#0

AD3

AE7

H_DSTBP#1

H_DSTBP#2

AD11

H_DSTBP#3

AC16

M7

R8

Y8

AB11

AB17

+VCC_CORE

R_E

R_F

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13H_A#16

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

V_MCH_GTLREF

49.9_0603_1%

R387

V_MCH_GTLREF

1 2

R390

1 2

100_0603_1%

H_D#[0..63] 7

DDR_D[0..63]14

H_DSTBN#[0..3] 8

H_DSTBP#[0..3] 8

V_DDR_MCH_REF14,15,45

+2.5V_MEM

150_0603_1%

R395

1 2

150_0603_1%

R392

1 2

3

DDR_D45

DDR_D46

DDR_D44

DDR_D41

DDR_D47

DDR_D42

DDR_D43

DDR_D40

DDR_D39

DDR_D37

DDR_D36

DDR_D33

DDR_D32

DDR_D38

DDR_D34

DDR_D35

DDR_D49

DDR_D53

DDR_D51

DDR_D55

DDR_D50

DDR_D48

DDR_D52

DDR_D56

DDR_D60

DDR_D58

DDR_D63

DDR_D57

DDR_D61

DDR_D62

DDR_D59

DDR_D27

DDR_D30

DDR_D29

DDR_D24

DDR_D31

DDR_D26

DDR_D25

DDR_D28

DDR_D22

DDR_D18

DDR_D17

DDR_D21

DDR_D23

DDR_D19

DDR_D20

DDR_D16

DDR_D11

DDR_D15

DDR_D12

DDR_D8

DDR_D10

DDR_D14

DDR_D13

DDR_D9

DDR_D7

DDR_D6

DDR_D5

DDR_D0

DDR_D3

DDR_D2

DDR_D1

C425

0.1U_0402_16V4Z

1 2

V_MCH_REF

0.1U_0402_16V4Z

C431

1 2

Layout Note:

Please closely

pin J9 & J21

DDR_D4

DDR_CB2

DDR_CB6

DDR_CB5

DDR_CB0

DDR_CB3

DDR_CB7

DDR_CB1

DDR_CB4

DDR_CB[0..7]14

+2.5V_MEM

R394

12

0_0402_5%

0.1U_0402_16V4Z

C430

1 2

V_DDR_MCH_REF

0.1U_0402_16V4Z

C419

1 2

U7C

G28

SDQ0

F27

SDQ1

C28

SDQ2

E28

SDQ3

H25

SDQ4

G27

SDQ5

F25

SDQ6

B28

SDQ7

E27

SDQ8

C27

SDQ9

B25

SDQ10

C25

SDQ11

B27

SDQ12

D27

SDQ13

D26

SDQ14

E25

SDQ15

D24

SDQ16

E23

SDQ17

C22

SDQ18

E21

SDQ19

C24

SDQ20

B23

SDQ21

D22

SDQ22

B21

SDQ23

C21

SDQ24

D20

SDQ25

C19

SDQ26

D18

SDQ27

C20

SDQ28

E19

SDQ29

C18

SDQ30

E17

SDQ31

E13

SDQ32

C12

SDQ33

B11

SDQ34

C10

SDQ35

B13

SDQ36

C13

SDQ37

C11

SDQ38

D10

SDQ39

E10

SDQ40

C9

SDQ41

D8

SDQ42

E8

SDQ43

E11

SDQ44

B9

SDQ45

B7

SDQ46

C7

SDQ47

C6

SDQ48

D6

SDQ49

D4

SDQ50

B3

SDQ51

E6

SDQ52

B5

SDQ53

C4

SDQ54

E5

SDQ55

C3

SDQ56

D3

SDQ57

F4

SDQ58

F3

SDQ59

B2

SDQ60

C2

SDQ61

E2

SDQ62

G5

SDQ63

C16

SDQ64/CB0

D16

SDQ65/CB1

B15

SDQ66/CB2

C14

SDQ67/CB3

B17

SDQ68/CB4

C17

SDQ69/CB5

C15

SDQ70/CB6

D14

SDQ71/CB7

J21

SDREF0

J9 AD26

SDREF1 NC0

RG82845MP_BGA-593

V_DDR_MCH_REF 14,15,45

Placed near

DIMMs <1"

2

MEMORY

SMA0/CS#11

SMA1/CS#10

SMA2/CS#6

SMA3/CS#9

SMA4/CS#5

SMA5/CS#8

SMA6/CS#7

SMA7/CS#4

SMA8/CS#3

SMA9/CS#0

SMA11/CS#2

SMA12/CS#1

SMRCOMP

RCVENIN#

RCVENOUT#

Layout note:

Place

C431<1"

from MCH

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCK6

SCK#6

SCK7

SCK#7

SCK8

SCK#8

SCS#0

SCS#1

SCS#2

SCS#3

SCS#4

SCS#5

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SMA10

SBS0

SBS1

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SSI_ST

SRAS#

SWE#

SCAS#

NC1

DIMM 0 CLOCK

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

K25

J25

G17

G16

H7

H6

E9

F7

F9

E7

G9

G10

F26

C26

C23

B19

D12

C8

C5

E3

E15

E12

F17

E16

G18

G19

E18

F19

G21

G20

F21

F13

E20

G22

G12

G13

G23

E22

H23

F23

J23

K23

J28

G3

H3

H27

F11

G11

G8

AD27

CK_DDR_CK0

CK_DDR_CK0#

CK_DDR_CK1

CK_DDR_CK1#

CK_DDR_CK2

CK_DDR_CK2#

CK_DDR_CK3

CK_DDR_CK3#

CK_DDR_CK4

CK_DDR_CK4#

CK_DDR_CK5

CK_DDR_CK5#

DIMM 1 CLOCK

DDR_CS0_DIMM0#

DDR_CS1_DIMM0#

DDR_CS2_DIMM1#

DDR_CS3_DIMM1#

DDR_DS5

DDR_DS4

DDR_DS6

DDR_DS7

DDR_DS3

DDR_DS2

DDR_DS1

DDR_DS0

DDR_DS8

DDR_MA0

DDR_MA1

DDR_MA2

DDR_MA3

DDR_MA4

DDR_MA5

DDR_MA6

DDR_MA7

DDR_MA8

DDR_MA9

DDR_MA10

DDR_MA11

DDR_MA12

DDR_BS0

DDR_BS1

DDR_CKE0_DIMM0

DDR_CKE1_DIMM0

DDR_CKE2_DIMM1

DDR_CKE3_DIMM1

SM_RCOMP

DDR_FEEDBACK

DDR_RAS#

DDR_WE#

DDR_CAS#

C467

0.1U_0402_16V4Z

1 2

SM_RCOMP

Layout note:

Place R409 closely

pin J28

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

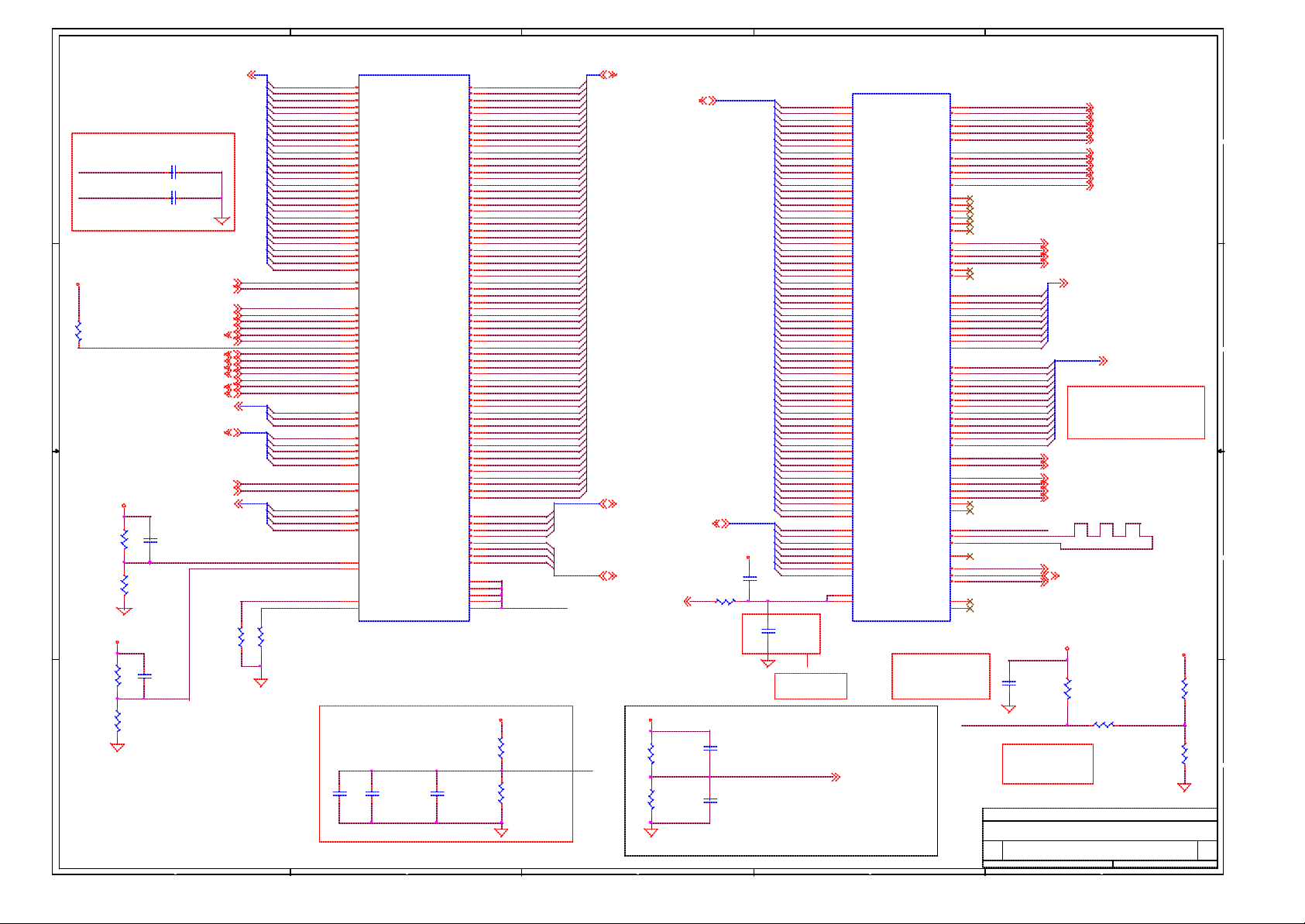

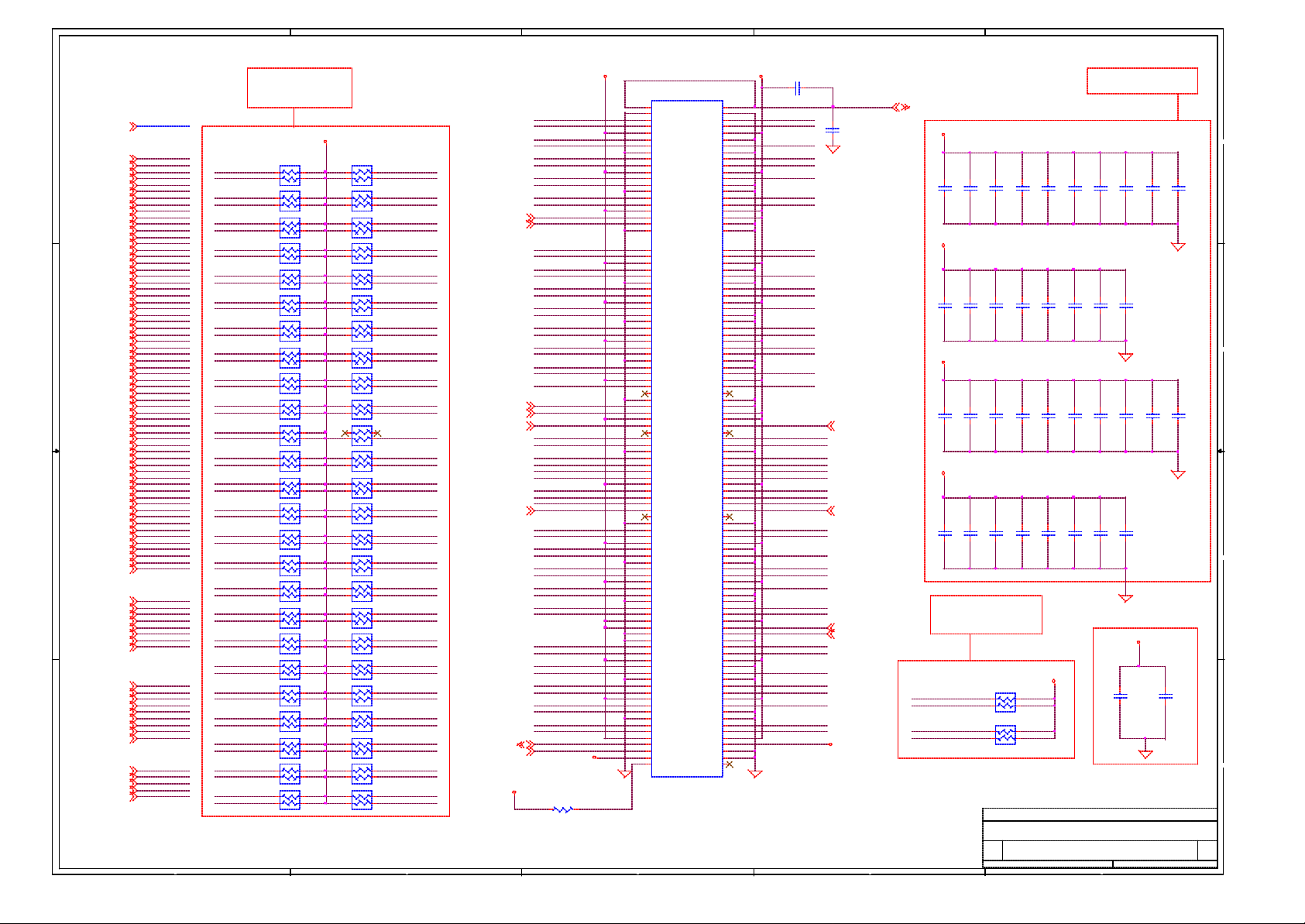

Brookdale MCH-M (1/3)

CK_DDR_CK0 14

CK_DDR_CK0# 14

CK_DDR_CK1 14

CK_DDR_CK1# 14

CK_DDR_CK2 14

CK_DDR_CK2# 14

CK_DDR_CK3 15

CK_DDR_CK3# 15

CK_DDR_CK4 15

CK_DDR_CK4# 15

CK_DDR_CK5 15

CK_DDR_CK5# 15

DDR_CS0_DIMM0# 14

DDR_CS1_DIMM0# 14

DDR_CS2_DIMM1# 15

DDR_CS3_DIMM1# 15

DDR_DS[0..8] 14

DDR_MA[0..12] 14,15

Layout note :

Place R_J closely ball

H3<40mil,Ball H3 to G3 trace

must routing 1"

DDR_BS0 14,15

DDR_BS1 14,15

DDR_CKE0_DIMM0 14

DDR_CKE1_DIMM0 14

DDR_CKE2_DIMM1 15

DDR_CKE3_DIMM1 15

DDR_RAS# 14,15

DDR_WE# 14,15

DDR_CAS# 14,15

V_1P25V_DDR_VTT

R409

30.1_0603_1%

1 2

R406

SM_RCOMP_R

1 2

@27.4_0603_1%

ADQ00/LA-1351

1

1 inch" INNER

LAYER DELAY

TRACE

+2.5V_MEM

11 50Wednesday, October 23, 2002

1 2

1 2

R407

@2K_0603_1%

R410

@2K_0603_1%

X025

5

4

3

2

1

HUB Interface Reference

Layout note :

1. Place R_C and R_D in middle of Bus.

2. Place capacitors near MCH.

301_0603_1%

R412

R_C

301_0603_1%

R414

R_D

R418

1K_0603_1%

R_M

R417

1K_0603_1%

R_N

+1.8VRUN

12

1 2

+1.5VRUN

12

1 2

@470P_0402_50V7K

C468

1 2

HLREF_TERMH

@56.2_0603_1%

R413

1 2

0_0402_5%

R415

1 2

HLREF_TERML

12

C470

0.1U_0402_16V4Z

12

C469

470P_0402_50V7 K

VREFCG_TERMH

R419

82.5_0603_1%

1 2

R420

1 2

82.5_0603_1%

VREFCG_TERML

12

C465

470P_0402_50V7 K

HL_REF 18

12

R416

@0_0402_5%

VREFCG 16

VREFGC 16

D D

G_AD[0..31]16

C C

G_ST0

0=System memory is DDR

1=System memory is SDR

R397

G_ST0

12

2K_0603_5%

B B

G_ST1

0=533Mhz

1=400Mhz

G_ST1

R399

@1K_0603_1%

H_BSEL0# 6,8

12

R398

@2K_0603_1%

12

A A

G_C/BE#[0..3]16

G_ST016

G_ST116

G_ST216

G_AD_STB016

G_AD_STB0#16

G_AD_STB116

G_AD_STB1#16

G_SB_STB16

G_SB_STB#16

G_FRAME#16

G_DEVSEL#16

G_IRDY#16

G_TRDY#16

G_STOP#16

G_PAR16

G_REQ#16

G_GNT#16

G_PIPE#16

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE#0 VREFGC

G_C/BE#1

G_C/BE#2

G_C/BE#3

G_ST0

G_ST1

G_ST2

G_AD_STB0

G_AD_STB0#

G_AD_STB1

G_AD_STB1#

G_SB_STB

G_SB_STB#

G_FRAME#

G_DEVSEL#

G_IRDY#

G_TRDY#

G_STOP#

G_PAR

G_REQ#

G_GNT#

G_PIPE#

R27

R28

R25

U27

U28

U23

U24

U25

AA28

AB25

AB27

AA27

AB26

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

AA23

AG25

AF24

AG26

R24

R23

AC27

AC28

AF27

AF26

W28

W27

W24

W23

W25

AG24

AH25

AF22

N22

M23

T25

T26

T27

V26

V27

T23

T24

V24

Y27

Y26

Y23

V25

V23

Y25

Y24

K27

K5

L24

K7

J26

A3

A7

A11

A15

U7B

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE#0

G_C/BE#1

G_C/BE#2

G_C/BE#3

ST0

ST1

ST2

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

SB_STB

SB_STB#

G_FRAME#

G_DEVSEL#

G_IRDY#

G_TRDY#

G_STOP#

G_PAR

G_REQ#

G_GNT#

PIPE#

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HUB

HI_7

HI_8

HI_9

HI_10

HI_STB

HI_STB#

HLRCOMP

HI_REF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

AGP

SBA6

SBA7

AGPREF

GRCOMP

66IN

RBF#

WBF#

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

RG82845MP_BGA-593

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

N25

N24

P27

P26

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AA21

AD25

P22

AE22

AE23

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J29

HUB_HL0

HUB_HL1

HUB_HL2

HUB_HL3

HUB_HL4

HUB_HL5

HUB_HL6

HUB_HL7

HUB_HL8

HUB_HL9

HUB_HL10

HUB_HLSTRB

HUB_HLSTRB#

HLRCOMP

G_SBA0

G_SBA1

G_SBA2

G_SBA3

G_SBA4

G_SBA5

G_SBA6

G_SBA7

AGP_RCOMP

CK_66M_MCH

G_RBF#

G_WBF#

HUB_HLSTRB 18

HUB_HLSTRB# 18

R411 36.5_0603_1%1 2

CK_66M_MCH 6

G_RBF# 16

G_WBF# 16

CK_66M_MCH

@33_0402_5%

@10P_0402_50V8 J

HUB_HL[0..10] 18

G_SBA[0..7] 16

VREFGC

12

C435

0.1U_0402_16V4Z

12

R393

CK66M_MCH_TERM

12

C428

+1.8VRUN

1 2

Place closely ball P26

Place this cap near MCH

R402

12

36.5_0603_1%

Place closely to pin P22

0.1U_0402_16V4Z

C454

HL_REF 18

AGP Interface Reference

Place close to MCH-M

5

4

3

2

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

Brookdale MCH-M (2/3)

ADQ00/LA-1351

12 50Wednesday, October 23, 2002

1

X025

5

4

3

2

1

12

0.047U_0402_10V4M

C434

0.047U_0402_10V4M

1 2

C429

12

12

0.047U_0402_10V4M

C382

+2.5V_MEM

1

+1.5VRUN

12

+

+VCC_CORE

12

+

+2.5V_MEM

12

+

0.047U_0402_10V4M

C392

12

+

C687

150U_D_6.3VM

13 50Wednesday, October 23, 2002

C70

150U_D_6.3VM

C411

150U_D_10VM_R40

C78

150U_D_6.3VM

X025

0402

U7D

+VCC_CORE

D D

+2.5V_MEM

C C

B B

A A

M8

VTT_0

U8

VTT_1

AA9

VTT_2

AB8

VTT_3

AB18

VTT_4

AB20

VTT_5

AC19

VTT_6

AD18

VTT_7

AD20

VTT_8

AE19

VTT_9

AE21

VTT_10

AF18

VTT_11

AF20

VTT_12

AG19

VTT_13

AG21

VTT_14

AG23

VTT_15

AJ19

VTT_16

AJ21

VTT_17

AJ23

VTT_18

A5

VCCSM1

A9

VCCSM2

A13

VCCSM3

A17

VCCSM4

A21

VCCSM5

A25

VCCSM6

C1

VCCSM7

C29

VCCSM8

D7

VCCSM9

D11

VCCSM10

D15

VCCSM11

D19

VCCSM12

D23

VCCSM13

D25

VCCSM14

F6

VCCSM15

F10

VCCSM16

F14

VCCSM17

F18

VCCSM18

F22

VCCSM19

G1

VCCSM20

G4

VCCSM21

G29

VCCSM22

H8

VCCSM23

H10

VCCSM24

H12

VCCSM25

H14

VCCSM26

H16

VCCSM27

H18

VCCSM28

H20

VCCSM29

H22

VCCSM30

H24

VCCSM31

K22

VCCSM32

K24

VCCSM33

K26

VCCSM34

L23

VCCSM35

K6

VCCSM36

J5

VCCSM37

J7

VCCSM38

L1

VSS41

L4

VSS42

L6

VSS43

L8

VSS44

L22

VSS45

L26

VSS46

N1

VSS47

N4

VSS48

N8

VSS49

N13

VSS50

N15

VSS51

N17

VSS52

N29

VSS53

P6

VSS54

P8

VSS55

P14

VSS56

P16

VSS57

R1

VSS58

R4

VSS59

R13

VSS60

R15

VSS61

R17

VSS62

R26

VSS63

T6

VSS64

T8

VSS65

T14

VSS66

T16

VSS67

T22

VSS68

U1

VSS69

U4

VSS70

U15

VSS71

U29

VSS72

V6

VSS73

V8

VSS74

V22

VSS75

W1

VSS76

W4

VSS77

W8

VSS78

W26

VSS79

Y6

VSS80

Y22

VSS81

AA1

VSS82

RG82845MP_BGA-593

5

POWER/GND

VCC1_5_0

VCC1_5_1

VCC1_5_2

VCC1_5_3

VCC1_5_4

VCC1_5_5

VCC1_5_6

VCC1_5_7

VCC1_5_8

VCC1_5_9

VCC1_5_10

VCC1_5_11

VCC1_5_12

VCC1_5_13

VCC1_5_14

VCC1_5_15

VCC1_5_16

VCC1_5_17

VCC1_5_18

VCC1_5_19

VCC1_5_20

VCC1_5_21

VCC1_5_22

VCC1_5_23

VCC1_5_24

VCC1_5_25

VCC1_8_0

VCC1_8_1

VCC1_8_2

VCC1_8_3

VCC1_8_4

VCCGA1

VCCHA1

VSSGA2

VSSHA2

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

R22

R29

U22

U26

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

L29

N26

L25

M22

N23

T17

T13

U17

U13

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ3

AJ5

AJ7

AJ9

AJ11

AJ13

AJ15

AJ17

AJ27

VCC_MCH_PLL1

VCC_MCH_PLL0

VSS_MCH_PLL1

VSS_MCH_PLL0

+1.5VRUN

Layout note :

Trace width >20mil ;

Spacing 10mil

Trace A to ball U13/T13 or

U17/T7 =1.5" Max

C461

12

0.1U_0402_16V4Z

"Trace A"

12

+

12

12

12

12

4

C68

33U_D2_16VM_R70

12

0.047U_0402_10V4M

C407

C462

12

C537

0.1U_0402_10V6K

12

C510

C532

0.1U_0402_10V6K

0.1U_0402_10V6K

12

C519

C520

0.1U_0402_10V6K

0.1U_0402_10V6K

12

C503

C525

0.1U_0402_10V6K

0.1U_0402_10V6K

"Trace A"

C436

12

0.1U_0402_16V4Z

4.7U_LQG21N4R7K10_30M_10%_0805

4.7U_LQG21N4R7K10_30M_10%_0805

12

0.047U_0402_10V4M

12

C538

0.1U_0402_10V6K

12

C533

0.1U_0402_10V6K

12

C502

0.1U_0402_10V6K

12

C501

0.1U_0402_10V6K

12

+

C55

33U_D2_16VM_R70

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C466

C363

12

12

C516

C547

0.1U_0402_10V6K

12

12

C517

C534

0.1U_0402_10V6K

12

12

C514

C512

0.1U_0402_10V6K

12

12

C500

C554

0.1U_0402_10V6K

12

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

C437

0.1U_0402_16V4Z

L27

12

12

L26

12

12

0.047U_0402_10V4M

C420

12

12

C553

C552

0.1U_0402_10V6K

12

12

C551

C518

0.1U_0402_10V6K

12

12

C513

C515

0.1U_0402_10V6K

12

12

C160

C499

0.1U_0402_10V6K

C464

12

0.1U_0402_16V4Z

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C388

C358

12

12

C544

0.1U_0402_10V6K

0.1U_0402_10V6K

12

12

C550

0.1U_0402_10V6K

0.1U_0402_10V6K

12

12

C539

0.1U_0402_10V6K

0.1U_0402_10V6K

12

12

C564

0.1U_0402_10V6K

0.1U_0402_10V6K

3

12

+1.8VRUN

C71

10U_1206_6.3V7K

1 2

12

0.047U_0402_10V4M

C460

12

C524

C545

0.1U_0402_10V6K

0.1U_0402_10V6K

12

C548

C549

0.1U_0402_10V6K

0.1U_0402_10V6K

12

C541

C540

0.1U_0402_10V6K

0.1U_0402_10V6K

12

C192

C563

0.1U_0402_10V6K

0.1U_0402_10V6K

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C399

C408

+1.5VRUN

12

12

0.047U_0402_10V4M

C455

12

12

C536

C546

0.1U_0402_10V6K

12

12

C555

C523

0.1U_0402_10V6K

12

12

C543

C542

0.1U_0402_10V6K

12

12

C526

C527

0.1U_0402_10V6K

12

12

0.047U_0402_10V4M

C409

12

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C391

C449

12

C535

0.1U_0402_10V6K

0.1U_0402_10V6K

12

12

C522

0.1U_0402_10V6K

0.1U_0402_10V6K

12

12

C530

0.1U_0402_10V6K

0.1U_0402_10V6K

12

12

C528

0.1U_0402_10V6K

0.1U_0402_10V6K

12

0.047U_0402_10V4M

C458

0402

12

0.047U_0402_10V4M

C397

0402

C521

0.1U_0402_10V6K

C531

0.1U_0402_10V6K

C529

0.1U_0402_10V6K

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C400

C453

12

0.047U_0402_10V4M

C417

12

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C421

C422

12

12

C557

10U_1206_6.3V7K

12

0.047U_0402_10V4M

C456

12

12

0.047U_0402_10V4M

C375

12

0.047U_0402_10V4M

C410

C351

V_1P25V_DDR_VTT

C190

10U_1206_6.3V7K

2

12

12

0.047U_0402_10V4M

C463

C459

0402

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C423

C369

12

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C401

C350

12

12

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C432

C433

12

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C384

C442

12

12

12

0.047U_0402_10V4M

0.047U_0402_10V4M

0.047U_0402_10V4M

C451

C366

V_1P25V_DDR_VTT

Title

Size Document Number Rev

Date: Sheet of

12

0.047U_0402_10V4M

C416

C389

12

0.047U_0402_10V4M

0.047U_0402_10V4M

C443

C424

12

12

0.047U_0402_10V4M

C383

C457

12

+

C686

150U_D_6.3VM

0.047U_0402_10V4M

0.047U_0402_10V4M

0.047U_0402_10V4M

12

0.047U_0402_10V4M

C360

Compal Electronics, Inc.

Brookdale MCH-M (3/3)

ADQ00/LA-1351

5

4

3

2

1

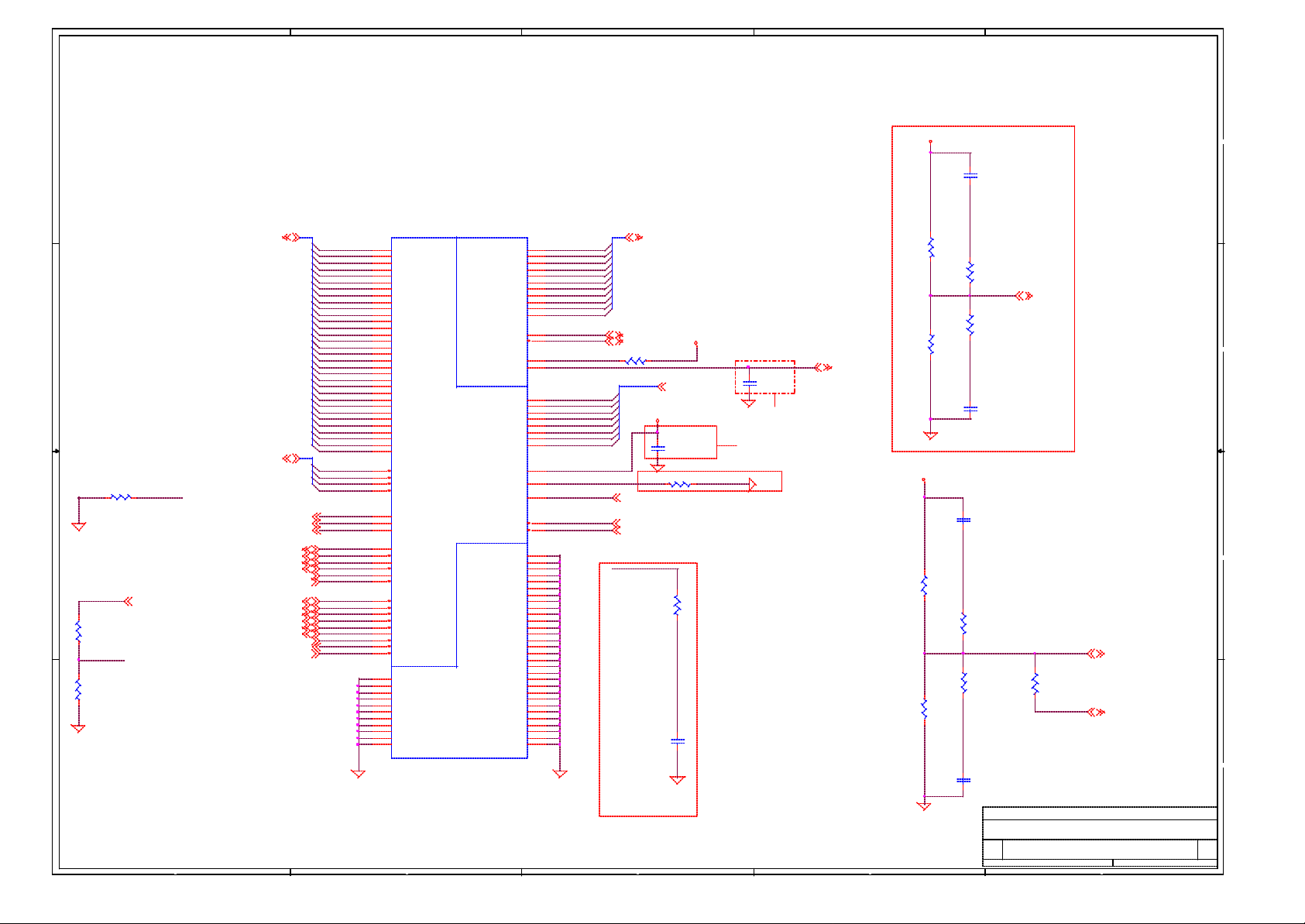

DDR_D[0..63]11

DDR_CB[0..7]11

DDR_DS[0..8]11

D D

C C

B B

A A

RN20 22_0402_4P2R_5%

DDR_CB4

DDR_CB0

DDR_D31

DDR_D27

DDR_D30

DDR_D26

DDR_DS3

DDR_D29

DDR_D25

DDR_D28

DDR_D24

DDR_D23

DDR_D19

DDR_D22

DDR_D18

DDR_DS2

DDR_D21

DDR_D17

DDR_D20

DDR_D16

DDR_D15

DDR_D11

DDR_D14

DDR_D10

DDR_DS1

DDR_D13

DDR_D9

DDR_D12

DDR_D8

DDR_D7

DDR_D3

DDR_D6

DDR_D2

DDR_DS0

DDR_D5

DDR_D1

DDR_D4

DDR_D0

DDR_CB7

DDR_CB3

DDR_CB6

DDR_CB2

DDR_DS8

DDR_CB5

DDR_CB1

DDR_D63

DDR_D59

DDR_D62

DDR_D58

DDR_DS7

DDR_D61

1 4

2 3

RN40 22_0402_4P2R_5%

1 4

2 3

RN19 22_0402_4P2R_5%

1 4

2 3

RN39 22_0402_4P2R_5%

1 4

2 3

RN18 22_0402_4P2R_5%

1 4

2 3

RN38 22_0402_4P2R_5%

1 4

2 3

RN17 22_0402_4P2R_5%

1 4

2 3

RN37 22_0402_4P2R_5%

1 4

2 3

RN16 22_0402_4P2R_5%

1 4

2 3

RN36 22_0402_4P2R_5%

1 4

2 3

RN35 22_0402_4P2R_5%

1 4

2 3

RN15 22_0402_4P2R_5%

1 4

2 3

RN34 22_0402_4P2R_5%

1 4

2 3

RN14 22_0402_4P2R_5%

1 4

2 3

RN33 22_0402_4P2R_5%

1 4

2 3

RN13 22_0402_4P2R_5%

1 4

2 3

RN32 22_0402_4P2R_5%

1 4

2 3

RN12 22_0402_4P2R_5%

1 4

2 3

RN31 22_0402_4P2R_5%

1 4

2 3

RN22 22_0402_4P2R_5%

1 4

2 3

RN42 22_0402_4P2R_5%

1 4

2 3

RN21 22_0402_4P2R_5%

1 4

2 3

RN41 22_0402_4P2R_5%

1 4

2 3

RN57 22_0402_4P2R_5%

1 4

2 3

RN30 22_0402_4P2R_5%

1 4

2 3

RN56 22_0402_4P2R_5%

1 4

2 3

DDR_CB4_R

DDR_CB0_R

DDR_D31_R

DDR_D27_R

DDR_D30_R

DDR_D26_R

DDR_DS3_R

DDR_D29_R

DDR_D25_R

DDR_D28_R

DDR_D24_R

DDR_D23_R

DDR_D19_R

DDR_D22_R

DDR_D18_R

DDR_DS2_R

DDR_D21_R

DDR_D17_R

DDR_D20_R

DDR_D16_R

DDR_D15_R

DDR_D11_R

DDR_D14_R

DDR_D10_R

DDR_DS1_R

DDR_D13_R

DDR_D9_R

DDR_D12_R

DDR_D8_R

DDR_D7_R

DDR_D3_R

DDR_D6_R

DDR_D2_R

DDR_DS0_R

DDR_D5_R

DDR_D1_R

DDR_D4_R

DDR_D0_R

DDR_CB7_R

DDR_CB3_R

DDR_CB6_R

DDR_CB2_R

DDR_DS8_R

DDR_CB5_R

DDR_CB1_R

DDR_D63_R

DDR_D59_R

DDR_D62_R

DDR_D58_R

DDR_DS7_R

DDR_D61_R

5

Layout Note:

Place these resistor

closely DIMM0,all

trace length<750 mil

RN29 22_0402_4P2R_5%

DDR_D57

DDR_D60

DDR_D56

DDR_D55

DDR_D51

DDR_D54

DDR_D50

DDR_DS6

DDR_D53

DDR_D49

DDR_D52

DDR_D48

DDR_D47

DDR_D43

DDR_D46

DDR_D42

DDR_DS5

DDR_D45

DDR_D41

DDR_D44

DDR_D40

DDR_D39

DDR_D35

DDR_D38

DDR_D34

DDR_DS4

DDR_D37

DDR_D33

DDR_D36

DDR_D32

1 4

2 3

RN55 22_0402_4P2R_5%

1 4

2 3

RN28 22_0402_4P2R_5%

1 4

2 3

RN54 22_0402_4P2R_5%

1 4

2 3

RN27 22_0402_4P2R_5%

1 4

2 3

RN53 22_0402_4P2R_5%

1 4

2 3

RN52 22_0402_4P2R_5%

1 4

2 3

RN26 22_0402_4P2R_5%

1 4

2 3

RN51 22_0402_4P2R_5%

1 4

2 3

RN25 22_0402_4P2R_5%

1 4

2 3

RN50 22_0402_4P2R_5%

1 4

2 3

RN24 22_0402_4P2R_5%

1 4

2 3

RN49 22_0402_4P2R_5%

1 4

2 3

RN23 22_0402_4P2R_5%

1 4

2 3

RN48 22_0402_4P2R_5%

1 4

2 3

Layout Note:

Place these resistor

closely DIMM0,all

trace length<750 mil

DDR_D57_R

DDR_D60_R

DDR_D56_R

DDR_D55_R

DDR_D51_R

DDR_D54_R

DDR_D50_R

DDR_DS6_R

DDR_D53_R

DDR_D49_R

DDR_D52_R

DDR_D48_R

DDR_D47_R

DDR_D43_R

DDR_D46_R

DDR_D42_R

DDR_DS5_R

DDR_D45_R

DDR_D41_R

DDR_D44_R

DDR_D40_R

DDR_D39_R

DDR_D35_R

DDR_D38_R

DDR_D34_R

DDR_DS4_R

DDR_D37_R

DDR_D33_R

DDR_D36_R

DDR_D32_R

DDR_BS011,15

DDR_WE#11,15

DDR_CAS#11,15

DDR_RAS#11,15

DDR_BS111,15

4

Layout Note:

Place these resistor

closely DIMM0,all

trace length

Max=1.3"

V_1P25V_DDR_VTT

RN75 56_0402_4P2R_5%

RN81 56_0402_4P2R_5%

DDR_MA[0..12]11,15

RN61 10_0404_4P2R_5%

DDR_BS0

DDR_WE#

DDR_CAS#

DDR_RAS#

DDR_BS1

DDR_MA0

DDR_MA1

DDR_MA10

DDR_MA2

DDR_MA4

DDR_MA5

DDR_MA3

DDR_MA6

DDR_MA8

DDR_MA9

DDR_MA7

DDR_MA11

DDR_MA12

1 4

2 3

RN47 10_0404_4P2R_5%

1 4

2 3

RN46 10_0404_4P2R_5%

1 4

2 3

RN60 10_0404_4P2R_5%

1 4

2 3

RN45 10_0404_4P2R_5%

1 4

2 3

RN62 10_0404_4P2R_5%

1 4

2 3

RN44 10_0404_4P2R_5%

1 4

2 3

RN59 10_0404_4P2R_5%

1 4

2 3

RN43 10_0404_4P2R_5%

1 4

2 3

RN58 10_0404_4P2R_5%

1 4

2 3

DDR_CKE0_DIMM0

14

23

DDR_CKE1_DIMM0

DDR_CS0_DIMM0#

23

14

DDR_CS1_DIMM0#

DDR_BS0_R

DDR_WE_R#

DDR_CAS_R#

DDR_RAS_R#

DDR_BS1_R

DDR_MA0_R

DDR_MA1_R

DDR_MA10_R

DDR_MA2_R

DDR_MA4_R

DDR_MA5_R

DDR_MA3_R

DDR_MA6_R

DDR_MA8_R

DDR_MA9_R

DDR_MA7_R

DDR_MA11_R

DDR_MA12_R

JDIM1

1

VREF

3

VSS

DIMM0_ID

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113