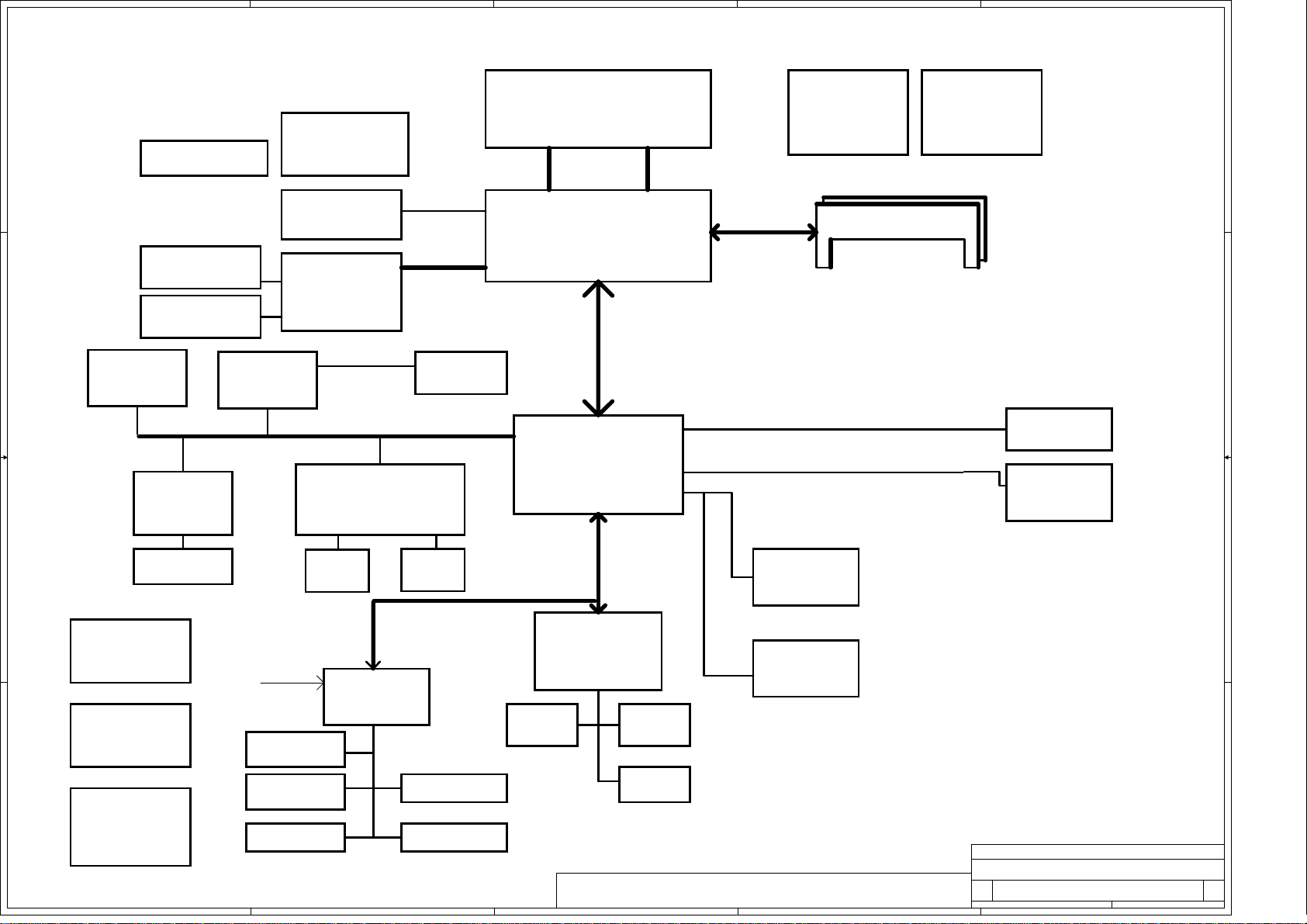

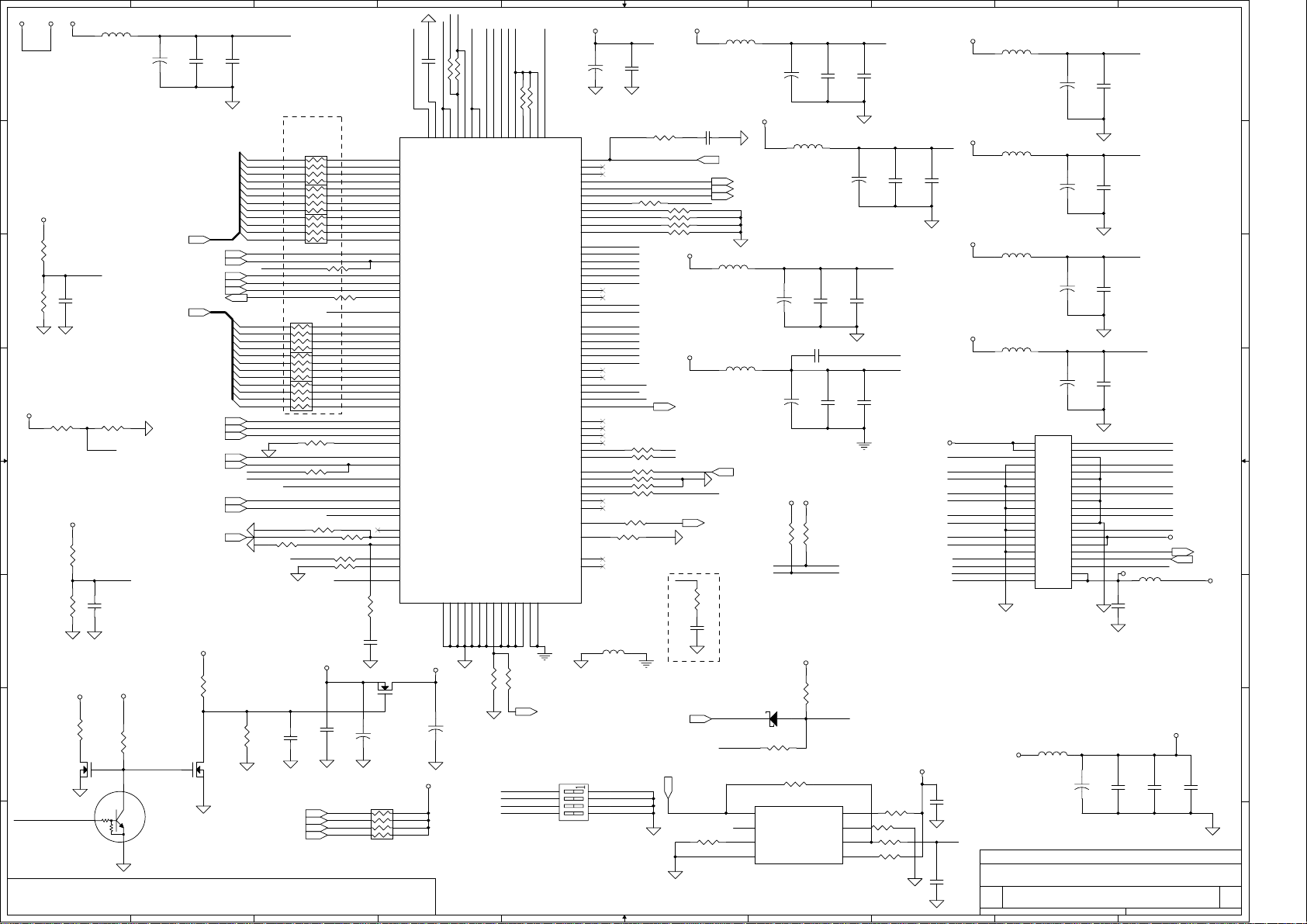

Acer LA-1341 Schematics

A

Compal confidential

File Name : LA-1341

B

C

D

E

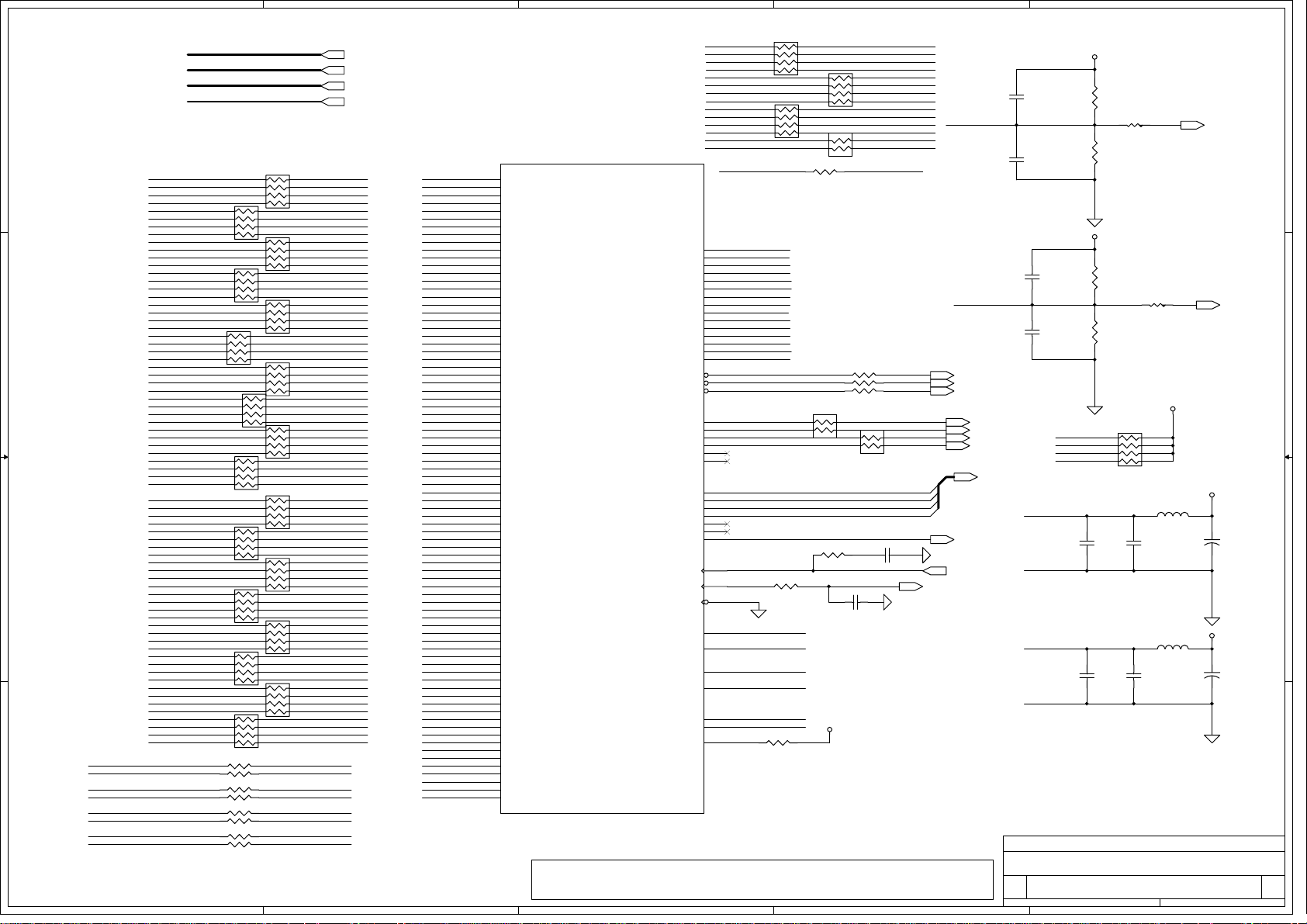

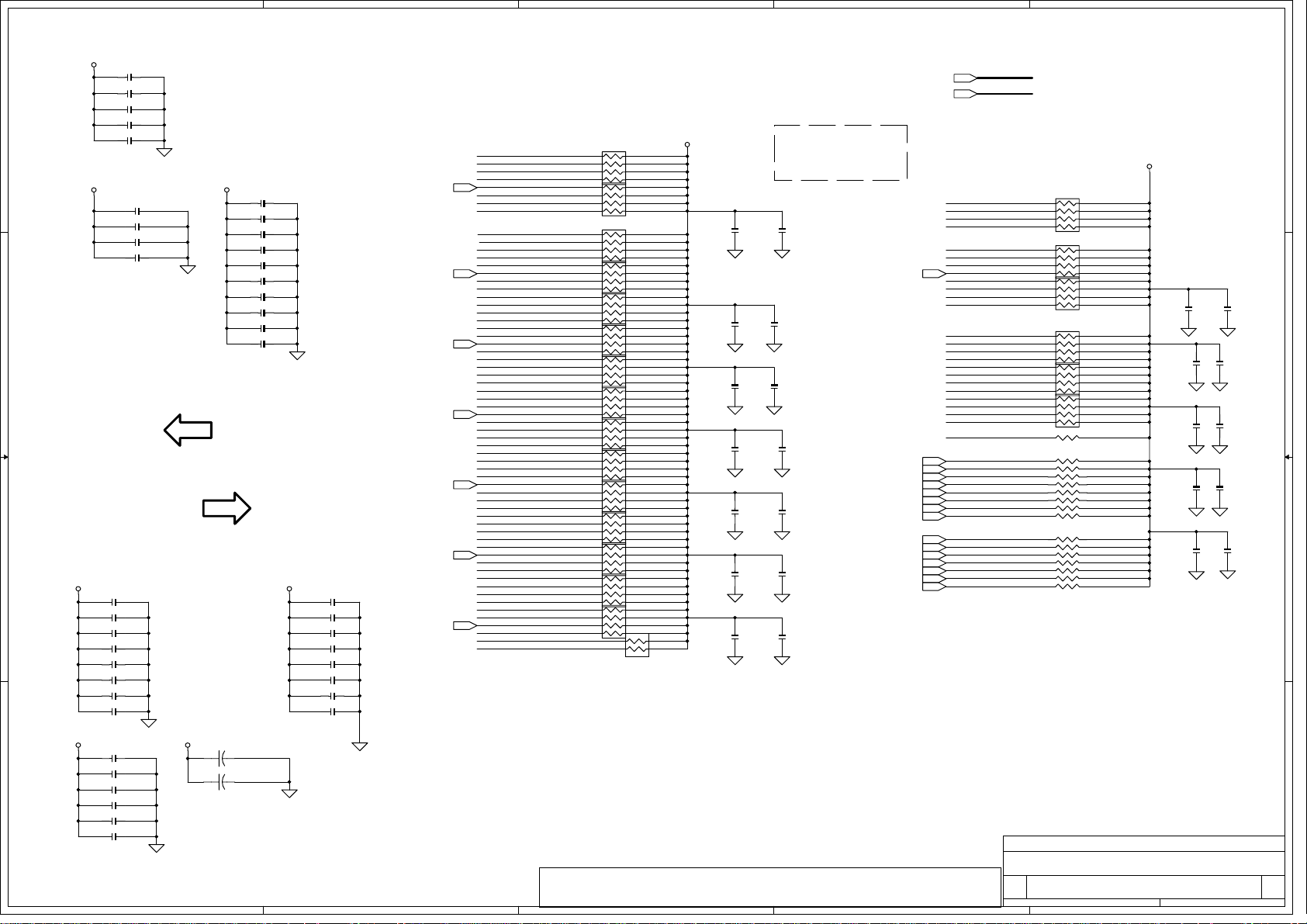

Block Diagram

Mobil e Nort hwood

1 1

CPU B ypass

Fan Cont rol

page 3

& CPUVID

page 5

uFCBGA/ uFC PGA CPU

page 3,4,5

System Bus

400MHz

HD#(0..63)HA#( 3..31)

Therm al Sensor

MAX1617

page 3

Clock Generator

page 12,13

Memory

CRT C onn

page 14

SIS 650

315 Graphics embedded

LCD C onn

page 15

TV-OUT Conn

IDSEL:AD16

(PIRQC#,GNT#0,REQ#0)

2 2

IEEE 1394

VT6306

page 22

page 14

Mini PCI

port

SIS302L V

( LVDS/TVOUT )

page 15

page 26

IDSEL:AD31

(PIRQB#,GNT#1,REQ#1)

VB BUS

MUTIOL

RJ11 Conn

page 26

BGA

page6,7,8,9

PCI BUS

IDSEL:AD17

(PIRQC#,GNT#3,REQ#3)

RTL 8100BL

LAN

page 21

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

CardBus Controller

ENE C B1420

3.3V 33MHz

SIS 961

page 16,17,18,19

page 23

BUS(DDR)

2.5V DDR 200/266 MHz

3.3V 48MHz

3.3V 24.57 6MHz

3.3V ATA100

DDR-SO-DIMM X2

BANK 0, 1, 2, 3

page 10,11

AC-LINK

USB conn

page 31

AC-LINK

CONN

page 25

3 3

RJ45

page 26

Slot 1

page 24

Slot 0

page 24

Power On/Off

Reset & RTC

page 32

DC/DC Interface

Suspend

page 33

4 4

Power Circuit

DC/DC

page

33,34,35,36,37,38,39

A

14M_5V

Touch Pad

page 28

EC I/O Buffer

page 30

BIOS

page 30 page 32

EC NS87591

page 29

B

Int.KBD

PS/2 conn

page 28

LPC BUS

3.3V 33MHz

SMsC

LPC 47N227

LPC to X-BUS &

Super I/O

page 27

SERIALPARALLEL

page 31 page 27

FDD

page 28

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

HDD IDE

Connector

page 22

CDROM IDE

Connector

page 22

Title

Size Docu ment Number Re v

D

Date: Sheet

Compal E l e c t r onics, Inc.

401210

星期五 十一

?15, 2002

SCHEMATIC, M/B LA-1341

246,

E

2A

of

A

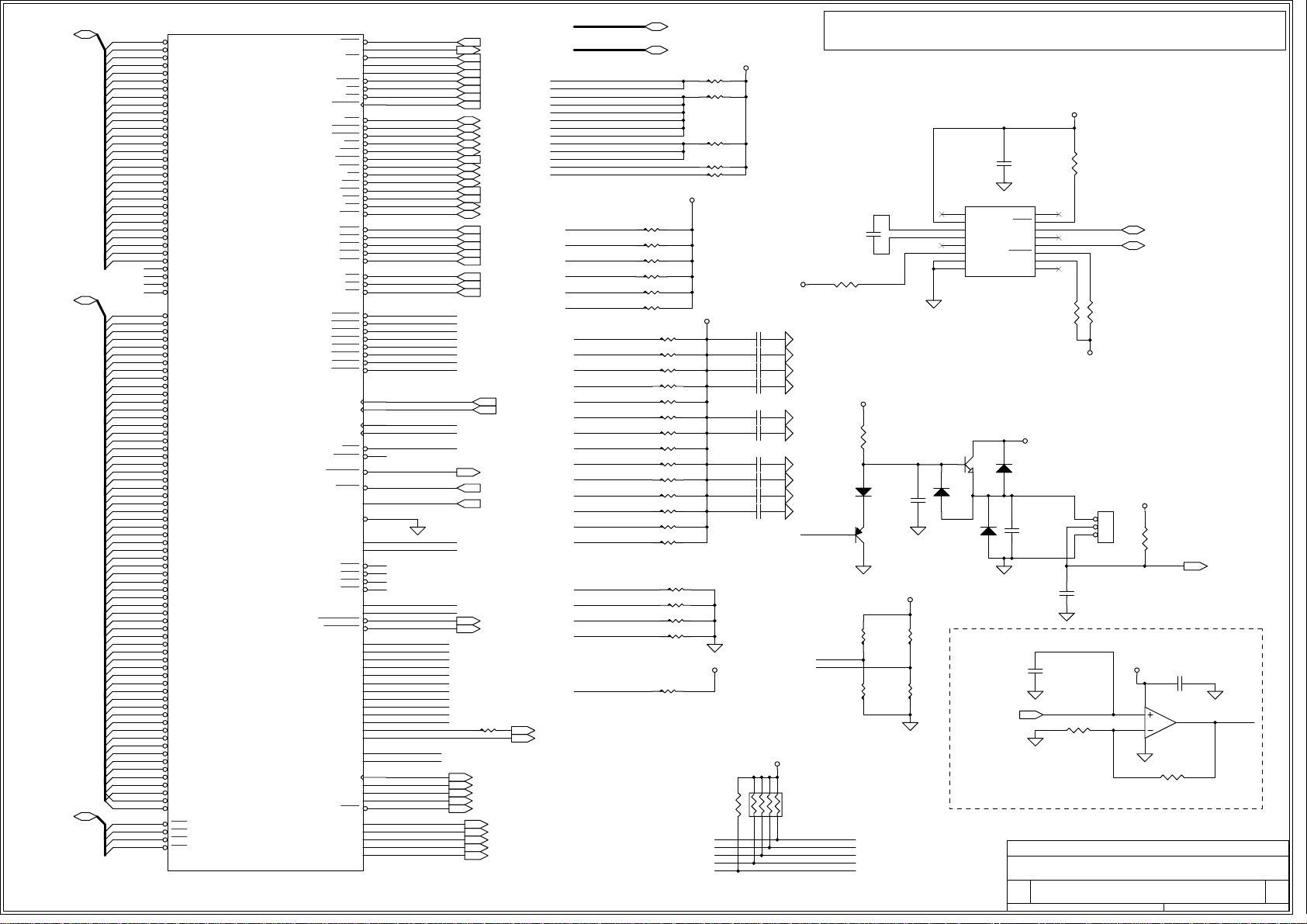

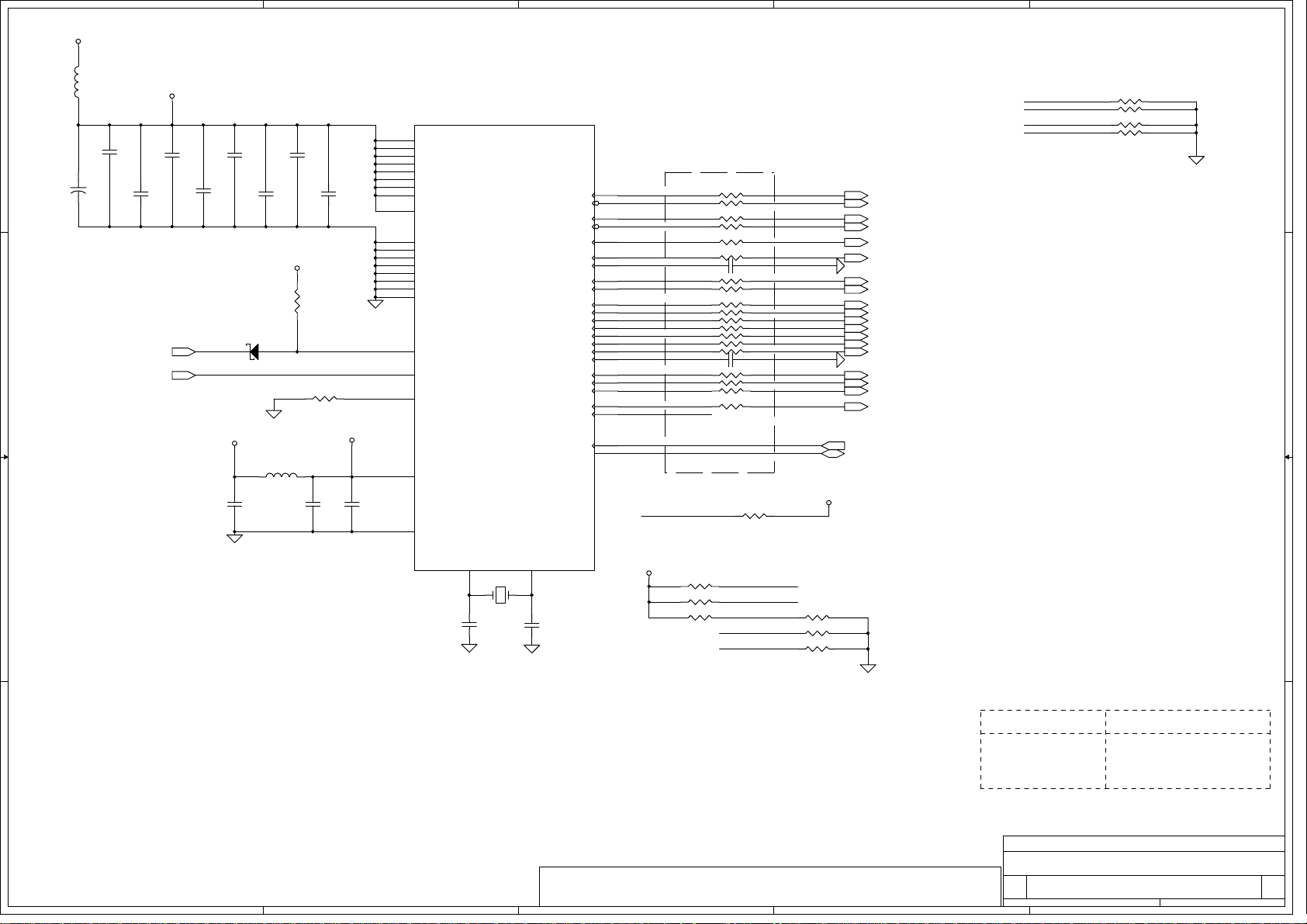

HTEST0

HTEST1

HTEST2

HTEST3

HTEST4

HTEST5

HTEST6

HTEST7

HTEST8

HTEST9

HTEST10

HTEST12

HTEST11

PROCHOT#

HDSTBP#[0..3]

HDSTBN#[0..3]

ITP_CLK#

ITP_CLK

TDI

TDO

TMS

STPCLK#

SMI#

CPUSLP#

INIT#

CPUPW RGD

FERR#

IERR#

TRIP#

A20M#

IGNNE#

INTR

NMI

BREQ0#

CPURST#

TCK

TRST#

CPU_COMP0

CPU_COMP1

DBRESET

R3

R4

R5

R6

R7

R9 39

HA[3..31]6

HD[0..63]6

1 1

DBI#[0..3]6

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

DBI#0

DBI#1

DBI#2

DBI#3

U1A

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

B21

D#0

B22

D#1

A23

D#2

A25

D#3

C21

D#4

D22

D#5

B24

D#6

C23

D#7

C24

D#8

B25

D#9

G22

D#10

H21

D#11

C26

D#12

D23

D#13

J21

D#14

D25

D#15

H22

D#16

E24

D#17

G23

D#18

F23

D#19

F24

D#20

E25

D#21

F26

D#22

D26

D#23

L21

D#24

G26

D#25

H24

D#26

M21

D#27

L22

D#28

J24

D#29

K23

D#30

H25

D#31

M23

D#32

N22

D#33

P21

D#34

M24

D#35

N23

D#36

M26

D#37

N26

D#38

N25

D#39

R21

D#40

P24

D#41

R25

D#42

R24

D#43

T26

D#44

T25

D#45

T22

D#46

T23

D#47

U26

D#48

U24

D#49

U23

D#50

V25

D#51

U21

D#52

V22

D#53

V24

D#54

W26

D#55

Y26

D#56

W25

D#57

Y23

D#58

Y24

D#59

Y21

D#60

AA25

D#61

AA22

D#62

AA24

D#63

E21

DBI0

G25

DBI1

P26

DBI2

V21

DBI3

ZIF_SOCKET478_478P

A20M

FERR

INIT

LINT0

LINT1

IGNNE

SMI

SLP

STPCLK

ADS

ADSTB0

ADSTB1

BNR

DBSY

DEFER

DRDY

HITM

TRDY

BPRI

BR0

LOCK

REQ0

REQ1

REQ2

REQ3

REQ4

RS0

RS1

RS2

DSTBP0

DSTBN0

DSTBP1

DSTBN1

DSTBP2

DSTBN2

DSTBP3

DSTBN3

BCLK0

BCLK1

ITP_CLK1

ITP_CLK0

IERR

MCERR

DBRESET

RESET

PWRGOOD

VSS75

COMP0

COMP1

DEP0

DEP1

DEP2

DEP3

THERMDA

THERMDC

THERMTRIP

PROCHOT

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

BSEL0

BSEL1

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

A20M#

C6

FERR#

B6

INIT#

W5

INTR

D1

NMI

E5

IGNNE#

B2

SMI#

B5

CPUSLP#

AB26

STPCLK#

Y4

G1

L5

R5

G2

H5

E2

H2

F3

HIT

E3

J6

D2

BREQ0#

H6

G4

J1

K5

J4

J3

H3

F1

G5

F4

HDSTBP#0

F21

HDSTBN#0

E22

HDSTBP#1

J23

HDSTBN#1

K22

HDSTBP#2

P23

HDSTBN#2

R22

HDSTBP#3

W23

HDSTBN#3

W22

AF22

AF23

AD26

AC26

AC3

V6

AE25

AB25

AB23

CPU_CLK

CPU_CLK#

ITP_CLK#

ITP_CLK

IERR#

DBRESET

CPURST#

CPUPWRGD

A20M# 17

FERR# 17

INIT# 17

INTR 17

NMI 17

IGNNE# 17

SMI# 17

CPUSLP# 17

STPCLK# 17

ADS# 6

HASTB0# 6

HASTB1# 6

BNR# 6

DBSY# 6

DEFER# 6

DRDY# 6

HIT# 6

HITM# 6

HTRDY# 6

BPRI# 6

BREQ0# 6

HLOCK# 6

HREQ0# 6

HREQ1# 6

HREQ2# 6

HREQ3# 6

HREQ4# 6

RS0# 6

RS1# 6

RS2# 6

CPUCLK0 12

CPUCLK0# 12

ITP_DBR#

CPURST# 6

CPUPWRGD 6

AF26

CPU_COMP0

L24

CPU_COMP1

P1

J26

K25

K26

L25

H_THERMDA

B3

H_THERMDC

C4

TRIP#

A2

PROCHOT#

C3

HTEST0

AD24

HTEST1

AA2

HTEST2

AC21

HTEST3

AC20

HTEST4

AC24

HTEST5

AC23

HTEST6

AA20

HTEST7

AB22

HTEST8

U6

HTEST9

W4

HTEST10

Y3

HTEST11

A6

AD25

AD6

AD5

D4

C1

TDI

D5

F7

E6

AE5

AE4

AE3

AE2

AE1

HTEST12

BSEL0

BSEL1

TCK

TDI

TDO

TMS

TRST#

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

H_THERMTRIP#

H_PROCHOT# 4

R34 0

TCK

TDI

TDO

TMS

TRST#

CPU_VID0 39

CPU_VID1 39

CPU_VID2 39

CPU_VID3 39

CPU_VID4 39

PM_CPUPERF# 17

H_DPSLP# 17

HDST B P # [0 ..3 ] 6

HDSTBN#[0..3] 6

R512 56

R513 56

R514 56

R515 56

R525 56

+CPU_CORE

62_0603

1K

1K

150

75

+CPU_CORE

R12 56

R13 56

R14 56

R15 56

R16 51

R17 62_0603

R18 1K

R20 62_0603

R21 56

R22 56

R23 56

R24 56

R25 200

R27 51

R28 27

R29 680

R30 51.1_1%_0603

R32 51.1_1%_0603

+CPU_CORE

R538 150

A

C464

C465

C466

C467

C468

C469

C470

C471

C472

C473

R61

10K

+CPU_CORE

+3VS

182736

12

+5VS

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

0.1UF

12

45

RP5

8P4R_10K_0804

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+5VS

R1

10K

1 2

16

NC

15

14

13

NC

12

11

10

9

NC

R11

1K

1 2

+5VS

1 2

EC_SMC2 29

EC_SMD2 29

R10

10K

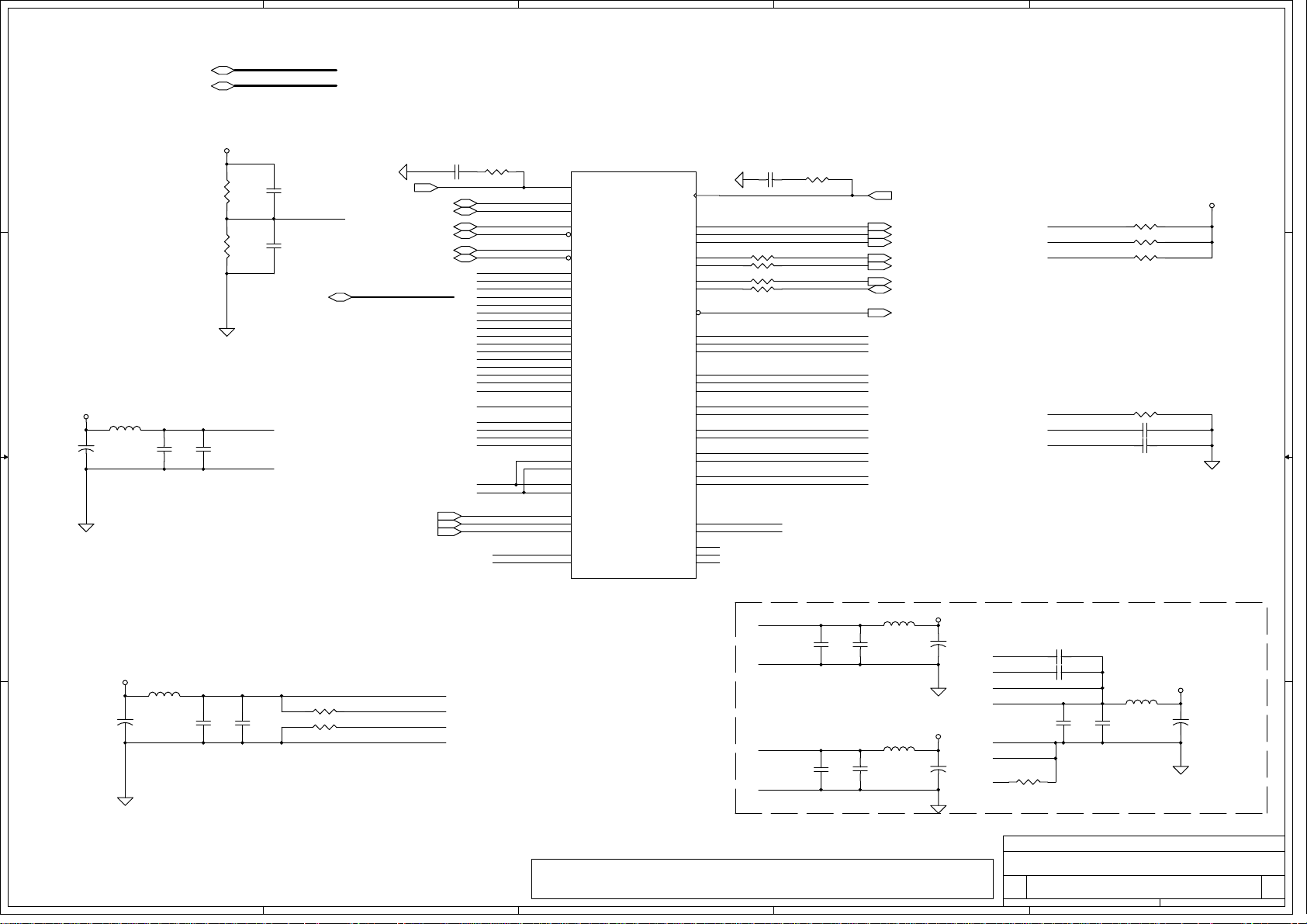

Thermal Sensor

MAX1617

12

C2

2200PF

R8 1K

12

H_THERMDA

H_THERMDC

W=15mil

U2

1

2

3

4

5

6

7

8

MAX1617

NC

VCC

DXP

DXN

NC

ADD1

GND

GND

C1

0.1UF

1 2

STBY

SMBCLK

SMBDATA

ALERT

ADD0

Fan1 Control circuit

+12VS

3.48K_1%_0603

FAN1

BSEL0

BSEL1

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

R19

2

1 2

21

D2

1N4148

CB1

2.2UF_16V_0805

31

Q2

2SA1036K

+3VS

R36

@1K

R40

@1K

FMMT619

1 2

R37

@1K

R41

@1K

Q1

@1SS355

2 1

2

D58

3 1

D3

1N4148

+5VS

D1

1SS355

2 1

+5VFAN1

C3

1000PF

2 1

C480

1000PF

12

C483

.1UF

EN_FAN129

Title

Size D o cument Numbe r R e v

Dat e : Sheet

1 2

R561

13K_1%_0603

Com pal Electronics, Inc.

SCHEMATIC, M/B LA-1341

401210

¬P , 15, 2002

期五 十一月

JP1

1

2

3

53398-0310

+5VS

+3VS

1

3

12

VCC

VEE

2 5

R562

R26

10K

.1UF

1 2

C484

4

U42

LMV321_SOT23-5

1 2

7.32K_1%_0603

FANSPEED1 29

3

of

FAN1

2A

46

A

B

C

D

E

AB9

VCC_CORE

VCC_CORE

GNDF2GND

F22

AC10

VCC_CORE

GND

F25

AC12

VCC_CORE

GNDF5GND

TP1

VCORE_SENSE BPM1

1

AB2

AC1

V5

VCC_SENSE

GND

W21

RSP

GNDV4GND

V26

V23

AC6

AP0

AP1

GND

GNDV1GNDU5GND

AC14

VCC_CORE

F8

AC16

VCC_CORE

GND

G21

AC18

VCC_CORE

GND

G24

AC8

AD11

AD13

VCC_CORE

VCC_CORE

VCC_CORE

GNDG3GNDG6GND

C22

AD15

AD17

VCC_CORE

VCC_CORE

GNDC9GNDY5GND

AD19

VCC_CORE

Y25

AE10

AE12

VCC_CORE

VCC_CORE

GND

GNDY2GNDW6GNDW3GND

Y22

AD9

AD7

VCC_CORE

VCC_CORE

A5

W24

AB5

BPM0

U25

AC4

BPM1

BPM2

GND

U22

AA5

BPM3Y6BPM4

GNDU2GNDT6GNDT3GND

+CPU_CORE Island >

AF2

VCC_CORE

VCC_CORE

GND

GND

B12

AF19

VCC_CORE

GND

B14

AF17

VCC_CORE

GND

B16

AF15

VCC_CORE

GND

B18

AF13

VCC_CORE

GND

B20

600ml

AE8

AF11

VCC_CORE

GND

B23

B26

AE6

VCC_CORE

VCC_CORE

GND

GNDB4GNDB8GND

AE20

VCC_CORE

AE18

VCC_CORE

C11

AE16

VCC_CORE

GND

C13

AE14

VCC_CORE

GND

C15

A10

VCC_CORE

GND

C17

A12

VCC_CORE

GND

C19

A14

VCC_CORE

GNDC2GND

A16

VCC_CORE

E11

A18

VCC_CORE

GND

E13

A20

VCC_CORE

GND

E15

AA10

VCC_COREA8VCC_CORE

GND

E17

E19

GND

AA12

VCC_CORE

GND

E23

AA14

E26

AA16

AA18

AA8

VCC_CORE

VCC_CORE

VCC_CORE

GND

GNDE4GNDE7GNDE9GND

AB11

VCC_CORE

VCC_CORE

F10

AB13

VCC_CORE

GND

F12

AB15

VCC_CORE

GND

F14

AB17

VCC_CORE

GND

F16

AB19

VCC_CORE

GND

F18

AB7

+CPU_CORE

AF21

AF5

AF7

U1B

4 4

3 3

2 2

1 1

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

E10

E12

E14

E16

E18

E20

F11

F13

F15

F17

F19

D10

K21

K24

L23

L26

M22

M25

N21

N24

P22

P25

R23

R26

D12

D14

D16

D18

D20

D24

D21

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

B7

B9

C8

D7

D9

E8

F9

D8

D6

D3

J2

J22

J25

J5

K3

K6

L1

L4

M2

M5

N3

N6

P2

P5

R1

E1

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AF9

VCC_CORE

VCC_CORE

VCC_CORE

GND

GND

GND

GND

GND

B10

AF6

AF8

AF16

AF18

AF20

AB4

AA3

AF4

AF3

BINIT

BPM5

VCCVIDPRG

VCCIOPLL

VSS_SENSE

GND

GND

ZIF_SOCKET478_478P

R4

T24

T21

BPM4

BPM5

BPM0

VCCVID

GTLREF

GTLREF

GTLREF

GTLREF

VCCA

VSSA

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AA21

AA6

F20

F6

AD20

AD22

AE23

A4

C7

C5

H1

H4

H23

H26

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

C25

+1.2VPP

CB3

1UF_10V_0603

C5

220PF

VCORE_PLL

VSS_PLL

VIO_PLL

VSS_SENSE

C6

220PF

GTLVREF2_CPU

1UF_10V_0603

PROCHOT#29

C7

220PF

VSS_SENSE

CB8

GTLVREF1_CPU

GTLVREF2_CPU

C8

220PF

L1

1 2

12

CB4

+

33UF_D2_16V

L2

1 2

12

CB6

+

33UF_D2_16V

1

TP2

+CPU_CORE

R43

49.9_1%_0603

2/3VCORE

R46

100_1%_0603

+5VALW

R56

1K

4.7UH_80mA

4.7UH_80mA

1 2

Q8

2

3 1

3904

(D)

+1.2VPP

1UF_10V_0603

R57

470

1 2

Q9

2

3 1

3904

BPM4

BPM5

BPM1

BPM0

+1.2VPP

CB7

10UF_10V_1206

GTLVREF1_CPU

CB9

R59

1 2

470

RP108

8P4R-56_0804

CB5

10UF_10V_1206

+CPU_CORE

R47

49.9_1%_0603

2/3VCORE

R51

100_1%_0603

+CPU_CORE

18

27

36

45

H_PROCHOT# 3

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

D

Title

SCHEMATIC, M/B LA-1341

Size D o cument Numbe r R e v

401210

Dat e : Sheet

Com pal Electronics, Inc.

期五 十一月

¬P , 15, 2002

446

E

2A

of

A

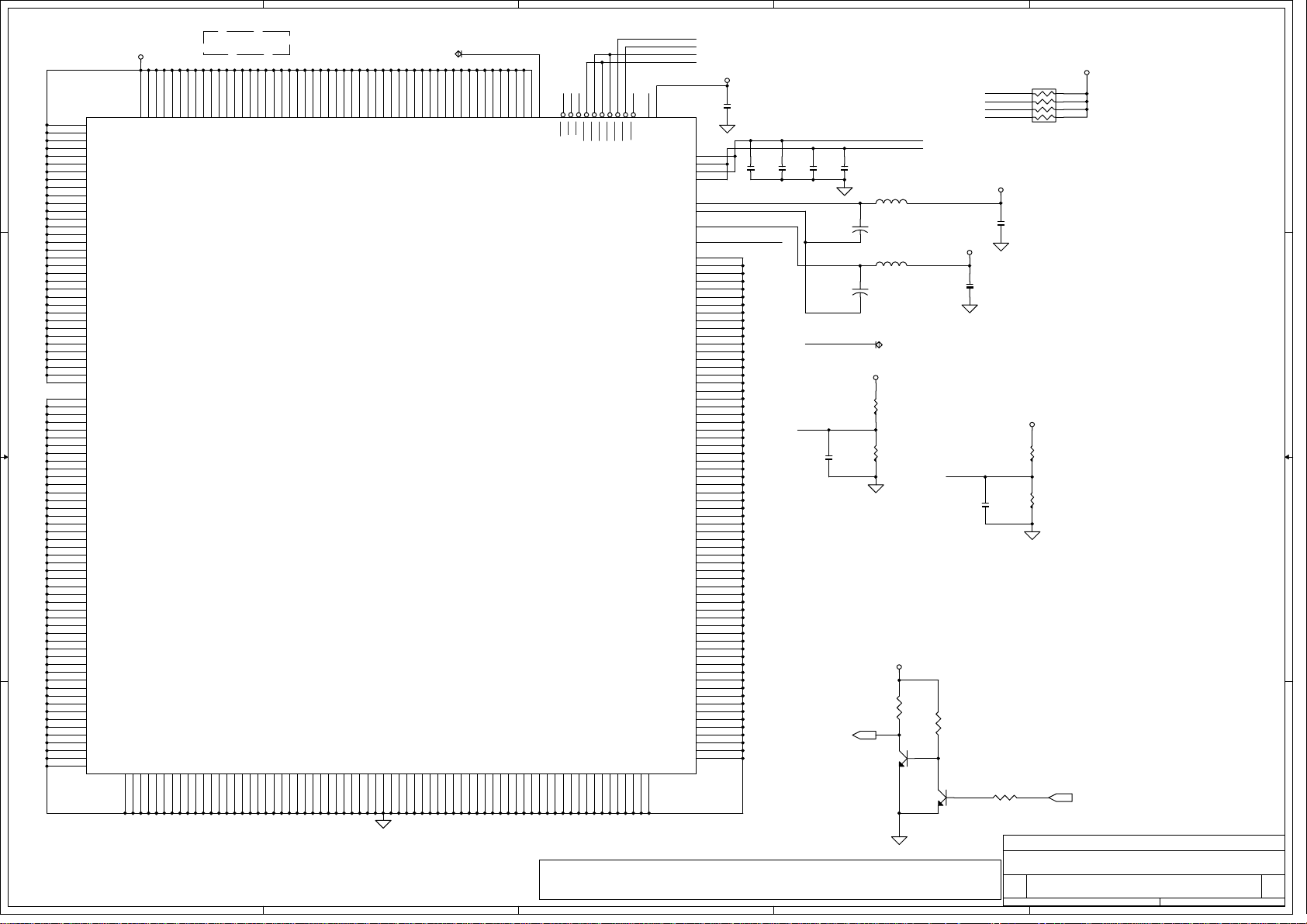

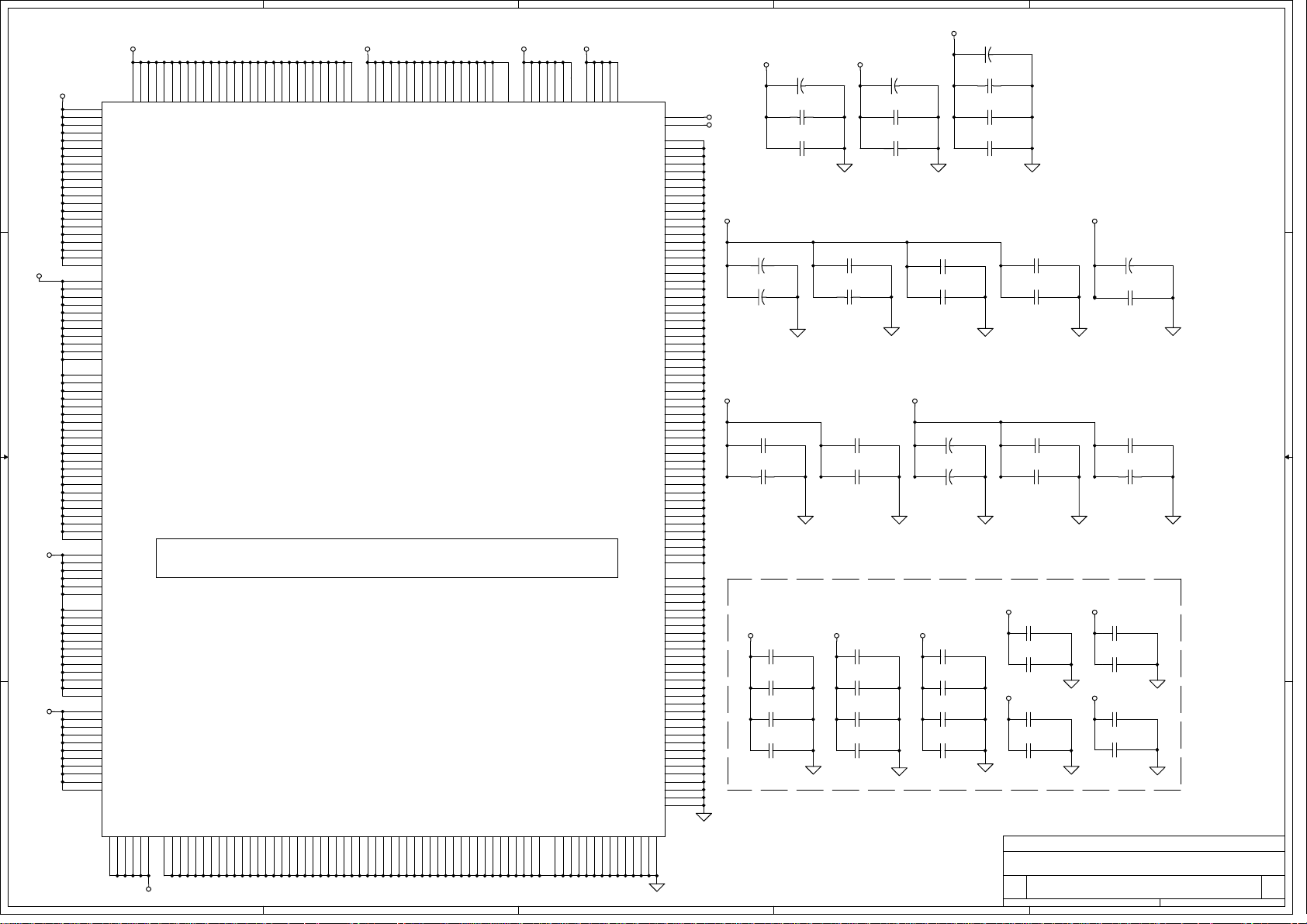

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

B

C

D

E

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

Please place these cap in the socket cavity area

+CPU_CORE

1 1

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

CB10

CB15

12

CB11

10UF_6.3V_1206

12

CB16

10UF_6.3V_1206

12

CB12

10UF_6.3V_1206

12

CB17

10UF_6.3V_1206

12

CB13

10UF_6.3V_1206

12

CB18

10UF_6.3V_1206

12

CB14

10UF_6.3V_1206

12

CB19

10UF_6.3V_1206

Please place these cap on the socket north side

+CPU_CORE

12

CB20

10UF_6.3V_1206

2 2

+CPU_CORE

12

CB25

10UF_6.3V_1206

+CPU_CORE

12

CB30

10UF_6.3V_1206

12

CB21

10UF_6.3V_1206

12

CB26

10UF_6.3V_1206

12

CB31

10UF_6.3V_1206

12

CB22

10UF_6.3V_1206

12

CB27

10UF_6.3V_1206

12

CB32

10UF_6.3V_1206

12

CB23

10UF_6.3V_1206

12

CB28

10UF_6.3V_1206

12

CB33

10UF_6.3V_1206

12

CB24

10UF_6.3V_1206

12

CB29

10UF_6.3V_1206

+CPU_CORE

12

+

+CPU_CORE

12

+

+CPU_CORE

12

CE1

220UF_D2_4V_25m

CE8

220UF_D2_4V_25m

C9

0.22UF

Used ESR 25m ohm cap total ESR=2.5m ohm

12

C10

0.22UF

12

CE2

+

220UF_D2_4V_25m

12

CE9

+

220UF_D2_4V_25m

12

C11

0.22UF

12

+

+

C12

0.22UF

12

CE3

220UF_D2_4V_25m

12

CE6

220UF_D2_4V_25m

12

C13

0.22UF

12

CE5

+

220UF_D2_4V_25m

12

CE7

+

220UF_D2_4V_25m

12

C14

0.22UF

12

C15

0.22UF

12

CE4

+

220UF_D2_4V_25m

12

CE10

+

220UF_D2_4V_25m

12

C16

0.22UF

12

C17

0.22UF

12

C18

0.22UF

Please place these cap on the socket south side

+CPU_CORE

3 3

4 4

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

+CPU_CORE

12

10UF_6.3V_1206

CB34

CB39

CB44

12

CB35

10UF_6.3V_1206

12

CB40

10UF_6.3V_1206

12

CB45

10UF_6.3V_1206

12

CB36

10UF_6.3V_1206

12

CB41

10UF_6.3V_1206

12

CB46

10UF_6.3V_1206

12

CB37

10UF_6.3V_1206

12

CB42

10UF_6.3V_1206

12

CB47

10UF_6.3V_1206

12

CB38

10UF_6.3V_1206

12

CB43

10UF_6.3V_1206

EMI Clip PAD for CPU

PAD1

PAD-2.5X3

1

PAD2

1

PAD-2.5X3

A

PAD3

PAD-2.5X3

1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

SCHEM AT IC , M/ B LA- 1341

Size Docu ment Number Re v

Date: Sheet

Compal E l e c t r onics, Inc.

401210

星期五 十一

?15, 2002

2A

of

546,

E

A

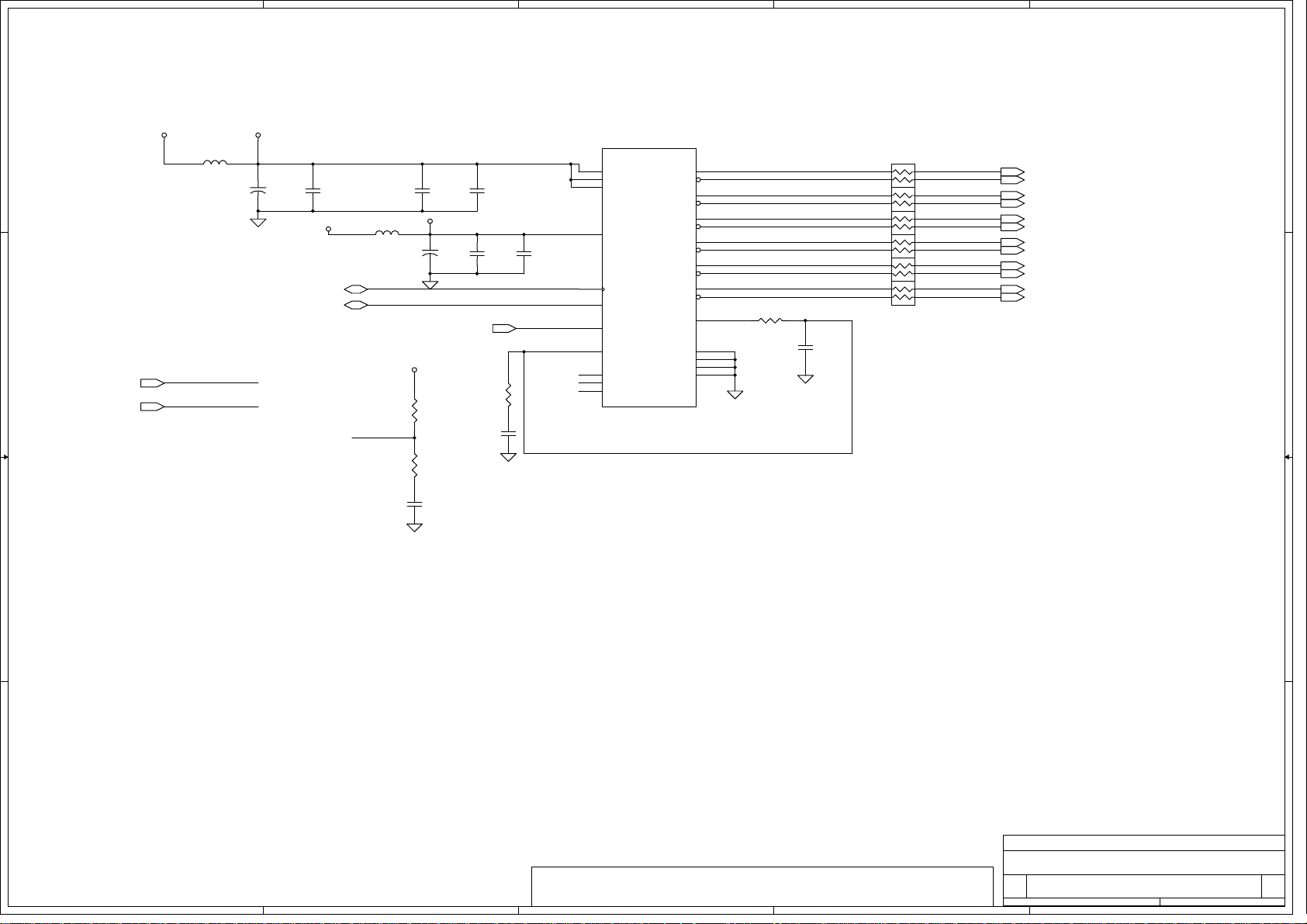

HD[0..63]3

HA[3..31]3

4 4

3 3

+CPU_CORE

R81

HNCOMP

R83

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

C26

0.01UF

HNCVREF

C27

0.01UF

20_1%_0603

113_1%_0603

+CPU_CORE

2 2

R84

150_1%_0603

R85

75_1%_0603

HNCVREF_G

HD[0..63]

HA[3..31]

CPUCLK112

CPUCLK1#12

HLOCK#3

DEFER#3

HTRDY#3

CPURST#3

CPUPWRGD3

BREQ0#3

DRDY#3

DBSY#3

HREQ4#3

HREQ3#3

HREQ2#3

HREQ1#3

HREQ0#3

HASTB1#3

HASTB0#3

CPUCLK1

CPUCLK1#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPW RGD

BPRI#3

RS2#3

RS1#3

RS0#3

ADS#3

HITM#3

HIT#3

BNR#3

BPRI#

BREQ0#

RS2#

RS1#

RS0#

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ4#

HREQ3#

HREQ2#

HREQ1#

HREQ0#

HASTB1#

HASTB0#

HA31

HA30

HA29

HA28

HA27

HA26

HA25

HA24

HA23

HA22

HA21

HA20

HA19

HA18

HA17

HA16

HA15

HA14

HA13

HA12

HA11

HA10

HA9

HA8

HA7

HA6

HA5

HA4

HA3

AJ26

AH26

U24

U26

V26

C20

D19

T27

U25

T24

T26

U29

V28

T28

U28

W26

V24

V27

W28

W29

W24

W25

Y27

AD24

AA24

AF26

AE25

AH28

AD26

AG29

AE26

AF28

AC24

AG28

AE29

AD28

AC25

AD27

AE28

AF27

AB24

AB26

AC28

AC26

AC29

AA26

AB28

AB27

AA25

AA29

AA28

Y26

Y24

Y28

B

HNCOMP

HNCVREF

HVREF0

HD#54

T21

HVREF1

HD#53

D21

HD53

HPCOMP

VBD6

VBD7

VBD4

VBD3

VBD5

P21

N21

J17

B20

HVREF2

HVREF3

HVREF4

B7

A19

B19

ST0A7ST1F9ST2

HPCOMP

HNCOMP

HNCOMPVREF

VBD7/AAD0M6VBD6/AAD1M5VBD5/AAD2M4VBD4/AAD3L3VBD3/AAD4L6VBD2/AAD5

650-1

HD#52

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

F22

HD52

D24

HD51

D23

HD50

C24

HD49

B24

HD48

E25

HD47

E23

HD46

D25

HD45

A25

HD44

C26

B26

HD42

HD43

B27

HD41

D26

HD40

B28

HD39

E26

HD38

F28

HD37

HVREF

C4XAVDD

C4XAVSS

AJ25

AJ27

U21

AH25

AH27

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HASTB#1

HASTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

C1XAVSS

C4XAVSS

C1XAVDD

C4XAVDD

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

HOST

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

F19

B21

A21

E19

B22

B23

A23

D22

D20

C22

HD60

HD59

HD58

HD57

HD56

HD55

HD54

HD63

HD61

HD62

VBD2

L4

HD#36

G25

HD36

VBD1

VBD0

L2

CBD1/AAD6K6CBD0/AAD7

HD#35

HD#34

F27

F26

HD35

HD34

VAD6

VAD5

VAD6/AAD8K3VAD5/AAD9

HD#33

G24

HD33

VAD4

J3

HD#32

H24

HD32

C

VAD7

VAD4/AAD10K4VAD7/AAD11J2VAD8/AAD12J6VAD9/AAD13

HD#31

J26

G29

HD31

HD30

HD#30

VAD8

G26

VAD9

J4

HD#29

J25

HD29

VAD10

HD#28

H26

HD27

HD28

VAD11

H6

VAD10/AAD14J1VAD11/AAD15

HD#27

HD#26

G28

HD26

ADE

F4

VADE/AAD16

HD#25

H28

HD25

AVSYNC

AHSYNC

G6

F1

VAVSYNC/AAD17

VAHSYNC/AAD18

HD#24

HD#23

J24

K28

HD24

HD23

VBD11

VBD10

F5

VBD11/AAD19E3VBD10/AAD20

HD#22

J29

K27

HD21

HD22

VAD3

VAD0

VAD1

VAD2

VBD9

VBD8

VBD8/AAD21E2VBD9/AAD22E4VAD1/AAD23E1VAD0/AAD24D3VAD2/AAD25D4VAD3/AAD26

LVDS

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

J28

L26

L25

K26

M24

HD18

HD20

HD16

HD17

HD19

BDE

F7

C2

HD#15

L28

M26

HD15

VBCTL0

C3

VBDE/AAD27

HD#14

P26

HD14

VBCTL1

E6

VBCTL0AAD28

HD#13

L29

HD13

BHSYNC

B2

VBCTL1/AAD29

HD#12

N24

HD12

BVSYNC

D5

VBHSYNC/AAD30

HD#11

N26

HD10

HD11

VBVSYNCAAD31

HD#10

M27

HD9

SBA7D6SBA6A3SBA5D7SBA4C5SBA3A5SBA2C6SBA1

HD#9

HD#8

HD#7

HD#6

HD#5

HD#4

P27

N28

N29

R24

R28

M28

HD4

HD7

HD8

HD6

HD5

HD3

D

BCLK

C20

@10PF

D8

C7

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

VBCLK/SBA0

VBCAD/AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

VBHCLK/RBF#

VGPIO2/WBF#

VGPIO3/PIPE#

SB_STB

SB_STB#

VAGCLK/AD_STB0

VAGCLKN/AD_STB#0

VBGCLK/AD_STB1

VBGCLKN/AD_STB#1

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HD#3

HD#2

HD#1

HD#0

DBI#3

DBI#2

DBI#1

P28

E21

A27

R26

R29

H27

DBI#3

DBI#2

DBI#1

HD1

HD0

HD2

U5A

R25

NC

NC

NC

DBI#0

DBI#0

SIS650

F6

F3

H4

K5

C9

A6

G2

G1

G3

G4

H5

H1

H3

E8

F8

D9

D10

B3

C4

B5

A4

K1

L1

C1

D1

B10

M1

B9

A9

B8

A8

M3

M2

F20

F23

K24

P24

F21

F24

L24

N25

R73 0

R76 0

R77 @0

R78 @0

AGCLK

AGCLKN

BGCLK

BGCLKN

AGPCLK0

AGPRCOMP

A4XAVDD

A4XAVSS

AVREFGC

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

BCLK

BGCLKN

BGCLK

AGCLKN

AGCLK

BVSYNC

BHSYNC

AHSYNC

AVSYNC

BHCLK

BCAD

AGPCLK0 12

R64 10

R65 @10

R66 10

R67 @10

R68 10

R69 10

R70 10

R71 10

R72 10

ADE

R74 10

BDE

R75 10

C21

@10PF

HDSTBN#[0..3] 3

HDST B P # [0 ..3 ] 3

VBCLK

VBGCLK#

VBGCLK

VAGCLK#

VAGCLK

VBVSYNC

VBHSYNC

VAHSYNC

VAVSYNC

C22

@10PF

E

VAD[0..11]

VBD[0..11]

VBCTL[0..1]

VADE

VBDE

VBGCLK

AGPRCOMP

AVREFGC

VBGCLK#

VAGCLK#

VAGCLK

C23

@10PF

AGPCLK0

R79 @10

R82 8.2K

VBCLK 15

VBGCLK# 15

VBGCLK 15

VAGCLK# 15

VAGCLK 15

VBVSYNC 15

VBHSYNC 15

VAHSYNC 15

VAVSYNC 15

VAD[0..11] 15

VBD[0..11] 15

VBCTL[0..1] 15

VADE 15

VBDE 15

C24

@10PF

R80

60_1%_0603

C25

@10PF

+3VS

+CPU_CORE

+3VS

R86

75_1%_0603

1 1

R89

150_1%_0603

C28

0.01UF

C29

0.01UF

HVREF_G

HVREF

C30

0.1UF

place this capacitor

under 650 solder side

A

A4XAVDD

C31

0.1UF

A4XAVSS

L3

1 2

HB-1M2012-121JT

C32

0.01UF

CB48

4.7UF_10V_0805

B

C4XAVDD

C4XAVSS

C33

0.1UF

1 2

C34

0.01UF

+3VS

L4

HB-1M2012-121JT

CB49

4.7UF_10V_0805

+3VS

R87

R88

4.7K

4.7K

BCAD

BHCLK

C

VBCAD 15

VBHCLK 15

D

DBI#[0..3] 3

Title

SCHEMATIC, M/B LA-1341

Size D o cument Numbe r R e v

401210

Dat e : Sheet

Com pal Electronics, Inc.

期五 十一月

of

646¬P , 15, 2002

E

2A

A

B

C

D

E

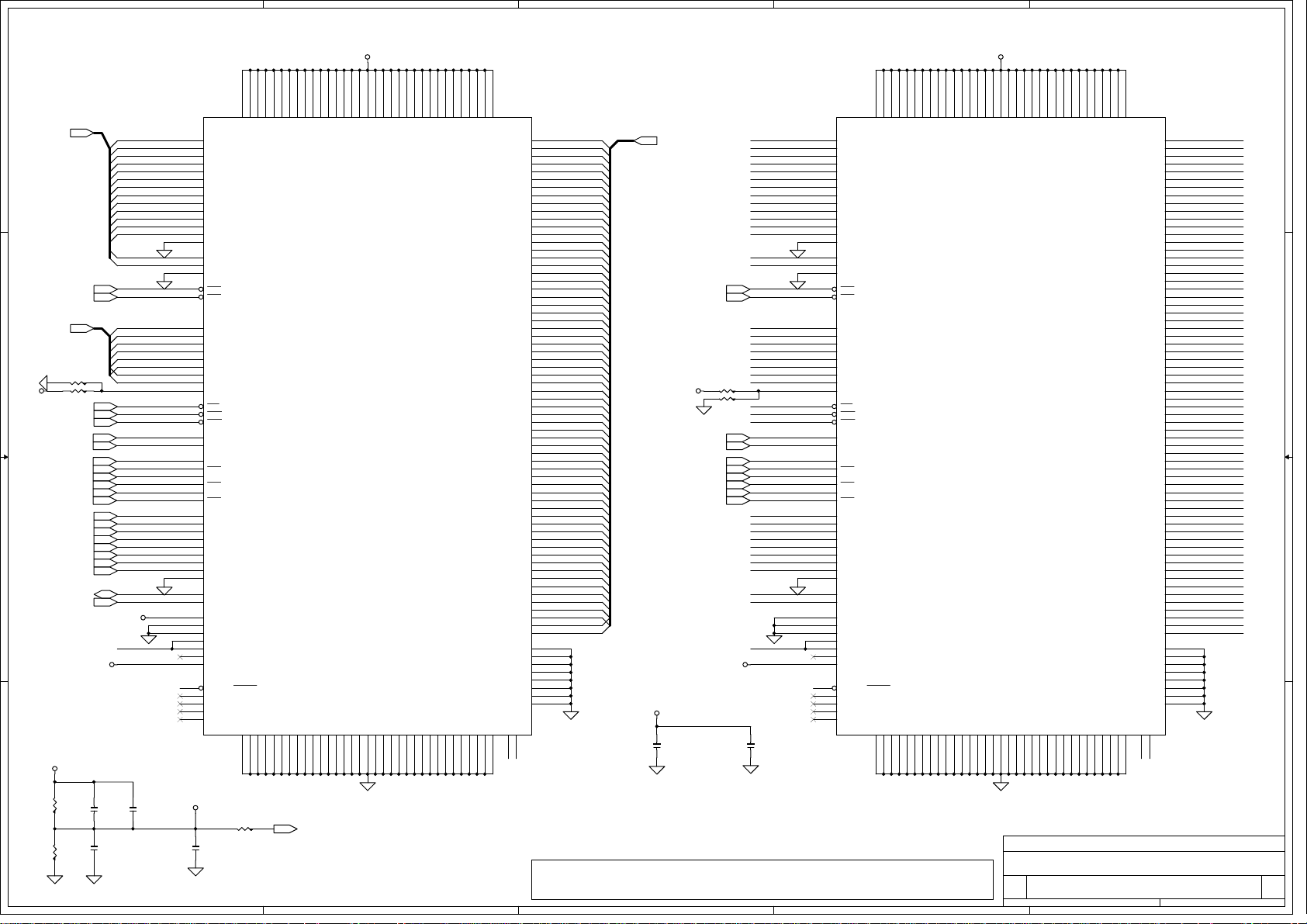

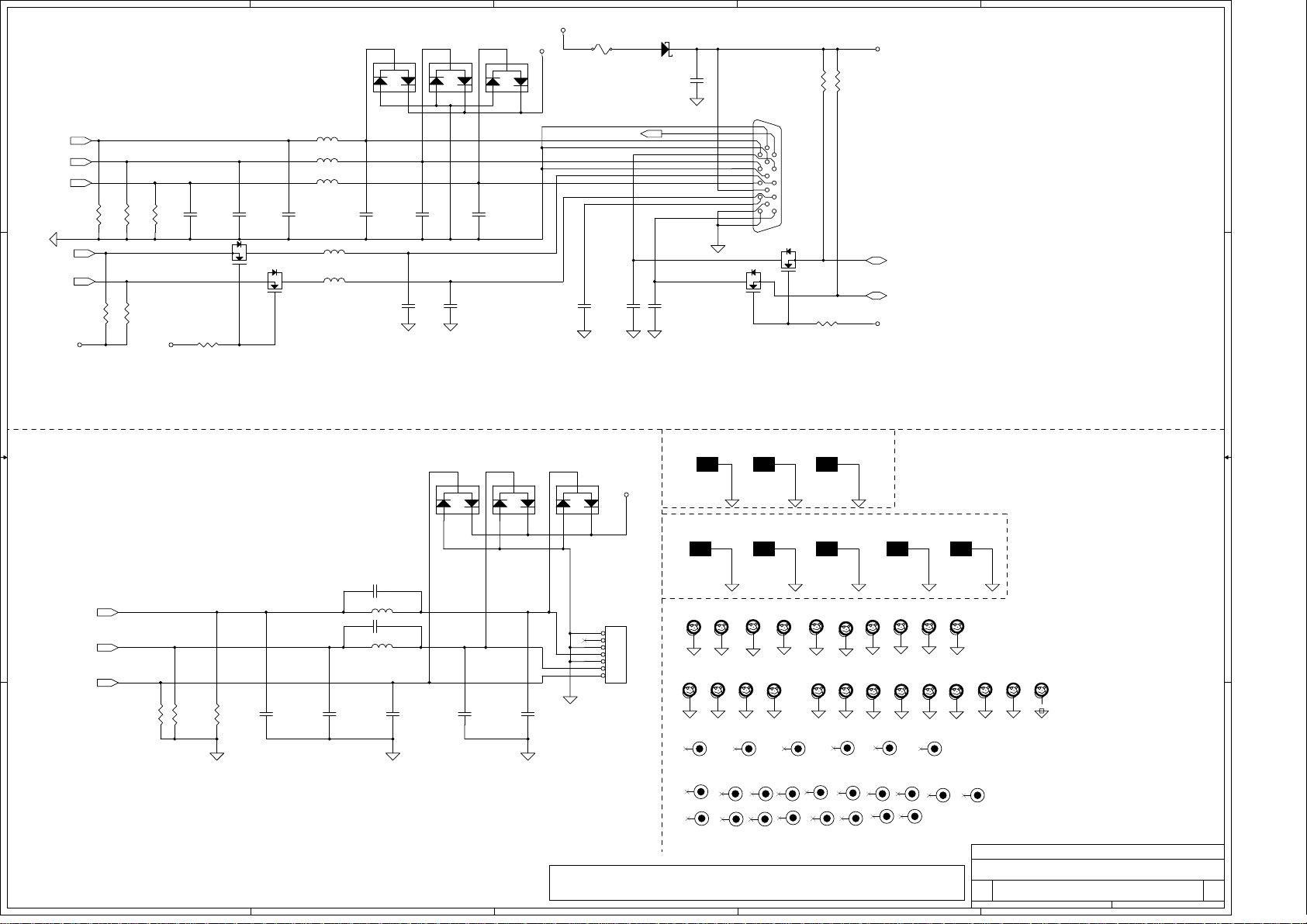

NOTE:This page is for pure DDR SDRAM PCB

MD[0..63]

RDQM[0..7]

RDQS[0..7]

MAA[0..14]

4 4

MD[0..63] 10,11

RDQM[0..7] 10,11

RDQS[0..7] 10,11

MAA[0..14] 10,11

RP* PLACE CLOSE TO DIMM

MD4

MD5

MD0

MD1

MD6

RDQS0

MD2

MD3

8P4R_10_0804

MD12

MD8

MD7

MD9

MD13

MD14

MD10

RDQS1

8P4R_10_0804

MD11

MD20

MD16

MD15

3 3

2 2

RDQM1

RDQM2

1 1

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

MD17 MA12

RDQS2

MD18

8P4R_10_0804

MD22 MMD22

MD19

MD24

MD28

MD29

MD25

RDQS3

8P4R_10_0804

MD30

MD27

MD31

MD26

MD32 MMD30

MD37

MD36

MD33

8P4R_10_0804

MD34

MD39

MD38 MMD35 CKE3

RDQS4

MD45

MD44

MD40

8P4R_10_0804

MD42

MD46

MD41

RDQS5

MD48

MD43

8P4R_10_0804

MD54

RDQS6

MD53

MD55

MD60

MD50

MD51 MMD52

8P4R_10_0804

MD59

MD62 MMD57

8P4R_10_0804

A

RP10

8P4R_10_0804

1 8

RP11

2 7

3 6

4 5

RP12

8P4R_10_0804

1 8

RP13

2 7

3 6

4 5

RP14

8P4R_10_0804

1 8

2 7

3 6

RP15

4 5

RP16

8P4R_10_0804

1 8

RP18

2 7

3 6

4 5

RP20

8P4R_10_0804

1 8

RP23

2 7

3 6

4 5

RP24

8P4R_10_0804

1 8

RP25

2 7

3 6

4 5

RP26

8P4R_10_0804

1 8

RP27

2 7

3 6

4 5

RP28

8P4R_10_0804

1 8

RP29

2 7

3 6

4 5

RP30

8P4R_10_0804

RP31

1 8

2 7

3 6

4 5

R101 10

R102 10

R103 10

R104 10

R105 10

R106 10

R107 10

R108 10

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

DQM0RDQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

MMD4

MMD5

MMD0

MMD1

MMD6

DQS0

MMD2

MMD3

MMD12

MMD8

MMD7

MMD9

MMD13

MMD14

MMD10

DQS1

MMD11

MMD20

MMD16

MMD15

MMD21MD21

MMD17

DQS2

MMD18

MMD19

MMD23MD23

MMD24

MMD28

MMD29

MMD25

DQS3

MMD30

MMD27

MMD31

MMD26

MMD32

MMD37

MMD36

MMD33

MMD34

MMD39

MMD38

DQS4

MMD35

MMD45

MMD44

MMD40

MMD42

MMD46

MMD41

DQS5

MMD48

MMD47

MMD43

MMD52

MMD49

MMD54

DQS6

MMD53

MMD55

MMD60

MMD50

MMD51

MMD56

MMD61

MMD57

DQS7

MMD58

MMD59

MMD62

MMD63

B

design

MMD0

MMD1

MMD2

MMD3

MMD4

MMD5

MMD6

MMD7

DQM0

DQS0

MMD8 MA1

MMD9 MA2

MMD10 MA3

MMD11 MA4

MMD12

MMD13 MA6

MMD14 MA7

MMD15 MA8

DQM1 MA9

DQS1 MA10

MMD16 MA11

MMD17

MMD18

MMD19

MMD20

MMD21 RAS- SRAS#

MMD22 CAS- SCAS#

MMD23 WE- SWE#

DQM2

DQS2

MMD24

MMD25 CS-0 RCS0#

MMD26 CS-1 RCS1#

MMD27

MMD28

MMD29

MMD31

DQM3

DQS3

MMD32 CKE0

MMD33 CKE1

MMD34 CKE2

MMD36

MMD37MD35

MMD38 S3AUXSW#

MMD39

DQM4

DQS4

MMD40 SDCLK

MMD41

MMD42

MMD43

MMD44MD47

MMD45

MMD46MD52

MMD47MD49

DQM5 SDAVDD

DQS5

MMD48 SDAVSS

MMD49

MMD50

MMD51 DDRAVDD

MMD53 DDRAVSSMD56

MMD54MD61

MMD55MD57

DQM6RDQS7

DQS6 DDRVREFAMD58

MMD56 DDRVREFB

MMD58MD63

MMD59

MMD60

MMD61

MMD62

MMD63

DQM7

DQS7

AJ23

AG22

AH21

AJ21

AD23

AE23

AF22

AF21

AD22

AH22

AD21

AG20

AE19

AF19

AE21

AD20

AD19

AH19

AF20

AH20

AF18

AG18

AH17

AD16

AD18

AD17

AF17

AJ17

AE17

AH18

AD14

AG14

AJ13

AE13

AJ15

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AE9

AD8

AG10

AF10

AH9

AF9

AD9

AH5

AG4

AE5

AH3

AG6

AF6

AF5

AF4

AH4

AE4

AD6

AE2

AC5

AG2

AG1

AF3

AC6

AD4

AF2

AB6

AD3

AA6

AB3

AC4

AE1

AD2

AC1

AB4

AC2

AJ9

AJ3

U5B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB#0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB#1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

SIS650

650-2

S3AUXSW#

FWDSDCLKO

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

MA1 MAA1

MA0 MAA0

MA3

MA2

MA5 MAA5

MA7

MA6

MA9 MAA9

MA8 MAA8

MA14

MA13

MA12 MAA12

RP9 4P2R_10

MA10

RP6

18

8P4R_10_0804

27

36

45

18

RP8

27

8P4R_10_0804

36

45

R93 10

RP* place close to DIMM1

MA0

AH11

MA0

AF12

MA1

AH12

MA2

AG12

MA3

AD12

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

SDCLK

SDRCLKI

SDAVDD

SDAVSS

AH15

AF15

AH16

AE15

AD15

AF11

AG8

AJ11

AG16

AF16

AH8

AJ7

AH7

AE7

AF7

CS-2

AH6

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

AA3

AD11

AE11

Y1

Y2

AA1

AA2

AJ19

AH2

R100 4.7K

W3

MA5

MA13

MA14

4P2R_10

RP19

R99 10

R516 10

R517 10

R97 10

1 4

2 3

RP214P2R_10

R98 @10

C42 @10PF

+3VALW

RP7

18

27

36

45

8P4R_10_0804

14

23

1 4

2 3

FW DSDCLKO

MAA10

C41 @10PF

D

MAA3

MAA2

MAA4MA4

MAA7

MAA6

MAA14

MAA13

MAA11MA11

RCS2#

RCS3#CS-3

FWDSDCLKO 13

DDRVREFA

DDRVREFB

SRAS# 10,11

SCAS# 10,11

SWE# 10,11

RCS0# 10,11

RCS1# 10,11

RCS2# 10,11

RCS3# 10,11

CKE[0..3] 10

S3AUXSW# 29,32

SDCLK 12

+2.5V

R90

C35

0.01UF

C36

0.01UF

DDRVREFA_G

C37

0.01UF

C38

0.01UF

DDRVREFB_G

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

Title

SCHEMATIC, M/B LA-1341

Size D o cument Numbe r R e v

401210

Dat e : Sheet

期五 十一月

150_1%_0603

R91

R92

@0_0603

150_1%_0603

+2.5V

R94

CKE0

CKE1

CKE2

CKE3

150_1%_0603

R96

150_1%_0603

RP22

1 8

2 7

3 6

4 5

8P4R_470_0804

R95

@0_0603

+2.5V

1 2

C39

0.1UF

C40

0.01UF

1 2

C43

0.1UF

C44

0.01UF

Com pal Electronics, Inc.

E

SDREF 10,35

+3VS

L5

HB-1M2012-121JT

+3VS

L6

HB-1M2012-121JT

746¬P , 15, 2002

SDREF 10,35

CB50

4.7UF_10V_0805

CB51

4.7UF_10V_0805

of

2A

A

B

C

D

E

ZVREF_G

Z4XAVDD

Z4XAVSS

ZSTB[0..1]

ZSTB[0..1]#

C47

0.1UF

C48

0.1UF

ZAD[0..15]16

ZVREF

R109

C45

10PF

ZCLK012

ZAD[0..15]

PCIRST-16,20,29

PWRGD17,32

RSM_RST17,29

ZCLK0

ZUREQ16

ZDREQ16

ZSTB016

ZSTB0#16

ZSTB116

ZSTB1#16

Z4XAVDD

Z4XAVSS

10

ZUREQ

ZDREQ

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZVREF

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

PCIRSTPWRGD

AUXOK

TRAP1

TRAP0

U5C

SIS650

D11

E10

V3

U6

U1

T3

T1

P1

P3

T4

R3

T5

T6

R2

R6

R1

R4

P4

N3

P5

P6

N1

N6

N2

N4

U3

V5

U4

U2

V6

W1

W2

V2

V1

Y3

W4

W6

ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB#0

ZSTB1

ZSTB#1

ZAD0

ZAD1

ZAD2

650-3

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

MuTIOL

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZVREF

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

PCIRST#

PWROK

AUXOK

TRAP1

TRAP0

VGA

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

ENTEST

DLLEN#

TESTMODE0

TESTMODE1

TESTMODE2

C46 10PF

C15

14.318M INPUT REFERENCE

A12

B13

A13

R115 33

F13

R117 33

E13

R119 100

D13

R120 100

D12

B11

E12

A11

F12

E14

D14

F14

B12

C12

C13

C14

B15

A15

B14

A14

F10

ENTEST

E11

DLLEN#

C11

F11

A10

R110 10

REFCLK0

RED

GREEN

BLUE

HSYNC

VSYNC

DDCCLK

DDCDATA

PIRQA#

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

REFCLK0 12,15

RED 14

GREEN 14

BLUE 14

HSYNC 14

VSYNC 14

DDCCLK 14

DDCDATA 14

PIRQA# 15,16,23

for 650 only

RSYNC

CSYNC

LSYNC

ENTEST

PWRGD

AUXOK

+3VS

R112 4.7K

R532 @4.7K

R533 @4.7K

R123 4.7K

C49 @0.1UF

C51 0.1UF

ZSTB [0 ..1 ]16

ZSTB[0..1]#16

4 4

3 3

+3VS

L7

1 2

HB-1M2012-121JT

CB52

4.7UF_10V_0805

2 2

150_1%_0603

150_1%_0603

C52

0.1UF

+1.8VS

R111

R113

C53

0.01UF

+3VS

DCLKAVDD

C56

DCLKAVSS

+1.8VS

L9

1 2

CB54

10UF_10V_1206

1 1

HB-1M2012-121JT

A

C59

0.1UF

C60

0.01UF

R125 56.2_1%_0603

R126 56.2_1%_0603

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

B

ECLKAVDD

ECLKAVSS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

0.01UF

C63

0.01UF

L8

1 2

HB-1M2012-121JT

C57

0.1UF

L11

1 2

HB-1M2012-121JT

C62

0.1UF

D

CB53

4.7UF_10V_0805

+3VS

CB57

4.7UF_10V_0805

C55

VVBWN

VCOMP

DACAVDD1

DACAVDD2

DACAVSS2

DACAVSS1

VRSET

130_1%_0603

Title

Size D o cument Numbe r R e v

Dat e : Sheet

0.1UF

C58

0.1UF

1 2

CB55

C61

1UF_10V_0603

0.1UF

R127

Com pal Electronics, Inc.

SCHEMATIC, M/B LA-1341

401210

期五 十一月

+1.8VS

L10

HB-1M2012-121JT

E

CB56

10UF_10V_1206

of

846¬P , 15, 2002

2A

5

NOTE:This page is for pure DDR SDRAM PCB design

+CPU_CORE

+CPU_CORE

A16

A17

C16

C17

C18

D15

D16

D17

D18

E15

E16

E17

E18

F15

F16

F17

F18

AB5

AD5

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE22

V10

V11

W18

Y10

Y12

Y14

Y16

Y18

Y19

AA8

AA9

AA10

AA13

AA14

AA15

AA16

AA17

AB8

AB9

AB13

AB17

K11

K13

A18

B16

B17

B18

J10

J13

L10

G5

D D

+2.5V

C C

+3VS

B B

N10

+1.8VS

W5

P10

R10

T10

A A

T11

H21

H22

J16

J20

J21

J22

K16

K17

K18

K19

K20

K21

L20

M20

N20

P20

R20

R21

T20

U20

V20

W20

Y20

Y21

AA20

AA21

AA22

AB21

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

650-4

VSS

VSS

VSS

VSS

VSS

P15

P16

P17

P18

R12

VSS

VTT

VSS

R13

R14

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

Y9

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

E5

VDDQ

E7

VDDQ

E9

VDDQ

VDDQ

J5

VDDQ

L5

VDDQ

H8

VDDQ

H9

VDDQ

J8

VDDQ

J9

VDDQ

VDDQ

VDDQ

K9

VDDQ

VDDQ

VDDQ

VDDQ

N9

VDDQ

VDDQ

N5

VDDZ

R5

VDDZ

U5

VDDZ

VDDZ

P9

VDDZ

VDDZ

R9

VDDZ

VDDZ

T9

VDDZ

VDDZ

VDDZ

PVDDP

L17

L19

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P12

P13

N19

R19

U19

+1.8VS

5

W19

N12

N13

N14

M12

M13

M14

M15

M16

N15

M17

M18

P14

N16

N17

N18

+1.8VS

AB22

L12

VTT

VTT

IVDD

Power

VSS

VSS

VSS

VSS

R15

R16

R17

L14

R18

L15

IVDD

VSS

T12

4

L16

IVDD

VSS

T13

4

L18

IVDD

VSS

T14

IVDD

VSS

M11

T15

IVDD

VSS

M19

T16

N11

IVDD

VSS

T17

P19

IVDD

VSS

T18

R11

IVDD

VSS

U12

T19

IVDD

VSS

U13

U11

IVDD

VSS

U14

V19

IVDD

VSS

U15

W11

IVDD

VSS

U16

W13

IVDD

VSS

U17

W15

IVDD

VSS

U18

W17

IVDD

VSS

V12

IVDD

VSS

V13

VSS

+3VS

P11

PVDDZ

VSS

V14

V15

VSS

3

+3VALW

+1.8VALW +3VALW

CB59

AF25

VSS

AUX1.8

AUX3.3

VSS

AG24

AG26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3

U5D

U10

+1.8VALW

U9

+3VALW

A20

A22

A24

A26

C19

C21

C23

C25

C27

E20

E22

E24

F25

H25

K25

M25

P25

T25

V25

Y25

AB25

AD25

E27

G27

J27

L27

N27

R27

U27

W27

AA27

AC27

AE27

D29

F29

H29

K29

M29

P29

T29

V29

Y29

AB29

AD29

AF29

AE24

AG25

B4

B6

C8

C10

D2

F2

H2

K2

P2

T2

V4

AD1

AF1

AC3

AE3

AG3

AG5

AG7

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AJ4

AJ6

AJ8

AJ10

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AG27

VSS

VSS

AH23

AH24

+CPU_CORE

+3VS

SIS650

10UF_10V_1206

CB62

1UF_10V_0603

C65

0.1UF

+1.8VS

CB65

1UF_10V_0603

CB68

1UF_10V_0603

CB64

10UF_10V_1206

CB67

10UF_10V_1206

C72

0.1UF

C74

0.1UF

Place these capacitors under 650 solder side

+CPU_CORE

C78

0.1UF

C82

0.1UF

C85

0.1UF

C91

0.1UF

J14

J15

K15

K10

K12

K14

M10

W10

Y11

Y13

Y15

Y17

PVDD

PVDD

PVDD

OVDD

VSS

V16

PVDD

OVDD

OVDD

VSS

VSS

V17

V18

PVDDM

PVDDM

PVDDM

PVDDM

PVDDM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B25

E28

E29

C28

C29

D27

D28

AF23

AF24

10UF_10V_1206

C73

0.1UF

C75

0.1UF

C79

0.1UF

C83

0.1UF

C86

0.1UF

C92

0.1UF

2

CB60

CB63

1UF_10V_0603

C66

0.1UF

+2.5V

+2.5V

2

+3VS

10UF_10V_1206

C69

0.1UF

C70

0.1UF

CB70

10UF_10V_1206

CB73

10UF_10V_1206

C80

0.1UF

C84

0.1UF

C87

0.1UF

C93

0.1UF

1

CB58

CB61

1UF_10V_0603

C64

0.1UF

C67

0.1UF

+1.8VS

C68

0.1UF

C71

0.1UF

CB71

1UF_10V_0603

CB74

1UF_10V_0603

+1.8VS

C76

0.1UF

CB76

10UF_10V_1206

C88

0.1UF

C94

0.1UF

Title

SCHEMATIC, M/B LA-1341

Size D o cument Numbe r R e v

401210

Dat e : Sheet

期五 十一月

CB66

10UF_10V_1206

CB69

1UF_10V_0603

CB72

1UF_10V_0603

CB75

1UF_10V_0603

+3VALW

C77

0.1UF

C81

0.1UF

+3VS+3VS

C89

0.1UF

C90

0.1UF

Com pal Electronics, Inc.

1

946¬P , 15, 2002

2A

of

A

B

C

D

E

131

VDDQ

GND

125

143

VDDQ

GND

137

+2.5V

JP5

179

155

157

167

191

VDD

VDD10VDD22VDD34VDD36VDD46VDD58VDD70VDD

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND4GND16GND28GND38GND40GND52GND64GND76GND88GND90GND

149

159

161

173

185

Title

Size D o cument Numbe r R e v

Dat e : Sheet

82

114

VDD92VDD94VDD

104

SCHEMATIC, M/B LA-1341

401210

期五 十一月

192

132

144

156

168

180

VDD

VDD

VDD

VDD

126

GND

138

GND

150

GND

VDD

GND

GND

162

174

VDDQ

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

GND

DDRAM_SODIMM_200P-R

186

201

202

InsightOutsight

5

7

13

17

6

8

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

71

73

79

83

72

74

80

84

Com pal Electronics, Inc.

E

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

2A

of

10 46¬P , 15, 2002

+2.5V

131

125

143

VDDQ

VDDQ

GND

GND

137

155

VDDQ

GND

149

157

VDDQ

GND

159

167

161

179

VDDQ

VDDQ

GND

GND

173

191

VDD

GND

185

82

114

VDD10VDD22VDD34VDD36VDD46VDD58VDD70VDD

VDD92VDD94VDD

GND4GND16GND28GND38GND40GND52GND64GND76GND88GND90GND

104

PC2100 - CL2 = 15 to Data 2-2-2/2.5-3-3

CL2.5 = 18.75 to Data

DDR266 256MB 4Bks Pmax = 8W

Ptyp = 7W

64MB/128MB/256MB - 500MB/s - 1.0W

- 1000MB/s - 1.65W

- 1500MB/s - 2.5W

- 2000MB/s - 3.2W

B

4 4

113

MAA[0..14]7,11

RCS2#7,11

RCS3#7,11

3 3

2 2

1 1

RDQM[0..7]7,11

R563 0

+2.5V +2.5V

R518 @100K

SWE#7,11

SCAS#7,11

SRAS#7,11

CKE27

CKE37

DDRCLK313

DDRCLK3#13

DDRCLK413

DDRCLK4#13

DDRCLK513

DDRCLK5#13

RDQS07,11

RDQS17,11

RDQS27,11

RDQS37,11

RDQS47,11

RDQS57,11

RDQS67,11

RDQS77,11

SMBDAT12,13,17

SMBCLK12,13,17

+2.5V

R128

1K_1%_0603

R130

1K_1%_0603

+3VS

+3VS

C486

0.1UF

C97

0.1UF

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA14

MAA11

MAA12

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

SWE#

SCAS#

SRAS#

CKE3

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

SMBDT

SMBCK

MVREF_DIM

C487

1000PF

MVREF_DIM

A

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

MVREF_DIM

C98

1000PF

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

3

R129

@0_0603

VDDQ9VDDQ21VDDQ33VDDQ45VDDQ57VDDQ69VDDQ81VDDQ93VDDQ

GND15GND27GND39GND51GND63GND75GND87GND

GND

103

-CS/-RAS/-CAS/-WE

R - 0101

W - 0100

SDREF 7,35

132

126

192

144

156

168

180

Lower Upper

VDD

VDD

VDD

VDD

GND

138

GND

VDD

VDDQ

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

GND

GND

GND

150

162

174

186

201

202

MD0

5

D0

MD1

7

D1

MD2

13

D2

MD3

17

D3

MD4

6

D4

MD5

8

D5

MD6

14

D6

MD7

18

D7

MD8

19

D8

MD9

23

D9

MD10

29

MD11

31

MD12

20

MD13

24

MD14

30

MD15

32

MD16

41

MD17

43

MD18

49

MD19

53

MD20

42

MD21

44

MD22

50

MD23

54

MD24

55

MD25

59

MD26

65

MD27

67

MD28

56

MD29

60

MD30

66

MD31

68

MD32

127

MD33

129

MD34

135

MD35

139

MD36

128

MD37

130

MD38

136

MD39

140

MD40

141

MD41

145

MD42

151

MD43

153

MD44

142

MD45

146

MD46

152

MD47

154

MD48

163

MD49

165

MD50

171

MD51

175

MD52

164

MD53

166

MD54

172

MD55

176

MD56

177

MD57

181

MD58

187

MD59

189

MD60

178

MD61

182

MD62

188

MD63

190

71

73

79

83

72

74

80

84

GND

DDRAM_SODIMM_200P-L

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MD[0..63] 7,11

MVREF_DIM

C95

0.1UF

C

RCS0#7,11

RCS1#7,11

R519 @100K

R564 0

CKE07

CKE17

DDRCLK013

DDRCLK0#13

DDRCLK113

DDRCLK1#13

DDRCLK213

DDRCLK2#13

+3VS

MVREF_DIM

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA14

MAA11

MAA12

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

SWE#

SCAS#

SRAS#

CKE0CKE2

CKE1

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

SMBDT

SMBCK

MVREF_DIM

C96

1000PF

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

3

VDDQ9VDDQ21VDDQ33VDDQ45VDDQ57VDDQ69VDDQ81VDDQ93VDDQ

GND15GND27GND39GND51GND63GND75GND87GND

GND

JP4

113

103

D

A

B

C

D

E

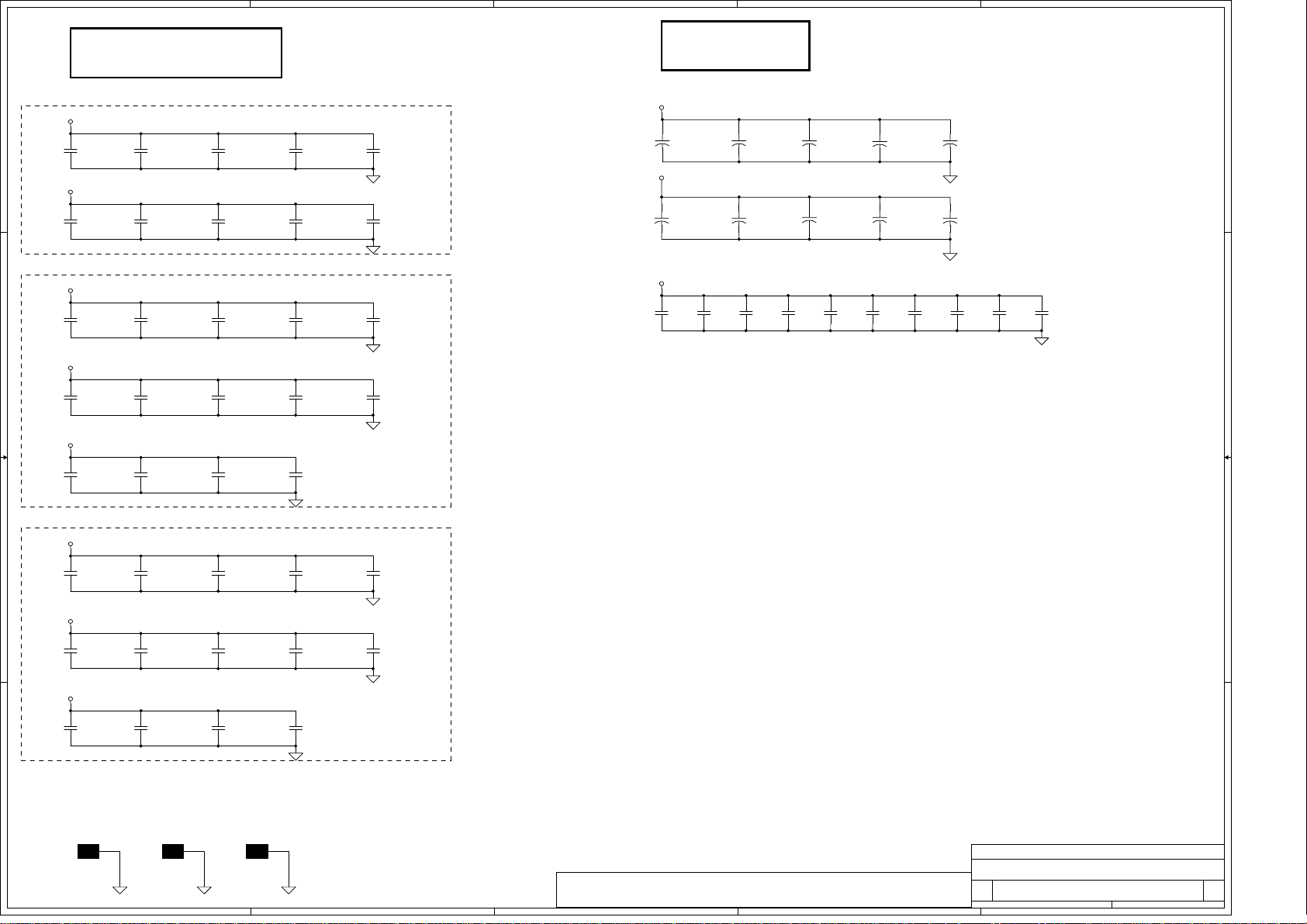

Decoupling capacitors

(Place near DDR SODIMM)

+2.5V

CB77 1UF_10V_0603

CB79 1UF_10V_0603

CB81 1UF_10V_0603

4 4

3 3

2 2

CB83 1UF_10V_0603

CB85 1UF_10V_0603

+2.5V

10UF_10V_1206

CB87

10UF_10V_1206CB88

10UF_10V_1206CB89

10UF_10V_1206CB90

Place these decoupling capacitors close to

VTT_MEM termination resistors.

+1.25VS

0.1UFC137

0.1UFC140

0.1UFC143

0.1UFC148

0.1UFC151

0.1UFC154

0.1UFC157

0.1UFC159

+2.5V

0.1UFC99

0.1UFC100

0.1UFC101

0.1UFC104

0.1UFC105

0.1UFC106

0.1UFC107

0.1UFC109

0.1UFC113

0.1UFC117

+1.25VS

C156

C158

1000PFC139

1000PFC142

1000PFC145

1000PFC150

1000PFC153

1000PF

1000PF

1000PFC160

MD0

MD4

MD1

MD5

RDQS07,10

RDQS17,10

RDQS27,10

RDQS37,10

RDQS47,10

RDQS57,10

RDQS67,10

RDQS0

MD6

MD2

MD3

MD7

MD8

MD12

MD9

MD13

RDQS1

MD10

MD14

MD11

MD15

MD16

MD20

MD17

MD21

RDQS2

MD18

MD22

MD19

MD23

MD24

MD28

MD25

MD29

RDQS3

MD26

MD30

MD27

MD31

MD32

MD36

MD33

MD37

RDQS4

MD38

MD34

MD39

MD35

MD44

MD40

MD45

MD41

RDQS5

MD42

MD46

MD43

MD47

MD48

MD52

MD49

MD53

RDQS6

MD54

MAA10

MAA12

Termianation Network place closely to DIMM

RP32

RP33

RP35

RP37

RP39

RP40

RP42

RP44

RP46

RP47

RP49

RP51

RP53

RP55

RP56

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RP574P2R_33

1 4

2 3

+1.25VS

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

C102

0.1UF

C114

0.1UF

C123

0.1UF

C127

0.1UF

C131

0.1UF

C135

0.1UF

C146

0.1UF

C103

1000PF

C115

1000PF

C124

1000PF

C128

1000PF

C132

1000PF

C136

1000PF

C147

1000PF

+1.25V Island

> 150ml

MD[0..63]7,10

MAA[0..14]7,10

RDQS77,10

RDQM07,10

RDQM17,10

RDQM27,10

RDQM37,10

RDQM47,10

RDQM57,10

RDQM67,10

RDQM77,10

SRAS#7,10

SWE#7,10

SCAS#7,10

RCS2#7,10

RCS3#7,10

RCS0#7,10

RCS1#7,10

MD50

MD55

MD51

MD60

MD56

MD61

MD57

RDQS7

MD62

MD58

MD63

MD59

MAA14

MAA13

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAA11

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

SRAS#

SWE#

SCAS#

RCS2#

RCS3#

RCS0#

RCS1#

MD[0 ..6 3 ]

MAA[0..14]

RP34

1 8

2 7

3 6

4 5

RP36

1 8

2 7

3 6

4 5

RP38

1 8

2 7

3 6

4 5

RP41

1 8

2 7

3 6

4 5

RP43

1 8

2 7

3 6

4 5

RP45

1 8

2 7

3 6

4 5

R493 33

R494 33

R495 33

R496 33

R497 33

R498 33

R499 33

R500 33

R501 33

R502 33

R503 33

R504 33

R505 33

R506 33

R507 33

R508 33

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

8P4R-33_0804

+1.25VS

C110

0.1UF

C120

0.1UF

C125

0.1UF

C129

0.1UF

C133

0.1UF

C111

1000PF

C121

1000PF

C126

1000PF

C130

1000PF

C134