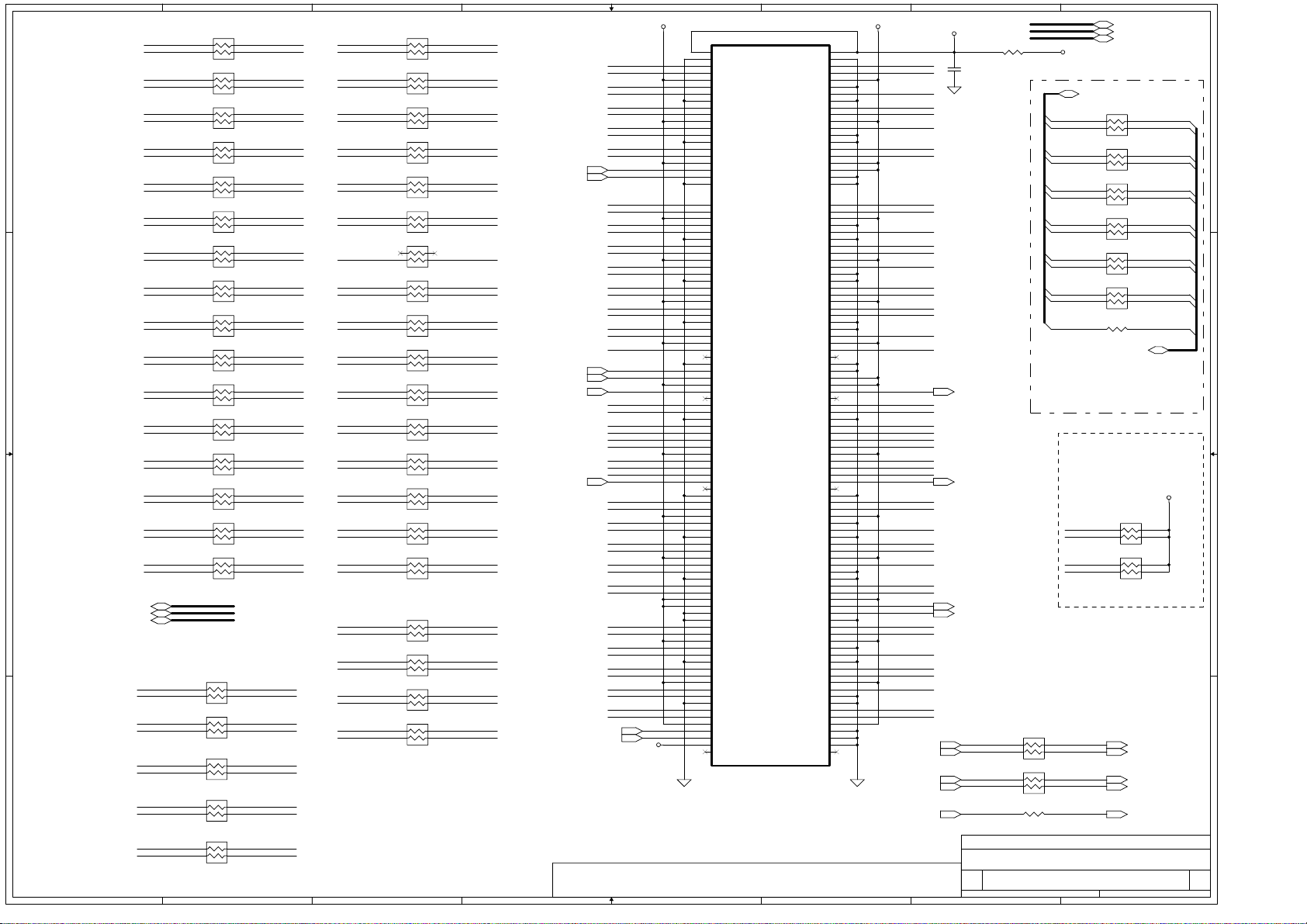

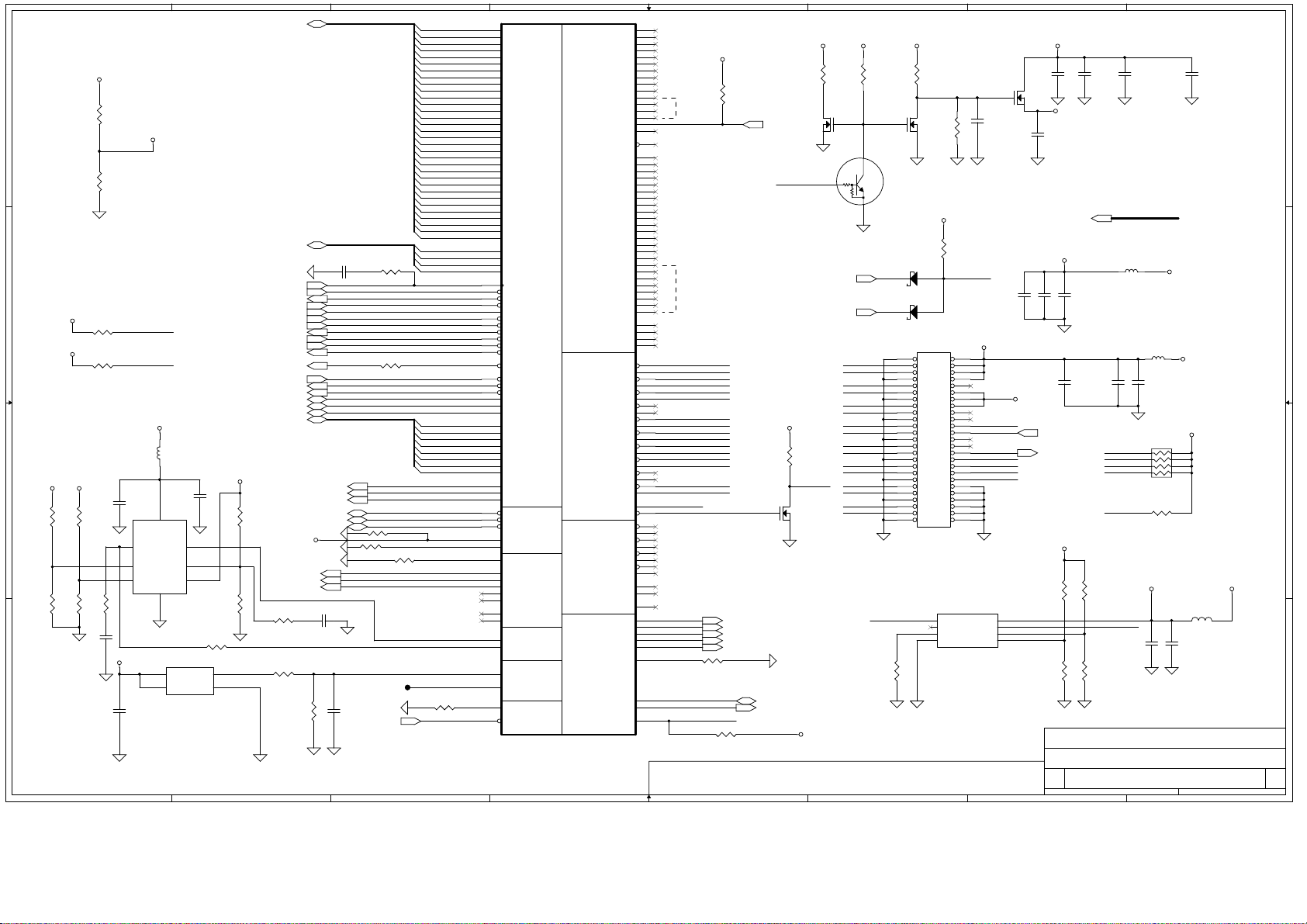

Acer LA-1301, LA-1302 Schematics

A

B

C

D

E

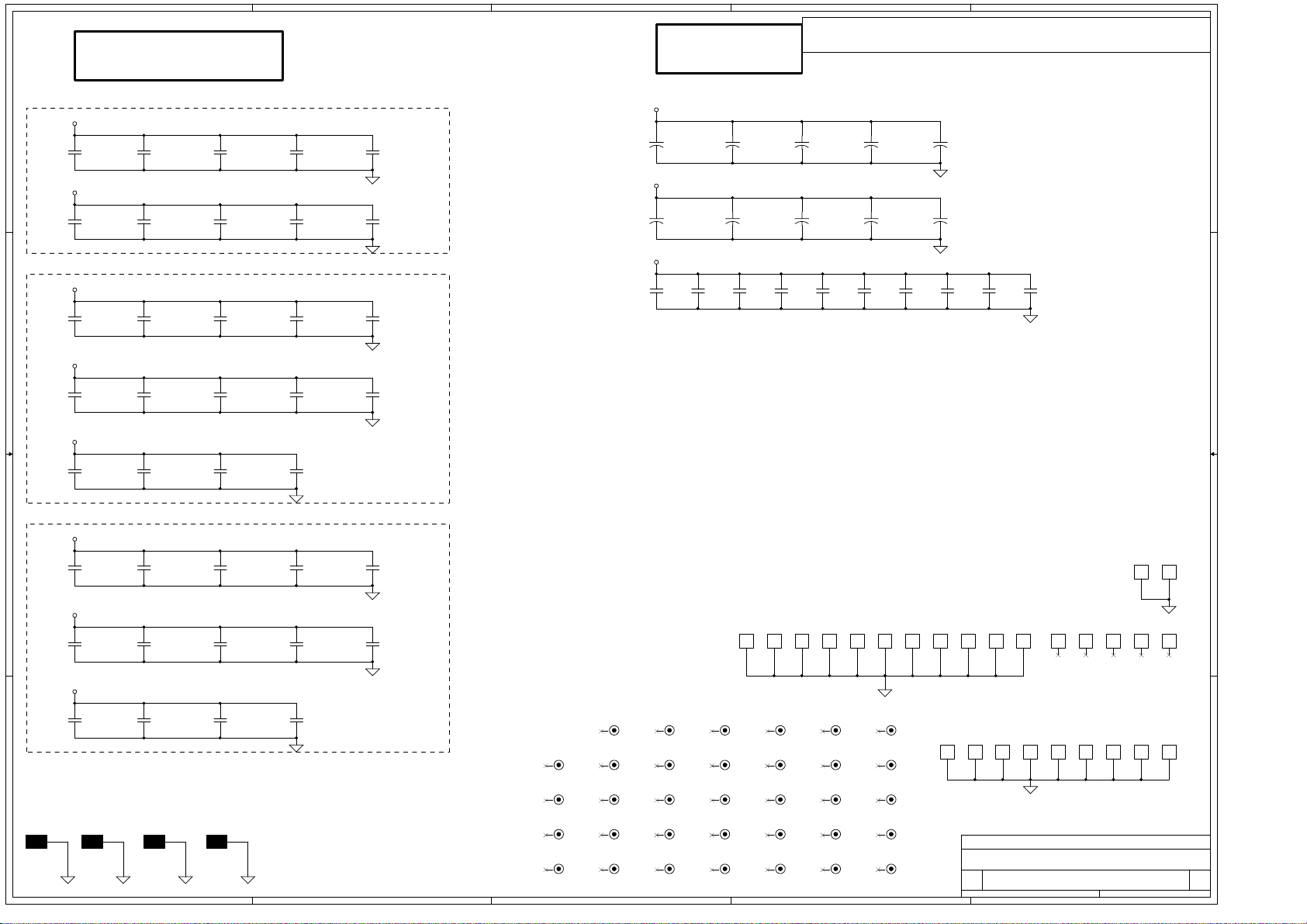

Cover Sheet

888Z4.5 / LA-1302 Mother Board

Rev : 0.5 for Layout

Intel (Northwood) with Intel 845M+ICH3

1 1

SHEET

SHEET

SHEETSHEET

1

2

3,4

5

6,7,8

9,10,11

12

13,14,15

2 2

16, 17

18,19,20

21

22

23

24

25

26

27

28

3 3

29

30

31

32

33

34

35

36

37

38

39

4 4

40

41

42

A

Cover Page

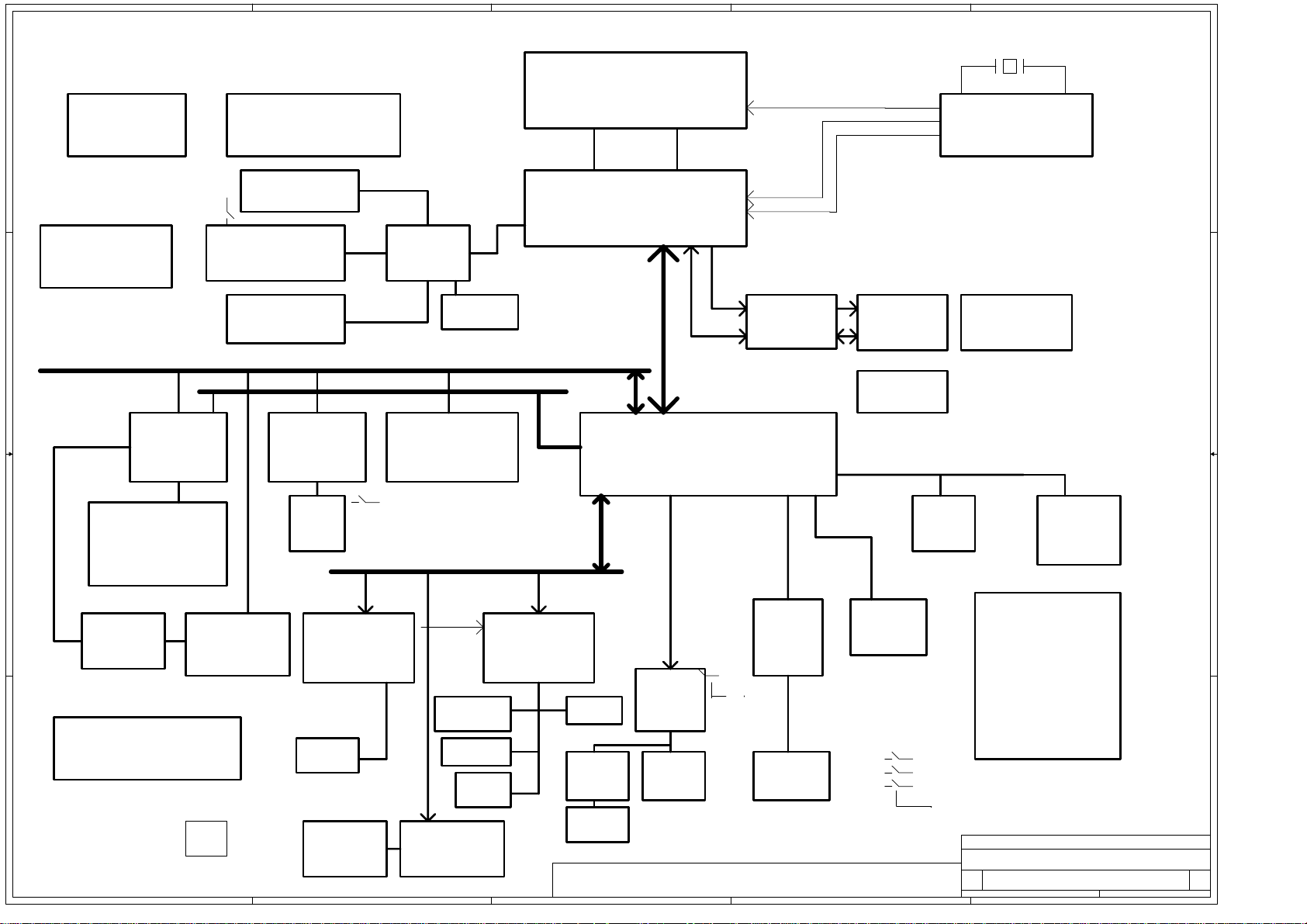

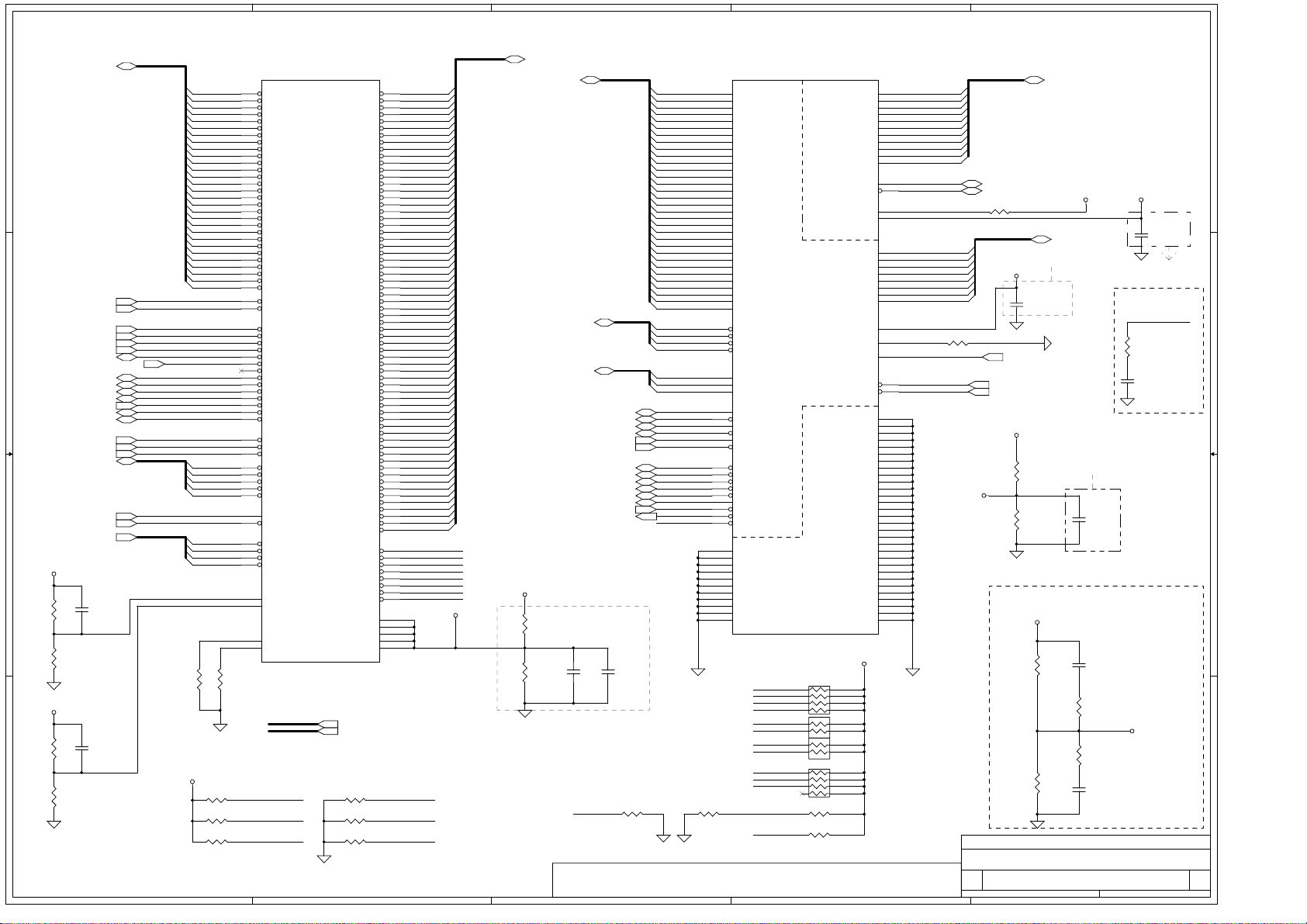

Block Diagram

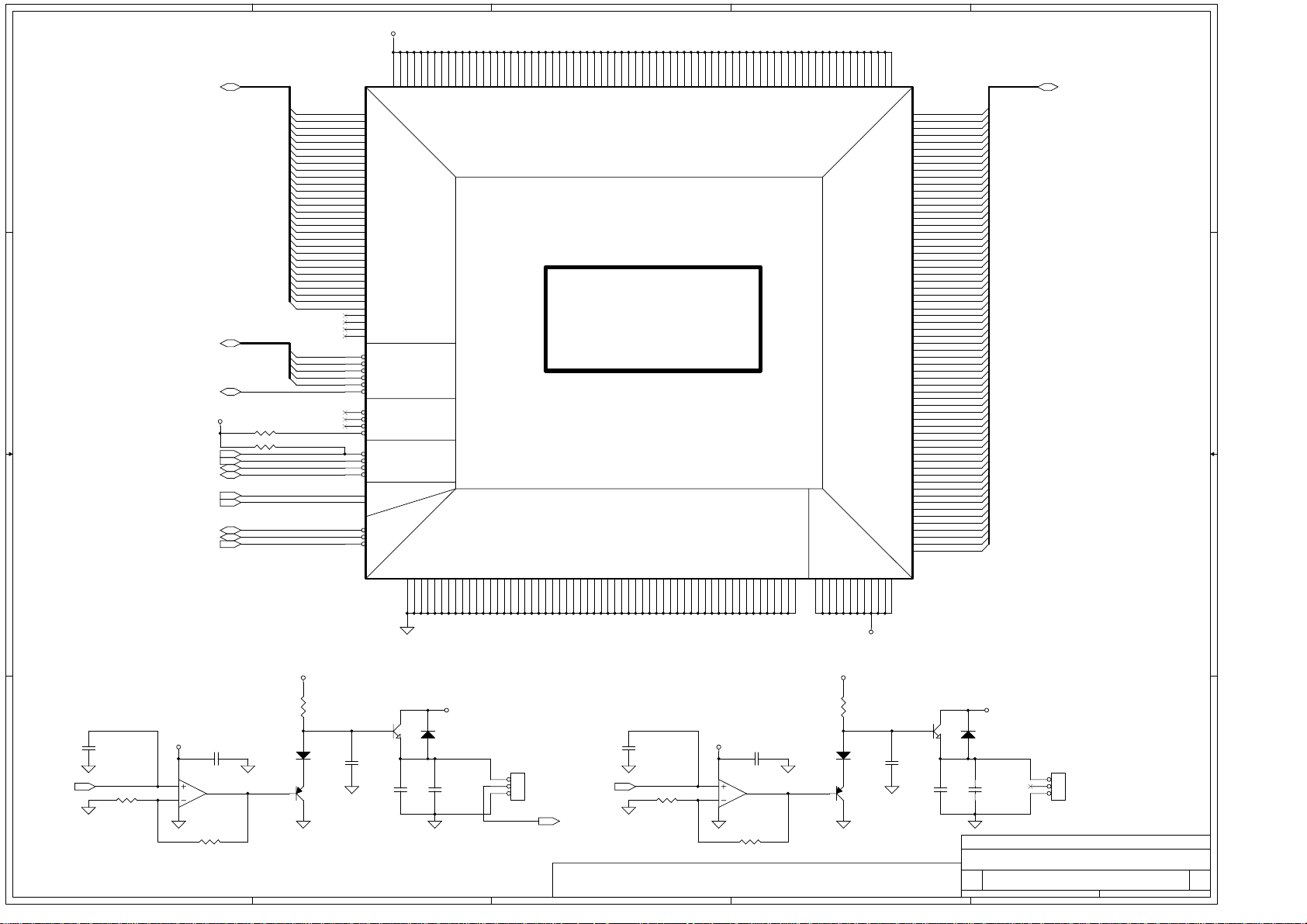

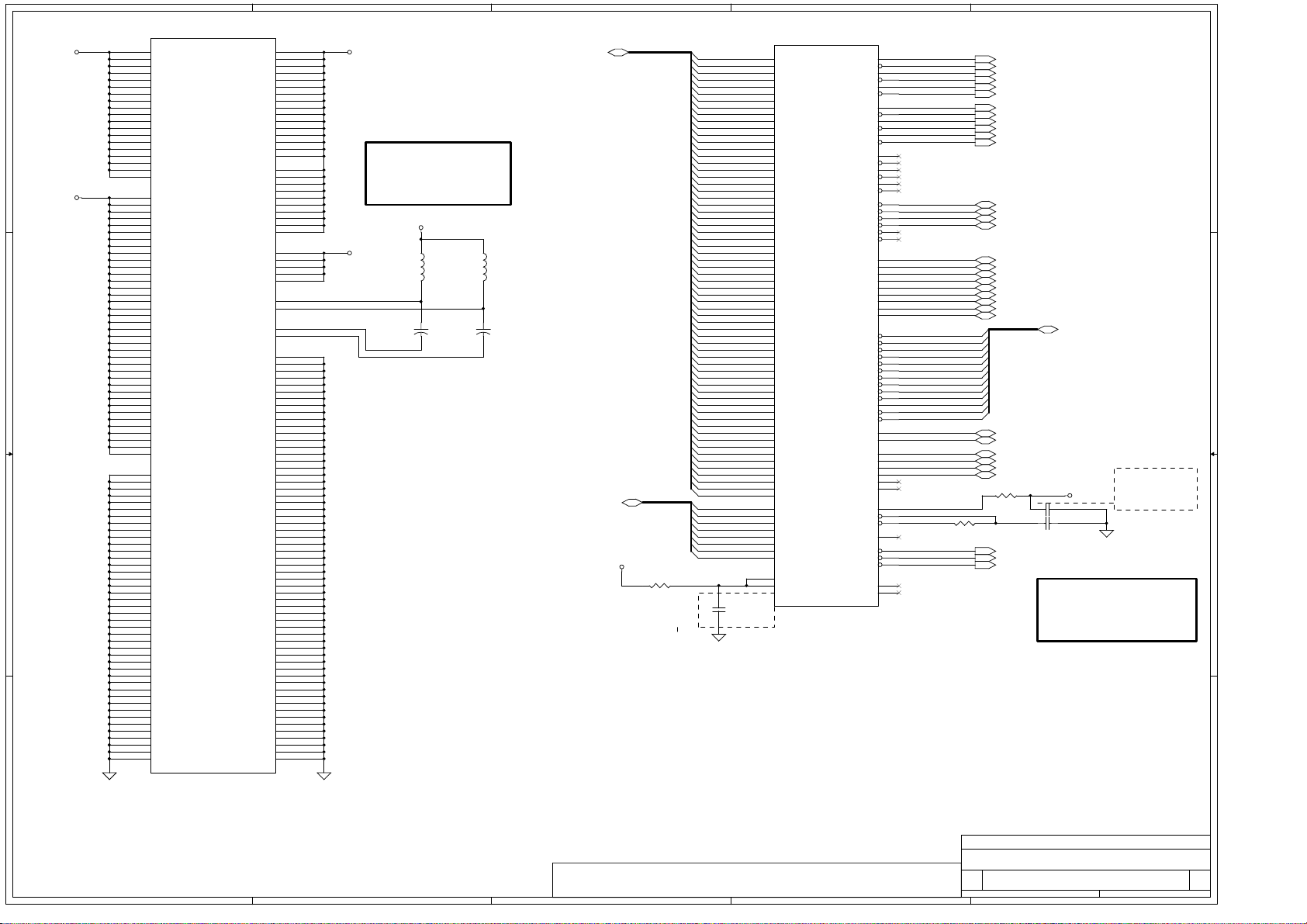

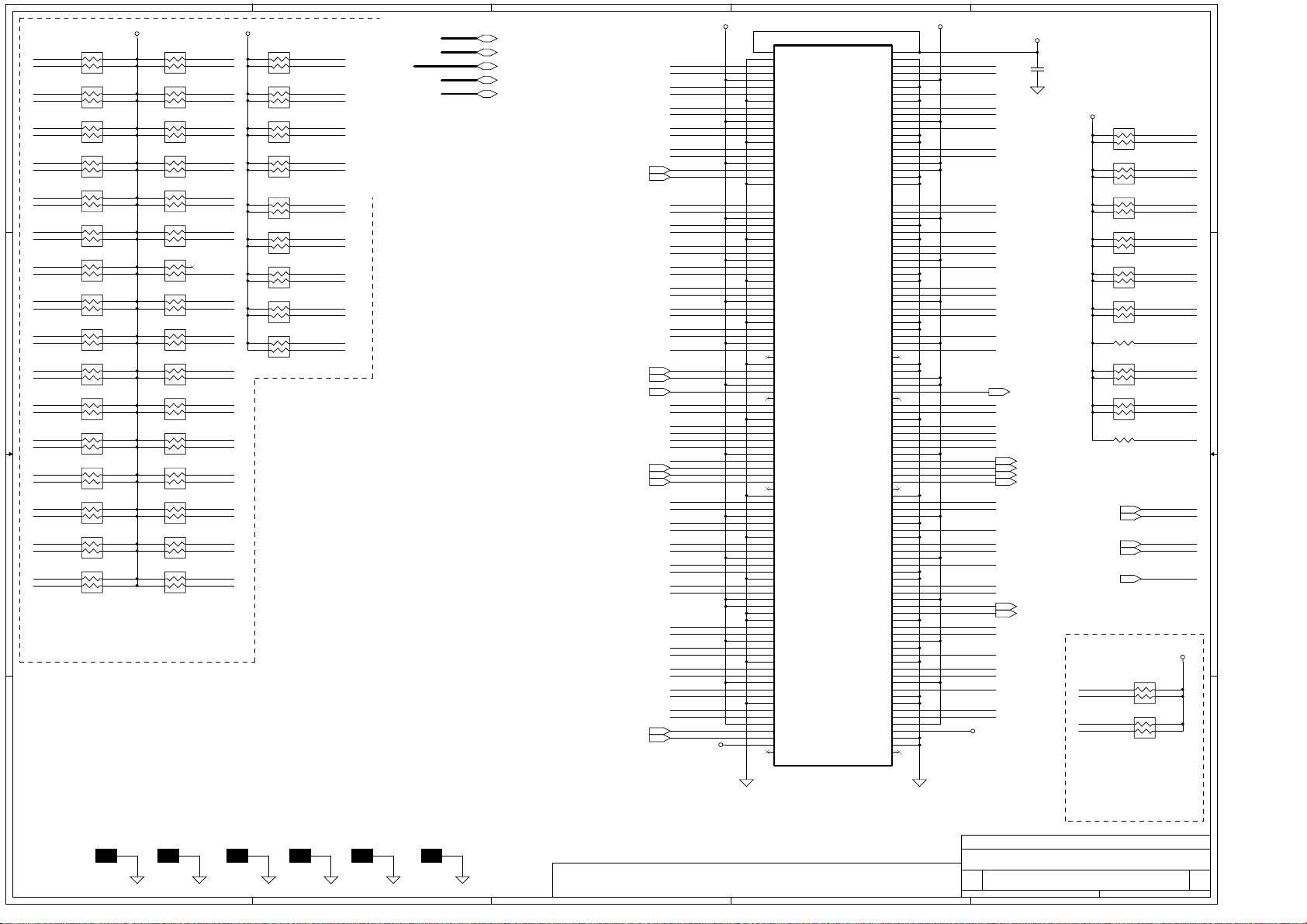

Northwood CPU / Fan / Thermal

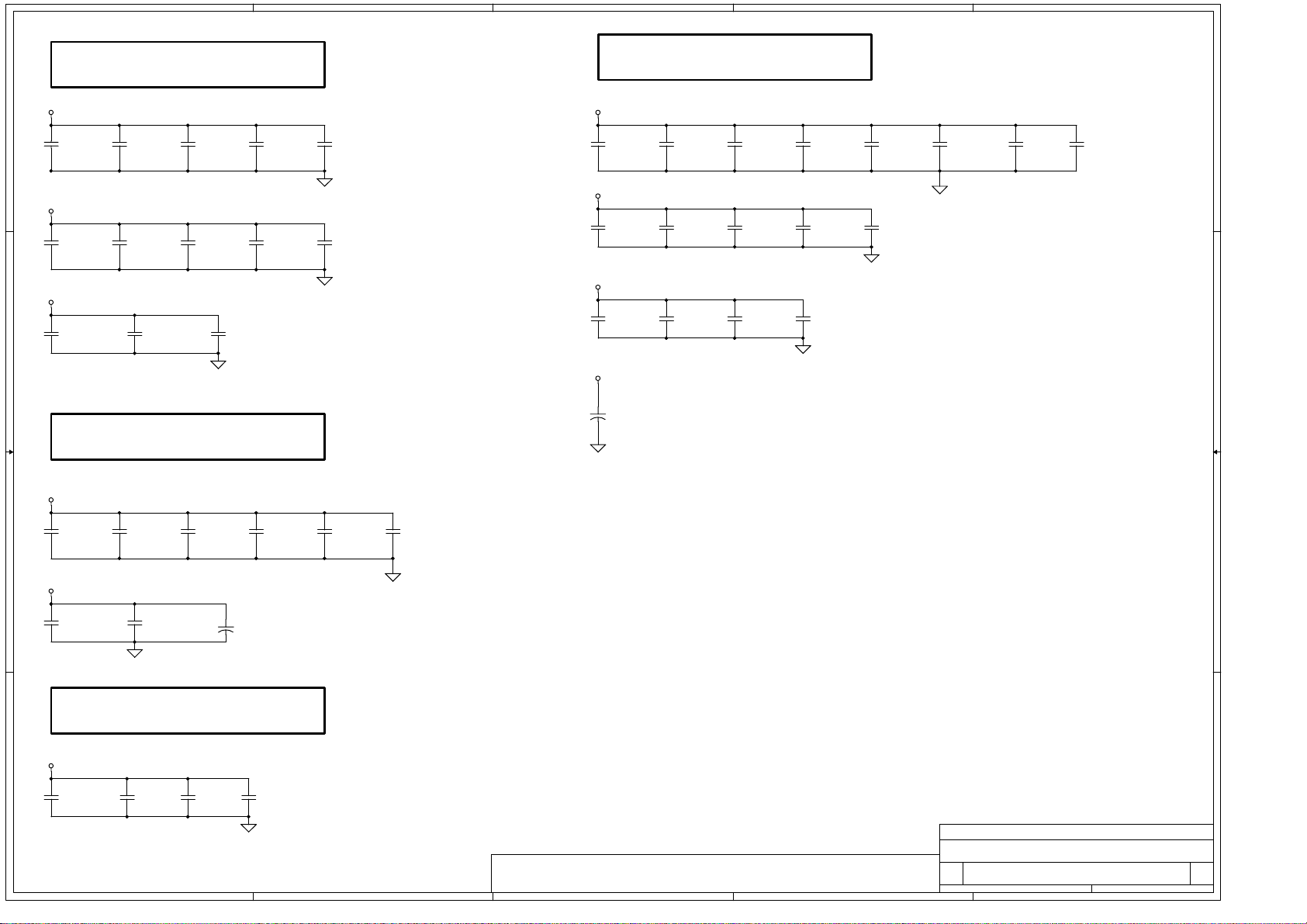

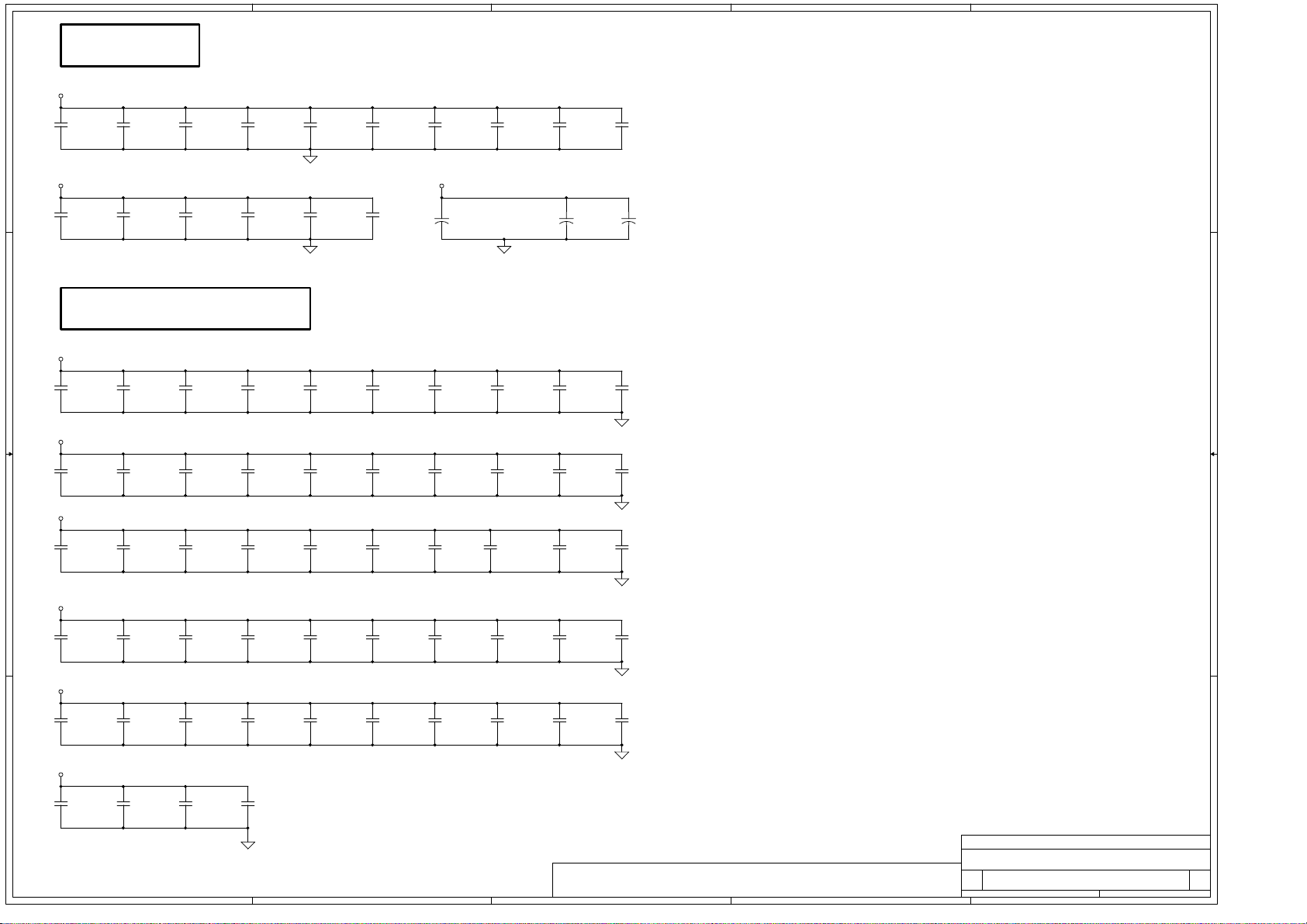

CPU Decoupling

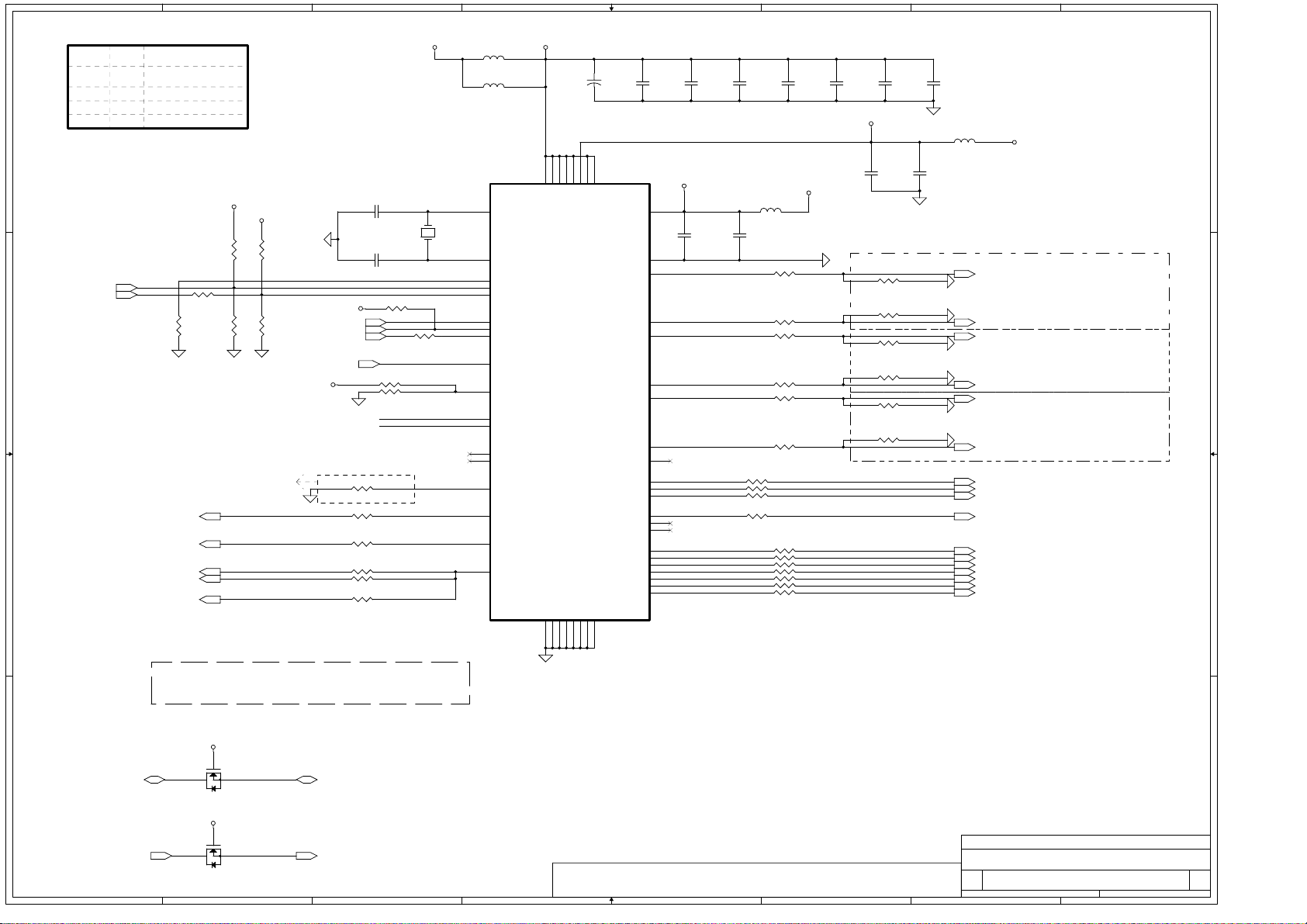

North Bridge Intel 845MP

DDR-SODIMM

Clock Genera to r

VGA ATI M7C/ Penal interface

VGA DDR SGRAM/ CRT & TVOUT CONNECTOR

South Bridge ICH3M

Card Bus Controller / Card Bus Socket

IEEE1394 VT6306 / PHY

LAN Controller RTL8100BL

Audio DJ OZ163

AC97 Codec_ALC2 0 1

Audio EQ_TAS3002

AMP & Audio Jack

HDD/CDROM

LPC EC_PC87591

BIOS & I/O Port

Printer/USB Port/TP

Dot Matrix LCD/FIR/Reset/PS

DC/DC Interface

Mimi-PCI & Docking

SIO VT1211

SD CONTROLLER/SOCKET/UNS E D GA T E S

5V/3V/12V

CHARGER

CPU_COR E

DETECTOR

DDR/Connector

Notes & PIR List

TITLE

TITLE

TITLETITLE

B

stencil not open:

J1

U24

PJP2

PJP4

C715

C716

PC155

C72

C94

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

Title

Size Document Number Rev

B

Date: Sheet

Comp a l Electro nics , In c .

SCHEMATIC, M/B LA -1302

401216

E

145Wednesday, May 29, 2002

of

1B

A

Compal confidential

Model Name : 888Z4/LA-1301 (Intel Northwood)

1 1

Power On/Off

Reset Circuit

page 29

DC/DC Interface

RTC Battery

page 30

2 2

+3VS +5VS +3VALW

Mini PCI

Socket

page 31 page 21

* HSP Modem Card

* Combo for HSP Modem and

802.11b

* Controllerless Modem

* Combo for Controllerless

3 3

Modem and 802.11b

VID SELECT

/CPU_CORE Decouple

CAP.

CRT Connector

+3VS

LCDVDD

page 17

+5VS FOR INVERTER

TFT/HPA Panel

Interface

page 13

TV OUT

Connector

page 17

PCMCIA

S1_VCC +3VALW

Slot 0

page 21

S1_VPP

page 5

B

+3VS

ATI M7C

page

13,14,15

VIA VT6306

1394 ControllerCB1410

+5VALW

+12VALW

LPC BUS

+1.8VS

+1.5VS

+2.5VS

+2.5VS

SGRAM

8/16MB

+3VS

page 22

page 16

AC Link

C

+CPU_CORE

+1.2VS

Intel

Northwood Micro-FCPGA

page 3,4,5

+1.8VS

+1.5VS

+CPU_CORE

Brookdale-M

MCH-M

page6,7,8

PCI BUS

AD(0..31)

+1.8VS +3VS +3VALW+3V

+2.5V

MA(0..13)

MD(0..63)

HUB LINK

ICH3-M

421 BGA

page 18,19,20

D

+2.5V +2.5V

+3VS +3VS

page 9

DDR

SO-DIMM 0

(Bank 0,1)

DDR

SO-DIMM 1

(Bank 2,3)

DDR

Decoupling

+1.8VALW+CPU_CORE

Y1

14.318MHZ

+3VS

Clock Generator

W320-04/9508-05

+3VSUS

+3VRUN

page 10

page12

+1.25VS

TERMINATION

RESISTORS

page 11

+5VS +5VALW +3VALW

USB

Port 0,1

page 31

E

Block Diagram

New

USB

Port 2

Bluetooth

page 31

RJ45/RJ11

Jack

page 23

6-7A 6-7A 3A 50mA

+3VALWP +5VALWP +2.5VALWP

Power Circuit

DC/DC

page 37,38,39,40,41

4 4

A

+3VALW OR +2.5VALW

LAN

RTL8100BL

page 23

+12VALWP

+1.25VP

+1.2VP

PCB1

LA-1302 PCB

3A

300mA

+3VS +3VALW

Super I/O

14M_5V

SMC47N227

page 35

+5VS

Touch Pad

page 31

PIO

page 31

+3VS

Smart Card

Connector

page 36

+3VS,+5VS

B

I/O Buffer

page 30

+3VALW

BIOS

page 30

SD

CONTROLLER

page 36

KeyBoard

NS87591

page 29

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

AC Link

+3VS AVDD +5VALW

AC97

KBD

page 29

+3VCD +5VAMP

Audio

EQ

page 26

Speaker

page 27

C

Codec

page 25

AMP

Jack

page 27

AC Link

+5VCD +5VS

OZ163

page 24

+5VS

+5VCD

CD-ROM

Connector

page 28

HDD

Connector

page 28

+5VCD

+3VCD

+5VAMP +5VALW

D

+5VALW

+3VALW

EN_CDPLAY#

Docking Connector

* DC-IN

* 2 USB Port

* TV Out (S Video)

* VGA Out

* 2 PS/2

* LAN

* Parallel Port

* Serial Port

* Line Out

* Headphone

* Microphone

page 34

Title

Size Document Number Rev

B

Date: Sheet

Comp a l Electro nics , In c .

SCHEMATIC, M/B LA -1302

401216

E

245Wednesday, May 29, 2002

of

1B

5

HA#[3..31]6

HA#3

R221 220_1%_0402

CLK_HCLK

CLK_HCLK#

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

D D

+CPU_CORE

HREQ#[0..4]

R233 10K_0402

1 2

1 2

C C

B B

HREQ#[0..4]6

HADS#6

HBR0#6

HBPRI#6

HBNR#6

HLOCK#6

CLK_HCLK12

CLK_HCLK#12

HIT#6

HITM#6

HDEFER#6

AF22

AF23

W1

W2

AB1

AC1

AA3

AC3

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

T5

U4

V3

Y1

J1

K5

J4

J3

H3

G1

V5

H6

D2

G2

G4

F3

E3

E2

4

+CPU_CORE

U13A

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

HIT#

HITM#

DEFER#

3

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

Mobile

NorthWood

VSS_0

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

H1H4H23

H26

A11

A13

A15

A17

A19

A21

A24

A26A3A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

2

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

HD#0

B21

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

F13

F15

F17

F19

F9

VCC_73

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

E12

E14

E16

E18

E20E8F11

NorthWood

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]HA#[3..31]

1

HD#[0..63] 6

+CPU_CORE

+12VS

+12VS

Fan1 Control circuit Fan2 Control circuit

R91

3.48K_1%

12

C429

.1UF_0402

A A

1 2

R249 13K_1%

5

1 2

VCC

5

1

3

U19

2

VEE

LMV321_SOT23-5

1 2

R245 7.32K_1%

.1UF_0402

C424

4

1 2

21

D15

1N4148

3

Q17

2

2SA1036K

1

Q12

FMMT619

2

C108

2.2UF_16V_0805

1 2

10UF_10V_0805

4

C722

12

+5VS

1

D7

1SS355

3

2 1

+5VFAN1 +5VFAN2

C123

1000PF_0402

JP13

1

2

3

53398-0310

FANSPEED1 29

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

12

C240

@.1UF_0402

EN_FAN229EN_FAN129

3

1 2

R144 @13K_1%

+5VS+5VS

@.1UF_0402

1 2

C239

VCC

5

1

4

3

U17

2

VEE

@LMV321_SOT23-5

1 2

R143 @7.32K_1%

R314

@3.48K_1%

2

1 2

21

3

1

2

D11

@1N4148

Q13

@2SA1036K

Q1

@FMMT619

2

C238

@2.2UF_16V_0805

1 2

C723

@10UF_10V_0805

+5VS

1

D1

@1SS355

3

2 1

12

C1

@1000PF_0402

JP4

1

2

3

@53398-0310

PIRPIR

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1302

Size Document Number Rev

401216

Date: Sheet

3

1

1B

45Wednesday, May 29, 2002

of

200_0402

12

12

12

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

56_0402

12

12

51.1_1%

12

+1.2VS

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_PREQ#

ITP_PRDY#

ITP_BPM0

ITP_BPM1

5

H_A20M#

H_SMI#

H_IGNNE#

H_STPCLK#

H_DPSLP#

H_NMI

H_INIT#

H_INTR

H_F_FERR#

H_PWRGD

H_RESET#

PM_CPUPERF#

Murata LQG21F4R7N00

L14

1 2

L15

1 2

4.7UH_80mA

4.7UH_80mA

12

+

+1.2VS

C49

33UF_D2_16V

CLK_ITPP12

CLK_ITPP#12

H_RS#06

H_RS#16

H_RS#26

H_TRDY#6

H_A20M#18

H_F_FERR#18

H_IGNNE#18

H_SMI#18

H_PWRGD18

H_STPCLK#18

H_DPSLP#18

H_INTR18

H_NMI18

H_INIT#18

H_RESET#6

H_DBSY#6

H_DRDY#6

H_BSEL012

H_BSEL112

1 2

R92 56_0402

TP1

12

C59

+

33UF_D2_16V

H_VSSA

H_A20M#

H_F_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_DPSLP#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM0

ITP_BPM1

ITP_PRDY#

ITP_PREQ#

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

H_VCCA

1

H_VCCIOPLL

R190

51.1_1%

1 2

+CPU_CORE

D D

C C

R226

R230

R234

R231

R191

R229

R228

R240

R224

R194 301_1%_0402

R187

R75

12

Place resistor <100mils from

CPU pin

If used ITP port must depop

RP16 8P4R_1.5K_0804

1 8

2 7

3 6

4 5

+CPU_CORE

B B

R117 51.1_1%

R116 51.1_1%

R119 51.1_1%

R118 51.1_1%

1 2

AB2

AB23

AD25

AB25

AD6

AD5

AC6

AB5

AC4

AA5

AB4

AD20

AE23

AF25

AF3

AC26

AD26

L24

R113

51.1_1%

F1

G5

F4

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

B3

C4

A2

Y6

D4

C1

D5

F7

E6

A5

P1

4

AE11

U13B

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCA

VCCSENSE

VCCIOPLL

NC7

NC8

ITP_CLK0

ITP_CLK1

COMP0

COMP1

3

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26B4B8

C11

C13

C15

C17

C19C2C22

C25C5C7C9D10

D12

D14

D16

D18

D20

D21

D24D3D6D8E1

E11

E13

E15

E17

E19

E23

E26E4E7E9F10

F12

F14

F16

F18F2F22

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

SKTOCC#

VSS_124

Mobile

NorthWood

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

F8

G21

G24G3G6J2J22

J25J5K21

K24K3K6L1L23

L26L4M2

VSS_181

VID0

M22

M25M5N21

N24N3N6P2P22

P25P5R1

R23

R26R4T21

T24T3T6U2U22

U25U5V1

V23

V26V4W21

W24W3W6Y2Y22

AE5

Y25

Y5

NC5

NC6

VID1

VID2

VID3

VID4

AE4

AE3

AE2

AE1

AE21

AF24

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

F25

VSS_125

VSS_126

VSS_127

ITPCLKOUT0

ITPCLKOUT1

PROCHOT#

VCCVID

AF4

F5

VSS_128

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

NC1

NC2

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI8

TESTHI9

TESTHI10

GHI#

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

MCERR#

SLP#

VSSA

VSSSENSE

NC3

NC4

NorthWood

2

J26

K25

K26

L25

AA21

AA6

F20

F6

A22

A7

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

AD22

A4

AD2

AD3

All of these pin

connected

inside

TESTTHI0_1

TESTTHI2_7

ITPCLKOUT0

ITPCLKOUT1

TESTTHI8_10

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_PROCHOT#

H_SLP#

H_VSSA

1

+1.2VS

C135

.1UF_0402

GTL Reference Voltage

Trace width > 7 mils

+CPU_CORE

R192 56_0402

1 2

R193 56_0402

1 2

R200 56_0402

1 2

R195 56_0402

1 2

R225 56_0402

1 2

PM_CPUPERF#

H_DSTBN#[0..3]

H_DSTBP#[0..3]

H_DBI#[0..3]

R232 56_0402

1 2

TP2

H_ADSTB#0 6

H_ADSTB#1 6

12

R188 200_0402

R104

1K_0402

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

PM_CPUPERF# 18

H_DSTBN#[0..3] 6

H_DSTBP#[0..3] 6

H_DBI#[0..3] 6

12

+CPU_CORE

H_SLP# 18

+CPU_CORE

+3VS

182736

1

+CPU_CORE

12

R197

12

C343

CPU_VID4 39

CPU_VID3 39

CPU_VID2 39

CPU_VID1 39

CPU_VID0 39

49.9_1%_0402

12

R196

100_1%_0402

+H_GTLREF1

C338

220PF_0402

1UF_10V

Layout note :

1. Place R_A and R_B near CPU.

2. Place decoupling cap 220PF near CPU.(Within

500mils)

45

RP112

8P4R_1K_0804

VDD1

ALERT

THERM

GND

W=15mil

1 2

+5VALW

+5VS

R246

R519

1 2

1K_0402

+3VALW

R83

10K_0402

1 2

R82

@0_0402

PROCHOT#

4

PROCHOT# 29 MAINP37,40

1

6

4

5

PCIRST#6,13,18,21,22,23,29,34,35,36

@301_1%_0402

2

G

1 3

D

S

Q21

2N7002

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

3

R241

470_0402

1 2

Q23

3904

1 2

1

2

3

Q19

3904

1

3

2

R238

1 2

470_0402

H_THERMTRIP#

PROCHOT#

2

R248

0_0402

R244

1K_0402

+3VS

1

3

R242

470_0402

1 2

1 2

2

Q22

Q18

3904

3904

1

3

R237

2

1 2

Title

Size Document Number Rev

Date: Sheet

H_PROCHOT#

470_0402

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1302

401216

1

4

of

1B

45Wednesday, May 29, 2002

Thermal Sensor ADM1032AR

H_THERMDA

R85

2200PF_0402

H_THERMDC

@0_0402

C122

R81

@0_0402

12

THERMDA_59129

THERMDC_59129

A A

EC_SMC224,29,34

EC_SMD224,29,34

Address:1001_100X

5

.1UF_0402

U56

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032AR_SOP-8

R02

PIR1

C129

A

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

Please place these cap in the socket cavity area

+CPU_CORE

1 1

12

C357

10UF_6.3V_1206_X7R

+CPU_CORE

12

C347

10UF_6.3V_1206_X7R

12

C370

10UF_6.3V_1206_X7R

12

C367

10UF_6.3V_1206_X7R

12

C378

10UF_6.3V_1206_X7R

12

C376

10UF_6.3V_1206_X7R

12

C346

10UF_6.3V_1206_X7R

12

C345

10UF_6.3V_1206_X7R

Please place these cap on the socket north side

+CPU_CORE

12

C102

10UF_6.3V_1206_X7R

2 2

+CPU_CORE

12

C363

10UF_6.3V_1206_X7R

+CPU_CORE

12

C404

10UF_6.3V_1206_X7R

12

C379

10UF_6.3V_1206_X7R

12

C339

10UF_6.3V_1206_X7R

12

C331

10UF_6.3V_1206_X7R

12

C350

10UF_6.3V_1206_X7R

12

C352

10UF_6.3V_1206_X7R

12

C380

10UF_6.3V_1206_X7R

12

C340

10UF_6.3V_1206_X7R

12

C368

10UF_6.3V_1206_X7R

12

C428

10UF_6.3V_1206_X7R

B

12

C355

10UF_6.3V_1206_X7R

12

C358

10UF_6.3V_1206_X7R

12

C421

10UF_6.3V_1206_X7R

12

C397

10UF_6.3V_1206_X7R

C

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

R02

12

C73

+

220UF_D2_4V_25m

12

C715

+

4SP560M

12

C79

.22UF_X7R

PIR2

12

+CPU_CORE

+CPU_CORE

+CPU_CORE

D

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

Used ESR 15m ohm cap total ESR=2.5m ohm

C95

.22UF_X7R

12

C126

+

@220UF_D2_4V_25m

12

C342

+

220UF_D2_4V_25m

12

C100

.22UF_X7R

12

C105

.22UF_X7R

12

+

12

+

C72

@220UF_D2_4V_25m

C364

220UF_D2_4V_25m

12

C78

.22UF_X7R

+

12

12

C60

@220UF_D2_4V_25m

12

C716

+

4SP560M

12

C103

C96

.22UF_X7R

.22UF_X7R

12

C94

+

@220UF_D2_4V_25m

12

C390

+

@220UF_D2_4V_25m

12

C111

.22UF_X7R

12

C113

.22UF_X7R

12

C99

.22UF_X7R

E

Please place these cap on the socket south side

+CPU_CORE

M1

3 3

4 4

12

C387

10UF_6.3V_1206_X7R

+CPU_CORE

12

C67

10UF_6.3V_1206_X7R

+CPU_CORE

12

C61

10UF_6.3V_1206_X7R

12

C150

10UF_6.3V_1206_X7R

12

C334

10UF_6.3V_1206_X7R

12

C112

10UF_6.3V_1206_X7R

12

C408

10UF_6.3V_1206_X7R

12

C383

10UF_6.3V_1206_X7R

12

C80

10UF_6.3V_1206_X7R

12

C56

10UF_6.3V_1206_X7R

12

C372

10UF_6.3V_1206_X7R

12

C97

10UF_6.3V_1206_X7R

EMI Clip PAD for CPU

PAD1

@PAD-2.5X3

1

PAD3

@PAD-2.5X3

PAD5

1

@PAD-2.5X3

A

1

PAD7

@PAD-2.5X3

1

R03 PIR 30

12

C305

10UF_6.3V_1206_X7R

12

C393

10UF_6.3V_1206_X7R

B

CF23

1

FIDUCIAL MARK

CF20

1

FIDUCIAL MARK

CF3

1

FIDUCIAL MARK

CF1

1

FIDUCIAL MARK

Fiducial Mar k

FD3

1

FIDUCIAL MARK

CF10

1

FIDUCIAL MARK

CF6

1

FIDUCIAL MARK

CF19

1

FIDUCIAL MARK

CF4

1

FIDUCIAL MARK

C

FD2

1

FIDUCIAL MARK

CF11

1

FIDUCIAL MARK

CF21

1

FIDUCIAL MARK

CF25

1

FIDUCIAL MARK

CF8

1

FIDUCIAL MARK

HOLEA

FD1

1

FIDUCIAL MARK

CF5

1

FIDUCIAL MARK

CF13

1

FIDUCIAL MARK

CF24

1

FIDUCIAL MARK

CF2

1

FIDUCIAL MARK

H1

1

1

H2

HOLEA

HOLEA

1

1

FD4

1

FIDUCIAL MARK

CF7

1

FIDUCIAL MARK

CF12

1

FIDUCIAL MARK

CF28

1

FIDUCIAL MARK

CF9

1

FIDUCIAL MARK

H4

1

1

FIDUCIAL MARK

FIDUCIAL MARK

FIDUCIAL MARK

FIDUCIAL MARK

FIDUCIAL MARK

H8

HOLEA

1

1

1

1

1

1

FD6

CF15

CF18

CF27

CF17

H3

HOLEA

HOLEA

1

1

FD5

1

FIDUCIAL MARK

CF16

1

FIDUCIAL MARK

CF14

1

FIDUCIAL MARK

CF26

1

FIDUCIAL MARK

CF22

1

FIDUCIAL MARK

H5

1

1

H6

HOLEA

1

1

1

D

H11

H7

HOLEB

1

HOLEH

1

H13

H9

H10

HOLEB

HOLEB

1

1

1

1

H19

H12

HOLEH

HOLEH

1

1

1

1

1

1

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1302

Size Document Number Rev

401216

Date: Sheet

HOLEB

1

HOLEH

H21

HOLEE

1

1

1

H22

H15

HOLEI

1

1

1

1

H16

HOLEF

1

H23

HOLEJ

1

H14

HOLEC

1

1

1

H20

HOLEL

1

1

1

E

HOLEI

1

H17

HOLED

1

H18

HOLEK

1

5

M2

HOLEI

1

1

1

H24

HOLEK

1

1

1

H25

HOLEL

1

1

1

1B

45Wednesday, May 29, 2002

of

A

B

C

D

E

HA#[3..31]3

1 1

H_ADSTB#04

H_ADSTB#14

H_RESET#4

H_TRDY#4

HREQ#[0..4]3

12

12

R213

150_1%_0402

12

12

R211

150_1%_0402

HDEFER#3

H_DBSY#4

H_DRDY#4

CLK_GHT12

CLK_GHT#12

H_DBI#[0..3]4

12

12

HBPRI#3

HLOCK#3

HIT#3

HITM#3

HBR0#3

HADS#3

HBNR#3

H_RS#04

H_RS#14

H_RS#24

C356

.01UF_0402

C351

.01UF_0402

2 2

3 3

+CPU_CORE

R212

301_1%_0402

+CPU_CORE

R208

301_1%_0402

4 4

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

PCIRST#4,13,18,21,22,23,29,34,35,36

HREQ#[0..4]

H_DBI#[0..3]

24.9_1%

A

CLK_GHT

CLK_GHT#

R204

+1.5VS

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_SWNG0

H_SWNG1

12

R218 8.2K_0402

R206 8.2K_0402

R199 8.2K_0402

12

R210

24.9_1%

12

12

12

T4

T5

T3

U3

R3

P7

R2

P4

R6

P5

P3

N2

N7

N3

K4

M4

M3

L3

L5

K3

J2

M5

J3

L2

H4

N5

G2

M6

L7

R5

N6

AE17

U7

Y4

Y7

W5

J27

H26

V5

V4

Y5

Y3

V7

V3

W3

W2

W7

W6

U6

T7

R7

U5

U2

J8

K8

AD5

AG4

AH9

AD15

AA7

AD13

AC2

AC13

AGP_ADSTB0

AGP_ADSTB1

AGP_SBSTB

U9A

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB#0

HADSTB#1

CPURST#

HTRDY#

DEFER#

BPRI#

HLOCK#

RSTIN#

TESTIN#

DBSY#

DRDY#

HIT#

HITM#

BREQ#0

ADS#

BNR#

RS#0

RS#1

RS#2

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

BCLK

BCLK#

DBI#0

DBI#1

DBI#2

DBI#3

HSWNG0

HSWNG1

HRCOMP0

HRCOMP1

H_DSTBN#[0..3]

H_DSTBP#[0..3]

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HOST

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

BROOKDALE(MCH-M)

H_DSTBN#[0..3] 4

H_DSTBP#[0..3] 4

R217 @8.2K_0402

R205 @8.2K_0402

R198 @8.2K_0402

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AD7

AC7

AC6

AC3

AC8

AE2

AG5

AG2

AE8

AF6

AH2

AF3

AG3

AE5

AH7

AH3

AF4

AG8

AG7

AG6

AF8

AH5

AC11

AC12

AE9

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

AD4

AE6

AE11

AC15

AD3

AE7

AD11

AC16

M7

R8

Y8

AB11

AB17

AGP_ADSTB0#

12

AGP_ADSTB1#

12

AGP_SBSTB#

12

B

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

HD#[0..63]

+V_MCH_GTLREF

GTL Reference Voltage

Layout note :

1. Place R_E and R_F near MCH

2. Place decoupling cap 220PF near MCH pin.(Within

500mils)

AGP_ST0

0=System memory is DDR

1=System memory is SDR

HD#[0..63] 3

+CPU_CORE

12

R_E

12

R_F

100_1%_0402

AGP_AD[0..31]13

AGP_C/BE#[0..3]13

AGP_ST[0..2]13

R223

49.9_1%_0402

R227

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

AGP_AD[0..31] HUB_PD[0..10]

AGP_ADSTB013

AGP_ADSTB0#13

AGP_ADSTB113

AGP_ADSTB1#13

AGP_SBSTB13

AGP_SBSTB#13

AGP_FRAME#13

AGP_DEVSEL#13

AGP_IRDY#13

AGP_TRDY#13

AGP_STOP#13

AGP_PAR13

AGP_REQ#13

AGP_GNT#13

Trace

width>=7mils

C362

C394

220PF_0402

1UF_10V

R201 2K_1%_0402

AGP_ST0 AGP_ST1

C

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_SBSTB

AGP_SBSTB#

AGP_FRAME#

AGP_DEVSEL#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_PAR

AGP_REQ#

AGP_GNT#

AGP_PIPE#

12

U9B

R27

G_AD0

R28

G_AD1

T25

G_AD2

R25

G_AD3

T26

G_AD4

T27

G_AD5

U27

G_AD6

U28

G_AD7

V26

G_AD8

V27

G_AD9

T23

G_AD10

U23

G_AD11

T24

G_AD12

U24

G_AD13

U25

G_AD14

V24

G_AD15

Y27

G_AD16

Y26

G_AD17

AA28

G_AD18

AB25

G_AD19

AB27

G_AD20

AA27

G_AD21

AB26

G_AD22

Y23

G_AD23

AB23

G_AD24

AA24

G_AD25

AA25

G_AD26

AB24

G_AD27

AC25

G_AD28

AC24

G_AD29

AC22

G_AD30

AD24

G_AD31

V25

G_C/BE#0

V23

G_C/BE#1

Y25

G_C/BE#2

AA23

G_C/BE#3

AG25

ST0

AF24

ST1

AG26

ST2

R24

AD_STB0

R23

AD_STB#0

AC27

AD_STB1

AC28

AD_STB#1

AF27

SB_STB

AF26

SB_STB#

Y24

G_FRAME#

W28

G_DEVSEL#

W27

G_IRDY#

W24

G_TRDY#

W23

G_STOP#

W25

G_PAR

AG24

G_REQ#

AH25

G_GNT#

AF22

PIPE#

N22

VSS0

K27

VSS1

K5

VSS2

L24

VSS3

M23

VSS4

K7

VSS5

J26

VSS6

A3

VSS7

A7

VSS8

A11

VSS9

A15

VSS10

R203 @1K_0402

12

AGP_FRAME#

AGP_TRDY#

AGP_PAR

AGP_STOP#

AGP_GNT#

AGP_REQ#

AGP_IRDY#

AGP_DEVSEL#

AGP_WBF#

AGP_PIPE#

AGP_RBF#

AGP_ST2

HUB

AGP

BROOKDALE(MCH-M)

R02

PIR3

1 8

2 7

3 6

4 5

1 4

2 3

1 4

2 3

1 8

2 7

3 6

4 5

R202 6.2K_0402

12

6.2K_0402

R189

12

HI_10

HI_STB

HI_STB#

HLRCOMP

HI_REF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPREF

GRCOMP

RBF#

WBF#

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

+1.5VS

D

P25

HI_0

P24

HI_1

N27

HI_2

P23

HI_3

M26

HI_4

M25

HI_5

L28

HI_6

L27

HI_7

M27

HI_8

N28

HI_9

M24

N25

N24

P27

P26

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AA21

AD25

P22

66IN

AE22

AE23

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J29

RP111

@8P4R_8.2K_0804

RP11

@4P2R_8.2K

RP15

@4P2R_8.2K

RP12

@8P4R_8.2K_0804

AGP_ST1

0=533Mhz

1=400Mhz

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HLRCOMP

GRCOMP

AGP_RBF#

AGP_WBF#

HUB_PD[0..10] 18

HUB_PSTRB 18

HUB_PSTRB# 18

R220

1 2

AGP_NBREF

AGP_SBA[0..7]

Place this cap near MCH

+AGPREF

12

C361

.1UF_0402

R66

40.2_1%

12

CLK_AGP_MCH 12

AGP_RBF# 13

AGP_WBF# 13

+1.5VS

12

R166

1K_1%_0402

12

R168

1K_1%_0402

+1.8VS

R214

301_1%_0402

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

CLK_AGP_MCH

R_C

R_D

Title

Size Document Number Rev

Date: Sheet

Comp a l Electro nics , In c .

SCHEMATIC, M/B LA -1302

401216

+1.8VS

36.5_1%

AGP_SBA[0..7] 13

Place this cap near AGP

12

C282

.1UF_0402

HUB Interface Reference

Layout note :

1. Place R_C and R_D close to MCH

2. Place capacitors near MCH.

12

12

C371

@470PF

12

R215

@56.2_1%

12

R216

R219

301_1%_0402

0_0402

12

C385

.01UF_0402

E

12

+VS_HUBREF

12

C384

.01UF_0402

Place closely

ball P26

Place closely pin P22

CLK_AGP_MCH

R222

@33_0402

1 2

C386

@10PF_0402

+VS_HUBREF

645Wednesday, May 29, 2002

of

1B

A

B

C

D

E

U9D

M8

+CPU_CORE

1 1

+2.5V

2 2

3 3

4 4

VTT_0

U8

VTT_1

AA9

VTT_2

AB8

VTT_3

AB18

VTT_4

AB20

VTT_5

AC19

VTT_6

AD18

VTT_7

AD20

VTT_8

AE19

VTT_9

AE21

VTT_10

AF18

VTT_11

AF20

VTT_12

AG19

VTT_13

AG21

VTT_14

AG23

VTT_15

AJ19

VTT_16

AJ21

VTT_17

AJ23

VTT_18

A5

VCCSM1

A9

VCCSM2

A13

VCCSM3

A17

VCCSM4

A21

VCCSM5

A25

VCCSM6

C1

VCCSM7

C29

VCCSM8

D7

VCCSM9

D11

VCCSM10

D15

VCCSM11

D19

VCCSM12

D23

VCCSM13

D25

VCCSM14

F6

VCCSM15

F10

VCCSM16

F14

VCCSM17

F18

VCCSM18

F22

VCCSM19

G1

VCCSM20

G4

VCCSM21

G29

VCCSM22

H8

VCCSM23

H10

VCCSM24

H12

VCCSM25

H14

VCCSM26

H16

VCCSM27

H18

VCCSM28

H20

VCCSM29

H22

VCCSM30

H24

VCCSM31

K22

VCCSM32

K24

VCCSM33

K26

VCCSM34

L23

VCCSM35

K6

VCCSM36

J5

VCCSM37

J7

VCCSM38

L1

VSS41

L4

VSS42

L6

VSS43

L8

VSS44

L22

VSS45

L26

VSS46

N1

VSS47

N4

VSS48

N8

VSS49

N13

VSS50

N15

VSS51

N17

VSS52

N29

VSS53

P6

VSS54

P8

VSS55

P14

VSS56

P16

VSS57

R1

VSS58

R4

VSS59

R13

VSS60

R15

VSS61

R17

VSS62

R26

VSS63

T6

VSS64

T8

VSS65

T14

VSS66

T16

VSS67

T22

VSS68

U1

VSS69

U4

VSS70

U15

VSS71

U29

VSS72

V6

VSS73

V8

VSS74

V22

VSS75

W1

VSS76

W4

VSS77

W8

VSS78

W26

VSS79

Y6

VSS80

Y22

VSS81

AA1

VSS82

BROOKDALE(MCH-M)

POWER/GND

VCC1_5_0

VCC1_5_1

VCC1_5_2

VCC1_5_3

VCC1_5_4

VCC1_5_5

VCC1_5_6

VCC1_5_7

VCC1_5_8

VCC1_5_9

VCC1_5_10

VCC1_5_11

VCC1_5_12

VCC1_5_13

VCC1_5_14

VCC1_5_15

VCC1_5_16

VCC1_5_17

VCC1_5_18

VCC1_5_19

VCC1_5_20

VCC1_5_21

VCC1_5_22

VCC1_5_23

VCC1_5_24

VCC1_5_25

VCC1_8_0

VCC1_8_1

VCC1_8_2

VCC1_8_3

VCC1_8_4

VCCGA1

VCCHA1

VSSGA2

VSSHA2

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

R22

R29

U22

U26

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

L29

N26

L25

M22

N23

T17

T13

U17

U13

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ3

AJ5

AJ7

AJ9

AJ11

AJ13

AJ15

AJ17

AJ27

VCC_MCH_PLL1

VCC_MCH_PLL0

VSS_MCH_PLL1

VSS_MCH_PLL0

+1.5VS

Layout note :

Trace width 5mil ; Spacing

10mil

Trace A to ball U13/T13 or

U17/T7 =1.5" Max

+1.5VS

+1.8VS

12

"Trace A"

12

+

"Trace A"

"Trace A"

L34

4.7UH_30mA

"Trace A"

C381

33UF_D2_16V

Murata LQG21N4R7K10

12

L35

4.7UH_30mA

12

C389

+

33UF_D2_16V

DDR_SDQ[0..63]9

DDR_CB[0..7]9

SDREF

DDR_SDQ[0..63]

DDR_CB[0..7]

R235

DDR_SDQ0

DDR_SDQ1

DDR_SDQ2

DDR_SDQ3

DDR_SDQ4

DDR_SDQ5

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ10

DDR_SDQ11

DDR_SDQ12

DDR_SDQ13

DDR_SDQ14

DDR_SDQ15

DDR_SDQ16

DDR_SDQ17

DDR_SDQ18

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ22

DDR_SDQ23

DDR_SDQ24

DDR_SDQ25

DDR_SDQ26

DDR_SDQ27

DDR_SDQ28

DDR_SDQ29

DDR_SDQ30

DDR_SDQ31

DDR_SDQ32

DDR_SDQ33

DDR_SDQ34

DDR_SDQ35

DDR_SDQ36

DDR_SDQ37

DDR_SDQ38

DDR_SDQ39

DDR_SDQ40

DDR_SDQ41

DDR_SDQ42

DDR_SDQ43

DDR_SDQ44

DDR_SDQ45

DDR_SDQ46

DDR_SDQ47

DDR_SDQ48

DDR_SDQ49

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ53

DDR_SDQ54

DDR_SDQ55

DDR_SDQ56

DDR_SDQ57

DDR_SDQ58

DDR_SDQ59

DDR_SDQ60

DDR_SDQ61

DDR_SDQ62

DDR_SDQ63

DDR_CB0

DDR_CB1

DDR_CB2

DDR_CB3

DDR_CB4

DDR_CB5

DDR_CB6

DDR_CB7

SDREF_M

12

0_0402

Layout note

Please

closely

pinJ21 and

J9

12

C402

.1UF_0402_X5R

U9C

G28

SDQ0

F27

SDQ1

C28

SDQ2

E28

SDQ3

H25

SDQ4

G27

SDQ5

F25

SDQ6

B28

SDQ7

E27

SDQ8

C27

SDQ9

B25

SDQ10

C25

SDQ11

B27

SDQ12

D27

SDQ13

D26

SDQ14

E25

SDQ15

D24

SDQ16

E23

SDQ17

C22

SDQ18

E21

SDQ19

C24

SDQ20

B23

SDQ21

D22

SDQ22

B21

SDQ23

C21

SDQ24

D20

SDQ25

C19

SDQ26

D18

SDQ27

C20

SDQ28

E19

SDQ29

C18

SDQ30

E17

SDQ31

E13

SDQ32

C12

SDQ33

B11

SDQ34

C10

SDQ35

B13

SDQ36

C13

SDQ37

C11

SDQ38

D10

SDQ39

E10

SDQ40

C9

SDQ41

D8

SDQ42

E8

SDQ43

E11

SDQ44

B9

SDQ45

B7

SDQ46

C7

SDQ47

C6

SDQ48

D6

SDQ49

D4

SDQ50

B3

SDQ51

E6

SDQ52

B5

SDQ53

C4

SDQ54

E5

SDQ55

C3

SDQ56

D3

SDQ57

F4

SDQ58

F3

SDQ59

B2

SDQ60

C2

SDQ61

E2

SDQ62

G5

SDQ63

C16

SDQ64/CB0

D16

SDQ65/CB1

B15

SDQ66/CB2

C14

SDQ67/CB3

B17

SDQ68/CB4

C17

SDQ69/CB5

C15

SDQ70/CB6

D14

SDQ71/CB7

J21

SDREF0

J9 AD26

SDREF1 NC0

BROOKDALE(MCH-M)

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCK6

SCK#6

SCK7

SCK#7

SCK8

SCK#8

SCS#0

SCS#1

SCS#2

SCS#3

SCS#4

MEMORY

SCS#5

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SMA0/CS#11

SMA1/CS#10

SMA2/CS#6

SMA3/CS#9

SMA4/CS#5

SMA5/CS#8

SMA6/CS#7

SMA7/CS#4

SMA8/CS#3

SMA9/CS#0

SMA10

SMA11/CS#2

SMA12/CS#1

SBS0

SBS1

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SMRCOMP

RCVENIN#

RCVENOUT#

SSI_ST

SRAS#

SWE#

SCAS#

NC1

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

K25

J25

G17

G16

H7

H6

E9

F7

F9

E7

G9

G10

F26

C26

C23

B19

D12

C8

C5

E3

E15

E12

F17

E16

G18

G19

E18

F19

G21

G20

F21

F13

E20

G22

G12

G13

G23

E22

H23

F23

J23

K23

J28

G3

H3

H27

F11

G11

G8

AD27

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SDQS8

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SBS0

DDR_SBS1

DDR_CKE0

DDR_CKE1

DDR_CKE2

DDR_CKE3

SM_RCOMP

RCVIN#

RCVOUT#

DDR_SRAS#

DDR_SWE#

DDR_SCAS#

R239

DDR_SMA[0..12]

R236 30.1_1%

12

0_0402

R_J

DDR_CLK0 9

DDR_CLK0# 9

DDR_CLK1 9

DDR_CLK1# 9

DDR_CLK2 9

DDR_CLK2# 9

DDR_CLK3 10

DDR_CLK3# 10

DDR_CLK4 10

DDR_CLK4# 10

DDR_CLK5 10

DDR_CLK5# 10

DDR_SCS#0 9

DDR_SCS#1 9

DDR_SCS#2 10

DDR_SCS#3 10

DDR_SDQS0 9

DDR_SDQS1 9

DDR_SDQS2 9

DDR_SDQS3 9

DDR_SDQS4 9

DDR_SDQS5 9

DDR_SDQS6 9

DDR_SDQS7 9

DDR_SDQS8 9

DDR_SBS0 9,10

DDR_SBS1 9,10

DDR_CKE0 9

DDR_CKE1 9

DDR_CKE2 10

DDR_CKE3 10

12

C399 .1UF_0402_X5R

C411 @47PF_0402

DDR_SRAS# 9,10

DDR_SWE# 9,10

DDR_SCAS# 9,10

DDR_SMA[0..12] 9,10

Layout note

+1.25VS

Layout note

Place R_J closely Ball

H3<40mil,Ball H3 to G3 trace

must

routing 1"

Place R620

closely pinJ28

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

A

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

Title

Size Document Number Rev

Date: Sheet

Comp a l Electro nics , In c .

SCHEMATIC, M/B LA -1302

401216

745Wednesday, May 29, 2002

E

1B

of

5

4

3

2

1

Layout note :

Distribute as close as p ossi ble

to MCH Processor Quad rant.(between VTTFSB and VSS pin)

+CPU_CORE

D D

12

C336

.1UF_0402_X 5R

+CPU_CORE

12

C348

.1UF_0402_X 5R

+CPU_CORE

12

C374

10UF_6.3V_1206 _X5R

C C

Layout note :

Distribute as close as p ossi ble

to MCH Processor Quadrant.(between VCCAGP/VCCCORE

and VSS pin)

Processor system bus

12

C337

.1UF_0402_X 5R

12

C335

.1UF_0402_X 5R

12

10UF_6.3V_120 6_X5R

C365

12

C341

.1UF_0402_X5 R

12

C344

.1UF_0402_X5 R

AGP/CORE

12

C359

.1UF_0402_X5 R

12

C392

.1UF_0402_X5 R

12

C332

10UF_6.3V_120 6_X5R

12

C373

.1UF_0402_X 5R

12

C353

.1UF_0402_X 5R

Layout note :

Distribute as close as p ossi ble

to MCH Processor Quadrant .(between VCCSM and VSS pin)

+2.5V

12

C407

.1UF_0402_X5 R

+2.5V

12

C426

.1UF_0402_X5 R

+2.5V

12

C403

.1UF_0402_X5 R

+2.5V

12

C405

+

150UF_6.3V_D2

DDR Memory interface

12

C418

.1UF_0402_X 5R

12

C409

.1UF_0402_X 5R

12

C412

.1UF_0402_X 5R

12

C415

.1UF_0402_X 5R

12

C410

.1UF_0402_X 5R

12

C422

.1UF_0402_X 5R

12

C400

.1UF_0402_X 5R

12

C420

.1UF_0402_X 5R

12

C414

.1UF_0402_X 5R

12

C416

.1UF_0402_X5 R

12

C406

.1UF_0402_X5 R

12

C423

.1UF_0402_X5 R

12

C413

22UF_10V_1 206

12

C417

22UF_10V_12 06

+1.5VS

12

C349

.1UF_0402_X 5R

B B

+1.5VS

12

C398

10UF_6.3V_1206 _X5R

Layout note :

Distribute as close as p ossi ble

to MCH Processor Quadrant .(between VCCHL and VSS pin)

+1.8VS

A A

12

C391

10UF_6.3V_1206 _X5R

12

C360

.1UF_0402_X 5R

12

10UF_6.3V_120 6_X5R

Hub-Link

12

C395

.1UF_0402_X 5R

5

C401

12

C354

.1UF_0402_X5 R

12

C388

.1UF_0402_X5 R

12

C366

+

150UF_6.3V_D2

12

12

C375

.1UF_0402_X5 R

C396

.1UF_0402_X 5R

12

C369

.1UF_0402_X 5R

4

12

C382

.1UF_0402_X 5R

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1302

401216

845Wednesday, May 29, 2002

1

1B

of

A

DDR_SDQ0

DDR_SDQ4

DDR_SDQ1

DDR_SDQ5

DDR_SDQ6

1 1

Layout note

Place these resistor

closely DIMM0,

all trace length<750mil

2 2

3 3

DDR_SDQ[0..63]7

DDR_SDQS[0..8]7

4 4

A

DDR_SDQS0

DDR_SDQ2

DDR_SDQ3

DDR_SDQ8

DDR_SDQ7

DDR_SDQ9

DDR_SDQ12

DDR_SDQS1

DDR_SDQ13

DDR_SDQ10

DDR_SDQ14

DDR_SDQ15

DDR_SDQ11

DDR_SDQ16

DDR_SDQ20

DDR_SDQ21

DDR_SDQ17

DDR_SDQ18

DDR_SDQS2

DDR_SDQ19

DDR_SDQ22

DDR_SDQ24

DDR_SDQ23

DDR_SDQ25

DDR_SDQ28

DDR_SDQS3

DDR_SDQ29

DDR_SDQ[0..63]

DDR_CB[0..7]7

DDR_CB[0..7]

DDR_SDQS[0..8]

DDR_SDQ56

DDR_SDQ51

DDR_SDQ60

DDR_SDQ57

DDR_SDQS7

DDR_SDQ61

DDR_SDQ62

DDR_SDQ58

DDR_SDQ63 DDR_DQ63

DDR_SDQ59 DDR_DQ59

B

RP42 4P2R_22

1 4

2 3

RP19 4P2R_22

1 4

2 3

RP43 4P2R_22

1 4

2 3

RP20 4P2R_22

1 4

2 3

RP44 4P2R_22

1 4

2 3

RP21 4P2R_22

1 4

2 3

RP45 4P2R_22

1 4

2 3

RP22 4P2R_22

1 4

2 3

RP46 4P2R_22

1 4

2 3

RP23 4P2R_22

1 4

2 3

RP47 4P2R_22

1 4

2 3

RP24 4P2R_22

1 4

2 3

RP48 4P2R_22

1 4

2 3

RP25 4P2R_22

1 4

2 3

RP49 4P2R_22

1 4

2 3

RP26 4P2R_22

1 4

2 3

RP61 4P2R_22

1 4

2 3

RP38 4P2R_22

1 4

2 3

RP62 4P2R_22

1 4

2 3

RP39 4P2R_22

1 4

2 3

RP63 4P2R_22

1 4

2 3

B

DDR_DQ0

DDR_DQ4

DDR_DQ1

DDR_DQ5

DDR_DQ6

DDR_DQS0

DDR_DQ2

DDR_DQ3

DDR_DQ8

DDR_DQ7

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ13

DDR_DQ10

DDR_DQ14

DDR_DQ15

DDR_DQ11

DDR_DQ16

DDR_DQ20

DDR_DQ21

DDR_DQ17

DDR_DQ18

DDR_DQS2

DDR_DQ19

DDR_DQ22

DDR_DQ24

DDR_DQ23

DDR_DQ25

DDR_DQ28

DDR_DQS3

DDR_DQ29

DDR_DQ56

DDR_DQ51

DDR_DQ60

DDR_DQ57

DDR_DQS7

DDR_DQ61

DDR_DQ62

DDR_DQ58

DDR_SDQ30

DDR_SDQ26

DDR_SDQ31

DDR_SDQ27

DDR_CB5

DDR_CB4

DDR_CB1

DDR_CB0

DDR_CB2

DDR_SDQS8

DDR_CB3

DDR_CB6

DDR_CB7

DDR_SDQ36

DDR_SDQ32

DDR_SDQ33

DDR_SDQ37

DDR_SDQ38

DDR_SDQS4

DDR_SDQ39

DDR_SDQ34

DDR_SDQ44

DDR_SDQ35

DDR_SDQ45

DDR_SDQ40

DDR_SDQS5

DDR_SDQ41

DDR_SDQ43

DDR_SDQ42

DDR_SDQ47

DDR_SDQ46

DDR_SDQ49

DDR_SDQ48

DDR_SDQ53

DDR_SDQ52

DDR_SDQ54

DDR_SDQS6

DDR_SDQ55

DDR_SDQ50

C

RP50 4P2R_22

1 4

2 3

RP27 4P2R_22

1 4

2 3

RP51 4P2R_22

1 4

2 3

RP28 4P2R_22

1 4

2 3

RP52 4P2R_22

1 4

2 3

RP29 4P2R_22

1 4

2 3

RP53 4P2R_22

1 4

2 3

RP40 4P2R_22

1 4

2 3

RP55 4P2R_22

1 4

2 3

RP32 4P2R_22

1 4

2 3

RP56 4P2R_22

1 4

2 3

RP33 4P2R_22

1 4

2 3

RP57 4P2R_22

1 4

2 3

RP34 4P2R_22

1 4

2 3

RP58 4P2R_22

1 4

2 3

RP35 4P2R_22

1 4

2 3

RP59 4P2R_22

1 4

2 3

RP36 4P2R_22

1 4

2 3

RP60 4P2R_22

1 4

2 3

RP37 4P2R_22

1 4

2 3

C

DDR_DQ30

DDR_DQ26

DDR_DQ31

DDR_DQ27

DDR_F_CB5

DDR_F_CB4

DDR_F_CB1

DDR_F_CB0

DDR_F_CB2

DDR_DQS8

DDR_F_CB3

DDR_F_CB6

DDR_F_CB7

DDR_DQ36

DDR_DQ32

DDR_DQ33

DDR_DQ37

DDR_DQ38

DDR_DQS4

DDR_DQ39

DDR_DQ34

DDR_DQ44

DDR_DQ35

DDR_DQ45

DDR_DQ40

DDR_DQS5

DDR_DQ41

DDR_DQ43

DDR_DQ42

DDR_DQ47

DDR_DQ46

DDR_DQ49

DDR_DQ48

DDR_DQ53

DDR_DQ52

DDR_DQ54

DDR_DQS6

DDR_DQ55

DDR_DQ50

D

DDR_DQ4

DDR_DQ5

DDR_DQS0

DDR_DQ3

DDR_DQ7

DDR_DQ12

DDR_DQ13

DDR_DQS1

DDR_DQ14

DDR_DQ11

DDR_CLK17

DDR_CLK1#7

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ22

DDR_DQ23

DDR_DQ28

DDR_DQ29

DDR_DQS3

DDR_DQ26

DDR_DQ27

DDR_F_CB4

DDR_F_CB0 DDR_F_CB1

DDR_DQS8

DDR_F_CB6

DDR_F_CB7

DDR_CLK07

DDR_CLK0#7

DIMM_SMDATA10,12

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

D

DDR_CKE1 DDR_CKE0

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS0

DDR_SWE#

DDR_SCS#0 DDR_SCS#1

DDR_DQ36

DDR_DQ33

DDR_DQS4

DDR_DQ38

DDR_DQ39

DDR_DQ44

DDR_DQ45

DDR_DQS5

DDR_DQ43

DDR_DQ47

DDR_DQ49

DDR_DQ53

DDR_DQS6

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ60

DDR_DQS7

DDR_DQ62

DDR_DQ63

DIMM_SMCLK10,12

+3VS

E

+2.5V +2.5V

JP17

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

DDR-SODIMM_200_Normal

VREF

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ31

DU/RESET#

CKE0

DU/BA2

RAS#

CAS#

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQ46

DQ47

CK1#

DQ52

DQ53

DQ54

DQ55

DQ60

DQ61

DQ62

DQ63

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

VDD

DM1

VSS

VDD

VDD

VSS

VSS

VDD

DM2

VSS

VDD

DM3

VSS

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

VSS

VSS

VDD

VDD

VSS

VDD

BA1

VSS

VDD

DM4

VSS

VDD

DM5

VSS

VDD

CK1

VSS

VDD

DM6

VSS

VDD

DM7

VSS

VDD

SA0

SA1

SA2

F

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

DIMM0

top side

E

F

DDR_DQ0

DDR_DQ1

DDR_DQ6

DDR_DQ2

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ15

DDR_DQ16

DDR_DQ21

DDR_DQ18

DDR_DQ19

DDR_DQ24

DDR_DQ25

DDR_DQ30

DDR_DQ31

DDR_F_CB5

DDR_F_CB2

DDR_F_CB3

DDR_SMA11

DDR_SMA8

DDR_SMA6

DDR_SMA4

DDR_SMA2

DDR_SMA0

DDR_SBS1

DDR_SRAS#

DDR_SCAS#

DDR_DQ32

DDR_DQ37

DDR_DQ34

DDR_DQ35

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ46

DDR_DQ48

DDR_DQ52

DDR_DQ50

DDR_DQ51

DDR_DQ57

DDR_DQ61

DDR_DQ58

DDR_DQ59

DDR_SBS07,10

DDR_SWE#7,10

DDR_SCAS#7,10

DDR_SRAS#7,10

DDR_SBS17,10

SDREF_DIMM

12

C184

.1UF_0402

G

DDR_DQ[0..63]

DDR_F_CB[0..7]

DDR_DQS[0..8]

12

SDREF

0_0402

R136

SDREF width 12 mil, space 12 mil

DDR_SMA[0..12] 7,10

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA8

DDR_SMA10

DDR_SMA0

DDR_SMA2

DDR_SMA5

DDR_SMA1

DDR_SMA3

DDR_SMA6

DDR_SMA4

DDR_SMA11

DDR_F_SMA[0..12]10

H

DDR_DQ[0..63] 10

DDR_F_CB[0..7] 10

DDR_DQS[0..8] 10

LENGTH < 3 "

RP30 4P2R_10

DDR_F_SMA12

1 4

DDR_F_SMA9

2 3

RP31 4P2R_10

DDR_F_SMA7

1 4

DDR_F_SMA8

2 3

RP41 4P2R_10

DDR_F_SMA10

1 4

DDR_F_SMA0

2 3

RP54 4P2R_10

DDR_F_SMA2

1 4

DDR_F_SMA5

2 3

RP18 4P2R_10

DDR_F_SMA1

1 4

DDR_F_SMA3

2 3

RP115 4P2R_10

DDR_F_SMA6

1 4

DDR_F_SMA4

2 3

R133 10_0402

1 2

DDR_F_SMA11

Layout note

DDR_CKE0 7DDR_CKE17

Place these resistor

closely DIMM0,

all trace length<=750mil

Layout note

Place these resistor

closely DIMM0,

DDR_SCS#1 7DDR_SCS#07

DDR_CLK2# 7

DDR_CLK2 7

all trace length Max=1.3"

RP127 4P2R_56

DDR_CKE0

1 4

DDR_CKE1

2 3

RP124 4P2R_56

DDR_SCS#0

1 4

DDR_SCS#1

2 3

Layout note

Place these resistor

closely DIMM0,

all trace

DDR_SBS0

DDR_SWE#

DDR_SCAS#

DDR_SRAS#

DDR_SBS1

Title

Size Document Number Rev

Date: Sheet

RP114 4P2R_10

1 4

2 3

RP113 4P2R_10

1 4

2 3

R134 10_0402

1 2

SCHEMATIC, M/B LA -1302

401216

G

length<=750mil

DDR_F_SBS0

DDR_F_SWE#

DDR_F_SCAS#

DDR_F_SRAS#

DDR_F_SBS1

DDR_F_SBS0 10

DDR_F_SWE# 10

DDR_F_SCAS# 10

DDR_F_SRAS# 10

DDR_F_SBS1 10

Comp a l Electro nics , In c .

945Wednesday, May 29, 2002

of

H

+1.25VS

1B

A

+1.25VS +1.25VS

RP64 4P2R_56

DDR_DQ4

1 4

2 3

RP65 4P2R_56

DDR_DQ5

1 4

DDR_DQ1

2 3

DDR_DQS0

DDR_DQ6

DDR_DQ3

DDR_DQ2

DDR_DQ7

DDR_DQ8

DDR_DQ12

DDR_DQ9

DDR_DQS1

DDR_DQ13

DDR_DQ14

DDR_DQ10

DDR_DQ11

DDR_DQ15

DDR_DQ20

DDR_DQ16

DDR_DQ17

DDR_DQ21

DDR_DQS2

DDR_DQ18

DDR_DQ22

DDR_DQ19

DDR_DQ23

DDR_DQ24

DDR_DQ28

DDR_DQ25

DDR_DQS3

DDR_DQ29

RP66 4P2R_56

1 4

2 3

RP67 4P2R_56

1 4

2 3

RP68 4P2R_56

1 4

2 3

RP69 4P2R_56

1 4

2 3

RP70 4P2R_56

1 4

2 3

RP71 4P2R_56

1 4

2 3

RP72 4P2R_56

1 4

2 3

RP132 4P2R_56

1 4

2 3

RP73 4P2R_56

1 4

2 3

RP74 4P2R_56

1 4

2 3

RP75 4P2R_56

1 4

2 3

RP130 4P2R_56

1 4

2 3

RP76 4P2R_56

1 4

2 3

RP77 4P2R_56

1 4

2 3

1 1

2 2

3 3

RP131 4P2R_56

DDR_DQ26

14

DDR_DQ30

23

RP79 4P2R_56

DDR_F_CB1

14

DDR_DQ27

23

RP78 4P2R_56

DDR_F_CB5

14

DDR_DQ31

23

RP80 4P2R_56

DDR_F_CB0

14

DDR_F_CB4

23

RP129 4P2R_56

DDR_F_CB2

14

DDR_DQS8

23

RP128 4P2R_56

DDR_F_CB3

14

DDR_F_CB6

23

RP81 4P2R_56

14

DDR_F_CB7

23

RP89 4P2R_56

DDR_DQ36

14

DDR_DQ32

23

RP122 4P2R_56

DDR_DQ37

14

DDR_DQ33

23

RP90 4P2R_56

DDR_DQ38

14

DDR_DQS4

23

RP91 4P2R_56

DDR_DQ39

14

DDR_DQ34

23