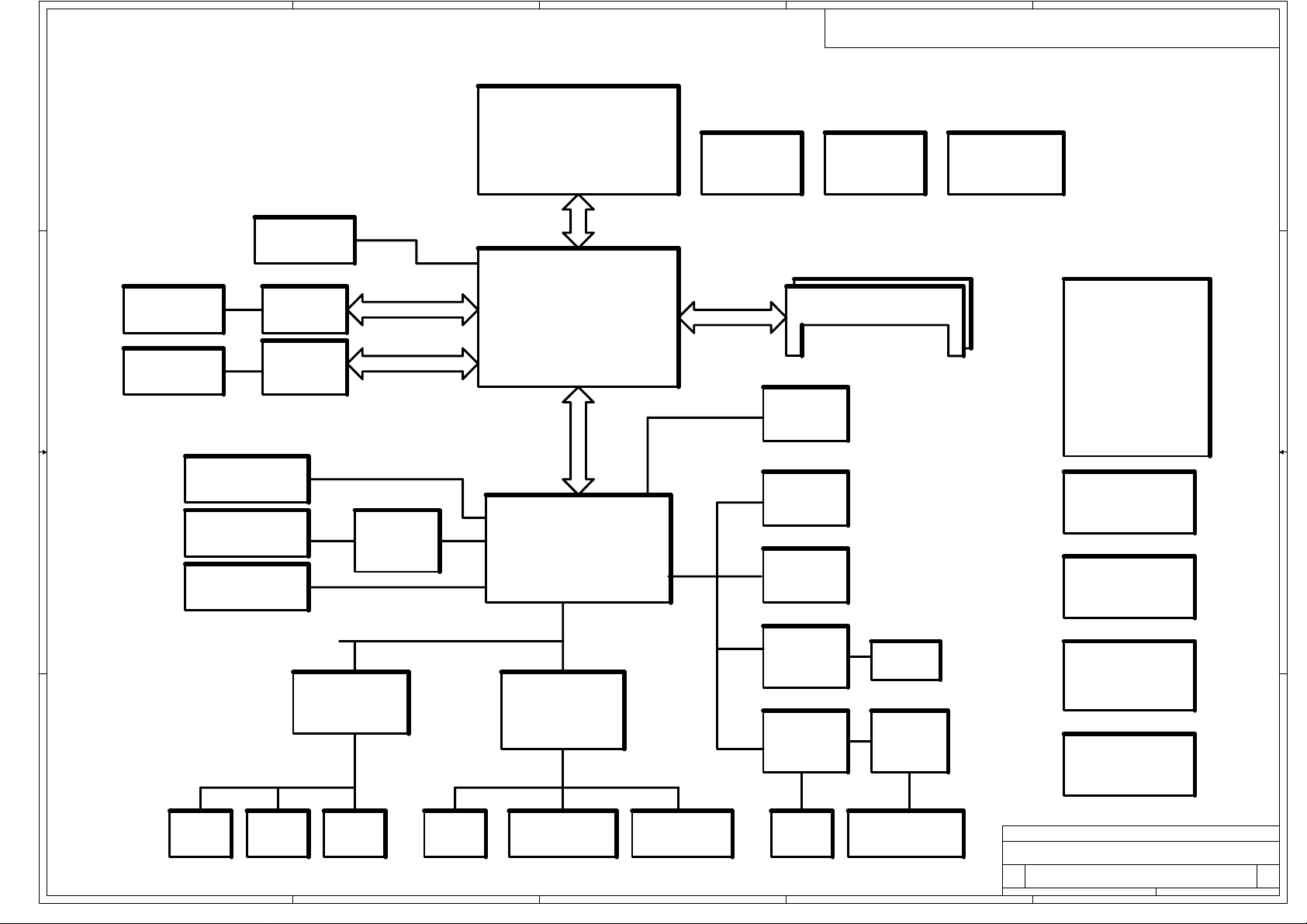

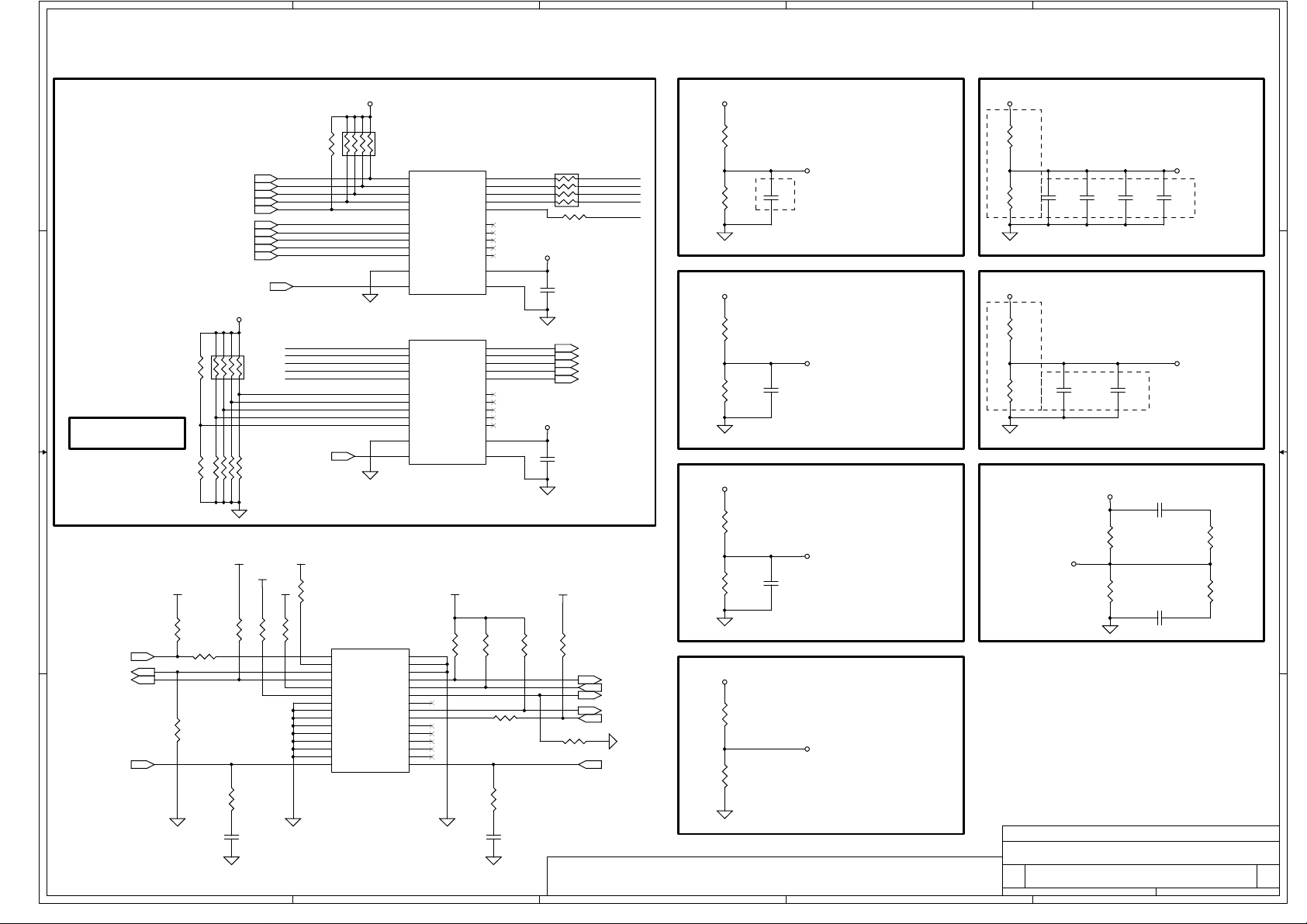

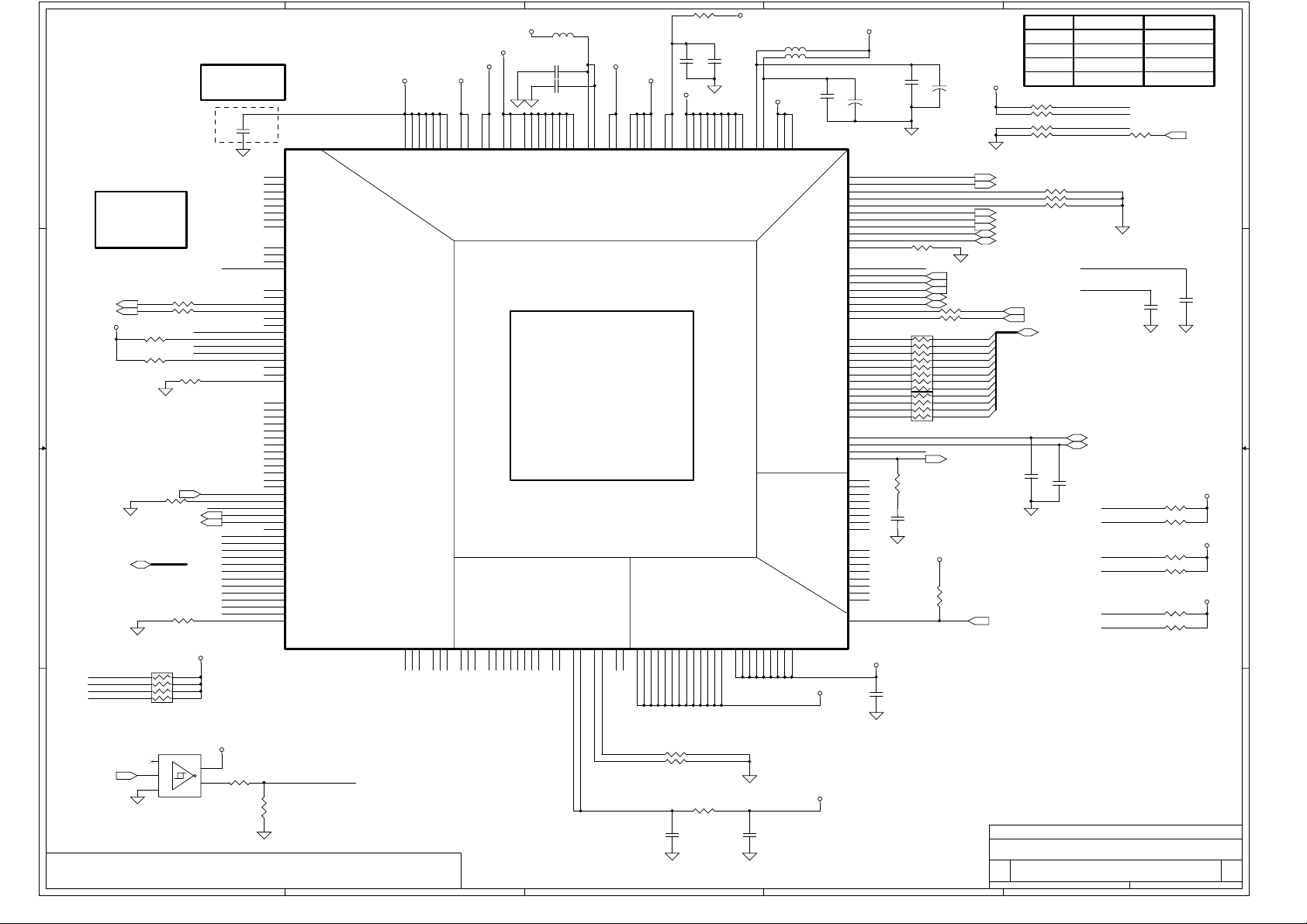

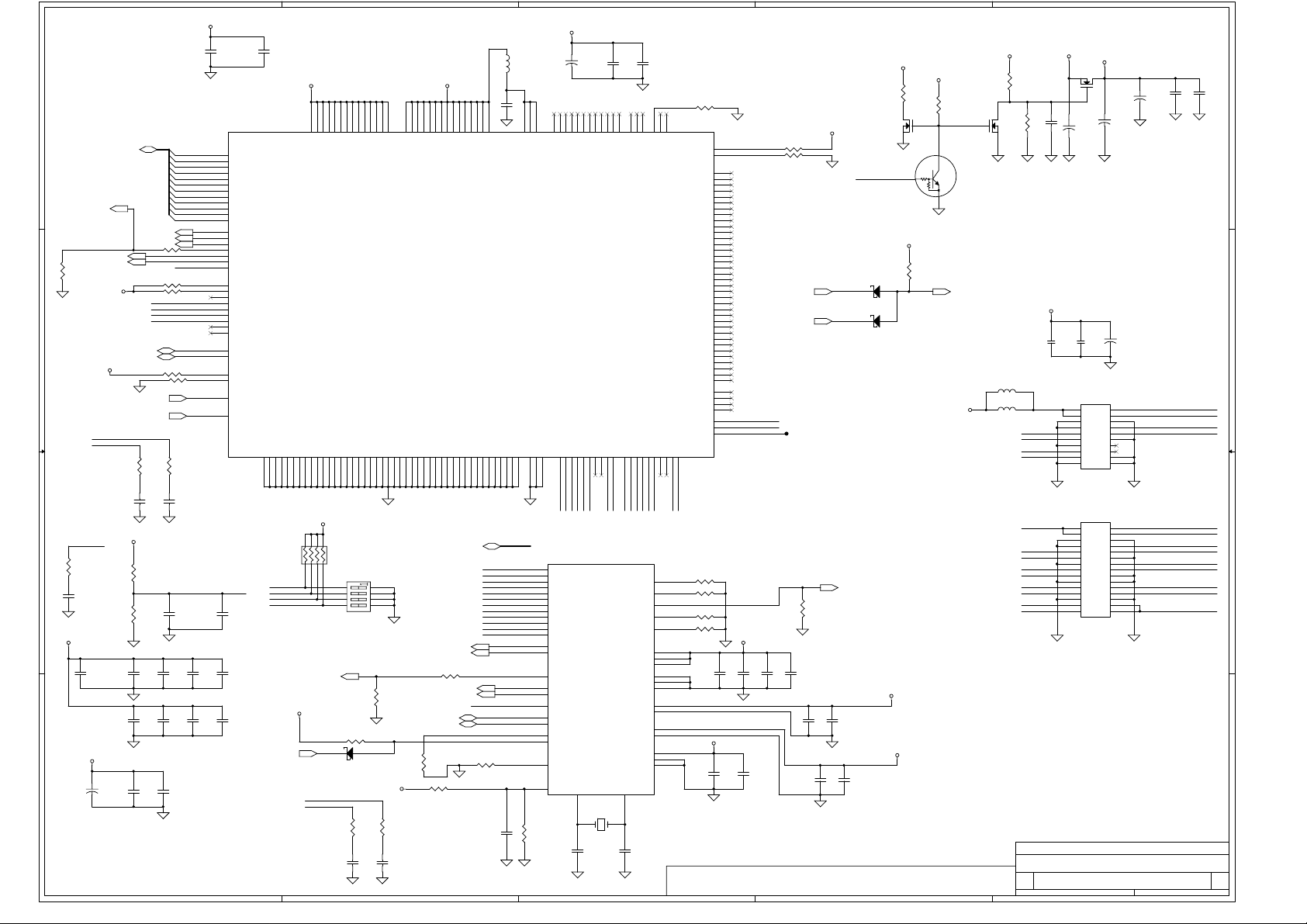

Acer LA-1011 Schematics

A

Model Name :

N32N101

PCB No :

4 4

LA-1011

Date :

2001/09/01

B

BLOCK

DIAGRAM

Mobile Tualatin

or

Coppermine -T

(uFCBGA/uFCPGA)

PAGE 4,5

C

Thermal Sensor

MAX1617MEE

PAGE 5

PAGE 8

D

CPU VID & All

reference vol t a g e

PAGE 7

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

CK TITAN

ICS9250-38

E

PSB

Revision : 1.0

CRT

Conn.

PAGE 16

LVDS

Conn.

PAGE 15

3 3

TV-Out

Conn.

PAGE 16

HDD Connec to r

CD-ROM Connec to r

2 2

1 1

USB & BlueTooth

VCH

TV-Out

Encoder

PAGE 21

PAGE 21

PAGE 20

DVOA Bus Interface

PAGE 15

DVOC Bus Interface

PAGE 15

Super I/O

NS PC87391

PAGE 32

ATA 66/100

Audio DJ

OZ163

Rev.C

PAGE 26

USB

LPC

GMCH-M

625 BGA

HUB

Interface

ICH3-M

421 BGA

Embedded

Controller

NS PC87591

PAGE 30

Memory Bus

PAGE 9,10,11

LAN

PCI BUS

PAGE 17,18

Almador-M

Kinnereth

82562ET

PAGE 25

IEEE-1394

Controller

PAGE 22

Mini PCI

Socket

PAGE 38

CardBus

OZ6933T

PAGE 23

Audio

Controller

ES1988

PAGE 27

SO-DIMM X2

BANK 0, 1, 2, 3

Slot 0/1

PAGE 24

EQ Circuit

PAGE 29

PAGE 14

Docking Connector

LAN

USB X 2

PARALLEL PORT

SERIAL PORT

DC-IN JACK

LINE OUT

EXT. MIC IN

CRT CONN.

PS/2 CONN.

PAGE 37

FAN on controller &

TEMP. sensing circuit

PAGE 36

DC/DC Interface

RTC Battery

PAGE 39

BATTERY

Charger

PAGE 42

POWER

Interface

PAGE 40,41,42,44

Parallel

PAGE 33 PAGE 31

A

FIR

PAGE 33

FDD

PAGE 33

B

ROM

BIOS

Scan KB

PAGE 35

PS/2 Interface

PAGE 35

C

Mic Jack

PAGE 28

Audio Amplifier

PAGE 28

D

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

246Friday, September 21, 2001

E

of

1A

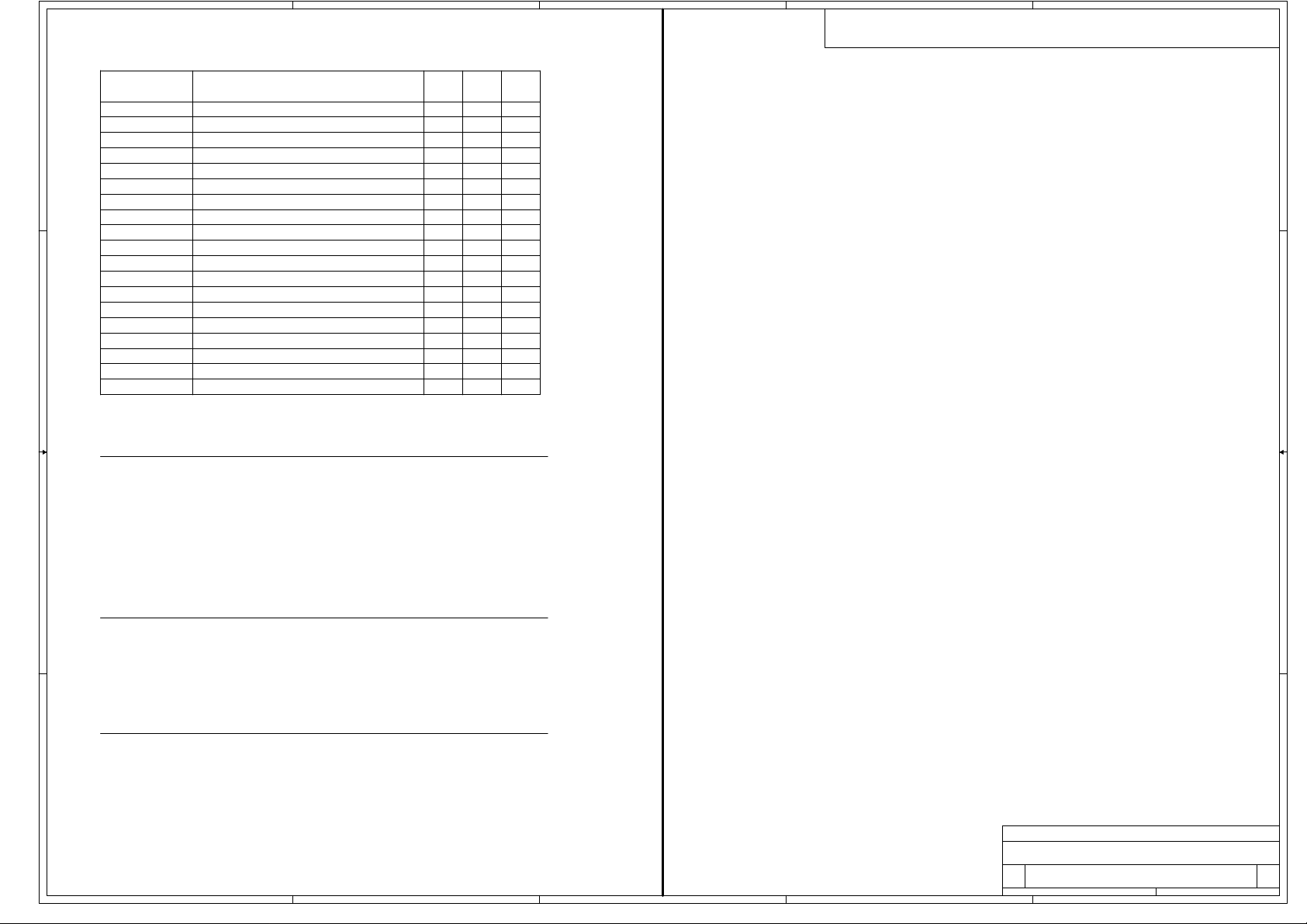

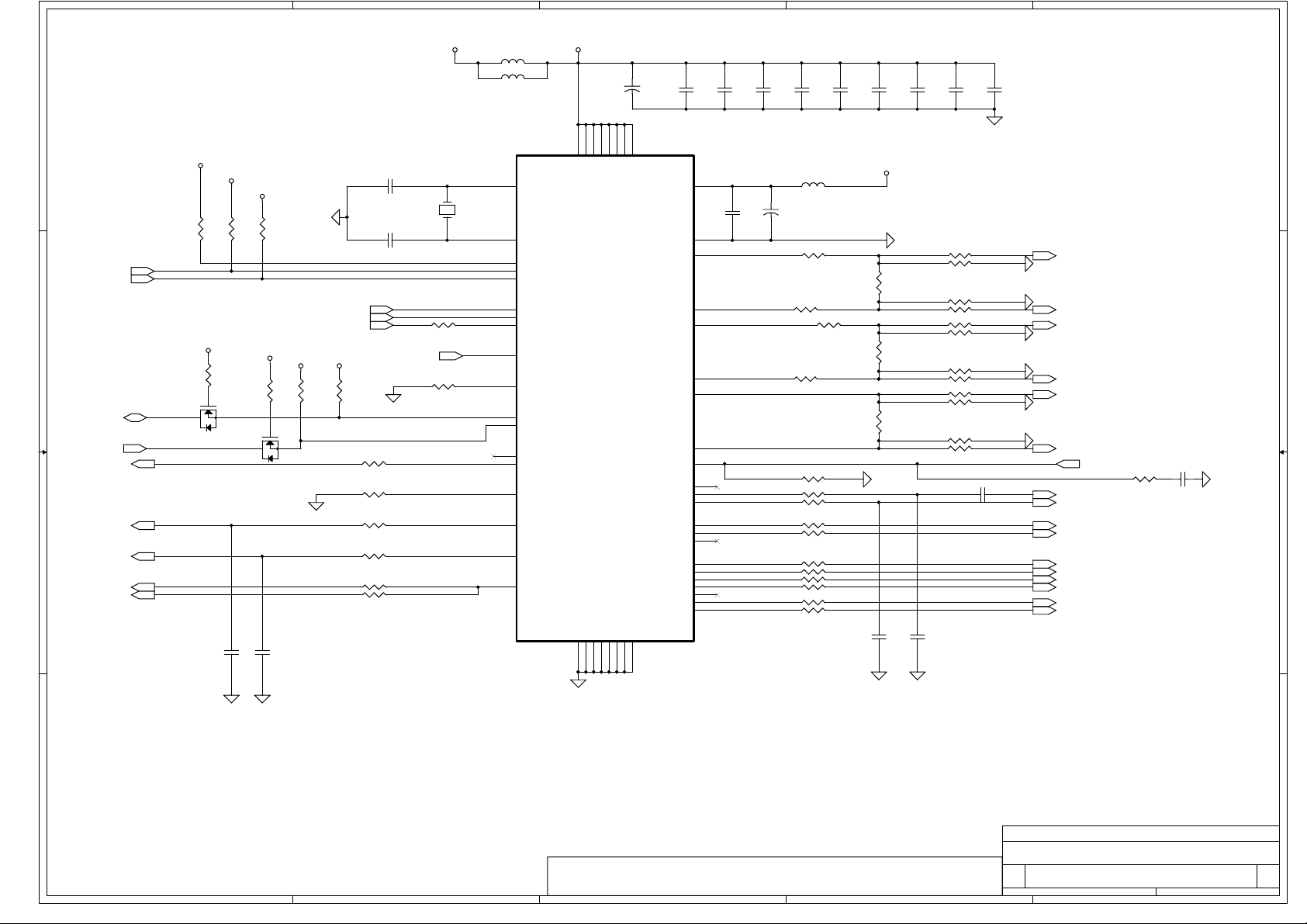

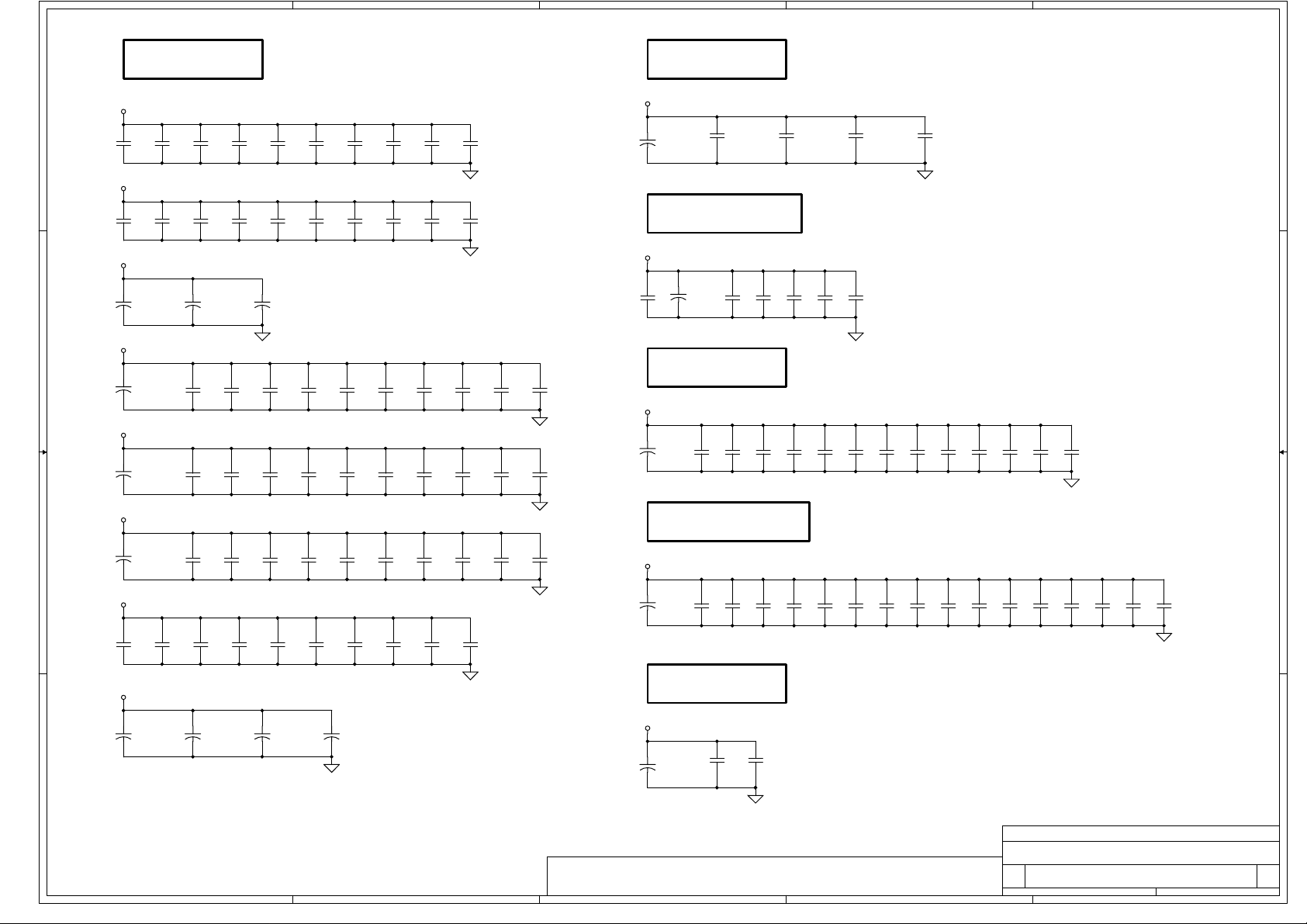

A

Voltage Rails

B

C

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

D

E

Power Plane Descripti on

1 1

B+

+VCC_H_CORE

+VTT

VIN

Adapter power supply (19V)

AC or battery power rail for power circu it.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

S1 S3 S5

N/A N/A N/A

N/AN/AN/A

ON OFF

ON OFF

OFF

OFF

+1.5V_ALW 1.5V always on power rail ON ON ON*

+1.5V_SW AGP 4 X ON OFF OFF

+1.8V_ALW 1.8V always on power rail ON ON ON*

+1.8V_SW OFF1.8V switched power rail ON OFF

ON+2.5V 2.5V power rail OFF

ON

+2-5V_MRIMM 2.5V switched power rail ON OFF OFF

+3V_ALW

+3V

+3V_SW

+5V_ALW

+5V

2 2

+5V_SW

+12V_ALW

+12V_SW

RTCVCC

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail OFFON

12V always on power r ail

12V switched power rail

RTC power

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON*

OFF

OFF

ON*

OFF5V switched power rail

ON*

OFF

ON

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

Device IDSEL# REQ# / G NT # Interrupts

LAN

CardBus

Audio Controller

Mini-PCI

Mini-PCI(LAN)

3 3

IEEE-1394 Controller

(AD24 internal)

AD20

AD19

AD18

AD22 4 PIRQD

AD16 0 PIRQA

2

3

1

PIRQA/PIRQB

PIRQD

PIRQC

EC SM Bus1 address

Device

Smart Batte r y

EEPROM

0001 011X b

1010 000X b

EC SM Bus2 address

Device

MAX1617MEE

OZ163

Docking

DOT Board

1001 110X b

0011 0100 b

0011 011X b

XXXX XXXXb

ICH3 SM Bus address

Device

SODIMM

4 4

Clock Gen.

P.S:Default Resistor & Capacitor's package are 0402.

1010 000X b

1101 001X b

Default 8P4R package is 0402.

A

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

B

C

D

Date: Sheet

346Friday, September 21, 2001

E

1A

of

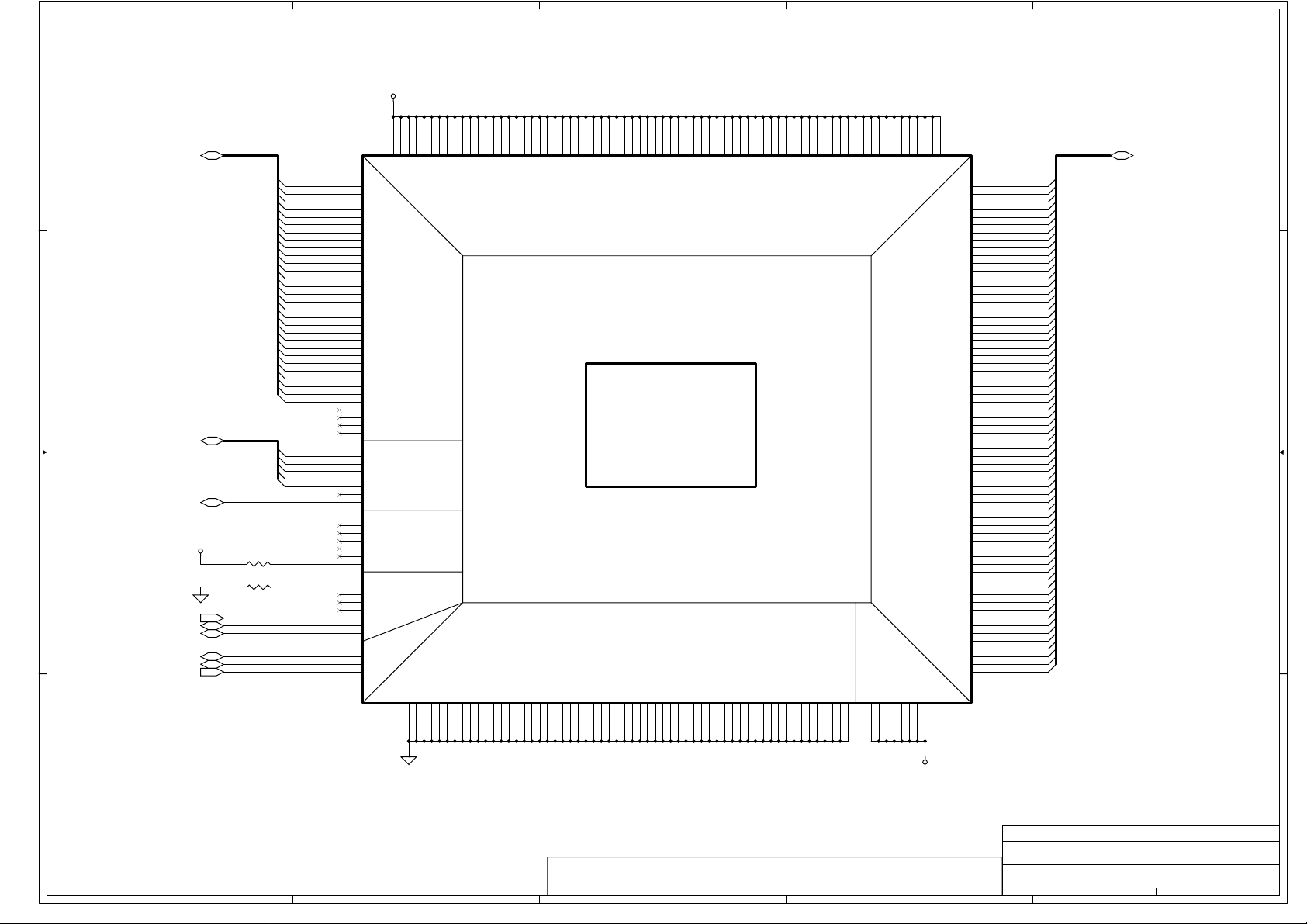

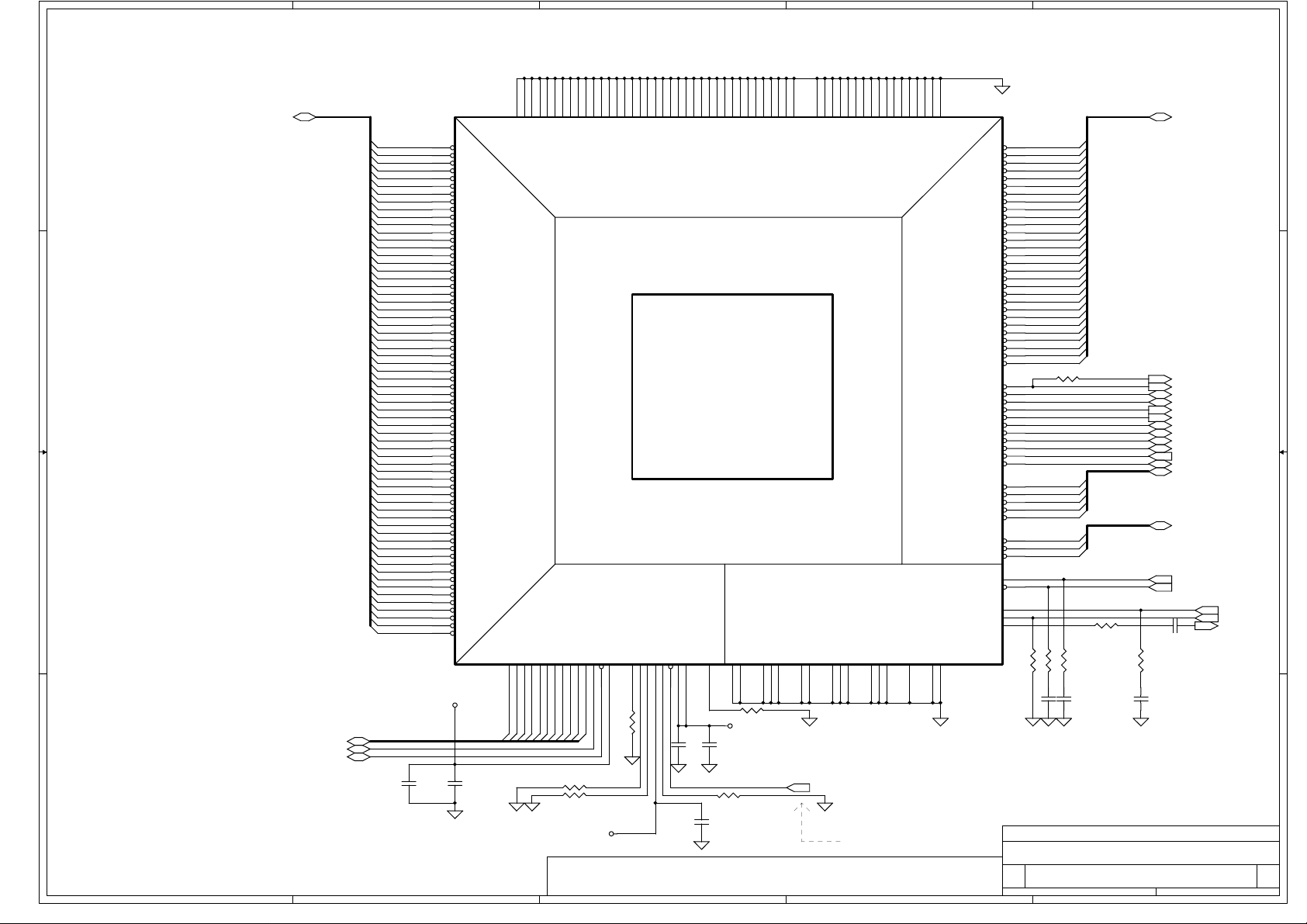

A

+VCC_H_CORE

1 1

AF23

AD23

B11

A10

A13

C12

C10

A15

A14

B13

A12

AA3

AB3

C14

AF4

C22

AA2

G2

H3

G1

H1

D3

G3

C2

C6

C8

C3

R1

U1

W2

C4

R2

U2

K1

J1

K3

J2

A3

J3

F3

B5

B9

B7

A8

B3

A9

A6

L3

T1

L1

T4

P3

A7

L2

V3

T3

U4A

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

RP#

ADS#

AERR#

AP#0

AP#1

BERR#

BINIT#

IERR#

BREQ0#

NC

NC

NC

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

TUALATIN

H_A#[3..31]9

2 2

H_REQ#[0..4]9

H_ADS#9

+1.5V_SW

3 3

H_BPRI#9

H_BNR#9

H_LOCK#9

H_HIT#9

H_HITM#9

H_DEFER#9

H_A#[3..31]

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#[0..4] H_D#33

R19 1.5K

1 2

R28 10

1 2

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

B

D22

F22

E21

H22

VCC_0

VCC_1

VCC_2

Address

Lines

Request

Signals

Error

Interface

Arbitration

Signals

Snoop

Signals

VSS_0

E16R4E25

C

G21

K22

J21

M22

L21

P22

N21

T22

R21

V22

U21

Y22

W21

AB22

AA21

AC21

D20

F20

E19

AB20

AA19

AC19

D18

F18

E17

AB18

AA17

AC17

D16

F16

E15

AB16

AA15

AC15

D14

F14

E13

AB14

AA13

AC13

D12

F12

E11

AB12

AA11

AC11

D10

F10E9AB10

AA9

AC9D8F8E7AB8

AA7

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_61

VCC

Mobile

Tualatin

VSS VCC

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

G25

J25

L25

N25

R25

U25

W25

AA25

AC25

AF25

AE26

C23

F23

H23

K23

M23

P23

T23

V23

Y23

AB23

AE23

B22

D21

F21

E22

H21

G22

K21

J22

M21

L22

P21

N22

T21

R22

V21

U22

Y21

W22

AB21

AA22

AC22

AE21

B20

D19

AB19

AA20

AC20

AE19

B18

D17

F17

E18

AB17

D

AC7D6F6E5H6G5K6J5N5T6V6

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

Data

Signals

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

U5Y6W5

AB6

AA5

AC5M6P6

E

H_D#[0..63]

H_D#0

A16

VCC_72

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

B17

A17

D23

B19

C20

C16

A20

A22

A19

A23

A24

C18

D24

B24

A18

E23

B21

B23

E26

C24

F24

D25

E24

B25

G24

H24

F26

L24

H25

C26

K24

G26

K25

J24

K26

F25

N26

J26

M24

U26

P25

L26

R24

R26

M25

V25

T24

M26

P24

AA26

T26

U24

Y25

W26

V26

AB25

T25

Y24

W24

Y26

AB24

AA24

V24

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_D#[0..63] 9

+VCC_H_CORE

4 4

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

A

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

446Friday, September 21, 2001

E

of

1A

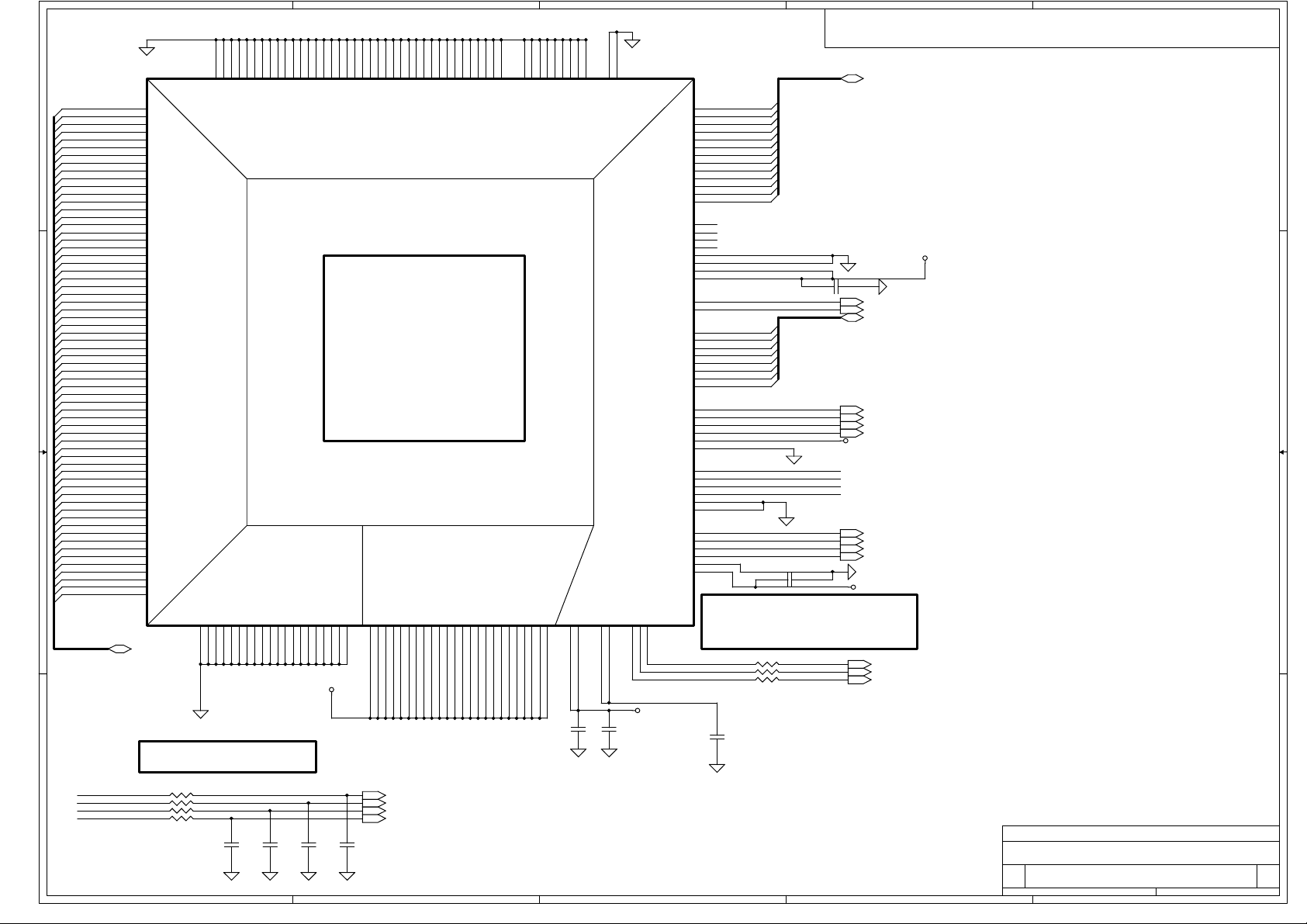

A

B

C

D

E

+VTT

+1.8V_SW

+1.5V_SW

+1.5V_SW

R21

3K

R42

150

12

12

R22

1.5K

12

12

R286

137_1%

H_RS#09

H_RS#19

H_RS#29

H_TRDY#9

H_A20M#17

H_IGNNE#17

H_SMI#17

H_STPCLK#17

H_DPSLP#17,43

H_INTR17

H_NMI17

H_INIT#17

H_DBSY#9

H_DRDY#9

H_BSEL08,11

H_BSEL18

C449

@10PF

ITP_TCK7

ITP_TDI7

ITP_TDO7

ITP_TMS7

ITP_TRST#7

ITP_PREQ#7

ITP_PRDY#7

PM_CPUPERF#17

H_A20M#

H_FLUSH#

H_IGNNE#

H_INTR

H_NMI

H_THERMDA

H_THERMDC

1 2

R35 110_1%

PIC_CLK

R285

1 2

@33

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_PREQ#

ITP_PRDY#

1 2

R38 56.2_1%

AC3

AF6

AF5

AD9

AD3

AB4

AE4

AF8

AD15

AE14

AE6

B15

AF13

AF14

AE12

AF10

AF16

AD19

AD17

AF20

AF22

AE20

AD22

AD21

AD10

AD7

AD11

AF7

AF15

AF19

AE22

AF12

AD5

AE16

12

1 1

2 2

3 3

Place H_RESET#

R272<0.1" from

U6

H_FERR#17

H_PWRGD17

H_RESET#9

CLK_CPU_APIC8

Note :

GHI# Pull-Up internally

But pull high too weak

56.2_1%

12

R267

R13

1.5K

+1.5V_SW

R40

150

R284 26.7_1%

+1.5V_SW

12

1 2

+VS_CMOSREF

AA18

AC18

AE17

B16

D15

F15

AB15

AA16

AC16

AE15

B14

D13

F13

E14

AB13

AA14

AC14

AE13

B12

D11

F11

E12

AB11

U4B

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

Y3

RS#0

V1

RS#1

U3

RS#2

M5

Request

RSP#

W1

Signals GND

TRDY#

A20M#

FERR#

FLUSH#

IGNNE#

SMI#

PWRGOOD

STPCLK#

Compatibilit y

DPSLP#

INTR/LINT0

NMI/LINT1

INIT#

RESET#

W3

DBSY#

Y1

DRDY#

THERMDA

THERMDC

SELFSB0

SELFSB1

EDGECTRLP

PICD0

L5

PICD1

PICCLK

RP2#

RP3#

BPM0#

BPM1#

TCK

TDI

TDO

TMS

TRST#

PREQ#

PRDY#

CMOSREF_1

CMOSREF_0

RTTIMPDEP

GHI#

APIC

Debug

Break

Point

Test

Access

PORT

( ITP )

AA12

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VCCT VID

AC12

AE11

B10D9F9

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

E10

AB9

AA10

AC10

AE9B8D7F7E8

AB7

AA8

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

Mobile

Tualatin

AC8

AE7B6F5H5G6K5J6N6L6T5R6V5U6Y5W6

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

AB5

AA6

AC6

AE5B4D4F4H4K4M3U4W4B2D2F2H2

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

Data

Signals

VTT Ref

Analog

VTTPWRGOOD

VSS_126

VSS_127

VSS_128

NCHCTRLP

VSS_129

DEP#0

DEP#1

DEP#2

DEP#3

DEP#4

DEP#5

DEP#6

DEP#7

VREF_1

VREF_2

VREF_3

VREF_4

VREF_5

VREF_6

VREF_7

VREF_8

TESTLO

VCC

PLL1

PLL2

CLK0

CLK0#

TESTLO

TESTHI

TESTHI

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

RP1

8P4R_1K

1 2

L10 4.7UH

C27

33UF_D2_16V

CLK_HCLK 8

CLK_HCLK# 8

TESTLO1

TESTLO2

TESTHI2

TESTHI1

R261

@33

1 2

C377

@10PF

+VTT

+VTT

AE24

AD25

AE25

AC24

AF24

AD26

AC26

AD24

AF21

AB26

H26

A21

AF9

A4

N1

AA1

Y4

R5

N3

N2

P1

NC

P5

NC

E1

NC

F1

NC

AC1

AD1

M1

AF18

NC

AD16

AF11

AE8

NC

N24

NC

AE10

NC

E2

P4

NC

AD4

A5

D1

AD13

B1

P26

A11

E3

D26

NC

+VTT

+V_AGTLREF

TESTLO1

VCPU_PLL1

VCPU_PLL2

CLK_HCLK

CLK_HCLK#

TESTLO2

NCHCTRLP

TESTHI1

TESTHI2

VTT_PWRGD

1 8

2 7

3 6

4 5

+VCC_H_CORE

+

R41 14_1%

1 2

CLK_HCLK CLK_HCLK#

R262

@33

1 2

C378

@10PF

VCCT_1

VCCT_2

VCCT_3

VCCT_4

VCCT_5

VCCT_6

VCCT_7

VCCT_8

VCCT_9

VCCT_10

VCCT_11

VCCT_12

VCCT_13

VCCT_14

VCCT_15

VCCT_16

VCCT_17

VCCT_18

VCCT_19

VCCT_20

VCCT_21

VCCT_22

VCCT_23

VCCT_24

VCCT_25

VCCT_26

VCCT_27

VCCT_28

VCCT_29

VCCT_30

VCCT_31

VCCT_32

VCCT_33

VCCT_34

VCCT_35

VCCT_36

VCCT_37

VCCT_38

VID0

VID1

VID2

VID3

VID4

VSS

VSS

+5V_ALW

W=40mil

R37

1 2

16

13

5

1

3

4

1K

1K

4 4

C58

2200PF

+5V_ALW

A

12

1 2

R36

1 2

H_THERMDA

H_THERMDC

R268

100K

NC

NC

NC

NC

NC

DXP

DXN

15

STBY#

ADD0

12

R274

200

C422

.1UF

1 2

2

Thermal Sensor

U6MAX1617

MAX1617/NE1617

VCC

14

SMBC

12

SMBD

11

ALERT#

ADD1

GND

GND

678910

+5V_ALW

Address:1001_110X

+VTT

A26

G23

J23

L23

N23

R23

U23

W23

AA23

C21

C19

AD20

C17

AD18

C15

C13

AD14

C11

AD12C9C7

AD8C5AD6

AC23

AA4E4G4J4L4

AC4V4AE3

AF2

AF1

AE18D5E6

AB1

AC2

AE2

AF3R3B26M4AF26C1AF17

EC_SMC_2 26,30,34,37

From 87591

R273

100K

1 2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

VSSNCNC

VSS_142

NC

E20

F19

N4

CPU_VR_VID4 7

CPU_VR_VID3 7

CPU_VR_VID2 7

CPU_VR_VID1 7

CPU_VR_VID0 7

VTT_PWRGD43EC_SMD_2 26,30,34,37

D

AE1

A25

C25

TUALATIN

AD2

2.2UF_16V_0805

K2M2P2T2V2Y2AB2

2

+3V_SW

12

R18

10K

1

Q8

3904

3

E

+VTT

12

R17

2K

VTT_PWRGD

C758

Title

Size Document Number Rev

Custom

Date: Sheet

R16

1 2

18K

12

Compal Electronics, inc.

SCHEMATIC, M/B LA-1011

401174

VTT_PWRGD# 8,30

546Friday, September 21, 2001

of

1A

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

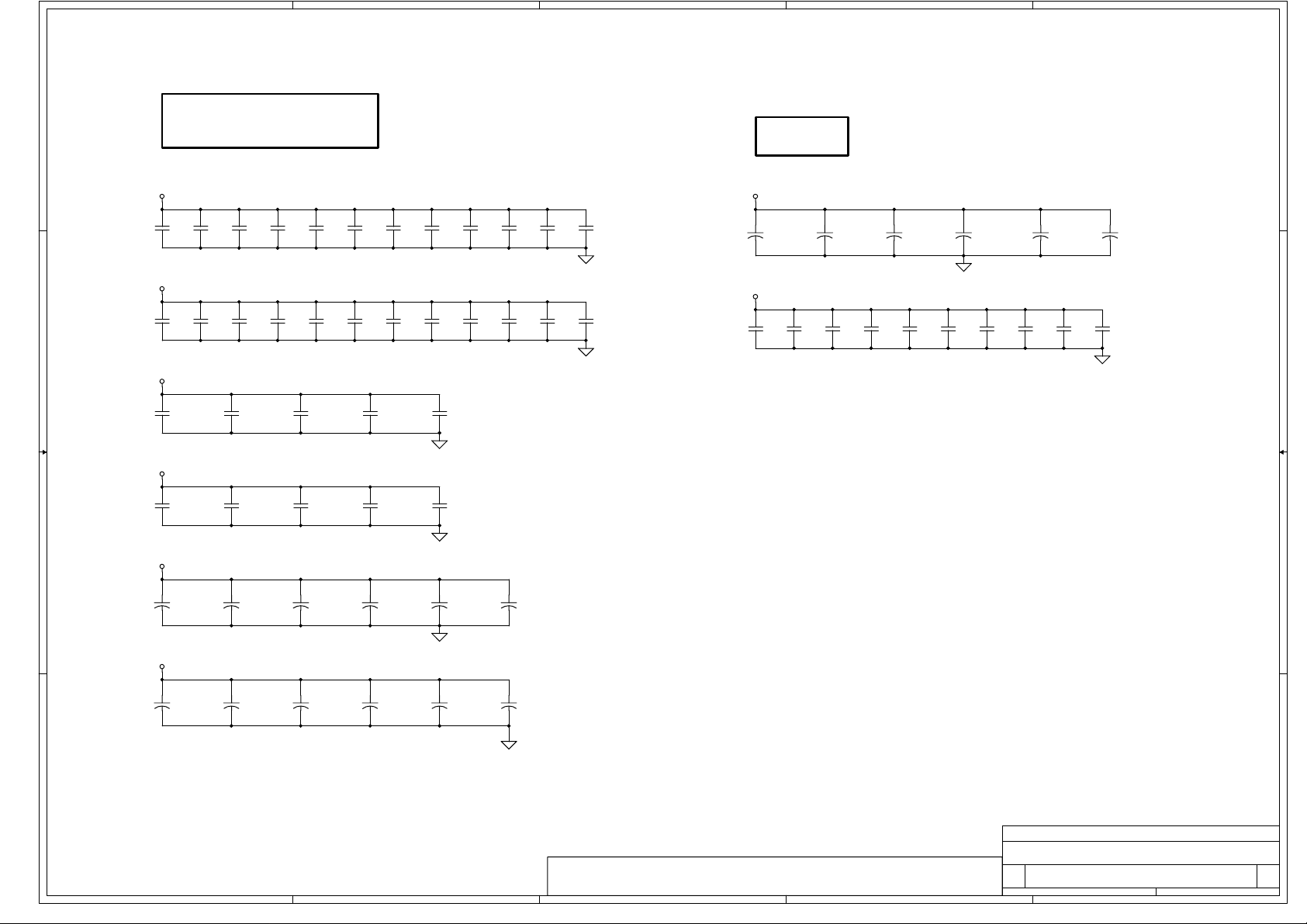

A

B

C

D

E

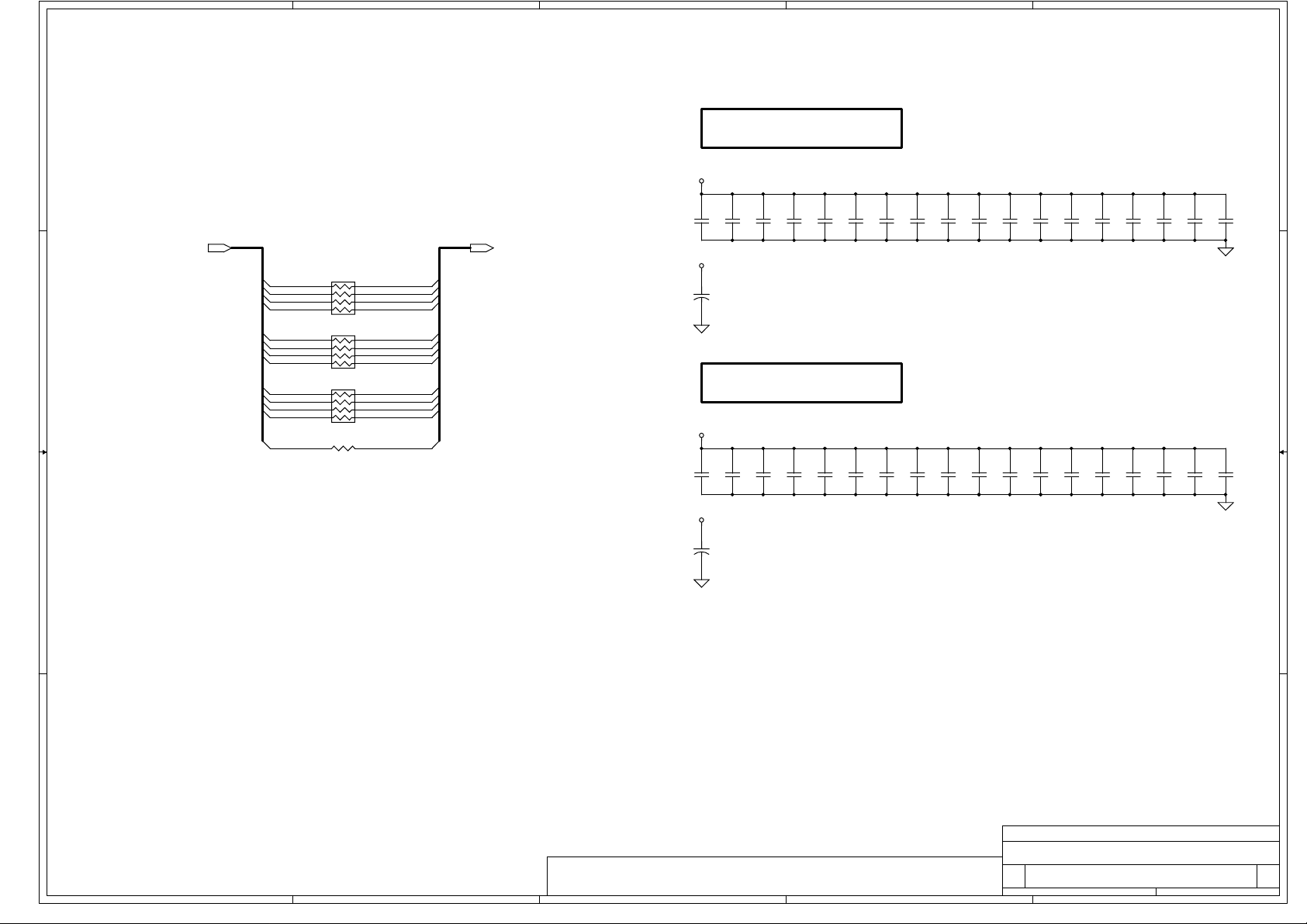

Layout note :

1 1

Place close to CPU, Use 2~3 vias per PAD.

Place .47uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

Layout note :

Place close to CPU,

Use 2 vias per PAD.

+VCC_H_CORE

12

12

12

C398

C399

.22UF_0603

.22UF_0603

+VCC_H_CORE

12

12

C397

C412

2 2

.22UF_0603

+VCC_H_CORE

12

C98

10UF_10V_1206

.22UF_0603

12

C396

.22UF_0603

12

C427

.22UF_0603

12

C62

10UF_10V_1206

12

C411

.22UF_0603

12

C435

.22UF_0603

12

12

C437

.22UF_0603

12

C403

.22UF_0603

C407

10UF_10V_1206

12

C401

.22UF_0603

12

C433

.22UF_0603

12

C17

10UF_10V_1206

C404

.22UF_0603

12

C402

.22UF_0603

12

C413

.22UF_0603

12

C410

.22UF_0603

12

C406

10UF_10V_1206

12

C440

.22UF_0603

12

C425

.22UF_0603

12

C434

.22UF_0603

12

C432

.22UF_0603

12

C426

.22UF_0603

12

C438

.22UF_0603

12

C428

.22UF_0603

12

C439

.22UF_0603

+VTT

12

C42

+

150UF_D2_6.3V

+VTT

12

C91

1UF_0603

12

C436

1UF_0603

12

C75

+

150UF_D2_6.3V

12

C56

1UF_0603

12

C105

+

150UF_D2_6.3V

12

12

C29

1UF_0603

Tualatin

C43

1UF_0603

+

12

C41

1UF_0603

12

C47

150UF_D2_6.3V

12

C63

1UF_0603

+

12

C55

1UF_0603

12

C51

150UF_D2_6.3V

12

C101

1UF_0603

12

C392

+

150UF_D2_6.3V

12

C102

1UF_0603

-------------------------------------------------------

+VCC_H_CORE

12

C429

10UF_10V_1206

3 3

+VCC_H_CORE

12

C59

+

150UF_D2_6.3V

+VCC_H_CORE

12

C24

+

150UF_D2_6.3V

12

C99

10UF_10V_1206

12

C104

+

150UF_D2_6.3V

12

C424

+

150UF_D2_6.3V

12

C390

10UF_10V_1206

12

C391

+

150UF_D2_6.3V

12

C469

+

150UF_D2_6.3V

12

C25

10UF_10V_1206

12

C387

+

150UF_D2_6.3V

12

C444

+

150UF_D2_6.3V

12

C46

10UF_10V_1206

12

C28

+

150UF_D2_6.3V

12

C471

+

150UF_D2_6.3V

12

C76

+

150UF_D2_6.3V

12

C52

+

150UF_D2_6.3V

D4 D3 D2 D1 D0 CPU_Core(V) QS( MP)

-------------------------------------------------------

1

111

0 1.15V0

000

1.40V

0

-------------------------------------------------------

Coppermine-T

D4 D3 D2 D1 D0 CPU_Core(V) ES(before MP)

-------------------------------------------------------

-------------------------------------------------------

-------------------------------------------------------

0

0

0

1

0

1

0

0

0

1.70V

0 1.35V

D4 D3 D2 D1 D0 CPU_Core(V) QS( MP)

0 1.70V

0

0

0

1

0

0

0

1

1.35V

0

-------------------------------------------------------

4 4

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

A

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

646Friday, September 21, 2001

E

of

1A

A

B

C

D

E

+VTT

GTL Reference Voltage

12

R62

Layout note :

1K_1%

1. Place R70 and R75 between and GMCH and CPU.

2. Place decoupling caps near CPU.(Within 500mils)

1 2

1 2

E

+V_AGTLREF

12

C443

.1UF

+VS_CMOSREF

12

R134

82.5_1%

12

R119

82.5_1%

746Friday, September 21, 2001

of

12

12

R64

C389

2K_1%

.1UF

+1.5V_SW

CMOS Reference Vo l t a g e

12

R68

Layout note :

499_1%

1. Place R81 and R76 between and GMCH and CPU.

2. Place decoupling caps near CPU.

12

R65

1K_1%

12

C430

.1UF

Place Reference Ci r cu it n ea r GM CH

+VAGP_CRDREF

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

12

C388

.1UF

+1.5V_SW

12

C400

.1UF

12

C423

.1UF

C229 470PF

12

R127

1K_1%

12

R113

1K_1%

C216 470PF

1A

12

R333

1K

R328

240

JP15

2

RESET#

4

DBRESET#

6

TCK

8

TMS

10

POWERON

12

DBINST#

14

GND

16

GND

18

GND

20

GND

22

GND

24

GND

26

GND

28

GND

30

BCLK

@ITP_RECEPTACLE

+3V_SW

182736

45

RP16

8P4R_1K

U34

4 5

B0 D0

8 9

B1 D1

14 15

B2 D2

18 19

B3 D3

22 23

B4 D4

1

BE#

SN74CBT3383

U33

4 5

B0 D0

8 9

B1 D1

14 15

B2 D2

18 19

B3 D3

22 23

B4 D4

1

BE#

@SN74CBT3383

R266

200

1

GND

3

GND

5

GND

7

TDI

9

TDO

11

TRST#

13

BSEN#

15

PREQ0#

17

PRDY0#

19

PREQ1#

21

PRDY1#

23

NC

25

NC

27

NC

29

BCLK#

B

VCC

GNDBX

VCC

GNDBX

12

23

C0A0

67

C1A1

1011

C2A2

1617

C3A3

2021

C4A4

24

1213

CPU_VID0

23

C0A0

CPU_VID1

67

C1A1

CPU_VID2

1011

C2A2

CPU_VID3

1617

C3A3

CPU_VID4

2021

C4A4

24

1213

12

R269

150

1 2

R43 240

12

R332

@10

12

C512

@15PF

RP37

MUX_VID0

MUX_VID1

MUX_VID2

MUX_VID3

MUX_VID4

12

8P4R_0

4 5

3 6

2 7

1 8

+5V_SW

12

+5V_SW

12

R275

200

1 2

1 2

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

R553 0

C515

.01UF

CPU_VID0 43

CPU_VID1 43

CPU_VID2 43

CPU_VID3 43

CPU_VID4 43

C516

@.01UF

+VTT+1.5V_SW+VTT

12

R44

56.2_1%

ITP_TDI 5

ITP_TDO 5

ITP_TRST# 5

ITP_PREQ# 5

R34 510

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

ITP_PRDY# 5

C

CPU Voltege ID

1 1

CPU_VR_VID05

CPU_VR_VID15

CPU_VR_VID25

CPU_VR_VID35

CPU_VR_VID45

AC_VID018

AC_VID118

AC_VID218

AC_VID318

PM_SSMUXSEL17,43

12

R100

12

12

R311 240

12

R270

39

AC_VID418

1 : for high Voltage B-C

+3V_SW

182736

45

RP2

@8P4R_10K

12

12

12

12

+1.5V_SW

+VTT

12

12

R79

R84

39

10K

12

12

R317

@10

12

C496

@15PF

MUX_VID0

MUX_VID1

MUX_VID2

MUX_VID3

MUX_VID4

STRAP_VID0

STRAP_VID1

STRAP_VID2

STRAP_VID3

STRAP_VID4

PM_DPRSLPVR17,43

+VTT

12

R86

1.5K

+3V_ALW

12

PM_SSGMUXSEL = 0 : for low Voltage A-C

2 2

@10K

Default f o r R e s is t o r s S h o u l d

be +VCC_CPU = 0.7V, for

Deeper Sleep Only.

R101

R103

R102

R107

@0

@0

In-Target Probe

3 3

H_RESETX#9

ITP_TCK5

ITP_TMS5

CLK_ITPP8 CLK_ITPP# 8

4 4

R108

@0

@0

@0

R313

56.2_1%

A

R133

249_1%

R126

49.9_1%

+1.8V_SW

R152

301_1%

+1.8V_SW

R435

301_1%

R438

301_1%

+1.8V_SW

R296

576_1%

R287

2K_1%

+3V

System Memory Reference

12

249.9_1%

Place capacitor close to GMCH.

12

+V_SMREF

12

C223

.1UF

HUB Interface Reference

12

Layout note :

1. Place R123 and R124 in middle of Bus.

2. Place capacitors near GMCH.

12

R159

301_1%

+VS_HUBREF

12

C256

.1UF

HUB Interface VSwing Voltage

12

1. Place R360 and R361 in middle of

Bus.

12

12

1. Place R255 and R253 near GMCH.

12

12

C643

.1UF

+VS_HUBVSWING

+VS_RIMMREF

D

A

B

C

D

E

+3V_SW

1 1

+3V_SW

+3V_SW

+3V_SW

12

12

12

R365

100K

H_BSEL15

H_BSEL05,11

2 2

SMB_DATA14,17,19

SMB_CLK14,17,19

CLK_VCH15

CLK_ICH4817

3 3

CLK_DREF9

CLK_ICH1417

CLK_SIO1432

+12V_SW

Q31

1 3

D

12

2

R231

100K

G

2N7002

R380

R386

1K

1K

SEL1

SEL0

+12V_SW

+3V_SW +3V_SW

12

R229

100K

S

2

G

Q29

1 3

D

S

2N7002

12

12

C589

C588

@10PF

@10PF

Place Crystal within 500 mils of CK_Titan

12

C629 10PF

caps are internal

to CK_TITAN

12

C647 10PF

PM_SLP_S1#17,30

PM_STPPCI#17

PM_STPCPU#17

12

12

R230

R232

10K

10K

R391 22_1%

R388 220_1%

R389 33

R390 22

R400 33

R399 33

1 2

1 2

1 2

1 2

1 2

1 2

R403 0

VTT_PWRGD#5,30

R364 10K

1 2

1 2

VCH_66M

USB_48M ICH_33M

DOT_48M

REF_14M

12

Y3

14.318MHZ

L46

BLM21A601SPT

1 2

1 2

L52 BLM21A601SPT

U41

2

40

55

54

25

34

53

28

43

29

30

33

35

42

39

38

56

ICS9250-38

+3V_CLK

XTAL_IN

SEL2

SEL1

SEL0

PWR_DWN#

PCI_STOP#

CPU_STOP#

VTT_PWRGD#

MULT0

SDATA

SCLK

3V66_0/DRCG

3V66_1/VCH_CLK

IREF

48MHZ_USB

48MHZ_DOT

REF

Width=40 mils

181419323746

VDD_PCI

VDD_PCI

VDD_REF

VDD_3V66

VDD_3V66

66MHZ_OUT2/3V66_4

66MHZ_OUT1/3V66_3

66MHZ_OUT0/3V66_2

GND_REF

GND_PCI

GND_PCI

GND_3V66

GND_3V66

491520313641

12

+

C626

22UF_1206_10V

50

VDD_CORE

VDD_CPU

VDD_CPU

VDD_48MHZ

GND_COREXTAL_OUT

CPUCLKT2

CPU_CLKC2

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

66MHZ_IN/3V66_5

PCICLK_F2

PCICLK_F1

PCICLK_F0

GND_48MHZ

GND_IREF

GND_CPU

47

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

12

12

C288

C289

.01UF

.01UF

26

12

C664

.01UF

273

HOST_CPU CLK_BCLK

45

HOST_CPU#

44

GMCH_CPU CLK_HT

49

GMCH_CPU#

48

52

51

24

23

GBIN_66M

22

ICH_66M

21

7

APIC_33M PCIF1

6

5

CB_33M

18

AUD_33M

17

SIO_33M

16

1394_33M

13

12

EC_33M

11

MINI_33M

10

12

12

C286

C287

.01UF

.01UF

L50

BLM21A601SPT

1 2

12

+

C335

22UF_1206_10V

R396

1 2

0

R397

1 2

0

R394

1 2

0

R393

1 2

0

R375 240K

1 2

R434 33

1 2

R433 33

1 2

R425 33

1 2

R424 33

1 2

R432 33

1 2

R431 33

1 2

R430 33

1 2

R429 33

1 2

R427 33

1 2

R426 33

1 2

12

C313

.01UF

12

C314

.01UF

+3V_SW

12

R8

475_1%

CLK_BCLK#

12

R281

475_1%

CLK_HT#

CLK_ITP

12

R325

475_1%

CLK_ITP#

GBIN_ISO

12

C654

@10PF

12

12

C315

C316

.01UF

.01UF

1 2

R9 33

1 2

R5 60.4_1%

R6 60.4_1%

1 2

R10 33

1 2

1 2

R278 33

1 2

R282 60.4_1%

R280 60.4_1%

1 2

R277 33

1 2

1 2

R318 33

1 2

R320 60.4_1%

R330 60.4_1%

1 2

R324 @33

1 2

C655 .01UF

12

C652

@10PF

Place caps. near

CK_Titan (U31)

12

C615

.01UF

CLK_HCLK 5

Place all these Block's

Components near CPU (U6)

CLK_HCLK# 5

CLK_GHT 9

Place all these Block's

Components near GMCH (U23)

CLK_GHT# 9

CLK_ITPP 7

Place all these Block's

Components near ITP (JP1)

CLK_ITPP# 7

CLK_GBOUT 9

CLK_GBIN 9

CLK_ICHHUB 17

CLK_ICHPCI 17

CLK_CPU_APIC 5

CLK_PCI_CB 23

CLK_PCI_AUD 27

CLK_LPC_SIO 32

CLK_1394 22

CLK_LPC_EC 30

CLK_MINIPCI 38

@33

R437

12

@10PF

C653

4 4

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

A

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

846Friday, September 21, 2001

E

of

1A

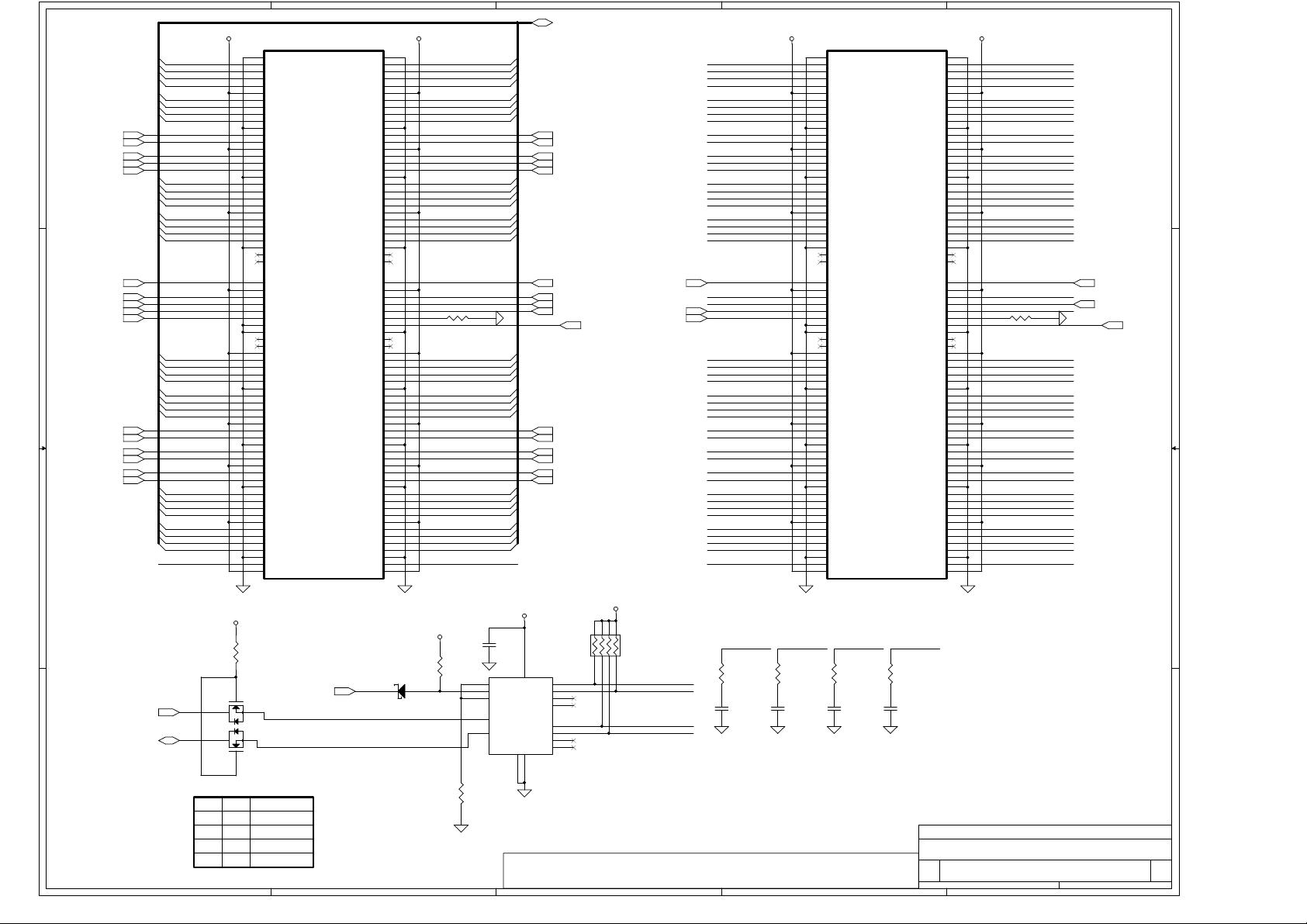

A

1 1

2 2

3 3

4 4

A

H_D#[0..63]

HUB_PD[0..10]17

HUB_PSTRB17

HUB_PSTRB#17

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

B

12

B

U4

P1

W6

U2

U6

R1

N3

W5

V4

P3

R3

U1

V6

W4

T3

P2

V3

R2

T1

W3

U3

Y4

AA3

W1

V1

Y1

Y6

AD3

AB4

AB5

V2

Y3

Y2

AA4

AA1

AA6

AB1

AC4

AA2

AB3

AD2

AD1

AC2

AB6

AC6

AC1

AF3

AD4

AD6

AC3

AH3

AE5

AE3

AG2

AF4

AF2

AJ3

AE4

AG1

AE1

AG4

AH4

AG3

AF1

+VS_HUBREF

C638

.1UF

U30A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

82830

12

C207

.01UF

M12

M13

M17

M18

N12

VSS0

VSS1

VSS2

VSS3

VSS4

Host

Interface

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

G26

H28

H29

H27

F29

F27

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

R348 28_1%

1 2

R109 54.9_1%

1 2

+VAGP_CRDREF

N13

E29

N14

VSS5

HUB_PD6

E28

HUB_PD7

N15

VSS6

HUB_PD7

G25

HUB_PD8

N16

VSS7

HUB_PD8

G27

HUB_PD9

N17

VSS8

HUB_PD9

H26

HUB_PD10

N18

VSS9

HUB_PD10

G29

P13

VSS10

VSS11

HUB_PSTRB

HUB_PSTRB#

F28

54.9_1%

P14

H24

R81

C

P15

P16

P17

R13

R14

R15

R16

R17

T13

T14

T15

T16

T17

U12

U13

U14

U15

U16

U17

U18

V12

V13

V17

V18

AJ5D2AC5Y5U5P5L5H5AH2

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS_H0

VSS_H1

VSS_H2

VSS_H3

VSS_H4

VSS_H5

VSS

Almador-M

GMCH

HUB_REF

DVO_RCOMP

SM_RCOMP

HUB_RCOMP

AGP_REF

AGP_RCOMP/DVOBC_RCOMP

RESET#

H_GTLREF1

H_GTLREF0

H_GTLRCOMP

VSS

VSS

VSSPCMOS_LM0

VSSPCMOS_LM1

VSSPCMOS_LM2

VSSP_HUB0

VSSP_HUB1

VSSP_IO0

VSSP_IO1

VSSP_IO2

AC22F6J23

J25

K24

AB24

AA7J7C2

12

12

AB23

1 2

R361 80.6_1%

+V_AGTLREF

12

C532

C527

.1UF

.1UF

R112 54.9_1%_0603

12

C198

.1UF

AC23

AH19

AH20

AF5

G28

H25

AC26

AD22

AE28

12

PCI_RST# 15,17,21,22,23,26,27,30,32,38

VSS_H6

VSS_H7

VSS_H8

VSSP_DVO0

VSSP_DVO1

AH24

AF25

D

AE2

AB2W2T2N2K2G2AC7

VSS_H9

VSS_H10

VSS_H11

VSS_H12

VSS_H13

Host

Interface

VSSP_DVO2

VSSA_DAC

AF27

AH26G8AD7

VSS_H14

VSS_H15

VSS_H16

VSSA_CPLL

VSSA_HPLL

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_CPURST#

H_ADS#

H_BNR#

H_BPRI#

H_DBSY#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

CLK_HT

CLK_HT#

CLK_DREF

CLK_GBIN

CLK_GBOUT

10 mils wide,length <=500 mils.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

E

H_A#[3..31]

H_A#3

H2

H_A#4

E3

H_A#5

G3

H_A#6

N4

H_A#7

M6

H_A#8

F1

H_A#9

F2

H_A#10

J3

H_A#11

F3

H_A#12

P6

H_A#13

G1

H_A#14

N5

H_A#15

H1

H_A#16

P4

H_A#17

T4

H_A#18

M2

H_A#19

J2

H_A#20

L2

H_A#21

R4

H_A#22

K1

H_A#23

L3

H_A#24

L1

H_A#25

J1

H_A#26

N1

H_A#27

T5

H_A#28

H3

H_A#29

M3

H_A#30

M1

H_A#31

K3

1 2

R96 @0

R6

C1

E1

L4

G5

J4

F4

D3

D1

J6

G4

H_REQ#0

K6

H_REQ#1

M4

H_REQ#2

K5

H_REQ#3

K4

H_REQ#4

L6

H_RS#0

H6

H_RS#1

H4

H_RS#2

G6

AJ4

AH5

AC19

AG26

GBOUT_GMCH GBOUT_ISO

AD24

R288

240K

1 2

@10PF

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

@33

1 2

R297

C455

1 2

R298

@33

C456

@10PF

H_REQ#[0..4]

H_RS#[0..2]

1 2

R60 47

1 2

R82

@33

C124

@10PF

H_A#[3..31] 4H_D#[0..63]4

H_RESETX# 7

H_RESET# 5

H_ADS# 4

H_BNR# 4

H_BPRI# 4

H_DBSY# 5

H_DEFER# 4

H_DRDY# 5

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 5

H_REQ#[0..4] 4

H_RS#[0..2] 5

CLK_GHT 8

CLK_GHT# 8

C79 .01UF

E

946Friday, September 21, 2001

CLK_DREF 8

CLK_GBIN 8

CLK_GBOUT 8

of

1A

U30B

A

AD8

AD9

AD10

AJ21

AE8

AE9

AE10

AE11

AE12

AE13

AE17

AE19

AH21

AF8

AF9

AF10

AF11

AF12

AF13

AF14

B

AF15

AF16

AF17

AF18

AF19

AF20

AG7

AG15

AG16

AG21

AH6

AH8

AH9

AH11

AH12

AH14

AH17

AH18

K28

N28

T28

W28

AB28

L25

P25

U25

Y25

AE20

C

G24

SM_D_MA[0..12]

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

D

SM_D_MA[0..12] 13

E

SM_DQ0

SM_DQ1

SM_DQ2

1 1

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

2 2

SM_DQ31

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

3 3

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

SM_DQ[0..63]

4 4

SM_D_CLK0

SM_D_CLK1

SM_D_CLK2

SM_D_CLK3

D29

SM_DQ0

C29

SM_DQ1

D27

SM_DQ2

C27

SM_DQ3

A27

SM_DQ4

B26

SM_DQ5

E24

SM_DQ6

C25

SM_DQ7

E23

SM_DQ8

B25

SM_DQ9

C23

SM_DQ10

F22

SM_DQ11

B23

SM_DQ12

C22

SM_DQ13

E21

SM_DQ14

B22

SM_DQ15

C12

SM_DQ16

D10

SM_DQ17

C11

SM_DQ18

A10

SM_DQ19

C10

SM_DQ20

C8

SM_DQ21

A7

SM_DQ22

E9

SM_DQ23

C7

SM_DQ24

E8

SM_DQ25

A5

SM_DQ26

F8

SM_DQ27

C5

SM_DQ28

D6

SM_DQ29

B4

SM_DQ30

C4

SM_DQ31

E27

SM_DQ32

C28

SM_DQ33

B28

SM_DQ34

E26

SM_DQ35

C26

SM_DQ36

D25

SM_DQ37

A26

SM_DQ38

D24

SM_DQ39

F23

SM_DQ40

A25

SM_DQ41

G22

SM_DQ42

D22

SM_DQ43

A23

SM_DQ44

F21

SM_DQ45

D21

SM_DQ46

A22

SM_DQ47

F11

SM_DQ48

A11

SM_DQ49

B11

SM_DQ50

F10

SM_DQ51

B10

SM_DQ52

B8

SM_DQ53

D9

SM_DQ54

B7

SM_DQ55

F9

SM_DQ56

A6

SM_DQ57

C6

SM_DQ58

D7

SM_DQ59

B5

SM_DQ60

E6

SM_DQ61

A4

SM_DQ62

D4

SM_DQ63

82830

SM_DQ[0..63] 14

VSS_LM

SDRAM

System

Memory

VSSP_SM0

VSSP_SM1

VSSP_SM2

B3B6B9

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSSP_SM3

VSSP_SM4

VSSP_SM5

VSSP_SM6

VSSP_SM7

B12

B15

B18

B21

B24

Layout note :

Place resistors & capacitors near GMCH

R378 10

1 2

R156 10

1 2

R148 10

1 2

R157 10

1 2

12

C259

@33PF

A

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

Almador-M

GMCH

VSS Power

VSSP_SM8

VSSP_SM9

VSSP_SM10

VSSP_SM11

VSSP_SM12

VSSP_SM13

VSSP_SM14

VSSP_SM15

VSSP_SM16

VSSP_SM17

VSSP_SM18

VSSP_SM19

VCC

VCC

VCC

VCC

VCC

B27E7E10

E13

E16

E19

E22

12

C255

@33PF

E25G9G21E4D28

+VTT

12

C260

@33PF

H7

H23K7K23L7N6T6W7Y7AB7

12

C587

@33PF

SMD_CLK0 14

SMD_CLK1 14

SMD_CLK2 14

SMD_CLK3 14

VSS_LM

VCC

VSS_LM

VSS

VCC

B

VSS_LM

VCC

VSS_LM

VCC

VSS_LM

VCC

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSS_LM

VSSP_AGP0

VSSP_AGP1

VSSP_AGP2

VSSP_AGP3

VSSP_AGP4

VSSP_AGP5

VSSP_AGP6

VSSP_AGP7

VSSP_AGP8

VSSA_DPLL0

SDRAM

System

Memory

SM_OCLK

SM_RCLK

SM_VREF0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M24

P24

T24

V24

Y23

M14

M15

M16

P12

R12

T12

VCC

VCC

VCC

F24

P18

R18

T18

C181/C188 close to

Ball E5 and F24

SM_VREF1

E5

12

C230

.1UF

A24

C24

12

VSSA_DPLL1

C217

.1UF

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

VSS

VSS

VCC_SM

VCC_SM

SM_BA0

SM_BA1

SM_DQM0

SM_DQM1

SM_DQM2

SM_DQM3

SM_DQM4

SM_DQM5

SM_DQM6

SM_DQM7

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

VCCQ_SM

VSS

SM_CLK0

SM_CLK1

SM_CLK2

SM_CLK3

VSS

VSS

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

VSS

VCC_SM

SM_RAS#

SM_CAS#

SM_WE#

C20

D19

A21

GMCH_RAS#

GMCH_CAS#

GMCH_WE#

SM_OCLK

+V_SMREF

@22PF_NPO

Total trace length from ball

C24 to A24 and C470 do not

exceed 200mils.

C

SM_D_MA0

A20

SM_D_MA1

B20

SM_D_MA2

B19

SM_D_MA3

C19

SM_D_MA4

A18

SM_D_MA5

A19

SM_D_MA6

C17

SM_D_MA7

C18

SM_D_MA8

B17

SM_D_MA9

A17

SM_D_MA10

A16

SM_D_MA11

C15

SM_D_MA12

C14

F20

NC

E20

NC

F12

NC

E11

NC

C21

F19

E12

A12

B16

C16

F18

D18

D13

D12

E18

F17

F14

F13

E17

F16

D16

D15

E15

E14

A15

B2

B14

A3

A14

C3

A13

C9

C13

A9

B13

A8

SM_DQM0

SM_DQM1

SM_DQM2

SM_DQM3

SM_DQM4

SM_DQM5

SM_DQM6

SM_DQM7

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_D_CLK0

SM_D_CLK1

SM_D_CLK2

SM_D_CLK3

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

C248 .1UF

C253 .1UF

1 2

1 2

Layout note :

1.Placement TP6 for Almad or -M A 2 st epping die.

2.The 0.1uF capacitor and connection to +3V

must be implanted for Almador-M A3 stepping

die.

R150 10

1 2

R149 10

1 2

R151 10

1 2

12

C254

SM_BA0 14

SM_BA1 14

SM_DQM[0..7] 14

SM_CS#0 14

SM_CS#1 14

SM_CS#2 14

SM_CS#3 14

+3V

SM_CKE0 14

SM_CKE1 14

SM_CKE2 14

SM_CKE3 14

+3V

SM_RAS# 14

SM_CAS# 14

SM_WE# 14

+3V

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

D

Date: Sheet

10 46Friday, September 21, 2001

E

1A

of

A

Layout note :

Place close to AE16,

AE15 of GMCH

1 1

AGP_PAR : Strapping option

for SW detection of AGP or

DVO device.

0 -> DVO B/C device

1 -> AGP device

R307 22

DVOC_CLK15

DVOC_CLK#15

+1.5V_SW

2 2

3 3

DVOC_D[0..11]15

M_DDC2_CLK

M_DDC2_DATA

M_DDC1_CLK

M_DDC1_DATA

1 2

R310 22

1 2

1 2

R369 100K

1 2

R363 100K

R104 330

DVOC_FLD15

4 5

3 6

2 7

1 8

RP36 8P4R_100K

12

R90 100K

DVOC_VSYNC15

DVOC_HSYNC15

R105 100K

1 2

+1.5V_SW

DVOC_D5

DVCCLK

DVCCLK#

M_DDC1_DATA

M_I2CCLK

M_DDC1_CLK

M_DDC2_DATA

M_I2CDATA

AGP_PAR

12

M_DDC2_CLK

DVOC_D0

DVOC_D1

DVOC_D2

DVOC_D3

DVOC_D4

DVOC_D7

DVOC_D6

DVOC_D9

DVOC_D8

DVOC_D11

DVOC_D10

DPMS_CLK

12

C127

68PF

AA29

AGP_SBA0/ZV_D8

AA24

AGP_SBA1/ZV_D7

AA25

AGP_SBA2/ZV_D6

Y24

AGP_SBA3/ZV_D5

Y27

AGP_SBA4/ZV_D2

Y26

AGP_SBA5/ZV_D1

W24

AGP_SBA6/ZV_D0

Y28

AGP_SBA7/ZV_HREF

L27

AGP_CBE#0/DVOB_D7

P29

AGP_CBE#1/DVOB_BLANK#

R27

AGP_CBE#2/ZV_VSYNC

T25

AGP_CBE#3/DVOC_D5

L29

AGP_ADSTB0/DVOB_CLK

L28

AGP_ADSTB#0/DVOB_CLK#

U29

AGP_ADSTB1/DVOC_CLK

U28

AGP_ADSTB#1/DVOC_CLK#

AA27

AGP_SBSTB/ZV_D4

AA28

AGP_SBSTB#/ZV_D3

R29

AGP_FRAME#/M_DDC1_DATA

P26

AGP_IRDY#/M_I2C_CLK

P27

AGP_TRDY#/M_DDC1_CLK

N25

AGP_STOP#/M_DDC2_DATA

R28

AGP_DEVSEL#/M_I2C_DATA

AC27

AGP_REQ#/ZV_CLK

AD29

AGP_GNT#/ZV_D15

P28

AGP_PAR

J29

AGP_AD0/DVOB_HSYNC

J28

AGP_AD1/DVOB_VSYNC

K26

AGP_AD2/DVOB_D1

K25

AGP_AD3/DVOB_D0

L26

AGP_AD4/DVOB_D3

J27

AGP_AD5/DVOB_D2

K29

AGP_AD6/DVOB_D5

K27

AGP_AD7/DVOB_D4

M29

AGP_AD8/DVOB_D6

M28

AGP_AD9/DVOB_D9

L24

AGP_AD10/DVOB_D8

M27

AGP_AD11/DVOB_D11

N29

AGP_AD12/DVOB_D10

M25

AGP_AD13/DVOBC_CLKINT#

N26

AGP_AD14/DVOB_FLD/STL

N27

AGP_AD15/M_DDC2_CLK

R25

AGP_AD16/DVOC_VSYNC

R24

AGP_AD17/DVOC_HSYNC

T29

AGP_AD18/DVOC_BLANK#

T27

AGP_AD19/DVOC_D0

T26

AGP_AD20/DVOC_D1

U27

AGP_AD21/DVOC_D2

V27

AGP_AD22/DVOC_D3

V28

AGP_AD23/DVOC_D4

U26

AGP_AD24/DVOC_D7

V29

AGP_AD25/DVOC_D6

W29

AGP_AD26/DVOC_D9

V25

AGP_AD27/DVOC_D8

W26

AGP_AD28/DVOC_D11

W25

AGP_AD29/DVOC_D10

W27

AGP_AD30/DVOC_INT#/DPMS_CLK

Y29

AGP_AD31/DVOC_FLD/STL

82830

U30C

(DVOB/DVOC & ZV po rt )

B

+VTT

V14

AGP

Interface

AB26

C

1 2

AC9

AC8

VCCPCMOS_LM

VCCPCMOS_LM

VCCPCMOS_LM

R66 0_0805

12

C96

.01UF

+VTT

VCCA_DAC

AF26

AG27F5J5M5R5V5AA5

VCC_H

VCCA_DAC

VCCA_DAC

1 2

L16

R26

V26

VCCP_AGP

VCCP_AGP

VCCP_AGP

L0603

+3V

12

12

AA26

L23

AA23

U24

AE6G7G10

VCCP_AGP

VCCP_AGP

VCCP_AGP

VCCP_AGP

Interface

VCCA_PLL

VCCA_HPLL

VCCA_CPLL

Power

+1.8V_SW

G20

AF6

AE7

VCCQ_SM

VCCQ_SM

VCCPCMOS_LM

+VTT

+1.5V_SW

+1.8V_SW

+3V

V15

V16

AE16

AE15

AD15

AD16

AE25

AD23

J24

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VCCP_IO

VCCP_IO

VCCP_HUB

C103 .1UF

C205 .1UF

F26

N24

W23

J26

M26

VCCP_AGP

VCCP_HUB

VCCQ_AGP

VCCQ_AGP

Almador-M

GMCH

Local Memory

Interface

AGP_PIPE#/ZV_D10

AGP_WBF#/ZV_D9

AGP_RBF#/ZV_D11

AGP_ST0/ZV_D14

AGP_ST1/ZV_D13

AGP_ST2/ZV_D12

LM_CMD

LM_SCK

LM_SIO

LM_RQ0

LM_RQ1

LM_RQ2

LM_RQ3

LM_RQ4

LM_RQ5

LM_RQ6

LM_RQ7

LM_RCLK

LM_GCLK

LM_RAMREF0

LM_RAMREF1

LM_CTM

LM_CTM#

LM_CFM

LM_CFM#

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

AB29

AB25

AC28

AC29

AB27

AH7

AF7

AJ7

AG11

AJ12

AG12

AH13

AG13

AJ13

AG14

AJ14

AJ6

AG6

AD14

AE14

AH15

AJ15

AJ16

AH16

D5D8D11

D14

D17

D20

D23

D26F7F15

+1.8V_SW

L14 .1UH_0805

12

C95

.1UF

+VCCA_DPLL1

+VCCA_DPLL0

AD5

AG5

E2

AC20

F25

VCC_H

VCC_H

VCC_H

VCC_H

VCC_H

VCC_H

VCC_H

VCC_H

VCCA_DPLL0

(DVOA port)

Local Memory

Interface

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCCP_SM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

G11

G19

G23

AC10

AC11

AD11

AD12

AD13

12

12

L17 .1UH_0805

+1.5V_SW

AC21

AF21

AF24

DAC_VSYNC

DAC_HSYNC

VCCP_DVO

VCCP_DVO

VCCP_DVO

VCCA_DPLL1

DAC_RED#

DAC_GREEN#

DAC_BLUE#

DAC_RED

DAC_GREEN

DAC_BLUE

IO_DDC1CLK

IO_DDC1DATA

DAC_REFSET

DVO_CLKIN

DVO_BLANK#

DVO_VSYNC

DVO_HSYNC

IO_I2CCLK

IO_I2CDATA

DVO_CLK#

DVO_CLK

Display

Interface

DVO_D10

DVO_D11

IO_DDC2DATA

IO_DDC2CLK

DVO_INTR#

DVO_FIELD

LM_DQA0

LM_DQA1

LM_DQA2

LM_DQA3

LM_DQA4

LM_DQA5

LM_DQA6

LM_DQA7

LM_DQB0

LM_DQB1

LM_DQB2

LM_DQB3

LM_DQB4

LM_DQB5

LM_DQB6

LM_DQB7

AGP_BUSY#

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

AE18

AD17

AD18

AD19

+3V

12

DVO_D0

DVO_D1

DVO_D2

DVO_D3

DVO_D4

DVO_D5

DVO_D6

DVO_D7

DVO_D8

DVO_D9

C227

.1UF

D

+VTT

12

C210

+

100UF_D2_6.3V

DAC_VSYNC

AE29

DAC_HSYNC

AD28

DAC_RED#

AF28

DAC_GREEN#

AG28

DAC_BLUE#

AH27

AF29

AG29

AH28

AE27

AD27

R53 255_1%

AJ27

DVOA_CLKINT

AD20

AD21

AF23

AF22

DVOA_I2CCLK

AD25

DVOA_I2CDATA

AC25

DVCLK#

AG24

DVCLK

AJ24

DVOD0

AJ22

DVOD1

AH22

DVOD2

AG22

DVOD3

AJ23

DVOD4

AH23

DVOD5

AG23

DVOD6

AE23

DVOD7

AE24

DVOD8

AJ25

DVOD9

AH25

DVOD10

AG25

DVOD11

AJ26

AD26

AE26

DVO_INTR#

AE21

AE22

AG17

AJ17

AG18

AJ18

AG19

AJ19

AG20

AJ20

AJ11

AH10

AJ10

AG10

AJ9

AG9

AJ8

AG8

AC24

+1.8V_SW

12

R, L, C

place near

GMCH.

12

12

C92

C93

+

.1UF

100UF_D2_6.3V

1 2

DVOA_BLANK# 15

DVOA_VSYNC 15

DVOA_HSYNC 15

DVOA_I2CCLK 15

DVOA_I2CDATA 15

R50 22

1 2

R52 22

1 2

RP13 16P8R_22

1

2

3

4

5

6

7

8 9

4 5

3 6

2 7

1 8

RP14 8P4R_22

R46

@33

1 2

C77

@10PF

C108

68PF

16

15

14

13

12

11

10

+3V_SW

12

DVOA_D0

DVOA_D1

DVOA_D2

DVOA_D3

DVOA_D4

DVOA_D5

DVOA_D6

DVOA_D7

DVOA_D8

DVOA_D9

DVOA_D10

DVOA_D11

DVOA_STALL 15

R452

8.2K

+1.5V_SW

R289 @2.2K

R290 2.2K

R292 @2.2K

R293 10K

DAC_VSYNC 16,37

DAC_HSYNC 16,37

R72 37.4_1%

R63 37.4_1%

R61 37.4_1%

DAC_RED 16,37

DAC_GREEN 16,37

DAC_BLUE 16,37

IO_DDC1CLK 16

IO_DDC1DATA 16

TV_I2CDATA

TV_I2CCLK

C756

27PF

AGP_BUSY# 17

E

Strap Name Low High

DVOA_D0 Rese r ved 133MHz

DVOA_D1 IOQ D =2 I OQD=8

DVOA_D5 Desk t op Mobile

DVOA_D6 Dual Ended Term Single Ended Term

1 2

1 2

1 2

1 2

1 2

1 2

1 2

DVOA_CLK# 15

DVOA_CLK 15

DVOA_D[0..11] 15

12

DVOA_D6

DVOA_D5

DVOA_D1

DVOA_D0

Place R8, R234, R278

near VGA Connector.

DAC_VSYNC

DAC_HSYNC

TV_DDCDATA 15

TV_DDCCLK 15

12

C757

27PF

R59

1 2

680

DVOA_I2CDATA

DVOA_I2CCLK

DVOA_CLKINT

DVO_INTR#

TV_I2CDATA

TV_I2CCLK

12

C765

10PF

R91 10K

1 2

1 2

R89 10K

R56 100K

1 2

1 2

R57 100K

R554 4.7K

1 2

1 2

R555 4.7K

H_BSEL0 5,8

12

C764

10PF

+3V_SW

+1.5V_SW

+3V_SW

VCC

Y

+3V_SW

5

4

R568

732_1%_0603

604_1%_0603

1.5V level clock

12

R569

1 2

DPMS_CLK

R295 10K

1 2

R55 10K

1 2

C452

.1UF

+VS_RIMMREF

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

D

Date: Sheet

11 46Friday, September 21, 2001

E

1A

of

VS_RIMMREF

B

C

1 2

R294 100_1%_0603

12

C454

.1UF

12

U60

1

NC

4 4

RTCCLK17,23,24

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

2

A

3

GND

NC7S14

A

A

B

C

D

E

Layout note :

Distri bute as close as possible

to GMCH Processor Quadrant .

+VTT

1 1

+VTT

+VTT

2 2

3 3

+VTT

+VTT

+VTT

+VTT

12

C100

.1UF

12

C109

.1UF

12

C65

+

150UF_D2_6.3V

12

C211

+

150UF_D2_6.3V

12

C64

+

150UF_D2_6.3V

12

C50

+

150UF_D2_6.3V

12

C156

.1UF

12

12

12

C87

.1UF

C86

.1UF

C173

.1UF

12

C537

.1UF

12

C89

.1UF

12

C414

+

150UF_D2_6.3V

12

C128

.1UF

12

C192

.1UF

12

C138

.1UF

12

C184

.1UF

12

12

12

12

12

C115

.1UF

C194

.1UF

C153

.1UF

12

C547

.1UF

C111

.1UF

C195

.1UF

12

12

12

C212

+

150UF_D2_6.3V

12

C116

.1UF

12

C199

.1UF

12

C159

.1UF

12

C84

.1UF

C113

.1UF

C206

.1UF

12

12

C142

.1UF

12

C88

.1UF

12

C117

.1UF

12

C204

.1UF

12

C171

.1UF

12

C187

.1UF

12

12

C132

C106

.1UF

.1UF

12

12

C112

C85

.1UF

.1UF

12

12

C143

C147

.1UF

.1UF

12

12

C172

C94

.1UF

.1UF

12

12

C189

C190

.1UF

.1UF

12

12

C191

C130

.1UF

.1UF

12

C114

C136

.1UF

.1UF

12

12

C151

C148

.1UF

.1UF

12

12

12

C161

C154

.1UF

.1UF

12

12

C155

C162

.1UF

.1UF

12

12

C188

C110

.1UF

.1UF

12

12

C226

C145

.1UF

.1UF

12

C174

C183

.1UF

.1UF

12

12

C140

C139

.1UF

.1UF

12

12

C134

C146

.1UF

.1UF

Layout note :

Distribute as close as possible

to VCCPCMOS_LM .

+1.8V_SW

12

C74

+

22UF_1206_10V

12

C224

.1UF

Layout note :

Distribute as close as possible

to GMCH Local Memory Quadrant .

+1.8V_SW

12

C133

82PF

12

+

22UF_1206_10V

C82

12

C135

.1UF

Layout note :

Distribute as close as possible

to GMCH AGP/DVO Quadrant .

+1.5V_SW

12

+

22UF_1206_10V

C165

12

12

C97

C157

.1UF

.1UF

Layout note :

Distribute as close as possible

to GMCH System Memory Quadrant .

+3V

12

+

22UF_1206_10V

C221

12

12

C202

C203

.1UF

.1UF

12

C120

.1UF

12

12

C131

C137

.1UF

82PF

12

12

C123

C168

.1UF

82PF

12

12

C214

C201

.1UF

82PF

12

C121

.01UF

12

12

C197

C118

.1UF

.1UF

12

12

C141

C193

.1UF

82PF

12

12

C236

C213

.1UF

82PF

12

C122

.01UF

12

12

12

12

12

12

C175

C126

C185

C181

.1UF

.1UF

82PF

12

12

C209

.1UF

12

C208

82PF

C240

.1UF

C125

.1UF

.1UF

12

12

C239

C220

.1UF

.1UF

12

C180

C186

82PF

.1UF

12

12

12

12

C215

82PF

C238

.1UF

C244

.1UF

C237

.1UF

12

C242

.1UF

Layout note :

+VTT

12

C66

+

150UF_D2_6.3V

4 4

12

C49

+

150UF_D2_6.3V

12

C67

+

150UF_D2_6.3V

12

C415

+

150UF_D2_6.3V

Distribute as close as possible

to IO Quadrant .

+3V

12

C235

+

22UF_1206_10V

12

C241

.1UF

12

C225

.1UF

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

A

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

12 46Friday, September 21, 2001

E

of

1A

A

B

C

D

E

1 1

SM_D_MA[0..12]10 SM_MA[0..12] 14

SM_D_MA3

SM_D_MA2

SM_D_MA1

SM_D_MA0

2 2

3 3

SM_D_MA5

SM_D_MA4

SM_D_MA7

SM_D_MA6

SM_D_MA9

SM_D_MA8

SM_D_MA10

SM_D_MA11

SM_D_MA12

RP3

1 8

2 7

3 6

4 5

8P4R_10

RP5

1 8

2 7

3 6

4 5

8P4R_10

RP4

1 8

2 7

3 6

4 5

8P4R_10

1 2

R147 10

SM_MA3

SM_MA2

SM_MA1

SM_MA0

SM_MA5

SM_MA4

SM_MA7

SM_MA6

SM_MA9

SM_MA8

SM_MA10

SM_MA11

SM_MA12

Layout note :

One .1uF cap per power pin .

Place each cap close to SODIMM(DIMM 0) pin .

+3V

12

12

12

C462

.1UF

+3V

12

C417

+

22UF_1206_10V

12

C475

C465

.1UF

.1UF

C491

.1UF

12

C566

.1UF

Layout note :

One .1uF cap per power pin .

Place each cap close to SODIMM(DIMM 1) pin .

+3V

12

12

12

C461

.1UF

+3V

12

C416

+

22UF_1206_10V

12

C521

C489

.1UF

.1UF

C574

.1UF

12

C586

.1UF

12

12

C592

C579

.1UF

.1UF

12

12

C606

C593

.1UF

.1UF

12

12

C494

C602

.1UF

.1UF

12

12

C495

C481

.1UF

.1UF

12

12

C613

.1UF

12

C543

.1UF

12

C598

.1UF

12

C553

.1UF

12

C584

C556

.1UF

.1UF

12

12

C591

C601

.1UF

.1UF

12

12

C540

C528

.1UF

.1UF

12

12

C611

C619

.1UF

.1UF

12

12

C492

.1UF

12

C575

.1UF

12

C479

C464

.1UF

.1UF

12

12

C467

C470

.1UF

.1UF

4 4

Compal Electronics, inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

A

B

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

C

D

SCHEMATIC, M/B LA-1011

Size Document Number Rev

Custom

401174

Date: Sheet

13 46Friday, September 21, 2001

E

of

1A

A

+3V +3V +3V +3V

JP28

1

SM_DQ0

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

1 1

2 2

3 3

SM_DQM010

SM_DQM110

SM_MA013

SM_MA113

SM_MA213

SMD_CLK010

SM_RAS#10

SM_WE#10

SM_CS#010

SM_CS#110

SM_MA613

SM_MA813

SM_MA913

SM_MA1013

SM_DQM210

SM_DQM310

SM_DQ7

SM_DQM0

SM_DQM1

SM_MA0

SM_MA1

SM_MA2

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SMD_CLK0

SM_RAS#

SM_WE#

SM_CS#0

SM_CS#1

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_MA6

SM_MA8

SM_MA9

SM_MA10

SM_DQM2

SM_DQM3

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SODIMM0_SMDAT

VSS

3

DQ0

5

DQ1

7

DQ2

9

DQ3

11

VCC

13

DQ4

15