Acer K42Jr Schematics

5

4

3

2

1

SYSTEM PAGE REF.

PAGE

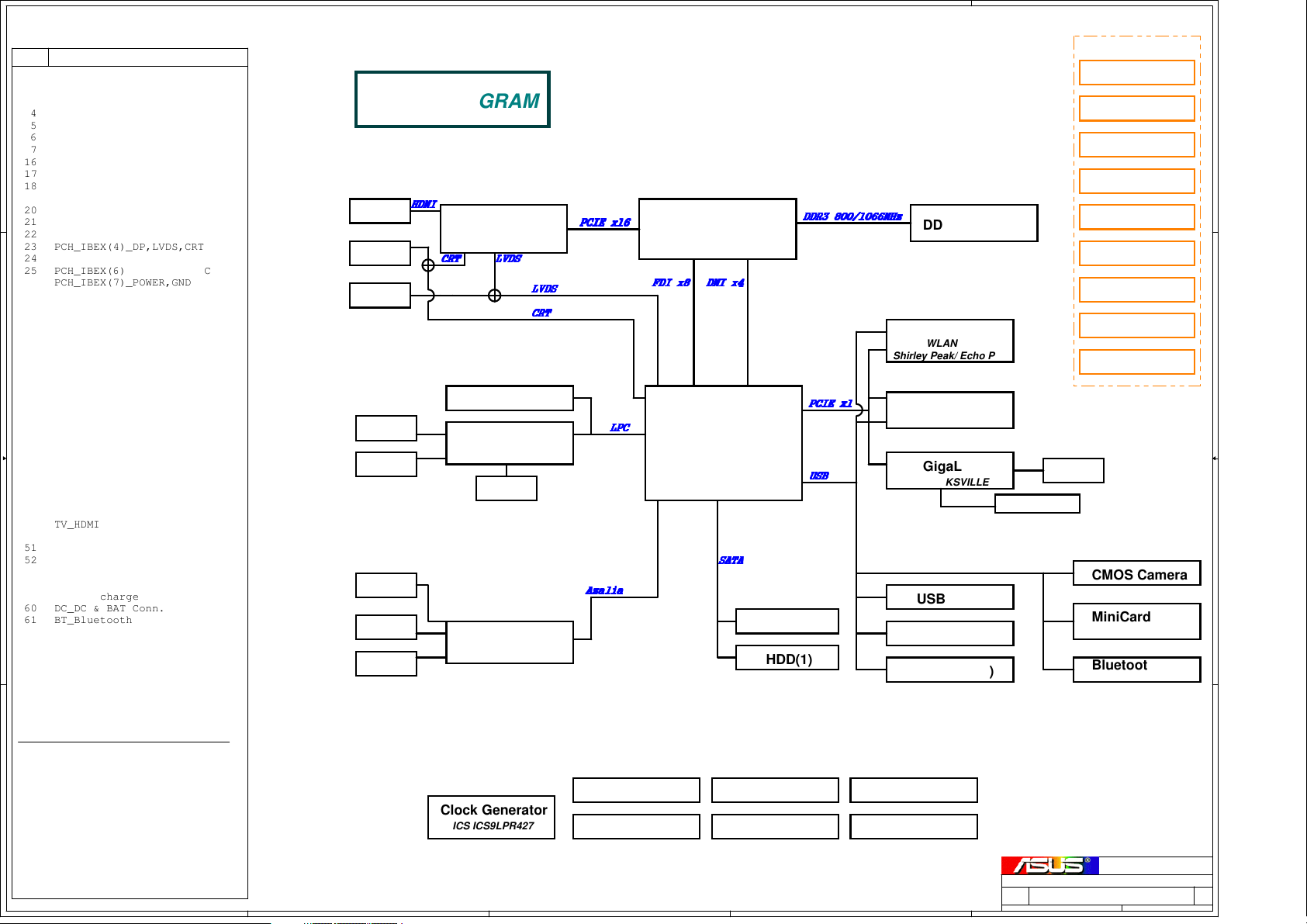

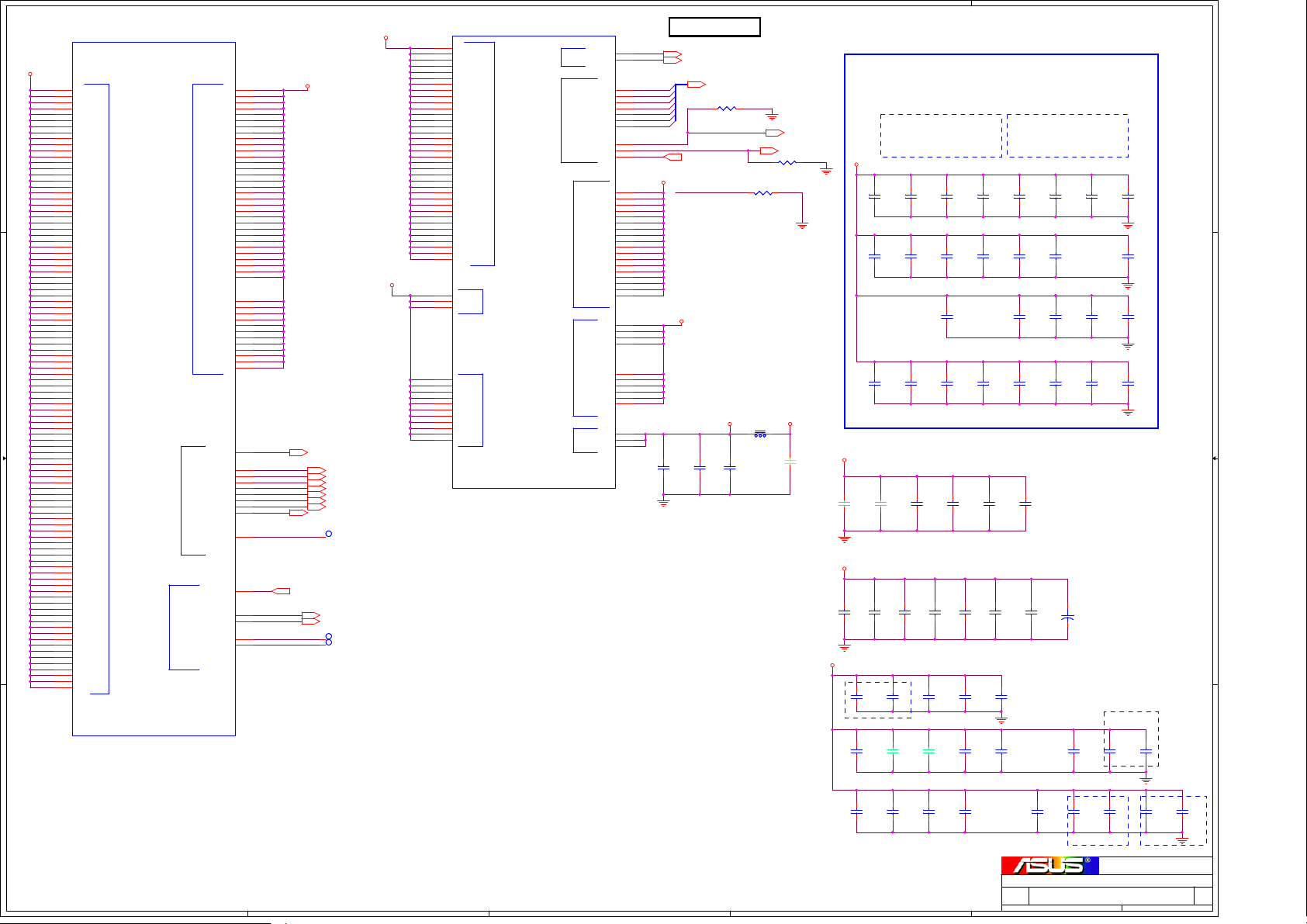

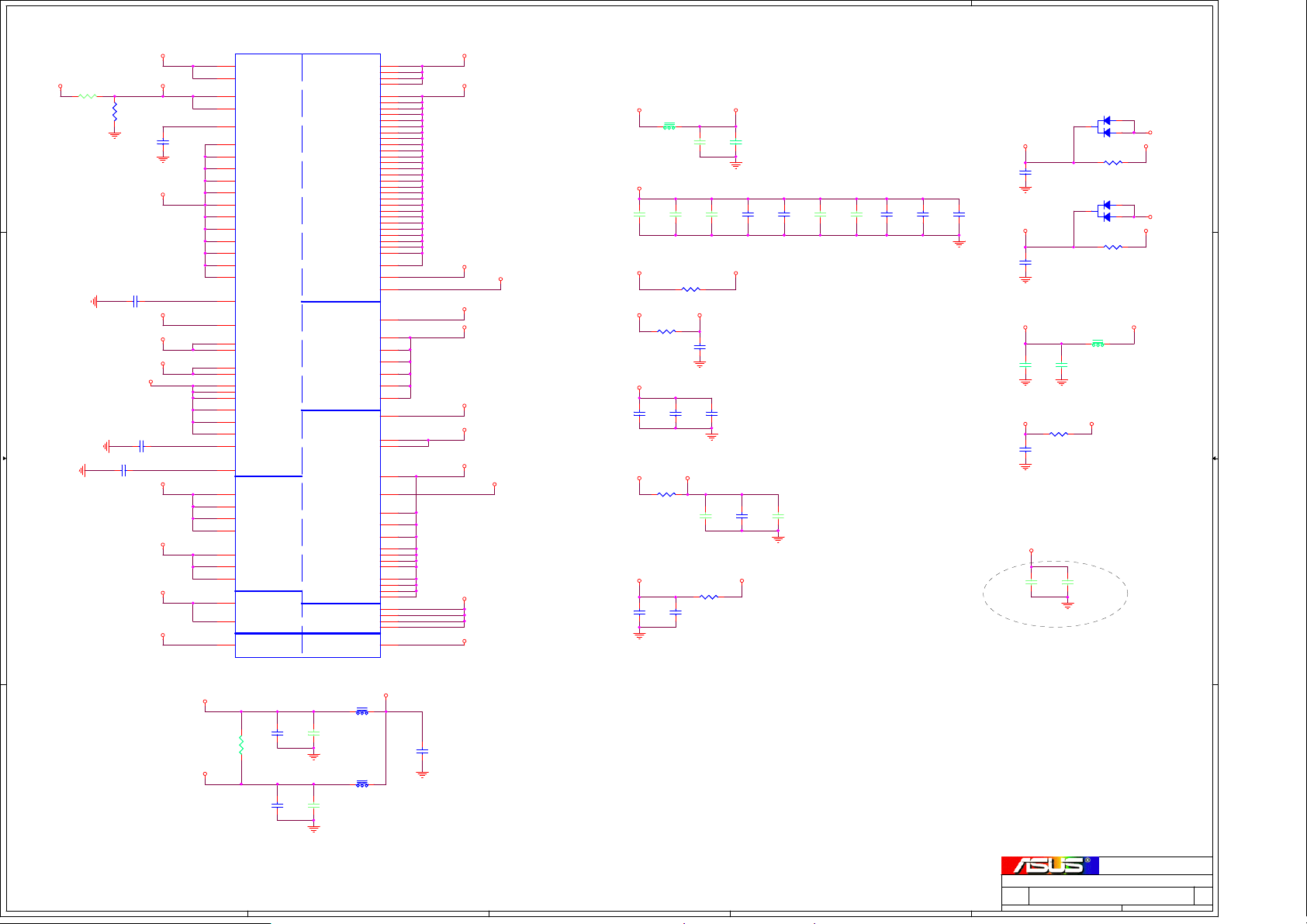

1 Block Diagram

2 System Setting

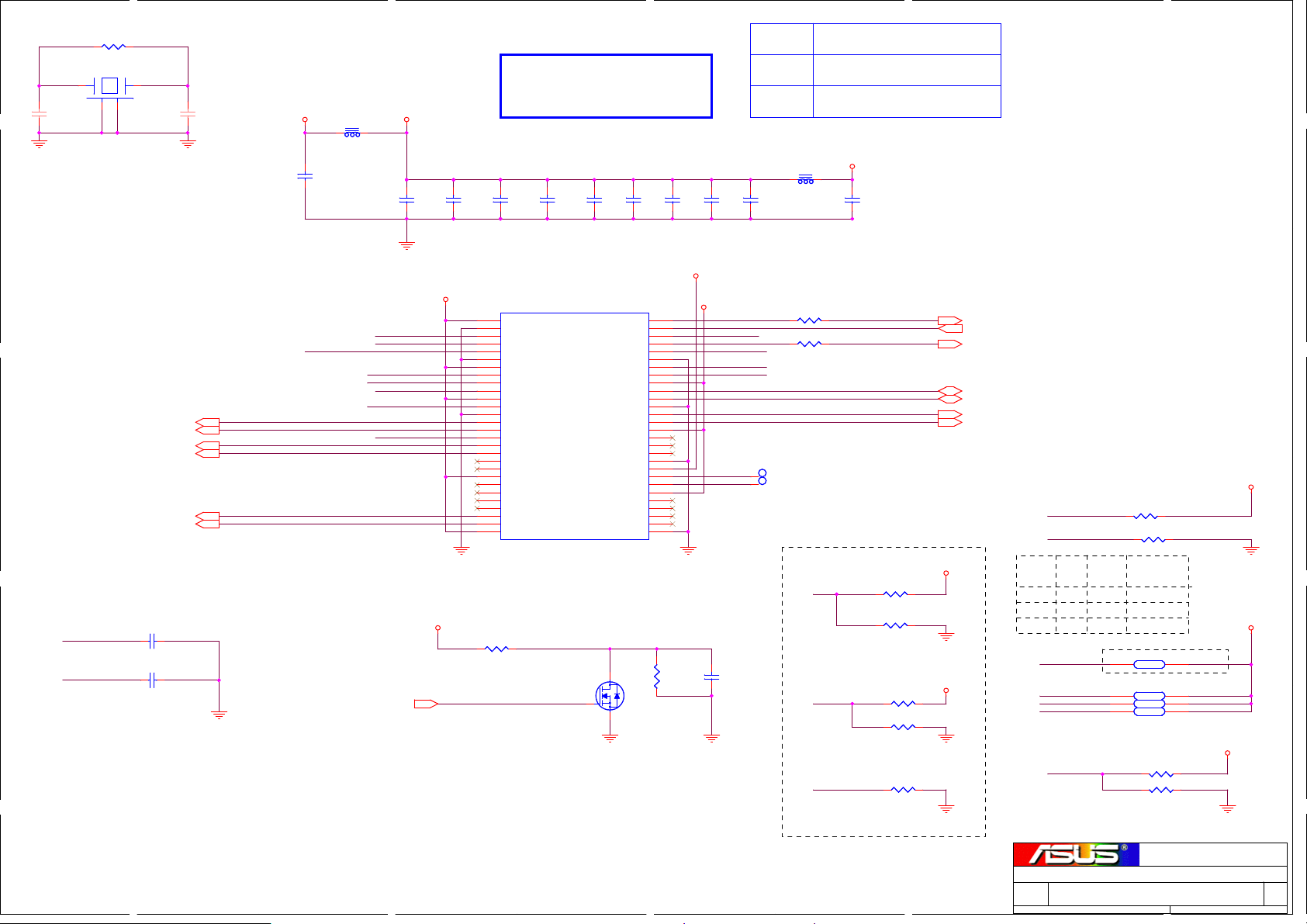

3 CPU(1)_DMI,PEG,FDI,CLK,MISC

4

D D

C C

B B

CPU(2)_DDR3

5

CPU(3)_CFG,RSVD,GND

6

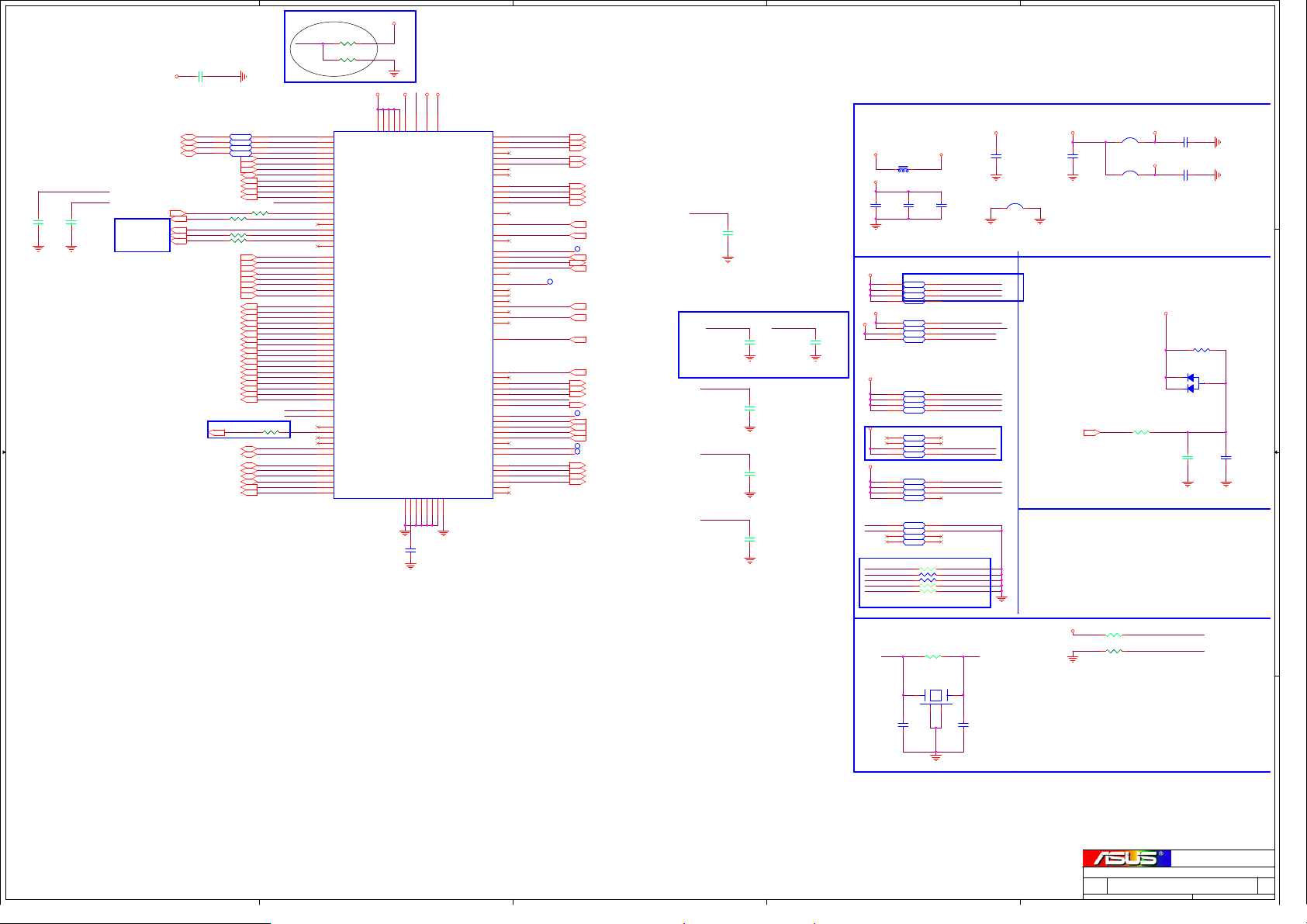

CPU(4)_PWR

7

CPU(5)_XDP

16

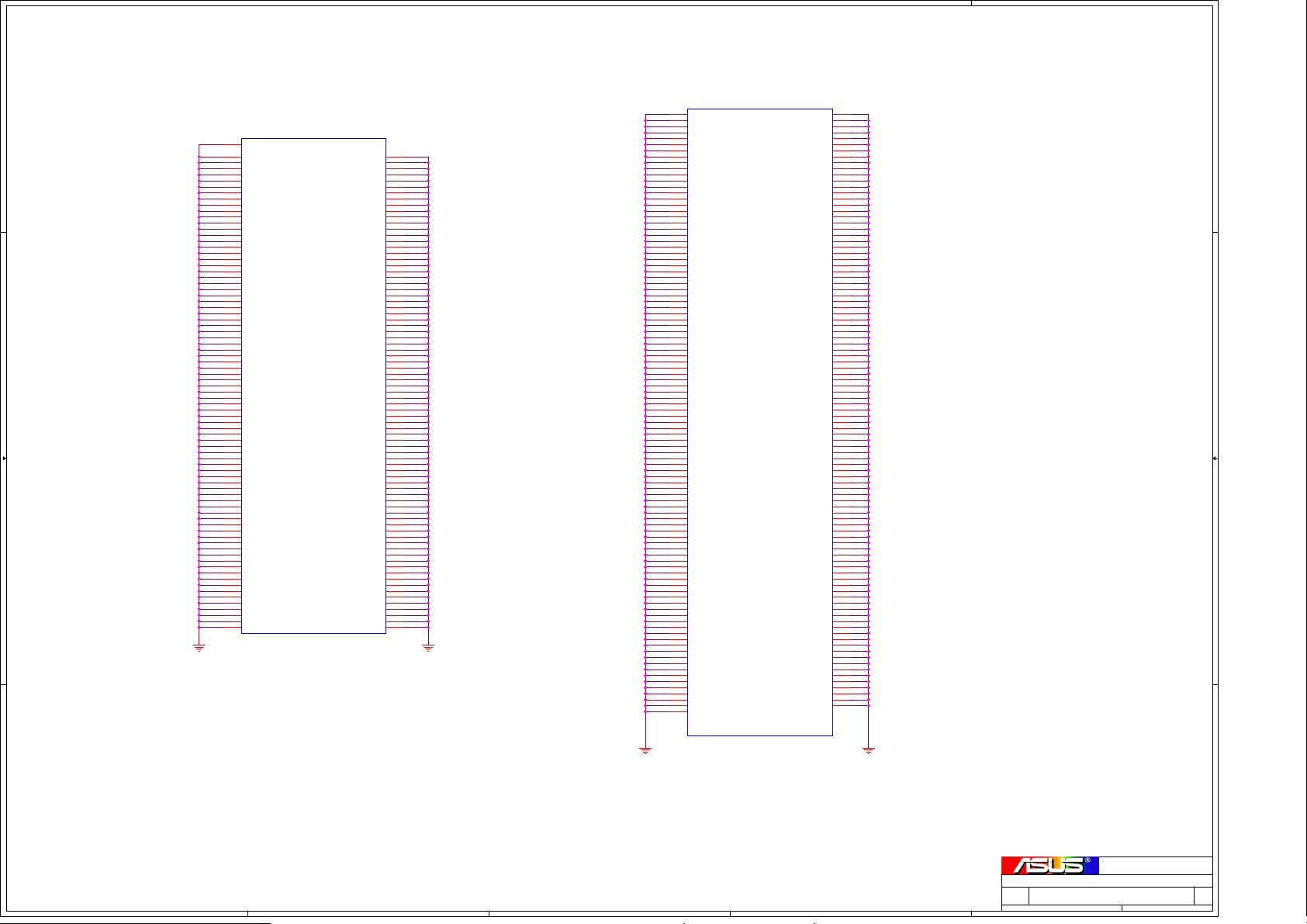

DDR3 SO-DIMM_0

17

DDR3 SO-DIMM_1

18

DDR3 CA_DQ VOLTAGE

19 VID controller

20

PCH_IBEX(1)SATA,IHDA,RTC,LPC

21

PCH_IBEX(2)_PCIE,CLK,SMB,PEG

22

PCH_IBEX(3)_FDI,DMI,SYS PWR

23

PCH_IBEX(4)_DP,LVDS,CRT

24

PCH_IBEX(5)_PCI,NVRAM,USB

25

PCH_IBEX(6)CPU,GPIO,MISC

PCH_IBEX(7)_POWER,GND

26

27

PCH_IBEX(8)_POWER,GND

28

PCH_SPI ROM,OTH

29

CLK_ICS9LPR362

30

EC_IT8512(1/2)

31

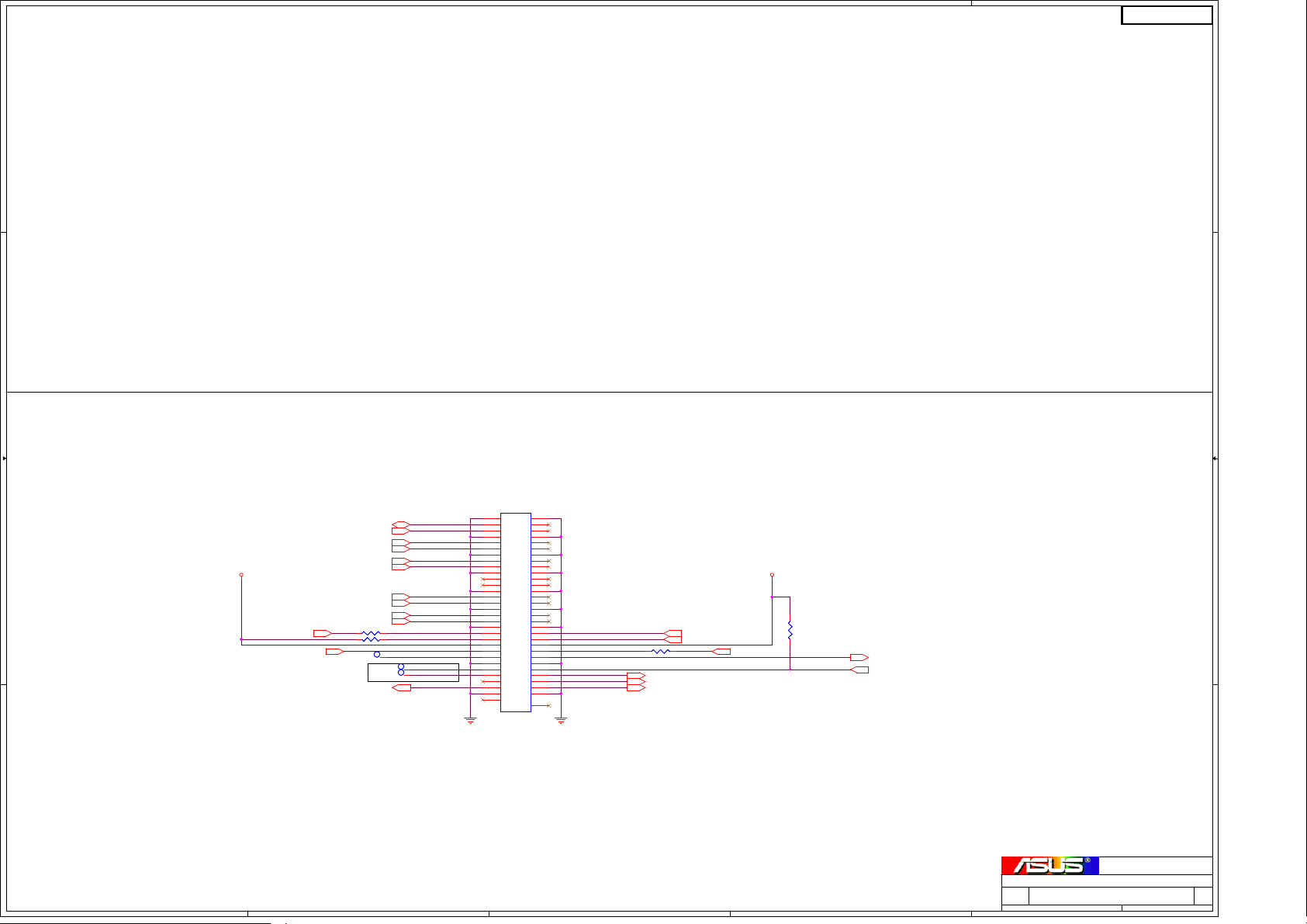

EC_IT8512(2/2)KB, TP

32

RST_Reset Circuit

33

HANKSVILLE

34

LAN_RJ45

36

CODEC-ALC663

37

AUD_Amp & Jack

38

AUD_FM2010

40

CB_R5C833

41

CB_R5C833

42

CB_4in1 CardReader

CB_NewCard

43

BUG_Debug

44

45

CRT_LCD Panel

46

CRT_D-Sub

Display Port

47

48

TV_HDMI

50

FAN_Fan & Sensor

51

XDD_HDD & ODD

USB_USB Port *2

52

MINICARD(WLAN)

53

LED_Indicator

56

DSG_Discharge

57

DC_DC & BAT Conn.

60

BT_Bluetooth

61

TUN_TV Tuner

64

ME_Conn & Skew Hole

65

ESA_ESATA

66

PCH_XDP, ONFI

67

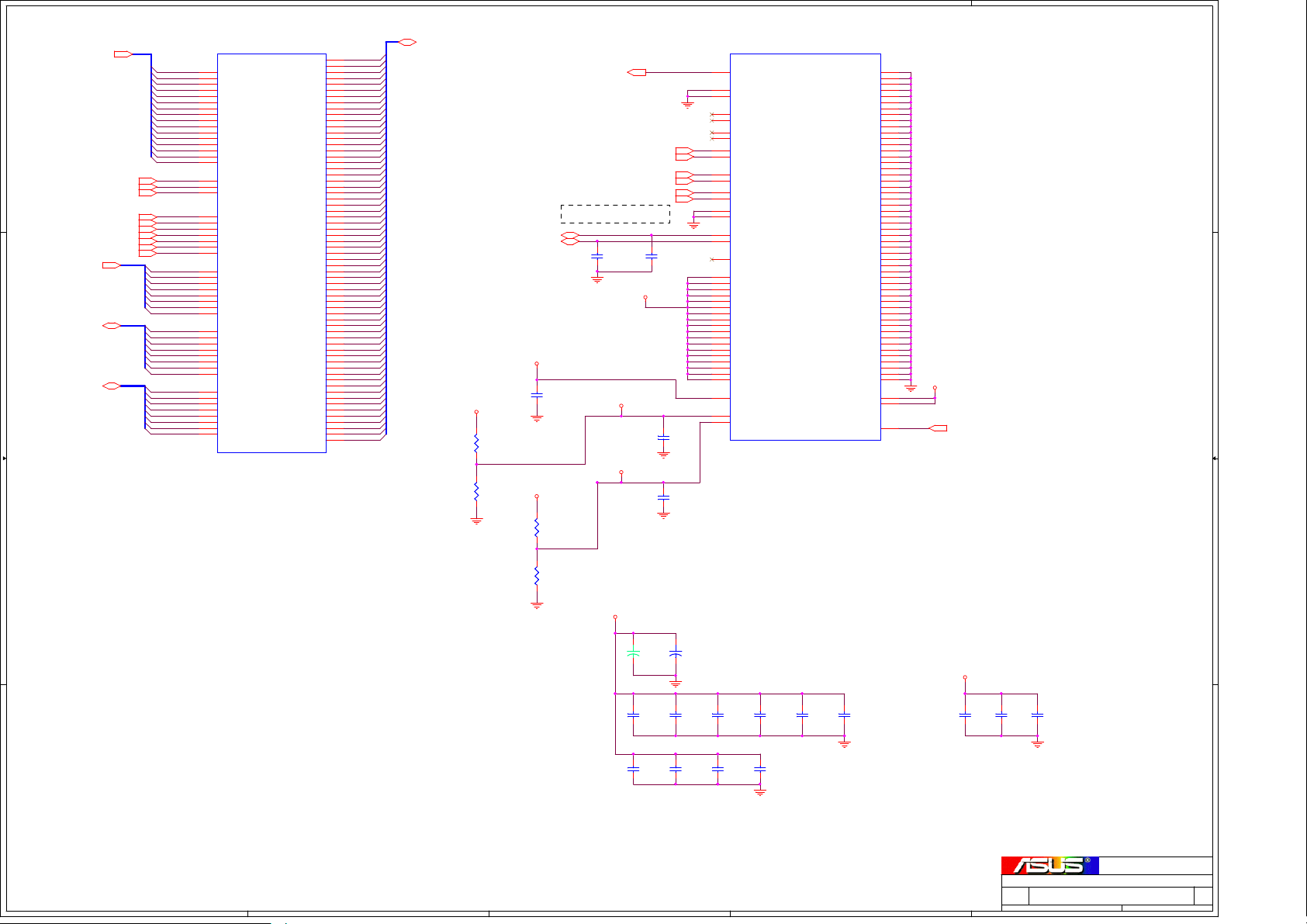

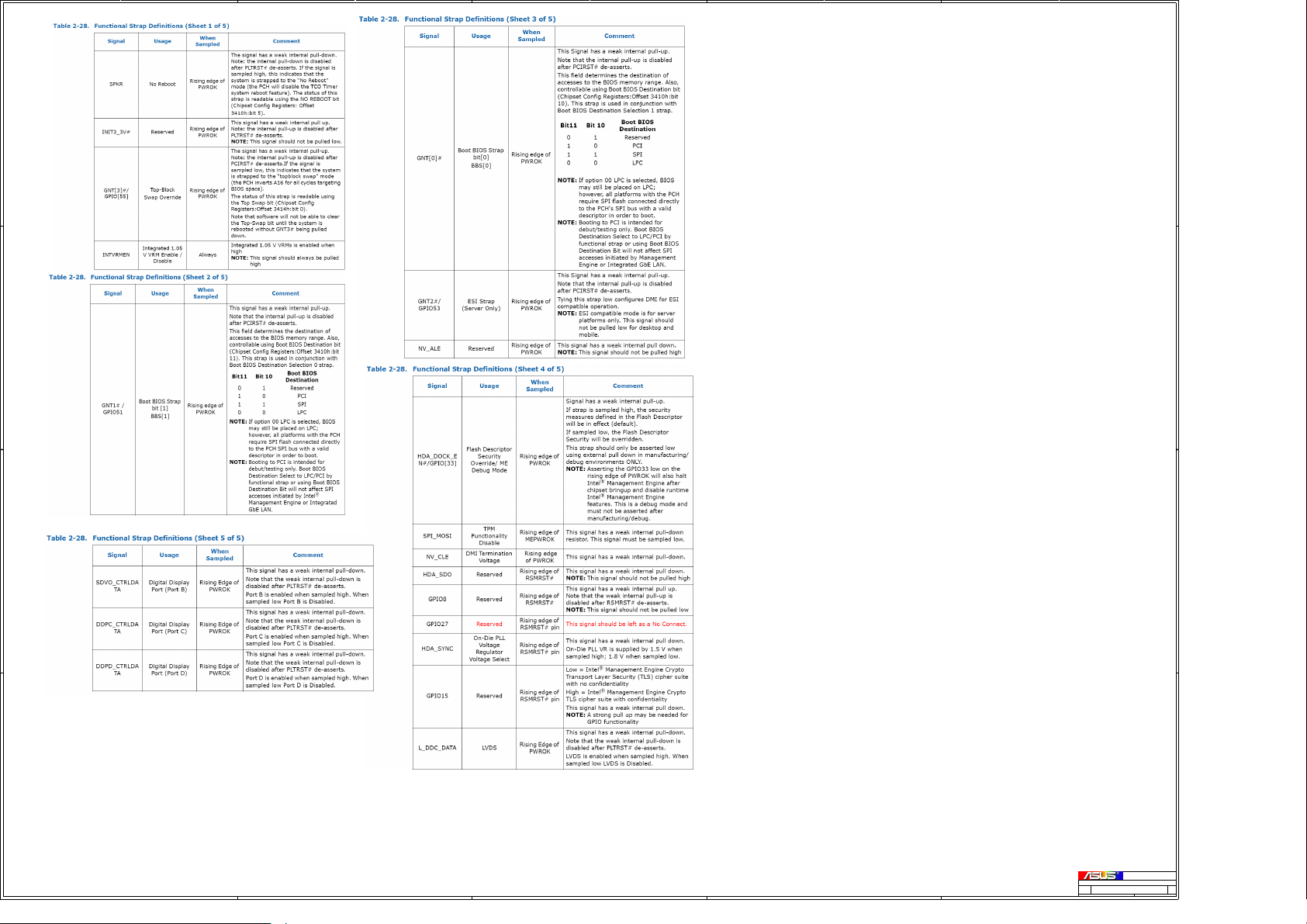

Content

K42Jr SCHEMATIC Revision 2.0

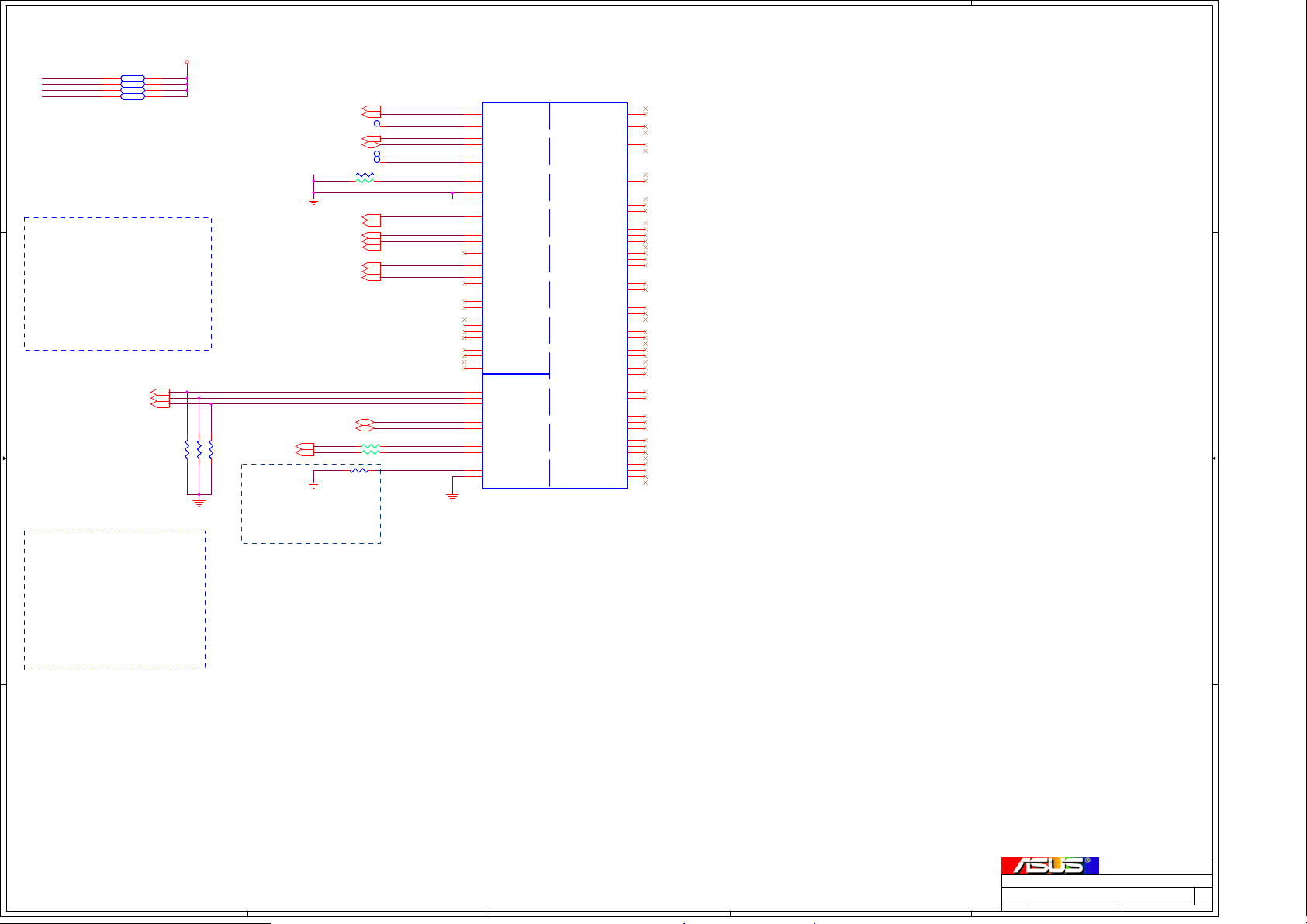

BLOCK DIAGRAM

HDMI

HDMI

Jack

HDMIHDMI

AMD PARK-XT-S3

LVDS

CRT

CRT

CRTCRT

LVDS

LVDSLVDS

Debug Conn.

EC

IT8500E-L

SPI ROM

Azalia Codec

Realtek ALC269

LVDS

LVDS

LVDSLVDS

CRT

CRT

CRTCRT

PCIE x16

PCIE x16

PCIE x16PCIE x16

LPC

LPC

LPCLPC

Azalia

Azalia

AzaliaAzalia

CPU

ARRANDALE

DMI x4

FDI x8

FDI x8FDI x8

DMI x4FDI x8

DMI x4DMI x4

PCH

Ibex Peak-M

SATA

SATA

SATASATA

DDR3 800/1066MHz

DDR3 800/1066MHz

DDR3 800/1066MHzDDR3 800/1066MHz

PCIE x1

PCIE x1

PCIE x1PCIE x1

USB

USB

USBUSB

ODD

HDD(1)

HDMI

CRT

LCD Panel

Touchpad

Keyboard

INT. MIC

Audio Amp

DDR3 SO-DIMM

MiniCard

WLAN

Shirley Peak/ Echo Peak

MiniCard

GigaLAN

HANKSVILLE

CardReader

USB Port(1)

USB Port(2)

USB Port(3)

RJ45

Power

VCORE

System

1.5VS & 1.05VS

DDR & VTT

+2.5VS

Charger

Detect

Load Switch

Power Protect

CMOS Camera

MiniCard

Bluetooth

VGA_MXM

70

VGA_LVDS Switch

71

PW_VCORE(MAX17034)

80

PW_SYSTEM(MAX17020)

81

PW_I/O_VTT_CPU&+1.1VM

82

A A

PW_I/O_DDR & VTT& +1.8VS83

PW_I/O_3VM & ME_+VM_PWEGD

84

PW_+VGFX_CORE(MAX17028)

86

PW_CHARGER(MAX17015)

88

PW_DETECT

90

PW_LOAD SWITCH

91

PW_PROTECT

92

PW_SIGNAL93

PW_FLOWCHART

94

5

Clock Generator

ICS ICS9LPR427

4

VID controller

PWM Fan

3

Discharge Circuit

Reset Circuit

DC & BATT. Conn.

Skew Holes

2

Title :

Title :

Title :

Block Diagram

Block Diagram

Block Diagram

Nic

Nic

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

K42Jr

K42Jr

K42Jr

1

Nic

1 96Thursday, November 12, 2009

1 96Thursday, November 12, 2009

1 96Thursday, November 12, 2009

Rev

Rev

Rev

1.1

1.1

1.1

5

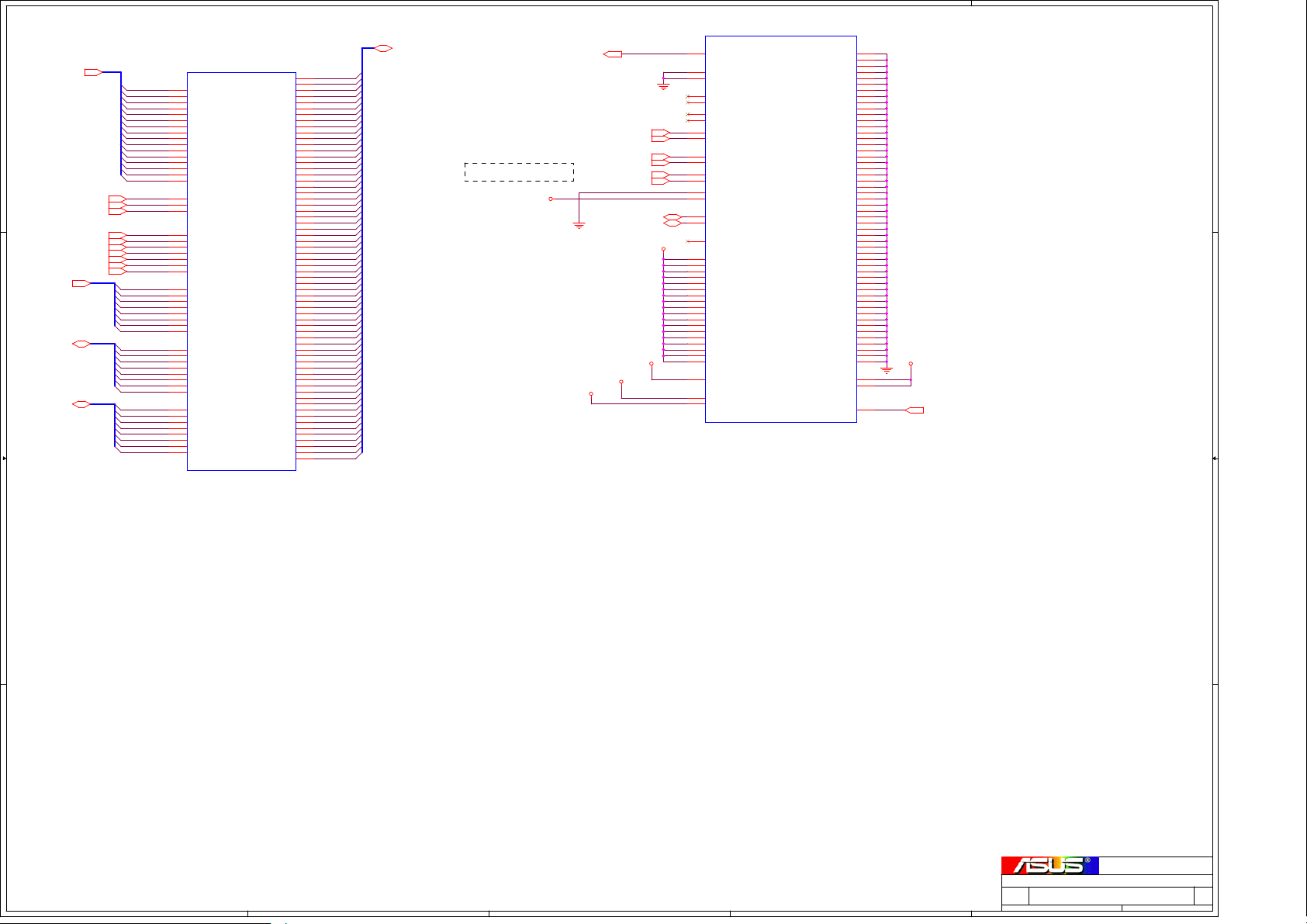

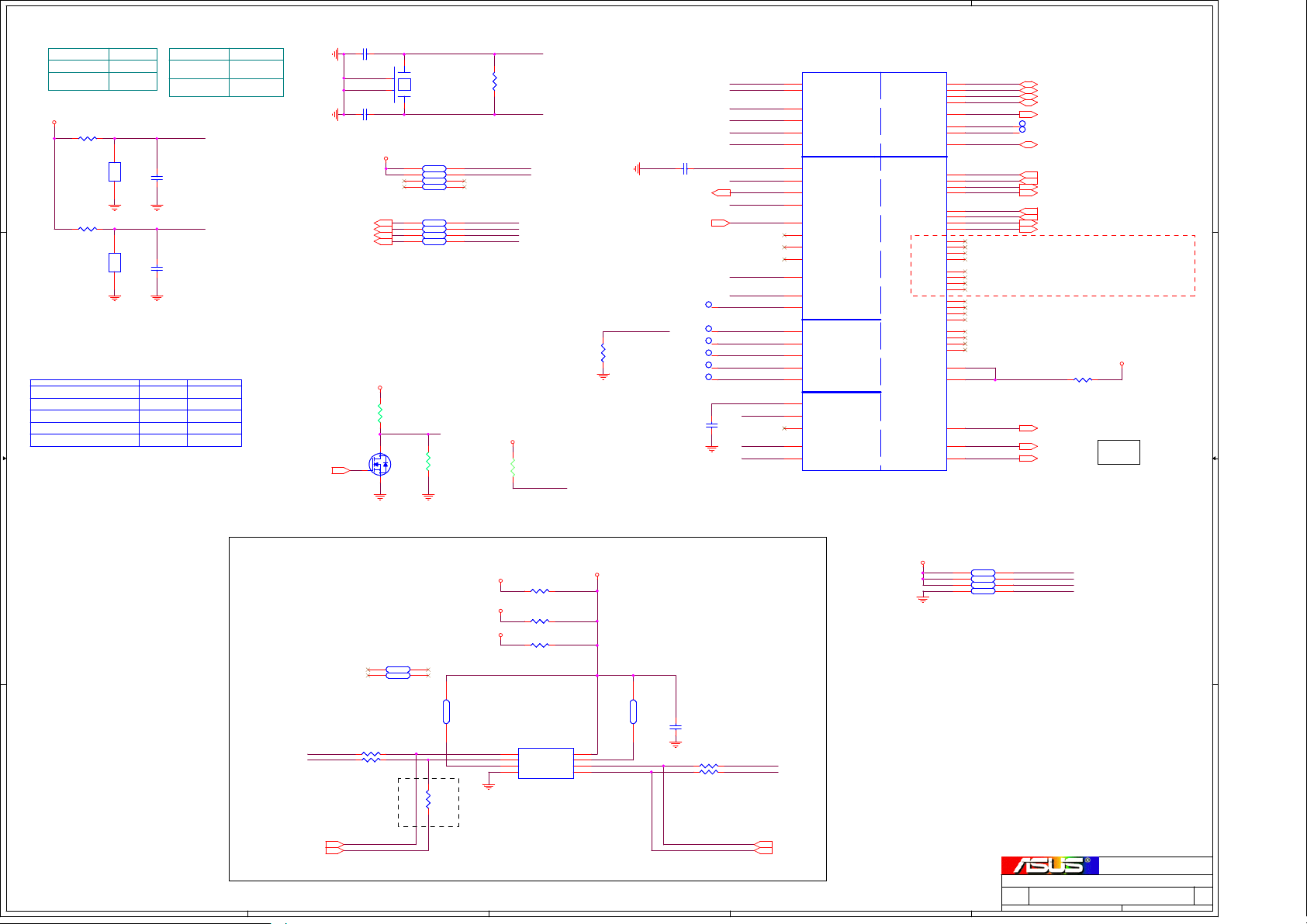

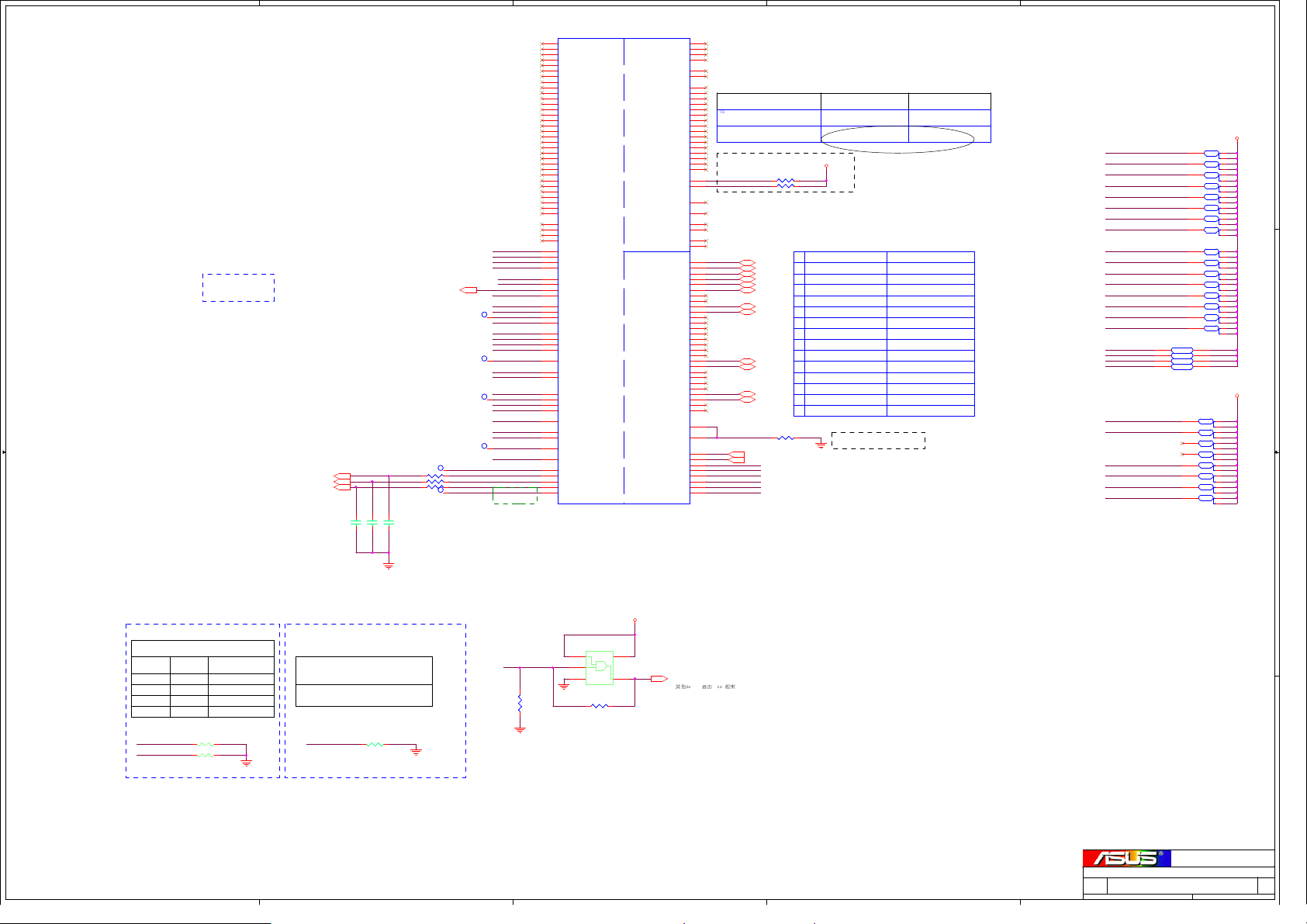

PCH_IBEX

GPIO

D D

C C

B B

A A

PCH_IBEX

GPIO

GPIO 00

GPIO 01

GPIO [2:5]

GPIO 06

GPIO 07

GPIO 08

GPIO 09

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16 +3VS

GPIO 17 +3VSGPO

GPIO 18 +3VS

GPIO 19 +3VS

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24 +3VSUS

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 38

GPIO 39 +3VS

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 44

GPIO 45

GPIO 46

GPIO 47

GPIO 48

GPIO 49

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54

GPIO 55

GPIO 56

GPIO 57

GPIO 58

GPIO 59

GPIO 60

GPIO 61

GPIO 62

GPIO 63

GPIO 64

GPIO 65

GPIO 66

GPIO 67

GPIO 72

GPIO 73

GPIO 74

GPIO 75

5

GPO

GPO

Native

GPO

GPO

GPI

Native

Native

GPI

Native

GPO

GPO

GPO

GPO

Native

GPO

Native

GPO

GPO

Native

GPO Native

Native CLKREQ4#

GPO

GPO

Native

Native

Native

Native

GPO

Native

Native

GPO

GPI

GPI

GPI

Native

Native

Native

Native

Native

Native

Native

Native CLKREQ_PEG#

GPO

Native

Native

GPO

GPO

GPO

GPO

Native

GPO

Native

Native

GPO

Native

Native

Native

Native

Native

Native

Native

GPO

Native

GPO

Native

Signal NameUse As Power

-

-

DGPU_HPD_INTR#

EXT_SMI#

USB_OC5#

USB_OC6#

EXT_SCI#

PM_LAYPHY_EN

CB_SD#

WLAN_ON

DGPU_HOLD_RST#

DGPU_PWROK

CLKREQ1#_TV

CLKREQ2#_WLAN

WLAN_LED

LDRQ1#

CLKREQ3#_NEWCARD

BT_LED

ME_PM_SLP_LAN#

ME_Sus_PwrDnAck

ME_AC_PRESENT

PM_CLKRUN#

STP_PCI#

SATA_CLK_REQ#

DGPU_PWR_EN#

DGPU_PRSNT#

PCB_ID0

PCB_ID1

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

CLK_REQ5#

CLK_REQ6#

CLK_REQ7#

GPU_RST#GPO

PCI_REQ1#

PCI_GNT1#

-

-

-

CLKREQ_GLAN#

BT_ON

SML1_CLK

USB_OC0#

PM_SUS_STAT#

SUS_CLK

PM_SLP_S5#

CLK_OUT0

CLK_OUT1

CLK_OUT2

CLK_OUT3

CLK_REQ0#

SML1_DATA

4

Internal &

External

Pull-up/down

-

INT TBD

EXT PU

INT TBD

INT TBD

EXT PU & INT PU

EXT PU

EXT PU

EXT PU

EXT PU

-

EXT PU(DIODE DNI)

INT PD

-

EXT PD & INT TBD

EXT PU(DNI)/PD

-

EXT PU(DNI)/PD

-

EXT PD

INT PU

-

EXT PU(DNI)/PD

EXT PU (Not used)

INT WEAK PU

EXT PD

EXT PU(DNI)/PD(DNI)

EXT PU

EXT PU

EXT PU

-

EXT PU/PD(DNI)

EXT PU

EXT PU

EXT PD

EXT PD

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PD

-

-

EXT PU (Not used)

INT PU

-

INT PU

-

INT PU

EXT PU(DNI)/PD

EXT PU(DIODE)

EXT PU

EXT PU (Not used)

-

-

-

-

INT TBD

INT TBD

INT TBD

INT TBD

-

EXT PU (Not used)

EXT PU (Not used)

EXT PU

4

+3VS

+3VS

+5VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+5VS

+3VS

+5VS

+3VS

+5VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

EC

IT8512

3

EC GPIO

Use As Signal Name

GPA0

GPA1

GPA2

GPA3

GPA4

GPA5

GPA6

GPA7

GPB0

GPB1

GPB2

GPB3

GPB4

GPB5

GPB6

GPB7

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

GPD0

GPD1

GPD2

GPD3

GPD4

GPD5

GPD6

GPD7

GPE0

GPE1

GPE2

GPE3

GPE4

GPE5

GPE6

GPE7

GPF0

GPF1

GPF2

GPF3

GPF4

GPF5

GPF6

GPF7

GPG0

GPG1

GPG2

GPG6 GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6 CAP_LED#

GPI0

GPI1

GPI2

GPI3

GPI4

GPI5

GPI6

GPI7

GPJ0

GPJ1

GPJ2

GPJ4

GPJ5 -

PWR_LED#

O

CHG_LED#

O

-

LCD_BL_PWM

O

FAN0_PWM

O

-

SUSC_EC#

O

SUSB_EC#

O

SMB0_CLK

IO

SMB0_DAT

IO

A20GATE

O

RC_IN#

O

O

PM_RSMRST#

SMB1_CLK

IO

SMB1_DAT

IO

PM_PWRBTN#

O

I

AC_IN_OC#

OP_SD#

I

BAT1_IN_OC#

I

RFON_SW#

-

I

PM_SUSC#

BUF_PLT_RST#

I

EXT_SCI#

O

EXT_SMI#

O

O

LCD_BACKOFF#

I

FAN0_TACH

-

O

VSUS_ON

O

EGAD (IT8301 Address/Data connect)

O

EGCS (IT8301 Cycle Start connect)

O

EGCLK (IT8301 Clock connect)

I

PWR_SW#

-

I

LID_SW#

CAP_ACK#

I

-

EXP_GATE#

I

TP_CLK

I

TP_DAT

IO

THRO_CPU

O

-

PM_SUSB#

I

-

IO

PM_CLKRUN#

-

O

GFX_VR_ON

O

BAT_LEARN

-

O

NUM_LED#

O

-

I

SUS_PWRGD

I

ALL_SYSTEM_PWRGD

I

VRM_PWRGD

I

GFX_VR

I

ALS_AD

-

-

O

CPU_VRON

O

PM_PWROK

O

VSET_EC

O

ISET_ECGPJ3

O

TP_LED

3

2

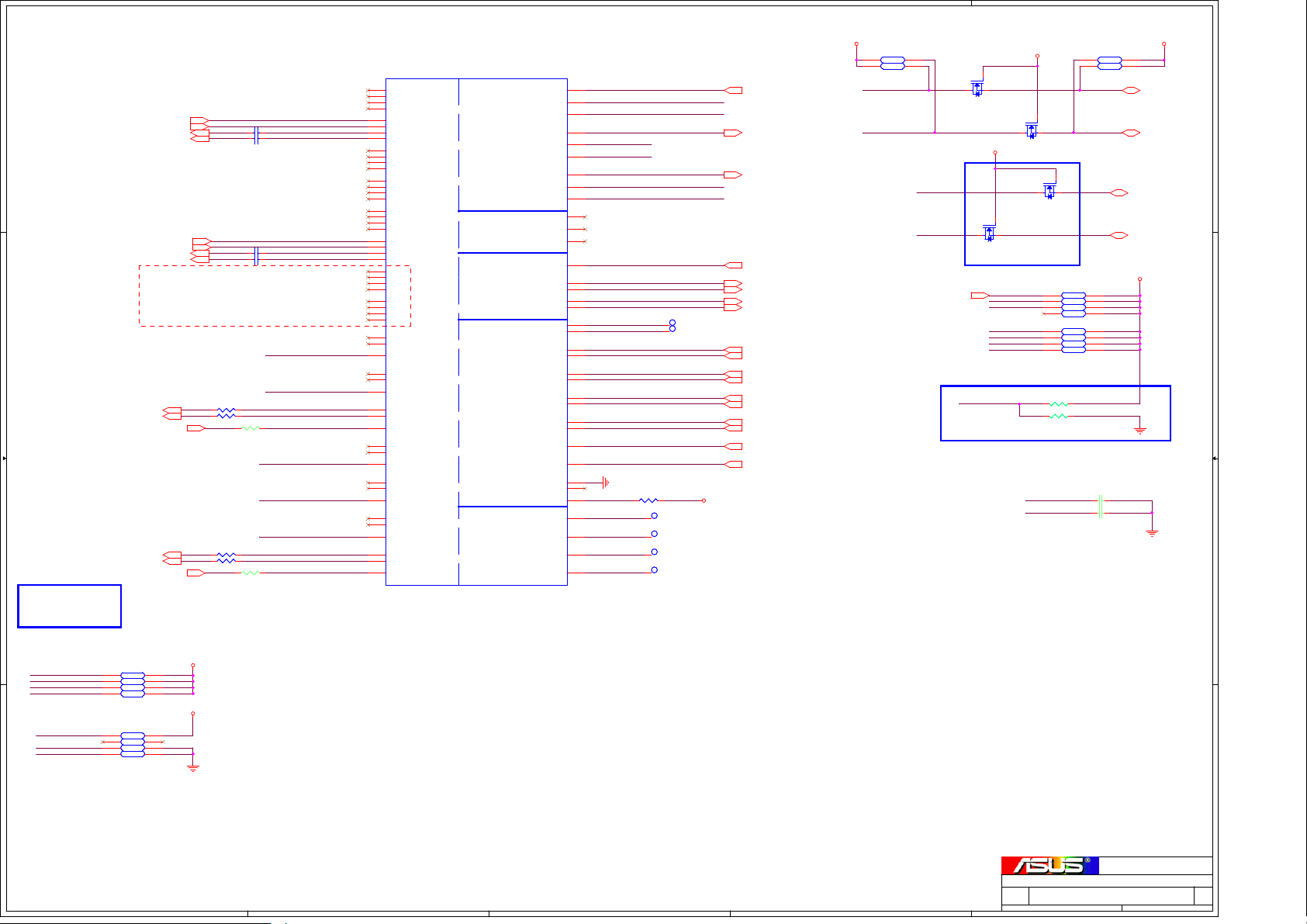

EC

IT8301

2

1

GPIO0 ME_PM_SLP_M#

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

I

I

I

I

O

O

O

Signal NameUse AsEC GPIO

ME_SusPwrDnAck

-

ME_+VM_PWRGD

ME_PM_SLP_LAN#

ME_AC_PRESENT

-

-

-

-

ME_PWROK

ME_SLP_M_EC#

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

SM_BUS ADDRESS :

PCH Master

SM-Bus Device

Clock Generator(ICS9LPR362)

SO-DIMM 0 1010000x ( A0 )

SO-DIMM 1

VID Controller(ASM8272)

WiFi/WiMax

EC Master (SMB1)

SM-Bus Device

CPU Thermal Sensor(G780) 1001100x ( 98 )

Minicard TV Tuner

PCIE 1

PCIE 2

Minicard WLAN

PCIE 3

Newcard

PCIE 4

PCIE 5

ESATA (for pre-ES1)

PCIE 6

GLAN

PCIE 7

PCIE 8

SATA 0

SATA HDD (1)

SATA1

SATA ODD

SATA HDD (2)

SATA4

SATA5

ESATA

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

ASUSTeK COMPUTER INC. NB4

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

SM-Bus Address

1101001x ( D2 )

1010001x ( A2 )

0011011x ( 36 )

N/A

SM-Bus Address

1001101x ( 9A )VGA Thermal IC(G781-1)

USB 0

USB Port (1)

USB Port (2)

USB 1

USB 2

USB Port (3)

USB Port (4)

USB 3

CMOS Camera

USB 4

USB 5

NewCard

Minicard TV Tuner

USB 6

USB 7

USB 8

USB 9

WLAN

USB 10

USB 11

USB 12

Bluetooth

USB 13

Finger Printer

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

M60JV

M60JV

M60JV

1

System Setting

System Setting

System Setting

CH_Lin

CH_Lin

CH_Lin

2 96Thursday, November 12, 2009

2 96Thursday, November 12, 2009

2 96Thursday, November 12, 2009

Rev

Rev

Rev

1.01

1.01

1.01

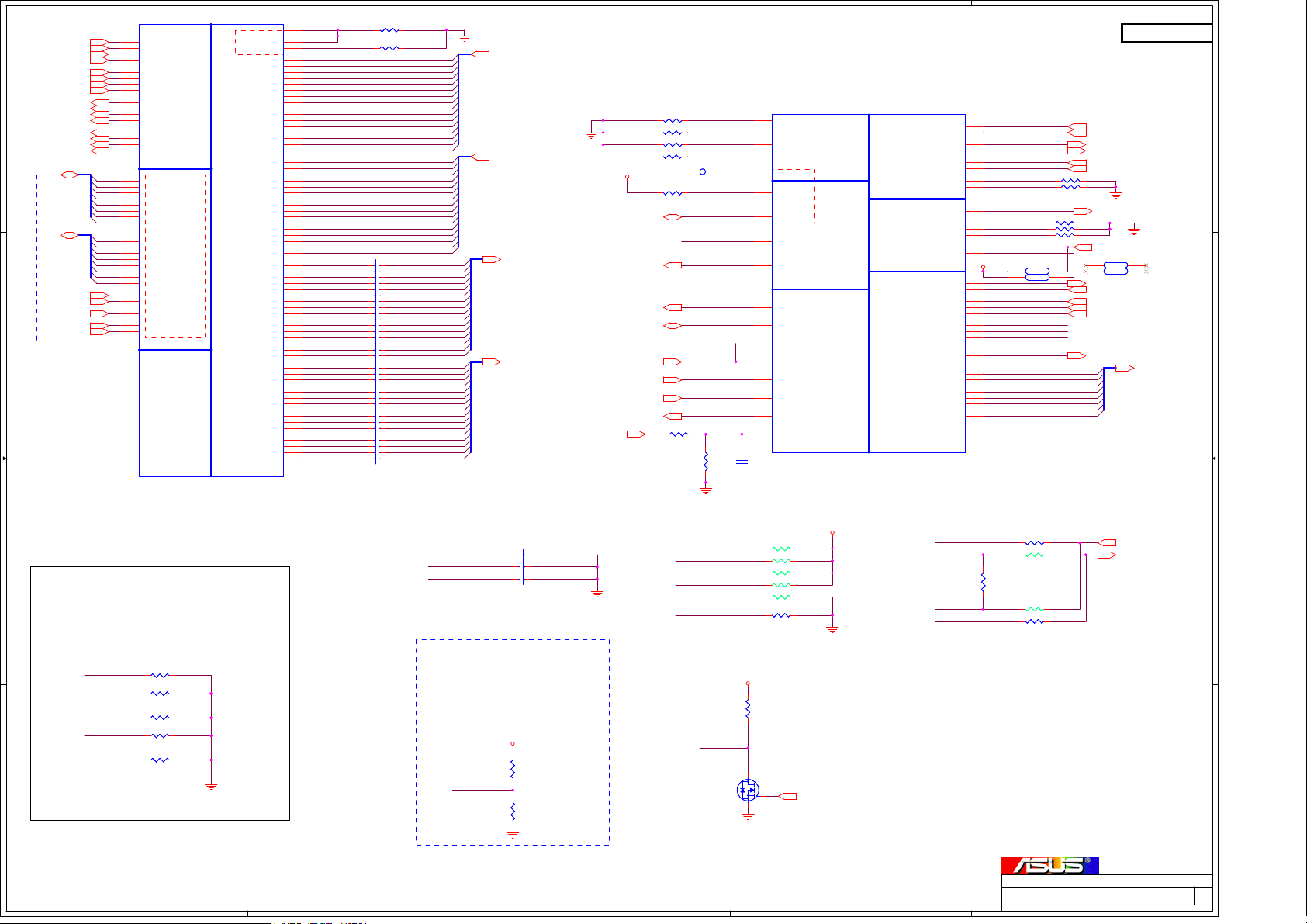

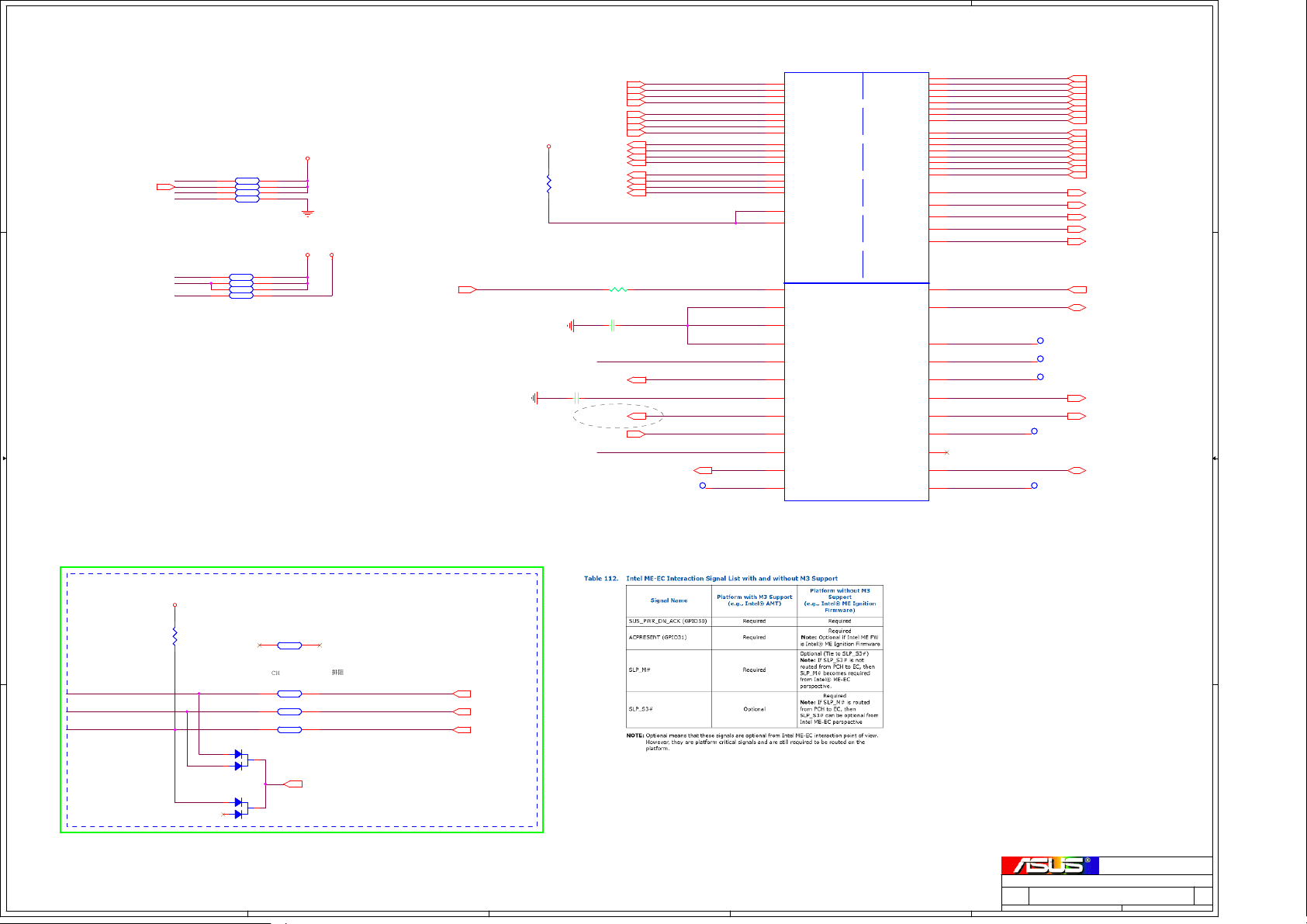

5

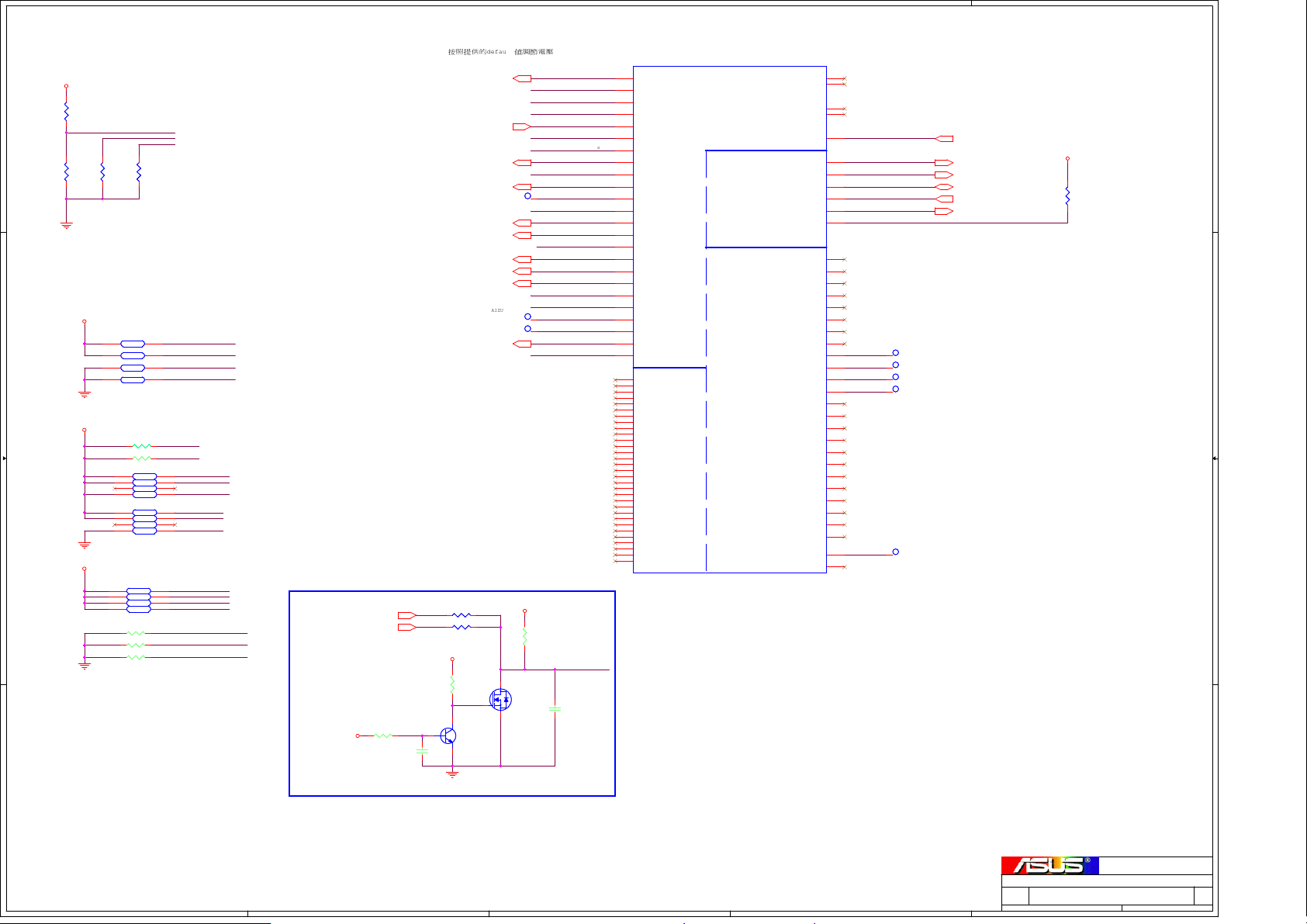

U0301A

U0301A

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

SOCKET989

SOCKET989

DMI_TXN0(22)

DMI_TXN1(22)

DMI_TXN2(22)

DMI_TXN3(22)

DMI_TXP0(22)

DMI_TXP1(22)

DMI_TXP2(22)

DMI_TXP3(22)

DMI_RXN0(22)

DMI_RXN1(22)

DMI_RXN2(22)

D D

C C

DMI_RXN3(22)

DMI_RXP0(22)

DMI_RXP1(22)

DMI_RXP2(22)

DMI_RXP3(22)

FDI_TXN[7:0](22)

FDI_TXP[7:0](22)

FDI_FSYNC0(22)

FDI_FSYNC1(22)

FDI_INT(22)

FDI_LSYNC0(22)

FDI_LSYNC1(22)

For Intel GFX display

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_IRCOMP_R

EXP_RBIAS

PCIENB_RXN15

PCIENB_RXN14

PCIENB_RXN13

PCIENB_RXN12

PCIENB_RXN11

PCIENB_RXN10

PCIENB_RXN9

PCIENB_RXN8

PCIENB_RXN7

PCIENB_RXN6

PCIENB_RXN5

PCIENB_RXN4

PCIENB_RXN3

PCIENB_RXN2

PCIENB_RXN1

PCIENB_RXN0

PCIENB_RXP15

PCIENB_RXP14

PCIENB_RXP13

PCIENB_RXP12

PCIENB_RXP11

PCIENB_RXP10

PCIENB_RXP9

PCIENB_RXP8

PCIENB_RXP7

PCIENB_RXP6

PCIENB_RXP5

PCIENB_RXP4

PCIENB_RXP3

PCIENB_RXP2

PCIENB_RXP1

PCIENB_RXP0

PCIENB_TXN15

PCIENB_TXN14

PCIENB_TXN13

PCIENB_TXN12

PCIENB_TXN11

PCIENB_TXN10

PCIENB_TXN9

PCIENB_TXN8

PCIENB_TXN7

PCIENB_TXN6

PCIENB_TXN5

PCIENB_TXN4

PCIENB_TXN3

PCIENB_TXN2

PCIENB_TXN1

PCIENB_TXN0

PCIENB_TXP15

PCIENB_TXP14

PCIENB_TXP13

PCIENB_TXP12

PCIENB_TXP11

PCIENB_TXP10

PCIENB_TXP9

PCIENB_TXP8

PCIENB_TXP7

PCIENB_TXP6

PCIENB_TXP5

PCIENB_TXP4

PCIENB_TXP3

PCIENB_TXP2

PCIENB_TXP1

PCIENB_TXP0

4

R0301 49.9Ohm1%R0301 49.9Ohm1%

1 2

R0302 750Ohm1%R0302 750Ohm1%

1 2

CX0316 0.1UF/16VC X0316 0.1UF/16V

1 2

CX0315 0.1UF/16VC X0315 0.1UF/16V

1 2

CX0314 0.1UF/16VC X0314 0.1UF/16V

1 2

CX0313 0.1UF/16VC X0313 0.1UF/16V

1 2

CX0312 0.1UF/16VC X0312 0.1UF/16V

1 2

CX0311 0.1UF/16VC X0311 0.1UF/16V

1 2

CX0310 0.1UF/16VC X0310 0.1UF/16V

1 2

CX0309 0.1UF/16VC X0309 0.1UF/16V

1 2

CX0308 0.1UF/16VC X0308 0.1UF/16V

1 2

CX0307 0.1UF/16VC X0307 0.1UF/16V

1 2

CX0306 0.1UF/16VC X0306 0.1UF/16V

1 2

CX0305 0.1UF/16VC X0305 0.1UF/16V

1 2

CX0304 0.1UF/16VC X0304 0.1UF/16V

1 2

CX0303 0.1UF/16VC X0303 0.1UF/16V

1 2

CX0302 0.1UF/16VC X0302 0.1UF/16V

1 2

CX0301 0.1UF/16VC X0301 0.1UF/16V

1 2

CX0332 0.1UF/16VC X0332 0.1UF/16V

1 2

CX0331 0.1UF/16VC X0331 0.1UF/16V

1 2

CX0330 0.1UF/16VC X0330 0.1UF/16V

1 2

CX0329 0.1UF/16VC X0329 0.1UF/16V

1 2

CX0328 0.1UF/16VC X0328 0.1UF/16V

1 2

CX0327 0.1UF/16VC X0327 0.1UF/16V

1 2

CX0326 0.1UF/16VC X0326 0.1UF/16V

1 2

CX0325 0.1UF/16VC X0325 0.1UF/16V

1 2

CX0324 0.1UF/16VC X0324 0.1UF/16V

1 2

CX0323 0.1UF/16VC X0323 0.1UF/16V

1 2

CX0322 0.1UF/16VC X0322 0.1UF/16V

1 2

CX0321 0.1UF/16VC X0321 0.1UF/16V

1 2

CX0320 0.1UF/16VC X0320 0.1UF/16V

1 2

CX0319 0.1UF/16VC X0319 0.1UF/16V

1 2

CX0318 0.1UF/16VC X0318 0.1UF/16V

1 2

CX0317 0.1UF/16VC X0317 0.1UF/16V

1 2

PCIENB_RXN[15:0] (75)

R0370,R0371,R0372 near U0301

PCIENB_RXP[15:0] (75)

For EC request, to read PECI via EC.

Connection: R0317.2-->Q0301.1-->U3001.118

PCIEG_RXN15

PCIEG_RXN14

PCIEG_RXN13

PCIEG_RXN12

PCIEG_RXN11

PCIEG_RXN10

PCIEG_RXN9

PCIEG_RXN8

PCIEG_RXN7

PCIEG_RXN6

PCIEG_RXN5

PCIEG_RXN4

PCIEG_RXN3

PCIEG_RXN2

PCIEG_RXN1

PCIEG_RXN0

PCIEG_RXP15

PCIEG_RXP14

PCIEG_RXP13

PCIEG_RXP12

PCIEG_RXP11

PCIEG_RXP10

PCIEG_RXP9

PCIEG_RXP8

PCIEG_RXP7

PCIEG_RXP6

PCIEG_RXP5

PCIEG_RXP4

PCIEG_RXP3

PCIEG_RXP2

PCIEG_RXP1

PCIEG_RXP0

PCIEG_RXN[15:0] (75)

PCIEG_RXP[15:0] (75)

3

2

1

Main Board

U0301B

12

C0304

C0304

@

@

0.1UF/10V

0.1UF/10V

AT23

AT24

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

G16

U0301B

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

SOCKET989

SOCKET989

MISC THERMAL

MISC THERMAL

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

SM_DRAMRST#

PM_EXT_TS#[0]

PM_EXT_TS#[1]

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TCK

TMS

TDI

TDO

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

+VTT_CPU

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

CLKDREF

CLKDREF#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

R0331 100Ohm1%R0331 100Ohm1%

R0332 24.9Ohm1%R0332 24.9Ohm1%

R0333 130Ohm1%R0333 130Ohm1%

PM_EXTTS#1

RN0301A 10KOhmRN0301A 10KOhm

RN0301B 10KOhmRN0301B 10KOhm

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

BCLK_CPU_P_PCH (25)

BCLK_CPU_N_PCH (25)

CLK_ITP_BCLK (7)

CLK_ITP_BCLK# (7)

CLK_DMI_PCH (21)

1 2

1 2

1 2

12

34

CLK_DMI#_PCH (21)

12

12

M_DRAMRST# (16,17)

PM_EXTTS#0 (16,17)

XDP_PRDY# (7)

XDP_PREQ# (7)

XDP_TCLK (7)

XDP_TMS (7)

XDP_TRST# (7)

IPU

IPU

XDP_DBRESET# (7,22)

R0366 1KOhmR0366 1KOhm

R0367 1KOhmR0367 1KOhm

5 6

10KOhm

10KOhm

7 8

10KOhm

10KOhm

IPU

RN0301C

RN0301C

RN0301D

RN0301D

IPU

IPU

IPU

IPU

XDP_OBS[7:0] (7)

R0303 20Ohm1%R0303 20Ohm1%

R0304 20Ohm1%R0304 20Ohm1%

R0305 49.9Ohm1%R 0305 49.9Ohm1%

R0306 49.9Ohm1%R 0306 49.9Ohm1%

+VTT_CPU

R0307 49.9Ohm1%R 0307 49.9Ohm1%

H_PECI(25)

H_THRMTRIP#(32)

H_XDPRST#(7)

PM_SYNC#(22)

H_CPUPWRGD(7,25)

H_DRAM_PWRGD(22)

H_VTTPWRGD(32)

H_PWRGD_XDP(7)

BUF_PLT_RST#(24,30,32,41,53,75)

R0318

R0318

1 2

1.5KOhm 1%

1.5KOhm 1%

12

12

12

12

T0301T0301

12

H_PROCHOT_S#

PLT_RST#_R

12

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKTOCC#

1

H_CATERR#

R0319

R0319

1%

1%

750Ohm

750Ohm

+VTT_CPU

H_CPUPWRGD

B B

H_DRAM_PWRGD

H_VTTPWRGD

C0301 0.1UF/10V@C0301 0.1UF/10V@

12

C0302 0.1UF/10V@C0302 0.1UF/10V@

12

C0303 0.1UF/10V@C0303 0.1UF/10V@

12

Stuff these res istors for disa ble IGPU

DRAMPWROK: (WW35 MoW)

FDI_FSYNC0

R0398 1KOhm@R0398 1KOhm@

1 2

FDI_FSYNC1

R0397 1KOhm@R0397 1KOhm@

1 2

FDI_LSYNC0

R0396 1KOhm@R0396 1KOhm@

1 2

FDI_LSYNC1

R0395 1KOhm@R0395 1KOhm@

1 2

FDI_INT

R0399 1KOhm@R0399 1KOhm@

1 2

A A

5

4

Choose either one solution: -->Choose solution 2

1. This pin should have an external pull-up of 1K Ohms

to 10K Ohms to a rail of 1.05/1.1V which is ON in S0-S3

2. Connect this pin through a voltage divider circuit;

recommend 4.75K Ohms pull- up to DDR3 Power Rail

(VDDQ) of +V1.5U and a 12K Ohms pull-down to

ground to convert to processor’s VTT level.

+1.5V

R0320

R0320

1%

1%

1.1KOHM

1.1KOHM

H_DRAM_PWRGD

1 2

12

R0321

R0321

1%

1%

3KOhm

3KOhm

3

H_XDPRST#

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

XDP_TRST#

H_PROCHOT_S#

R0313 68OHM@R0313 68OHM@

R0345 51Ohm@R0345 51Ohm@

R0346 51Ohm@R0346 51Ohm@

R0347 51Ohm@R0347 51Ohm@

R0348 51Ohm@R0348 51Ohm@

R0354 49.9Ohm1%R0354 49.9Ohm1%

+VTT_CPU

12

32

3

3

D

D

S

S

2

2

1 2

1 2

1 2

1 2

1 2

R0322

R0322

68OHM

68OHM

Q0301

Q0301

2N7002

2N7002

1

1

1

G

G

12

THRO_CPU (30)

2

JTAG MAPPING

XDP_TDI_R

XDP_TDO_M

XDP_TDI_M

XDP_TDO_R

R0349 0Ohm/XDPR 0349 0Ohm/XDP

1 2

R0350 0Ohm

R0350 0Ohm

1 2

@

12

@

R0351

R0351

0Ohm

0Ohm

/XDP

/XDP

R0352 0Ohm@R0352 0Ohm@

1 2

R0353 0Ohm/XDPR 0353 0Ohm/XDP

1 2

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Engineer:

Engineer:

M60JV

M60JV

M60JV

1

XDP_TDI (7)

XDP_TDO (7)

Title :

Title :

Title :

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

CH_Lin

CH_Lin

CH_Lin

Rev

Rev

Rev

1.01

1.01

1.01

3 96Thursday, November 12, 2009

3 96Thursday, November 12, 2009

3 96Thursday, November 12, 2009

5

4

3

2

1

Main Board

U0301C

U0301C

U0301D

U0301D

AA6

SA_CK[0]

M_A_DQ[63:0](16)

D D

C C

B B

M_A_DQ0

A10

AM10

AR11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AR14

AP14

AJ10

AL10

AK12

AK11

AL11

AL13

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0(16)

M_A_BS1(16)

M_A_BS2(16)

M_A_CAS#(16)

M_A_RAS#(16)

M_A_WE#(16)

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 (16)

M_CLK_DDR#0 (16)

M_CKE0 (16)

M_CLK_DDR1 (16)

M_CLK_DDR#1 (16)

M_CKE1 (16)

M_CS#0 (16)

M_CS#1 (16)

M_ODT0 (16)

M_ODT1 (16)

M_A_DM[7:0] (16)

M_A_DQS#[7:0] (16)

M_A_DQS[7:0] (16)

M_A_A[15:0] (16)

M_B_DQ[63:0](17)

M_B_DQ0

B5

AR10

AT10

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0(17)

M_B_BS1(17)

M_B_BS2(17)

M_B_CAS#(17)

M_B_RAS#(17)

M_B_WE#(17)

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

M_B_DM0

D4

M_B_DM1

E1

M_B_DM2

H3

M_B_DM3

K1

M_B_DM4

AH1

M_B_DM5

AL2

M_B_DM6

AR4

M_B_DM7

AT8

M_B_DQS#0

D5

M_B_DQS#1

F4

M_B_DQS#2

J4

M_B_DQS#3

L4

M_B_DQS#4

AH2

M_B_DQS#5

AL4

M_B_DQS#6

AR5

M_B_DQS#7

AR8

M_B_DQS0

C5

M_B_DQS1

E3

M_B_DQS2

H4

M_B_DQS3

M5

M_B_DQS4

AG2

M_B_DQS5

AL5

M_B_DQS6

AP5

M_B_DQS7

AR7

M_B_A0

U5

M_B_A1

V2

M_B_A2

T5

M_B_A3

V3

M_B_A4

R1

M_B_A5

T8

M_B_A6

R2

M_B_A7

R6

M_B_A8

R4

M_B_A9

R5

M_B_A10

AB5

M_B_A11

P3

M_B_A12

R3

M_B_A13

AF7

M_B_A14

P5

M_B_A15

N1

M_CLK_DDR2 (17)

M_CLK_DDR#2 (17)

M_CKE2 (17)

M_CLK_DDR3 (17)

M_CLK_DDR#3 (17)

M_CKE3 (17)

M_CS#2 (17)

M_CS#3 (17)

M_ODT2 (17)

M_ODT3 (17)

M_B_DM[7:0] (17)

M_B_DQS#[7:0] (17)

M_B_DQS[7:0] (17)

M_B_A[15:0] (17)

SOCKET989

SOCKET989

SOCKET989

SOCKET989

A A

Title :

Title :

Title :

CPU(2)_DDR3

CPU(2)_DDR3

CPU(2)_DDR3

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

1

CH_Lin

4 96Thursday, November 12, 2009

4 96Thursday, November 12, 2009

4 96Thursday, November 12, 2009

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

Main Board

D D

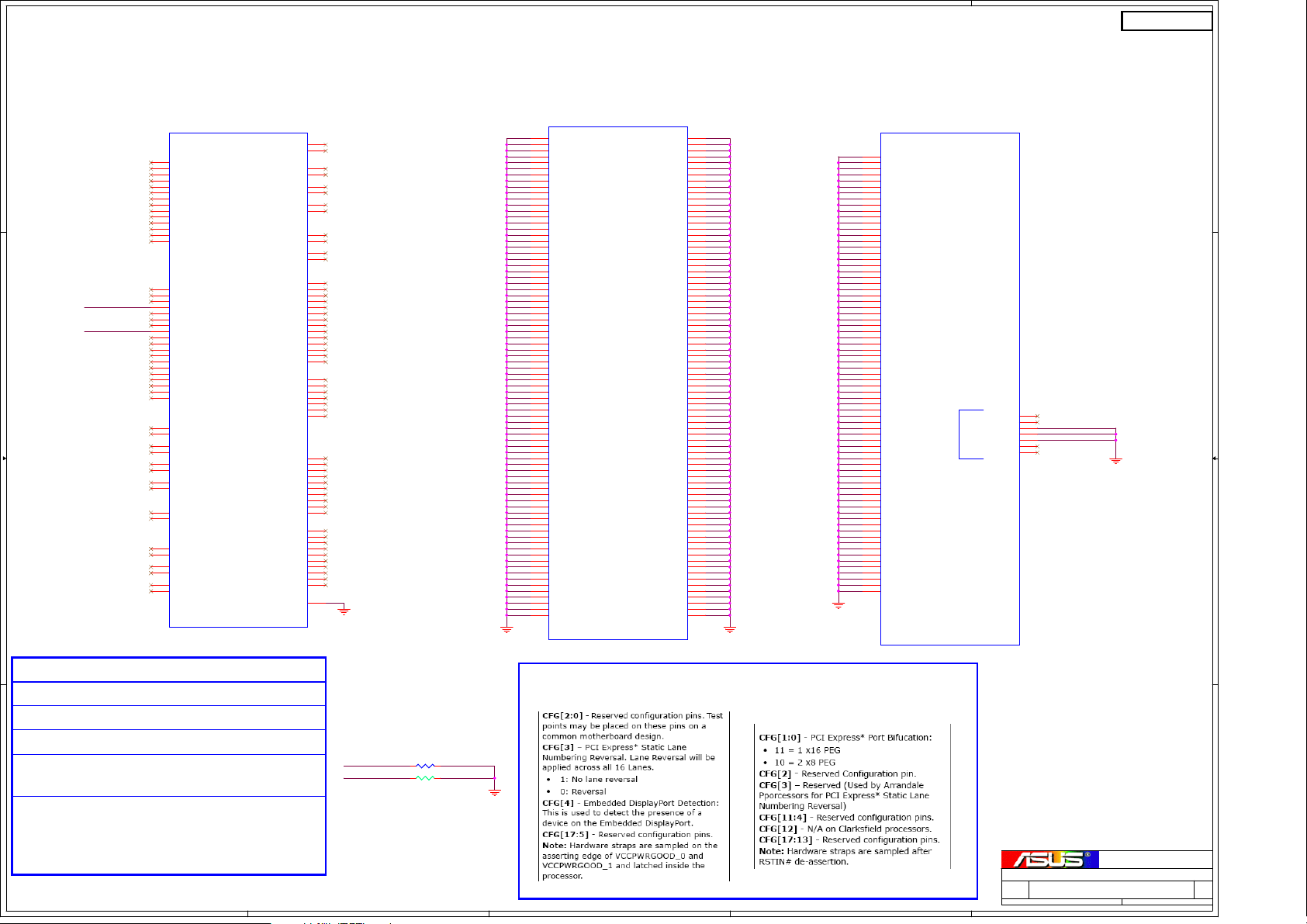

CFG[0:17] : IPU

CFG3

CFG7

C C

B B

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

AC9

AB9

J29

J28

A34

A33

C35

B35

U9

T9

C1

A3

U0301E

U0301E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

SOCKET989

SOCKET989

AJ13

RSVD32

AJ12

RSVD33

AH25

RSVD34

AK26

RSVD35

AL26

RSVD36

AR2

RSVD37

AJ26

RSVD38

AJ27

RSVD39

AP1

RSVD40

AT2

RSVD41

AT3

RSVD42

AR1

RSVD43

AL28

RSVD45

AL29

RSVD46

AP30

RSVD47

AP32

RSVD48

AL27

RSVD49

AT31

RSVD50

AT32

RSVD51

AP33

RSVD52

AR33

RSVD53

AT33

RSVD54

AT34

RSVD55

AP35

RSVD56

AR35

RSVD57

AR32

RSVD58

E15

RSVD59

F15

RSVD60

RSVD61

RSVD62

RSVD63

RSVD64

RSVD65

RSVD66

RSVD67

RSVD68

RSVD69

RSVD70

RSVD71

RSVD72

RSVD73

RSVD74

RSVD75

RSVD76

RSVD77

RSVD78

RSVD79

RSVD80

RSVD81

RSVD82

RSVD83

RSVD84

RSVD85

RSVD86

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

RESERVED

RESERVED

CFG strapping information:

CFG[1:0]: PCI Express Port Bifurcation:(Clarksfield Only)

- 11 = 1 x 16 PEG (Default)

- 10 = 2 x 8 PEG

CFG[3]: PCIE Static Numbering Lane Reversal.(Arrandale Only)

- 1:Normal Operation (Default)

- 0:Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

CFG[4]: Embedded DisplayPort Detection.(Arrandale Only)

- 1:Disabled - No Physical Display Port attached to Embedded DisplayPort

- 0:Enabled - An external Display Port device is connected to the Embedded Display Port

CFG[7]: Fixed for PCI Express 2.0 jitter specifications.(Clarksfi eld)

Clarksfield (only for early samples pre-ES1) - Connect to GND with 3.01K Ohm /5% resistor

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not impact Arrandale functionality.

Unmount if Intel has fixed this issue.

A A

CFG3

R0544 3KOhm1%R0544 3KOhm1%

CFG7

1 2

R0538 3KOhm 1% @R0538 3KOhm 1% @

12

AT20

AT17

AR31

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AP20

AP17

AP13

AP10

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

U0301H

AR9

AR6

AR3

AP7

AP4

AP2

AM8

AM5

AM2

AL9

AL6

AL3

AJ8

AJ5

AJ2

AH9

AH6

AH3

AF8

AF4

AF2

U0301H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

SOCKET989

SOCKET989

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

CFG strapping information:

For Arrandale For Clarksfield

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

U0301I

U0301I

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

SOCKET989

SOCKET989

VSS

VSS

AT35

VSS_NCTF1

AT1

VSS_NCTF2

AR34

VSS_NCTF3

B34

VSS_NCTF4

B2

VSS_NCTF5

B1

VSS_NCTF6

A35

VSS_NCTF7

NCTF

NCTF

Note: (Auburndale)Hardware Straps are sampled on

the asserting edge of VCCPWRGOOD_0 and

VCCPWRGOOD_1 and latched inside the processor.

Note: (Clarksfield)Hardware Straps are sampled

after RSTIN# de-assertion.

5

Title :

Title :

Title :

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

1

CH_Lin

5 96Thursday, November 12, 2009

5 96Thursday, November 12, 2009

5 96Thursday, November 12, 2009

Rev

Rev

Rev

1.01

1.01

1.01

5

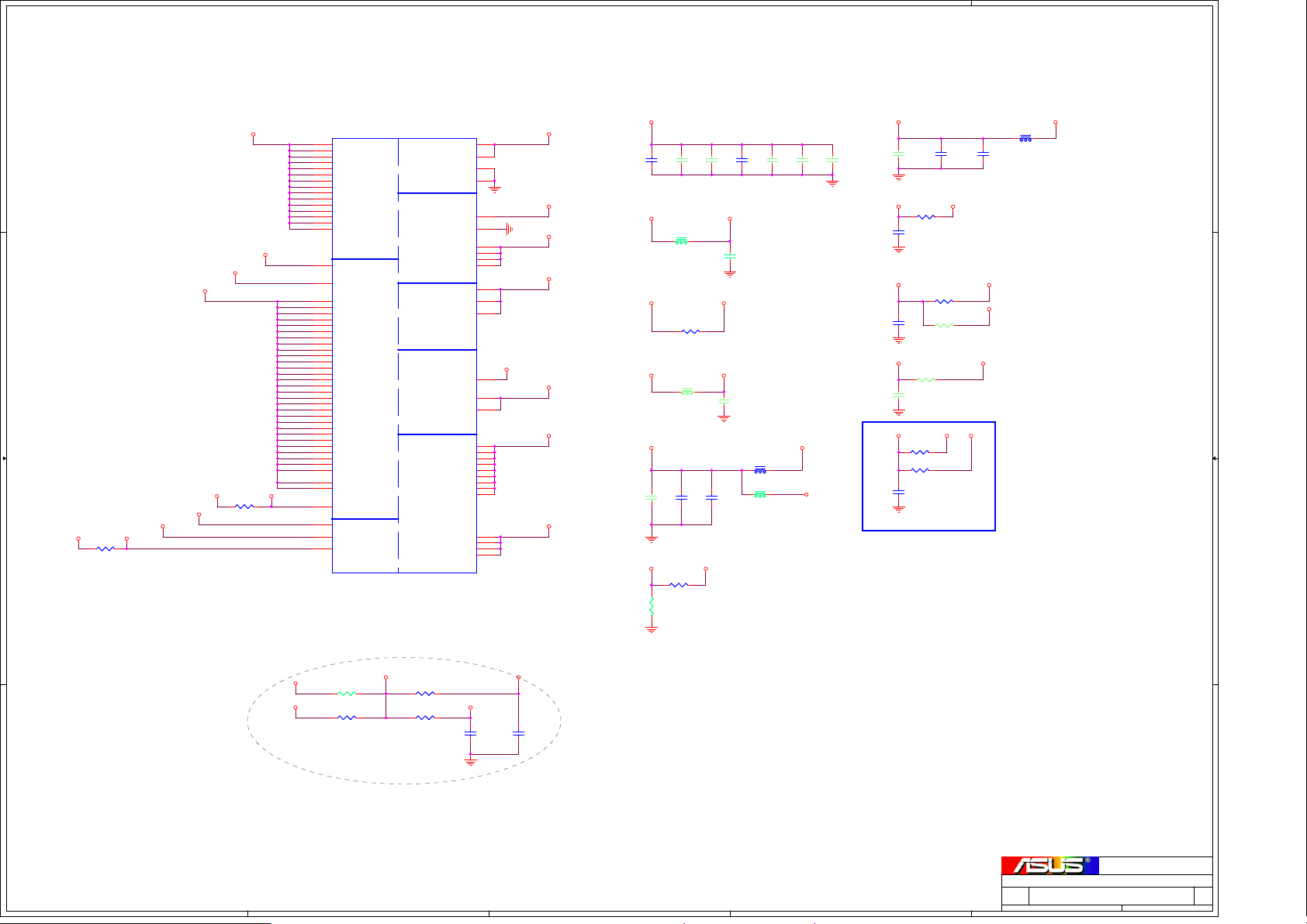

U0301F

U0301F

+VCORE

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

Max 48A

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

SOCKET989

SOCKET989

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

D D

C C

B B

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

PSI#

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

VTT_TEST TBD

AN35

AJ34

AJ35

B15

A15

Max 18A

+VTT_CPU

VTT_SELECT

I_MON (88)

VTT_SENSE

TP_VSS_SENSE_VTT

PM_PSI# (88)

PM_DPRSLPVR (88)

1

VCCSENSE (88)

VSSSENSE (88)

1

1

VR_VID0 (88)

VR_VID1 (88)

VR_VID2 (88)

VR_VID3 (88)

VR_VID4 (88)

VR_VID5 (88)

VR_VID6 (88)

T633T633

T0632T0632

T0631T0631

4

+VGFX_CORE

+VTT_CPU

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

J24

J23

H25

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

U0301G

U0301G

VCCAXG1

VCCAXG2

VCCAXG3

VCCAXG4

VCCAXG5

VCCAXG6

VCCAXG7

VCCAXG8

VCCAXG9

VCCAXG10

VCCAXG11

VCCAXG12

VCCAXG13

VCCAXG14

VCCAXG15

VCCAXG16

VCCAXG17

VCCAXG18

VCCAXG19

VCCAXG20

VCCAXG21

VCCAXG22

VCCAXG23

VCCAXG24

VCCAXG25

VCCAXG26

VCCAXG27

VCCAXG28

VCCAXG29

VCCAXG30

VCCAXG31

VCCAXG32

VCCAXG33

VCCAXG34

VCCAXG35

VCCAXG36

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

VTT52

VTT53

VTT54

VTT55

VTT56

VTT57

VTT58

SOCKET989

SOCKET989

3

2

1

Main Board

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT59

VTT60

VTT61

VTT62

VTT63

VTT64

VTT65

VTT66

VTT67

VTT68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

VCCAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GRAPHICS

GRAPHICS

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

GVR_VID0

GVR_VID1

GVR_VID2

GVR_VID3

GVR_VID4

GVR_VID5

GVR_VID6

+1.5V

+VTT_CPU

Imax=1.35A

12

C0628

C0628

0.1UF/16V

0.1UF/16V

VCC_AXG_SENSE (92)

VSS_AXG_SENSE (92)

GVR_VID[0:6] (92)

R0605 4.7KOhmR0605 4.7KOhm

1 2

GVR_PWR_MON (92)

GVR_PWR_MON

R0613 1KOhmR0613 1KOhm

12

12

C0629

C0629

1UF/10V

1UF/10V

GFXVR_DPRSLPVR (92)

R0606 4.7KOhmR0606 4.7KOhm

1 2

1 2

PL0601

PL0601

21

70Ohm/100Mhz

70Ohm/100Mhz

C0667

C0667

10UF/6.3V

10UF/6.3V

GFX_VRON (87,92)

+1.8VS+1.8VS_HPLL

12

C7113

C7113

@

@

0.1UF/10V

0.1UF/10V

+VTT_CPU

Processor Decoupling

Decoupling guide from Intel

Schematic R0.9: Schematic Checklist R0.7:

VCORE 22uF * 16pcs

10uF * 16pcs

+VCORE

+VGFX_CORE

12

C0650

C0650

22UF/6.3V

22UF/6.3V

+1.5V

12

C0621

C0621

N/A

N/A

27PF/50V

27PF/50V

12

12

C0617

C0617

@

@

22UF/6.3V

22UF/6.3V

C0613

C0613

10UF/6.3V

10UF/6.3V

470uF* 6pcs(2 no stuff).

12

12

12

C0633

C0633

C0632

C0632

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

12

12

C0641

C0641

C0640

C0640

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

8/5 delete C0646 (22UF,6.3V) for layout placement.

(+1.8VS,VCCPLL)

12

12

C0678

C0678

C0677

C0677

@

@

@

@

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

12

12

C0648

C0648

C0651

C0651

@

@

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

12

C0622

C0622

1UF/10V

1UF/10V

Intel use 22u

12

C0618

C0618

@

@

22UF/6.3V

22UF/6.3V

12

C0615

C0615

@

@

10UF/6.3V

10UF/6.3V

12

C0623

C0623

N/A

N/A

27PF/50V

27PF/50V

12

12

12

C0655

C0655

@

@

22UF/6.3V

22UF/6.3V

C0616

C0616

@

@

10UF/6.3V

10UF/6.3V

12

12

12

C0624

C0624

@

@

1UF/10V

1UF/10V

C0634

C0634

22UF/6.3V

22UF/6.3V

C0642

C0642

22UF/6.3V

22UF/6.3V

C0671

C0671

@

@

10UF/6.3V

10UF/6.3V

C0679

C0679

@

@

10UF/6.3V

10UF/6.3V

12

C0649

C0649

22UF/6.3V

22UF/6.3V

12

12

12

12

12

12

C0625

C0625

1UF/10V

1UF/10V

C0656

C0656

@

@

22UF/6.3V

22UF/6.3V

C0687

C0687

@

@

10UF/6.3V

10UF/6.3V

C0635

C0635

22UF/6.3V

22UF/6.3V

C0643

C0643

22UF/6.3V

22UF/6.3V

C0680

C0680

@

@

10UF/6.3V

10UF/6.3V

12

C0619

C0619

@

@

10UF/6.3V

10UF/6.3V

12

VCORE 22uF * 12pcs

10uF * 16pcs

470uF* 6pcs(2 no stuff).

12

C0636

C0636

22UF/6.3V

22UF/6.3V

12

C0644

C0644

22UF/6.3V

22UF/6.3V

12

C0673

C0673

@

@

10UF/6.3V

10UF/6.3V

12

C0681

C0681

@

@

10UF/6.3V

10UF/6.3V

12

C0620

C0620

10UF/6.3V

10UF/6.3V

12

C0685

C0685

C0686

C0686

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

12

C0657

C0657

@

@

22UF/6.3V

22UF/6.3V

12

C0688

C0688

@

@

10UF/6.3V

10UF/6.3V

12

12

C0637

C0637

22UF/6.3V

22UF/6.3V

12

C0645

C0645

22UF/6.3V

22UF/6.3V

12

12

C0674

C0674

@

@

10UF/6.3V

10UF/6.3V

12

12

C0682

C0682

@

@

10UF/6.3V

10UF/6.3V

12

CE0604

CE0604

+

+

@

@

330UF/2V

330UF/2V

PANASONIC/EEFSX0D331XE

PANASONIC/EEFSX0D331XE

ESR=6mOhm/Ir=3A

ESR=6mOhm/Ir=3A

12

C0626

C0626

10UF/6.3V

10UF/6.3V

C0638

C0638

22UF/6.3V

22UF/6.3V

C0675

C0675

@

@

10UF/6.3V

10UF/6.3V

C0683

C0683

@

@

10UF/6.3V

10UF/6.3V

Intel use 22u

12

12

12

12

12

C0627

C0627

@

@

10UF/6.3V

10UF/6.3V

C0639

C0639

22UF/6.3V

22UF/6.3V

C0647

C0647

22UF/6.3V

22UF/6.3V

C0676

C0676

@

@

10UF/6.3V

10UF/6.3V

C0684

C0684

@

@

10UF/6.3V

10UF/6.3V

12

C0654

C0654

10UF/6.3V

10UF/6.3V

A A

5

4

3

2

12

C0601

C0601

@

@

10UF/6.3V

10UF/6.3V

12

C0602

C0602

@

@

10UF/6.3V

10UF/6.3V

12

C0604

C0604

@

@

10UF/6.3V

10UF/6.3V

12

C0606

C0606

@

@

10UF/6.3V

10UF/6.3V

12

C0611

C0611

@

@

10UF/6.3V

10UF/6.3V

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

12

C0665

C0665

10UF/6.3V

10UF/6.3V

M60JV

M60JV

M60JV

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

12

C0664

C0664

10UF/6.3V

10UF/6.3V

12

C0658

C0658

10UF/6.3V

10UF/6.3V

Intel use 22uIntel use 22u

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

CH_Lin

CH_Lin

CH_Lin

6 96Thursday, November 12, 2009

6 96Thursday, November 12, 2009

6 96Thursday, November 12, 2009

12

C0659

C0659

10UF/6.3V

10UF/6.3V

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

Main Board

D D

C C

CPU XDP connector

XDP1

XDP1

1

2

1

2

3

XDP_PREQ#(3)

XDP_PRDY#(3)

XDP_OBS0(3)

XDP_OBS1(3)

XDP_OBS2(3)

B B

H_CPUPWRGD(3,25)

H_PWRGD_XDP(3)

Update 1105 (R2 .0)

A A

5

XDP_OBS3(3)

XDP_OBS4(3)

XDP_OBS5(3)

XDP_OBS6(3)

XDP_OBS7(3)

R0708 1KOhm/XDPR0708 1KOhm/XDP

R712 49.9Ohm/XD PR712 49.9Ohm/XDP

T0701T0701

XDP_TCLK(3)

CPUPWRGD_XDP

12

HOOK1

12

PCIE_CLK_XDP_P XDP_RST#_R

PCIE_CLK_XDP_N

1

SMB_DAT_XDP

T702T702

1

SMB_CLK_XDP

T703T703

1

4

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

31

31

33

33

35

35

37

37

39

39

41

41

43

43

45

45

47

47

49

49

51

51

53

53

55

55

57

57

59

59

61

NP_NC1

BtoB_CON_60P

BtoB_CON_60P

/XDP

/XDP

NP_NC2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

60

62

R0707 1KOhm/XDPR0707 1KOhm/XDP

3

1 2

XDP_TRST# (3)

XDP_TDI (3)

XDP_TMS (3)

CLK_ITP_BCLK (3)

CLK_ITP_BCLK# (3)

+VTT_CPU+VTT_CPU

H_XDPRST# (3)

1 2

R0711

R0711

49.9Ohm

49.9Ohm

/XDP

/XDP

XDP_DBRESET# (3,22)

XDP_TDO (3)

2

Title :

Title :

Title :

CPU(5)_XDP

CPU(5)_XDP

CPU(5)_XDP

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

1

CH_Lin

7 96Thursday, November 12, 2009

7 96Thursday, November 12, 2009

7 96Thursday, November 12, 2009

Rev

Rev

Rev

1.01

1.01

1.01

5

D D

C C

4

3

2

1

B B

A A

NB_****

NB_****

NB_****

Title :

Title :

Title :

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

CH_Lin

CH_Lin

CH_Lin

8 96Thursday, November 12, 2009

8 96Thursday, November 12, 2009

1

8 96Thursday, November 12, 2009

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

CH_Lin

Rev

Rev

Rev

1.01

1.01

9 96Thursday, November 12, 2009

9 96Thursday, November 12, 2009

1

9 96Thursday, November 12, 2009

1.01

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

CH_Lin

Rev

Rev

Rev

1.01

1.01

10 96Thursday, November 12, 2009

10 96Thursday, November 12, 2009

1

10 96Thursday, November 12, 2009

1.01

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

CH_Lin

Rev

Rev

Rev

1.01

1.01

11 96Thursday, November 12, 2009

11 96Thursday, November 12, 2009

1

11 96Thursday, November 12, 2009

1.01

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

CH_Lin

Rev

Rev

Rev

1.01

1.01

12 96Thursday, November 12, 2009

12 96Thursday, November 12, 2009

1

12 96Thursday, November 12, 2009

1.01

5

4

3

2

1

Main Board

D D

C C

B B

A A

Title :

Title :

Title :

NB_****

NB_****

NB_****

CH_Lin

CH_Lin

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

M60JV

M60JV

M60JV

CH_Lin

Rev

Rev

Rev

1.01

1.01

13 96Thursday, November 12, 2009

13 96Thursday, November 12, 2009

1

13 96Thursday, November 12, 2009

1.01

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB6

ASUSTeK COMPUTER INC. NB6

ASUSTeK COMPUTER INC. NB6

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Thursday, November 12, 2009

Date: Sheet of

Thursday, November 12, 2009

Date: Sheet of

5

4

3

Thursday, November 12, 2009

2

M60JV

M60JV

M60JV

Engineer:

CH_Lin

CH_Lin

CH_Lin

14 96

14 96

14 96

1

Rev

Rev

Rev

1.01

1.01

1.01

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB6

ASUSTeK COMPUTER INC. NB6

ASUSTeK COMPUTER INC. NB6

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Thursday, November 12, 2009

Date: Sheet of

Thursday, November 12, 2009

Date: Sheet of

5

4

3

Thursday, November 12, 2009

2

M60JV

M60JV

M60JV

Engineer:

CH_Lin

CH_Lin

CH_Lin

15 96

15 96

15 96

1

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

DIMM1A

M_A_A[15:0](4)

D D

M_A_BS0(4)

M_A_BS1(4)

M_A_BS2(4)

M_A_CAS#(4)

M_CLK_DDR#0(4)

M_CLK_DDR#1(4)

M_CLK_DDR0(4)

M_CLK_DDR1(4)

M_CKE0(4)

M_A_DM[7:0](4)

M_A_DQS[7:0](4)

C C

M_A_DQS#[7:0](4)

M_CKE1(4)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

DIMM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

115

CAS#

103

CK#0

104

CK#1

101

CK0

102

CK1

73

CKE0

74

CKE1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3_DIMM_204P

DDR3_DIMM_204P

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ0

5

DQ0

M_A_DQ1

7

DQ1

M_A_DQ2

15

DQ2

M_A_DQ3

17

DQ3

M_A_DQ4

4

DQ4

M_A_DQ5

6

DQ5

M_A_DQ6

16

DQ6

M_A_DQ7

18

DQ7

M_A_DQ8

21

DQ8

M_A_DQ9

23

DQ9

M_A_DQ10

33

M_A_DQ11

35

M_A_DQ12

22

M_A_DQ13

24

M_A_DQ14

34

M_A_DQ15

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ18

51

M_A_DQ19

53

M_A_DQ20

40

M_A_DQ21

42

M_A_DQ22

50

M_A_DQ23

52

M_A_DQ24

57

M_A_DQ25

59

M_A_DQ26

67

M_A_DQ27

69

M_A_DQ28

56

M_A_DQ29

58

M_A_DQ30

68

M_A_DQ31

70

M_A_DQ36

129

M_A_DQ33

131

M_A_DQ34

141

M_A_DQ35

143

M_A_DQ32

130

M_A_DQ37

132

M_A_DQ38

140

M_A_DQ39

142

M_A_DQ40

147

M_A_DQ41

149

M_A_DQ42

157

M_A_DQ45

159

M_A_DQ44