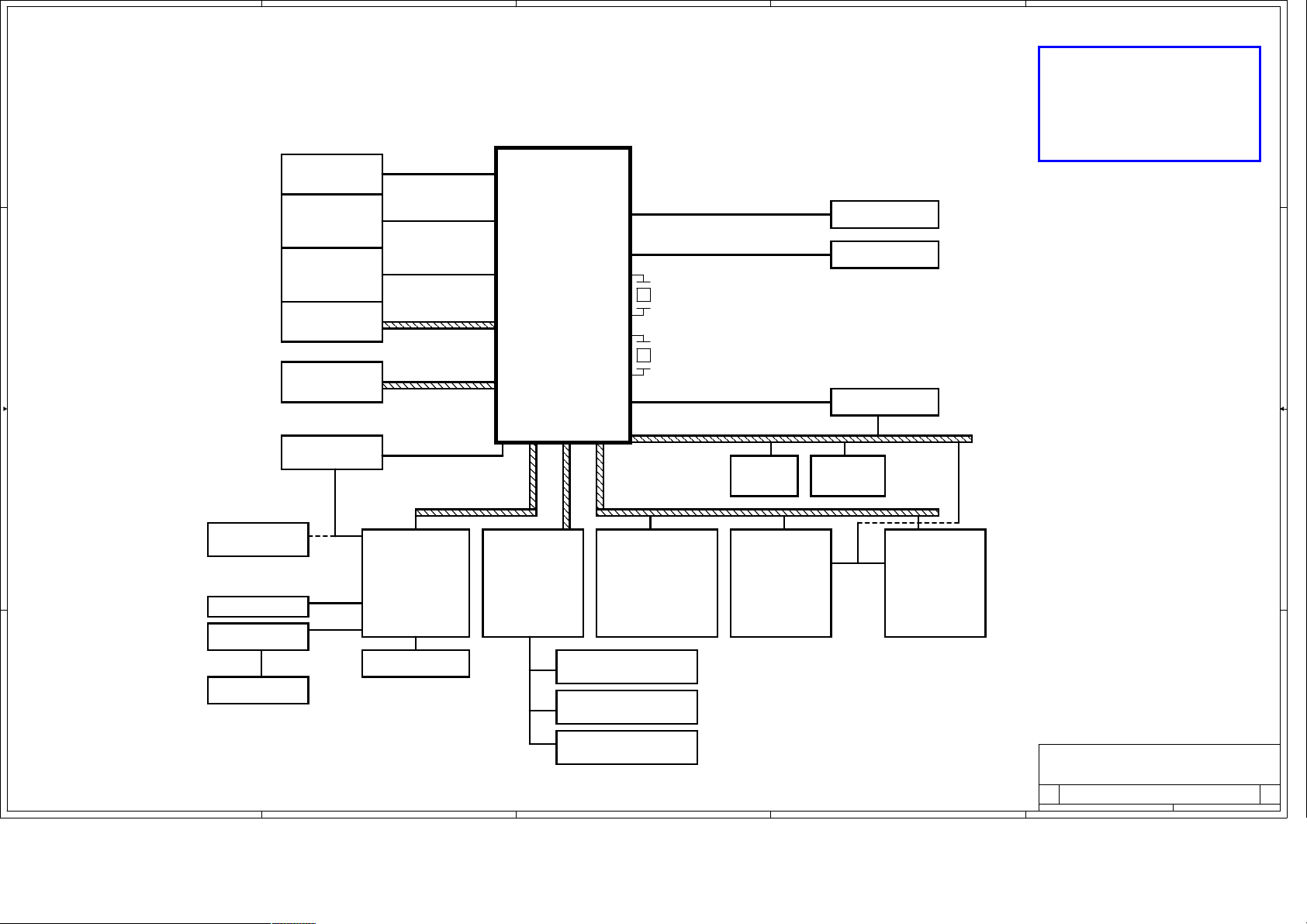

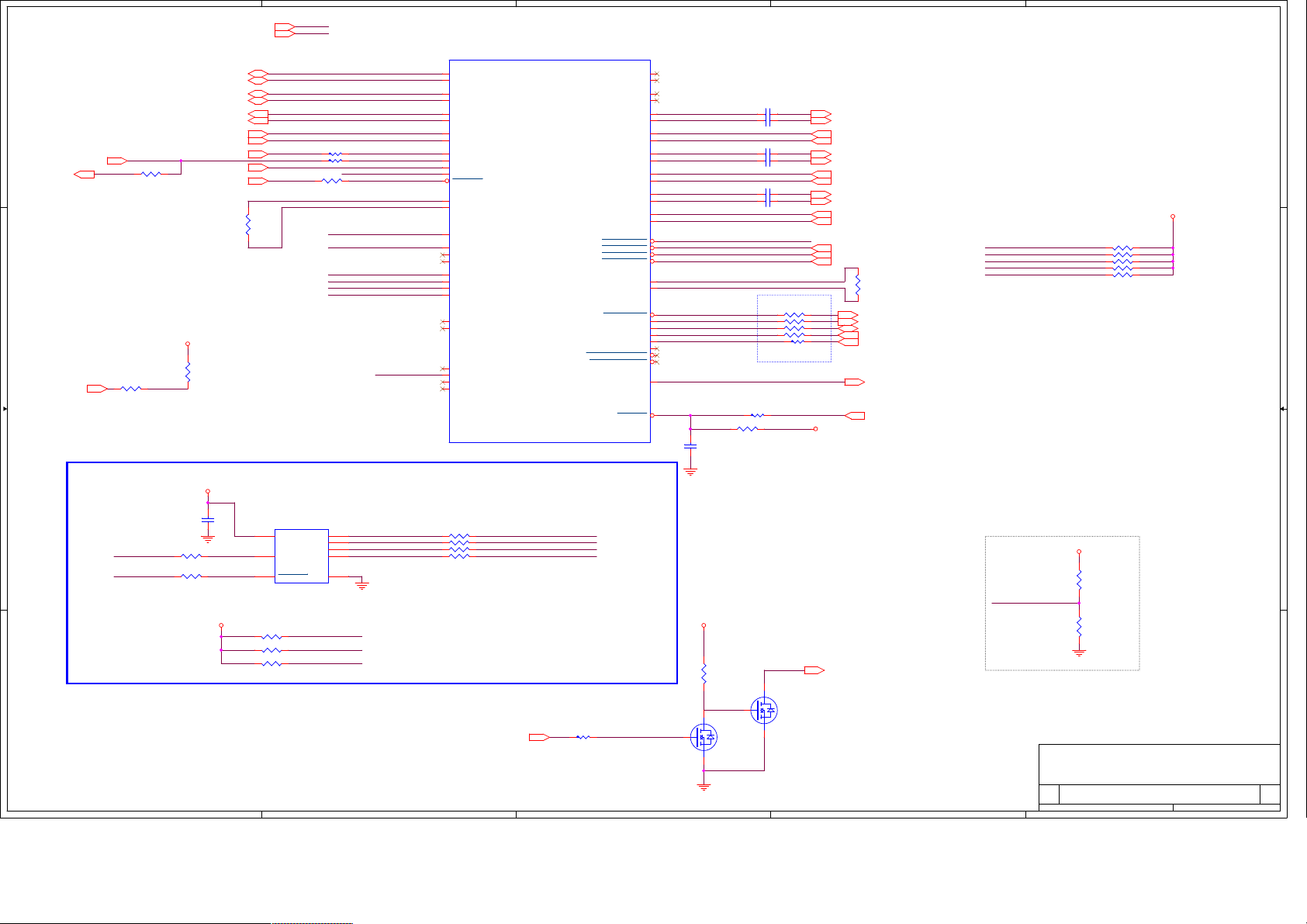

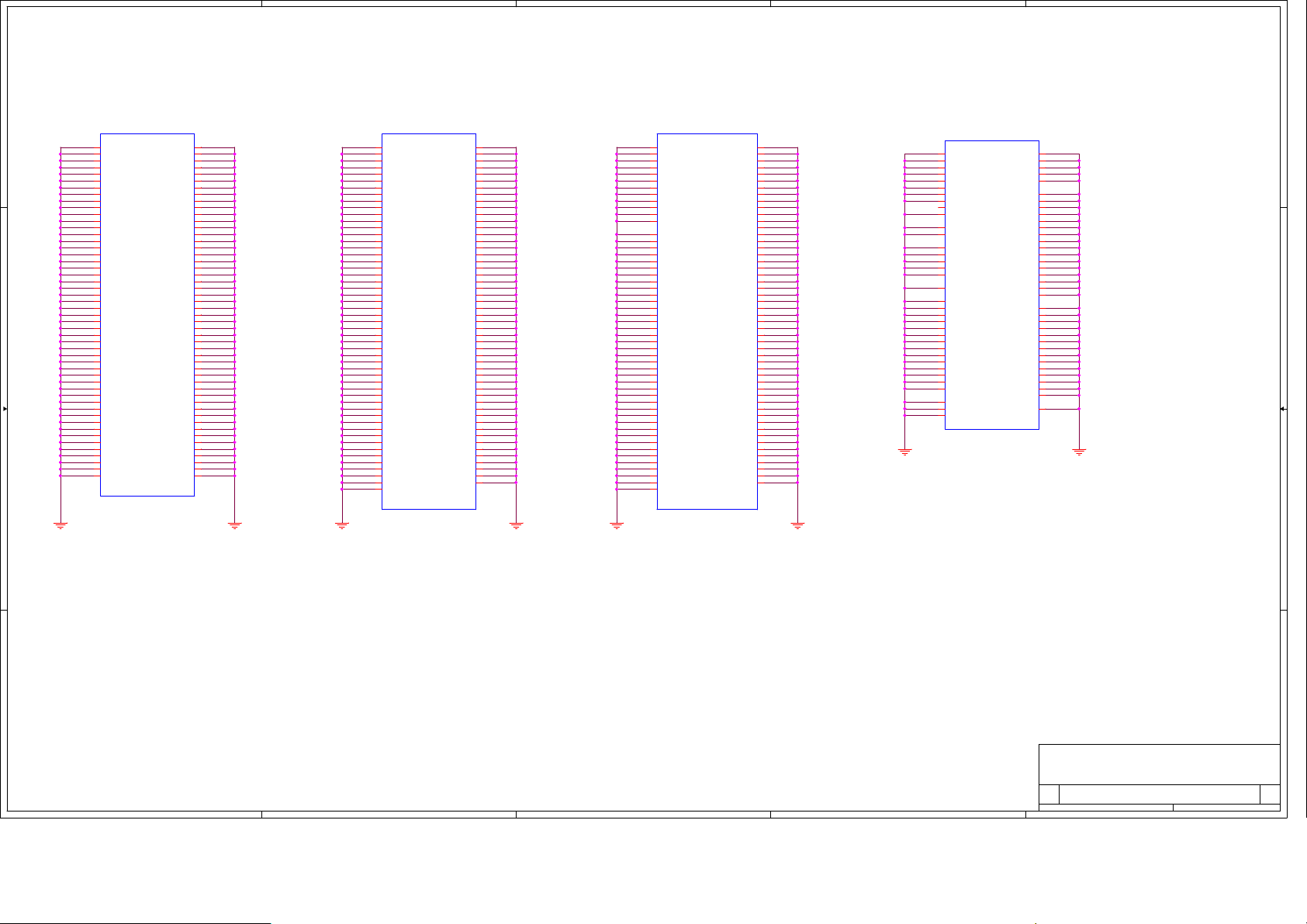

Acer ES1-431 Schematic

5

4

3

2

1

Z8AD UMA(14")

BOM

@ : EMMc

EM

D D

Intel Brasewll Platform Block Diagram

DDR3L SO-DIMM 0

Maximum 8GB

DDR3L

PAGE 11

EMMC 5.0

32GB/64GB

Card Reader

SDMMC1

SDMMC3

Intel Brasewll

Power : 7.5 Watt

Package : FCBG 1170

C C

SATA - HDD

Package : 9.5 (mm)

Power :

PAGE 16

SATA - ODD

Package : 9.5 (mm)

Power :

1.8V BIOS+TXE

SPI ROM(64Mb)

PAGE 16

PAGE 6

SATA0 3GB/s

SATA1 3GB/s

SPI Interface

Size : 25 x 27 (mm)

Int

PAGE 2~10

Az

alia

1

DDI

0

DDI

32.768KHz

PAGE 6

19.2 Mhz

PAGE 6

B3.0

US

USB 2.0 Interface

Port2

Camera

PAGE 13

B B

3.3V EC code

SPI ROM(1Mb)

PAGE 23

Embedded Controller

IT8987

Audio Codec

ALC255

PCIE Gen 2 x 1 LaneLPC Interface

Port3 Port2

LAN

Half Mini Card

Port3

RTL8111H-CG

eDP

HDMI Conn PAGE 13

Port0

USB3.0 Conn PAGE 18

Port1

USB2.0 Port

PAGE 18

PAGE 13

Port0

Port4

NGFF Card

HD@ : HDD

GS@ :G-sensor

TPM@ : TPM

TSI@ :TOUCH SCREEN I2C

SP@ :Special

Keyboard

Touch Pad

PAGE 15

PS2

Package : LQPF128

Size : 14 x 14 (mm)

PAGE 23

Package : QFN

Size : 6 x 6 (mm)

PAGE 19

Package : QFN

Size : x (mm)

PAGE 12

WLAN / BT Combo

PAGE 21

WLAN / BT Combo

PAGE 15

I2C

I2C from CPU

A A

5

FAN

Sp

PAGE 16

eaker

PAGE 19

Universal Jack

Headphone + MIC

alog MIC

An

4

3

PAGE 19

PAGE 19

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

Qu

Qu

Qu

PROJECT :

PROJECT :

Si

Si

Si

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

We

We

We

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

2

dnesday, April 08, 2015

PROJECT :

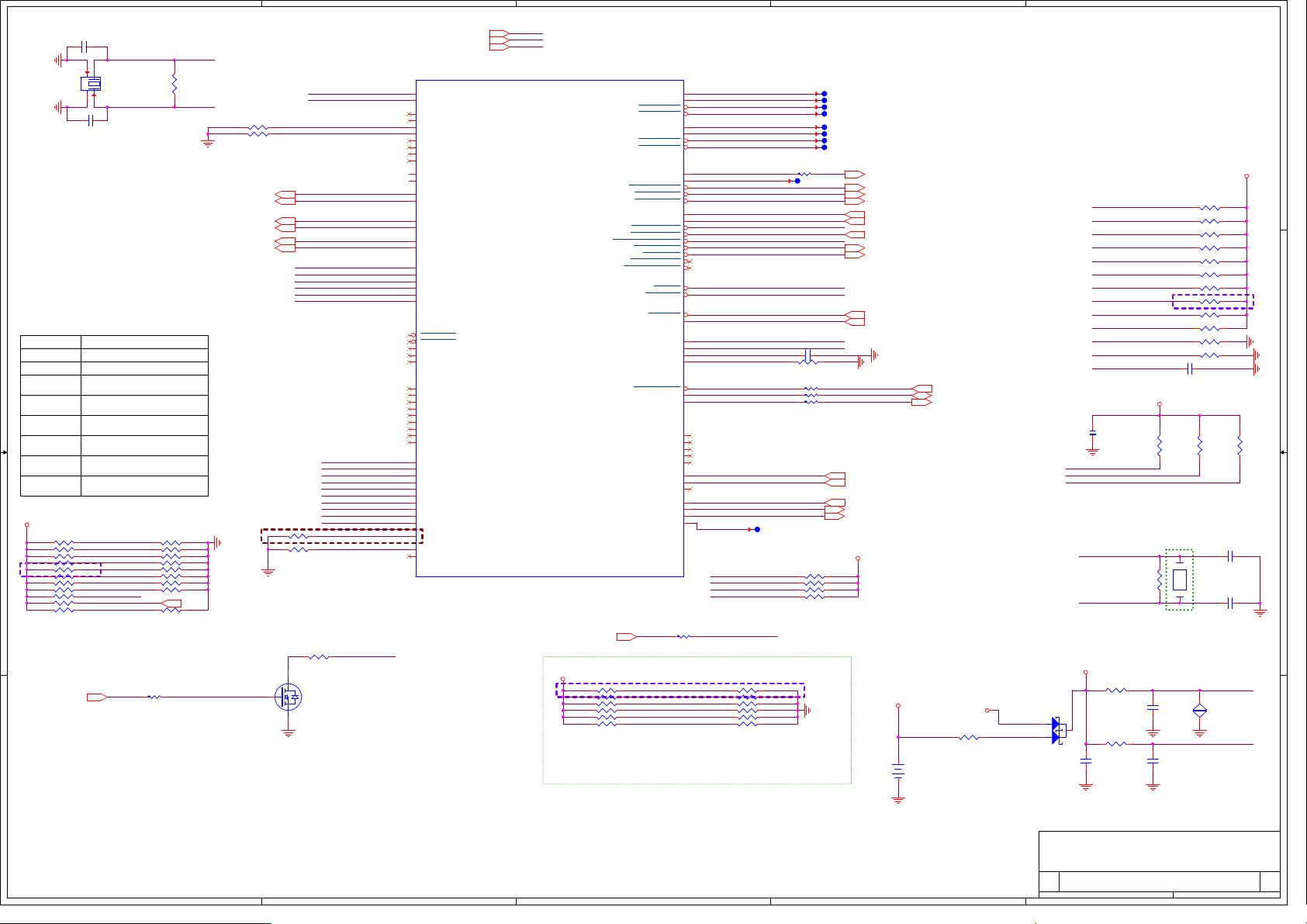

Intel Block Diagram

Intel Block Diagram

Intel Block Diagram

Z8AD

Z8AD

Z8AD

1A

1A

1A

of

321

of

321

of

1

321

5

+1

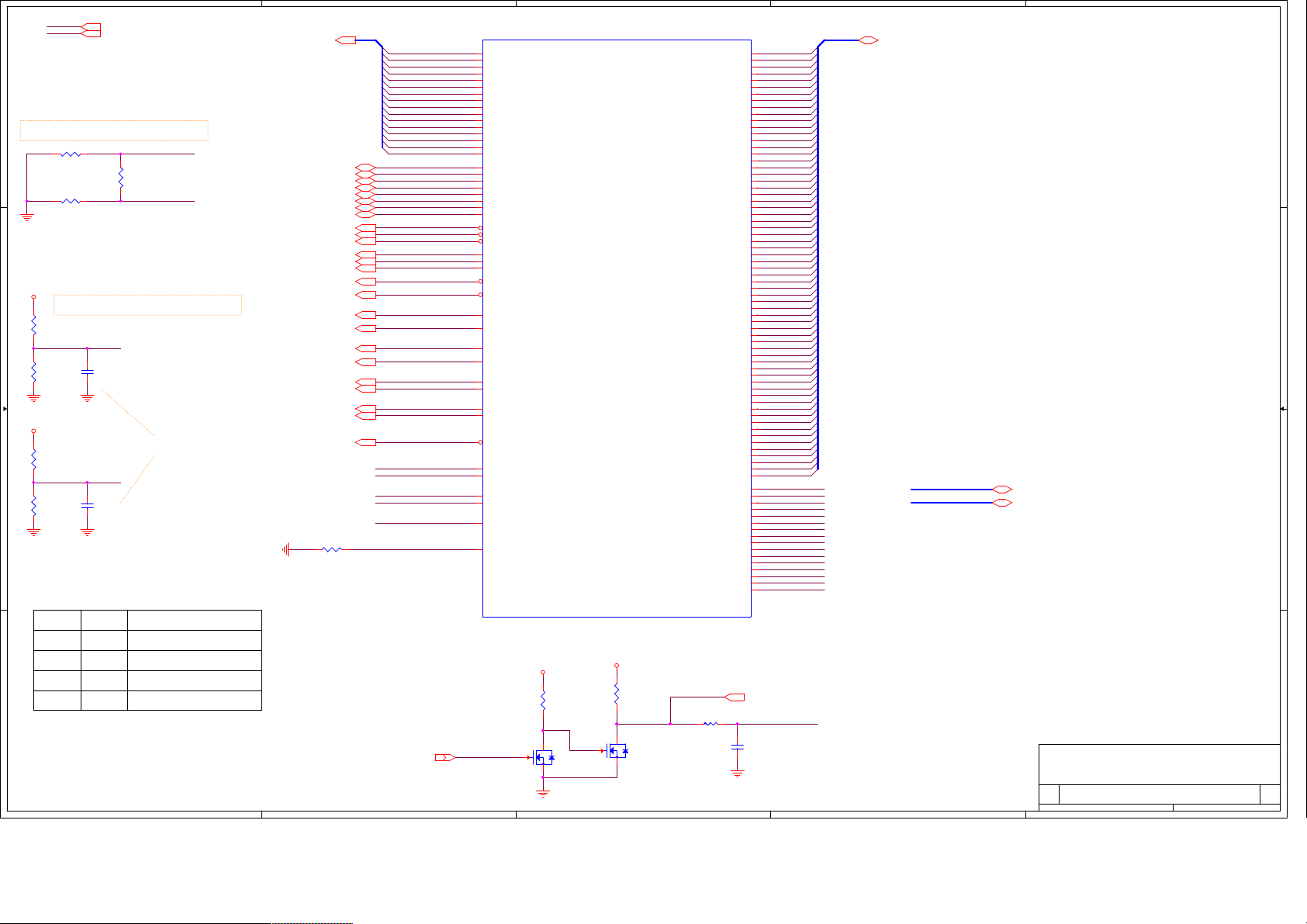

.35VSUS [3,9,11,27]

+3

V_S5 [3,5,9,12,14,15,16,22,26]

D D

PLACE THE RESISTORS AS CLOSE AS POSSIBLE TO SOC(BSW)

ROUTE THEM AS SINGLE ENDED LINES

12 *49.9_4

R2

13 *49.9_4

R2

D

GN

ROUTE ALL VREF POWER SIGNALS AS THICK TRACES

+1

.35VSUS

C C

B B

A A

PLACE TWO 4.7K RESISTORS CLOSE TO CPU PINS ON M_VREF

ROUTE THE VREF POWER SIGNALS WITH THICK TRACES

28

R2

*4.7K_4

A_VREF_CA

M_

03

A_VREF_DQ

M_

D

GN

D

GN

1333 MHz

1600 MHz

C2

*0.1U/16V_4

02

C2

*0.1U/16V_4

X

X

20

R2

*4.7K_4

D

GN

+1

.35VSUS

27

R2

*4.7K_4

19

R2

*4.7K_4

D

GN

Channel 0

1333 MHz

1600 MHz

1333 MHz

1600 MHz

Channel 0 need to

be populated first for the platform to power on

A_MON1P

M_

08

R2

*100_4

A_MON1N

M_

PLACE 0.1UF CAP CLOSE TO CPU

SoC Supported Memory Operation SpeedChannel 1

1066 MHz

1600 MHz

1066 MHz

1600 MHz

5

M_

A_A[15:0][11]

M_

A_DM0[1 1]

M_

A_DM1[1 1]

M_

A_DM2[1 1]

M_

A_DM3[1 1]

M_

A_DM4[1 1]

M_

A_DM5[1 1]

M_

A_DM6[1 1]

M_

A_DM7[1 1]

M_

A_RAS#[11]

M_

A_CAS#[11]

M_

A_WE#[11]

M_

A_BS#0[11]

M_

A_BS#1[11]

M_

A_BS#2[11]

M_

A_CS#0[11]

M_

A_CS#1[11]

M_

A_CKE0[11]

M_

A_CKE1[11]

M_

A_ODT0[11]

M_

A_ODT1[11]

M_

A_CLK0[11]

M_

A_CLK0#[11]

M_

A_CLK1[11]

M_

A_CLK1#[11]

M_

A_DRAMRST#[11]

79 182_4

R1

GN

D

4

A_A0

M_

A_A1

M_

A_A2

M_

A_A3

M_

A_A4

M_

A_A5

M_

A_A6

M_

A_A7

M_

A_A8

M_

A_A9

M_

A_A10

M_

A_A11

M_

A_A12

M_

A_A13

M_

A_A14

M_

A_A15

M_

A_DM0

M_

A_DM1

M_

A_DM2

M_

A_DM3

M_

A_DM4

M_

A_DM5

M_

A_DM6

M_

A_DM7

M_

A_RAS#

M_

A_CAS#

M_

A_WE#

M_

A_BS#0

M_

A_BS#1

M_

A_BS#2

M_

A_CS#0

M_

A_CS#1

M_

A_CKE0

M_

A_CKE1

M_

A_ODT0

M_

A_ODT1

M_

A_CLK0

M_

A_CLK0#

M_

A_CLK1

M_

A_CLK1#

M_

A_DRAMRST#

M_

A_VREF_CA

M_

A_VREF_DQ

M_

A_MON1P

M_

A_MON1N

M_

C_DRAM_PWROK

SO

M_RCOMP0

DRA

P_S4#[6,14]

SL

4

BB47

BC42

BJ48

BH47

BD42

BH48

BB46

BE46

BD44

BE52

BJ45

BB49

BF48

BF44

BD47

BD49

AP52

AT48

AP44

BA53

BG41

AY36

BD32

BH30

BA40

BG45

BH44

BH46

AY40

BF52

AY38

AU38

BB44

AY42

AV36

BA38

BD40

BF40

BD38

BF38

BA42

AT28

AU28

AT30

AU30

AV28

BA28

SL

P_S4#

U23A

DDR3

_M0_MA_0

DDR3

_M0_MA_1

DDR3

_M0_MA_2

DDR3

_M0_MA_3

DDR3

_M0_MA_4

DDR3

_M0_MA_5

DDR3

_M0_MA_6

DDR3

_M0_MA_7

DDR3

_M0_MA_8

DDR3

_M0_MA_9

DDR3

_M0_MA_10

DDR3

_M0_MA_11

DDR3

_M0_MA_12

DDR3

_M0_MA_13

DDR3

_M0_MA_14

DDR3

_M0_MA_15

DDR3

_M0_DM_0

DDR3

_M0_DM_1

DDR3

_M0_DM_2

DDR3

_M0_DM_3

DDR3

_M0_DM_4

DDR3

_M0_DM_5

DDR3

_M0_DM_6

DDR3

_M0_DM_7

DDR3

_M0_RASB

DDR3

_M0_CASB

DDR3

_M0_WEB

DDR3

_M0_BS_0

DDR3

_M0_BS_1

DDR3

_M0_BS_2

DDR3

_M0_CSB_0

DDR3

_M0_CSB_1

DDR3

_M0_CKE_0

DDR3

_M0_CKE_1

DDR3

_M0_ODT_0

DDR3

_M0_ODT_1

DDR3

_M0_CK_0

DDR3

_M0_CKB_0

DDR3

_M0_CK_1

DDR3

_M0_CKB_1

DDR3

_M0_DRAMRSTB

DRA

M_M0_OCAVREF

DRA

M_M0_ODQVREF

RS

VD_AT30

RS

VD_AU30

DDR3

_DRAM_PWROK

DDR3

_M0_RCOMPPD

VLV_M_D/BGA

RE

V = 1.15

3

AK51

A_DQ0

GN

D

AL51

AT52

AR51

AL53

AK52

AR53

AP51

AP48

AT47

AY48

AV50

AP47

AT50

AY50

AV45

AT40

AP42

AT38

AP40

AT44

AV41

AP41

AV42

BD52

AV52

BC53

AV51

AW51

BC52

AW53

BB51

BG42

BG43

BG37

BJ37

BH42

BJ41

BH36

BH38

BC36

BA36

AU34

AU32

BF36

BD36

AV34

AV32

BF34

BC34

BA32

BD30

BD34

BA34

BF30

BD28

BJ33

BG29

BH34

BG32

BG28

BJ29

BH28

BG33

AM52

AM51

AV47

AV48

AT42

AT41

AY52

BA51

BH40

BG39

AT32

AT34

BC30

BC32

BH32

BG31

PG_1.35V [22,27]

HW

SO

C_DRAM_PWROK

C2

08

*0.1U/16V_4

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

A_DQ1

A_DQ2

A_DQ3

A_DQ4

A_DQ5

A_DQ6

A_DQ7

A_DQ8

A_DQ9

A_DQ10

A_DQ11

A_DQ12

A_DQ13

A_DQ14

A_DQ15

A_DQ16

A_DQ17

A_DQ18

A_DQ19

A_DQ20

A_DQ21

A_DQ22

A_DQ23

A_DQ24

A_DQ25

A_DQ26

A_DQ27

A_DQ28

A_DQ29

A_DQ30

A_DQ31

A_DQ32

A_DQ33

A_DQ34

A_DQ35

A_DQ36

A_DQ37

A_DQ38

A_DQ39

A_DQ40

A_DQ41

A_DQ42

A_DQ43

A_DQ44

A_DQ45

A_DQ46

A_DQ47

A_DQ48

A_DQ49

A_DQ50

A_DQ51

A_DQ52

A_DQ53

A_DQ54

A_DQ55

A_DQ56

A_DQ57

A_DQ58

A_DQ59

A_DQ60

A_DQ61

A_DQ62

A_DQ63

A_DQS0

A_DQS#0

A_DQS1

A_DQS#1

A_DQS2

A_DQS#2

A_DQS3

A_DQS#3

A_DQS4

A_DQS#4

A_DQS5

A_DQS#5

A_DQS6

A_DQS#6

A_DQS7

A_DQS#7

DDR3

_M0_DQ_0

DDR3

_M0_DQ_1

DDR3

_M0_DQ_2

DDR3

_M0_DQ_3

DDR3

_M0_DQ_4

DDR3

_M0_DQ_5

DDR3

_M0_DQ_6

DDR3

_M0_DQ_7

DDR3

_M0_DQ_8

DDR3

_M0_DQ_9

DDR3

_M0_DQ_10

DDR3

_M0_DQ_11

DDR3

_M0_DQ_12

DDR3

_M0_DQ_13

DDR3

_M0_DQ_14

DDR3

_M0_DQ_15

DDR3

_M0_DQ_16

DDR3

_M0_DQ_17

DDR3

_M0_DQ_18

DDR3

_M0_DQ_19

DDR3

_M0_DQ_20

DDR3

_M0_DQ_21

DDR3

_M0_DQ_22

DDR3

_M0_DQ_23

DDR3

_M0_DQ_24

DDR3

_M0_DQ_25

DDR3

_M0_DQ_26

DDR3

_M0_DQ_27

DDR3

_M0_DQ_28

DDR3

_M0_DQ_29

DDR3

_M0_DQ_30

DDR3

_M0_DQ_31

DDR3

_M0_DQ_32

DDR3

_M0_DQ_33

DDR3

_M0_DQ_34

DDR3

_M0_DQ_35

DDR3

_M0_DQ_36

DDR3

_M0_DQ_37

DDR3

_M0_DQ_38

DDR3

_M0_DQ_39

DDR3

_M0_DQ_40

DDR3

_M0_DQ_41

DDR3

_M0_DQ_42

DDR3

_M0_DQ_43

DDR3

_M0_DQ_44

DDR3

_M0_DQ_45

DDR3

_M0_DQ_46

DDR3

_M0_DQ_47

DDR3

_M0_DQ_48

DDR3

_M0_DQ_49

DDR3

_M0_DQ_50

DDR3

_M0_DQ_51

DDR3

_M0_DQ_52

DDR3

_M0_DQ_53

DDR3

_M0_DQ_54

DDR3

_M0_DQ_55

DDR3

_M0_DQ_56

DDR3

_M0_DQ_57

DDR3

_M0_DQ_58

DDR3

_M0_DQ_59

DDR3

_M0_DQ_60

DDR3

_M0_DQ_61

DDR3

_M0_DQ_62

DDR3

_M0_DQ_63

DDR3

_M0_DQSP_0

DDR3

_M0_DQSN_0

DDR3

_M0_DQSP_1

DDR3

_M0_DQSN_1

DDR3

_M0_DQSP_2

DDR3

_M0_DQSN_2

DDR3

_M0_DQSP_3

DDR3

_M0_DQSN_3

DDR3

_M0_DQSP_4

DDR3

_M0_DQSN_4

DDR3

_M0_DQSP_5

DDR3

_M0_DQSN_5

DDR3

_M0_DQSP_6

DDR3

_M0_DQSN_6

DDR3

_M0_DQSP_7

DDR3

_M0_DQSN_7

1 OF 12

+1

_PWOK_C1

R2

10K_4

.35VSUS

31

HW

PG_1.35V

61

2

Q2

7B

PJ4N3KDW

R2

32 *short_4

3

+3

V_S5

R2

40

4.7K_4

DRM

34

5

Q2

7A

PJ4N3KDW

GN

D

2

M_

A_DQ[63:0] [11]

2

A_DQS[7:0]

M_

A_DQS#[7:0]

M_

1

M_

A_DQS[7:0] [11]

M_

A_DQS#[7:0] [11]

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

Qu

Qu

Qu

PROJECT :

PROJECT :

Si

Si

Si

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

We

We

We

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

PROJECT :

Valley 1/9 (DDRA)

Valley 1/9 (DDRA)

Valley 1/9 (DDRA)

Z8AD

Z8AD

Z8AD

1

3A

3A

3A

of

322

of

322

of

322

5

4

3

2

1

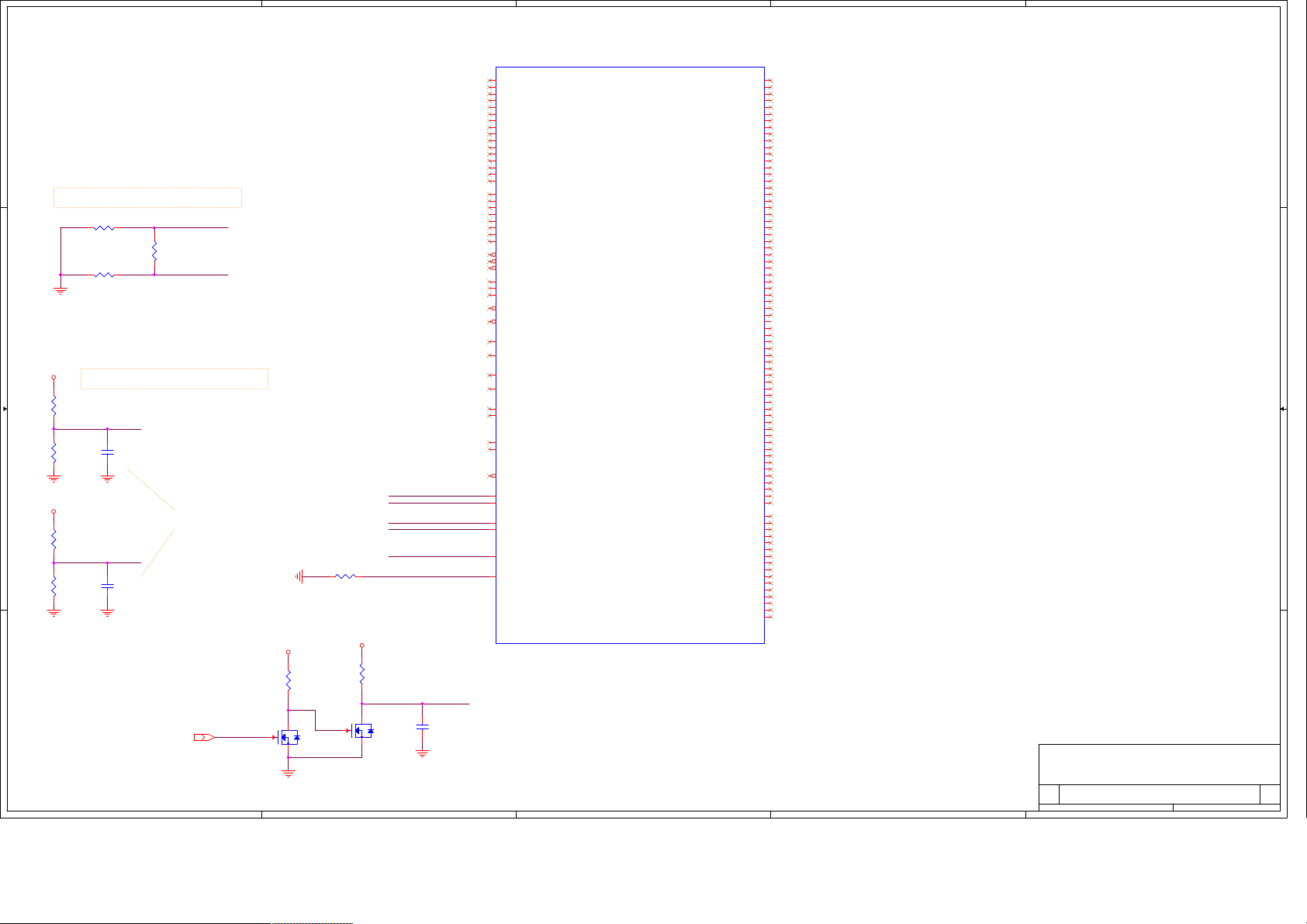

U23B

BB7

DDR3

_M1_MA_0

BC12

DDR3

_M1_MA_1

BJ6

DDR3

_M1_MA_2

BH7

DDR3

_M1_MA_3

BD12

DDR3

BD10

BF10

AP10

BG13

AY18

BD22

BH24

BA14

BH10

AY14

AY16

AU16

BB10

AY12

AV18

BA16

BD14

BF14

BD16

BF16

BA12

AT26

AU26

AT24

AU24

AV26

BA26

BH6

BB8

BE8

BE2

BJ9

BB5

BF6

BD7

BD5

AP2

AT6

BA1

BG9

BH8

BF2

_M1_MA_4

DDR3

_M1_MA_5

DDR3

_M1_MA_6

DDR3

_M1_MA_7

DDR3

_M1_MA_8

DDR3

_M1_MA_9

DDR3

_M1_MA_10

DDR3

_M1_MA_11

DDR3

_M1_MA_12

DDR3

_M1_MA_13

DDR3

_M1_MA_14

DDR3

_M1_MA_15

DDR3

_M1_DM_0

DDR3

_M1_DM_1

DDR3

_M1_DM_2

DDR3

_M1_DM_3

DDR3

_M1_DM_4

DDR3

_M1_DM_5

DDR3

_M1_DM_6

DDR3

_M1_DM_7

DDR3

_M1_RASB

DDR3

_M1_CASB

DDR3

_M1_WEB

DDR3

_M1_BS_0

DDR3

_M1_BS_1

DDR3

_M1_BS_2

DDR3

_M1_CSB_0

DDR3

_M1_CSB_1

DDR3

_M1_CKE_0

DDR3

_M1_CKE_1

DDR3

_M1_ODT_0

DDR3

_M1_ODT_1

DDR3

_M1_CK_0

DDR3

_M1_CKB_0

DDR3

_M1_CK_1

DDR3

_M1_CKB_1

DDR3

_M1_DRAMRSTB

DDR3

_M1_OCAVREF

DDR3

_M1_ODQVREF

RS

VD_AT24

RS

VD_AU24

DDR3

_DRAM_PWROK

DDR3

_M1_RCOMPPD

VLV_M_D/BGA

RE

V = 1.15

2 OF 12

3

D D

PLACE THE RESISTORS AS CLOSE AS POSSIBLE TO SOC(BSW)

ROUTE THEM AS SINGLE ENDED LINES

14 *49.9_4

R2

15 *49.9_4

R2

D

+1

+1

GN

.35VSUS

GN

.35VSUS

GN

ROUTE ALL VREF POWER SIGNALS AS THICK TRACES

PLACE TWO 4.7K RESISTORS CLOSE TO CPU PINS ON M_VREF

ROUTE THE VREF POWER SIGNALS WITH THICK TRACES

30

R2

*4.7K_4

B_VREF_CA

M_

05

B_VREF_DQ

M_

GN

GN

C2

*0.1U/16V_4

D

04

C2

*0.1U/16V_4

D

EC

5

R2

*4.7K_4

D

R2

*4.7K_4

R2

*4.7K_4

D

22

29

21

C C

B B

A A

B_MON1P

M_

09

R2

*100_4

B_MON1N

M_

PLACE 0.1UF CAP CLOSE TO CPU

EC

_PWROK[14,22]

_PWROK

B_VREF_CA

M_

B_VREF_DQ

M_

B_MON1P

M_

B_MON1N

M_

C_VCCA_PWROK

SO

SO

C_VCCA_PWROK

3B

4

DRA

M_RCOMP1

C2

01

*0.1U/16V_4

GN

D

78 *182_4

R1

GN

D

+1

_PWOK_C2

R2

10K_4

.35VSUS

26

61

2

Q2

PJ4N3KDW

+3

V_S5

R2

36

4.7K_4

DRM

34

5

Q2

3A

PJ4N3KDW

GN

D

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

_M1_DQSP_0

_M1_DQSN_0

_M1_DQSP_1

_M1_DQSN_1

_M1_DQSP_2

_M1_DQSN_2

_M1_DQSP_3

_M1_DQSN_3

_M1_DQSP_4

_M1_DQSN_4

_M1_DQSP_5

_M1_DQSN_5

_M1_DQSP_6

_M1_DQSN_6

_M1_DQSP_7

_M1_DQSN_7

_M1_DQ_0

_M1_DQ_1

_M1_DQ_2

_M1_DQ_3

_M1_DQ_4

_M1_DQ_5

_M1_DQ_6

_M1_DQ_7

_M1_DQ_8

_M1_DQ_9

_M1_DQ_10

_M1_DQ_11

_M1_DQ_12

_M1_DQ_13

_M1_DQ_14

_M1_DQ_15

_M1_DQ_16

_M1_DQ_17

_M1_DQ_18

_M1_DQ_19

_M1_DQ_20

_M1_DQ_21

_M1_DQ_22

_M1_DQ_23

_M1_DQ_24

_M1_DQ_25

_M1_DQ_26

_M1_DQ_27

_M1_DQ_28

_M1_DQ_29

_M1_DQ_30

_M1_DQ_31

_M1_DQ_32

_M1_DQ_33

_M1_DQ_34

_M1_DQ_35

_M1_DQ_36

_M1_DQ_37

_M1_DQ_38

_M1_DQ_39

_M1_DQ_40

_M1_DQ_41

_M1_DQ_42

_M1_DQ_43

_M1_DQ_44

_M1_DQ_45

_M1_DQ_46

_M1_DQ_47

_M1_DQ_48

_M1_DQ_49

_M1_DQ_50

_M1_DQ_51

_M1_DQ_52

_M1_DQ_53

_M1_DQ_54

_M1_DQ_55

_M1_DQ_56

_M1_DQ_57

_M1_DQ_58

_M1_DQ_59

_M1_DQ_60

_M1_DQ_61

_M1_DQ_62

_M1_DQ_63

AK3

AL3

AT2

AR3

AL1

AK2

AR1

AP3

AP6

AT7

AY6

AV4

AP7

AT4

AY4

AV9

AT14

AP12

AT16

AP14

AT10

AV13

AP13

AV12

BD2

AV2

BC1

AV3

AW3

BC2

AW1

BB3

BG12

BG11

BG17

BJ17

BH12

BJ13

BH18

BH16

BC18

BA18

AU20

AU22

BF18

BD18

AV20

AV22

BF20

BC20

BA22

BD24

BD20

BA20

BF24

BD26

BJ21

BG25

BH20

BG22

BG26

BJ25

BH26

BG21

AM2

AM3

AV7

AV6

AT12

AT13

AY2

BA3

BH14

BG15

AT22

AT20

BC24

BC22

BH22

BG23

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

Qu

Qu

Qu

PROJECT :

PROJECT :

Si

Si

Size Document Number Rev

ze Document Number Rev

ze Document Number Rev

We

We

We

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

2

dnesday, April 08, 2015

PROJECT :

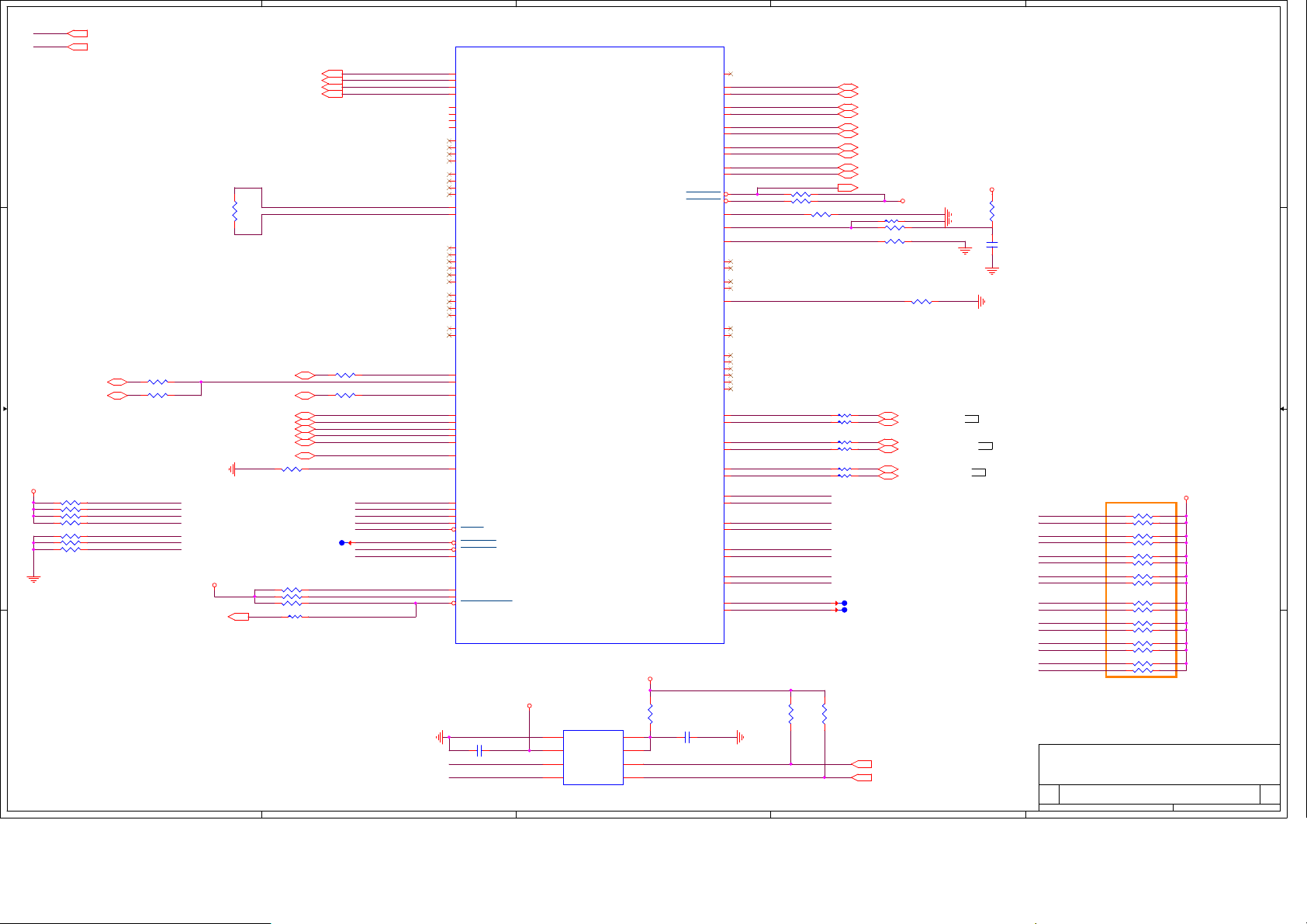

Valley 2/9 (DDRB)

Valley 2/9 (DDRB)

Valley 2/9 (DDRB)

Z8AD

Z8AD

Z8AD

3A

3A

3A

of

323

of

323

of

1

323

5

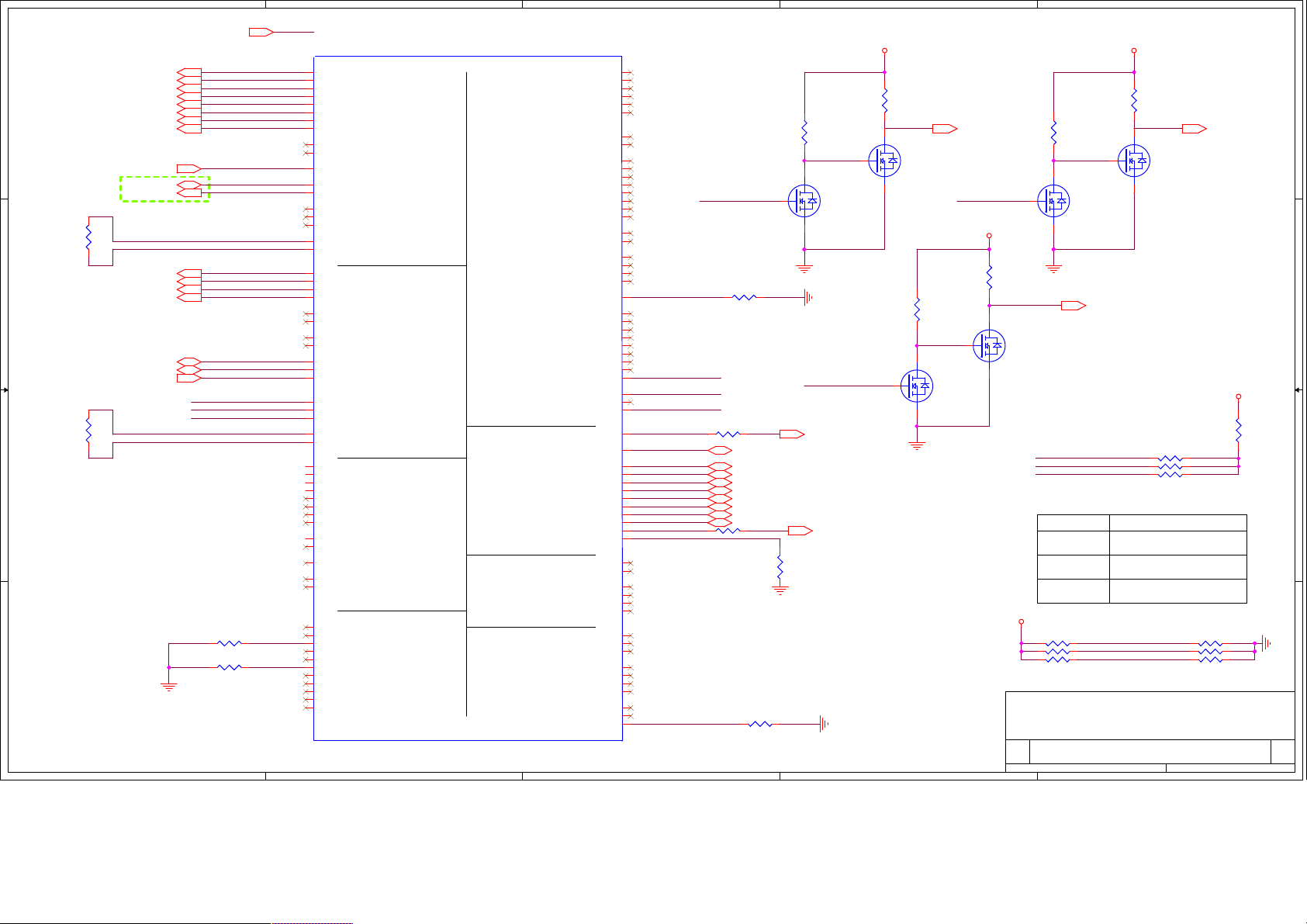

V[7,9,11,12,13,14,15,16,18,19,21,22,25,27,28,29,30]

+3

U23C

IN

_D2[13]

_D2#[13]

IN

IN

_D1[13]

IN

_D1#[13]

_D0[13]

D D

HDM

IN

I

IN

_D0#[13]

_CLK[13]

IN

IN_CLK#[13]

I_HPD_CON[13]

HDM

SD

VO_DATA[13]

VO_CLK[13]

SD

Internal Pull-High 1.8V

R1

03

402_4

IN

T_EDP_TXP0[13]

T_EDP_TXN0[13]

IN

IN

C C

B B

A A

eDP

R102

402_4

T_EDP_TXP1[13]

IN

T_EDP_TXN1[13]

T_eDP_AUXP[13]

IN

INT_eDP_AUXN[13]

1_EDP_HPD_R[13]

DDI

5

GN

D

C_DDIO_RCOMP

SO

SOC_DDIO_RCOMP_P

H_DISP_ON_C

PC

PC

H_EDP_BLON_C

H_DPST_PWM_C

PC

SO

C_DDI1_RCOMP

C_DDI1_RCOMP_P

SO

80 *0_4

R3

79 *0_4

R3

D50

C51

H49

H50

F53

F52

G53

G52

H47

H46

W51

Y52

Y51

W53

V52

V51

F38

G38

J51

H51

K51

K52

L53

L51

M52

M51

M42

K42

R51

R53

P51

P52

F47

F49

F40

G40

J40

K40

F42

G42

D44

F44

D48

C49

U51

T51

T52

A49

A51

A52

B49

B50

B53

C53

D52

E52

E53

G44

DDI

0_TXP_0

DDI

0_TXN_0

0_TXP_1

DDI

DDI

0_TXN_1

0_TXP_2

DDI

0_TXN_2

DDI

DDI

0_TXP_3

0_TXN_3

DDI

DDI

0_AUXP

DDI

0_AUXN

HV

_DDI0_HPD

_DDI0_DDC_SDA

HV

_DDI0_DDC_SCL

HV

EL0_VDDEN

PAN

PAN

EL0_BKLTEN

EL0_BKLTCTL

PAN

0_PLLOBS_P

DDI

DDI

0_PLLOBS_N

1_TXP_0

DDI

DDI

1_TXN_0

1_TXP_1

DDI

DDI

1_TXN_1

DDI

1_TXP_2

1_TXN_2

DDI

1_TXP_3

DDI

DDI

1_TXN_3

DDI

1_AUXP

1_AUXN

DDI

HV

_DDI1_HPD

EL1_VDDEN

PAN

PAN

EL1_BKLTEN

EL1_BKLTCTL

PAN

1_PLLOBS_P

DDI

DDI

1_PLLOBS_N

2_TXP_0

DDI

2_TXN_0

DDI

2_TXP_1

DDI

DDI

2_TXN_1

2_TXP_2

DDI

DDI

2_TXN_2

DDI

2_TXP_3

DDI

2_TXN_3

DDI

2_AUXP

2_AUXN

DDI

HV_DDI2_HPD

_DDI2_DDC_SCL

HV

HV

_DDI2_DDC_SDA

VD_A49

RS

VD_A51

RS

RS

VD_A52

RS

VD_B49

VD_B50

RS

RS

VD_B53

RS

VD_C53

VD_D52

RS

RS

VD_E52

VD_E53

RS

VD_G44

RS

VLV_M_D/BGA

REV = 1.15

4

4

DDI0

DDI1

DDI2

NC's

3

OF 12

T50

RS

VD_T50

T48

RS

VD_T48

M44

VD_M44

RS

SI_1_CLKP

MC

MC

SI_1_CLKN

MC

MC

SI_1_DN_0

MC

SI_1_DN_1

MC

MC

MC

SI_1_DN_2

MC

MC

SI_1_DN_3

MC

SI_2_CLKP

SI_2_CLKN

MC

MC

MCSI and Camera interface

SDMMC1

SDMMC2

SDMMC3

MCSI_2_DN_0

MC

MC

SI_2_DN_1

MC

GP

_CAMERASB00

_CAMERASB01

GP

GP

_CAMERASB02

_CAMERASB03

GP

GP

_CAMERASB04

_CAMERASB05

GP

GP

_CAMERASB06

_CAMERASB07

GP

GP

_CAMERASB08

GP

_CAMERASB09

_CAMERASB10

GP

GP

_CAMERASB11

MMC1_CLK

SD

MMC1_CMD

SD

SD

SD

SD

SD

MMC1_D3_CD_B

1_D4_SD_WE

MMC

MMC

SD

MMC1_RCOMP

SDMMC2_CLK

SD

MMC2_CMD

SD

SD

SD

MMC2_D3_CD_B

SD

MMC3_CLK

SD

SD

MMC3_CMD

SD

MMC3_CD_B

SD

SD

SD

SD

MMC3_1P8_EN

SD

MMC3_PWR_EN_B

SD

SD

MMC3_RCOMP

RS

VD_K48

VD_K47

RS

VD_K44

RS

SI_1_DP_0

SI_1_DP_1

SI_1_DP_2

SI_1_DP_3

SI_2_DP_0

SI_2_DP_1

SI_COMP

MMC1_D0

MMC1_D1

MMC1_D2

MMC

1_D5

MMC

1_D6

MMC

1_D7

1_RCLK

MMC2_D0

MMC2_D1

MMC2_D2

MMC3_D0

MMC3_D1

MMC3_D2

MMC3_D3

K48

K47

K44

T44

T45

Y47

Y48

V45

V47

V50

V48

T41

T42

P50

P48

P47

P45

M48

M47

P44

AB41

AB45

AB44

AC53

AB51

AB52

AA51

AB40

Y44

Y42

Y41

V40

M7

P6

M6

M4

P9

P7

T6

T7

T10

T12

T13

P13

K10

K9

M12

M10

K7

K6

F2

D2

K3

J1

J3

H3

G2

K2

L3

P12

3

MC

_CAMERASB08

GP

GP

_CAMERASB09

GP

_CAMERASB11

EM

MC_CLK_R

EM

MC_RCLK_R

MMC1_COMP

SD

SD

MMC3_COMP

3

SI_COMP

H_EDP_BLON_C

PC

R1

24 150_4

R1

10 0_4

EM

EM

EM

EM

EM

EM

EM

EM

EM

R1

46 *0_4

R4

16 80.6_4

2

MC_CMD [21]

MC_DATA_0 [21]

MC_DATA_1 [21]

MC_DATA_2 [21]

MC_DATA_3 [21]

MC_DATA_4 [21]

MC_DATA_5 [21]

MC_DATA_6 [21]

MC_DATA_7 [21]

D

GN

R2

10K_4

3

1

GN

D

GN

PC

H_DPST_PWM_C

EM

EM

17

R4

100_4

6

Q1

1

PJA138K

D

MC_CLK [21]

MC_RCLK [21]

D

GN

2

+3

V

7

R2

10K_4

R8

PC

R5

10K_4

6

Q1

3

PJA138K

PC

H_EDP_BLON [21]

H_DISP_ON_C

+3V

7

R3

10K_4

H_DPST_PWM

PC

3

2

Q1

2

PJA138K

1

+1

.8V_S5

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

3

0

Q1

2

PJA138K

1

3

2

1

GN

D

2

7

10K_4

3

Q1

7

PJA138K

2

1

GN

D

PC

PC

H_DISP_ON_C

H_EDP_BLON_C

PC

H_DPST_PWM_C

PC

Hardware Strap

GP_CAMERASB08

GP_CAMERASB09

GP_CAMERASB11

31 *10K_4

R4

25 *10K_4

R4

R4

20 *10K_4

V

V

V

alley 3/9 (Display)

alley 3/9 (Display)

Wednesday, April 08, 2015

Wednesday, April 08, 2015

Wednesday, April 08, 2015

alley 3/9 (Display)

2

H_DPST_PWM [13]

follow CRB v1.0

ICLK Xtal OSC Bypass

0 = No Bypass

1 = Bypass

CCU SUS RO Bypass

0 = No Bypass

1 = Bypass

RTC OSC Bypass

0 = No Bypass

1 = Bypass

_CAMERASB08

GP

_CAMERASB09

GP

GP

_CAMERASB11

Qu

Qu

Qu

PROJECT :

PROJECT :

PROJECT :

1

+3

V

1

R8

10K_4

PC

32 100K_4

R4

26 100K_4

R4

R4

21 100K_4

Z8AD

Z8AD

Z8AD

H_DISP_ON [13]

+1

.8V_S5

R40

*0_4

3

5

Q1

PJA138K

1

R9

7 *100K_4

9 *100K_4

R3

R7

8 *100K_4

Strap Description

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

1

GN

D

3A

3A

3A

324

324

324

5

+1

.05V_S5[6,8,26,28,29]

+1

.8V[9,12,13,14,15,16,19,20,21,22,26,30]

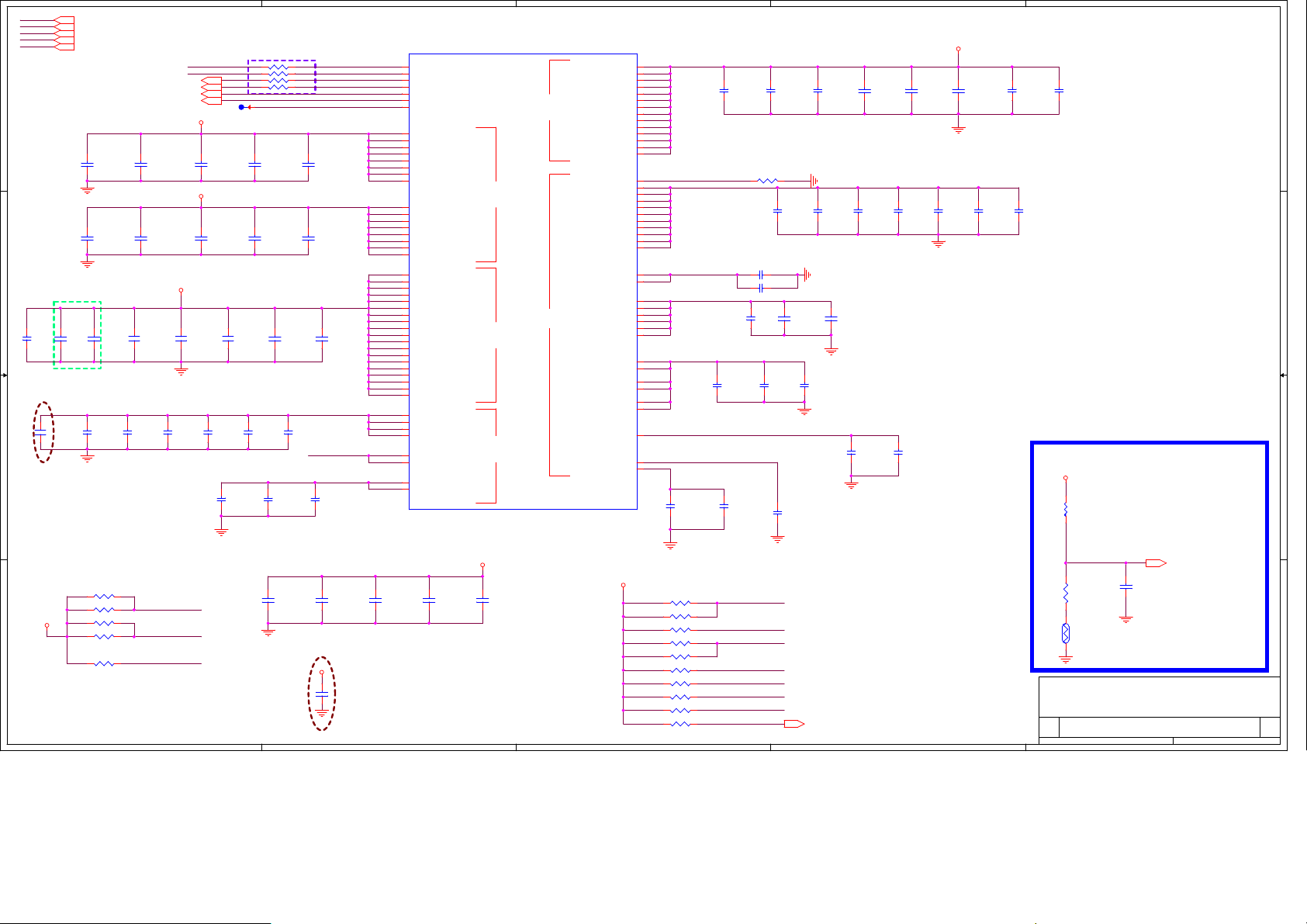

SAT

A_TXP0[16]

SAT

+1

OD

.8V_S5

R8

*100K/F_4

A_TXN0[16]

SAT

A_RXP0[16]

SAT

A_RXN0[16]

SAT

A_TXP1[16]

SAT

A_TXN1[16]

SAT

A_RXP1[16]

SAT

A_RXN1[16]

SO

C_KBC_SCI[14]

DE

VSLP0[16]

D_PRSNT#[16]

16

R1

402_4

10

+1

.8V_S5

84 *short_4

R4

00 *short_4

R4

VSLP0

DE

77 *0_4

R4

SATA HDD

D D

TA ODD

SA

SO

C_KCB_SMI[14]

IO_SUS7

01 *0_4

GP

GP

IO_SUS7[6]

C C

High is SSD ,Low is ODD

SSD

_ID[16]

R1

Add SSD ID 1/14

11

R8

10K_4

A_GP3

SAT

C_SPI_CLK

SO

C_SPI_CS#

SO

T_SPI_D0

FS

T_SPI_D1

FS

T_SPI_D2

FS

T_SPI_D3

FS

SAT

SAT

SAT

SAT

A_RCOMP_DP

SAT

A_RCOMP_DN

SAT

BI

4

A_GP0

A_GP1

A_GP3

A_LED#

OS_STRAP

AK10

AK12

AK13

C31

B30

N28

M28

C29

A29

J28

K28

AH2

AG3

AG1

AF3

AH3

N30

M30

W3

V4

V6

V7

V2

V3

U1

U3

B16

C16

AK9

U23D

SAT

A_TXP_0

SAT

A_TXN_0

SAT

A_RXP_0

SAT

A_RXN_0

SAT

A_TXP1

SAT

A_TXN_1

SAT

A_RXP_1

SAT

A_RXN_1

SAT

A_GP0

SAT

A_GP1

SAT

A_GP2

SAT

A_GP3

SAT

A_LED

SAT

A_OBSP

SAT

A_OBSN

FS

T_SPI_CLK

FS

T_SPI_CS0_B

FS

T_SPI_CS1_B

FS

T_SPI_CS2_B

FS

T_SPI_D0

FS

T_SPI_D1

FS

T_SPI_D2

FS

T_SPI_D3

RS

VD_B16

RS

VD_C16

GP

_SSP_2_CLK

GP

_SSP_2_FS

GP

_SSP_2_TXD

GP

_SSP_2_RXD

VLV_M_D/BGA

REV = 1.15

4

OF 12

PC

PC

PC

PC

IE_RXN_0

PC

PC

IE_TXN_1

PC

IE_RXP_1

PC

IE_RXN_1

PC

PC

IE_TXN_2

PC

IE_RXP_2

PC

IE_RXN_2

PC

PC

IE_TXN_3

PC

IE_RXP_3

PC

IE_RXN_3

PC

IE_CLKREQ0B

PC

IE_CLKREQ1B

PC

IE_CLKREQ2B

PC

IE_CLKREQ3B

PC

PC

M

F_HDA_RSTB

MF

_HDA_SYNC

MF

_HDA_CLK

MF

_HDA_SDO

MF

_HDA_SDI0

MF

_HDA_SDI1

M

F_HDA_DOCKRSTB

M

F_HDA_DOCKENB

PR

IE_TXP_0

IE_TXN_0

IE_RXP_0

IE_TXP_1

IE_TXP_2

IE_TXP_3

IE_OBSP

IE_OBSN

SPKR

OCHOT

3

C24

B24

G20

J20

A25

C25

D20

F20

B26

C26

D22

F22

A27

C27

G24

J24

AM10

AM12

AK14

AM14

D26

F26

AF13

AF12

AD9

AF14

AD7

AD6

AB7

AB9

H4

AD50

0.1U/16V_4

IE_TXP1_NGFF_C

PC

IE_TXN1_NGFF_C

PC

IE_TXP2_WLAN_C

PC

IE_TXN2_WLAN_C

PC

IE_TXP3_LAN_C

PC

IE_TXN3_LAN_C

PC

SP7

IE_CLKREQ1_NGFF #

PC

IE_CLKREQ2_W LAN#

PC

IE_CLKREQ3_LAN#

PC

C_PCIE_COMP

SO

C_PCIE_COMN

SO

Z_RST#

AC

Z_SYNC

AC

Z_BCLK

AC

Z_SDOUT

AC

Z_SDIN0

AC

C_PROCHOT#

SO

54

C3

GN

_R

D

C3

C3

C3

C3

C3

C3

33 *short_4

R4

48 20K_4

R4

43 0.1U/16V_4

44 0.1U/16V_4

42 0.1U/16V_4

41 0.1U/16V_4

40 0.1U/16V_4

48 0.1U/16V_4

68 75_4

R2

64 75_4

R2

58 75_4

R2

65 75_4

R2

62 *short_4

R2

CRB is 75 ohm

PC

IE_TXP1_NGFF [19]

PC

IE_TXN1_NGFF [19 ]

PEG

_RXP1_NGFF [19]

PEG

_RXN1_NGFF [19 ]

PC

IE_TXP2_WLAN [20]

PC

IE_TXN2_WLAN [20]

PC

IE_RXP2_WLAN [20]

PC

IE_RXN2_WLAN [20]

PC

IE_TXP3_LAN [12]

PC

IE_TXN3_LAN [ 12]

PC

IE_RXP3_LAN [12]

PC

IE_RXN3_LAN [12 ]

PC

IE_CLKREQ1_NGFF # [19]

PC

IE_CLKREQ2_W LAN# [20]

PC

IE_CLKREQ3_LAN# [12]

PC

PC

PC

PC

PC

.8V_S5

+1

2

NGFF X1

WLAN x1

LAN x1

07

R1

402_4

H_AZ_CODEC_RST# [1 8]

H_AZ_CODEC_SYNC [18]

H_AZ_CODEC_BITCLK [18]

H_AZ_CODEC_SDOUT [18]

H_AZ_CODEC_SDIN0 [18]

AC

Z_SPKR [18]

H_

PROCHOT# [22,24,28,29]

IE_CLKREQ1_NGFF #

PC

IE_CLKREQ2_W LAN#

PC

IE_CLKREQ3_LAN#

PC

VSLP0

DE

_R

SP7

25 10K_4

R5

23 10K_4

R5

22 10K_4

R5

78 10K_4

R4

21 10K_4

R5

1

.8V_S5

+1

SPI NOR FLASH

B B

T_SPI_D2

FS

T_SPI_D3

FS

A A

5

64

C3

0.1U/16V_4

39 10_4

R4

94 10_4

R4

U2

2

#

_HOLD

5

C_SPI_MOSI_R

SO

SPI

_SI

2

C_SPI_MISO_R

SO

SPI

_SO

1

C_SPI_CS#_R

SO

CS

#

6

C_SPI_CLK_R

_SCK

GN

SO

4

D

D

GN

SPI

95 10_4

R4

38 10_4

R4

40 33_4

R4

96 10_4

R4

2nd source: AKE5EG-0Q01

SO

C_SPI_CS#

FS

T_SPI_D2_R

FS

T_SPI_D3_R

AC

4

T_SPI_D0

FS

T_SPI_D1

FS

C_SPI_CS#

SO

C_SPI_CLK

SO

BI

OS_STRAP

V_S5

+3

R3

56

10K_4

3

R3

PRESENT[24]

51 *short_4

AC

_PRESENT_NM

2

1

GN

D

3

3

2

Q4

3

2N7002K

2N7002K

Q4

1

AC Present: This input pin indicates when the

platform is plugged into AC power.

_PRESENT [6]

AC

2

2

0 = LPC

1 = SPI

.8V_S5

+1

13

R5

*10K_4

R5

14

*10K_4

GN

D

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

Qu

Qu

Qu

PROJECT :

PROJECT :

Si

Si

ze Document Number Rev

ze Document Number Rev

Size Document Number Rev

We

We

We

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

PROJECT :

Valley 4/9 (SD/PCIE/SATA)

Valley 4/9 (SD/PCIE/SATA)

Valley 4/9 (SD/PCIE/SATA)

Z8AD

Z8AD

Z8AD

of

325

of

325

of

1

325

3A

3A

3A

8

VC

D

GN

T_SPI_D2_R

FS

T_SPI_D3_R

FS

+1

.8V_S5

C

3

WP

7

SPI

SPI_FLASH

soic8-7_9-1_27

AKE5EZN0N00

IC FLASH (8P) W25Q64FWSSIG (SOIC)

R1

40 3.3K_4

R1

39 3.3K_4

R4

93 3.3K_4

5

0 12P/50V_4

C4

D

GN

D

GN

D D

C C

+1

.8V_S5

B B

C3

2nd source:BG619200014 (TXC)

Hardware Strap

GPIO_SUS[0]

GPIO_SUS[1]

GPIO_SUS[2]

GPIO_SUS[4]

GPIO_SUS[5] Security Flash Descriptors

GPIO_SUS[8]

GPIO_SUS[9]

GPIO_SUS[10] POSM Select

93 4.7K_4

R3

96 4.7K_4

R3

25 10K_4

R1

35 100K_4

R4

29 100K_4

R4

08 *10K_4

R4

13 *1K_4

R4

98 *10K_4

R3

23 4.7K_4

R4

R4

24 *4.7K_4

R4

56 *10K_4

AL25_OUT

XT

1

2

Y7

6

R3

200K_4

2MHZ

19.

4

3

AL25_IN

XT

9 12P/50V_4

NG

FF

AN

WL

LAN

Strap Description

0 = DDI0 not detected

1 = DDI0 detected

0 = DDI1 not detected

1 = DDI1 detected

Top Swap(A16 Override)

0 = Change Boot Loader address

1 = Normal Operation

BIOS Boot Selection

0 = No SPI

1 = SPI

0 = Override

1 = Normal Operation

ICLK,USB 2.0,DDI SFR supply select

0 = Supply is 1.25V

1 = Supply is 1.35V

ICLK,USB 2.0,DDI SFR Bypass

0 = No bypass

1 = Bypass with 1.05V (internal PU)

0 = Fuse controller

1 = PMC (internal PD)

IO_SUS0

94 *10K_4

GP

R3

IO_SUS1

97 *10K_4

GP

R3

IO_SUS2

48 *10K_4

GP

R1

IO_SUS4

36 *10K_4

GP

R4

IO_SUS5

30 *4.7K_4

GP

R4

IO_SUS8

09 4.7K_4

GP

R4

IO_SUS9

14 *10K_4

GP

R4

IO_SUS10

99 *10K_4

GP

R3

IO_SUS6

GP

GP

IO_SUS7

GP

R4

IO_SUS3

63 *10K_4

GN

IO_SUS7 [5]

GP

D

CL

K_PCIE_NGFFN[19]

CL

K_PCIE_NGFFP[19]

CL

K_PCIE_WLANN[20]

CL

K_PCIE_WLANP[20]

CL

K_PCIE_LANN[12]

CL

K_PCIE_LANP[12]

GN

41 2.49K_4

R1

15 49.9_4

R1

D

12/29

R5

R1

D

GN

BO

BO

BO

BO

BO

BO

81 *100_4

56 100_4

AL25_IN

XT

AL25_OUT

XT

LK_ICOMP

IC

LK_RCOMP

IC

ARD_ID0

ARD_ID1

ARD_ID2

ARD_ID3

ARD_ID4

ARD_ID5

SO

11/28 modify

R5

8 1K_4

3

R8

_Override[22]

EC

A A

5 *short_4

SO

C_Override_NM

2

2N7002K

Q1

4

1

GN

D

IO_SUS0

GP

IO_SUS1

GP

IO_SUS2

GP

IO_SUS3

GP

IO_SUS4

GP

IO_SUS5

GP

IO_SUS6

GP

IO_SUS7

GP

IO_SUS8

GP

IO_SUS9

GP

IO_SUS10

GP

C_GPIO_RCOMP

GP

IO_SUS5

4

M22

M26

AH45

AM40

AM41

AM44

AM45

AM47

AK48

AM48

AK41

AK42

AD51

AD52

AH50

AH48

AH51

AH52

AG51

AG53

AF52

AF51

AE51

AC51

AH40

P24

J26

N26

P20

N20

P26

K26

C21

A21

B20

C19

B18

C18

A17

C17

C9

Y13

Y12

V13

V12

V14

IC

IC

RS

RS

IC

IC

RS

RS

RS

RS

PC

PC

PC

PC

PC

PC

PC

PC

A9

MF

MF

B8

MF

B7

MF

B5

MF

B4

MF

S

S

SPI

SPI

SPI

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

GP

SEC

SEC

SEC

SEC

GP

Y3

GP

U23E

LK_OSCIN

LK_OSCOUT

VD_J26

VD_N26

LK_ICOMP

LK_RCOMP

VD_P26

VD_K26

VD_M26

VD_AH45

IE_CLK_DIFF_N_ 0

IE_CLK_DIFF_P_0

IE_CLK_DIFF_N_ 1

IE_CLK_DIFF_P_1

IE_CLK_DIFF_N_ 2

IE_CLK_DIFF_P_2

IE_CLK_DIFF_N_ 3

IE_CLK_DIFF_P_3

_PLT_CLK0

_PLT_CLK1

_PLT_CLK2

_PLT_CLK3

_PLT_CLK4

_PLT_CLK5

PI1_CS0_B

PI1_CS1_B

1_MISO

1_MOSI

1_CLK

IO_DFX0

IO_DFX1

IO_DFX2

IO_DFX3

IO_DFX4

IO_DFX5

IO_DFX6

IO_DFX7

IO_DFX8

IO_SUS0

IO_SUS1

IO_SUS2

IO_SUS3

IO_SUS4

IO_SUS5

IO_SUS6

IO_SUS7

_GPIO_SUS9

_GPIO_SUS8

_GPIO_SUS10

_GPIO_SUS11

IO0_RCOMP

IO0_ALERT

VLV_M_D/BGA

REV = 1.15

3

+1

.8V_S5[4,5,7,9,13,14,22,24,26,28,29]

+3

VPCU[8,9,12,15,16,18,19,21,22,24,25,26]

+1

.05V_S5[8,26,28,29]

AD12

RT1_RXD

AD10

AD14

AD13

Y7

Y6

V10

V9

AE3

C15

A13

C12

B14

C13

N16

C14

M16

AF2

F14

D14

B12

P18

J16

D18

F18

G16

M18

K18

F16

G18

AD40

AD41

AD42

C11

B10

F12

F10

D12

E8

C7

D6

J12

F7

J14

L13

ARD ID

ARD_ID0

ARD_ID1

ARD_ID2

ARD_ID3

ARD_ID4

ARD_ID5

UA

RT1_TXD

UA

PU_EVENT#_Q

DG

_CLAMP_REQ#_Q

FB

PU_EN

VG

PU_HOLD_RST#_Q

DG

PU_PWR_EN_Q

DG

PU_PWROK_Q

DG

S_PWRDOW NACK

SU

U_WIFI_SUSCL K_R

PM

P_S0IX#

SL

P_S4#

SL

P_S3#

SL

_PRESENT

AC

C_PMC_WAKE

SO

U_BATLOW#

PM

C_PWRBTN#

SO

C_REST_BTN#

SO

C_PLTRST#

SO

H_SUS_STAT#

PC

C_RTEST#

SO

T_CRST#

SR

C_RSMRST#

SO

RE_PWROK

CO

C_X1

RT

C_X2

RT

TC_EXTPAD

BR

D_ALERT#_SOC

SVI

D_DATA_SOC

SVI

D_CLK_SOC

SVI

_INT#

TP

ensor_INT

Gs

_INT_C

TP

_RST#_Q

TP

H_ODD_EN

PC

_INT#

TP

_INT_C

TP

_RST#_Q

TP

ensor_INT

Gs

BO

ARD_ID1

R6

01 NGS@10K_4

R3

86 *10K_4

R3

87 *10K_4

R3

88 NTPM@10K_4

R3

89 10K_4

R3

90 NAC@10K_4

82 *short_4

R4

C7

R1

R4

R4

R4

45

TP

UA

RT1_RXD

UA

RT1_TXD

U

ART1_RTS_B

U

ART1_CTS_B

UA

RT2_RXD

UA

RT2_TXD

U

ART2_RTS_B

U

ART2_CTS_B

SU

SPWRDNACK

PM

U_SUSCLK

P

MU_SLP_S0IX_B

P

MU_SLP_S4_B

P

MU_SLP_S3_B

PM

U_AC_PRESENT

PM

U_WAKE_B

P

MU_BATLOW_B

P

MU_PWRBTN_B

P

MU_RESETBUTTON_B

P

MU_PLTRST_B

S

US_STAT_B

P

MU_SLP_LAN_B

P

MU_WAKE_LAN_B

R

TEST_B

S

RTCRST_B

R

SMRST_B

CO

REPWROK

BR

TCX1_PAD

BR

TCX2_PAD

BVC

CRTC_EXTPAD

RS

VD_VSS

S

VID0_ALERT_B

SVI

D0_DATA

SVI

D0_CLK

RS

VD_C11

RS

VD_B10

RS

VD_F12

RS

VD_F10

RS

VD_D12

RS

VD_E8

RS

VD_C7

RS

VD_D6

RS

VD_J12

RS

VD_F7

RS

VD_J14

RS

VD_L13

OF 12

5

R4

IO8[13]

GP

+1

.8V_S5

R6

00 *GS@10K_4

R3

69 10K_4

R3

70 10K_4

R3

71 *TPM@10K_4

R3

72 *10K_4

R3

73 *AC@10K_4

BOARD_ID0 :"H" W/ G-Sensor; "Low " W/O G-Sensor

BOARD_ID1 :"H" W/ touch panel; "Low " W/O touch panel

BOARD_ID2 :"H" is UMA ; "Low " is DIS

BOARD_ID3 :TPM ; HIGH=TPM, LOW=W/O TPM

BOARD_ID4 :"L" is for Z8AD,MB ID

BOARD_ID5 :IOAC ; High=IOAC ,Low=non-IOAC

4 *short_4

BO

BO

BO

BO

BO

BO

BO

7 0.1U/16V_4

00 10K_4

52 *short_4

49 *short_4

57 *short_4

46

TP

2/11

32

TP

28

TP

30

TP

31

TP

26

TP

23

TP

27

TP

24

TP

TP

PC

+1

.8V_S5

6710K_4

R3

0210K_4

R4

7510K_4

R3

8510K_4

R3

SU

SPWRDANCK [14]

SL

P_S0IX# [14,26]

SL

P_S4# [2,14]

SL

P_S3# [14,26]

AC

_PRESENT [5]

SO

C_PMC_WAKE [14]

SO

C_PWRBTN# [14]

SO

C_PLTRST# [14,21]

PC

H_SUS_STAT# [14]

SO

C_RSMRST# [1 4]

CO

RE_PWROK [14]

GN

D

GN

D

_SVID_ALERT#

VR

_SVID_DATA

VR

_SVID_CLK

VR

TP

_INT# [14]

Gs

ensor_INT [21]

TP

_INT_C [1 4]

_RST#_Q [14]

H_ODD_EN [16]

+3

2

VR

To

Touch panel

11/26 modify

RT

C Circuitry(RTC)

V_RTC_0

+3

V_RTC_0

12

CN2

1

BAT_CONN

GN

D

VR

_SVID_ALERT# [2 8,29]

VR

_SVID_DATA [28,2 9]

_SVID_CLK [28 ,29]

uch pad

20mils

VPCU

+3

R5

59 1K_4

20M

H_SUS_STAT#

PC

U_BATLOW#

PM

S_PWRDOW NACK

SU

C_PMC_WAKE

SO

_PRESENT

AC

P_S4#

SL

P_S3#

SL

P_S0IX#

11/28 modify

*0.1u/16V_4

D3

0

VC

CRTC_1

BAT54C

20MIL

IL 20MIL

SL

C_REST_BTN#

SO

C_PLTRST#

SO

_PRESENT

AC

SPWRDANCK

SU

RE_PWROK

CO

Change from +1.0V to +1.05V

53

C3

D

GN

D_DATA_SOC

SVI

D_ALERT#_SOC

SVI

D_CLK_SOC

SVI

C Clock 32.768KHz

RT

C_X1

RT

RT

C_X2

+3

V_RTC

R3

68 20K_4

30mils

R3

65 20K_4

C4

14

1u/6.3V_4

6/25 Change G9G10 footprint from

"SOLDERJUMPER-2" to "RC0603-C" for

SMT request

1

47 *10K_4

R3

84 10K_4

R3

81 10K_4

R4

01 10K_4

R4

66 10K_4

R3

3 *10K_4

R2

4 *10K_4

R2

3 *10K_4

R4

79 2.7K_4

R4

5 *1K_4

R6

55 *10K_4

R3

83 *100K_4

R4

8 0.1U/16V_4

C7

+1.05V_S5

53

50

R4

R4

*200_4

3

R3

10M_4

2013/07/25

change package , P/N change

from BG332768224 to

BG332768453

C3

1u/6.3V_4

C3

1u/6.3V_4

*301_4

200_4

12

Y6

768KHZ

32.

12

G6

47

*S

38

+1

58

R4

SO

C_RTEST#

HORT_ PAD1

SR

T_CRST#

.8V_S5

C4

C4

GN

D

GN

D

GN

D

115P/50V_4

215P/50V_4

GN

D

Qu

Qu

Qu

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

PROJECT :

PROJECT :

Si

Si

Size Document Number Rev

ze Document Number Rev

ze Document Number Rev

We

We

We

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

5

4

3

2

dnesday, April 08, 2015

PROJECT :

lley 5/9 (SPI/GPIO/CLK)

lley 5/9 (SPI/GPIO/CLK)

lley 5/9 (SPI/GPIO/CLK)

Va

Va

Va

Z8AD

Z8AD

Z8AD

3A

3A

3A

of

326

of

326

of

1

326

5

+1

.8V_S5 [4,5,6,9,13,14,22,24,26,28,29]

+3

V [4,9,11,12,13,14,15,16,18,19,21,22,25,27,28,29,30]

US

B30_TX0+[17]

US

B30_TX0-[17]

US

B30_RX0+[17]

US

B30_RX0-[17]

D D

06

R1

402_4

C C

37 22_4

CL

GN

.8V_S5

K_24M_KBC[22]

CL

KRUN#[15,22]

LF

RAME#[15,19,20,22]

SO

C_SERIRQ[14,15]

14 100_4

R1

D

85 1K_4

R1

86 1K_4

R1

R5

08 1K_4

R5

09 *short_4

46 22_4

P_H_TDO

XD

P_H_TMS

XD

P_H_TDI

XD

P_H_PREQ#

XD

P_H_TRST#

XD

P_H_TCK

XD

VD_M13

RS

R4

R4

5

43 TPM@22_4

For TPM

SM

+1

B1ALERT#[16]

CL

K_24M_DEBUG[19,20]

CL

K_TPM[15]

+1

.8V_S5

27 51_4

R1

28 51_4

R1

B B

A A

GN

R4

R1

R4

R1

R4

D

44 51_4

26 51_4

45 51_4

67 51_4

15 *10K_4

R4

42 22_4

R4

RAME#

LF

D0

LA

D0[15,19,20,22]

LA

D1[15,19,20,22]

LA

D2[15,19,20,22]

LA

D3[15,19,20,22]

LA

D1

LA

D2

LA

D3

LA

TP

29

B_SOC_DATA

SM

B_SOC_CLK

SM

SM

B_SOC_ALERTB

B3_OBSP

US

B3_OBSN

US

SO

SO

SO

SO

LP

P_H_TCK

XD

P_H_TDI

XD

P_H_TDO

XD

P_H_TMS

XD

P_H_TRST#

XD

P_H_PRDY#

XD

P_H_PREQ#

XD

VD_M13

RS

4

C_CLKOUT_0

C_CLKOUT_1

C_CLKRUN#

C_SERIRQ

C_RCOMP

4

GN

B32

C32

F28

D28

A33

C33

F30

D30

C34

B34

G32

J32

C35

A35

G34

J34

D34

F34

C37

A37

F36

D36

M34

M32

C38

B38

G36

J36

N34

P34

P2

R3

T3

P3

M3

M2

N3

N1

T2

T4

AF42

AD47

AF40

AD48

AB48

AD45

AF41

M13

AM7

AM6

AM9

D

U23F

US

B3_TXP0

US

B3_TXN0

US

B3_RXP0

US

B3_RXN0

US

B3_TXP1

US

B3_TXN1

US

B3_RXP1

US

B3_RXN1

US

B3_TXP2

US

B3_TXN2

US

B3_RXP2

US

B3_RXN2

US

B3_TX3

US

B3_TXN3

US

B3_RXP3

US

B3_RXN3

US

B3_OBSP

US

B3_OBSN

RS

VD_C37

RS

VD_A37

RS

VD_F36

RS

VD_D36

RS

VD_M34

RS

VD_M32

RS

VD_C38

RS

VD_B38

RS

VD_G36

RS

VD_J36

RS

VD_N34

RS

VD_P34

MF

_LPC_CLKOUT0

MF

_LPC_CLKOUT1

LP

C_CLKRUNB

LP

C_FRAMEB

MF

_LPC_AD0

MF

_LPC_AD1

MF

_LPC_AD2

MF

_LPC_AD3

IL

B_SERIRQ

LP

C_HVT_RCOMP

TC

K

TD

I

TD

O

TM

S

T

RST_B

C

X_PRDY_B

C

X_PREQ_B

RS

VD_M13

MF

_SMB_DATA

_SMB_CLK

MF

F_SMB_ALERTB

M

VLV_M_D/BGA

REV = 1.15

C1

85 0.1U/25V_4

SM

B_SOC_DATA

SM

B_SOC_CLK

+1

.8V_S5

1

2

4

3

1

U1

D

GN

EF1

VR

A1

SD

L1

SC

PCA9306

3

B_OTG_ID

US

B_DP0

US

B_DN0

US

B_DP1

US

B_DN1

US

B_DP2

US

B_DN2

US

B_DP3

US

B_DN3

US

B_DP4

US

B_DN4

US

B_OC_00

US

B_OC_11

RS

VD_B46

B_VBUSSNS

B_RCOMP

RS

VD_H5

RS

VD_H7

RS

VD_P28

RS

VD_P30

RS

VD_AF50

RS

VD_AF48

RS

VD_AF44

RS

VD_AF45

I2

C0_SDA

I2

C0_SCL

I2

C1_SDA

I2

C1_SCL

I2

C2_SDA

I2

C2_SCL

I2

C3_SDA

I2

C3_SCL

I2

C4_SDA

I2

C4_SCL

I2

C5_SDA

I2

C5_SCL

I2

C6_SDA

I2

C6_SCL

VD_Y2

RS

VD_AA3

RS

B48

C42

B42

C43

B44

C41

A41

C45

A45

B40

C40

P14

P16

B46

B47

A48

M36

N36

K38

M38

N38

H5

H7

P28

P30

AF50

AF48

AF44

AF45

AH7

AK6

AH6

AF6

AF7

AF9

AD2

AE4

AD3

AC1

AC3

AB2

AB3

AA1

Y2

AA3

B2_OBSP

US

B_VBUSSNS

US

B_RCOMP

US

B_HSIC_RCOMP

US

C_0_SDA_R

I2

C_0_SCL_R

I2

C_1_SDA

I2

C_1_SCL

I2

C_2_SDA_R

I2

C_2_SCL_R

I2

C_3_SDA

I2

C_3_SCL

I2

C_4_SDA

I2

C_4_SCL

I2

C_5_SDA

I2

C_5_SCL

I2

C_6_SDA

I2

C_6_SCL

I2

I2

C_NFC_SOC_SDA

I2

C_NFC_SOC_SCL

D

GN

1810K_4

R4

1910K_4

R4

1 *49.9_4

R9

10 *short_4

R5

15 *short_4

R5

90 *short_4

R4

01 *short_4

R5

03 *short_4

R5

92 *short_4

R4

R2

16

2.2K_4

R2

2.2K_4

T7

T6

17

US

US

US

US

B_HSIC_0_STROBE

US

B_HSIC_0_DATA

US

B_HSIC_1_STROBE

US

B_HSIC_1_DATA

US

B_HSIC_RCOMP

6

OF 12

+3

V

R2

18

200K_4

8

C2

EN

EF2

VR

A2

SD

L2

SC

06 0.1U/25V_4

7

5

6

3

US

BP0+ [17]

US

BP0- [17]

US

BP1+ [17]

US

BP1- [17]

US

BP2+ [13]

US

BP2- [13]

US

BP3+ [13]

US

BP3- [13]

US

BP4+ [19,20]

US

BP4- [19,20]

SO

C_USB_OC0 [17]

83 *short_4

R3

82 *0_4

R3

81 113_4

R3

B_RUN_DAT [11,20,21]

SM

B_RUN_CLK [11,20, 21]

SM

2

+1

.8V_S5

R1

I2

C_0_SDA [14]

I2

C_0_SCL [14]

I2

C1_SDA_GPIO6 [13]

I2

C1_SCL_GPIO7 [13]

I2

C_2_SDA [21]

I2

C_2_SCL [21]

2

Port 1 is debug port

USB3. 0

US

B2

uchPanel

To

CAMERA

BT

.8V_S5

+1

GN

D

GN

D

D

GN

D

GN

1145.3_4

GN

Touch pad

G S

1

61

R3

*20K_4

36

C3

*0.1U/16V_4

D

Touch panel

ensor

C_0_SDA

I2

C_0_SCL

I2

C_1_SDA

I2

C_1_SCL

I2

C_2_SDA_R

I2

C_2_SCL_R

I2

C_3_SDA

I2

C_3_SCL

I2

I2

C_4_SDA

I2

C_4_SCL

I2

C_5_SDA

I2

C_5_SCL

I2

C_6_SDA

I2

C_6_SCL

I2

C_NFC_SOC_SDA

I2

C_NFC_SOC_SCL

Si

Si

Size Document Number Rev

ze Document Number Rev

ze Document Number Rev

We

We

We

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

Date: Sheet

dnesday, April 08, 2015

11 1K_4

R5

16 1K_4

R5

89 1K_4

R4

00 1K_4

R5

02 1K_4

R5

91 1K_4

R4

64 1K_4

R4

80 1K_4

R4

R4

65 *1K_4

R4

66 *1K_4

R4

67 *1K_4

R4

68 *1K_4

R4

69 *1K_4

R4

70 *1K_4

R4

72 *1K_4

R4

71 *1K_4

change to 1K as CRB

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

Qu

Qu

Qu

PROJECT :

PROJECT :

PROJECT :

Valley 6/9 (USB/LPC/I2C)

Valley 6/9 (USB/LPC/I2C)

Valley 6/9 (USB/LPC/I2C)

1

+1

.8V_S5

Z8AD

Z8AD

Z8AD

3A

3A

3A

of

327

of

327

of

327

5

+V

CC_CORE [28]

+V

GG [29]

+3

V [4,7,9,11,12,13,14,15,16,18,19,21,22,25,27,28,29,30]

+1

.05V_S5 [6,26,28,29]

+1

.15V [26]

VC

C1_SENSEP[28]

VC

C1_SENSEN[28]

VG

G_SENSEP[29]

VG

69

C1

1U/10V_4

CO

DDI

FU

5

C1

10u/6.3V_6

G_SENSEN[29]

+V

64

C1

22uF/6.3V_6

+V

50

C1

22uF/6.3V_6

+V

GG

57

D

GN

RE_V1P15_PWR

CO

67

C1

1U/10V_4

RE_V1P15_PWR

_1P15_PWR

SE_1P15_PWR

CC_CORE

CC_CORE

77

C1

10u/6.3V_6

D D

60

C1

22uF/6.3V_6

D

GN

52

C1

22uF/6.3V_6

D

54

GN

95

C5

22uF/6.3V_6

96

C5

*22uF/6.3V _6

C C

C1

*1U/10V_4

1/7 add

58

97

C1

C5

*10u/6.3V_6

B B

1/13 Add

+1

.15V

A A

D

GN

76 *short_8

R1

R1

83 *short_8

R1

92 *short_8

R1

91 *short_8

R1

66

1U/10V_4

*SHORT_6

3/16 change 0 ohm by acer

C1_SENSEP

VC

C1_SENSEN

VC

T8

Fixed Vnn Sense

C1

10u/6.3V_6

_1P15_PWR

DDI

70

1U/10V_4

56

C1

1U/10V_4

59

C1

4.7uF/6.3V_6

63

C1

4.7uF/6.3V_6

80

C1

C1

10U/6.3V_6

GN

D

61

C1

4.7uF/6.3V_6

62

C1

4.7uF/6.3V_6

72

C1

1U/10V_4

C1

D

GN

R4

R4

R4

R4

79

C1

22uF/6.3V_6

C1

1U/10V_4

83

1U/10V_4

01

872.2_4

982.2_4

862.2_4

972.2_4

68

C0_SENSEP_R

VC

C0_SENSEN_R

VC

C1_SENSEP_R

VC

C1_SENSEN_R

VC

VG

VG

VN

65

C1

4.7uF/6.3V_6

51

C1

4.7uF/6.3V_6

C1

22uF/6.3V_6

SE_1P15_PWR

FU

84

C1

1U/10V_4

C5

1

10U/6.3V_6

+V

GG

C5

98

*100U/6.3V_ 1206

GN

D

G_SENSEP

G_SENSEN

N_REFIN_R

78

1/13 Add

4

AG32

AJ32

AD29

AF27

AD24

AD22

AC27

AF36

AG33

AG35

AG36

AG38

AJ33

AJ36

AJ38

AF30

AG27

AG29

AG30

AJ27

AJ29

AJ30

AF29

AD16

AD18

AD19

AF16

AF18

AF19

AF21

AF22

AJ19

AG16

AG18

AG19

AG21

AG22

AG24

AJ21

AJ22

AJ24

AK24

AK30

AK35

AK36

AM29

AK33

AJ35

AM19

AK21

C5

4

10U/6.3V_6

4

U23G

CO

RE_VCC0_SENSE

CO

RE_VSS0_SENSE

CO

RE_VCC1_SENSE

CO

RE_VSS1_SENSE

DDI

_VGG_SENSE

UNCO

RE_VSS_SENSE[2]

UNCO

RE_VSS_SENSE[1]

CO

RE_VCC1_S0IX[3]

CO

RE_VCC1_S0IX[7]

CO

RE_VCC1_S0IX[8]

CO

RE_VCC1_S0IX[9]

CO

RE_VCC1_S0IX[10]

CO

RE_VCC1_S0IX[14]

CO

RE_VCC1_S0IX[15]

CO

RE_VCC1_S0IX[16]

CO

RE_VCC1_S0IX[2]

CO

RE_VCC1_S0IX[4]

CO

RE_VCC1_S0IX[5]

CO

RE_VCC1_S0IX[6]

CO

RE_VCC1_S0IX[11]

CO

RE_VCC1_S0IX[12]

CO

RE_VCC1_S0IX[13]

CO

RE_VCC1_S0IX[1]

DDI

_VGG_S0IX[1]

DDI

_VGG_S0IX[2]

DDI

_VGG_S0IX[3]

DDI

_VGG_S0IX[4]

DDI

_VGG_S0IX[5]

DDI

_VGG_S0IX[6]

DDI

_VGG_S0IX[7]

DDI

_VGG_S0IX[8]

DDI

_VGG_S0IX[15]

DDI

_VGG_S0IX[9]

DDI

_VGG_S0IX[10]

DDI

_VGG_S0IX[11]

DDI

_VGG_S0IX[12]

DDI

_VGG_S0IX[13]

DDI

_VGG_S0IX[14]

DDI

_VGG_S0IX[16]

DDI

_VGG_S0IX[17]

DDI

_VGG_S0IX[18]

DDI

_VGG_S0IX[19]

CO

RE_V1P15_S0IX[1]

CO

RE_V1P15_S0IX[2]

CO

RE_V1P15_S0IX[3]

CO

RE_V1P15_S0IX[4]

FU

SE_V1P15_S0IX[2]

FU

SE_V1P15_S0IX[1]

DDI

_V1P15_S0IX[2]

DDI

_V1P15_S0IX[1]

VLV_M_D/BGA

V = 1.15

RE

C5

10U/6.3V_6

3

RS

VD_AA30

+1

.05V_S5

AA18

AA19

AA21

AA22

AA24

AA25

AC18

AC19

AC21

AC22

AC24

AC25

AD25

AD27

AA30

V33

AA32

AA33

AA35

AA36

AC32

Y30

Y32

Y33

Y35

V19

V18

AM21

AM33

AM22

AN22

AN32

AM32

V22

V24

U24

U22

V27

U27

V29

N18

U19

3

R1

R1

R1

R1

R1

R7

R7

R8

R7

R6

CSRANSOCI_OBS

VC

LK_1P05_PWR

IC

1P05_PWR

DDR_

PD_1P05_PWR

BM

BSSIC_1P05_PWR

US

SE3_1P05_PWR

FU

SE_1P05_PWR

FU

1

C8

1U/10V_4

D

GN

22 *short_8

49 *short_8

50 *short_8

89 *short_8

84 *short_8

5 *SHORT_6

3 *SHORT_6

0 *SHORT_6

9 *SHORT_6

6 *SHORT_6

49

C1

1U/10V_4

R1

C1

C1

6

C6

1U/10V_4

7

C6

1U/10V_4

CO

RE_1P05_PWR

IC

LK_1P05_PWR

DDR_

1P05_PWR

US

BSSIC_1P05_PWR

BM

PD_1P05_PWR

FU

SE3_1P05_PWR

FU

SE_1P05_PWR

FU

SE1_1P05_PWR

53 *0_4

44 1U/10V_4

40 *1U/10V_4

71

C1

1U/10V_4

0

C8

1U/10V_4

GN

45

C1

1U/10V_4

37

C1

1U/10V_4

C1

10U/6.3V_6

6

C7

1U/10V_4

D

GN

D

C1

GN

D

86

GN

1

C6

1U/10V_4

D

GN

SE1_1P05_PWR [9]

FU

29

C1

1U/10V_4

04

1U/10V_4

C1

10U/6.3V_6

D

87

GN

UNCO

RE_VNN_S4[1]

UNCO

RE_VNN_S4[2]

UNCO

RE_VNN_S4[3]

UNCO

RE_VNN_S4[4]

UNCO

RE_VNN_S4[5]

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

RE_V1P15_S0IX[6]

UNCO

RE_V1P15_S0IX[1]

UNCO

RE_V1P15_S0IX[2]

UNCO

RE_V1P15_S0IX[3]

UNCO

RE_V1P15_S0IX[4]

UNCO

RE_V1P15_S0IX[5]

UNCO

RE_V1P15_S0IX[7]

UNCO

RE_V1P15_S0IX[8]

UNCO

RE_V1P15_S0IX[9]

UNCO

RE_V1P15_S0IX[10]

IC

IC

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

PC

IE_V1P05A_G3[1]

PC

IE_V1P05A_G3[2]

SAT

A_V1P05A_G3[2]

SAT

A_V1P05A_G3[1]

US

B3_V1P05A_G3[2]

US

B3_V1P05A_G3[1]

US

BSSIC_V1P05A_G3

RE_VNN_S4[6]

RE_VNN_S4[7]

RE_VNN_S4[8]

RE_VNN_S4[9]

RE_VNN_S4[10]

RE_VNN_S4[11]

RE_VNN_S4[12]

RE_VNN_S4[13]

RE_VNN_S4[14]

LK_GND_OFF[2]

LK_GND_OFF[1]

V1P05A_G3[1]

V1P05A_G3[4]

V1P05A_G3[2]

V1P05A_G3[5]

V1P05A_G3[6]

V1P05A_G3[3]

3.5A

6.4A

1.9A

11A

0.7A

FU

SE3_V1P05A_G5

FU

SE_V1P05A_G3

7 OF 12

+1

.05V_S5

C5

5

0

10U/6.3V_6

C8

D

C1

10U/6.3V_6

CO

36

C1

1U/10V_4

6

1U/10V_4

2

28

RE_1P05_PWR

C1

C7

2

C9

10U/6.3V_6

05

1U/10V_4

2

1U/10V_4

1

.05V_S5

+1

41

C1

*1U/10V_4

18

hrm Protect

+3

VPCU

Si

Si

Size Document Number Rev

ze Document Number Rev

ze Document Number Rev

We

We

We

Date: Sheet

Date: Sheet

Date: Sheet

IO T

03

R4

*10K_4

de

fault 25 degree for detect tempera ture

TH

RM_MOINTO R [22]

04

R4

*0_4

TH

ER_CPU

R3

92

*10K_6_NTC

dnesday, April 08, 2015

dnesday, April 08, 2015

dnesday, April 08, 2015

49

C3

*0.1U/16V_4

1 2

Qu

Qu

Qu

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

lley 7/9 (Power 1)

lley 7/9 (Power 1)

lley 7/9 (Power 1)

Va

Va

Va

1

Z8AD

Z8AD

Z8AD

of

of

of

3A

3A

3A

328

328

328

26

C1

*1U/10V_4

30

C1

*1U/10V_4

C1

*1U/10V_4

GN

C1

1U/10V_4

D

GN

48

2

C5

10U/6.3V_6

D

6

+1

+3

+3

+3

+1

+1

D D

+1

.35VSUS

94

C1

22uF/6.3V_6

D

GN

3_3P3_PWR

CF

C C

B B

A A

+1

CF

CO

GP

GP

.8V_S5

1_3P3_PWR

RE_1P8_PWR

IOCF2_1P8_PWR

IOCF1_1P8_PWR

+1

.35VSUS

5

.35VSUS [2,3,11,27]

V_RTC [6]

V_S5 [2,3,5,12,14,15,16,22,26]

VPCU [6,8,12,15,16,18,19,21,22,24,25,26]

.8V_S5 [4,5,6,7,13,14,22,24,26,28,29]

.24VS5 [26]

LLDDR_1P35_PWR

+P

LKDDR_1P35_PWR

+C

82

C1

22uF/6.3V_6

12

R1

17

R1

80

R1

R1

81

R2

10 *short_8

R2

11 *short_8

GN

GN

5

GN

GN

GN

D

D

*SHORT_6

*SHORT_6

*SHORT_6

*SHORT_6

D

D

D

GN

D

GN

D

92

C1

22uF/6.3V_6

C8

C7

C7

C1

C1

C1

C1

C1

C1

SE_1P8_PWR

FU

IOCF2_1P8_PWR

GP

B_1P8_PWR

US

GP

IOCF1_1P8_PWR

+P

LLDDR_1P35_PWR

+C

LKDDR_1P35_PWR

5 1U/10V_4

1 1U/10V_4

9 1U/10V_4

55 1U/10V_4

20 1U/10V_4

27 1U/10V_4

21 1U/10V_4

73 1U/10V_4

74 1U/10V_4

96 1U/10V_4

C1

00 22uF/6.3V_6

C2

C1

99 22uF/6.3V_6

C1

97 1U/10V_4

1.9A

95

C1

22uF/6.3V_6

GN

C1

91

*1U/16V_4

D

GN

0.2A

C1

*1U/16V_4

D

AN27

AM25

BE1

BE53

BJ2

BJ3

BJ49

BJ5

BH50

BH5

BH49

BH4

BE3

BG51

BG3

BJ51

BJ52

AY10

AY44

AV44

AV10

BE51

AV38

AV16

AU36

AU18

AN36

AN35

AN19

AN18

AM36

AM18

E1

E2

G1

AH4

AF4

Y18

AD33

AK18

AF33

AK19

+3

.8V_S5

+1

90

U23H

DDRS

FR_VDDQ_G_S4

DDR_

VDDQ_G_S4[2]

DDR_

VDDQ_G_S4[16]

DDR_

VDDQ_G_S4[19]

DDR_

VDDQ_G_S4[26]

DDR_

VDDQ_G_S4[27]

DDR_

VDDQ_G_S4[28]

DDR_

VDDQ_G_S4[29]

DDR_

VDDQ_G_S4[25]

DDR_

VDDQ_G_S4[24]

DDR_

VDDQ_G_S4[23]

DDR_

VDDQ_G_S4[22]

DDR_

VDDQ_G_S4[17]

DDR_

VDDQ_G_S4[21]

DDR_

VDDQ_G_S4[20]

DDR_

VDDQ_G_S4[30]

DDR_

VDDQ_G_S4[31]

DDR_

VDDQ_G_S4[14]

DDR_

VDDQ_G_S4[15]

DDR_

VDDQ_G_S4[13]

DDR_

VDDQ_G_S4[10]

DDR_

VDDQ_G_S4[18]

DDR_

VDDQ_G_S4[12]

DDR_

VDDQ_G_S4[11]

DDR_

VDDQ_G_S4[9]

DDR_

VDDQ_G_S4[8]

DDR_

VDDQ_G_S4[7]

DDR_

VDDQ_G_S4[6]

DDR_

VDDQ_G_S4[5]

DDR_

VDDQ_G_S4[4]

DDR_

VDDQ_G_S4[3]

DDR_

VDDQ_G_S4[1]

SD

IO_V3P3A_V1P8A_G3 [1]

SD

IO_V3P3A_V1P8A_G3 [2]

SD

IO_V3P3A_V1P8A_G3 [3]

UNCO

RE_V1P8A_G3[2]

UNCO

RE_V1P8A_G3[1]

GP

IO_V1P8A_G3[5]

GP

IO_V1P8A_G3[1]

GP

IO_V1P8A_G3[3]

GP

IO_V1P8A_G3[2]

GP

IO_V1P8A_G3[4]

VLV_M_D/BGA

REV = 1.15

+3

V_S5

+3

V

+1

.8V

V_S5

V

+3

+1

.5V

+1

.8V_S5

4

74

R3

TWO PAD SHARING

R7

0

R7

R8

6

R9

R8

R1

R1

4

1.9A

0.6A

OF 12

8

1 *0_6

4 *0_6

13 *0_6

65

63 *0_6

0.6A

RT

RT

*SHORT_6

*SHORT_6

*SHORT_6

*SHORT_6

DDI

_VDDQ_G3[1]

DDI

_VDDQ_G3[2]

MI

PI_V1P2A_G3[2]

MI

PI_V1P2A_G3[1]

IC

LK_VSFR_G3[2]

IC

LK_VSFR_G3[1]

CO

RE_VSFR_G3[5]

CO

RE_VSFR_G3[6]

CO

RE_VSFR_G3[7]

CO

RE_VSFR_G3[4]

CO

RE_VSFR_G3[2]

CO

RE_VSFR_G3[3]

CO

RE_VSFR_G3[1]

US

BHSIC_V1P2A_G3

US

B_VDDQ_G3[2]

US

B_VDDQ_G3[3]

US

B_VDDQ_G3[1]

US

BSSIC_V1P2A_G3

US

B_V1P8A_G3

US

B_V3P3A_G3[2]

US

B_V3P3A_G3[1]

C_V3P3RTC_G5[2]

C_V3P3RTC_G5[1]

RT

C_V3P3A_G5[1]

RT

C_V3P3A_G5[2]

FU

SE_V1P8A_G3

FU

SE1_V1P05A_G4

FU

SE0_V1P05A_G3

RS

RS

RS

B_3P3_PWR

US

3_3P3_PWR

CF

SD3 IO SUPPLY

3/2 add

V36

Y36

T40

P40

Y27

Y25

P38

V30

AC30

AF35

AD35

AD38

AC36

M41

U35

V35

H44

P41

AA29

C23

B22

C5

B6

D4

E3

U16

H10

G10

A3

VD_VSS

K20

VD_K20

M20

VD_M20

CF

1_3P3_PWR

LPC IO SUPPLY

CO

RE_1P8_PWR

AUDIO IO SUPPLY

_FUSE_PW R

TP

_FUSE_LDO

TP

C1

C9

C9

C8

C6

C9

C1

BHSIC_1P24_PWR

US

B_1P24_PWR

US

B2_1P24_PWR

US

BSSIC_1P24_PWR

US

C1

C1

C3

C7

C8

SE_1P8_PWR

FU

SE1_1P05_PWR

FU

3

_1P24_PWR

12 1U/10V_4

2 1U/10V_4

3 1U/10V_4

3 1U/10V_4

2 1U/10V_4

1 1U/10V_4

46 1U/10V_4

47 1U/10V_4

81 1U/10V_4

46 1U/10V_4

3 1U/10V_4

4 1U/10V_4

TP

12

TP

13

FU

SE1_1P05_PWR [8]

R3

10K_4

D

GN

DDI

GN

D

Y_1P24_PWR

DP

GN

D

LK_VSFR_1P24_PWR

IC

GN

D

L_1P24_PWR

PL

GN

D

LCPU_1P24_PW R

PL

GN

D

GN

D

GN

D

B_1P8_PWR

US

GN

D

B_3P3_PWR

US

GN

D

RTC_3P3

+V

C_3P3A_PWR

RT

GN

D

SE_1P8_PWR

FU

91

VSDIO VOLTAGE SETTING (CF3_3P3_PWR)

SDMMC3_PWR_EN_N

3

2

PLACE THE CAPS UNDER THE PKG SHADOW

BHSIC_1P24_PWR

US

D

GN

+1

.24VS5

SE1_1P05_PWR

FU

13

C1

1U/10V_4

D

GN

0

C9

1U/10V_4

D

GN

2

4

C9

1U/10V_4

4 *short_8

R6

08

R1

8

R9

3 *short_8

R6

2 *short_8

R6

0 *short_8

R6

13

R1

62 *short_8

R1

3

R9

1 *short_8

R6

B_1P24_PWR

US

2

C8

1U/10V_4

D

GN

IC

US

*SHORT_6

US

*SHORT_6

US

US

DDI

*SHORT_6

PL

DP

*SHORT_6

PL

Si

Si

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

B2_1P24_PWR

US

8

C6

1U/10V_4

LK_VSFR_1P24_PWR

BSSIC_1P24_PWR

BHSIC_1P24_PWR

B_1P24_PWR

B2_1P24_PWR

_1P24_PWR

LCPU_1P24_PW R

Y_1P24_PWR

L_1P24_PWR

+3

V_S5

9

R6

+3

VPCU

+3

ze Document Number Rev

ze Document Number Rev

R6

CAPS PLACE NEAR SOC PIN

V_RTC

R6

7

Valley 8/9 (Power 2)

Valley 8/9 (Power 2)

Valley 8/9 (Power 2)

We

We

We

dnesday, April 08, 2015

dnesday, April 08, 2015

dnesday, April 08, 2015

8 *0_6

1

BSSIC_1P24_PWR

US

4

C7

1U/10V_4

D

GN

9

C8

1U/10V_4

D

GN

RT

*SHORT_6

*SHORT_6

GN

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

Qu

Qu

Qu

PROJECT :

PROJECT :

PROJECT :

1

GN

C_3P3A_PWR

+V