Page 1

5

4

3

2

1

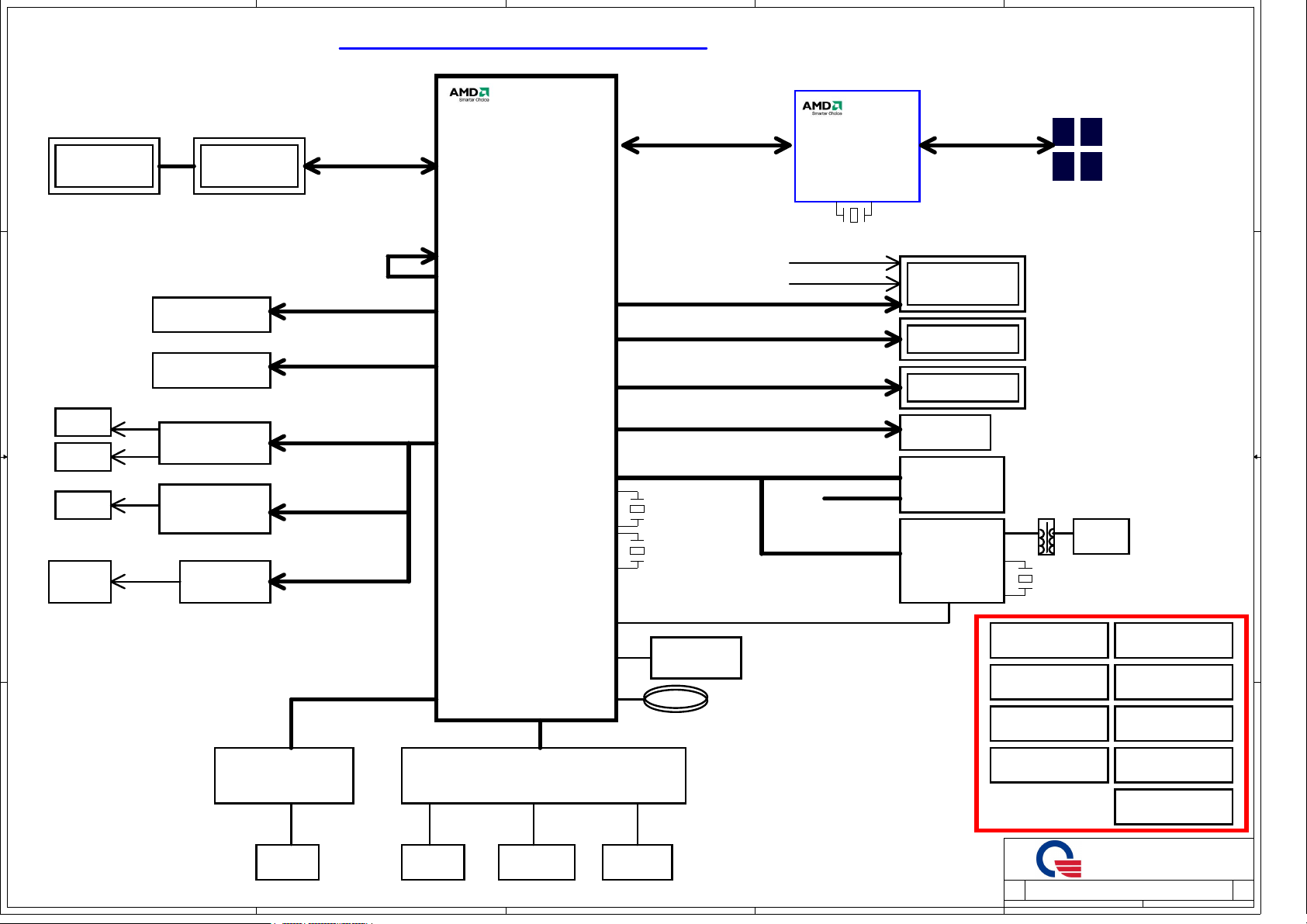

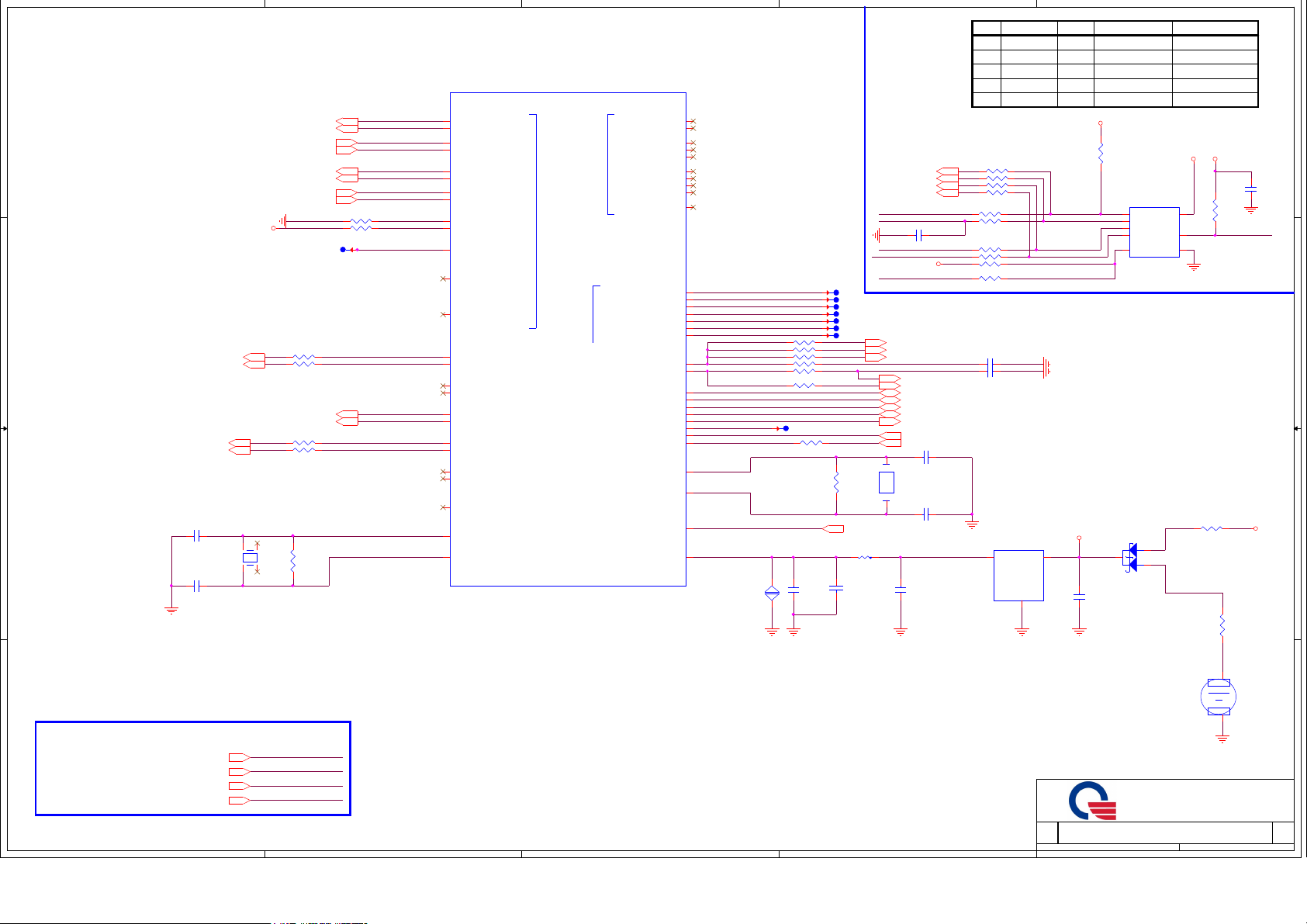

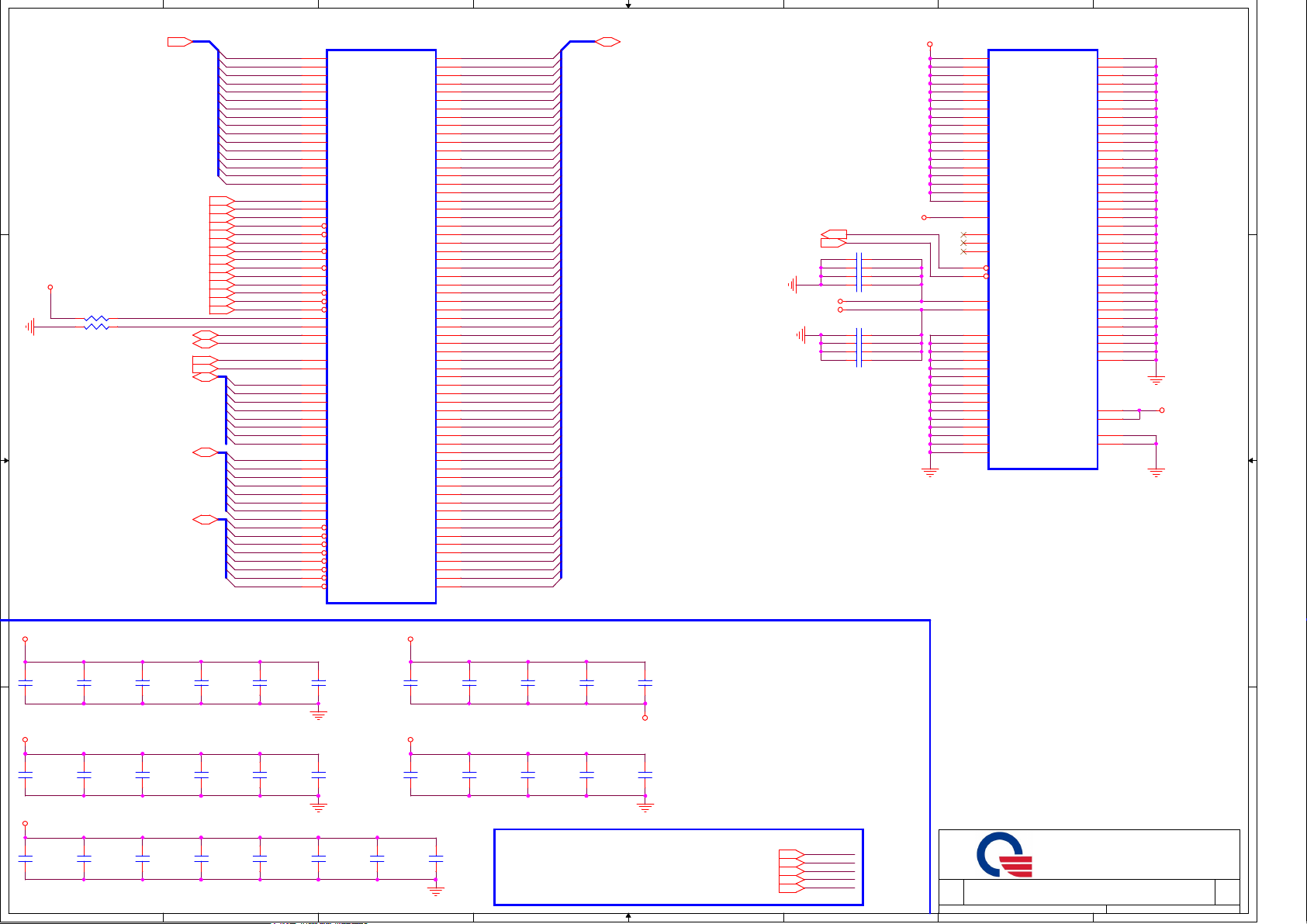

ZQN BLOCK DIAGRAM

D D

DDRIII-SODIMM1

(STD)

DDRIII-SODIMM2

(RVS)

One Channel DDR III

SATA 0

SATA - HDD

C C

SATA 1

SATA - ODD

USB 2.0

Connector

USB 2.0

Connector

CardReader

Connector

USB/IO Board

Connector

GL834L

Card Reader

USB2.0(Port 0 and Port 5)

USB2.0(Port 6)

BEEMA

IMC

CLK

SATA0

SATA1

USB2.0

BGA 769

FT3B

APU

PEG

TX/RX

eDP

Display

HDMI

USB3.0

PCI-E x1

PEG0~3(PCI-E x4)

INT_eDP

INT_CRT

INT_HDMI

USB3

X'TAL

32.768KHz

GPU

Jet XT(25W)

29mm X 29mm

USB-1 (CCD)

USB-3 (TouchS)

PCIE-1

USB-7

X'TAL

27.0MHz

eDP/CCD Con.

USB 3.0

Connector

Channel B

CRT Con.

HDMI Con.

MINI CARD

WLAN

VRAM

VRAM DDR3-512MB*4 = 2GB

SD

X'TAL 48MHz

B B

Touch Pad

Connector

MCU

USB2.0(Port 2)I2C

PCIE-2

RTL8111GS-CG

10/100/1G

X'TAL

25MHz

RJ45

CLK

BQ24737

Batery Charger

TPS51225

3V/5V

TPS51216

+1.5V_SUS

TPS51211

0.95V_S5

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

3

SPI ROM

8M

BATTERY

2

SPI

Azalia

ALC283-CG

AUDIO CODEC

A A

Universal

Jack

5

4

K/B Con.

IHDA

LPC

EC

ITE8587

HALL SENSOR

RTC

Fan Driver

P20

P21

P22

P23

ISL62771

CPU core/VAXG

TPS54318RTER

+1.8V

TPS54318RTER

+1.5V_GFX

TPS54318RTER

+PCIE_VDDC_GFX

TPS51728RHAR

GPU_Core

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZQN

ZQN

ZQN

1

P24

P25

1 39Tuesday, April 29, 2014

1 39Tuesday, April 29, 2014

1 39Tuesday, April 29, 2014

1A

1A

1A

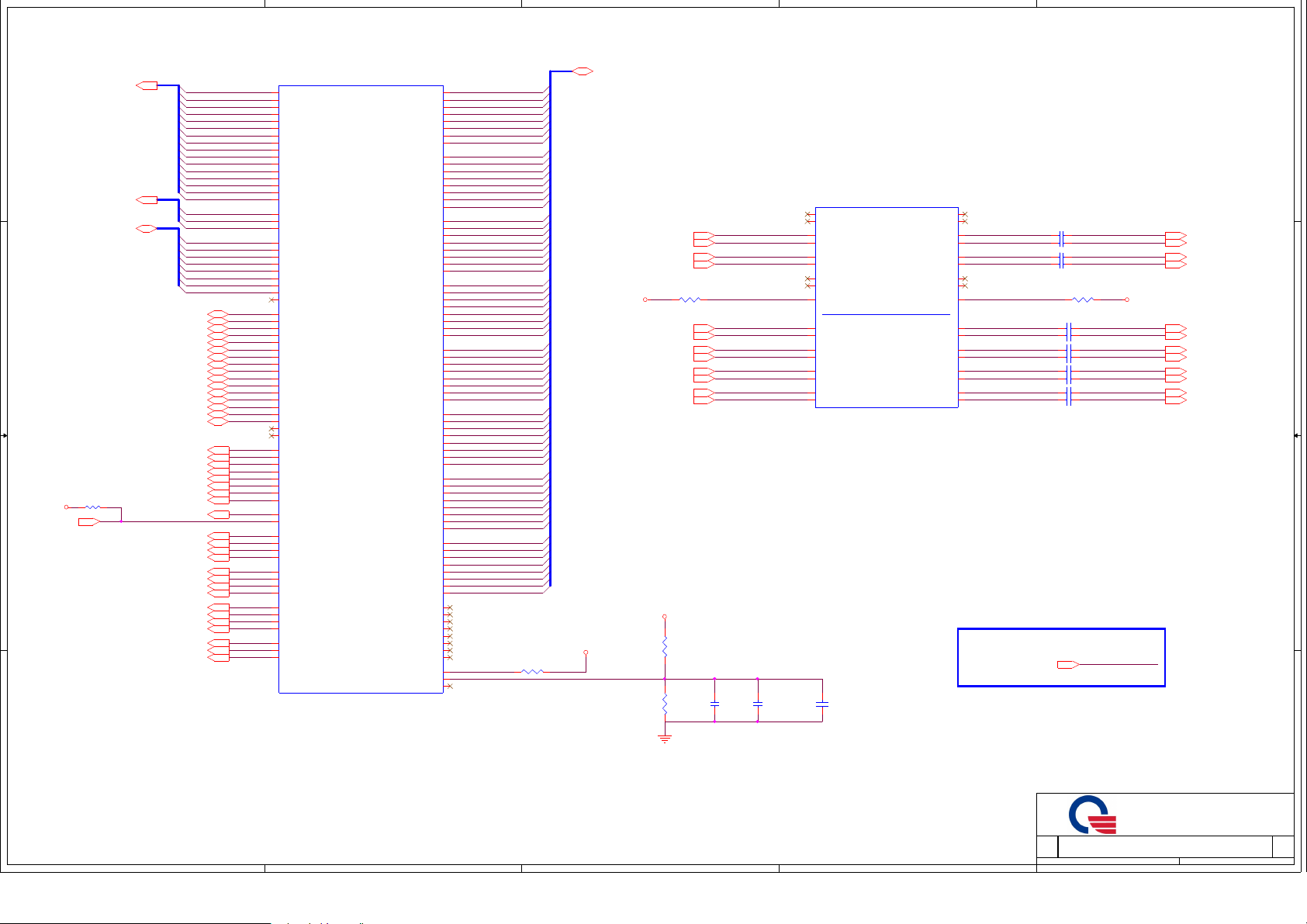

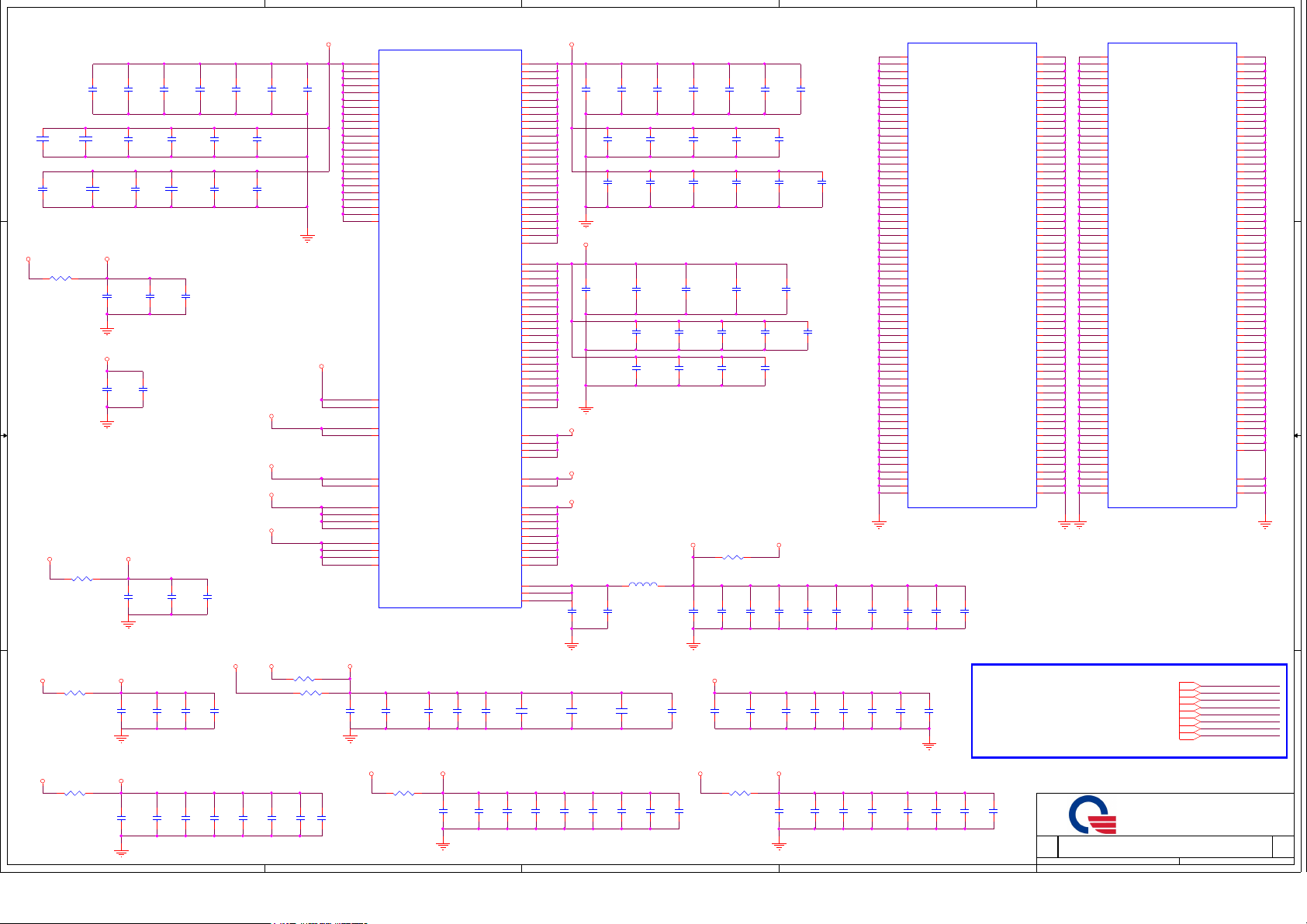

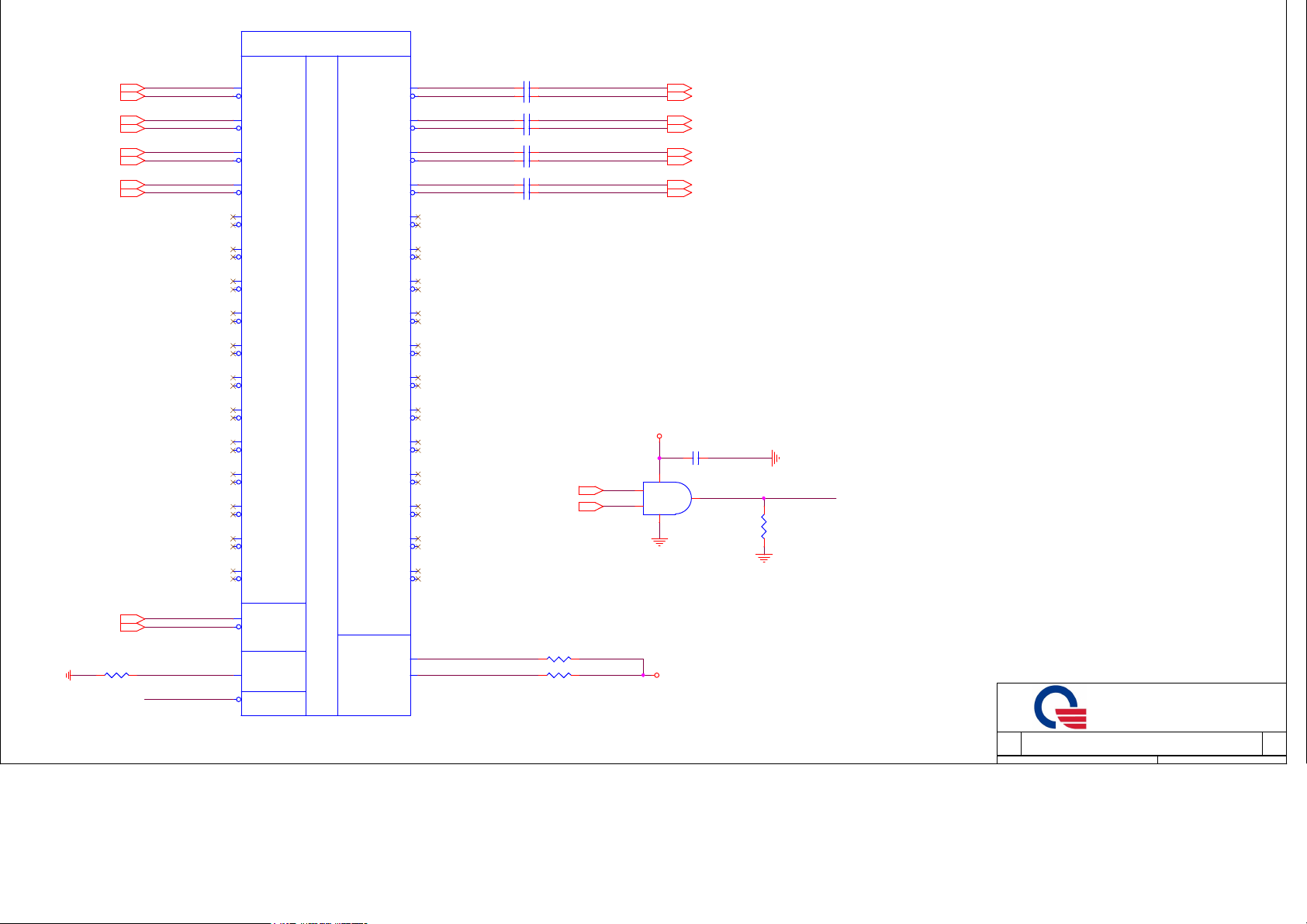

Page 2

1

2

3

4

5

6

7

8

Power Sequence

ACIN

3V/5VPCU

4

NBSWON#

DNBSWON #

S5_ON/S5

RSMRST#

PCIE_WAKE#

SUSC

SUSB

SUSON

MAINON

VR_ON

CPU_CORE

VRM_PWRGD

HWPG

ECPWROK

PWR_GOOD

PCI_RST#

Thermal Follow Chart

APU

CORE PWR

CORE_PW M_PROCHOT#

5

H/W Th rottling

SM-Bus

APU

EC

6

THERM_ALERT#

PROCHOT_EC

CPUFAN#

S5_ON

FANFAN Driver

NTC

Thermal

Protection

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

PWR Status & GP U PW R CRL

PWR Status & GP U PW R CRL

PWR Status & GP U PW R CRL

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

SYS_SHDN#

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

3V/5 V

SYS PW R

ZQN

ZQN

ZQN

2 39Tuesday , April 29, 201 4

2 39Tuesday , April 29, 201 4

2 39Tuesday , April 29, 201 4

8

1A

1A

1A

A A

B B

Power States

POWER PLANE

VIN

+1.5V_RTC

+3VPCU

+5VPCU

+15V

VOLTAGE

+10V~+19V

+1.5V

+3.3V

+5V

+15V

+3.3V

C C

+5V_S5

+5V

DESCRIPTION

RTC POWE R

EC POW ER

CHARGE POWER

CHARGE PUMP POW ER

LAN/ TPM POWE R

USB POWE R

APU POWER+1.8V+1.8V_S5 S0-S5S5_ON

+0.95V_S 5 +0.95V APU CORE POWER S0-S5S5_ON

+5V

+1.5VSUS

+SMDDR_VTT

+1.8V

+1.5V

+0.95V

+VDDNB_CORE

LCDVCC

+VGPU_CORE

D D

+1.5V_GFX

+1.8V_GFX

+3V_GFX

1

+5V

+3.3V

+1.5V

+0.75V

+1.8V

+1.5V

+0.95V

variation

+3.3V

variation

+1.5V

+1.8V

+3V

HDD/ODD/Codec /TP/CRT/HDMI POWER

APU/Peripheral co mponent /WL AN POWER+3V

CPU/SODIMM CORE POWE R

SODIMM Terminatio n POWE R

APU POWER

MINI CARD

APU CORE POW ER MAINON

APU CORE POW ER

LCD POW ER

GPU POWE R

GPU POWE R

GPU POWE R

GPU POWE R

2

CONTROL

SIGNAL

ALWAYSMAIN POWER

ALWAYS

ALWAYS

ALWAYS

S5_ON+3V_S5

S5_ON

MAINON

MAINON

SUSON

MAINON

MAINON

MAINON

VRON

LVDS_VDDEN

DGPU_PW REN S0

DGPU_PW REN

DGPU_PW REN

DGPU_PW REN

3

ACTIVE IN

ALWAYS

ALWAYS

ALWAYS

ALWAYS

ALWAYSALWAYS

S0-S5

S0-S5

S0

S0

S0-S3

S0

S0

S0

S0

S0

S0

S0

S0

S0

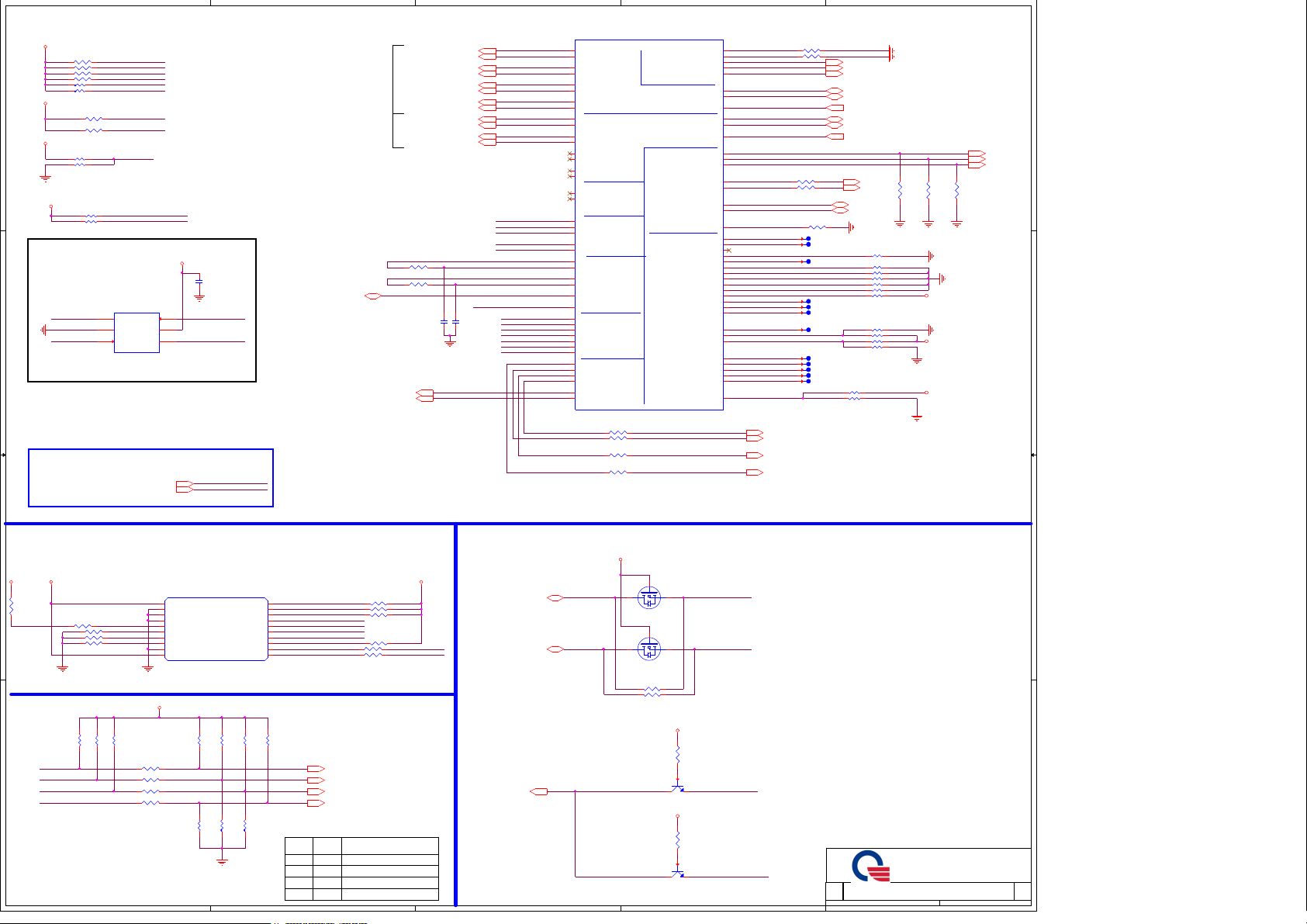

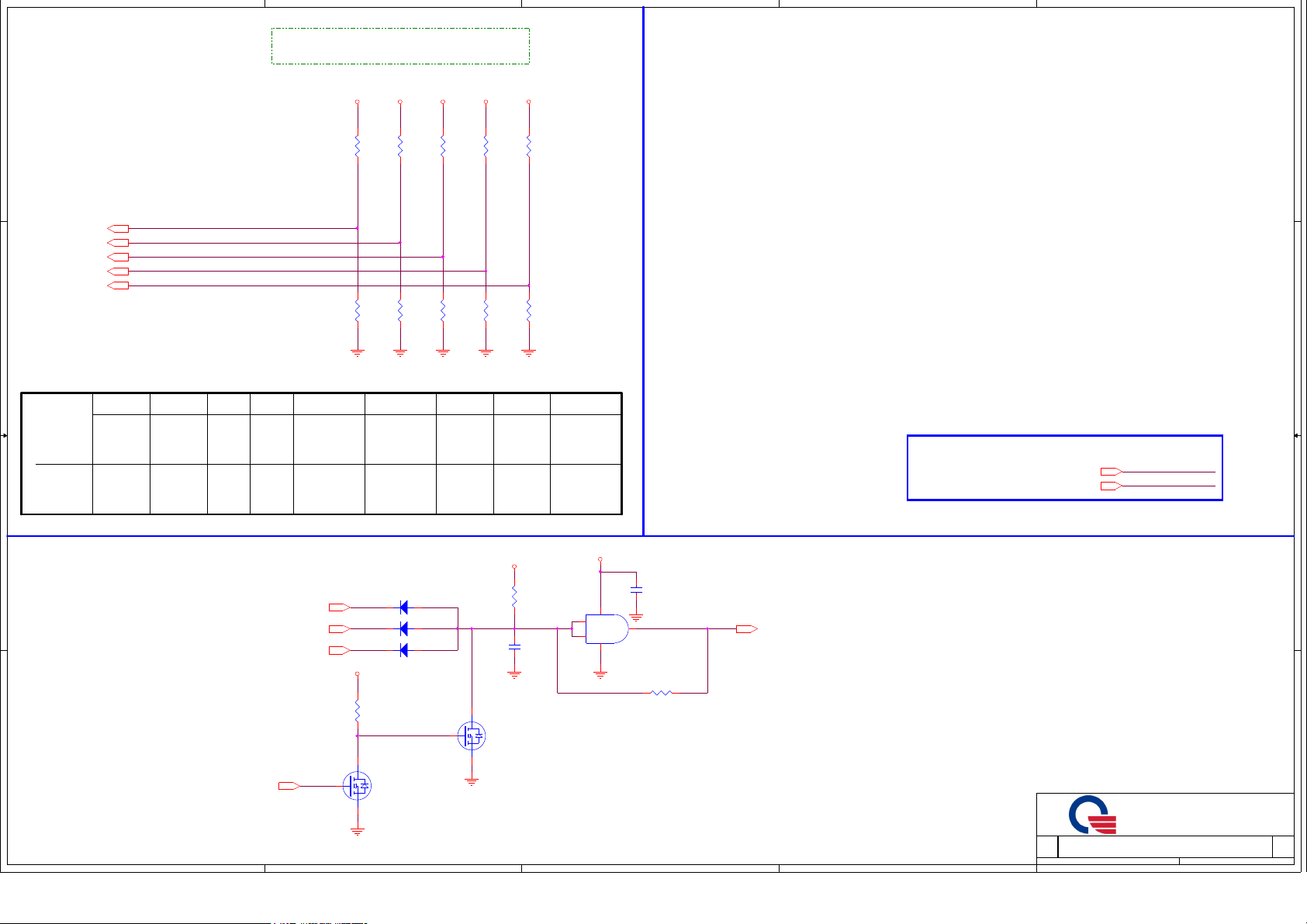

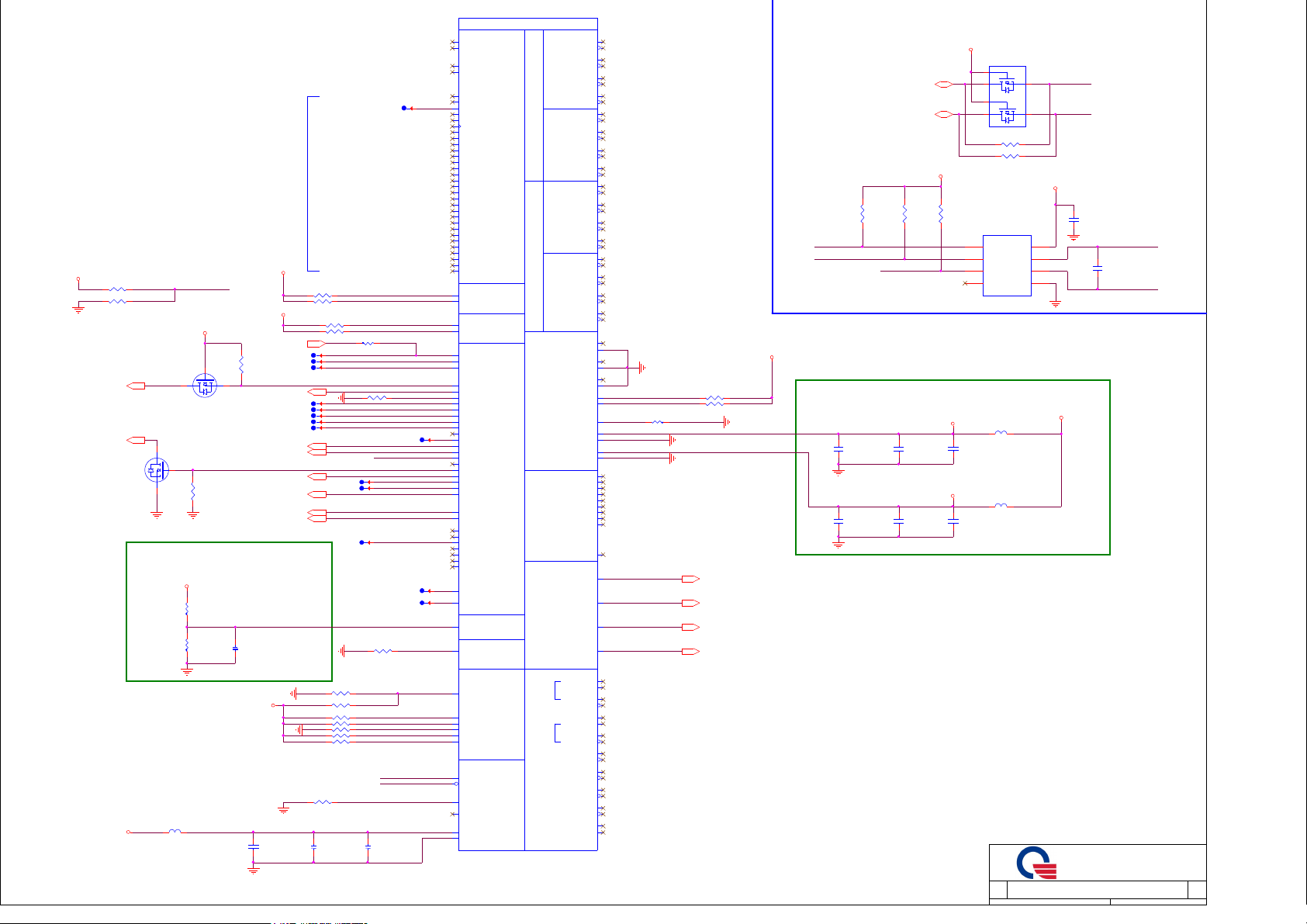

Page 3

5

4

3

2

1

M_A_DQ[0..63] <9,10>

R10

P_GPP_RXP0

R8

PCIE_RXP1<24>

PCIE_RXN1<24>

PCIE_RXP2_LAN<23>

PCIE_RXN2_LAN<23>

+0.95V +0.95V

+1.5V_SUS

R330 1.69K/F_4 R3291K/F_4

PEG_RXP0<11>

PEG_RXN0<11>

PEG_RXP1<11>

PEG_RXN1<11>

PEG_RXP2<11>

PEG_RXN2<11>

PEG_RXP3<11>

PEG_RXN3<11>

+1.5V_SUS

R467

1K/F_4

R464

1K/F_4

PCIE_RXP1

PCIE_RXN1

PCIE_RXP2_LAN

PCIE_RXN2_LAN

P_TX_ZVDD_095 P_RX_ZVDD_095

C627

C630

1000P/50V_4

0.1U/10V_4

R5

R4

N5

N4

N10

N8

W8

L5

L4

J5

J4

G5

G4

D7

E7

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_TX_ZVDD_095

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

C633

0.47u/10V_4

1 2

U24A

KABINI

PART 1 OF 9

GFX

FT3B_Beema

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

PCIE I/F

P_RX_ZVDD_095

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

L2

L1

PCIE_TXP1_C

K2

PCIE_TXN1_C

K1

PCIE_TXP2_LAN_C

J2

PCIE_TXN2_LAN_C

J1

H2

H1

W7

PEG_TXP0_C

G2

PEG_TXN0_C

G1

PEG_TXP1_C

F2

PEG_TXN1_C

F1

PEG_TXP2_C

E2

PEG_TXN2_C

E1

PEG_TXP3_C

D2

PEG_TXN3_C

D1

C565 0.1U/10V_4

C566 0.1U/10V_4

C571 0.1U/10V_4

C572 0.1U/10V_4

C559 *EV@0.1u/10V_4

C550 *EV@0.1u/10V_4

C558 *EV@0.1u/10V_4

C557 *EV@0.1u/10V_4

C570 *EV@0.1u/10V_4

C569 *EV@0.1u/10V_4

C556 *EV@0.1u/10V_4

C555 *EV@0.1u/10V_4

Power trace tracking

+1.5V_SUS<7,9,10,32,37>

+1.5V_SUS

PCIE_TXP1 <24>

PCIE_TXN1 <24>

PCIE_TXP2_LAN <23>

PCIE_TXN2_LAN <23>

PEG_TXP0 <11>

PEG_TXN0 <11>

PEG_TXP1 <11>

PEG_TXN1 <11>

PEG_TXP2 <11>

PEG_TXN2 <11>

PEG_TXP3 <11>

PEG_TXN3 <11>

KABINI

PART 2 OF 9

U24B

MEMORY I/F

FT3B_Beema

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_CHECK0

M_CHECK1

M_CHECK2

M_CHECK3

M_CHECK4

M_CHECK5

M_CHECK6

M_CHECK7

M_ZVDDIO_MEM_S

M_VREF

M_VREFDQ

B30

A32

B35

A36

B29

A30

A34

B34

B37

A38

D40

D41

B36

A37

B41

C40

F40

F41

K40

K41

E40

E41

J40

J41

M41

N40

T41

U40

L40

M40

R40

T40

AF40

AF41

AK40

AK41

AE40

AE41

AJ40

AJ41

AM41

AN40

AT41

AU40

AL40

AM40

AR40

AT40

AV41

AW40

BA38

AY37

AU41

AV40

AY39

AY38

BA36

AY35

BA32

AY31

BA37

AY36

BA33

AY32

V41

W40

AB40

AC40

U41

V40

AA41

AB41

AD41

AD40

AC38

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

+M_ZVDDIO

M_VREF

R466 39.2/F_4

M_A_A[15:0]<9,10>

D D

M_A_BS#[2..0]<9,10>

M_DM[7..0]<9,10>

C C

R113 1K/F_4

+1.5V_SUS

M_A_EVENT#<9,10>

B B

DDR3_DRAMRST#<9,10>

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_A_DQS0<9,10>

M_A_DQS#0<9,10>

M_A_DQS1<9,10>

M_A_DQS#1<9,10>

M_A_DQS2<9,10>

M_A_DQS#2<9,10>

M_A_DQS3<9,10>

M_A_DQS#3<9,10>

M_A_DQS4<9,10>

M_A_DQS#4<9,10>

M_A_DQS5<9,10>

M_A_DQS#5<9,10>

M_A_DQS6<9,10>

M_A_DQS#6<9,10>

M_A_DQS7<9,10>

M_A_DQS#7<9,10>

M_A_CLK0<9>

M_A_CLK0#<9>

M_A_CLK1<9>

M_A_CLK1#<9>

M_B_CLK0<10>

M_B_CLK0#<10>

M_B_CLK1<10>

M_B_CLK1#<10>

M_A_CKE0<9>

M_A_CKE1<9>

M_B_CKE0<10>

M_B_CKE1<10>

M_A_ODT0<9>

M_A_ODT1<9>

M_B_ODT0<10>

M_B_ODT1<10>

M_A_CS#0<9>

M_A_CS#1<9>

M_B_CS#0<10>

M_B_CS#1<10>

M_A_RAS#<9,10>

M_A_CAS#<9,10>

M_A_WE#<9,10>

AG38

W35

W38

W34

AG34

AN34

AJ38

AG35

AG40

AN41

AY40

AY34

AH41

AH40

AP41

AP40

BA40

AY41

AY33

BA34

AA40

AC35

AC34

AA34

AA32

AE38

AE37

AA37

AA38

AE34

AN38

AU38

AN37

AR37

AJ34

AR38

AL38

AN35

AJ37

AL34

AL35

U38

U37

U34

R35

R38

N38

R34

N37

L38

L35

N34

B32

B38

G40

N41

Y40

B33

A33

B40

A40

H41

H40

P41

P40

Y41

G38

L34

J38

J37

J34

M_ADD0

M_ADD1

M_ADD2

M_ADD3

M_ADD4

M_ADD5

M_ADD6

M_ADD7

M_ADD8

M_ADD9

M_ADD10

M_ADD11

M_ADD12

M_ADD13

M_ADD14

M_ADD15

M_BANK0

M_BANK1

M_BANK2

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_DM8

M_DQS_H0

M_DQS_L0

M_DQS_H1

M_DQS_L1

M_DQS_H2

M_DQS_L2

M_DQS_H3

M_DQS_L3

M_DQS_H4

M_DQS_L4

M_DQS_H5

M_DQS_L5

M_DQS_H6

M_DQS_L6

M_DQS_H7

M_DQS_L7

M_DQS_H8

M_DQS_L8

M_CLK_H0

M_CLK_L0

M_CLK_H1

M_CLK_L1

M_CLK_H2

M_CLK_L2

M_CLK_H3

M_CLK_L3

M_RESET_L

M_EVENT_L

M0_CKE0

M0_CKE1

M1_CKE0

M1_CKE1

M0_ODT0

M0_ODT1

M1_ODT0

M1_ODT1

M0_CS_L0

M0_CS_L1

M1_CS_L0

M1_CS_L1

M_RAS_L

M_CAS_L

M_WE_L

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ME M/PCIE (1/6)

ME M/PCIE (1/6)

ME M/PCIE (1/6)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZQN

ZQN

ZQN

1A

1A

3 39Tuesday, March 11, 2014

3 39Tuesday, March 11, 2014

1

3 39Tuesday, March 11, 2014

1A

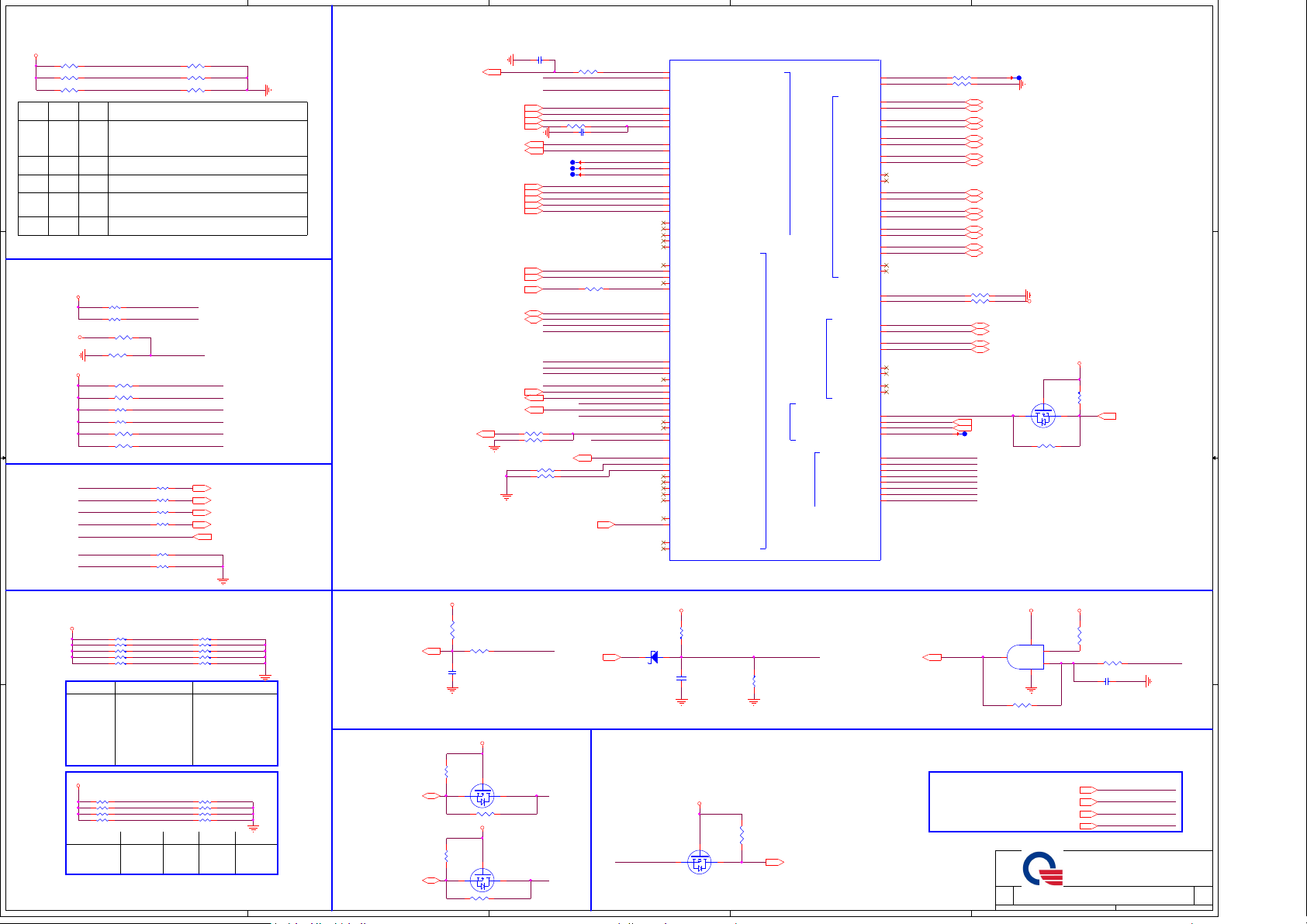

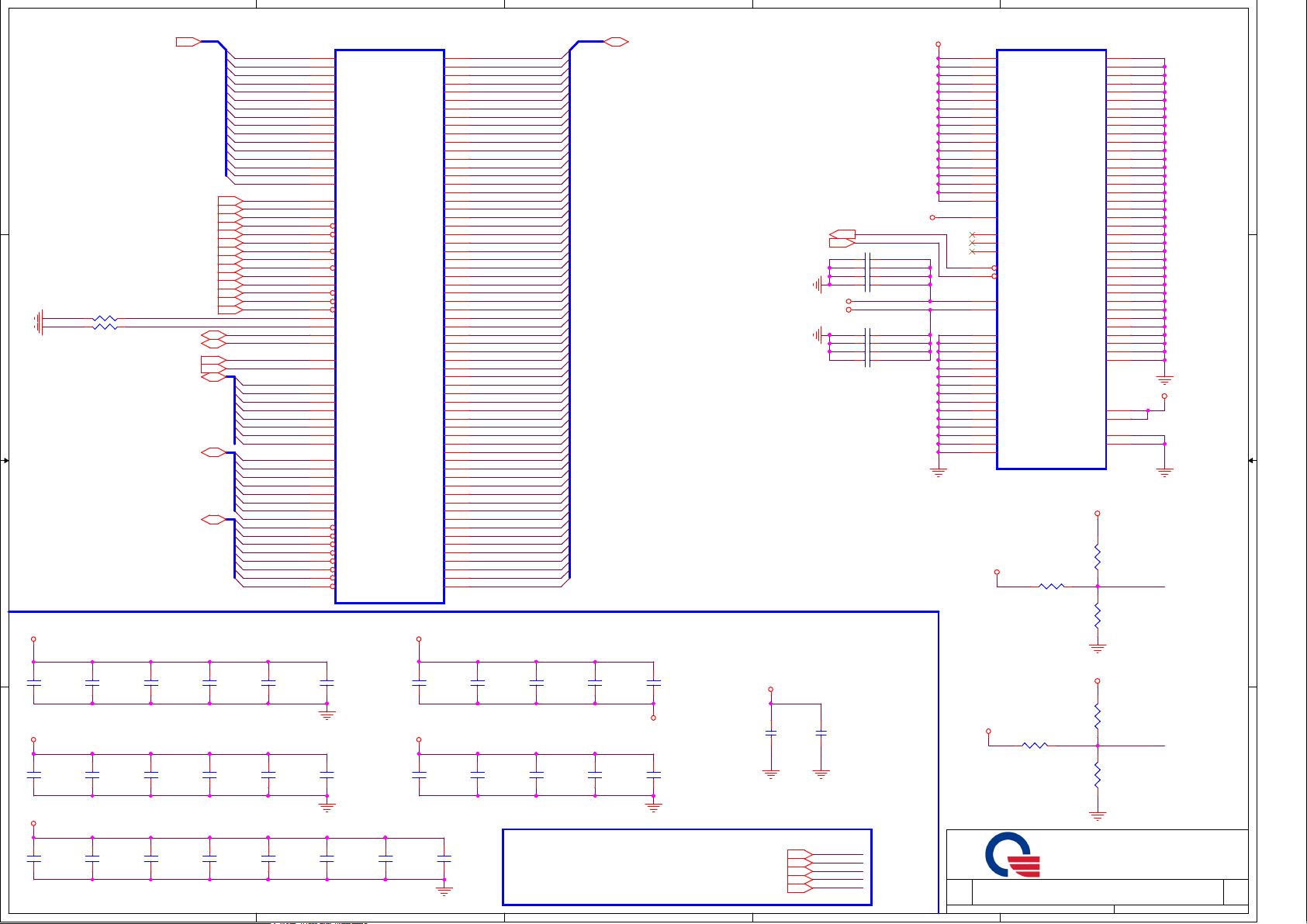

Page 4

5

4

3

2

1

+3V

R397 1K/F_4

R423 1K/F_4

R410 1K/F_4

R407 1K/F_4

R391 4.7K_4

R378 4.7K_4

APU_VDD_18

+3V

+1.8V

R412 300_4

R406 300_4

R388 1K/F_4

R389 *1K/F_4

R109 *1K/F_4

R108 *1K/F_4

D D

Can remove on MP(For HDT test)

APU_RST#

C C

APU_PWRGD APU_PWRGD_BUF

CORE_PWM_PROCHOT#

APU_SIC

APU_SID

APU_ALERT#

DDCCLK

DDCDATA

APU_RST#

APU_PWRGD

CRT_HSYNC

APU_LDT_RST_HTPA#

APU_PWRGD_BUF

U23

1

1A

2

GND

3

2A

*SN74LVC2G07DCKR

HDMI

eDP

Reserve

+3V

C605

*0.1U/10V_4

APU_LDT_RST_HTPA#

6

1Y

5

VCC

4

2Y

CORE_PWM_PROCHOT#<5,29,34>

VDD_095_FB_H<33>

VDD_095_FB_L<33>

APU_RST#

R424 *0_4

APU_PWRGD

R413 *0_4

*150p/50V_4

C607

INT_HDMITX2P<22>

INT_HDMITX2N<22>

INT_HDMITX1P<22>

INT_HDMITX1N<22>

INT_HDMITX0P<22>

INT_HDMITX0N<22>

INT_HDMICLK+<22>

INT_HDMICLK-<22>

VDD_095_FB_H

VDD_095_FB_L

EDP_TX0<21>

EDP_TX0#<21>

EDP_TX1<21>

EDP_TX1#<21>

C606

*150p/50V_4

Power trace tracking

+3V

+3V<5,7,9,10,21,22,23,24,25,27,28,29,31,32,33,34,35,36,37>

APU_VDD_18<7,34>

APU_VDD_18

INT_HDMITX2P

INT_HDMITX2N

INT_HDMITX1P

INT_HDMITX1N

INT_HDMITX0P

INT_HDMITX0N

INT_HDMICLK+

INT_HDMICLK-

EDP_TX0

EDP_TX0#

EDP_TX1

EDP_TX1#

SVT

SVC

SVD

APU_SIC

APU_SID

LDT_RST#

LDT_PWRGD

CORE_PWM_PROCHOT#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

A9

TDP1_TXP0

B9

TDP1_TXN0

A10

TDP1_TXP1

B10

TDP1_TXN1

A11

TDP1_TXP2

B11

TDP1_TXN2

A12

TDP1_TXP3

B12

TDP1_TXN3

A4

LTDP0_T XP0

B4

LTDP0_T XN0

A5

LTDP0_T XP1

B5

LTDP0_T XN1

A6

LTDP0_T XP2

B6

LTDP0_T XN2

A7

LTDP0_T XP3

B7

LTDP0_T XN3

K15

DISP_CLKIN_H

H15

DISP_CLKIN_L

G31

SVT

D27

SVC

E29

SVD

B22

SIC

B21

SID

B20

APU_RST_L

A20

LDT_RST_ L

B19

APU_PWROK

A19

LDT_PWROK

A22

PROCHOT_L

B18

ALERT_L

D29

TDI

D31

TDO

D35

TCK

D33

TMS

G27

TRST_L

B25

DBRDY

A25

DBREQ_L

D23

VDDCR_NB_SENSE

G23

VDDCR_CPU_SENSE

E25

VDDIO_MEM_S_SENSE

E23

VSS_SENSE

AV33

VDD_095_F B_H

AU33

VDD_095_F B_L

VSS_SENSE APU_VDD_RUN_FB_L

VDDCR_APU_SENSE

VDDCR_NB_SENSE

FT3B_Beema

R85 *SHORT_4

R84 *SHORT_4

R93 *SHORT_4

R90 *SHORT_4

ANALOG/DISPLA Y/MISC

DISPLAYPORT 0 DISPLA YPORT 1

CLK

SER

JTAG CTRL

KABINI

PART 4 OF 9

U24D

DP_150_ZVSS

DP_2K_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP MISC

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_GREEN

DAC_BLUE

DAC_HSYNC

DAC_VSYNC

DAC_SCL

VGA DAC

DAC_SDA

DAC_ZVSS

THERMDA

THERMDC

DIECRACKMON

PLLTEST1

PLLTEST0

BYPASSCLK_H

BYPASSCLK_L

PLLCHRZ_H

TEST

PLLCHRZ_L

GIO_TSTDT M0_SERIALCLK

GIO_TSTDT M0_CLKINIT

USB_ATEST0

USB_ATEST1

M_ANALOGIN

M_ANALOGOUT

TMON_CAL

HDMI_EN/DP_STEREOSYNC

APU_VDD_RUN_FB_H

VDDIO_MEM_S_SENSEVDDIO_MEM_S_SENSE_R

APU_VDDNB_RUN_FB_H

M_TEST

FREE_2

BP0

BP1

BP2

BP3

DP_150_ZVSS

B16

DP_2K_ZVSS

A21

APU_BLEN

B17

APU_DISP_ON

A17

APU_DPST_PWM

A18

HDMI_DDCCLK_SW

D17

HDMI_DDCDATA_SW

E17

HDMI_HPD

H19

EDP_AUX

D15

EDP_AUX#

E15

EDP_HPD

H17

B14

A14

B15

CRT_HSYNC

G19

CRT_VSYNC

E19

D19

D21

DAC_ZVSS

A16

APU_THERMDA_R

H27

APU_THERMDC_R

H29

D25

A27

BP0

B27

BP1

A26

BP2

B26

BP3

B28

PLLTEST1

A28

PLLTEST0

BYPASSCLK_H

B24

BYPASSCLK_L

A24

PLLCHRZ_H

AV35

PLLCHRZ_L

AU35

M_TEST

E33

FREE_2

A29

GIO_TSTDTMO_SERIALCLK

H21

GIO_TSTDTM0_CLKINIT

H25

USB_ATEST0

AJ10

USB_ATEST1

AJ8

M_ANALOGIN

R32

M_ANALOGOUT

N32

TMON_CAL

AP29

DP_STEREOSYNC

E21

R400 150/F_4

R425 2k/F_4

R380 *SHORT_4

R387 *SHORT_4

R404 499/F_4

TP24

TP25

TP64

TP28

TP29

TP27

TP65

TP21

TP20

TP67

TP68

TP26

R381 *1K/F_4

R382 *1K/F_4

APU_VDD_RUN_FB_L <34>

APU_VDD_RUN_FB_H <34>

VDDIO_MEM_S_SENSE <32>

APU_VDDNB_RUN_FB_H <34>

APU_BLEN <21,29>

APU_DISP_ON <21>

APU_DPST_PWM <21>

HDMI_DDCCLK_SW <22>

HDMI_DDCDATA_SW <22>

HDMI_HPD <22>

EDP_AUX <21>

EDP_AUX# <21>

EDP_HPD <21>

HSYNC <21>

R383

VSYNC <21>

DDCCLK <21>

DDCDATA <21>

R446 *1K/F_4

R445 *1K/F_4

R444 *1K/F_4

R449 1K/F_4

R450 1K/F_4

R441 510/F_4

R440 510/F_4

R87 *1K/F_4

R86 *1K/F_4

R97 *1K/F_4

R98 *1K/F_4

150/F_4

DIFFERENTIAL ROUTING

+1.8V

+1.8V

+1.8V

R390

150/F_4

R396

150/F_4

CRT_R <21>

CRT_G <21>

CRT_B <21>

HDT(Hardware Debug Tool ) Connector

B B

+1.8V +1.8V +1.8V

R117

1K/F_4

APU_TRST#

R118 *SHORT_4

R119 10K_4

R120 10K_4

R121 10K_4

HDT_TRST# APU_PWRGD_BUF

Serial VID

R422

R432

R439

*1K/F_4

*1K/F_4

*1K/F_4

SVT

SVC

SVD

A A

APU_PWRGD

5

CN1

1

CPU_VDDIO

3

GND

5

GND

7

GND

9

CPU_TRST_L

11

CPU_DBRDY 3

13

CPU_DBRDY 2

15

CPU_DBRDY 1

17

GND

19

CPU_VDDIO

*HDT

+1.8V

R421 33_4

R438 33_4

R431 33_4

R405 *SHORT_4

HDT+ HEADER / PLACE ON TOP

R437

R420

*300/F_4

*300/F_4

R403

R436

*220/F_4

*0_4

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

CPU_PWROK_BUF

CPU_RST_L_BUF

CPU_DBRDY 0

CPU_DBREQ_L

CPU_PLLTEST0

CPU_PLLTEST1

R430

*300/F_4

R429

*0_4

APU_TCK

2

APU_TMS

4

APU_TDI

6

APU_TDO

8

10

APU_LDT_RST_HTPA#

12

APU_DBRDY

14

APU_DBREQ#

16

J108_PLLTST0

18

J108_PLLTST1

20

R399

*2.2K_4

APU_SVT <34>

APU_SVC <34>

APU_SVD <34>

APU_PWRGD_SVID_REG <34>

VFIX MODE

SVDSVC

0

0

0

110 0.9V

11

4

R105 1K/F_4

R106 1K/F_4

R107 1K/F_4

R110 1K/F_4

R111 *SHORT_4

R112 *SHORT_4

VID Override table (VDD)

Boot Voltage

1.1V

1.0V

0.8V

SMBUS (Internal Thermal sensor)

+3V

2

3

2N7002K

Q33

2

3

2N7002K

Q31

R426 *0_4

R411 *0_4

THERM_ALERT# APU_ALERT#

MMST3904-7-F

*MMST3904-7-F

PLLTEST0

PLLTEST1

2ND_MBCLK<12,29>

2ND_MBDATA<12,29>

THERM_ALERT#<28>

3

Q30

Q29

1

1

+3V

2

+3V

2

R401

10K/F_4

13

R392

*10K/F_4

CORE_PWM_PROCHOT#

13

APU_SIC

APU_SID

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DIS/MISC (2/6)

DIS/MISC (2/6)

DIS/MISC (2/6)

Date: Sheet of

Date: Sheet of

Date: Sheet

PROJECT :

ZQN

ZQN

ZQN

of

4 39Tuesday, April 29, 2014

4 39Tuesday, April 29, 2014

4 39Tuesday, April 29, 2014

1

1A

1A

1A

Page 5

5

4

3

2

1

Test mode setting (Follow AMD's suggestion)

+3V_S5

NC,no install by default

R409 *1K/F_4

R386 *1K/F_4

R374 *1K/F_4

TEST2 TEST1 TEST0 Description

D D

0

0 0

0

0

0

1

1

TMS

1 TMS

External pull-up

C C

+3V_S5

+3V_S5

To Azalia

B B

Board ID

+3V

A A

APU_TEST0

APU_TEST1

APU_TEST2

FCH TAP accessible from APU when TAPEN is asserted

FCH JTAG pins are overloaded for multiple

functions, in this configuration the FCH JTAG are

used as non-JTAG pins

1

Reserved

X

Reserved

FCH JTAG multi-function pins are configured as

0

JTAG pins, in this configuration the FCH TAP

can be accessed from FCH JTAG pins

Use on ATE only

Yuba JTAG enabled 1

+3V

R451 2.2K_4

R448 2.2K_4

R379 *10K/ F_4

J1 *0_ 4

R88 *10K/F_4

R92 100K_4

R416 2. 2K_4

R417 2. 2K_4

R332 10 K/F_4

R331 10 K/F_4

ACZ_SDOUT_R

ACZ_SYNC_R

ACZ_BCLK_R

ACZ_RST#_R

PCH_AZ_CODEC_SDIN0

ACZ_BCLK_R

PCH_AZ_CODEC_SDIN0

R104 *10K_4

R443 *10K_4

R434 *10K_4

R419 *10K_4

R428 10K_4

GPIO

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

+3V_S5

(Depend on cable) (Depend on cable)

R360 *10K/F _4

R315 *10K/F _4

R314 *10K/F _4

R313 *10K/F _4

CLK_SCLK

CLK_SDATA

SYS_RST#

R316 33_4

R327 33_4

R317 33_4

R324 33_4

R328 *10K/F _4

R323 *10K/F _4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

High

d'TPM

d'GPU

17"

Reserve

Touch

RAMID_0

RAMID_1

RAMID_2

RAMID_3

R408 15K/F_4

R385 15K/F_4

R373 15K/F_4

TP_I2C_INT#_APU

PCIE_WAKE#

SCL1

SDA1

USB_OC1#

USB_OC2#

R101 10K_4

R442 10K_4

R433 10K_4

R418 10K_4

R427 *10K_4

R365 10K/F_4

R326 10K/F_4

R325 10K/F_4

R322 10K/F_4

PCH_AZ_CODEC_SDOUT <2 5>

PCH_AZ_CODEC_SYNC <25>

PCH_AZ_CODEC_BITCLK <25>

PCH_AZ_CODEC_RST# <25>

PCH_AZ_CODEC_SDIN0 <25>

Low

i'TPM

UMA

14"

Reserve

None Touch

S0-domai n

DGPU_PWREN<37>

TP SMBus

TP_SMCLK<2 8>

PLTRST#<24 ,29>

PCIE_CLKREQ_WLAN#<24>

PCIE_REQ_LAN#<23>

PCIE_REQ_GPU#<12>

CORE_PWM_PROCHOT#<4,29,34>

+3V

PR191

*EV@100K/F_6

R531 *SHORT_4

C616

*EV@0.1U/10V_4

R461

*2.2K_4

1

R453 *0_4

DNBSWON#<29>

SYS_PWRGD<8,28 >

SYS_RST#<8>

PCIE_LAN_WAKE#<23,24>

SIO_A20GATE<29>

SIO_EXT_SCI#<29>

SIO_EXT_SMI#<29>

LPCPD#<24,28>

CLK_SCLK<9 ,10,24>

CLK_SDATA<9,10,24>

S5-domai n

BOARD_ID4<21>

DGPU_RST_L<11>

+3V_S5

2

+3V_S5

C597 150P/50V_4

PLTRST#

SUSB#<8,29>

SUSC#<2 9>

KBRST#<29>

SPKR<25>

R100 *0_4

R560 10 K/F_4

R558 10 K/F_4

R559 10 K/F_4

GPU_Enable

Q34

3

SCL1

*2N7002K

R367 33_4

R91 *SHORT_ 4

C220 *100p/50V_4

TP63

TP60

TP57

PCIE_CLKREQ_WLAN#

PCIE_REQ_LAN#

R447 *0_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

PROCHOT#_CT RL

GEVENT2#<8>

PE_PWRGD<37>

PCH_RSMRST#<29>

LPC_RST#_R

PCIE_RST#

PCH_RSMRST#_R

DNBSWON#

SYS_PWRGD

SYS_RST#

PCIE_WAKE#

SUSB#

SUSC#

APU_TEST0

APU_TEST1

APU_TEST2

KBRST#

SIO_A20GATE

SIO_EXT_SCI#

SIO_EXT_SMI#

LPCPD#

CLK_SCLK

CLK_SDATA

SCL1

SDA1

TP_INT_APU

GPU_Enable

RAMID_0

GEVENT2#

TS interrupt (reserve only)

RAMID_1 RAMID_2 RAMID_3RAMID_0RAM

R462

Reserve Reserve Reserve Reserve Reserve

5

TP_SMDATA<28>

4

*2.2K_4

2

1

R454 *0_4

Q35

3

*2N7002K

SDA1

3

U24C

AY4

LPC_RST_L

AY9

PCIE_RST_L

AY5

RSMRST_L

BA8

PWR_BTN_L

AM19

PWR_GOOD

AY7

SYS_RESET_L/GEVENT19_L

AW11

WAKE_L/GEVENT8_L

AY3

SLP_S3_L

BA5

SLP_S5_L

AU13

TEST0

AY10

TEST1/TMS

AY6

TEST2

AR23

KBRST_L

AR31

GA20IN/GEVENT0_ L

AN5

LPC_PME_L/GEVENT3_ L

AL7

LPC_SMI_L/GEVENT23 _L

AV2

LPC_PD_L/G EVENT5_L/SPI_TPM_CS_L

AP15

AC_PRES/IR_RX0/G EVENT16_L

AV13

IR_TX0/GEVENT21_ L

BA9

IR_TX1/GEVENT6_L

BA10

IR_RX1/GEVENT20 _L

AV15

IR_LED_L/L LB_L/GPIO184

AU29

CLK_REQ0_L /SATA_IS0_L/SATA_ZP0_L/GPI O60

AW29

CLK_REQ1_L /GPIO61

AR27

CLK_REQ2_L /GPIO62

AV27

CLK_REQ3_L /SATA_IS1_L/SATA_ZP1_L/GPI O63

AY29

CLK_REQG_L /GPIO65/OSCIN

AU25

SCL0/GPIO4 3

AV25

SDA0/GPIO47

AY11

SCL1/GPIO2 27

BA11

SDA1/GPIO22 8

AP27

GPIO49

AY28

GPIO50

BA28

GPIO51

AV23

GPIO55

AP21

GPIO57

BA26

GPIO58

AV19

GPIO59

AY27

GPIO64

BA27

SPKR/GPIO66

AU21

GPIO68

AY26

GPIO69

AV21

GPIO70

AM21

GPIO71

BA3

GPIO174

AV17

GEVENT2_L

BA4

GEVENT4_L

AR15

GEVENT7_L

AP17

GEVENT10_L

AP11

GEVENT11_L

AN8

GEVENT17_L

AU17

BLINK/GEVENT18_L

BA6

GEVENT22_L

BA29

GENINT1_L/G PIO32

AP23

GENINT2_L/G PIO33

AV31

FANOUT0/GPIO52

AU31

FANIN0/GPIO56

+1.8V_S5

R366

47K/F_4

D3

RB500V-40

TP_INT_APU

1

Q32

*2N7002K

C598

0.1u/10V_ 4

+3V

2

ACPI / WAKE UP

EVENTS

USB_SS_ZVDD_095 _USB3_DUAL

GPIO

USB_OC0_L/ SPI_TPM_CS_L/TRST_L/GEVENT12_L

FT3B_Bee ma

PCH_RSMRST#_R

R435

*10K_4

LDO +3V PU in Panel device

3

R368

*10K_4

USB

OC

KABINI

PART 3 OF 9

TP_INT <21 >

USB_OC1_L/ TDI/GEVENT13_L

USB_OC2_L/ TCK/GEVENT14_L

USB_OC3_L/ TDO/GEVENT15_L

HD

USBCLK/14M_25 M_48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB

MISC

USB

1.1

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB

2.0

USB_HSD8P

USB_HSD8N

USB_HSD9P

USB_HSD9N

USB_SS_ZVSS

USB_SS_TX0P

USB_SS_TX0N

USB_SS_RX0P

USB_SS_RX0N

USB

3.0

USB_SS_TX1P

USB_SS_TX1N

USB_SS_RX1P

USB_SS_RX1N

AZ_BITCLK

AZ_SDOUT

AZ_SDIN0/GPIO1 67

AZ_SDIN1/GPIO1 68

AZ_SDIN2/GPIO1 69

AZ_SDIN3/GPIO1 70

AZ_SYNC

AZ_RST_L

AUDIO

2

W4

USB_ZVSS

AG4

AL4

AL5

AJ4

AJ5

AG7

AG8

AG1

AG2

AF1

AF2

AE1

AE2

AD1

AD2

AC1

AC2

AB1

AB2

AA1

AA2

USB_SS_ZVSS

AE10

USB_ZVDD

AE8

T2

T1

V2

V1

R1

R2

W1

W2

TP_I2C_INT#_APU

AY8

USB_OC1#

AW1

USB_OC2#

AV1

USB_OC3#

AY1

AN2

AN1

AK2

AK1

AM1

AL2

AM2

AL1

PCIERST#<11,23,24 ,27>

R76 *33_4

R79 11.8K/F_ 4

R81 1K/F_ 4

R80 1K/F_4

USB_OC1# <2 7>

USB_OC2# <2 7>

TP53

ACZ_BCLK_R

ACZ_SDOUT_R

PCH_AZ_CODEC_SDIN0

RAMID_3

RAMID_1

RAMID_2

ACZ_SYNC_R

ACZ_RST#_R

*MC74VHC1G08DFT 2G

PCIERST#

Power trace tracking

TP19

USBP0+ <27>

USBP0- <27>

USBP1+ <21>

USBP1- <21>

USBP2+ <24>

USBP2- <24>

USBP3+ <21>

USBP3- <21>

USBP5+ <27>

USBP5- <27>

USBP6+ <27>

USBP6- <27>

USBP7+ <24>

USBP7- <24>

USBP8+ <27>

USBP8- <27>

Daughter board side USB2.0

Camera USB

USB to I2C

Touch Panel

Daughter board side USB2.0

Card reader

WLAN Min-Card

USB Combo 3.0/2.0

+0.95V_DUAL

USB30_TX1+ <27>

USB30_TX1- <27>

USB30_RX1+ <27>

USB30_RX1- <27>

3

R89 *0_ 4

U7

4

R82 *SHORT_ 4

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

GPIO/ USB/AZ (3/6)

GPIO/ USB/AZ (3/6)

GPIO/ USB/AZ (3/6)

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3V

Q6

R95

2

*2N7002K

*10K_4

1

+3V_S5+3V_S5

R78

35

+0.95V_DUAL<7 >

*4.7K_4

1

2

C207 150P/50V_4

+3V<4,7,9,10 ,21,22,23,2 4,25,27,28 ,29,31,32,3 3,34,35,36 ,37>

+1.8V<4,7,35>

+3V_S5<6,7,8,23 ,24,26,27, 28,29,31,36 >

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

TP_I2C_INT# <24,28>

R83 33_4

+3V

+1.8V

+3V_S5

+0.95V_DUAL

ZQN

ZQN

ZQN

PCIE_RST#PCIERST_R#

5 39Tuesday , April 29, 201 4

5 39Tuesday , April 29, 201 4

5 39Tuesday , April 29, 201 4

1A

1A

1A

Page 6

5

D D

SATA HDD

SATA ODD

+0.95V

C C

CLK_PCIE_VGAP<11>

CLK_PCIE_VGAN<11>

CLK_PCIE_LANP<23>

CLK_PCIE_LANN<23>

B B

C544 5.6p/16V_4

C546 5.6p/16V_4

13

R309 *SHORT_4

R307 *SHORT_4

CLK_PCIE_WLAN<24>

CLK_PCIE_WLAN#<24>

R333 *SHORT_4

R321 *SHORT_4

2

Y3

48MHZ

4

SATA_TXP 0<26>

SATA_TXN0<26>

SATA_RXN0<26>

SATA_RXP0<26>

SATA_TXP 1<26>

SATA_TXN1<26>

SATA_RXN1<26>

SATA_RXP1<26>

TP66

R310

1M_4

4

SATA_TXP 0

SATA_TXN0

SATA_RXN0

SATA_RXP0

SATA_TXP 1

SATA_TXN1

SATA_RXN1

SATA_RXP1

SATA_ZVS S

R961K/F_4

SATA_ZVDD

R941K/F_4

CLK_PCIE_VGAP_R

CLK_PCIE_VGAN_R

CLK_PCIE_LANP_R

CLK_PCIE_LANN_R

48M_X1

48M_X2

BA14

SATA_TX0P

AY14

SATA_TX0N

BA16

SATA_RX0N

AY16

SATA_RX0P

AY19

SATA_TX1P

BA19

SATA_TX1N

AY17

SATA_RX1N

BA17

SATA_RX1P

AR19

SATA_ZVSS

AP19

SATA_ZVDD_095

BA30

SATA_ACT_L/GPIO67

AY12

SATA_X1

BA12

SATA_X2

U4

GFX_CLKP

U5

GFX_CLKN

AC8

GPP_CLK0P

AC10

GPP_CLK0N

AE4

GPP_CLK1P

AE5

GPP_CLK1N

AC4

GPP_CLK2P

AC5

GPP_CLK2N

AA5

GPP_CLK3P

AA4

GPP_CLK3N

AP13

X14M_25M_48M_OSC

N2

X48M_X1

N1

X48M_X2

U24E

KABINI

PART 5 OF 9

SERIAL

ATA

FT3B_Beema

SD

CARD

SPI

ROM

3

SD__PWR_CTRL

SD_CLK/GPIO73

SD_CMD/GPIO74

SD_CD/GPIO75

SD_WP/GPIO76

SD_DATA0/GPIO77

SD_DATA1/GPIO78

SD_DATA2/GPIO79

SD_DATA3/GPIO80

SD_LED/GPIO45

SPI_CLK/GPIO162

SPI_CS1_L/GPIO165

SPI_CS2_L/GPIO166

SPI_DO/GPIO163

SPI_DI/GPIO164

SPI_HOLD_L/GEVENT9_L

SPI_WP_L/GPIO161

LPCCLK0

LPCCLK1

LAD0

LAD1

LAD2

LAD3

LFRAME_L

LDRQ0_L

SERIRQ/GPIO48

LPC_CLKRUN_L

32K_X1

32K_X2

RTCCLK

VDDBT_RTC_G

BA23

AY22

AY23

AY20

BA20

BA22

AY21

AY24

BA24

AY25

AU7

AW9

AR4

AR11

AR7

AU11

AU9

AY2

AW2

AT2

AT1

AR2

AR1

AP2

AP1

AV29

AP25

AJ2

AJ1

AV11

AN4

SPI_CLK

SPI_CS1#

SPI_SO

SPI_SI

SPI_HOLD

SPI_WP

LPC_CLK0_R

LPC_CLK1_R

LPC_LAD0

LPC_LAD1

LPC_LAD2

LPC_LAD3

LPC_LFRAME#

LDRQ#0

SERIRQ

LPC_CLKRUN#_R

+1.5V_RTC_R

*SHORT_ PAD

R355 22_4

R352 22_4

R351 22_4

R359 *22_4

R364 22_4

R356 22_4

32K_X1

32K_X2

20MIL

12

G1

TP51

R99 *SHORT_4

R312

20M_4

C198

0.1U/10V_4

APU SPI ROM

SPI_CS1#

SPI_CLK

C601 22p/50V_4

SPI_SO

SPI_SI SPI_SDI

SPI_WP SPI_WP_R

TP61

TP58

TP52

TP59

TP56

TP62

TP55

R75 10 K_4

12

RTC_CLK <8>

C199

0.22u/10V_4

PCLK_TPM <24>

LPC_CLK0 <8>

CLK_LPC_DEBUG <24>

C545 22p/50V _4

C547 22p/50V _4

2

SPI_CS<29>

SPI_SCK<29>

SPI_SDO<29>

SPI_SDI<29>

+3V_S5

CLK_PCI_775 <29>

LPC_CLK1 <8>

LPC_LAD0 <24,29>

LPC_LAD1 <24,29>

LPC_LAD2 <24,29>

LPC_LAD3 <24,29>

LPC_LFRAME# <8,24,29>

SERIRQ <24,29>

LPC_CLKRUN# <24,28,29>

Y2

32.768KHZ

C196

1u/10V_4

R525 33_4

R526 33_4

R527 33_4

R528 33_4

R375 33_4

R393 33_4

R384 33_4

R372 33_4

R370 10K/F_ 4

R369 *SHORT_4

C592 *15p/50V_4

C595 *15p/50V_4

+1.5V_RTC

AP2138N-1.5TRG1

Vender Size Quanta P/N

1st

AMIC

?

?

MAX MX25L6436E

?

EON

?

USE GROUND GUARD FOR 32K_X1 AND 32K_X2

Q4

1

VOUT

3

VIN

GND

2

8M

8M

8M

8M

8M

SPI_CS

SPI_SCK

SPI_SDOSATA_ACT#

+3VRTC

AKE3EFP0N07

AKE3EGN0Q01

AKE3EZN0Q01

+3V_S5

R376

10K/F_4

1

6

5

2

3

20MIL20MIL

C197

1u/10V_4

?

?

U22

CE#

SCK

SI

SO

WP#

SPI_W25Q64FVSSIQ

D2

BAT54C

1

Vender P/N

W25Q64FVSSIQWND

GD25B64BSIGRGGD

EN25QH64-104HIP

+3V_S5

8

VDD

7

HOLD#

4

VSS

R72 *SHORT_4

+3VPCU_R

20MIL

+VCCRTC_2

?

+3V_S5

R398

10K/F_4

R70

1K/F_4

C222

0.1U/10V_4

SPI_HOLD

+3VPCU

+BAT

ZQN

ZQN

ZQN

12

1A

1A

6 39Tuesday, April 29, 2014

6 39Tuesday, April 29, 2014

6 39Tuesday, April 29, 2014

1A

CN10

CR2032_CONN

Power trace tracking

A A

5

+3V<4,5,7,9,10,21,22,23,24,25,27,28,29,31,32,33,34,35,36,37>

+0.95V_S5<7,33>

+3V_S5<5,7,8,23,24,26,27,28,29,31,36>

+3VPCU<21,25,26,28,29,30,31,35,37>

+3V

+0.95V_S5

+3V_S5

+3VPCU

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SATA/CLK/LPC (4/6 )

SATA/CLK/LPC (4/6 )

SATA/CLK/LPC (4/6 )

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

PROJECT :

1

Page 7

5

4

3

2

1

+1.5V_SUS +VDD_CORE

C257

180p/50V_4

D D

C270

0.1u/10V_4

C261

1U/10V_4

+1.5V APU_VDDIO_AZ

R103 *SHORT_6

C C

B B

+3V_S5 APU_VDD33_ALW

R402 *SHORT_8

C269

180p/50V_4

C263

0.1u/10V_4

C264

0.1u/10V_4

C243

4.7U/6.3V_6

APU_VDDIO_AZ

C232

1U/10V_4

180p/50V_4

C604

4.7U/6.3V_6

C266

C259

180p/50V_4

C258

C272

1U/10V_4

1U/10V_4

C267

C262

1U/10V_4

0.1u/10V_4

PLACE ON TOP LAYER

C230

C231

1U/10V_4

180p/50V_4

PLACE ON BOT LAYER

C229

1U/10V_4

C603

1U/10V_4

C289

10u/6.3V_8

C602

1U/10V_4

C271

1U/10V_4

C265

1U/10V_4

10u/6.3V_8

C283

C273

10u/6.3V_8

C268

1U/10V_4

C260

1U/10V_4

APU_VDD18_ALW

APU_VDD33_ALW

+0.95V_DUAL

VDD_0.95V_ALW

APU_VDDIO_AZ

U24F

J35

VDDIO_MEM_S_1

L32

VDDIO_MEM_S_2

L37

VDDIO_MEM_S_3

N35

VDDIO_MEM_S_4

R31

VDDIO_MEM_S_5

R37

VDDIO_MEM_S_6

U32

VDDIO_MEM_S_7

U35

VDDIO_MEM_S_8

W31

VDDIO_MEM_S_9

W32

VDDIO_MEM_S_10

W37

VDDIO_MEM_S_11

AA31

VDDIO_MEM_S_12

AA35

VDDIO_MEM_S_13

AC32

VDDIO_MEM_S_14

AC37

VDDIO_MEM_S_15

AE31

VDDIO_MEM_S_16

AE35

VDDIO_MEM_S_17

AG32

VDDIO_MEM_S_18

AG37

VDDIO_MEM_S_19

AJ35

VDDIO_MEM_S_20

AL32

VDDIO_MEM_S_21

AL37

VDDIO_MEM_S_22

AR35

VDDIO_MEM_S_23

AL10

VDDIO_AZ_ALW_1

AL11

VDDIO_AZ_ALW_2

B1

VDD_18_ALW_1

B2

VDD_18_ALW_2

AL13

VDD_33_ALW_1

AM13

VDD_33_ALW_2

AR5

VDD_095_USB3_DUAL1

AU4

VDD_095_USB3_DUAL2

AV7

VDD_095_USB3_DUAL3

AW5

VDD_095_USB3_DUAL4

AE11

VDD_095_ALW_1

AE13

VDD_095_ALW_2

AJ11

VDD_095_ALW_3

AJ13

VDD_095_ALW_4

KABINI

PART 7 OF 9

FT3B_Beema

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_CPU_16

VDDCR_CPU_17

VDDCR_CPU_18

VDDCR_CPU_19

VDDCR_CPU_20

VDDCR_CPU_21

VDDCR_CPU_22

VDDCR_CPU_23

VDDCR_CPU_24

VDDCR_CPU_25

VDDCR_CPU_26

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

POWER

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDCR_NB_10

VDDCR_NB_11

VDDCR_NB_12

VDDCR_NB_13

VDDCR_NB_14

VDDCR_NB_15

VDDCR_NB_16

VDDCR_NB_17

VDDCR_NB_18

VDDCR_NB_19

VDDCR_NB_20

VDDCR_NB_21

VDD_095_GFX_1

VDD_095_GFX_2

VDD_095_GFX_3

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_33_1

VDD_33_2

VDD_095_1

VDD_095_2

VDD_095_3

VDD_095_4

VDD_095_5

VDD_095_6

VDD_095_7

VDD_095_8

VDD_095_9

L21

L23

L25

L27

L29

N21

N23

N27

R21

R23

R27

U21

U23

U27

W21

W23

W27

AA21

AA23

AA27

AC21

AC23

AC27

AE21

AE23

AE27

L13

L17

N11

N13

N17

R11

R13

R17

U13

U17

W13

W17

AA13

AA17

AC13

AC17

AE15

AE17

AE19

AG17

AG21

A2

A3

B3

C3

AM15

AM17

AG23

AG27

AJ21

AJ27

AL21

AL23

AL27

AM23

AM25

U10

W10

AA10

+VDDNB_CORE

APU_VDD_18

APU_VDD_33

APU_VDD_0.95

VDD_095_GFX

C214

1U/10V_4

C112

10u/6.3V_8

10u/6.3V_8

C234

1U/10V_4

C235

1U/10V_4

C225

10u/6.3V_8

L17

PBY160808T-60 0Y-N(60,3A)

C226

10u/6.3V_8

C593

10u/6.3V_8

C212

1U/10V_4

C204

1U/10V_4

42R

C200

10u/6.3V_8

10u/6.3V_8

C238

1U/10V_4

C249

1U/10V_4

C223

C152

10u/6.3V_8

C205

1U/10V_4

C202

1U/10V_4

APU_VDD_0.95 +0.95V

C241

1U/10V_4

C203

C245

10u/6.3V_8

C248

C237

1U/10V_4

1U/10V_4

C251

C246

1U/10V_4

1U/10V_4

C224

10u/6.3V_8

C211

1U/10V_4

C216

1U/10V_4

R124 *SHORT_8

C111

10u/6.3V_8

C217

1U/10V_4

C213

1U/10V_4

C247

180p/50V_4

C236

1U/10V_4

C252

1U/10V_4

C206

180p/50V_4

C215

1U/10V_4

C250

1U/10V_4

If P_GFX [3:0] ar e not us ed, lea ve VDD_0 95_GFX u nconnect ed.

C253

1U/10V_4

C240

1U/10V_4

C256

1U/10V_4

C255

1U/10V_4

C284

10u/6.3V_8

C285

10u/6.3V_8

U24G

A8

VSS_1

A13

VSS_2

A23

VSS_3

A31

VSS_4

A35

VSS_5

A39

VSS_6

B8

VSS_7

B13

VSS_8

B23

VSS_9

B31

VSS_10

B39

VSS_11

C1

VSS_12

C2

VSS_13

C5

VSS_14

C7

VSS_15

C9

VSS_16

C11

VSS_17

C13

VSS_18

C15

VSS_19

C17

VSS_20

C19

VSS_21

C21

VSS_22

C23

VSS_23

C25

VSS_24

C27

VSS_25

C29

VSS_26

C31

VSS_27

C33

VSS_28

C35

VSS_29

C37

VSS_30

C39

VSS_31

C41

VSS_32

D9

VSS_33

D11

VSS_34

D13

VSS_35

E3

VSS_36

E4

VSS_37

E9

VSS_38

E11

VSS_39

E13

VSS_40

E27

VSS_41

E31

VSS_42

E35

VSS_43

E38

VSS_44

E39

VSS_45

G3

VSS_46

G7

VSS_47

G11

VSS_48

G13

VSS_49

G15

VSS_50

G17

VSS_51

G21

VSS_52

G25

VSS_53

G29

VSS_54

G35

VSS_55

G37

VSS_56

G39

VSS_57

G41

VSS_58

H11

VSS_59

H13

VSS_60

H23

VSS_61

H31

VSS_62

C254

1U/10V_4

FT3B_Beema

C239

1U/10V_4

KABINI

PART 8 OF 9

GROUND

C242

180p/50V_4

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

J3

J7

J8

J39

K11

K13

K17

K19

K21

K23

K25

K27

K29

K31

L3

L7

L8

L10

L11

L15

L19

L31

L39

L41

M1

M2

N3

N7

N15

N19

N25

N29

N31

N39

P1

P2

R3

R7

R15

R19

R25

R29

R39

R41

U1

U2

U3

U7

U8

U11

U15

U19

U25

U29

U31

U39

W3

W5

W11

W15

W19

W25

W29

W39

W41

AA11

AA15

AA19

AA25

AA29

AA39

AC11

AC15

AC19

AC25

AC29

AC31

AC39

AC41

AE25

AE29

AE32

AE39

AG10

AG11

AG13

AG15

AG19

AG25

AG29

AG31

AG39

AG41

AJ15

AJ17

AJ19

AJ23

AJ25

AJ29

AJ31

AJ32

AJ39

AL15

AL17

AL19

AL25

AL29

U24H

VSS_125

VSS_126

VSS_127

Y1

VSS_128

Y2

VSS_129

AA3

VSS_130

AA7

VSS_131

AA8

VSS_132

VSS_133

VSS_1134

VSS_135

VSS_136

VSS_137

VSS_138

AC3

VSS_139

AC7

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

AE3

VSS_149

AE7

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

AG3

VSS_155

AG5

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

AH1

VSS_167

AH2

VSS_168

AJ3

VSS_169

AJ7

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

AL3

VSS_180

AL8

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

KABINI

PART 9 OF 9

GROUND

FT3B_Beema

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSSBG_DAC

VBURN

PSEN

AL39

AL41

AM11

AM27

AM31

AN3

AN7

AN39

AP31

AR3

AR13

AR17

AR21

AR25

AR29

AR39

AR41

AU1

AU2

AU3

AU15

AU19

AU23

AU27

AU39

AV9

AW3

AW7

AW13

AW15

AW17

AW19

AW21

AW23

AW25

AW27

AW31

AW33

AW35

AW37

AW39

AW41

AY13

AY15

AY18

AY30

BA2

BA7

BA13

BA15

BA18

BA21

BA25

BA31

BA35

BA39

A15

AL31

AM29

C563

1U/10V_4

S5 DOMAI N

R55 *SHORT_8

R59 *0_8

S0 DOMAI N

C562

C548

1U/10V_4

1U/10V_4

C549

180p/50V_4

C177

10u/6.3V_8

C553

C191

1U/10V_4

10u/6.3V_8

R347 *SHORT_8

4

C567

1U/10V_4

C583

10u/6.3V_8

C551

1U/10V_4

C588

1U/10V_4

C573

1U/10V_4

C554

0.1U/10V_4

C575

1U/10V_4

C162

0.1U/10V_4

C587

1U/10V_4

C589

1U/10V_4

C568

0.1U/10V_4

C576

1U/10V_4

C586

1U/10V_4

3

C552

180p/50V_4

C574

180p/50V_4

+0.95V

C192

10u/6.3V_8

R51 *SHORT_8

C287

10u/6.3V_8

VDD_0.95V_ALW+0.95V_S5+1.8V APU_VDD_18

C286

1U/10V_4

C176

10u/6.3V_8

C184

1U/10V_4

C166

10u/6.3V_8

C288

1U/10V_4

C190

10u/6.3V_8

C189

1U/10V_4

C156

10u/6.3V_8

C282

1U/10V_4

C210

1U/10V_4

2

C193

180p/50V_4

C208

1U/10V_4

Power trace tracking

C209

C219

1U/10V_4

1U/10V_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

+1.5V_SUS<3,9,10,32,37>

+1.5V<24,25,32,35>

+3V_S5<5,6,8,23,24,26,27,28,29,31,36>

+3V<4,5,9,10,21,22,23,24,25,27,28,29,31,32,33,34,35,36,37>

+1.8V<4,35>

+1.8V_S5<5,8,35,37>

+0.95V<3,6,33,35>

+0.95V_S5<33>

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

POWER/GND(5/6)

POWER/GND(5/6)

POWER/GND(5/6)

+1.5V_SUS

+1.5V

+3V_S5

+3V

+1.8V

+1.8V_S5

+0.95V

+0.95V_S5

ZQN

ZQN

ZQN

1A

1A

1A

of

7 39Tuesday, April 29, 2014

7 39Tuesday, April 29, 2014

1

7 39Tuesday, April 29, 2014

+3V APU_VDD_33

R102 *SHORT_8

A A

+1.8V_S5 APU_VDD18_ALW

R308 *SHORT_8

C218

4.7U/6.3V_6

C542

4.7U/6.3V_6

5

C221

1U/10V_4

C560

1U/10V_4

+0.95V +0.95V_S5 +0.95V_DUAL

C228

C227

180p/50V_4

1U/10V_4

C561

C564

1U/10V_4

1U/10V_4

Page 8

5

4

3

2

1

STRAPS PINS

D D

LPC_CLK0<6>

LPC_CLK1<6>

LPC_LFRAME#<6,24,29>

GEVENT2#<5>

RTC_CLK<6>

C C

LPC_CLK0

LPC_CLK1

LPC_LFRAME#

GEVENT2#

RTC_CLK

OVERLAP COMMON PADS WHERE

POSSIBLE FOR DUAL-OP RESISTORS.

+3V_S5 +3V_S5 +3V_S5+3V_S5

R354

*10K/F_4

R353

2K/F_4

R358

10K/F_4

R357

*2K/F_4

R320

10K/F_4

R319

*2K/F_4

R415

*10K/F_4

R414

2K/F_4

+3V_S5

R395

*10K_4

R394

*2K/F_4

DEBUG STRAPS

REQUIRED STRAPS

PULL

HIGH

PULL

LOW

RTC_CLK

Normal power up

DEFAULT

Fast power on

LPC_CLK0

BOOT FAIL TIMER

ENABLED

BOOT FAIL TIMER

DISABLED

DEFAULT

LPC_CLK1

CLKGEN

ENABLED

DEFAULT

CLKGEN

DISABLED

LFRAME#

SPI ROM

DEFAULT

LPC ROM

GEVENT2#

1.8V SPI ROM

3.3V SPI ROM

DEFAULT

Power trace tracking

+3V<4,5,7,9,10,21,22,23,24,25,27,28,29,31,32,33,34,35,36,37>

+3V_S5<5,6,7,23,24,26,27,28,29,31,36>

+3V

+3V_S5

B B

SYS PWRGD

+3V_S5

2

D5 *1N4148WS

D7 1N4148WS

D6 1N4148WS

R169

100K_4

3

Q16

2N7002K

1

4

2

SYS_RST#<5>

SUSB#<5,29>

PWROK_EC<29>

A A

HWPG<29>

5

+1.8V_S5

R142

10K/F_4

C316

0.1U/10V_4

3

Q10

2N7002K

1

2

1

SYS_PWRGD_R

+3V_S5

3 5

*TC7SH08FU

C308

*0.1U/10V_4

U10

SYS_PWRGD

4

R134 *SHORT_4

3

SYS_PWRGD <5,28>

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

STRAP(6/6)

STRAP(6/6)

STRAP(6/6)

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZQN

ZQN

ZQN

1A

1A

8 39Tuesday, April 29, 2014

8 39Tuesday, April 29, 2014

1

8 39Tuesday, April 29, 2014

1A

Page 9

5

4

3

2

1

2.48A

+3V

+1.5V_SUS

JDIM2B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

DDR3-DIMM_H=4_STD

+SMDDR_VREF

3mA

PC2100 DDR3 SDRAM SO-DIMM

R223 *0_6

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

(204P)

VTT1

VTT2

+1.5V_SUS

GND

GND

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

205

206

R219

1K/F_4

+DDR_VREF

R211

1K/F_4

+SMDDR_VTT

M_A_A[15:0]<3,10>

D D

M_A_BS#0<3,10>

M_A_BS#1<3,10>

M_A_BS#2<3,10>

M_A_CS#0<3>

M_A_CS#1<3>

M_A_CLK0<3>

M_A_CLK0#<3>

M_A_CLK1<3>

M_A_CLK1#<3>

M_A_CKE0<3>

M_A_CKE1<3>

M_A_CAS#<3,10>

M_A_RAS#<3,10>

R198 10K_4

R200 10K_4

C C

B B

+1.5V_SUS +1.5V_SUS

Place these Caps near So-Dimm1.

M_A_WE#<3,10>

CLK_SCLK<5,10,24>

CLK_SDATA<5,10,24>

M_A_ODT0<3>

M_A_ODT1<3>

M_DM[7..0]<3,10>

M_A_DQS[7:0]<3,10>

M_A_DQS#[7:0]<3,10>

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

DIMM2_SA0

DIMM2_SA1

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

JDIM2A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3-DIMM_H=4_STD

PC2100 DDR3 SDRAM SO-DIMM

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

(204P)

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQ[63:0] <3,10>

M_A_EVENT#<3,10>

DDR3_DRAMRST#<3,10>

+DDR_VREF2

+DDR_VREF

Stitching Cap

M_A_EVENT#

C325 0.1u/10V_4

C332 0.1u/10V_4

C380 1000p/50V_4

C383 0.1u/10V_4

+DDR_VREF2

+DDR_VREF

C416 0.1u/10V_4

C408 1000p/50V_4

C398 0.1u/10V_4

C430 0.1u/10V_4

C384

0.22u/10V_4

+1.5V_SUS

C418

0.22u/10V_4

C389

0.22u/10V_4

C419

0.22u/10V_4

C421

0.22u/10V_4

C422

0.22u/10V_4

C439

0.22u/10V_4

+SMDDR_VTT

C438

0.22u/10V_4

C440

0.22u/10V_4

C437

0.22u/10V_4

+SMDDR_VTT

C436

0.22u/10V_4

+1.5V_SUS

C357

180p/50V_4

C359

180p/50V_4

+SMDDR_VREF

R209 *0_6

3mA

C423

0.22u/10V_4

A A

+1.5V_SUS

C427

0.22u/10V_4

C426

0.22u/10V_4

C385

0.22u/10V_4

5

C388

0.22u/10V_4

C420

0.22u/10V_4

C391

0.22u/10V_4

C387

0.22u/10V_4

C386

0.22u/10V_4

C392

0.22u/10V_4

C390

0.22u/10V_4

C417

0.22u/10V_4

C425

0.22u/10V_4

4

C394

0.22u/10V_4

C424

0.22u/10V_4

C429

0.22u/10V_4

C411

0.22u/10V_4

C381

0.22u/10V_4

Power trace tracking

3

C413

0.22u/10V_4

+1.5V_SUS<3,7,10,32,37>

+3V<4,5,7,10,21,22,23,24,25,27,28,29,31,32,33,34,35,36,37>

+SMDDR_VTT<10,32>

+SMDDR_VREF<32>

+DDR_VREF2<10>

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DDRIII SO-DIMM-1

DDRIII SO-DIMM-1

DDRIII SO-DIMM-1

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1.5V_SUS

20K=>1K

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

R206

1K/F_4

+DDR_VREF2

R191

1K/F_4

1

ZQN

ZQN

ZQN

9 39Thursday, March 27, 2014

9 39Thursday, March 27, 2014

9 39Thursday, March 27, 2014

1A

1A

1A

Page 10

1

2

3

4

5

6

7

8

2.48A

+3V

+1.5V_SUS

JDIM1B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

DDR3-DIMM_H=4_RVS

PC2100 DDR3 SDRAM SO-DIMM

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

GND

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

205

206

+SMDDR_VTT

M_A_A[15:0]<3,9>

A A

M_A_BS#0<3,9>

M_A_BS#1<3,9>

M_A_BS#2<3,9>

M_B_CS#0<3>

M_B_CS#1<3>

M_B_CLK0<3>

M_B_CLK0#<3>

M_B_CLK1<3>

M_B_CLK1#<3>

+3V

R163 10K_4

R162 10K_4

B B

10/1 For DIM1

C C

+1.5V_SUS +1.5V_SUS

Place these Caps near So-Dimm1.

M_B_CKE0<3>

M_B_CKE1<3>

M_A_CAS#<3,9>

M_A_RAS#<3,9>

M_A_WE#<3,9>

CLK_SCLK<5,9,24>

CLK_SDATA<5,9,24>

M_B_ODT0<3>

M_B_ODT1<3>

M_DM[7..0]<3,9>

M_A_DQS[7:0]<3,9>

M_A_DQS#[7:0]<3,9>

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

DIMM1_SA0

DIMM1_SA1

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

JDIM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3-DIMM_H=4_RVS

PC2100 DDR3 SDRAM SO-DIMM

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

(204P)

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQ[63:0] <3,9>

M_A_EVENT#<3,9>

DDR3_DRAMRST#<3,9>

+DDR_VREF2

+DDR_VREF

M_A_EVENT#

C376 0.1u/10V_4

C346 0.1u/10V_4

C348 1000p/50V_4

C323 0.1u/10V_4

C358 0.1u/10V_4

C360 1000p/50V_4

C349 0.1u/10V_4

C350 0.1u/10V_4

C367

0.22u/10V_4

+1.5V_SUS

C335

0.22u/10V_4

D D

+1.5V_SUS

C345

0.22u/10V_4

C374

0.22u/10V_4

C341

0.22u/10V_4

C375

0.22u/10V_4

1

C373

0.22u/10V_4

C372

0.22u/10V_4

C369

0.22u/10V_4

C370

0.22u/10V_4

C336

0.22u/10V_4

C337

0.22u/10V_4

2

C343

0.22u/10V_4

C340

0.22u/10V_4

C371

0.22u/10V_4

C339

0.22u/10V_4

C338

0.22u/10V_4

C342

0.22u/10V_4

+SMDDR_VTT

C344

0.22u/10V_4

3

C318

0.22u/10V_4

C330

0.22u/10V_4

C368

0.22u/10V_4

C310

0.22u/10V_4

C333

0.22u/10V_4

C324

0.22u/10V_4

C366

0.22u/10V_4

Power trace tracking

4

C315

0.22u/10V_4

+SMDDR_VTT

C365

0.22u/10V_4

C326

0.22u/10V_4

C347

0.22u/10V_4

Quanta Computer Inc.

Quanta Computer Inc.

+1.5V_SUS<3,7,9,32,37>

+3V<4,5,7,9,21,22,23,24,25,27,28,29,31,32,33,34,35,36,37>

+SMDDR_VTT<9,32>

+SMDDR_VREF<9,32>

+DDR_VREF2<9>

5

6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DDRIII SO-DIMM-1

DDRIII SO-DIMM-1

DDRIII SO-DIMM-1

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

7

ZQN

ZQN

ZQN

1A

1A

1A

10 39Thursday, February 20, 2014

10 39Thursday, February 20, 2014

10 39Thursday, February 20, 2014

8

Page 11

PART 1 0F 9

U19A

AA38

W36

W38

U36

U38

R36

R38

N36

N38

M37

M35

H37

H35

G36

G38

Y37

Y35

V37

V35

T37

T35

P37

P35

L36

L38

K37

K35

J36

J38

F37

F35

E37

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCI EXPRESS INTERFACE

PEG _TXP0<3>

PEG _TXN0<3 >

PEG _TXP1<3>

PEG _TXN1<3 >

PEG _TXP2<3>

PEG _TXN2<3 >

PEG _TXP3<3>

PEG _TXN3<3 >

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Y33

Y32

W33

W32

U33

U32

U30

U29

T33

T32

T30

T29

P33

P32

P30

P29

N33

N32

N30

N29

L33

L32

L30

L29

K33

K32

J33

J32

K30

K29

H33

H32

PEG _RXP0_ C

PEG _RXN0_C

PEG _RXP1_ C

PEG _RXN1_C

PEG _RXP2_ C

PEG _RXN2_C

PEG _RXP3_ C

PEG _RXN3_C

C53 1 *EV@0 .1u/10V_ 4

C53 8 *EV@0 .1u/10V_ 4

C52 8 *EV@0 .1u/10V_ 4

C53 0 *EV@0 .1u/10V_ 4

C52 5 *EV@0 .1u/10V_ 4

C52 6 *EV@0 .1u/10V_ 4

C52 3 *EV@0 .1u/10V_ 4

C52 2 *EV@0 .1u/10V_ 4

DGP U_RST_L<5>

PCI ERST#<5,23 ,24,27>

+3V_ GFX

C54 1 *EV@0 .1u/10V_ 4

U20

2

1

*EV@T C7SH08 FU(F)

3 5

PEG _RXP0 <3 >