5

Dr-Bios.com

4

3

2

1

!"

D D

C C

Cardreader

CONN. 2in 1

P28

I/O board

B B

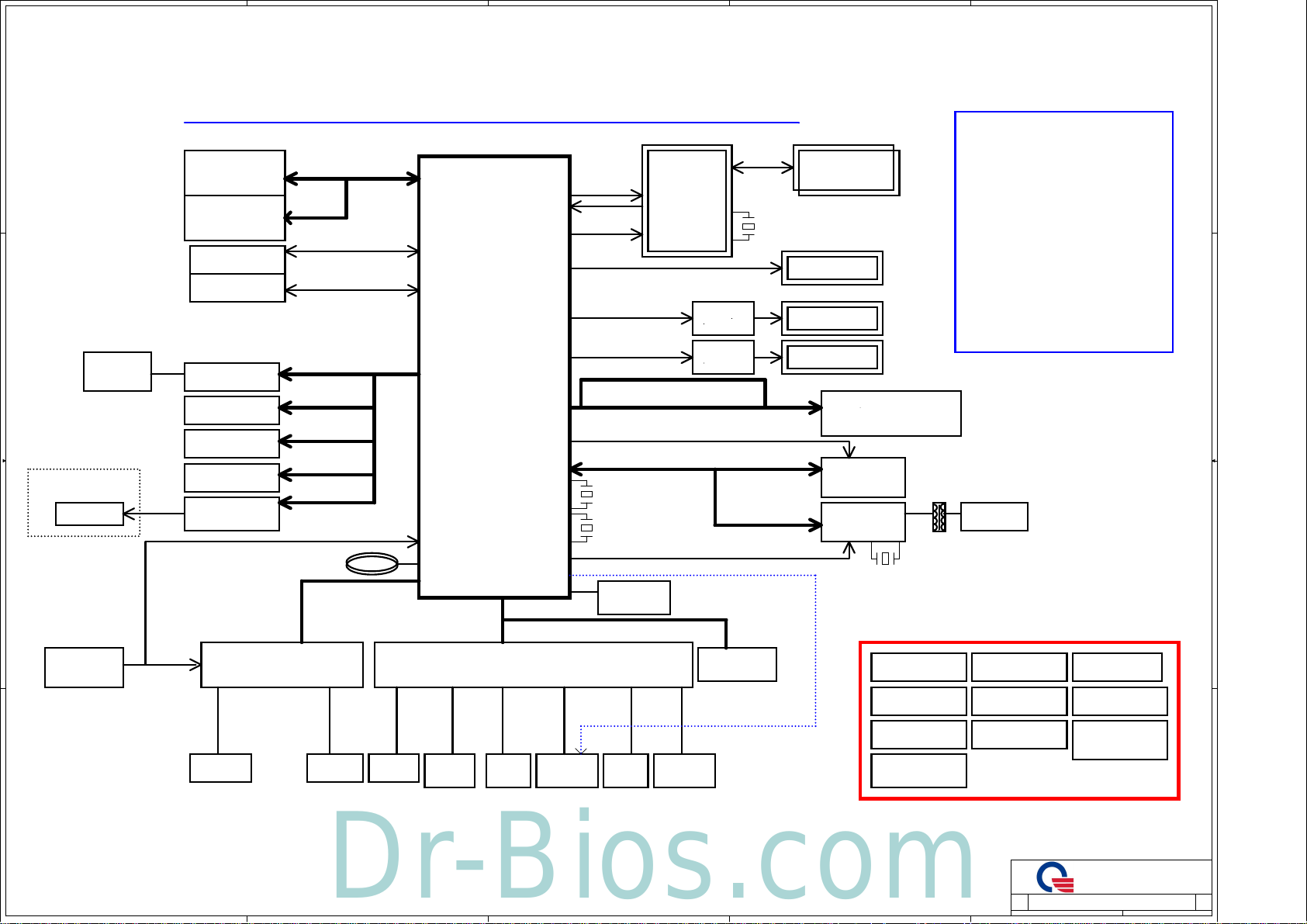

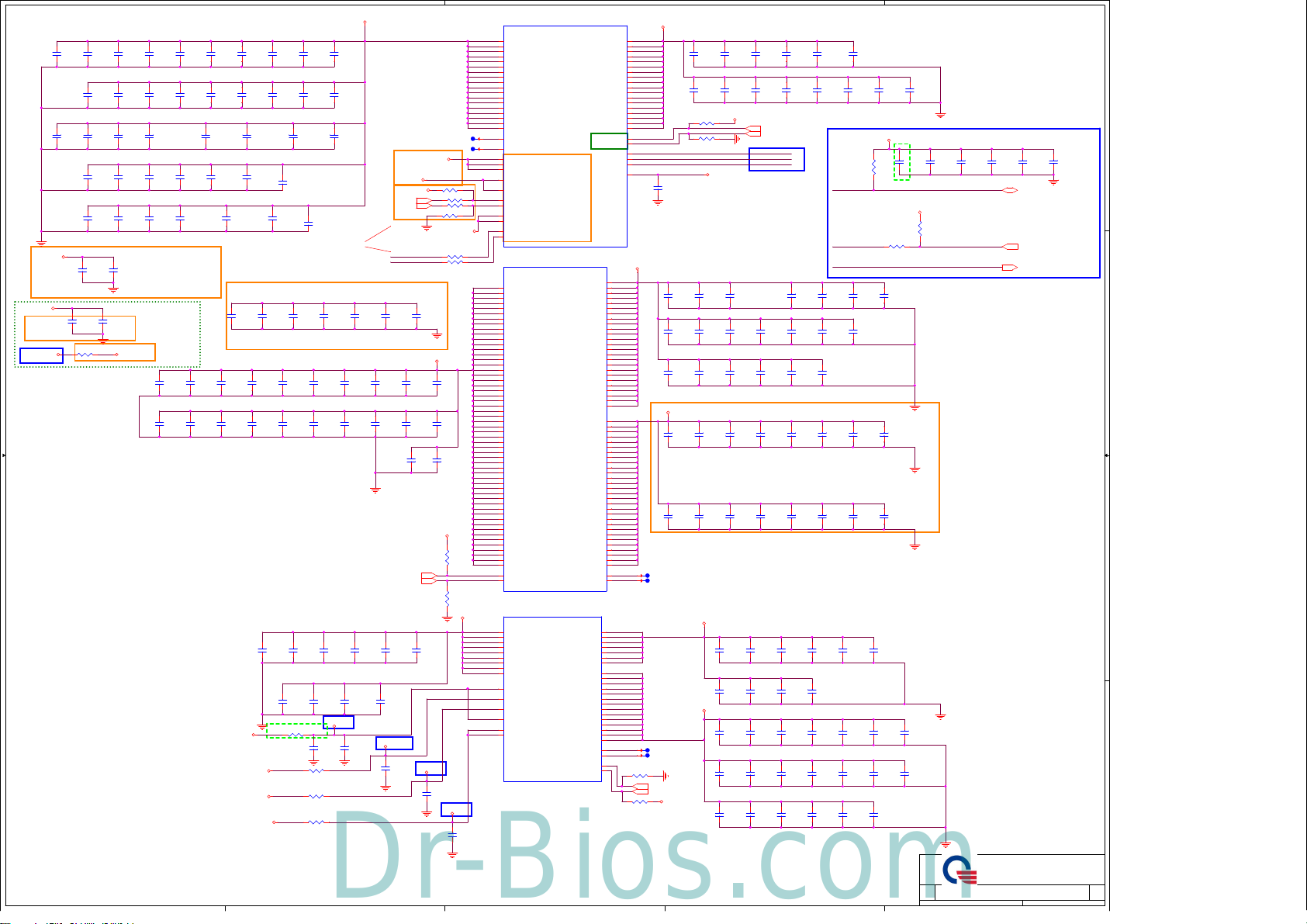

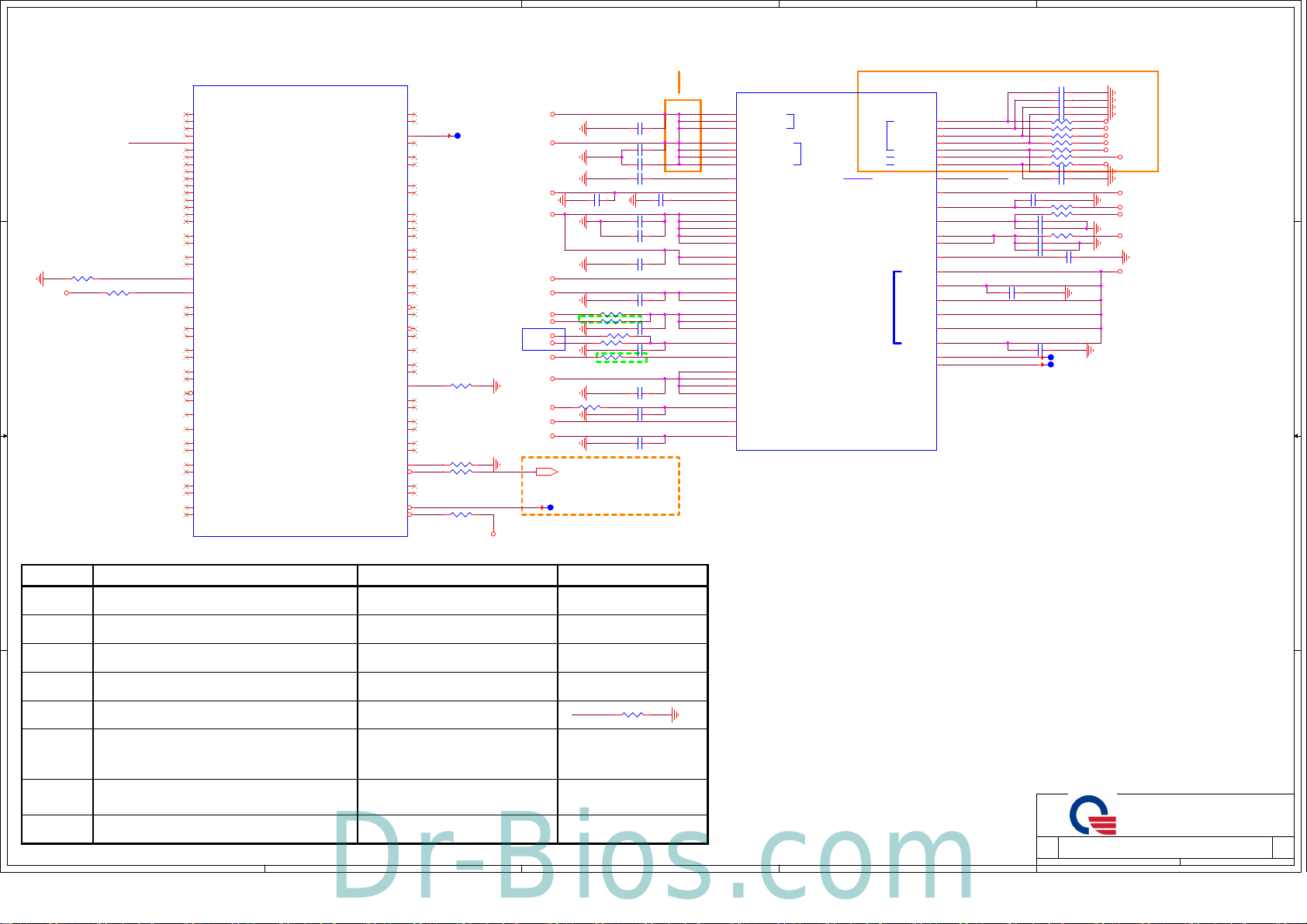

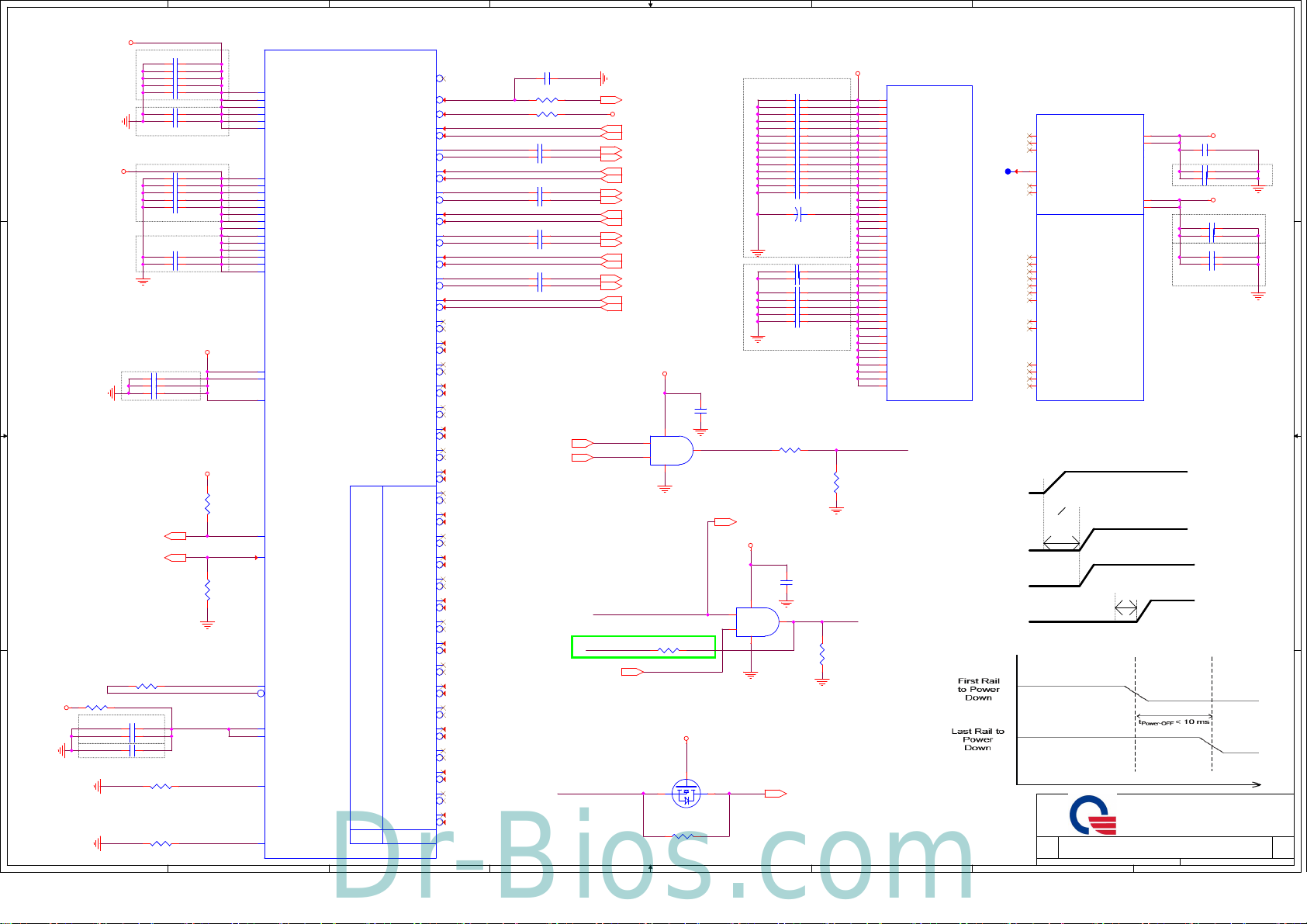

Zoro_SL (ZRW) SKL ULT SYSTEM BLOCK DIAGRAM

DDR3L-SODIMM CHA

P12

DDR3L-SODIMM CHB

P13

SATA - HDD

SATA ODD

RTS5170

(cardreader)

CCD(Camera)

Touch Screen

Blue Tooth

I/O Board Conn.USB2 IO*1

P25

P25

P28

P21

P21

P26

P28

Dual Channel DDR III

1066/1333/1600 MHZ

SATA0

SATA1

USB2-8

USB2-7

USB2-6

USB2-5

USB2-4

P6

BATTERY

Azalia

SKY LAKE ULT 15W

MCP 1356pins

IMC

DC+GT3e

42 mm X 24 mm

SATA

Integrated PCH

USB2.0

DMIC_CLK0

DMIC_DATA0

RTC

IHDA

P2~P10

LPC

PCI-E x4

TX/RX

CLK

eDP

USB3.0/2.0

CLK

PCI-E x1

CLK

I2C_0

SPI

DP

PCIE1-4

EDP

DDI2

DDI1

USB3-1 & USB3-2

USB2-1 & USB2-2

X'TAL

32.768KHz

X'TAL 24MHz

SPI ROM

8M+4M

GPU

N16S-GT

N16V-GM

P7

P14~P19

ITE6516

PS8201

X'TAL 27MHz

P20

P22

PCIE-6

PCIE-5

VRAM

DDR3

P18~P19

eDP Conn.

VGA Conn.

HDMI Conn.

P21

P21

P22

USB3 Port MB side

CN13 -> USB3 port 2 ( up )

CN16 -> USB3 port 1 ( down )

MINI CARD

WLAN+BT

RTL8111H

10/100/1G

P26

P23

X'TAL 25MHz

IV@ : iGPU

EV@ : Optimus

GT@ : N16S-GT / GC6

GM@ : N16V-GM / WO GC6

DR@ : For Dual Rank ( VRAM 8 pcs)

KBL@ : Keyboard backlight

TPM@ : TPM

TPM_N@: For TPM 2.0

TPM_l@ : For TPM 1.2

8M@ : 8M FLASH ROM

4M@ : 4M FLASH ROM

GS@ :G-SENSOR

TDI@ : TOUCH PAD I2C

TSU@ : TOUCH SCREEN USB

TSI@ : TOUCH SCREEN I2C

GT3@ : GT3 CPU

NAC@ : Non IOAC

IOAC@ : For IOAC

P28

RJ45

P23

BOM

K/B

BL

Con.

EC

IT8987

P27

Touch PAD

P27

HALL

SENSOR

3

P17

P29

Fan Driver

(Fan signal)

TPM(option)

P27

P25

2

BQ24780RUYR

Batery C harger

TPS51225

+3V/+5V

RT8237CZQW

+1V_S5

NB681GD-Z

+VCCOPC/+VCCEOPIO

G5316RZ1D

+1.35VSUS

P30

MDV1528Q

+5V_S5/+3V_S5/+3V/+5V

P31

ISL95859HRT Z-T

+VCORE/VCCSA/VCCGT

P32

P33

Thermal Protection

P35

Discharger

UP1658RQKF

+VGPU_CORE

P31

RT8068AZQW

P38

+1.05V_GFX/+3V_GFX

+1.5V_GFX

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

P7

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

1

P40

ZRW

ZRW

ZRW

P41

P42

148Monday, July 20, 2015

148Monday, July 20, 2015

148Monday, July 20, 2015

D-MIC

Int. D -MIC

P24

Universal HP

A A

ALC25 5

AUDIO CODEC

P24 P24

P24

Speaker*2

LED

P27

K/B Con.

P27

5

4

3A

3A

3A

5

Dr-Bios.com

4

3

2

1

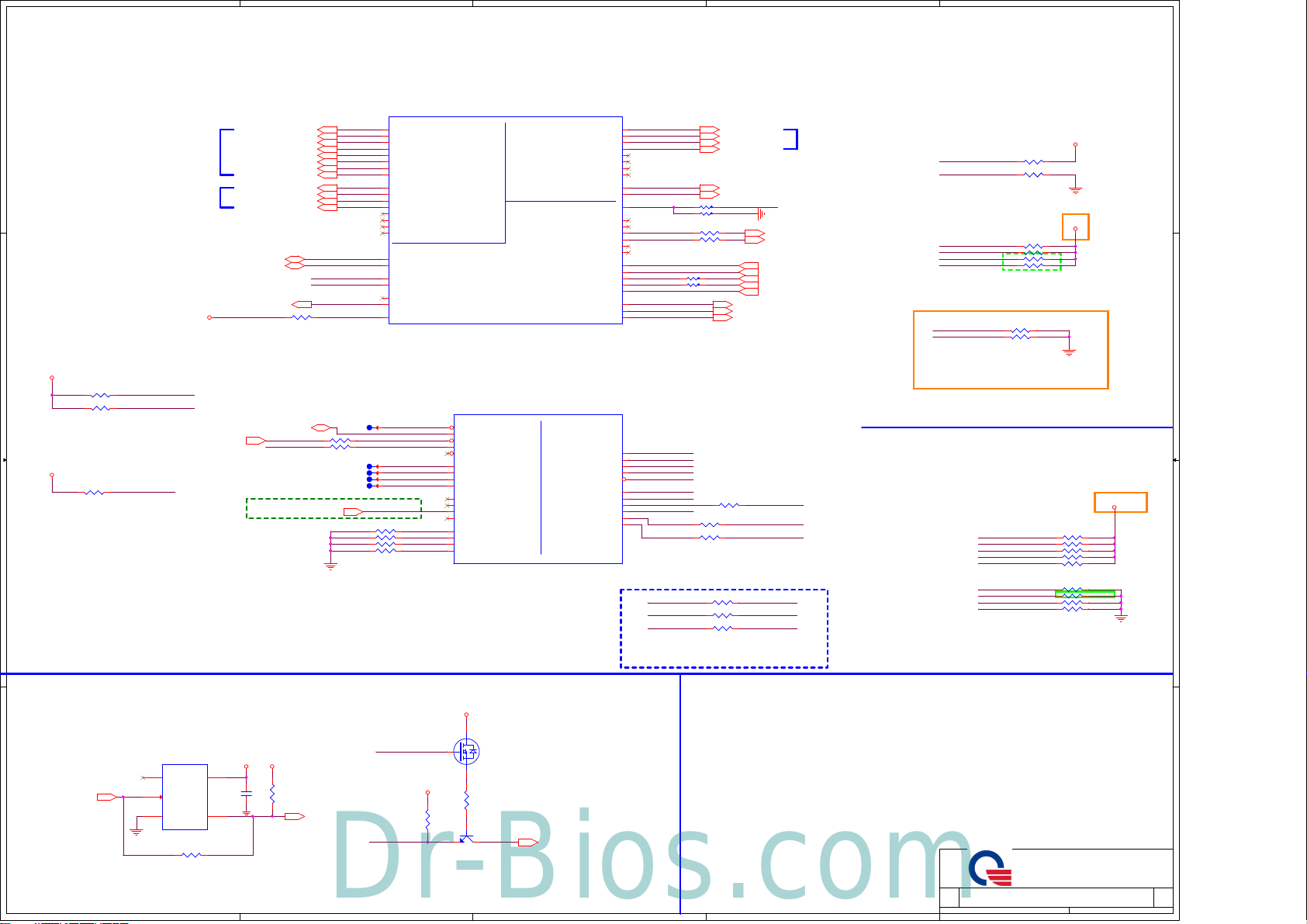

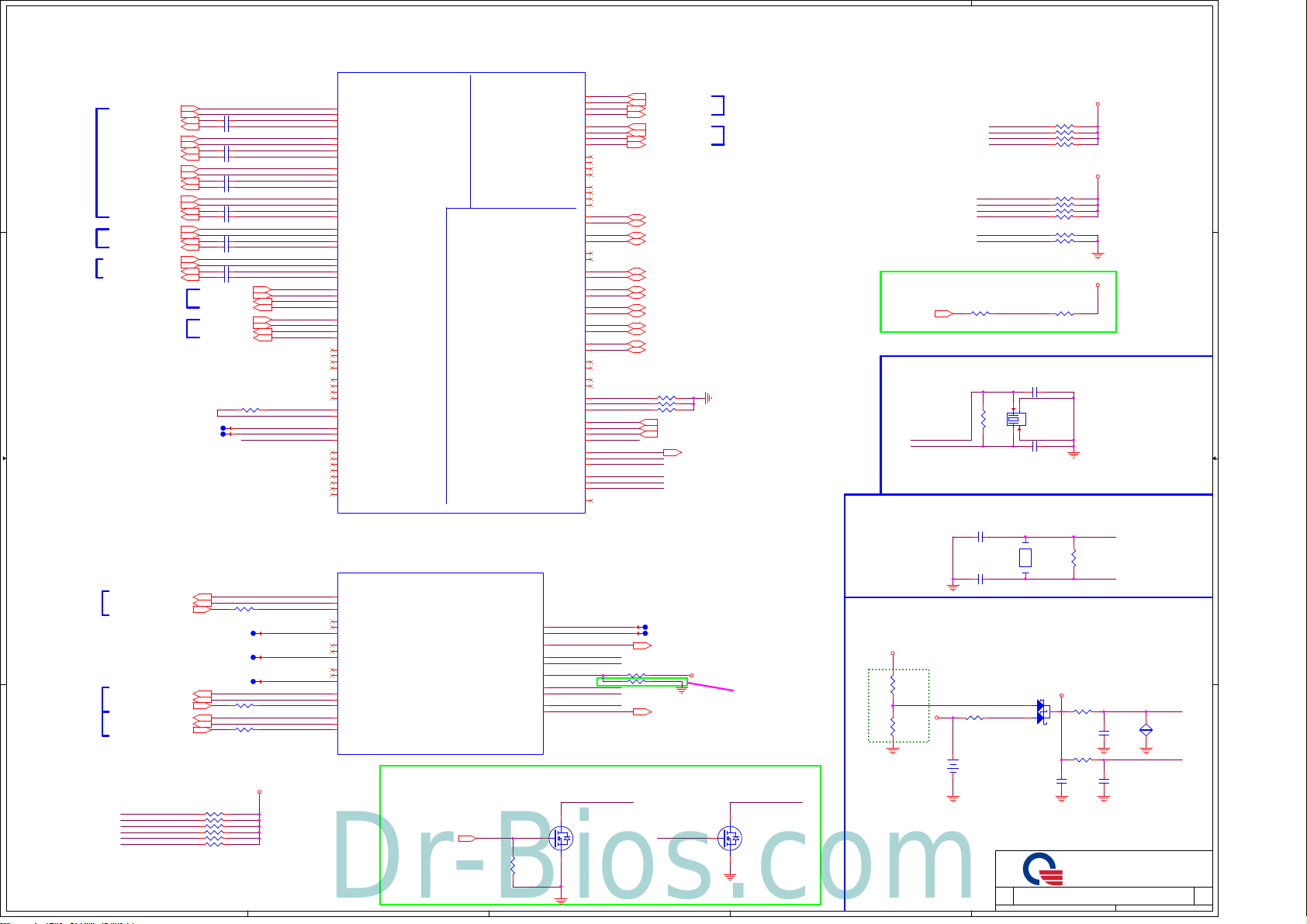

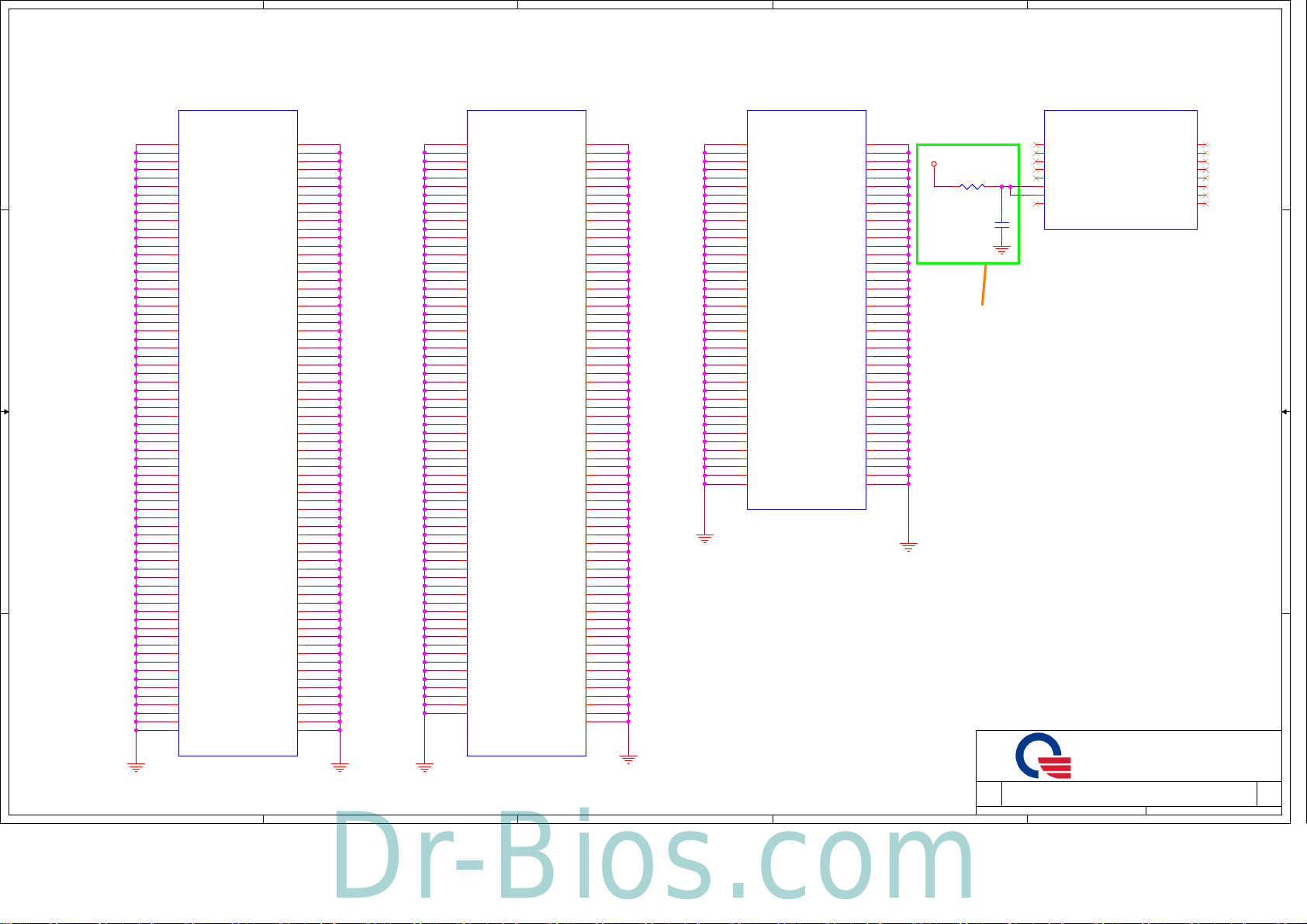

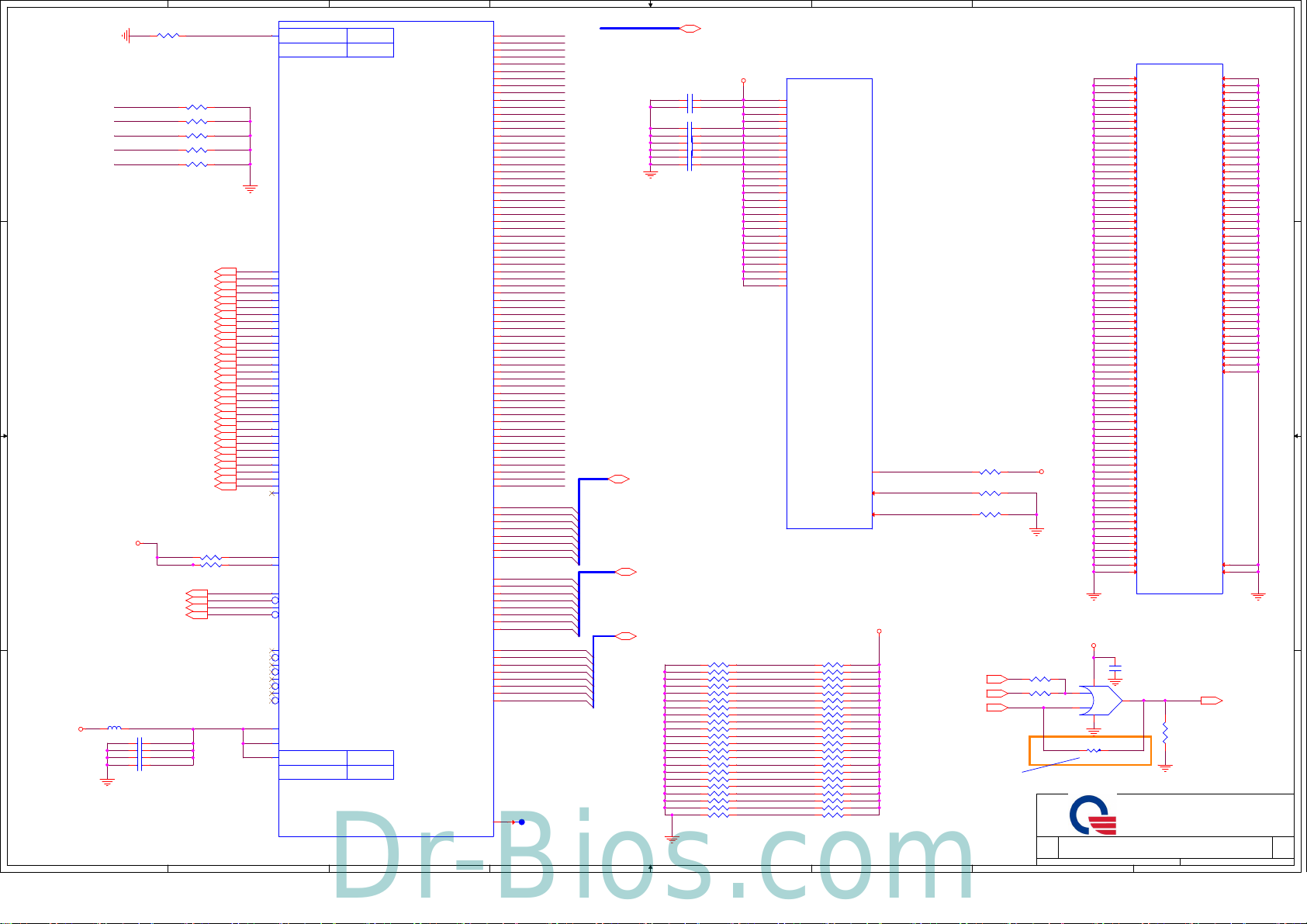

Skylake ULT (DISPLAY,eDP)

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

H66

H65

SKL_ULT

DDI

DISPLAY SIDEBANDS

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

U35D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL_ULT/BGA

REV = 1

SKL_ULT

1 OF 20

+3V_S5

+3V_S5

+3V_S5

+3V_S5

EDP

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

4 OF 20

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

C47

EDP_TXN0

C46

EDP_TXP0

D46

EDP_TXN1

C45

EDP_TXP1

A45

B45

A47

B47

E45

EDP_AUXN

F45

EDP_AUXP

B52

G50

F50

E48

CRT_AUX#_C

F48

CRT_AUX_C

G46

F46

L9

INT_HDMI_HPD

L7

CRT_HPD

L6

R567 *short_4

N9

R571 *short_4

L10

EDP_HPD

R12

PCH_BLON

R11

PCH_BRIGHT

U13

PCH_VDDEN

?

B61

XDP_TCK0

D60

XDP_TDI_CPU

A61

XDP_TDO_CPU

C60

XDP_TMS_CPU

B59

XDP_TRST#

B56

XDP_TCK1

D59

XDP_TDI

A56

PCH _JTAG_TDO

C59

XDP_TMS

C61

A59

PCH_TRST#

PCH_JTAGX

EDP_TXN0 (21)

EDP_TXP0 (21)

EDP_TXN1 (21)

EDP_TXP1 (21)

EDP_AUXN (21)

EDP_AUXP (21)

R546 *0_4

R553 *0_4

C671 *short_4

C670 *short_4

Rev:D change to shortpad

R539 *short_4

R549 *short_4

R517 *short_4

Rev:D change to shortpad

?

XDP_TDO

R795 0_4

XDP_TDI

R796 0_4

If use Intel DCI USB 3.0 fixture need to short

1. XDP_TDO <--> XDP_TDO_CPU

2. XDP_TDI <--> XDP_TDI_CPU

3. XDP_TMS <--> XDP_TMS_CPU

R797 0_4

PCH_BRIGHTDP_UTIL

CRT_AUXN (20)

CRT_AUXP (20)

INT_HDMI_HPD (22)

CRT_HPD (20)

KBSMI# (29)

EC_SCI# (29)

EDP_HPD (21)

PCH_BLON (21)

PCH_BRIGHT (21)

EDP_VDD_EN (21)

XDP_TDO

XDP_TRST#

XDP_TCK0

XDP_TDO_CPU

XDP_TDI_CPU

XDP_TMS_CPUXDP_TMS

Rev:F add

eDP Panel

PCH JTAG

TCK,TMS

Trace Length < 9000mi ls

H_PWRGOOD (50ohm )

Trace Length: 1~11.25 inc hes

CRT_AUXN

CRT_AUXP

CRT_CLK

CRT_DATA

KBSMI#

EC_SCI#

CRT_HPD

EDP_HPD

100k pull-down on PCH side

JTAG_TCK,JTAG_TMS

Trace Length < 9000mils

R533 *100K_4

R532 *100K_4

R577 2.2K_4

R152 2.2K_4

R780 20K/F_4

R781 20K/F_4

Rev:D add

R564 100K_4

R563 100K_4

Change to +1V_VCCST 11/6

XDP_TDO_CPU

XDP_TMS

XDP_TDI

PCH _JTAG_TDO

PCH_JTAGX

XDP_TRST#

XDP_TCK0

XDP_TCK1

PCH_TRST#

2/16

,XDP_TCK1,XDP_ TMS

don't need pull up or pull down

5/29 XDP_TCK0 R558 Stuff

R559 51_4

R514 51_4

R515 51_4

R538 51_4

R513 *1K_4

R535 *51_4

R558 51_4

R537 *51_4

R534 51_4

D D

HDMICRT

+VCCIO

C C

+1V_VCCST

CPU_THRMTRIP#

R5291K_4

CATERR#

Rev:E Stuff only for C2 build Debug

Ramp will remove

+VCCIO

R465 1K_4

B B

R78849.9/F_4

H_PROCHOT#

H_PROCHOT#(29,30,36)

Avoid 125Mhz

BPM#[0:7]

Trace Length 1~6 inches

Length match < 300 mils

H_PECI (50ohm )

Route on mi crostrip only

Spacing >18 mi ls

Trace Length: 0.4~6.125 iches

SM_RCOMP[0: 2]

Trace length < 500 m ils

Trace width = 12~15 m ils

Trace spacing = 20 m ils

INT_HDMITX2N(22)

INT_HDMITX2P(22)

INT_HDMITX1N(22)

INT_HDMITX1P(22)

INT_HDMITX0N(22)

INT_HDMITX0P(22)

INT_HDMICLK-(22)

INT_HDMICLK+(22)

CRT_TXN0(20)

CRT_TXP0(20)

CRT_TXN1(20)

ITE FAE suggest CAP

should be at PCH side.

HDMI_DDCCLK_SW(22)

HDMI_DDCDATA_SW(22)

CRT_TXP1(20)

PCH_ODD_EN(25)

eDP_RCOMP

Trace length < 100 mils

Trace width = 20 mils

Trace spacing = 25 mils

H_PECI(29)

THRMTRIP#

DGPU_PW_CTRL#(4)

HDMI_DDCCLK_SW

HDMI_DDCDATA_SW

CRT_CLK

CRT_DATA

EDP_RCOMP

R15424.9/F_4

TP65

R531 499/F_4

R530 100/F_4

TP89

TP90

TP64

TP62

U35A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL_ULT/BGA

REV = 1

CATERR#

H_PECI

H_PROCHOT#_RH_PROCHOT#

CPU_THRMTRIP#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

DGPU_PW_CTRL#

R635 49.9/F_4

R646 49.9/F_4

R158 49.9/F_4

R162 49.9/F_4

!#

+3V

+3V

MP remove(Inte l)

+1V_VCCST

+1V_VCCST

+1V_VCCST

2

R488

*1K_4

1 3

Q5 MMBT3904-7-F

3

Q31

FDV301N

1

R74

1K_4

2

SYS_SHDN# (31,40)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

3

2

Monday, July 20, 2015

PROJECT :

Skylake 1/4 (DDI/eDP)

Skylake 1/4 (DDI/eDP)

Skylake 1/4 (DDI/eDP)

ZRW

ZRW

ZRW

1

3A

3A

248

248

248

3A

CPU thermal trip

+1V_VCCST

U33

NC1VCC

A A

IMVP_PWRGD(36)

2

A

GND3Y

74AUP1G07GW

R478 *0_4

5

C628

0.1u/16V_4

4

+3V

12

R485

10K_4

IMVP_PWRGD_3V (8)

IMVP_PWRGD_3V

THRMTRIP#

5

4

5

Dr-Bios.com

4

3

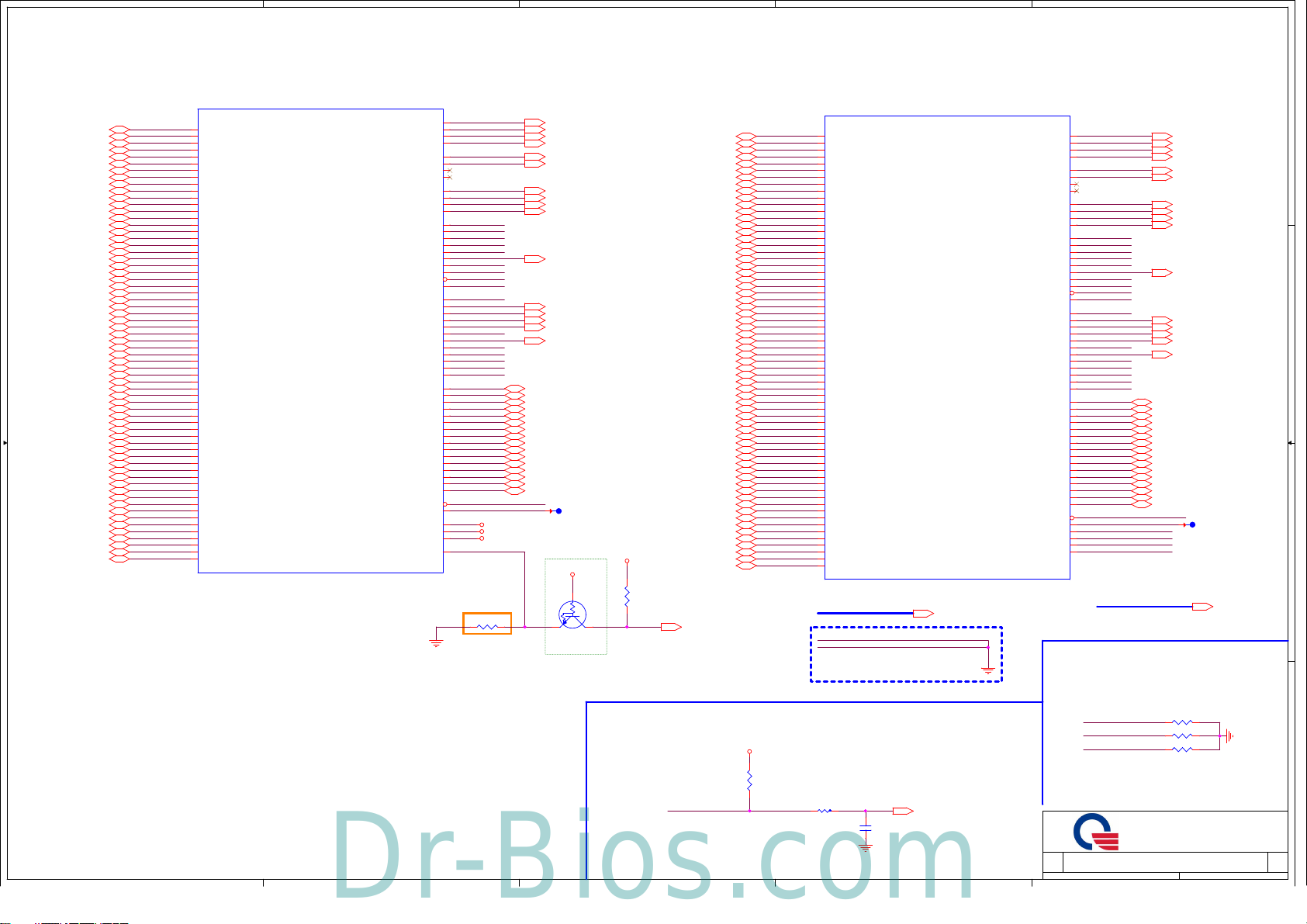

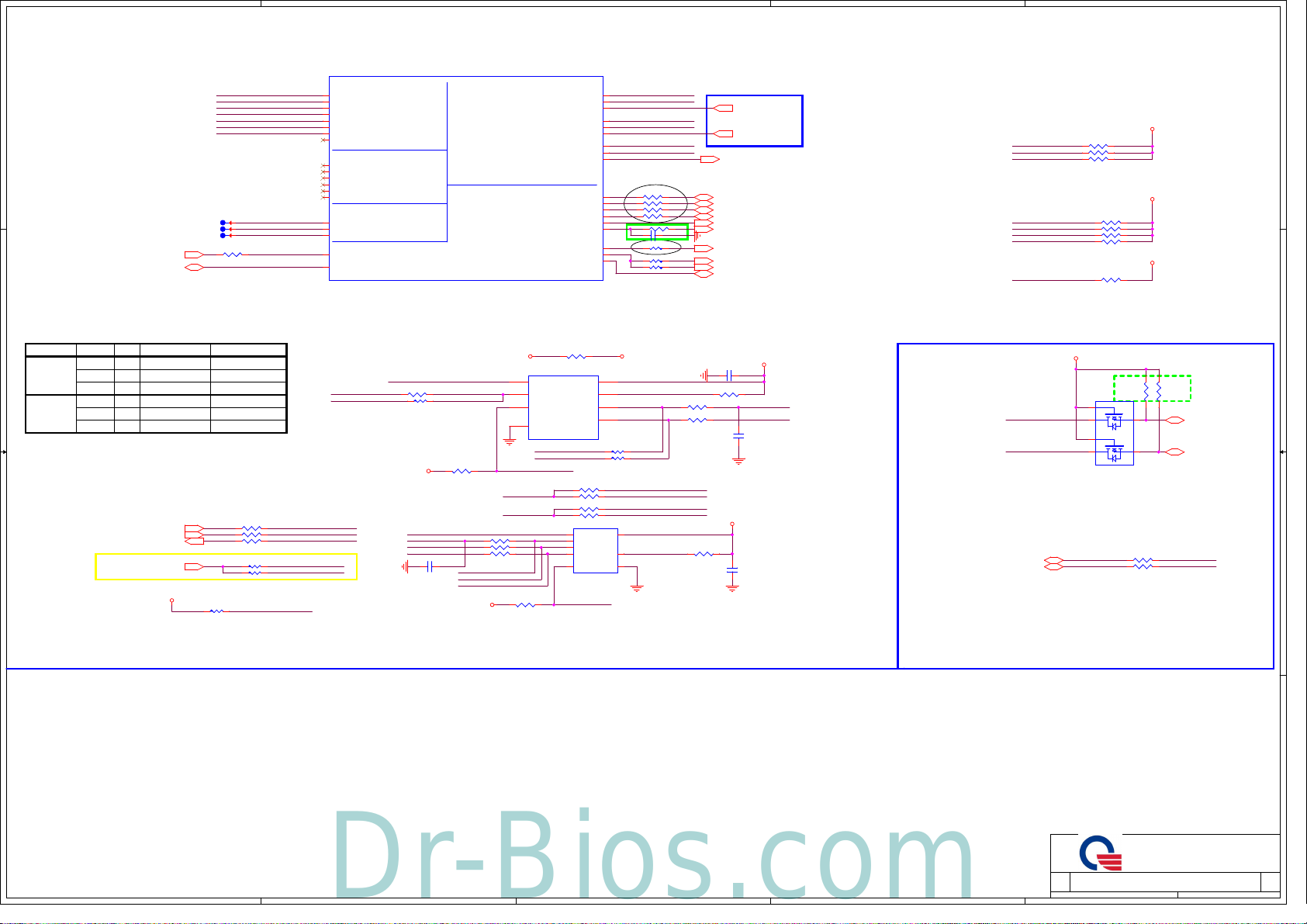

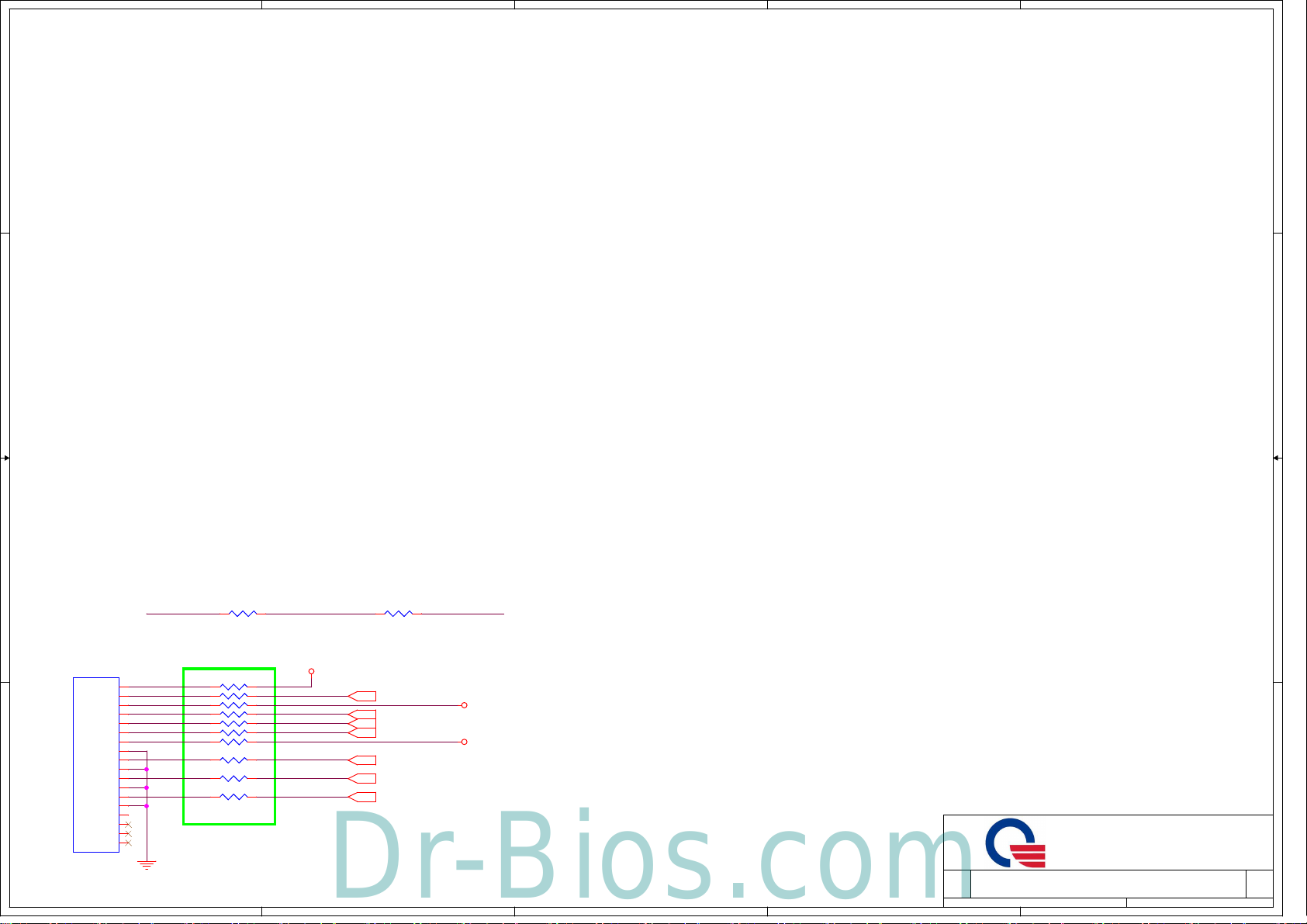

2

1

Change Data and DQS to interleave.

!$

?

D D

C C

B B

M_A_DQ0(12)

M_A_DQ1(12)

M_A_DQ2(12)

M_A_DQ3(12)

M_A_DQ4(12)

M_A_DQ5(12)

M_A_DQ6(12)

M_A_DQ7(12)

M_A_DQ8(12)

M_A_DQ9(12)

M_A_DQ10(12)

M_A_DQ11(12)

M_A_DQ12(12)

M_A_DQ13(12)

M_A_DQ14(12)

M_A_DQ15(12)

M_A_DQ16(12)

M_A_DQ17(12)

M_A_DQ18(12)

M_A_DQ19(12)

M_A_DQ20(12)

M_A_DQ21(12)

M_A_DQ22(12)

M_A_DQ23(12)

M_A_DQ24(12)

M_A_DQ25(12)

M_A_DQ26(12)

M_A_DQ27(12)

M_A_DQ28(12)

M_A_DQ29(12)

M_A_DQ30(12)

M_A_DQ31(12)

M_A_DQ32(12)

M_A_DQ33(12)

M_A_DQ34(12)

M_A_DQ35(12)

M_A_DQ36(12)

M_A_DQ37(12)

M_A_DQ38(12)

M_A_DQ39(12)

M_A_DQ40(12)

M_A_DQ41(12)

M_A_DQ42(12)

M_A_DQ43(12)

M_A_DQ44(12)

M_A_DQ45(12)

M_A_DQ46(12)

M_A_DQ47(12)

M_A_DQ48(12)

M_A_DQ49(12)

M_A_DQ50(12)

M_A_DQ51(12)

M_A_DQ52(12)

M_A_DQ53(12)

M_A_DQ54(12)

M_A_DQ55(12)

M_A_DQ56(12)

M_A_DQ57(12)

M_A_DQ58(12)

M_A_DQ59(12)

M_A_DQ60(12)

M_A_DQ61(12)

M_A_DQ62(12)

M_A_DQ63(12)

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U35B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL_ULT/BGA

REV = 1

SKL_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

?

M_A_ODT0

M_A_ODT1

M_A_A5

M_A_A9

M_A_A6

M_A_A8

M_A_A7

M_A_A12

M_A_A11

M_A_A15

M_A_A14

M_A_A13

M_A_A2

M_A_A10

M_A_A1

M_A_A0

M_A_A3

M_A_A4

M_A_DQS#0

M_A_DQS0

M_A_DQS#1

M_A_DQS1

M_A_DQS#2

M_A_DQS2

M_A_DQS#3

M_A_DQS3

M_A_DQS#4

M_A_DQS4

M_A_DQS#5

M_A_DQS5

M_A_DQS#6

M_A_DQS6

M_A_DQS#7

M_A_DQS7

DDR0_ALERT#

TP_DDR0_PARITY #

+VREF_CA_CPU

+VREFDQ_SA_M3

+VREFDQ_SB_M3

DDR_VTT_CTRL

R621 *10K_4

M_A_CLK0# (12)

M_A_CLK0 (12)

M_A_CLK1# (12)

M_A_CLK1 (12)

M_A_CKE0 (12)

M_A_CKE1 (12)

M_A_CS#0 (12)

M_A_CS#1 (12)

M_A_ODT0_DIMM (12)

M_A_ODT1_DIMM (12)

M_A_BS#2 (12)

M_A_CAS# (12)

M_A_WE# (12)

M_A_RAS# (12)

M_A_BS#0 (12)

M_A_BS#1 (12)

M_A_DQS#0 (12)

M_A_DQS0 (12)

M_A_DQS#1 (12)

M_A_DQS1 (12)

M_A_DQS#2 (12)

M_A_DQS2 (12)

M_A_DQS#3 (12)

M_A_DQS3 (12)

M_A_DQS#4 (12)

M_A_DQS4 (12)

M_A_DQS#5 (12)

M_A_DQS5 (12)

M_A_DQS#6 (12)

M_A_DQS6 (12)

M_A_DQS#7 (12)

M_A_DQS7 (12)

TP21

+1.35VSUS

2

1 3

Q35

*DTC144EU

+3V_S5

R682

*100K_4

M_B_DQ0(13)

M_B_DQ1(13)

M_B_DQ2(13)

M_B_DQ3(13)

M_B_DQ4(13)

M_B_DQ5(13)

M_B_DQ6(13)

M_B_DQ7(13)

M_B_DQ8(13)

M_B_DQ9(13)

M_B_DQ10(13)

M_B_DQ11(13)

M_B_DQ12(13)

M_B_DQ13(13)

M_B_DQ14(13)

M_B_DQ15(13)

M_B_DQ16(13)

M_B_DQ17(13)

M_B_DQ18(13)

M_B_DQ19(13)

M_B_DQ20(13)

M_B_DQ21(13)

M_B_DQ22(13)

M_B_DQ23(13)

M_B_DQ24(13)

M_B_DQ25(13)

M_B_DQ26(13)

M_B_DQ27(13)

M_B_DQ28(13)

M_B_DQ29(13)

M_B_DQ30(13)

M_B_DQ31(13)

M_B_DQ32(13)

M_B_DQ33(13)

M_B_DQ34(13)

M_B_DQ35(13)

M_B_DQ36(13)

M_B_DQ37(13)

M_B_DQ38(13)

M_B_DQ39(13)

M_B_DQ40(13)

M_B_DQ41(13)

M_B_DQ42(13)

M_B_DQ43(13)

M_B_DQ44(13)

M_B_DQ45(13)

M_B_DQ46(13)

M_B_DQ47(13)

M_B_DQ48(13)

M_B_DQ49(13)

M_B_DQ50(13)

M_B_DQ51(13)

M_B_DQ52(13)

M_B_DQ53(13)

M_B_DQ54(13)

M_B_DQ55(13)

M_B_DQ56(13)

M_B_DQ57(13)

M_B_DQ58(13)

M_B_DQ59(13)

M_B_DQ60(13)

M_B_DQ61(13)

M_B_DQ62(13)

M_B_DQ63(13)

DDR_VTTT_PG_CTRL (35)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AF65

AF64

AK65

AK64

AF66

AF67

AK67

AK66

AF70

AF68

AH71

AH68

AF71

AF69

AH70

AH69

AT66

AU66

AP65

AN65

AN66

AP66

AT65

AU65

AT61

AU61

AP60

AN60

AN61

AP61

AT60

AU60

AU40

AT40

AT37

AU37

AR40

AP40

AP37

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AU27

AT27

AT25

AU25

AP27

AN27

AN25

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

Stuff Q54 for both UMA and GPU in DDR_VTT_CNTL

SKL ULT (DDR3L)SKL ULT (DDR3L)

U35C

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ[18]

DDR1_DQ[3]/DDR0_DQ[19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ[22]

DDR1_DQ[7]/DDR0_DQ[23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

SKL_ULT/BGA

REV = 1

M_A_A[15:0]

DDR0_ALERT#

DDR1_ALERT#

&-./-)0122304)41)56%)

?

SKL_ULT

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

M_A_A[15:0] (12)

DDR1_ODT[1]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

?

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_ODT0

M_B_ODT1

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_A15

M_B_A14

M_B_A13

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

M_B_DQS#0

M_B_DQS0

M_B_DQS#1

M_B_DQS1

M_B_DQS#2

M_B_DQS2

M_B_DQS#3

M_B_DQS3

M_B_DQS#4

M_B_DQS4

M_B_DQS#5

M_B_DQS5

M_B_DQS#6

M_B_DQS6

M_B_DQS#7

M_B_DQS7

DDR1_ALERT#

TP_DDR1_PARITY #

CPU_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

M_B_A[15:0]

M_B_CLK0# (13)

M_B_CLK1# (13)

M_B_CLK0 (13)

M_B_CLK1 (13)

M_B_CKE0 (13)

M_B_CKE1 (13)

M_B_CS#0 (13)

M_B_CS#1 (13)

M_B_ODT0_DIMM (13)

M_B_ODT1_DIMM (13)

M_B_BS#2 (13)

M_B_CAS# (13)

M_B_WE# (13)

M_B_RAS# (13)

M_B_BS#0 (13)

M_B_BS#1 (13)

M_B_DQS#0 (13)

M_B_DQS0 (13)

M_B_DQS#1 (13)

M_B_DQS1 (13)

M_B_DQS#2 (13)

M_B_DQS2 (13)

M_B_DQS#3 (13)

M_B_DQS3 (13)

M_B_DQS#4 (13)

M_B_DQS4 (13)

M_B_DQS#5 (13)

M_B_DQS5 (13)

M_B_DQS#6 (13)

M_B_DQS6 (13)

M_B_DQS#7 (13)

M_B_DQS7 (13)

%&'()*+(,

TP18

M_B_A[15:0] (13)

DRAMRST

+1.35VSUS

A A

CPU DRAM

CPU_DRAMRST#

5

4

3

12

R679

470_4

R670 *short_4

12

C750

*0.1u/16V_4

DDR3_DRAMRST# (12 ,13)

2

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

PROJECT :

Skylake 2/3 (DDR3 I/F)

Skylake 2/3 (DDR3 I/F)

Skylake 2/3 (DDR3 I/F)

R685120/F_4

R67880.6/F_4

R681100/F_4

ZRW

ZRW

ZRW

3A

3A

348

348

1

348

3A

5

Dr-Bios.com

4

3

2

1

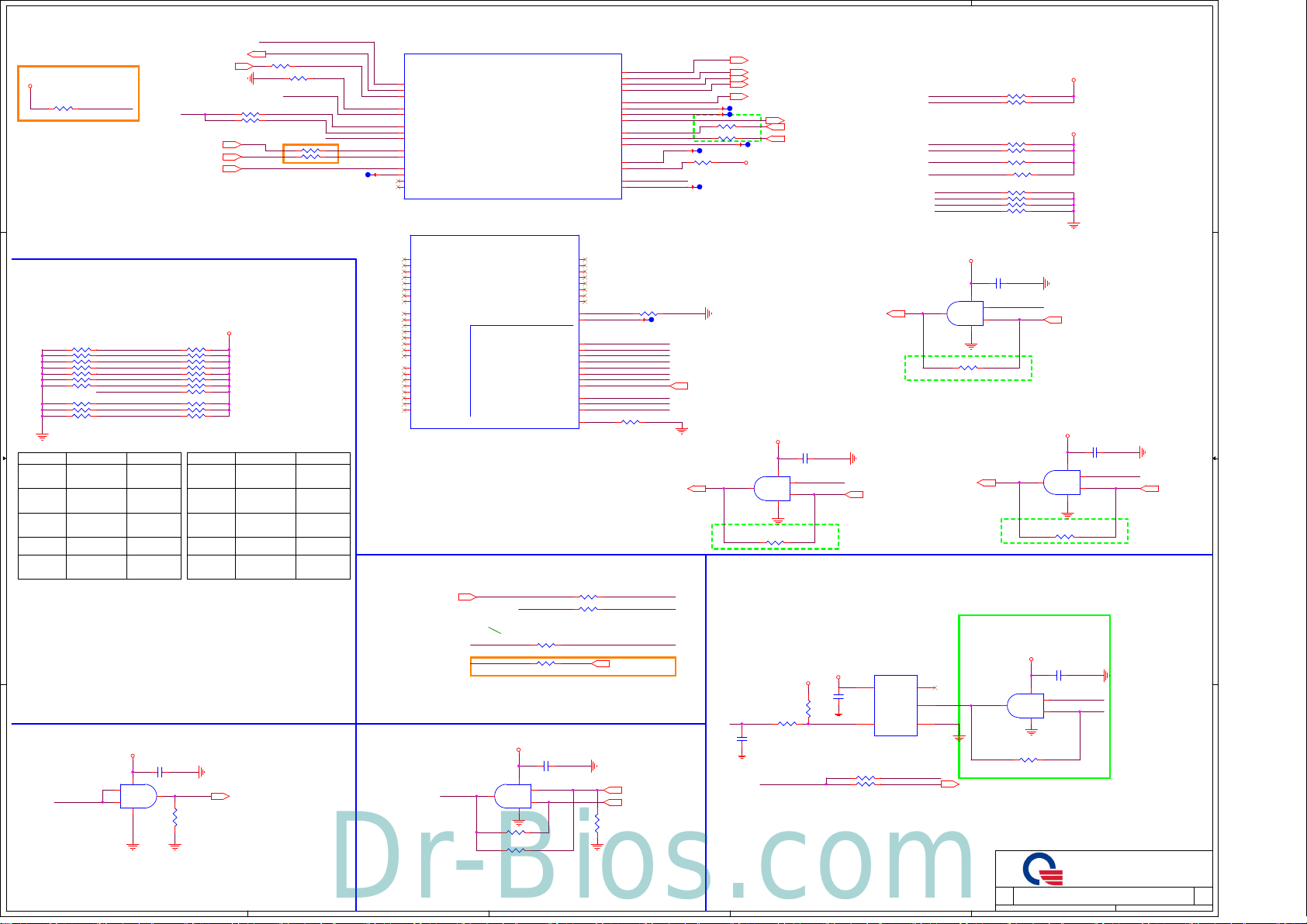

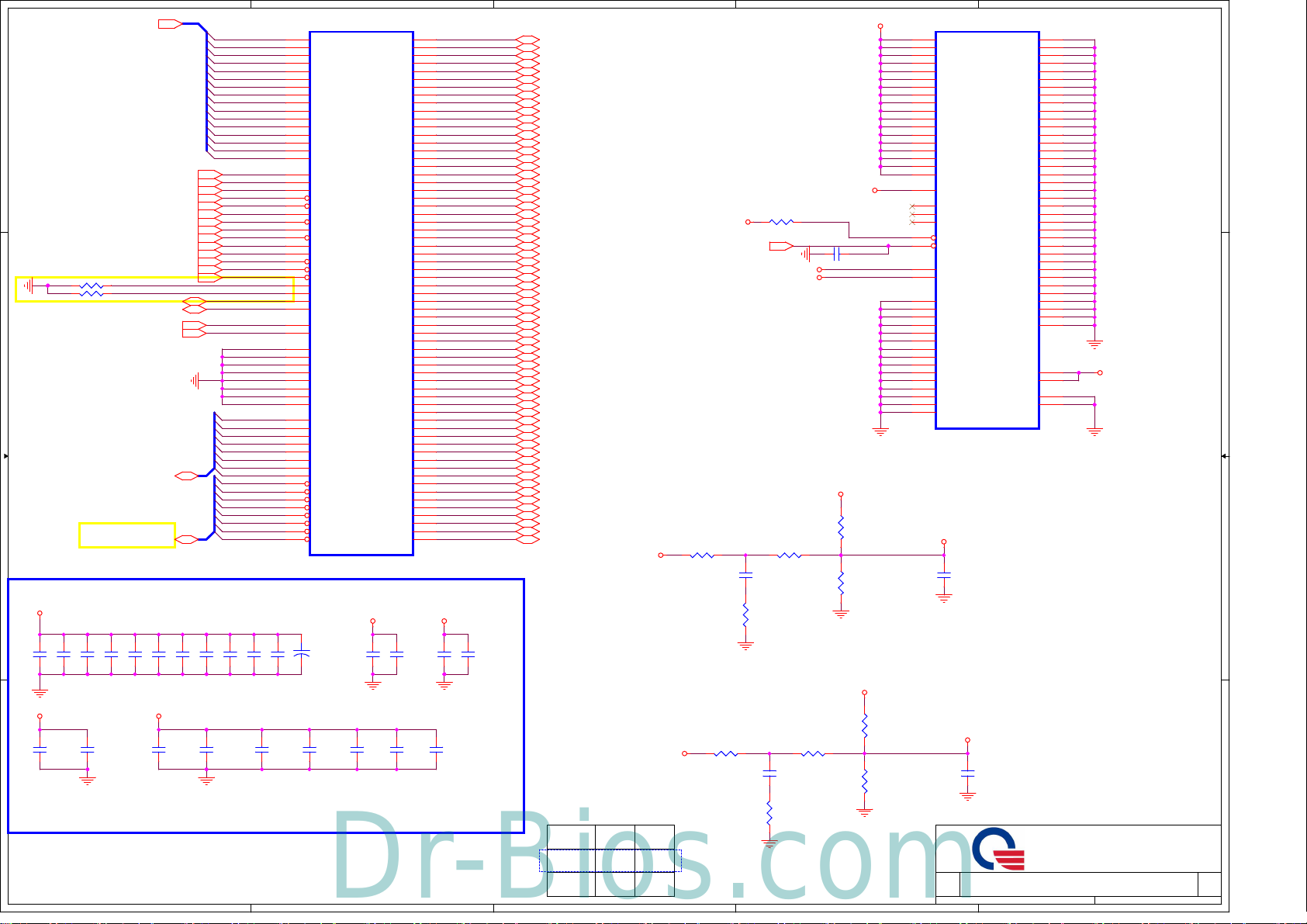

SKL ULT (SIDEBAND ) GPIO

H_PECI (50ohm)

Route on microstrip only

Spacing >18 mils

Trace Length: 0.4~6.125 iches

H_PWRGOOD (50ohm)

Touch PAD

Touch Screen

R196*IV@10K_4

R256*100K_4

R199*10K_4

UMA boot

GPU boot

+3V

Trace Length: 1~11.25 inches

UART2 for RMT

HDA

PCH_AZ_CODEC_SYNC(24)

PCH_AZ_CODEC_BITCLK(24)

PCH_AZ_CODEC_SDOUT(24)

PCH_AZ_CODEC_SDIN0(24)

PCH_AZ_CODEC_RST#(24)

Reserve connect to DMI C (acer request 1/14)

SPKR

R624 *20K_4

D D

+3V_S5

I2C0_SDA

R1672.2K_4

I2C0_SCL

R1662.2K_4

I2C1_SDA

R165*2.2K_4

I2C1_SCL

R169*2.2K_4

PU 2.2K for touch pad I2C bus(400 KHz)

+3V

+3V

DGPU_PW_CTRL#

C C

high

low

DGPU_PW_CTRL#(2)

R127 EV@100K_4

GPU Control PU/PD

R220*EV@10K_4

R257*10K_4

R204*10K_4

20131015 For GC6 NV DG GC6_FB_EN PD.1A-1

R208 10K_4

UMA Only

GPU power is control by PCH

GPIO (Discrete, SG or Optimize)

DGPU_PW_CTRL#

DGPU_PWROK

VGPU_EN

DGPU_PWR_EN

GC6_FB_EN

DGPU_HOLD_RST#

R115 IV@1K_4

DGPU_PWROK PD on GPU side

Setup

DGPU_PW_CTRL#

UMA Only

SG/Optimise

VGA H/W

Menu

Signal

UMA

1

0

Hidden

Hidden

GPU

545659-103

Add GPU Power Con trol Siganls

Touch PAD

Touch Screen

DMIC_CLK0_L(24)

DMIC_DATA0_L(24)

DGPU_HOLD_RST#(14)

DGPU_PWR_EN(42)

DGPU_PWROK(16)

GC6_FB_EN(15,17)

DGPU_EVENT#(17)

C739

*10p/50V_4

ODD_PRSNT#(25)

VGPU_EN(41)

ACCEL_INTA(27)

TP_INT_PCH(21)

I2C0_SDA(27)

I2C0_SCL(27)

I2C1_SDA(21)

I2C1_SCL(21)

C742 *10p/50V_4

R667 33_4

R644 33_4

R645 33_4

R660 33_4R110 *10K_4

R769 *33_4

R770 *33_4

Strapping

SPKR(24)

TPD_INT#_D

UART2_RXD

UART2_TXD

UART2_RTS#

UART2_CTS#

I2C0_SDA

I2C0_SCL

I2C1_SDA

I2C1_SCL

HDA_SYNC_R

HDA_BCLK_R

HDA_SDO_R

HDA_RST#_R

DMIC_CLK0_R

DMIC_DATA0_R

SPKR

GSPI0_MOSI

GSPI1_MOSI

Skylake-U Strapping Table

Pin Name Strap description

GPP_B14 (SPKR)

B B

GPP_B18

(GSPI0_MOSI)

GPP_C2

(SMBALERT#)

GPP_B22

(GSPI1_MOSI)

GPP_C5

(SML0ALERT#)

SPI0_MOSI

SPI0_MISO

GPP_B23

(SML1ALERT#

/PCHHOT#)

SPI0_IO2

A A

SPI0_IO3

HDA_SDO /

I2S_TXD0

GPP_E19

(DDPB_CTRLDATA)

GPP_E21

(DDPC_CTRLDATA)

Top-Block Swap override PCH_PWROK

No reboot PCH_PWROK

TLS Confidentiality

Boot BIOS Strap Bit (BBS)

eSPI or LPC

Reserved

Reserved

Reserved

Reserved

Reserved

Flash Descriptor Security

Override / Intel ME Debug Mode

Display Port B Det ected

Display Port C Detec ted

5

Sampled

RSMRST#

PCH_PWROK

RSMRST#

RSMRST#

RSMRST#

RSMRST#

RSMRST#

RSMRST#

PCH_PWROK

PCH_PWROK

PCH_PWROK

Configuration note

0 = *Disable T op Swap (iPD 20K)

1 = Enable Top Swap Mode

0 = *Disable No Reboot (iPD 20K)

1 = Enable No Reboot Mode

0 = *Disable I ntel ME Cryp to TLS(iPD 20K)

1 = Enable Int el ME Cryp to T LS

0 = *SPI (iP D 20K)

1 = LPC

0 = *LPC is sel ected for EC (iPD 20K)

1 = eSPI select ed for EC

+3V

+3V

+3V_S5

+3V

+3V_S5

(iPU 15 ~ 40K)

(iPU 15 ~ 40K)

(iPD 20K)

(iPU 15 ~ 40K)

(iPU 15 ~ 40K)

0 = *Enable secu rity in the Flash

Description (iPD 20K)

1 = Disable Fl ash Descriptor Securi ty (Override)

0 = *Port B i s not detected ( iPD 20K)

1 =Port B i s detected

0 = *Port C i s not detected ( iPD 20K)

1 =Port C is det ected

4

R625 *1K_4

R619 *1K_4

R160 *10K_4

R207 *1K_4

change location to near CPU to prevent impact HDA_SDO signal

HDA_SDO_R

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

AH10

AH11

AH12

AF11

AF12

BA22

AY22

BB22

BA21

AY21

AW22

J5

AY20

AW20

AK7

AK6

AK9

AK10

H5

D7

D8

C8

AW5

R586 *1K_4

R737 1K_4

U35F

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL_ULT/BGA

REV = 1

U35G

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFR M

I2S1_TX D

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

+3V_S5

GPP_B14/SPKR

SKL_ULT/BGA

REV = 1

SPKR

GSPI0_MOSI

GSPI1_MOSI

3

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+3V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

ME_WR# (29)

SKL_ULT

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

SKL_ULT

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

7 OF 20

SMBALERT# (7)

SML0ALERT# (7)

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+1.8V_S5

+1.8V_S5

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

6 OF 20

SDIO/SDXC

SD GPI

SD GPI

SD GPI

SD GPI

SD GPI

SD GPI

SD GPI

SD GPI

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

+1.8V_S5

?

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

GPP_D9

GPP_D10

GPP_D11

GPP_D12

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

?

R174200/F_4

Touchpad INT

2

Reserve UART FFC conn ector for Win 7 debug

UART2_RXD

R275 *49.9K/F_4

UART2_TXD

R280 *49.9K/F_4

UART2_RTS#

R283 *49.9K/F_4

UART2_CTS#

R290 *49.9K/F_4

+5V

CN3

UART2_RXD

UART2_TXD

UART2_RTS#

UART2_CTS#

TPD_INT#_D

S5 S5

TPD_INT#(27,29)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

1

2

3

7

4 8

5

6

*UART Function

+3V_S5

R177TDI@100K_4

+3V

2

1

Skylake 6/7 (PEG/DMI/FDI)

Skylake 6/7 (PEG/DMI/FDI)

Skylake 6/7 (PEG/DMI/FDI)

3

Q20

TDI@2N7002K

R164 *0_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

!7

+3V_S5

TPD_INT#_D

ZRW

ZRW

ZRW

448

448

448

3A

3A

3A

5

Dr-Bios.com

Backside cap

C184

1U/6.3V_2

C243

22u/6.3V_6

C233

22u/6.3V_6

C226

22u/6.3V_6

C203

22u/6.3V_6

C219

22u/6.3V_6

C224

22u/6.3V_6

C236

22u/6.3V_6

Backside cap

C214

C245

C676

1U/6.3V_2

1U/6.3V_2

D D

C282

C272

C273

22u/6.3V_6

22u/6.3V_6

22u/6.3V_6

10u/6.3V_4

C289

22u/6.3V_6

10u/6.3V_4

Backside cap

C259

10u/6.3V_4

C189

1U/6.3V_2

C647

10u/6.3V_4

C252

1U/6.3V_2

C651

10u/6.3V_4

Backside cap

C212

C196

1U/6.3V_2

1U/6.3V_2

C181

C228

1U/6.3V_2

1U/6.3V_2

+VCCEOPIO

C708

GT3@10u/6.3V_4

+1.8V_PRIM

GT3@10u/6.3V_4

C C

B B

A A

C687

R565

C709

GT3@10u/6.3V_4

Backside cap

C686

GT3@10u/6.3V_4

GT3@0_6

5

Backside cap

+1.8V_PRIM+1.8V_S5

C201

1U/6.3V_2

Backside cap

C269

1U/6.3V_2

For 2+3e CPU

For 2+3e CPU

C186

10u/6.3V_4

C197

1U/6.3V_2

C262

1U/6.3V_2

C237

1U/6.3V_2

C185

10u/6.3V_4

C194

1U/6.3V_2

C215

1U/6.3V_2

C209

1U/6.3V_2

C682

GT3@10u/6.3V_4

C155

10u/6.3V_4

C193

1U/6.3V_2

+1.35VSUS

Backside cap

+1V_SUS

C227

C246

1U/6.3V_2

1U/6.3V_2

C285

1U/6.3V_2

Backside cap

C688

GT3@1U/6.3V_2

Backside cap

C158

C232

10u/6.3V_4

10u/6.3V_4

Backside cap

C241

C188

1U/6.3V_2

1U/6.3V_2

C318

10u/6.3V_4

C326

10u/6.3V_4

R194 *short_4

1 2

Rev:F change to Shortpad

+VCCIO

Rev:F change to Shortpad

+1V_SUS

Rev:F change to Shortpad

4

C255

C251

22u/6.3V_6

22u/6.3V_6

C657

C257

10u/6.3V_4

10u/6.3V_4

C235

C222

1U/6.3V_2

1U/6.3V_2

C200

1U/6.3V_2

100 ohm near CPU

1.0V_CPU 3A

C681

C684

GT3@1U/6.3V_2

GT3@1U/6.3V_2

For 2+3e CPU

C218

10u/6.3V_4

C240

1U/6.3V_2

Backside cap

C313

C328

1U/6.3V_2

10u/6.3V_4

Primary side cap

C323

10u/6.3V_4

+VDDQC

C299

1U/6.3V_2

R550 *shor t_6

Primary side cap

R135 *shor t_6

R112 *shor t_6

4

+VCCCORE

+1.8V_PRIM

+VCCOPC

+VCCOPC_SRC(33)

681_AGND(33)

For 2+3e CPU

+VCCOPC_SRC

681_AGND

+VCCOPC

C685

C683

GT3@1U/6.3V_2

GT3@1U/6.3V_2

C161

C151

10u/6.3V_4

10u/6.3V_4

C198

C239

1U/6.3V_2

1U/6.3V_2

100 ohm Near CPU

VCCGT_SEN SE(36)

VSSGT_SE NSE(36)

C311

C308

1U/6.3V_2

1U/6.3V_2

C325

C327

10u/6.3V_4

10u/6.3V_4

+1V_VCCST

C286

10u/6.3V_4

C677

1U/6.3V_4

Backside cap

Primary side cap

+VCCOPC

For 2+3e CPU

+1.8V_PRIM

C689

GT3@1U/6.3V_2

+VCCGT

C223

10u/6.3V_4

C204

1U/6.3V_2

C205

1U/6.3V_2

R155

100/F_4

R161

100/F_4

C312

1U/6.3V_2

+VCCSTG

TP12

TP20

R172 GT3@100/F_4

R634 GT3@0_4

R636 GT3@0_4

R176 GT3@100/F_4

+VCCEOPIO

R633 GT3@0_4

R632 GT3@0_4

C148

10u/6.3V_4

C206

1U/6.3V_2

C195

1U/6.3V_2

+VCCGT

+1.35VSUS

C176

1U/6.3V_4

+VCCPLL

C172

1U/6.3V_4

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

A48

A53

A58

A62

A66

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

REV = 1

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

U35L

VCC_A30

S0

VCC_A34

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

S0

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

SKL_ULT/BGA

REV = 1

SKL_ULT

U35M

CPU POWER 2 OF 4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

S0

VCCGT

0.55~1.5V

VCCGT

VCCGT

VCCGT

VCCGT

2+3e peak 6A

VCCGT

2+3e TPY 4A

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

SKL_ULT/BGA

U35N

SKL_ULT

CPU POWER 3 OF 4

S3

DDR3L

VDDQ_AU23

VDDQ_AU28

1.35V

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

S3

1.0V

VCCSTG_A22

S0

VCCPLL_OC

S0

1.0V

VCCPLL_K20

VCCPLL_K21

S3

1.0V

SKL_ULT/BGA

3

?

SKL_ULT

CPU POWER 1 OF 4

VCC

0.55V~1.5V

2+2 peak 24A

2+2 TPY 17A

2+3e peak 24A

2+3e TPY 17A

1.0V

S0

Sx

1.8V

GT3 CPU

1.0V

?

VCCGT

S0

0.55~1.5V

2+2 peak 31A

2+2 TPY 15A

2+3e peak 56A

2+3e TPY 17A

VCCGTX

2+2 X

13 OF 20

?

S0

0.85V/0.95V

2A

S0

1.15V

2+2 peak 5A

2+2 TPY 4A

2+3e peak 5.1A

2+3e TPY 5A

120mA

40mA

1.0V

260mA

120mA

14 OF 20

3

3A

50mA

3A

12 OF 20

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

VCCIO

3.0A

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

REV = 1

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

?

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

?

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

?

+VCCGT

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

R109 100/F_4

R122 100/F_4

100 ohm near CPU

+VCCCORE

C174

1U/6.3V_4

C199

47u/6.3V_8

C693

22u/6.3V_6

C692

22u/6.3V_6

+VCCGT

C303

GT3@22u/6.3V_6

C291

GT3@10u/6.3V_4

TP86

TP87

TP17

TP14

VSASS_SEN SE (36)

VSA_SENSE (36)

+VCCSA

C666

47u/6.3V_8

C679

10u/6.3V_4C258

R96 100/ F_4

R98 100/ F_4

+VCCSTG

C190

47u/6.3V_8

C705

22u/6.3V_6

C704

22u/6.3V_6

C310

GT3@22u/6.3V_6

C279

GT3@10u/6.3V_4

+VCCIO

+VCCSA

2

Primary side cap

C645

C144

47u/6.3V_8

47u/6.3V_8

Primary side cap

C667

C674

10u/6.3V_4

10u/6.3V_4

+VCCCORE

100 ohm Near CPU

VCORE_SE NSE (36)

VCORESS_ SENSE (36)

H_CPU_SVIDART#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

Primary side cap

C702

47u/6.3V_8

Primary side cap

C706

C178

22u/6.3V_6

22u/6.3V_6

Primary side cap

C202

C694

47u/6.3V_6

22u/6.3V_6

E3A C202 change to 47u/6.3v_6

Primary side cap

C277

C302

22u/6.3V_6

GT3@22u/6.3V_6

REV:F Stuff C277,C274,C275

For 2+3e CPU

Backside cap

C324

C281

GT3@10u/6.3V_4

GT3@10u/6.3V_4

Backside cap

C283

C284

10u/6.3V_4

10u/6.3V_4

Primary side cap

C701

C710

1U/6.3V_4

1U/6.3V_4

Backside cap

C254

C238

10u/6.3V_4

10u/6.3V_4

Backside cap

C207

C278

1U/6.3V_2

1U/6.3V_2

Primary side cap

C114

C643

10u/6.3V_4

10u/6.3V_4

2

C650

47u/6.3V_8

C664

10u/6.3V_4

C171

22u/6.3V_6

C691

22u/6.3V_6

C307

GT3@22u/6.3V_6

C316

GT3@10u/6.3V_4

C266

1U/6.3V_2

C700

1U/6.3V_4

C247

10u/6.3V_4

C216

1U/6.3V_2

C641

10u/6.3V_4

C690

47u/6.3V_8

C659

47u/6.3V_8

C673

10u/6.3V_4

C707

22u/6.3V_6

C703

22u/6.3V_6

C274

22u/6.3V_6

C280

GT3@10u/6.3V_4

Imax 3(A)

C297

1U/6.3V_2

C711

1U/6.3V_4

C229

10u/6.3V_4

C242

1U/6.3V_2

C165

10u/6.3V_4

C150

47u/6.3V_8

C663

C675

10u/6.3V_4

10u/6.3V_4

+1V_VCCST

SVID

R138

100/F_4

H_CPU_SVIDDAT

Place PU resistor

close to CPU

Place PU resistor

close to CPU

H_CPU_SVIDART#

R552 220_4

H_CPU_SVIDCLK

C697

C248

47u/6.3V_8

47u/6.3V_8

C210

47u/6.3V_6

E3A C210 change to 47u/6.3v_6

C275

C276

22u/6.3V_6

GT3@22u/6.3V_6

C317

C290

GT3@10u/6.3V_4

GT3@10u/6.3V_4

C264

C298

1U/6.3V_2

1U/6.3V_2

C263

C221

10u/6.3V_4

10u/6.3V_4

C267

C260

1U/6.3V_2

1U/6.3V_2

C642

C157

10u/6.3V_4

10u/6.3V_4

1

C678

10u/6.3V_4

Layout note: need routing together

and ALERT need between CLK and DATA.

C814

1000P/50V_4

+1V_VCCST

C696

47u/6.3V_8

C288

10u/6.3V_4

C249

1U/6.3V_2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

C816

C815

*1000P/50V_4

*1000P/50V_4

REV:F add 1000p

R134

54.9/F_4

Skylake 12/13/1 4 (POWER)

Skylake 12/13/1 4 (POWER)

Skylake 12/13/1 4 (POWER)

Monday , J uly 20, 201 5

Monday , J uly 20, 201 5

Monday , J uly 20, 201 5

C818

C817

*1000P/50V_4

*1000P/50V_4

H_CPU_SVIDDAT (36)

VR_SVID_ALE RT#_VCOR E (36)

H_CPU_SVIDCLK (36)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

!8

C819

*1000P/50V_4

ZRW

ZRW

ZRW

548

548

548

3A

3A

3A

5

Dr-Bios.com

4

3

2

1

Skylake ULT (GPU, SATA , ODD, CLK ,USB2&3)

?

U35H

PCIE/USB3/SATA

PEG_RX#0(14)

PEG_RX0(14)

D D

dGPU PEG*4

LAN

WIFI

C C

B B

PEG_TX#0(14)

PEG_TX0(14)

PEG_RX#1(14)

PEG_RX1(14)

PEG_TX#1(14)

PEG_TX1(14)

PEG_RX#2(14)

PEG_RX2(14)

PEG_TX#2(14)

PEG_TX2(14)

PEG_RX#3(14)

PEG_RX3(14)

PEG_TX#3(14)

PEG_TX3(14)

PCIE_RX5-_LAN(23)

PCIE_RX5+_LAN(23)

PCIE_TX5-_LAN(23)

PCIE_TX5+_LAN(23)

PCIE_RX6-_WLAN(26)

PCIE_RX6+_WLAN(26)

PCIE_TX6-_WLAN(26)

PCIE_TX6+_WLAN(26)

CLK_PCIE_VGA#(14)

CLK_PCIE_VGA(14)

CLK_PEGA_REQ#(14)

N16S VGALANWLAN

CLK_PCIE_LANN(23)

CLK_PCIE_LANP(23)

CLK_PCIE_LAN_REQ#(23)

CLK_PCIE_WLANN(26)

CLK_PCIE_WLANP(26)

PCIE_CLKREQ_WLAN#(26)

HDD

ODD

C653 EV@0.22u/10V_4

C652 EV@0.22u/10V_4

C656 EV@0.22u/10V_4

C655 EV@0.22u/10V_4

C661 EV@0.22u/10V_4

C662 EV@0.22u/10V_4

C654 EV@0.22u/10V_4

C660 EV@0.22u/10V_4

C668 0.1u/16V_4

C669 0.1u/16V_4

C648 0.1u/16V_4

C649 0.1u/16V_4

SATA_RXN0(25)

SATA_RXP0(25)

SATA_TXN0(25)

SATA_TXP0(25)

SATA_RXN1(25)

SATA_RXP1(25)

SATA_TXN1(25)

SATA_TXP1(25)

R562 100/F_4

TP91

TP92

R235

*short_4

TP22

TP25

TP73

R229

*short_4

R224

*short_4

XDP_PRDY#

XDP_PREQ#

PIRQA#

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

Rev:D change to shortpad

A A

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

R234 10K_4

R215 10K_4

R227 10K_4

R618 10K_4

R228 10K_4

R223 10K_4

+3V

C_PEG_TX#0

C_PEG_TX0

C_PEG_TX#1

C_PEG_TX1

C_PEG_TX#2

C_PEG_TX2

C_PEG_TX#3

C_PEG_TX3

PCIE_TX5PCIE_TX5+

PCIE_TX6PCIE_TX6+

PCIE_RCOMPN

PCIE_RCOMPP

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_T XN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_T XN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_T XN

A21

PCIE7_TXP/SATA0_T XP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_T XN

C21

PCIE8_TXP/SATA1A_T XP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_T XN

C24

PCIE11_TXP/SATA1B_T XP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_T XN

B25

PCIE12_TXP/SATA2_T XP

SKL_ULT/BGA

REV = 1

U35J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL_ULT/BGA

REV = 1

+3V_S5

5

4

SKL_ULT

SSIC / USB3

USB2

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

+3V_S5

GPP_E2/SATAXPCIE2/SATAGP2

+3V_S5

+3V_S5

8 OF 20

?

SKL_ULT

CLOCK SIGNALS

+3V_S5

CLKOUT_ITPXDP_N

+3V_S5

+3V_S5

+3V_S5

+3V_S5

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XCLK_BIASREF

+3V_S5

+3V_S5

10 OF 20

Rev:D add for EC reset RTC

EC_RTCRST(29)

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2_COMP

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

?

F43

E43

BA17

E37

XTAL24_IN

E35

XTAL24_OUT

E42

AM18

RTCX1

AM20

RTCX2

AN18

SRTCRST#

AM16

RTCRST#

?

2

R786

100K_4

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

USB2N_1

AB10

USB2P_1

AD6

USB2N_2

AD7

USB2P_2

AH3

USB2N_3

AJ3

USB2P_3

AD9

USB2N_4

AD10

USB2P_4

AJ1

USB2N_5

AJ2

USB2P_5

AF6

USB2N_6

AF7

USB2P_6

AH1

USB2N_7

AH2

USB2P_7

AF8

USB2N_8

AF9

USB2P_8

AG1

USB2N_9

AG2

USB2P_9

AH7

USB2N_10

AH8

USB2P_10

AB6

AG3

USB2_ID

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

CLK_PCIE_XDPN

CLK_PCIE_XDPP

SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTC_X1

RTC_X2

SRTC_RST#

RTC_RST#

SRTC_RST#

3

PQ6059

*2N7002K

1

Rev:E Reserve o nly Rev:E Reser ve only

USB3_RXN0 (28)

USB3_RXP0 (28)

USB3_TXN0 (28)

USB3_TXP0 (28)

USB3_RXN1 (28)

USB3_RXP1 (28)

USB3_TXN1 (28)

USB3_TXP1 (28)

USBP0- (28)

USBP0+ (28)

USBP1- (28)

USBP1+ (28)

USBP3- (28)

USBP3+ (28)

USBP4- (26)

USBP4+ (26)

USBP5- (21)

USBP5+ (21)

USBP6- (21)

USBP6+ (21)

USBP7- (28)

USBP7+ (28)

USBCOMP

R178 113/F_4

USB2_ID

R587 1K_4

R778 1K_4

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

SATA_DEVSLP0

SATA_DEVSLP1

SATA_DEVSLP2

SATAGP0

SATAGP1

SATAGP2

TP93

TP94

SUSCLK (26)

R512 2.7K/F_4

R768 *60.4/F_4

RTC_RST# (11)

1V power plane

0.71 checklist p14

3

1A-1

USB_OC0# (28)

USB_OC1# (28)

USB_OC2# (28)

DEVSLP0 (25)

EC_RTCRST

MB USB3.0 CN16 ( Charger IC ) Down

MB USB3.0 CN13 -> Up

MB USB3.0 CN16 ( Charger IC ) Down

MB USB3.0 CN13 -> Up

DB USB2.0

BT

Touch Screen

CCD

Card reader

USBCOMP

Impedance = 50 ohm

Trace length < 500 m ils

Trace spacing = 15 m ils

MB U3

MB U3

DB U2

+1V_S5

Reserve PD 60 ohm in E42

ball for Cannonlake U

RTC_RST#

3

2

PQ6060

*2N7002K

1

Add SSD ID 1/1 4

Hight is SSD , Low is ODD

SSD_ID(25)

Skylake-U userd 24 MHz (50 Ohm ESR) XTAL

XTAL24_IN

XTAL24_OUT

Note: Change Y4 to 38.4 MHz(ESR 30 ohm) for Cannonlake U

RTC Clock 32.768KHz (RTC)

Trace length < 1000 mils

RTC Circuitry (RTC)

+3VPCU

On SKL voltage at VCCRTC does not exceed 3.2V

R304

1.5K/F_4

VCCRTC_2

R301

45.3K/F_4

2013/10/16 Chage +3V_RTC_0 to VCCTC_2.

1A-2

1. AHL03003057 DBV CR2032

2. AHL03003003 VDE CR2032

2

PCH PU/PD

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

SATA_DEVSLP0

SATA_DEVSLP1

SATA_DEVSLP2

PIRQA#

SATAGP1

SATAGP2

R568 10K_4

C351 6.8p/50V_4

C362 6.8p/50V_4

1B-1

R308 1K_4

12

BT1

BAT_CONN

SATAGP0

C665 10P/50V_4

4

3

Y4

R536

24MHz

1M_4

1

2

C658 10P/50V_4

12

Y2

32.768KHZ

D7

+3V_RTC_2

+3V_RTC_1

+3V_RTC_[0:2]

Trace width = 20 m ils

BAT54C

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

+3V_S5

R541 10K_4

R540 10K_4

R543 10K_4

R542 10K_4

R573 *10K_4

R574 *10K_4

R575 *10K_4

R631 *10K_4

R569 *10K_4

R566 *10K_4

+3V_S5

R570 100K_4

CH01006JB08 -> 10p

CH01506JB06 -> 15p

CH-6806TB01 -> 6.8p

RTC_X1

R255

10M_4

RTC_X2

+3V_RTC

+3V_RTC

Trace width = 30 m ils

R299

20K/F_4

R300

20K/F_4

C381

1u/6.3V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Skylake 9/10 (PEG/USB/CLK)

Skylake 9/10 (PEG/USB/CLK)

Skylake 9/10 (PEG/USB/CLK)

!9

+3V

24MHz: BG624000078

38.4MHz : ?

BG332768453 - > SEG

BG332768104 - > TXC

12

C380

1u/6.3V_4

C382

1u/6.3V_4

ZRW

ZRW

ZRW

1

RTC_RST#

J1

*JUMP

SRTC_RST#

3A

3A

648

648

648

3A

5

Dr-Bios.com

4

3

2

1

?

U35E

SPI - FLASH

EC_RCIN#

PCH_SPI_CS0#

PCH_SPI_CS1#

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

C LINK

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

AW13

GPP_A0/RCIN#

AY11

GPP_A6/SERIRQ

SKL_ULT/BGA

REV = 1

PCH_SPI_SO

PCH_SPI_SO_EC

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

only 0ohm option

1A-13

+3V_S5

+3V_S5

+3V_PCH_ME

PCH_SPI_CLK

PCH_SPI_SO

PCH_SPI_SI

PCH_SPI_IO2

D D

For M.2 wifi module must

Rev:D change to shortpad

C C

SPI ROM

Skylake

3.3V

B B

Vender Size Quanta P/N Vender P/N

8M

8M

PCH_SPI_CLK_EC(29)

PCH_SPI_SI_EC(29)

PCH_SPI_SO_EC(29)

SPI_CS0#_UR_ME(29)

SIO_RCIN#(29)

IRQ_S ERIRQ(25,29)

AKE3EFP0N07

AKE2EZN0Q00

+3V_PCH_ME

PCH_SPI_IO3

PCH_SPI_CS0#

PCH_SPI_CS1# SML0ALERT#

CL_CLK

TP68

CL_DAT

TP66

CL_RST#

TP67

R652 *short_4

IRQ_S ERIRQ

W25Q64FVSSIQWND

GD25B64CSIGRGGD

R689 *4M@33_4

R641 *4M@33_4

R594 *4M@33_4

R602 8M@0_4

R603 *4M@0_4

R591 10K_4

SPI_CS0#_UR_ME

SKL_ULT

+3V_S5

LPC

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

5 OF 20

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

PCH SPI ROM(8M+4M)

15ohm CS01502JB12

33ohm CS03302JB29

PCH_SPI_CS0#

R588 8M@15_4

3.3K is original and for no

support fast read function

PCH_SPI_CS1#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

C745 *22p/50V_4

R649 1K_4

R669 *4M@33_4

R658 *4M@33_4

R604 *4M@33_4

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

+3V_PCH_ME

SPI_SO_8M

SMBUS, SMLINK

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

GPP_A14/SUS_STAT#/ ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESP I_CLK

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI _IO0

GPP_A2/LAD1/ESPI _IO1

GPP_A3/LAD2/ESPI _IO2

GPP_A4/LAD3/ESPI _IO3

GPP_A5/LFRAME#/ESPI _CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

Rev:D change to shortpad

R700 *short_6

+3V_S5

U41

1

CS#

2

IO3/HOLD#

IO1/DO

3

4

W25Q64FV -- 8MB

SPI_WP_IO2_ME

PCH_SPI_IO2

PCH_SPI_IO3

R597 *1K_4

IO2/WP#

GND

IO0/DI

PCH_SPI_CLK_EC

PCH_SPI_SI_EC

R596 *4M@33_4

R589 8M4M@15_4

R238 *4M@33_4

R239 8M4M@15_4

U39

1

CE#

6

SCK

5

SI

2

SO

3

WP#

*4M@ROM-4M_EC

SPI_WP_IO2_EC

R7

PCH_MBCLK0_R

R8

PCH_MBDAT0_R

R10

SMBALERT#

R9

VGA_MBC LK

W2

VGA_MBD ATA

W1

W3

SMB_ME1_CLK

V3

SMB_ME1_DAT

AM7

SML1ALERT#

eSPI change to 15 ohm

AY13

R659 *short_4

BA13

R640 *short_4

BB13

R653 *short_4

AY12

R668 *short_4

BA12

BA11

R748 *0_4

C806 0.1u/16V_4

eSPI change to 15 ohm

AW9

R623 22/J_4

AY9

AW11

R626 22/J_4

R627 22/J_4

CLKRUN#

2/10 add C806 for EMI request ,

?

R748 no stuiff from EC site

move at CPU site

+3V_PCH_ME

8

VCC

7

SPI_HOLD_IO3_ME

6

SPI_CLK_8M

CLK

5

SPI_SI_8M

R687 8M@15_4

R654 8M@15_4

SPI_HOLD_IO3_ME

8

VDD

7

SPI_HOLD_IO3_EC

HOLD#

4

VSS

Rev:D change to shortpad

R698 1K_4R650 8M4M@15_4

R684 8M4M@15_4

R691 8M4M@15_4

SPI_WP_IO2_EC

SPI_WP_IO2_ME

SPI_HOLD_IO3_EC

R232 *1K_4

C741

*4M@0.1u/16V_4

Strapping

SMBALERT# (4)

SML0ALERT# (4)

SMB1ALERT# (27)

ckl v0.71 p.24

LPC_LAD0 (25,26,29)

LPC_LAD1 (25,26,29)

LPC_LAD2 (25,26,29)

LPC_LAD3 (25,26,29)

LPC_LFRAME# (25,26,29)

ESPI_RST# (29)

CLK_PCI_EC (29)

PCLK_TPM (25)

CLK_PCI_LPC (26)

CLKRUN# (25,29)

+3V_PCH_ME

C754 0.1u/16V_4

PCH_SPI_CLK

PCH_SPI_SI

C747

*22p/50V_4

reserve for SPI fast read

+3V_PCH_ME

CLKRUN#

IRQ_S ERIRQ

EC_RCIN#

R630 8.2K/F_4

R629 10K_4

R639 10K_4

SMBus

PCH_MBCLK0_R

PCH_MBDAT0_R

VGA_MBD ATA

VGA_MBC LK

SML1ALERT#

Termination Resistor Requirement for PCH PCHHOT# Pin

Reserve PU 150K resister

+3V

S5 S0

SMBus(PCH)

PCH_MBDAT0_R

PCH_MBCLK0_R

PCH_XDP_WLAN/S5 DDR_TP/S0

R5782.2K_4

R5802.2K_4

R5852.2K_4

R5822.2K_4

R205*150K_4

D2B change to 2.2k

R576

2.2K_4

Q32

5

2

6

43

1

2N7002DW

SMBus(EC)

2ND_MBCLK(17,29)

2ND_MBDATA(17,29)

EC/S5

2ND_MBCLK

2ND_MBDATA

R171 *short_4

R175 *short_4

Rev:D change to shortpad

+3V

+3V_S5

+3V_S5

!:

R572

2.2K_4

CLK_SDATA (12,13,27)

CLK_SCLK (12,13,27)

SMB_ME1_CLK

SMB_ME1_DAT

1A-3 2013/10/16 Add U34 flash 4M ROM reserve for ZQ0D.

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

5

4

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

Monday, July 20, 2015

Date: Sheet of

3

2

Monday, July 20, 2015

PROJECT :

Skylake 5 (SATA/HDA/SPI)

Skylake 5 (SATA/HDA/SPI)

Skylake 5 (SATA/HDA/SPI)

ZRW

ZRW

ZRW

748

748

1

748

3A

3A

3A

5

Dr-Bios.com

4

3

2

1

PCI_PLTRST#

SYS_RESET#(11)

+VCCIO

11/12 Reserve PU 10K

R544 *10K_4

D D

Rev:D change to shortpad

PROC_PWRGD

Rev:D change to shortpad

Board ID

C1D

2

1

RAM_ID1

RAM_ID2

RAM_ID3

Board_ID0

Board_ID1

Board_ID2

Board_ID3

Board_ID4

Board_ID5

Board_ID6

Board_ID7

?@AB

IOACNon IOAC

G-sensor No G-sensor

TPM

touch panel

+3V

C332 0.1u/16V_4

U14

3 5

TC7SH08FU

<+'&%=>%!

R610 10K_4

R612 10K_4

R614 10K_4

R595 10K_4

R598 10K_4

R605 10K_4

R592 10K_4

R606 10K_4

R764 10K_4

R766 10K_4

VRAM 2GB VRAM 4GB

C C

<+'&%=>%"

<+'&%=>%#

<+'&%=>%$

<+'&%=>%7

B B

No TPM

No touch panel

PLTRST# Buffer

A A

PCI_PLTRST#

RSMRST#(29)

SYS_PWROK

R556 *short_4

R643 *0_4

PCH_SUSPWRACK_R(29)

PCH_SUSACK#(29)

PCIE_LAN_WAKE#(23,26)

+1.8V_S5

R611 *10K_4

R613 *10K_4

R615 *10K_4

R600 *10K_4

R599 *10K_4

R608 *10K_4

R590 *10K_4

R593 10K_4

R607 *10K_4

R765 *10K_4

R767 *10K_4

<+'&%=>%8

<+'&%=>%9

<+'&%=>%: Reserve

4

R214

100K_4

Realtek

Audio codec

(Default)

Reserved

(Default)

PLTRST# (14,23,25,26,29)

R655 *short_4

R554 10K_4

VCCST_PWRGD

R622 *0_4

R617 *0_4

SYS_RESET#

PCH_RSMRST#

PCIE_LAN_WAKE#

?@ABC1D

CPU DSP

ReserveReserved

PROC_PWRGD

SYS_PWROK_R

EC_PWROK_R

DPWROK_R PCH_ACPRESENT

PCH_SUSPWRACK

SUSACK#_R

TP84

For platforms not supporting Deep

Sx, connect directly to RSMRST#

U35K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWR GD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL_ULT/BGA

REV = 1

U35I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL_ULT/BGA

Power Sequence

PCH_PWROK(29)

SYSPWOK

SYSTEM POWER MANAGEMENT

I

I

REV = 1

SYS_PWROK

5

4

?

SKL_ULT

GPP_B12/SLP_S0#

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

SKL_ULT

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

Rev:D change to shortpad

DPWROK_R PCH_RSMRST#

DPWROK_R

U8

*TC7SH08FU

+3V_S5

+3V_S5

+3V_S5

+3V_S5

GPD9/SLP_WLAN#

+3V_S5

+3V_S5

GPD1/ACPRESENT

+3V_S5

+3V_S5

+3V_S5

+3V_S5

GPP_B11/EXT_PWR_GATE#

+3V_S5

+3V_S5

11 OF 20

?

+3V_S5

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

9 OF 20

EMMC

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC_RCOMP

?

GPP_B2/VRALERT#

Non Deep Sx

R647 *short_4

EC_PWROK SYS_PWROK_R

R131 *0_4

No Deep Sx

+3V_S5

4

3 5

R113 *0_4

R560 *short_4

Rev:D change to shortpad

R661 *short_4

R674 *0_4

C168 *0.1u/16V_4

2

EC_PWROK

1

GPD10/SLP_S5#

GPD3/PWRBTN#

GPD0/BATLOW#

Rev:D change to shortpad

GPD4/SLP_S3#

GPD5/SLP_S4#

SLP_SUS#

SLP_LAN#

GPD6/SLP_A#

GPP_A11/PME#

INTRUD ER#

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

INTRUDER#

AM10

MPHY_EXT_PWR

AM11

PCH_VRALERT#

?

R145 100/F_4

RAM_ID1

RAM_ID2

RAM_ID3

Board_ID0

Board_ID1

Board_ID2

Board_ID3

Board_ID4

Board_ID5

Board_ID6

Board_ID7

R616200/F_4

EC_PWROK_R

DPWROK_C (29)

EC_PWROK (29)

IMVP_PWRGD_3V (2)

R130

*10K_4

3

SUSB#