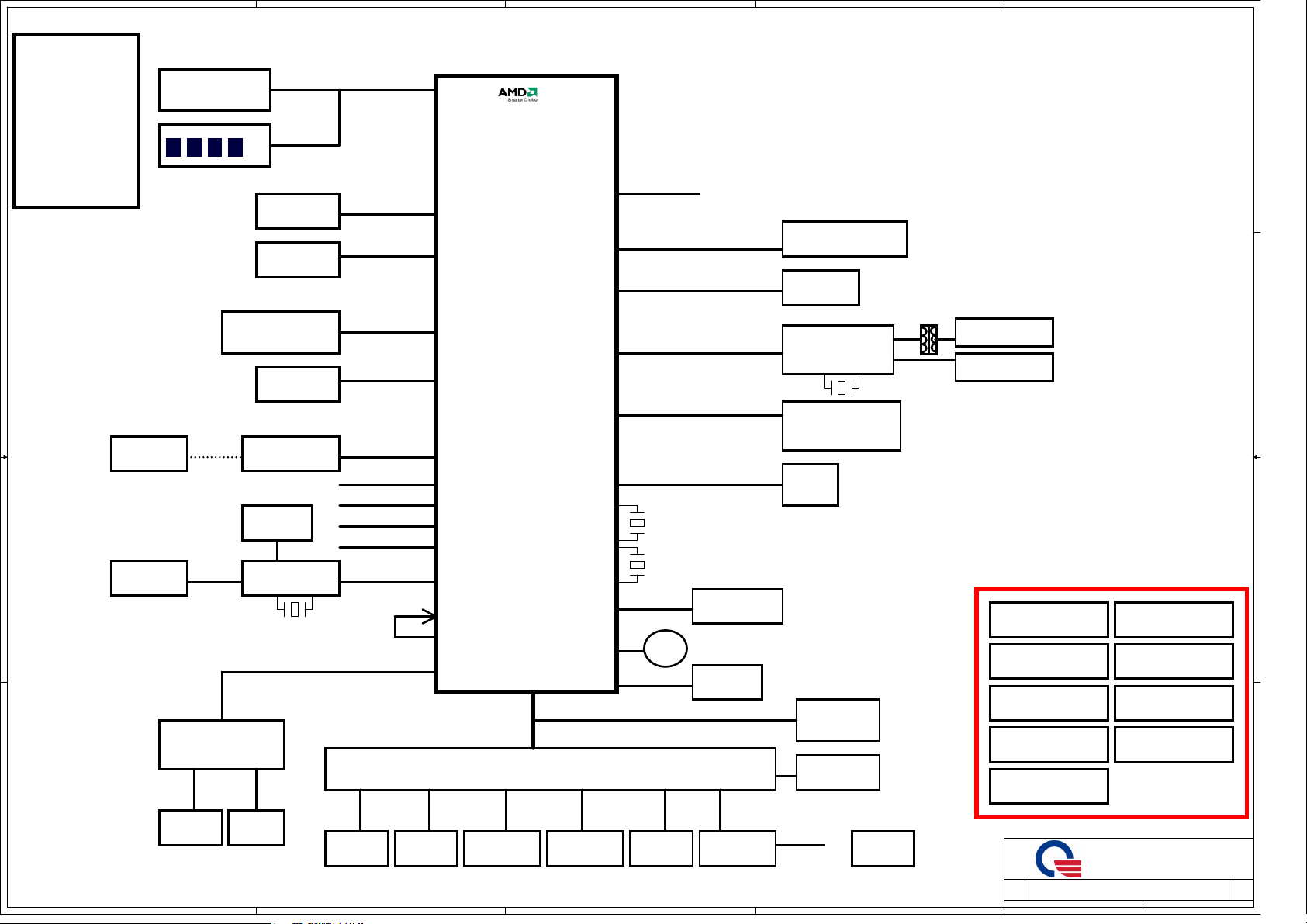

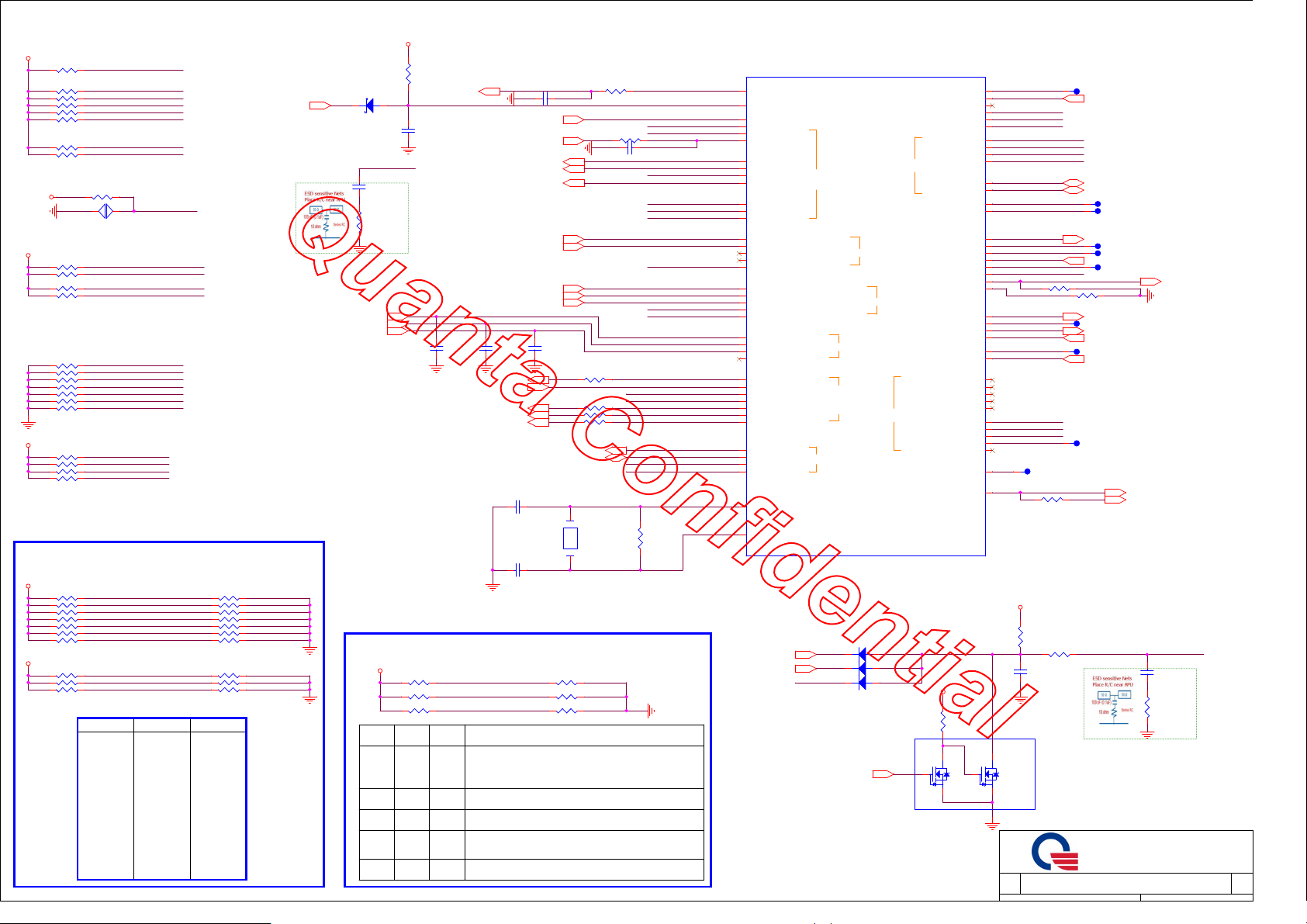

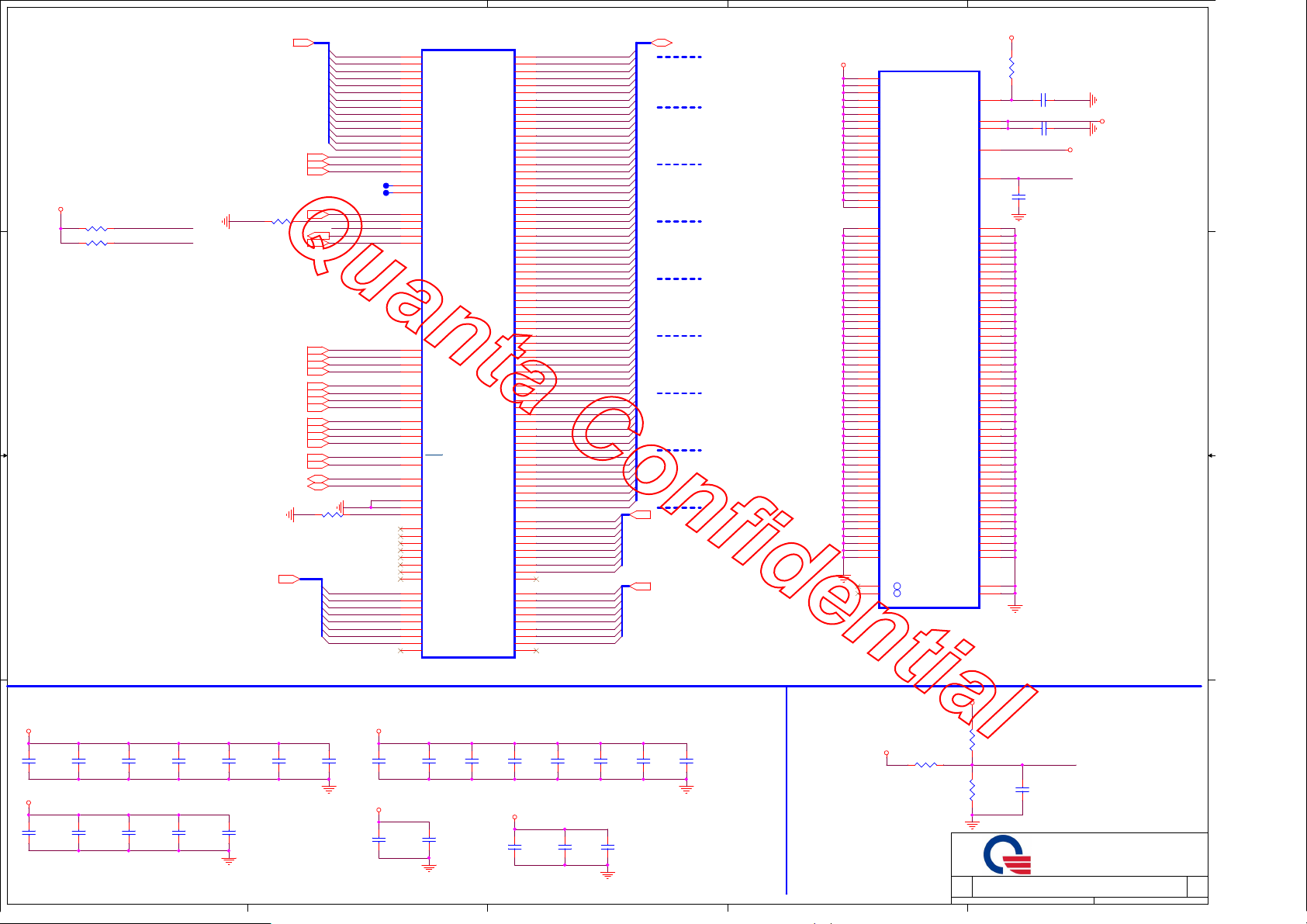

Acer ASPIRE A315 Schematics

5

www.schematic-x.blogspot.com

4

3

2

1

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND1

LAYER 3 : IN1

LAYER 4 : SVCC

D D

LAYER 5 : IN2

DDR4 SO-DIMM

STD

Memory Down

LAYER 6 : IN3

Channel A0

P9

Channel A1

P10

DIMM+Down:1600~1866 MT/s

LAYER 7 : GND2

LAYER 8 : BOT

SATA - HDD

SATA - SSD

USB3 Type-C CONN

C C

(CC:TPS25810)

USB3 Con.

USB2 CONN x2

Phone Jack

B B

ODD CONN

P15

FFC

I/O Board CONN

ROM 128 kB

3

.3 V

P15

U2 to SATA

ASM1153

X'TAL

25 MHz

AUDIO CODEC

ALC255-CG

A A

P14

ZAS BLOCK DIAGRAM

Memory

GFX

STONEY

FT

4 (BGA769)

I2C

DP

GPP

SPI

RTC

SMBUS

EC

P18

P1

P20

P21

P21

P15

5

SATA 0

SATA 1

USB2 - 4

USB3 - 0 & 1

USB2 - 6

USB3 - 2

USB2-0 & USB2-1

USB2-2 (BT)

USB2-3 (CCD)

USB2-4 (Type-c)

USB2-6 (USB3)

USB2-7 (ODD)

Azalia

15h (70h-7Fh)

SATA

USB3.0

USB2.0

CLK

HDA

APU

BGA769

P2,3,4,5,6,7,8

PC

L

IT8987E/BX

I2C-0 (Touch Pad)

0

DP

USB2-3 (CCD)

DP1

GPP0

GPP1

USB2-2 (BT)

GPP2 & GPP3

SATA 1

X'TAL

32.768 kHz

X'TAL 48 MHz

BATT

P7

SPI ROM 8MB

1.8 V

G-Sensor

P19

PS/2

P24

eDP/CCD/MIC CONN

HDMI CONN

LAN+Card Reader

RTL8411B

X'TAL

25 MHz

M

.2

WLAN+BT w/ Debug

M.2

SSD

P16

P6

TPM

PCT650

N

ROM 128 kB

3.3 V

P12

P19

P24

P13

P17

P11

RJ45 CONN

C.R. CONN

Power source

BQ24737RGRR

Batery Charger

TPS51225R

3V/5V

G5335QT2U

VDDP

RT8231B

+1.2VSUS

RT3662AC

CPU CORE / VDDNB

SP@ Special part

HDT@ Debug

KBL@ KB Backlight

ODD@ ODD

EV@ GPU

UMA@ UMA

TYP_C@ Type C solution

NTYP_C@ non-TYP_C solution

TPM@ TPM

NTPM@ non-TPM

GS@ G-sensor

NGS@ non-G-sensor

VL@ 12V Panel Power

NVL@ 19V Panel Power

SSD@ SSD

P13

SSDP@ PCIE SSD

SSDS@ SATA SSD

SSD_DS@ SSD Device Sleep

P13

SSD_NDS@ SSD non-Device Sleep

SRD@ SATA's Redriver

NSRD@ non-SATA's Redriver

DS@ HDD Device Sleep

NDS@ HDD non-Device Sleep

DDP@ DRAM x16(DDP)

SDP@ DRAM x16(SDP)

M

5671RE1U

1.8V

P25

G9336ADJTP1U

0.775V

P26

G5719CTB1U

1.5V

27

P

TPS61087DRCR

12V(PANEL)

P28

P29, P30

01

P31

P31

P31

P33

Speaker DMIC

P14 P14

Squirtle_SR SSID : 1192

5

LED(DB)

P21

4

K/B CONN

K/B BL CONN

P23 P11 P23 P22

P23

HALL SENSOR

FAN CONN

(PWM)

3

Touch Pad

CONN

I2C-0

Reset Button

P24

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZAS

ZAS

ZAS

1 35

1 35

1

1 35

1A

1A

1A

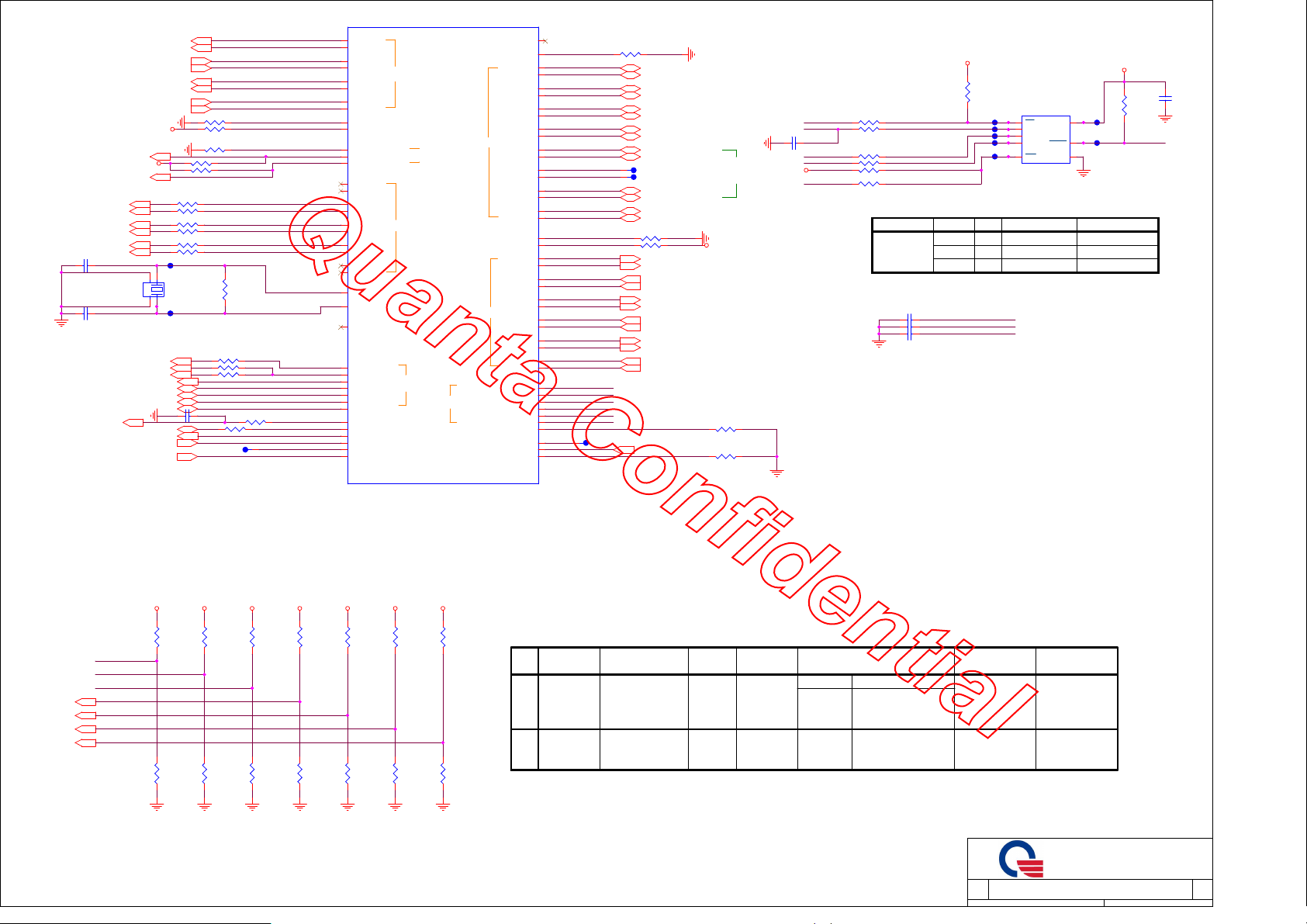

(CPU)

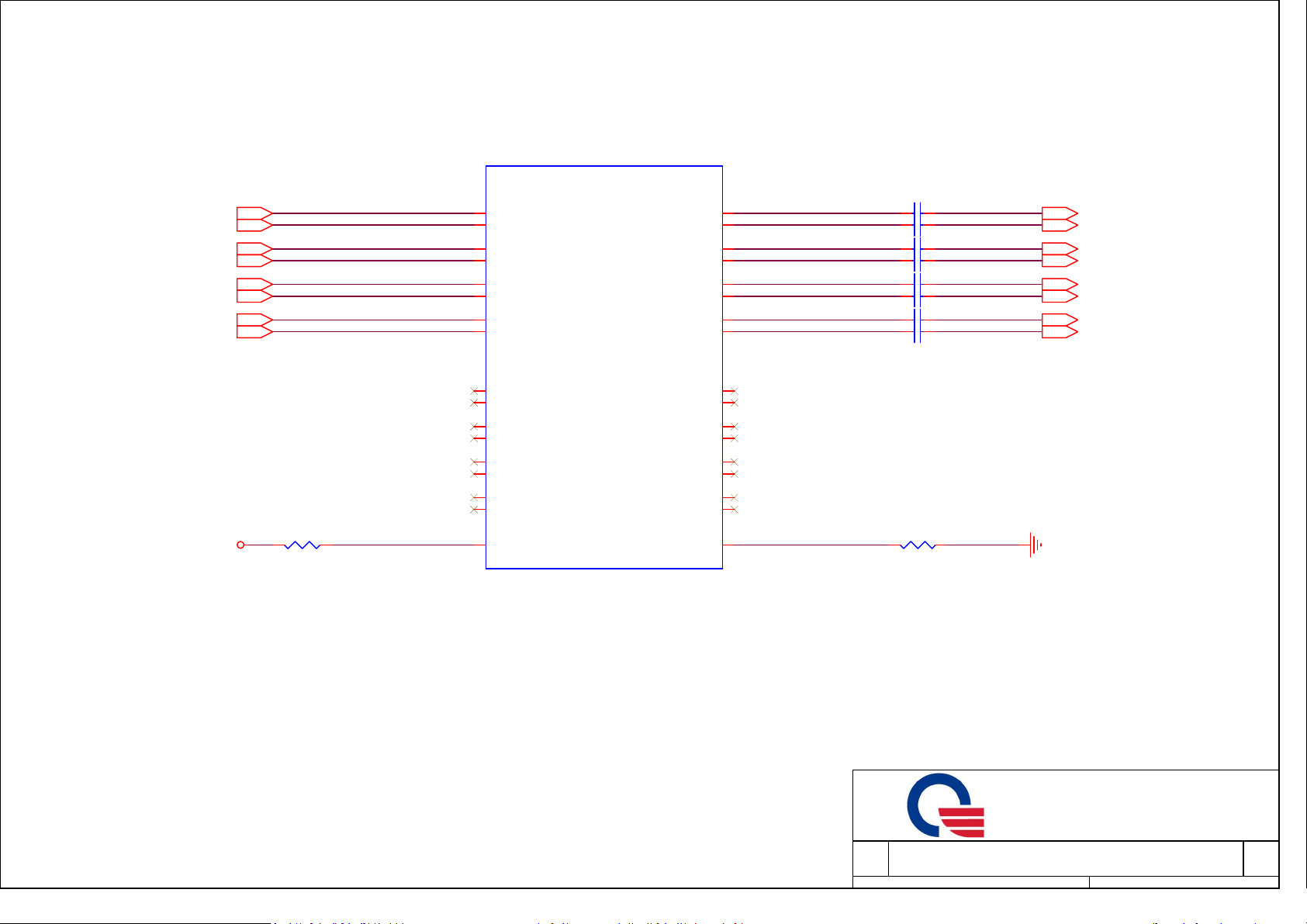

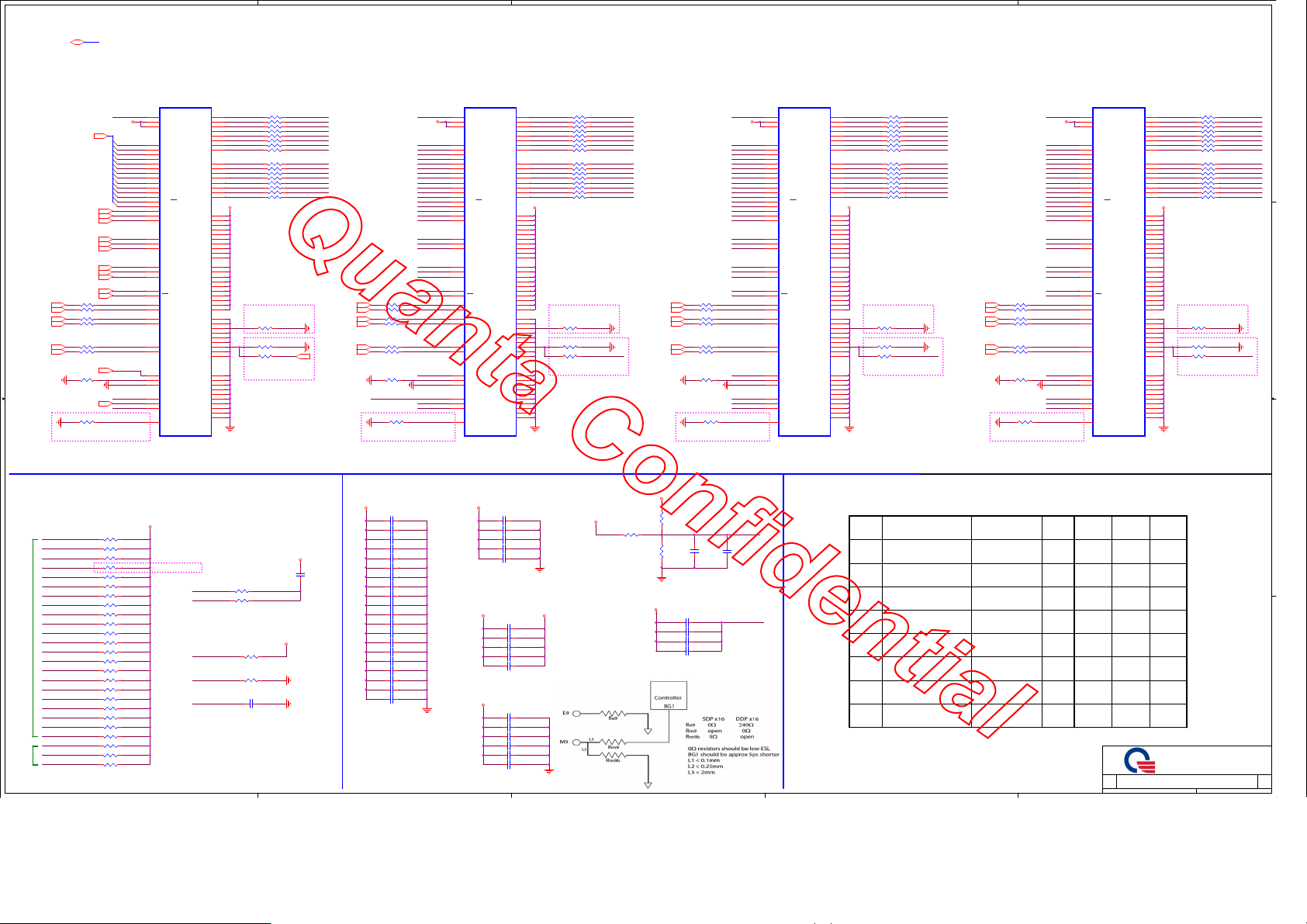

02

LAN

WLAN

SSD

SSD

PCIE_RX0[13]

PCIE_RX0#[13]

PCIE_RX1[17]

PCIE_RX1#[17]

PCIE_RX2[16]

PCIE_RX2#[16]

PCIE_RX3[16]

PCIE_RX3#[16]

VDDP_0.95V

R40 196_1%_4

U19B

U4

P_GPP_RXP0

U5

P_GPP_RXN0

R8

P_GPP_RXP1

R10

P_GPP_RXN1

R5

P_GPP_RXP2

R4

P_GPP_RXN2

N4

P_GPP_RXP3

N5

P_GPP_RXN3

L5

P_GFX_RXP0

L4

P_GFX_RXN0

J5

P_GFX_RXP1

J4

P_GFX_RXN1

G5

P_GFX_RXP2

G4

P_GFX_RXN2

D7

P_GFX_RXP3

E7

P_GFX_RXN3

P_ZVDDP P_ZVSS

U8

P_ZVDDP

SP@AMD_SR_FT4

PCIE

VDDP_S0

VDDP_S0

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_ZVSS

D2

D1

C2

C1

B2

B1

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

W8

supporting both Gen 2and Gen 3 operation is 220 nF

supporting Gen 3 operation only is 220 nF

supporting Gen 2 operation only is 100 nF

PCIE_TX0_C

PCIE_TX0#_C

PCIE_TX1_C

PCIE_TX1#_C

PCIE_TX2_C

PCIE_TX2#_C

PCIE_TX3_C

PCIE_TX3#_C

C353 0.1u/16V_4

C350 0.1u/16V_4

C355 0.1u/16V_4

C354 0.1u/16V_4

C357 SSDP@0.22u/10V_4

C356 SSDP@0.22u/10V_4

C359 SSDP@0.22u/10V_4

C361 SSDP@0.22u/10V_4

Samsung SM951 (M.2 PCIE Gen3 SSD)

R36 196_1%_4

PCIE_TX0 [13]

PCIE_TX0# [13]

PCIE_TX1 [17]

PCIE_TX1# [17]

PCIE_TX2 [16]

PCIE_TX2# [16]

PCIE_TX3 [16]

PCIE_TX3# [16]

LAN

WLAN

SSD

SSD

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FT4 PCIE I/F(1/7)

FT4 PCIE I/F(1/7)

FT4 PCIE I/F(1/7)

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

ZAS

ZAS

ZAS

2 35

2 35

2 35

1A

1A

1A

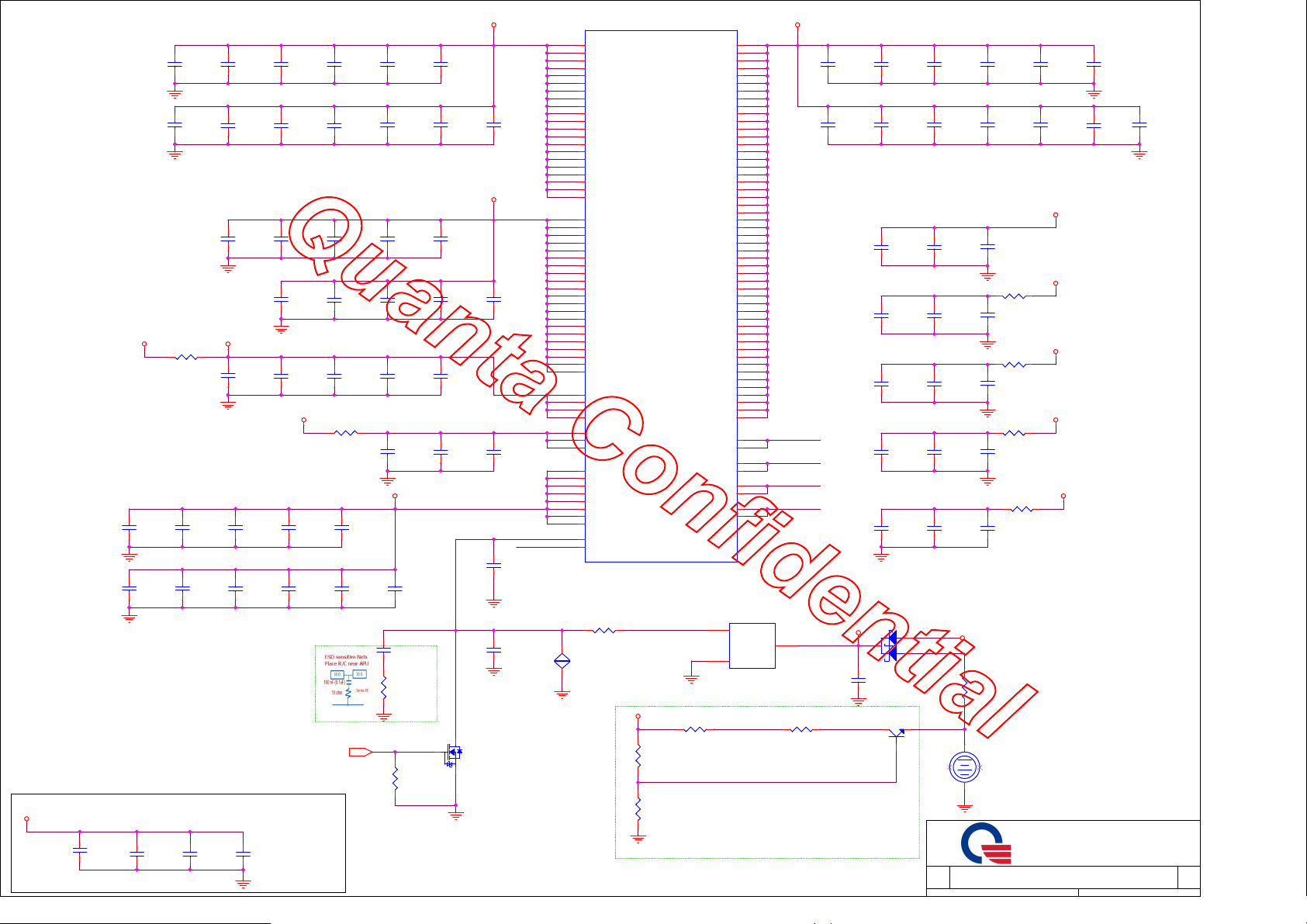

(CPU)

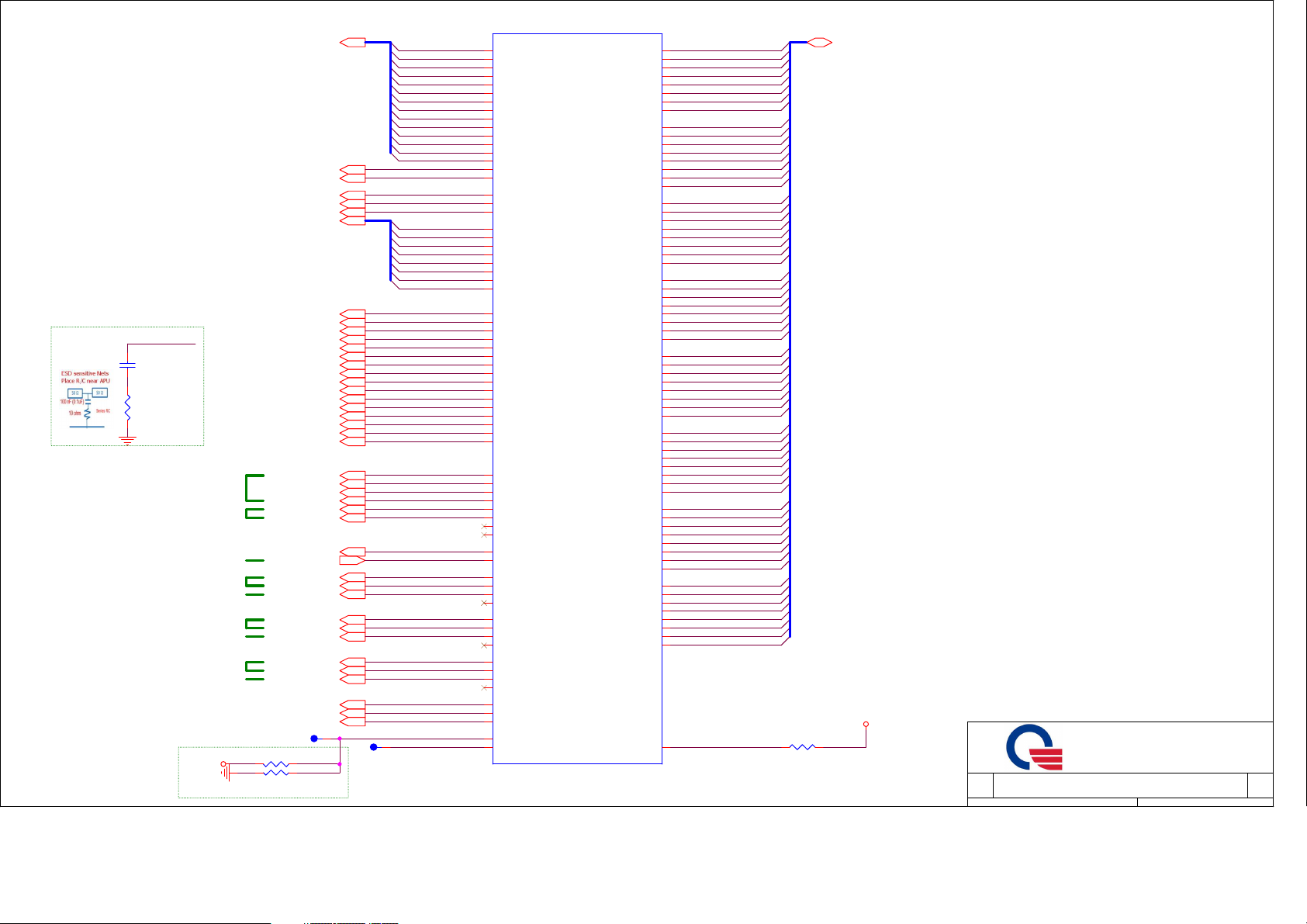

M_A_RST#

C109

*0.1u/16V_4

R98

*10_5%_6

A0-DIMM

A1-ON BOARD

A0-DIMM

A0-DIMM

A1-ON BOARD

A0-DIMM

A1-ON BOARD

A0-DIMM

A1-ON BOARD

+1.2VSUS

only for DDR3 need mount

M_A_BG1[9,10]

M_A_ACT#[9,10]

M_A_BANK0[9,10]

M_A_BANK1[9,10]

M_A_BG0[9,10]

M_A_DM[7..0][9,10]

M_A_DQS0[9,10]

M_A_DQS#0[9,10]

M_A_DQS1[9,10]

M_A_DQS#1[9,10]

M_A_DQS2[9,10]

M_A_DQS#2[9,10]

M_A_DQS3[9,10]

M_A_DQS#3[9,10]

M_A_DQS4[9,10]

M_A_DQS#4[9,10]

M_A_DQS5[9,10]

M_A_DQS#5[9,10]

M_A_DQS6[9,10]

M_A_DQS#6[9,10]

M_A_DQS7[9,10]

M_A_DQS#7[9,10]

M_A0_CLK0[9]

M_A0_CLK0#[9]

M_A0_CLK1[9]

M_A0_CLK1#[9]

M_A1_CLK0[10]

M_A1_CLK0#[10]

M_A_RST#[9,10]

M_A_EVENT#[9]

M_A0_CKE0[9]

M_A0_CKE1[9]

M_A1_CKE0[10]

M_A0_ODT0[9]

M_A0_ODT1[9]

M_A1_ODT0[10]

M_A0_CS#0[9]

M_A0_CS#1[9]

M_A1_CS#0[10]

M_A_RAS#[9,10]

M_A_CAS#[9,10]

M_A_WE#[9,10]

TP72

R513 *1K_1%_4

R512 *1K_1%_4

TP70

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_VREF

M_A_VREFDQ

U19A

AG38

M_ADD0

W35

M_ADD1

W38

M_ADD2

W34

M_ADD3

U38

M_ADD4

U37

M_ADD5

U34

M_ADD6

R35

M_ADD7

R38

M_ADD8

N38

M_ADD9

AG34

M_ADD10

R34

M_ADD11

N37

M_ADD12

AN35

M_ADD13

L38

M_ADD14/M_BG1

L35

M_ADD15/M_ACT_L

AJ38

M_BANK0

AG35

M_BANK1

N34

M_BANK2/M_BG0

B35

M_DM0

D40

M_DM1

K40

M_DM2

T41

M_DM3

AE41

M_DM4

AL40

M_DM5

AU40

M_DM6

BA37

M_DM7

B36

M_DQS_H0

A36

M_DQS_L0

E40

M_DQS_H1

D41

M_DQS_L1

L40

M_DQS_H2

K41

M_DQS_L2

U41

M_DQS_H3

U40

M_DQS_L3

AF41

M_DQS_H4

AE40

M_DQS_L4

AM40

M_DQS_H5

AM41

M_DQS_L5

AV40

M_DQS_H6

AV41

M_DQS_L6

BA36

M_DQS_H7

AY36

M_DQS_L7

AC35

M_CLK_H0

AC34

M_CLK_L0

AA34

M_CLK_H1

AA32

M_CLK_L1

AE38

M_CLK_H2

AE37

M_CLK_L2

AA37

M_CLK_H3

AA38

M_CLK_L3

G38

M_RESET_L

AA41

M_EVENT_L

J38

M0_CKE0

J34

M0_CKE1

L34

M1_CKE0

J37

M1_CKE1

AN37

M0_ODT0

AU38

M0_ODT1

AL34

M1_ODT0

AN34

M1_ODT1

AL35

M0_CS_L0

AR37

M0_CS_L1

AJ34

M1_CS_L0

AR38

M1_CS_L1

AJ37

M_RAS_L/M_RAS_L_ADD16

AN38

M_CAS_L/M_CAS_L_ADD15

AL38

M_WE_L/M_WE_L_ADD14

AA40

M_VREF

Y41

M_VREFDQ

SP@AMD_SR_FT4

MEMORY

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_ZVDDIO_MEM_S3

A34

B34

A38

B38

A33

B33

A37

B37

B41

C40

F41

G40

A40

B40

E41

F40

J40

J41

N40

N41

H40

H41

M40

M41

R40

T40

W40

Y40

P40

P41

V40

V41

AD41

AD40

AH41

AH40

AB40

AC40

AF40

AG40

AK41

AK40

AP41

AP40

AJ41

AJ40

AN41

AN40

AT40

AU41

AY40

BA40

AR40

AT41

AW40

AY41

BA38

AY37

BA34

BA33

AY39

AY38

AY35

AY34

AB41

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_ZVDDIO

M_A_DQ[0..63] [9,10]M_A_A[13:0][9,10]

+1.2VSUS

R514 39.2_1%_4

03

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

PROJECT :

FT4 DDR4 I/F(2/7)

FT4 DDR4 I/F(2/7)

FT4 DDR4 I/F(2/7)

ZAS

ZAS

ZAS

3 35

3 35

3 35

1A

1A

1A

(CPU)

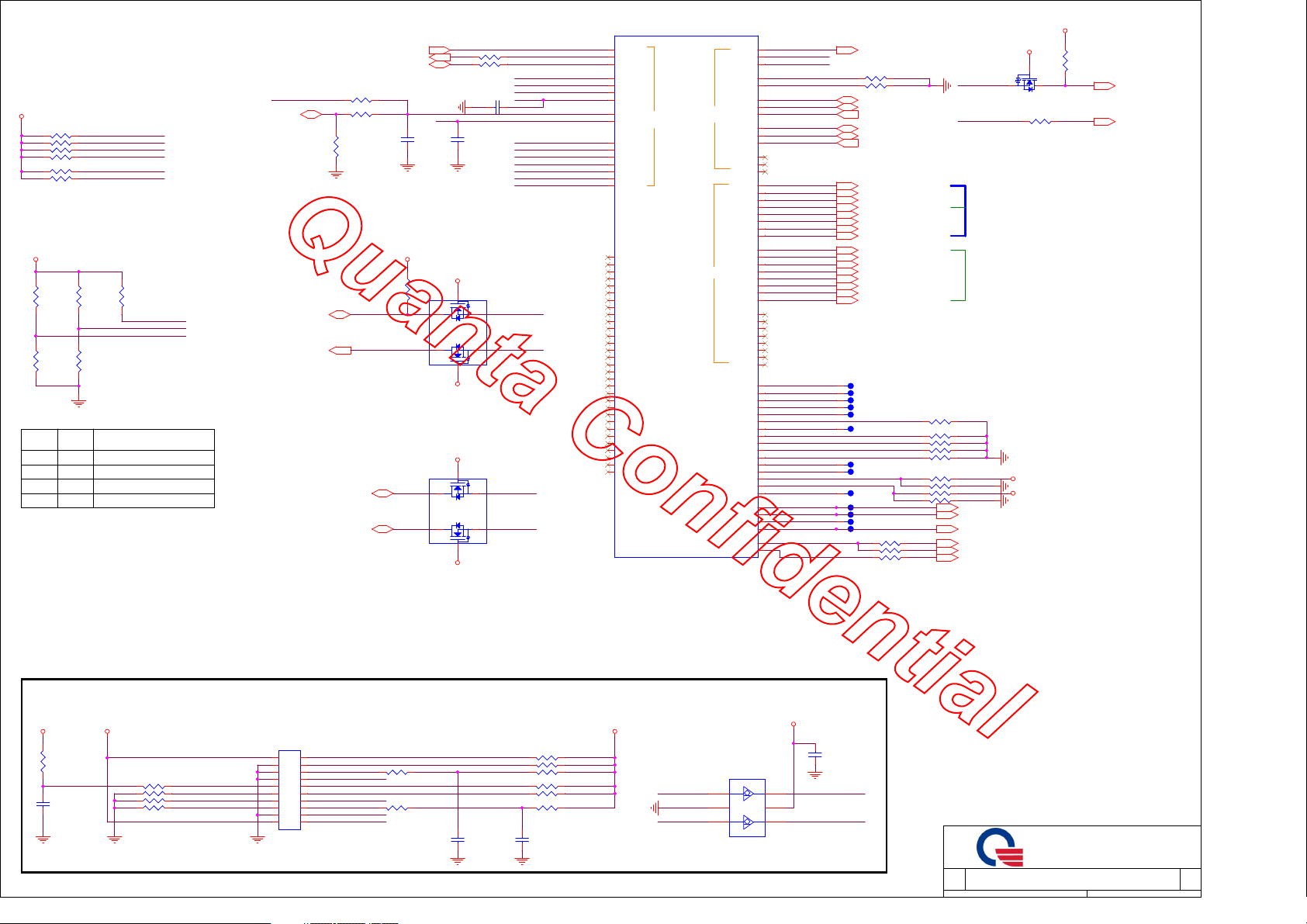

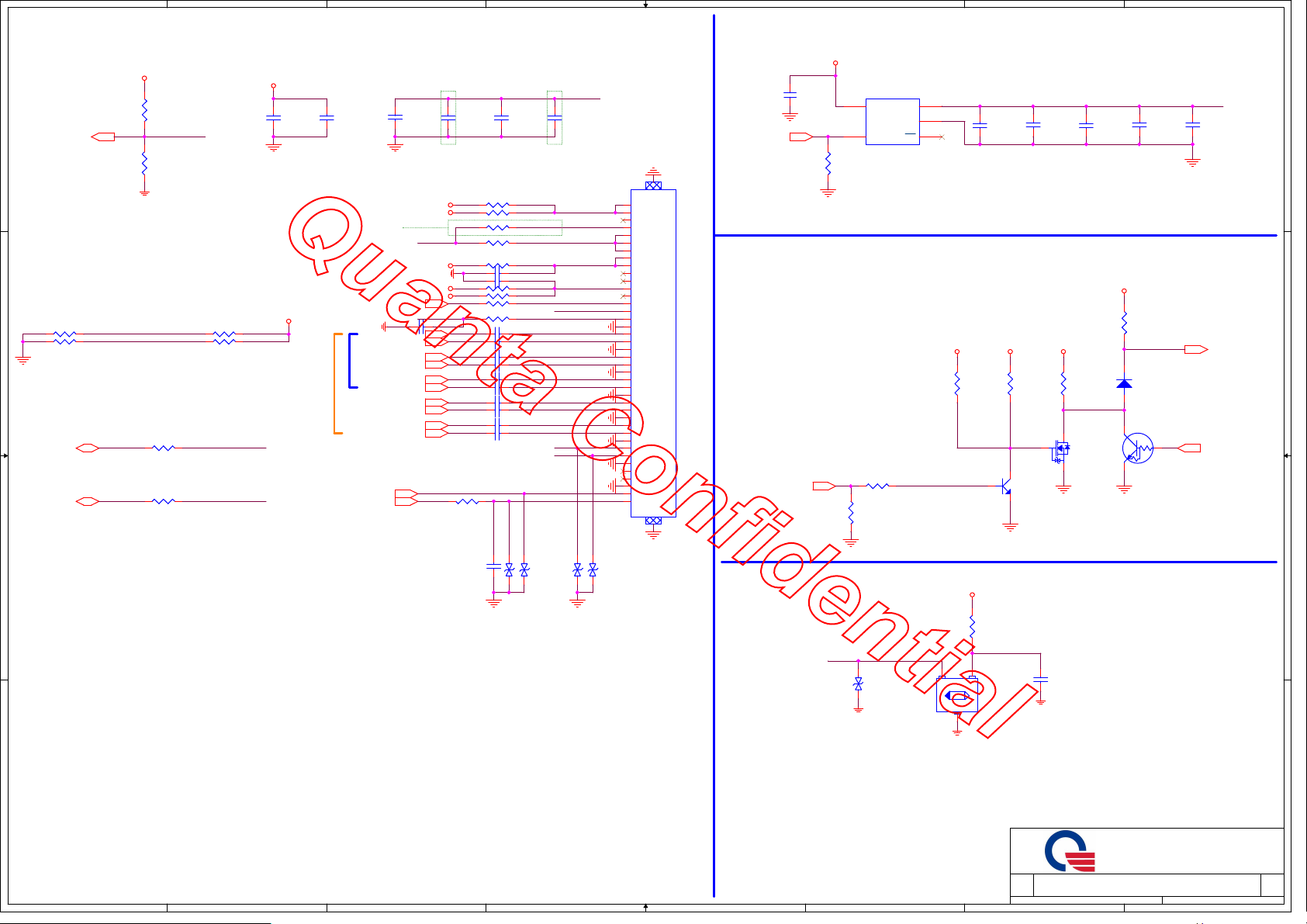

VDD_18

R483 1K_1%_4

R489 1K_1%_4

R481 1K_1%_4

R493 1K_1%_4

R454 300_5%_4

R477 300_5%_4

APU_SIC

APU_SID

APU_ALERT#

APU_PROCHOT#

APU_PWRGD

APU_RST#

Serial VID

VDD_18

R62

R447

R471

*1K_1%_4

R463

*220_1%_4

VFIX MODE

SVDSVC

0

0

0

110 0.9V

for normal operation open all switches

11

*1K_1%_4

*1K_1%_4

R450

*220_1%_4

VID Override table (VDD)

Boot Voltage

1.1V

1.0V

0.8V

APU_SVT

APU_SVC

APU_SVD

APU_SVT[29]

APU_SVC[29]

APU_SVD[29]

R456 HDT@0_5%_4

APU_PWRGD_SVID_RE G[29]

R455 *short_4

R452

*220_1%_4

FOR DEBUG, PLACE THESE CAPS CLOSE TO APU

+3V

3V_S0

CORE_PWM_PROCHOT#[24,25,29]

THERM_ALERT#[23]

3V_S0 (PU in FAN side)

SVT need 0R in power side

R459 *short_4

R464 *short_4

VDD_18

5

C371

*27p/50V_4

C365

*27p/50V_4

R494

10K_1%_4

3 4

Q23A PJT138K

Q23B PJT138K

6 1

2

VDD_18

SMBUS(Internal Thermal sensor)

VDD_18

5

2ND_MBCLK[24]

3V_S5

(PU in EC side )

2ND_MBDATA[24]

3 4

Q21A PJT138K

Q21B PJT138K

6 1

2

VDD_18

C475 *0.1u/16V_4

APU_PROCHOT#

1.8_S0

APU_ALERT#

APU_SIC

1.8_S0

APU_SID

APU_SVC_R

APU_SVD_R

APU_SIC

APU_SID

APU_ALERT#

APU_PROCHOT#APU_PWRGD_D

APU_PWRGD

APU_RST#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

U19C

H27

E27

D27

B30

B29

A30

A31

G25

D29

B25

A27

B27

B26

A29

A26

A25

D9

D11

D13

E4

E31

H11

H13

L11

AE34

AM15

AM17

AM19

AN8

AP13

AP15

AP17

AR13

AR15

AR17

AU4

AU13

AU15

AU17

AV7

AV9

AV11

AV13

AV15

AV17

AY3

AY7

SP@AMD_SR_FT4

SVT

SVC

SVD

SIC

SID

ALERT_L

PROCHOT_L

PWROK

RESET_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

RSVD_16

RSVD_17

RSVD_18

RSVD_19

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_31

DISPLAY/SVI2/JTAG/TEST

1.8V_S0

1.8V_S0

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

DP_ZVSS

DP0_AUXP

DP0_AUXN

DP0_HPD

1.8V_S0

DP1_AUXP

DP1_AUXN

DP1_HPD

DP2_AUXP

DP2_AUXN

DP2_HPD

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

VDDP_S0

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST28_H

TEST28_L

TEST31

DP_STEREOSYNC/TEST36

TEST41

VDDCR_CPU_SENSE

VDDCR_NB_SENSE

VDDIO_MEM_S3_SENSE

VDDP_SENSE

VSS_SENSE_A

VSS_SENSE_B

B23

APU_DIGON

B24

APU_BLPWM

A24

DP_AUX_ZVSS

D21

DP_ZVSS

B18

G15

H15

D15

G17

H17

D17

G19

H19

D19

A9

B9

A10

B10

A11

B11

A12

B12

A14

B14

A15

B15

A16

B16

A17

B17

A19

B19

A20

B20

A21

B21

A22

B22

APU_TEST4

H29

APU_TEST5

G29

APU_TEST6

H25

APU_TEST9

R32

APU_TEST10

N32

APU_TEST14

G21

APU_TEST15

H21

APU_TEST16

D23

APU_TEST17

E23

APU_TEST18

A28

APU_TEST19

B28

APU_TEST28_H

N8

APU_TEST28_L

N10

APU_TEST31

H31

DP_STEREOSYNC

D25

TMON_CAL

B31

D31

E33

D35

AM21

APU_VSS_SENSE_A

D33

AM23

APU_VSS_SENSE_B

Power design no 1.2VSUS_H/L & VDDNB_L sense (the same ZAB/ZRZ)

APU_DISP_BLEN [11,24]

R55 150_1%_4

R444 2K_1%_4

EDP_AUX [11]

EDP_AUX# [11]

EDP_HPD [11]

HDMI_DDCCLK [12]

HDMI_DDCDATA [12]

HDMI_HPD [12]

EDP_TX0 [11]

EDP_TX0# [11]

EDP_TX1 [11]

EDP_TX1# [11]

EDP_TX2 [11]

EDP_TX2# [11]

EDP_TX3 [11]

EDP_TX3# [11]

HDMI_TX2 [12]

HDMI_TX2# [12]

HDMI_TX1 [12]

HDMI_TX1# [12]

HDMI_TX0 [12]

HDMI_TX0# [12]

HDMI_CLK [12]

HDMI_CLK# [12]

TP10

TP13

TP8

TP18

TP16

TP9

TP3

TP5

TP69

TP17

TP14

TP20

TP6

R61 *1K_1%_4

R457 *1K_1%_4

R65 *1K_1%_4

R468 1K_1%_4

R476 1K_1%_4

R66 *39.2_1%_4

R69 *39.2_1%_4

R449 1K_1%_4

R446 *1K_1%_4

R500 *short_4

R499 *short_4

R432 *short_4

VDD_18

1.8V

APU_BLPWM

APU_DIGON

2

3

1

Q20

PJA138K

R448 *short_4

1.8V

eDP FHD

eDP UHD

AMD DG HDMI

APU P0 - conn P2

APU P1 - conn P1

HDMI

APU P2 - conn P0

APU P3 - conn CK

VDD_18

APU_VDD_RUN_FB_H [29]

APU_VDDNB_RUN_FB_ H [29]

APU_VDDP_RUN_FB_H [27]

APU_VDD_RUN_FB_L [29]

APU_VDDNB_RUN_FB_ L [29]

APU_VDDP_RUN_FB_L [27]

VDD_18

+3V

R441

10K_1%_4

LCD 3.3V

APU_DISP_PWM [11]

APU_DISP_ON [11]

EN:>1.5V

M_TEST CONNECTION TBD

PU : Enable HDMI (1.8V_S0 by 1k)

PD : Disable HDMI

04

HDT(Hardware Debug Tool ) Connector

VDD_18 VDD_18 VDD_18

CN6

R525

HDT@1K_1%_4

APU_TRST#

C384

HDT@0.01u/50V_4

R524 HDT@33_5%_4

R523 HDT@10K_1%_4

R522 HDT@10K_1%_4

R521 HDT@10K_1%_4

PLACE HDT CONNECTOR ON TOP

HDT_TRST#

DBRDY3

DBRDY2

DBRDY1

1 2

3

5 6

7

9

11

13 14

15

17

19

4

8

10

12

16

18

20

*HDT@HDT CONN

APU_TCK

APU_TMS

HDT_APU_TDI

APU_TDO

APU_PWROK_BUF

APU_RST_L_BUF

APU_DBRDY

HDT_DBREQ#

APU_TEST19

APU_TEST18

R505 HDT@0_5%_4

R509 HDT@33_5%_4

APU_TDI

APU_DBREQ#

C382

*HDT@0.01u/50V_4

R508 HDT@ 1K_1%_4

R507 HDT@ 1K_1%_4

R506 HDT@ 1K_1%_4

R526 HDT@ 1K_1%_4

R527 HDT@ 1K_1%_4

R520 HDT@ 1K_1%_4

C383

HDT@0.01u/50V_4

VDD_18

C381

U20

A1

APU_RST#

APU_PWRGD_D APU_PWROK_BUF

Y1

1

2

3

6

5

GND

VCC

A24Y2

*HDT@SN74LVC2G07DCKR

HDT@0.1u/16V_4

APU_RST_L_BUF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

PROJECT :

FT4 DISPLAY/MISC(3/7)

FT4 DISPLAY/MISC(3/7)

FT4 DISPLAY/MISC(3/7)

ZAS

ZAS

ZAS

4 35

4 35

4 35

1A

1A

1A

(CPU)

+3V_S5

R16 10K_1%_4

R17 10K_1%_4

R383 *10K_1%_4

R384 10K_1%_4

R389 10K_1%_4

R391 10K_1%_4

R392 10K_1%_4

R385 *10K_1%_4

+3V_S5

+3V

VDD_18

BOARD ID

+3V

VDD_18

R388 *10K_1%_4

J1

*SHORT_PAD

R510 2.2K_5%_4

R504 2.2K_5%_4

R497 10K_1%_4

R503 10K_1%_4

R415 1K_1%_4

R410 1K_1%_4

R412 1K_1%_4

R420 1K_1%_4

R418 *10K_1%_4

R416 10K_1%_4

R417 10K_1%_4

R451 2.2K_5%_4

R460 2.2K_5%_4

R443 10K_1%_4

R440 10K_1%_4

R431 TPM@10K_1%_4

R425 NTYP_C@10K_1%_4

R429 NGS@10K_1%_4

R427 EV@10K_1%_4

R437 SP@10K_1%_4

R426 SP@10K_1%_4

R501 SP@10K_1%_4

R635 SSDS@ 10K_1%_4

R636 SP@10K_1%_4

R639 SP@10K_1%_4

1 2

GPIO

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

BOARD_ID7

BOARD_ID8

BOARD_ID9

PCIE_WAKE#

LR_LED_L

S0A3

DNBSWON#

USB_OC1#

USB_OC2#

AGPIO8

S3_RESUME

SYS_RST#

PU in STRAPS PINS side

CLK_SCLK

CLK_SDATA

CLK_REQ3_L

PCIE_REQ_GPU#_R

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

ACZ_BCLK_R

PCH_AZ_CODEC_SDIN0

AZ_SDIN1

AZ_SDIN2

I2C_SCL_TP

I2C_SDA_TP

I2C_SCL_TS

I2C_SDA_TS

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

BOARD_ID7

BOARD_ID8

BOARD_ID9

High Low

dTPM

non-Type C

non-G sensor

GPU UMA

Memory ID Memory ID

Memory ID

Memory ID Memory ID

SATA SSD PCIE SSD

Reserve

Reserve

S0A3_GPIO pin

Checklist v1.04 change to left unconnected

1.AZ_BITCLK

FT4 CRB:1K(stuff), FT4 CL:10K(DNI)

2016/11/30 AMD : install 1K or 10K . (follow CRB 1K first)

2.AZ_RST#/SYNC/SDOUT

FT4 CL:1K(stuff), FP4 CL :1K(DNI)

2016/11/30 AMD : stuff

R430 NTPM@10K_1%_4

R424 TYP_C@10K_1%_4

R438 GS@10K_1%_4

R435 UMA@10K_1%_4

R436 SP@10K_1%_4

R434 SP@10K_1%_4

R502 SP@10K_1%_4

R637 SSDP@ 10K_1%_4

R638 SP@10K_1%_4

R640 SP@10K_1%_4

RSMRST#[24]

OC0: Type-c

OC1: USB3.0

OC2: USB2.0

1

CC_OC#[20]

USB_OC1#[21]

USB_OC2#[21]

Test mode setting (Follow AMD's suggestion)

iTPM

Type C

G sensor

Memory ID

Reserve

Reserve

Reserve:Default PD

Reserve:Default PD

VDD_18_S5

R390

D16

2

RB500V-40

PCH_RSMRST#_R

C344

*0.1u/16V_4

R379

*10_5%_6

+3V_S5

NC,no install by default

R387 *2.2K_5%_4

R386 *1K_1%_4

R25 *2.2K_5%_4

15K_1%_4

PCIERST#[13,16,17]

AMD : 10ms RC-delay

C352

0.1u/16V_4

C477

*0.1u/16V_4

PCH_AZ_CODEC_BITCLK[14]

PCH_AZ_CODEC_SDIN0[14]

PCH_AZ_CODEC_RST#[14]

PCH_AZ_CODEC_SYNC[14]

PCH_AZ_CODEC_SDOUT[14]

C15 150p/50V_4

DNBSWON#[24]

PCIE_LAN_WAKE#[13]

SUSB#[24]

SUSC#[24]

APU_S5_MUX_CTRL[32]

ACPRESENT[25]

APU_TYPEC_UFP#[20]

PCIE_REQ_LAN#[13]

PCIE_CLKREQ_WLAN#[17]

PCIE_CLKREQ_SSD#[16]

C478

*0.1u/16V_4

C349 18p/50V_4

C348 18p/50V_4

AMD CL maximum ESR of the XTAL is 65 kΩ

TXC:BG332768111 20PPM (ESR 70kΩ)Metal shell

NDK:BG332768108 20PPM (ESR 70kΩ)Metal shell

SEIKO:BG632768006 20PPM (ESR 70kΩ)Metal shell

**SEG:BG332768453 20PPM (ESR 70kΩ)Glass shell

APU_TEST0

APU_TEST1

APU_TEST2

R408 15 K_1%_4

R407 15 K_1%_4

R29 15K_1%_4

R27 33_5%_4

R15 *short_4

C14 *100p/50V_4

S0A3:

if unused, need PU VDD_33_S5 10K or PD 10K

CLK_REQ0,3,G:

if unused, need PU VDD_33 10K or PD 10K

C479

*0.1u/16V_4

R419 33_5%_4

R414 33_5%_4

R411 33_5%_4

R413 33_5%_4

I2C_SCL_TP[22]

I2C_SDA_TP[22]

Use for I2C bus:

PU VDD_18 2.2K

I2C Not Implemented:

Used as EGPIO or PU VDD_18 10K or PD VSS 10K

12

Y3

32.768KHZ/20ppm

TEST2 TEST1 TEST0 Description

0

0 0

0

0

0

1

1

TMS

1 TMS

FCH TAP accessi ble from APU wh en TAPEN is ass erted

FCH JTAG pins a re overloaded f or multiple

functions, in t his configurati on the FCH JTAG are

used as non-JTA G pins

1

Reserved

X

Reserved

FCH JTAG multi- function pins a re configured a s

JTAG pins, in t his configurati on the FCH TAP

0

can be accessed from FCH JTAG pins

Use on ATE only

1

Yuba JTAG enabl ed

PCIE_RST#

PCH_RSMRST#_R

SYS_PWRGD

SYS_RST#

PCIE_WAKE#

S0A3

APU_TEST0

APU_TEST1

APU_TEST2

LR_LED_L

CLK_REQ3_L

PCIE_REQ_GPU#_R

ACZ_BCLK_R

AZ_SDIN1

AZ_SDIN2

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

I2C_SCL_TS

I2C_SDA_TS

32K_X1

32K_X2

R404

20M_5%_4

U19D

AE4

PCIE_RST_L/EGPIO26

AG1

RSMRST_L

AD2

PWR_BTN_L/AGPIO0

AE2

PWR_GOOD

AF1

SYS_RESET_L/AGPIO1

AE7

WAKE_L/AGPIO2

AC2

SLP_S3_L

AG4

SLP_S5_L

AB1

S0A3_GPIO/AGPIO10

AA7

S5_MUX_CTRL/EGPIO42

AF2

TEST0

AE1

TEST1/TMS

AC8

TEST2

AH2

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AA4

IR_TX0/USB_OC5_L/AGPIO13

AG8

IR_TX1/USB_OC6_L/AGPIO14

AL5

IR_RX1/AGPIO15

AE8

IR_LED_L/LLB_L/AGPIO12

AY32

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AY31

CLK_REQ1_L/AGPIO115

AV29

CLK_REQ2_L/AGPIO116

AP31

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AV35

CLK_REQG_L/OSCIN/EGPIO132

AB2

USB_OC0_L/TRST_L/AGPIO16

AG2

USB_OC1_L/TDI/AGPIO17

AJ1

USB_OC2_L/TCK/AGPIO18

AH1

USB_OC3_L/TDO/AGPIO24

AY6

AZ_BITCLK/I2S_BCLK_MIC

BA6

AZ_SDIN0/I2S_DATA_MIC0

AY5

AZ_SDIN1/I2S_LR_PLAYBACK

BA5

AZ_SDIN2/I2S_DATA_PLAYBACK

AY4

AZ_RST_L/I2S_LR_MIC

BA3

AZ_SYNC/I2S_BCLK_PLAYBACK

BA4

AZ_SDOUT/I2S_DATA_MIC1

AY22

I2C0_SCL/EGPIO145

BA22

I2C0_SDA/EGPIO146

AU19

I2C1_SCL/EGPIO147

AV19

I2C1_SDA/EGPIO148

BA2

X32K_X1

AY2

RTC

X32K_X2

SP@AMD_SR_FT4

EC_PWROK[24]

SYS_RST#[6]

SUSB#

ACPI/SD/AZ/GPIO/RTC/MISC

3V_S5

1.8V_S5

3V_S5

3V_S0

3V_S5

3V_S5

3V_S5

VDDIO_AUDIO

1.8V_S0

DGPU_PWREN_A : ZAB chose 3V_S0 GPIO

D14 1N4148WS

D13 *1N4148WS

D12 *1N4148WS

HWPG[24]

3V_S0

3V_S0

3V_S0

3V_S0

3V_S0

3V_S0

3V_S5

3V_S5

3V_S0

3V_S5

1.8V_S0

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

UART1_INTR/BT_I2S_LRCLK/AGPIO144

21

21

21

SD_WP/EGPIO101

SD_PWR_CTRL/AGPIO102

SD_CD/AGPIO25

3V_S5

SD_CLK/EGPIO95

SD_CMD/EGPIO96

SD_LED/EGPIO93

SD_DATA0/EGPIO97

SD_DATA1/EGPIO98

SD_DATA2/EGPIO99

SD_DATA3/EGPIO100

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO3

S5

AGPIO4

S5

AGPIO5

S5

AGPIO6/LDT_RST_L

3V_S5

AGPIO7/LDT_PWROK

3V_S5

S0

3V_S0

3V_S0

3V_S0

3V_S0

UART1_RXD/BT_I2S_SDI/EGPIO141

UART1_TXD/BT_I2S_SDO/EGPIO143

5

AGPIO8

S5

AGPIO9

S5

AGPIO40

S5

BLINK/USB_OC7_L/AGPIO11

GENINT2_L/AGPIO90

SPKR/AGPIO91

GA20IN/AGPIO126

FANIN0/AGPIO84

FANOUT0/AGPIO85

UART0_CTS_L/EGPIO135

UART0_RXD/EGPIO136

UART0_RTS_L/EGPIO137

UART0_TXD/EGPIO138

UART0_INTR/AGPIO139

UART1_RTS_L/EGPIO142

HVBEN_L

3V_S0

RTCCLK

3V_S5

SYS_PWRGD_R

+3V_S5

R382

100K_1%_4

34

2

Q19A

2N7002KDW

05

DGPU_PWREN

BA28

AY29

AY13

BOARD_ID4

BA14

BOARD_ID5

AY15

BOARD_ID6

BA29

SD_LED/EGPIO93 : unused need PU 10K to 3V or GND

BOARD_ID0

AY14

BOARD_ID1

BA13

BOARD_ID2

BA16

BOARD_ID3

AY16

AY33

BA32

AC5

SCL1

AC4

SDA1

AJ7

AK2

AGPIO4

PCH_ODD_EN

AK1

AL4

AJ2

AGPIO7

AJ4

AGPIO8

DEVSLP_GATE# need use S5 domain

AG5

AD1

R32 *SSD_DS@100K _1%_4

S3_RESUME

S3 resume time measure point

AJ8

DGPU_RST_L

AR29

AP29

AU35

APU_TP_INT#

AV33

AU33

BLINK/USB_OC7_L/AGPIO11

FP4 PU, FT4 DNI

AP23

2016/11/30 AMD :BLINK is not implemented at design

AP25

follow FP4 PU OK

AR25

AV25

AU23

BOARD_ID7

AP21

BOARD_ID8

AV21

BOARD_ID9

AP19

PE_PWRGD

AV23

AR21

AP27

TP12

AN4

R19 *22_5%_4

+3V

R377

4.7K_5%_4

R378 *short_4

C342

0.22u/10V_4

61

Q19B

2N7002KDW

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

TP64

ODD_PLUGIN# [15]

CLK_SCLK [9,19]

CLK_SDATA [9,19]

TP2

TP1

GEVENT2# [6]

TP51

TP52

ACCEL_INTA [19]

TP53

R406 10K_1%_4

AGPIO11 [6]

TP15

SPKR [14]

SIO_A20GATE [24]

TP19

APU_I2C_INT# [22]

TP87

Hardwave validated boot(HVB)

Enable : connected to GND

Dissable : floating

RTC_CLK [6]

SUS_CLK [17]

DEVSLP_GATE# [16,18]

SYS PWRGD

SYS_PWRGD

C343

*0.1u/16V_4

R380

*10_5%_6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

FT4 GPIO/AZ/I2C/UARTS/ACPI(4/7)

FT4 GPIO/AZ/I2C/UARTS/ACPI(4/7)

FT4 GPIO/AZ/I2C/UARTS/ACPI(4/7)

ZAS

ZAS

ZAS

5 35

5 35

5 35

1A

1A

1A

DEVSLP

connects to device : don't PU

unused : Need PU

CLK_PCIE_WLAN[17]

CLK_PCIE_WLAN#[17]

C346 4.7p/50V_4

TXC:BG648000021 15PPM

HHE:BG648000026 15PPM

C347 5.6p/50V_4

HDD

SSD

VDDP_0.95V

DEVSLP_HDD[18]

+3V

DEVSLP_SSD[16]

CLK_PCIE_LAN[1 3]

CLK_PCIE_LAN#[13]

CLK_PCIE_SSD[16]

CLK_PCIE_SSD#[16]

2

4

all XTAL need add TP2650 for ICT test

test pad must place in Bottom side

CLK_PCI_EC[24]

PCLK_TPM[19]

CLK_LPC_DEBUG[17 ]

LPC_LFRAME#[17,19,24]

LPC_LAD0[17,19,24]

LPC_LAD1[17,19,24]

LPC_LAD2[17,19,24]

LPC_LAD3[17,19,24]

PLTRST#[17,19,24]

CLKRUN#[19 ,24]

LPCPD#[19]

SIO_EXT_SCI#[24]

SERIRQ[19,24]

SATA_TX0[18]

SATA_TX0#[18]

SATA_RX0#[18]

SATA_RX0[1 8]

SATA_TX1[16]

SATA_TX1#[16]

SATA_RX1#[16]

SATA_RX1[1 6]

R46 1K_1%_4

R45 1K_1%_4

R496 10K_1%_4

R492 NDS@10K_1%_4

R498 SSD_NDS@10K_1%_4

R401 *short_4

R402 *short_4

R399 *short_4

R400 *short_4

R397 *short_4

R398 *short_4

TP55

1

Y2

48MHZ/15ppm

3

TP56

R491 2 2_5%_4

R467 2 2_5%_4

R474 2 2_5%_4

C379 150p/50V_4

R490 *short_4

SATA_ZVSS

SATA_ZVDD

AGPIO130

DEVSLP_HDD

DEVSLP_SSD

CLK_PCIE_LAN_C

CLK_PCIE_LAN#_C

CLK_PCIE_WLAN_C

CLK_PCIE_WLAN#_C

CLK_PCIE_SSD_C

CLK_PCIE_SSD#_C

CLK:Not connected to any test points.

R403

1M_1%_4

R495 33_5%_ 4

TP63

48M_X1

48M_X2

LPCCLK0

LPCCLK1

LPC_RST#_R

LPC_CLKRUN#_R

SIO_EXT_SMI#

BA10

AY10

AY12

BA12

AU11

AP11

AY30

AV31

AU31

AU27

BA25

BA24

AY24

BA26

AY28

AY25

AY23

AY27

AY26

BA27

AV27

AY9

BA9

BA8

AY8

H2

H1

M2

M1

L2

L1

K2

K1

J2

J1

F2

F1

AC1

AA8

U19E

SATA_TX0P

SATA_TX0N

SATA_RX0N

SATA_RX0P

VDDP_S0

SATA_TX1P

SATA_TX1N

SATA_RX1N

SATA_RX1P

SATA_ZVSS

SATA_ZVDDP

SATA_ACT_L/AGPIO130

DEVSLP0/EGPIO67

DEVSLP1/EGPIO70

GFX_CLKP

GFX_CLKN

GPP_CLK0P

GPP_CLK0N

GPP_CLK1P

VDDP_S0

GPP_CLK1N

GPP_CLK2P

GPP_CLK2N

GPP_CLK3P

GPP_CLK3N

X48M_X1

VDDP_S5

X48M_X2

X25M_48M_OSC

LPCCLK0/EGPIO74

LPCCLK1/EGPIO75

LFRAME_L

LAD0

LAD1

LAD2

LAD3

LPC_RST_L

LPC_CLKRUN_L/AGPIO88

LPC_PD_L/AGPIO21

LPC_PME_L/AGPIO22

LPC_SMI_L/AGPIO86

SERIRQ/AGPIO87

3V_S0

3V_S0

CLK/SATA/USB/SPI/LPC

3V_S0

3V_S5

3V_S0

3V_S5

3V_S5

S5

3V_S0

3V_S5

1.8V_S0

SPI_HOLD_L/ESPI_DAT3/EGPIO133

3V_S0

3V_S0

ESPI_RESET_L/KBRST_L/AGPIO129

3V_S0

1.8V_S0

USBCLK/25M_48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

3V_S5

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

VDDP_S0

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

SPI_CLK/ESPI_CLK/EGPIO117

SPI_DO/ESPI_DAT0/EGPIO121

SPI_DI/ESPI_DAT1/EGPIO120

SPI_WP_L/ESPI_DAT2/EGPIO122

SPI_CS1_L/EGPIO118

SPI_TPM_CS_L/AGPIO76

ESPI_ALERT_L/LDRQ0_L

SPI_CS2_L/ESPI_CS_L/EGPIO119

AL8

AN7

AW1

AW2

AV1

AV2

AU1

AU2

AT1

AT2

AR1

AR2

AP1

AP2

AN1

AN2

AM1

AM2

W4

W5

T1

T2

V2

V1

R1

R2

W2

W1

P1

P2

Y2

Y1

AY17

AY20

BA17

BA18

BA20

AY21

BA21

AY18

BA30

AY19

USB_ZVSS

USB5

USB5#

USBSS_CALP

USBSS_CALN

SPI_CLK

SPI_SI

SPI_SO

SPI_HOLD#

SPI_WP

SPI_CS#

AGPIO76

EGPIO119

R34 11.8K_1%_4

USB0 [21]

USB0# [21]

USB1 [21]

USB1# [21]

USB2 [17]

USB2# [17]

USB3 [11]

USB3# [11]

USB4 [20]

USB4# [20]

TP54

TP57

USB6 [21]

USB6# [21]

USB7 [15]

USB7# [15]

R30 1K_1%_4

R31 1K_1%_4

USB30_TX0 [20]

USB30_TX0# [20]

USB30_RX0 [20]

USB30_RX0# [20 ]

USB30_TX1 [20]

USB30_TX1# [20]

USB30_RX1 [20]

USB30_RX1# [20 ]

USB30_TX2 [21]

USB30_TX2# [21]

USB30_RX2 [21]

USB30_RX2# [21 ]

TP58

SIO_RCIN# [24]

USB2.0/DB

USB2.0/DB

BT

CCD

Type-C

AMD ST4 U2/U3 pair

U2P4_U3P0

U2P5_U3P1

Type-C

U2P6_U3P2

USB3.0

ODD

VDDP_0.95V_S5

Type-C

Type-C

USB3.0

R453 10K_1 %_4

R445 10K_1 %_4

SPI_CS# SPI_CS_A

R518 33_5 %_4

SPI_CLK

C375 *22p/50V_4

VDD_18

R479 33_5 %_4

SPI EMI

SPI_SI

R478 33_5 %_4

SPI_SO

R517 33_5 %_4

R516 10K_1 %_4

SPI_WP SPI_WP_R

R515 *short_4

SP@ socket P/N: DG008000011 only for A-TEST

TYP13

1.8V

VDD_18

R519

10K_1%_4

SPI_SCK_A

SPI_SDI_A

SPI_SDO_A

SPI ROM

C370 33p/50V_4

C367 *15p/50V_4

C378 15p/50V_4

20160205_EMI

20170104_EMI modunt CLK_LPC_DEBUG 33pF

TP74

TP68

TP67

TP73

TP71

Vender Size Quanta P/N

WND

8M

GGD

8M

EON

8M

CLK_LPC_DEBUG

PCLK_TPM

CLK_PCI_EC

06

VDD_18

R480

C374

10K_1%_4

U21

1

CS

VCC

6

CLK

5

DI

2

DO

HOLD

3

WP

GND

SP@W25Q64FW SSIG

BIOS every pin need add TP2675(First)/TP2650 for ICT test

test pad must place in TOP side

TP66

8

SPI_HOLD#

TP65

7

4

Vender P/N

AKE5EZN0N00

W25Q64FWSSIG

GD25LQ64CSIGRAKE5EG-0Q00

0.1u/16V_4

STRAPS PINS

LPCCLK0

LPCCLK1

LPC_LFRAME#

RTC_CLK[5]

GEVENT2#[5]

SYS_RST#[5]

AGPIO11[5]

R484

*10K_1%_4

R485

2K_1%_4

R473

10K_1%_4

R472

*2K_1%_4

R466

10K_1%_4

R465

*2K_1%_4

R20

10K_1%_4

R18

*2K_1%_4

SP@AMD_SR_FT4

R393

10K_1%_4

R394

*2K_1%_4

R381

10K_1%_4

R409

*2K_1%_4

+3V_S5+3V_S5+3V_S5+3V+3V+3V +3V_S5

R396

10K_1%_4

R395

*2K_1%_4

LPC_CLK0 LFRAME#

BOOT Fail Timer

PU

ENABLE

LPC_CLK1

Use 48Mhz crystal clock

and generate both internal

and external clocks

DEFAULT

PD

BOOT Fail Timer

DISABLE

DEFAULT

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

SPI ROM

DEFAULT

LPC ROM

BLINK/USB_OC7_L/AGPIO11

FP4 PU, FT4 DNI

2016/11/30 AMD :BLINK is not implemented at design

follow FP4 PU OK

Int pull-up

AGPIO11(BLINK)

LDT_RST#/LDT_PW RGD

output to APU

RTC_CLK

Coin battery

is on board.

Int pull-up

GEVENT2# (AGPIO3)

CZ-L

1.8V SPI ROM

TYP13

Enhanced Reset logic

(for quicker S5 resume)

Int pull-upInt pull-up

SYS_RST#

normal reset mo de

DEFAULT DEFAULT DEFAULT DEFAULT

Coin battery

isn't on board.

3.3V SPI ROM

DEFAULT

Default to

traditional res et logic

short reset mod e

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

LDT_RST#/LDT_PW RGD

output to Pads

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

FT4 SATA/USB/LPC/SPI/eSPI(5/7)

FT4 SATA/USB/LPC/SPI/eSPI(5/7)

FT4 SATA/USB/LPC/SPI/eSPI(5/7)

ZAS

ZAS

ZAS

6 35

6 35

6 35

1A

1A

1A

(CPU)

CRB:22u*9, 1u*2, 180p*X1

CL: 22u*9, 1u*3,

CRB:22u*7, 1u*1, 180p*X1

CL: 22u*7, 1u*2

CRB:22u*1, 1u*4

CL: 10u*1, 1u*2, 1n*2

CRB:22u*1, 1u*3

CL: 10u*1, 1u*1, 1n*1

CRB:22u*2, 1u*8, 180p*1

CL: 22u*5, 10u*2, 1n*4

+1.2VSUS

C111

22u/6.3V_6

BU BU BU BU BU BU

C86

180p/50V_4

VDDCR_FCH_S5

R26 *0_5%_4

C72

22u/6.3V_6

VDDCR_FCH_ALW

C77

22u/6.3V_6

BU BU BU BU BU

C59

10u/6.3V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDIO AND VSS SPLIT

C152

0.22u/10V_4

2x0.22UF (0402)+2x180PF(0402)

C153

0.22u/10V_4

C71

10u/6.3V_4

C99

180p/50V_4

Place under APU

C96

22u/6.3V_6

C98

22u/6.3V_6

C80

22u/6.3V_6

C94

22u/6.3V_6

Place under APU

C84

1u/6.3V_4

C87

1u/6.3V_4

C85

1u/6.3V_4

C95

22u/6.3V_6

Place under APU

C63

22u/6.3V_6

C47

22u/6.3V_6

BU BU BU BU BU

C61

180p/50V_4

BU BU BU BU

C16

10u/6.3V_4

C19

1u/6.3V_4

VDDP_0.95V_S5

C46

22u/6.3V_6

C64

1u/6.3V_4

C20

1u/6.3V_4

BUBU

R42 *short_6

C79

22u/6.3V_6

Place under APU

C69

1u/6.3V_4

VDDCR_FCH_ALW

C18

1000p/50V_4

VDDP_S5

C37

10u/6.3V_4

VDDP_0.95V

Place under APU

C76

22u/6.3V_6

C70

1000p/50V_4

C103

180p/50V_4

C78

22u/6.3V_6

C60

1000p/50V_4

CLR_CMOS[24]

For EC reset RTC

C68

22u/6.3V_6

C39

1000p/50V_4

C62

1000p/50V_4

C21

*0.1u/16V_4

R28

*10_5%_6

R589

100K_1%_4

2

+1.2VSUS

C100

22u/6.3V_6

C102

22u/6.3V_6

VDDCR_CPU

C53

22u/6.3V_6

C65

22u/6.3V_6

C17

1000p/50V_4

C31

1u/6.3V_4

BU

+1.5V_RTC_RST#

3

Q27

2N7002K

1

C106

22u/6.3V_6

BUBUBUBUBUBUBU

C82

22u/6.3V_6

C30

1000p/50V_4

VDDIO_AZ

C22

0.22u/10V_4

BU

20MIL

C423

1u/6.3V_4

U19F

J35

VDDIO_MEM_S3_1

L32

VDDIO_MEM_S3_2

L37

VDDIO_MEM_S3_3

N35

VDDIO_MEM_S3_4

R37

VDDIO_MEM_S3_5

U32

VDDIO_MEM_S3_6

U35

VDDIO_MEM_S3_7

W32

VDDIO_MEM_S3_8

W37

VDDIO_MEM_S3_9

AA35

VDDIO_MEM_S3_10

AC32

VDDIO_MEM_S3_11

AC37

VDDIO_MEM_S3_12

AE32

VDDIO_MEM_S3_13

AE35

VDDIO_MEM_S3_14

AG32

VDDIO_MEM_S3_15

AG37

VDDIO_MEM_S3_16

AJ32

VDDIO_MEM_S3_17

AJ35

VDDIO_MEM_S3_18

AL32

VDDIO_MEM_S3_19

AL37

VDDIO_MEM_S3_20

AR35

VDDIO_MEM_S3_21

K21

VDDCR_CPU_1

K23

VDDCR_CPU_2

K25

VDDCR_CPU_3

K27

VDDCR_CPU_4

K29

VDDCR_CPU_5

K31

VDDCR_CPU_6

N21

VDDCR_CPU_7

N23

VDDCR_CPU_8

N25

VDDCR_CPU_9

N27

VDDCR_CPU_10

N29

VDDCR_CPU_11

N31

VDDCR_CPU_12

U23

VDDCR_CPU_13

U25

VDDCR_CPU_14

U27

VDDCR_CPU_15

U29

VDDCR_CPU_16

U31

VDDCR_CPU_17

AA25

VDDCR_CPU_18

AA27

VDDCR_CPU_19

AA29

VDDCR_CPU_20

AA31

VDDCR_CPU_21

AR4

VDDCR_FCH_S5_1

AR5

VDDCR_FCH_S5_2

AR7

VDDCR_FCH_S5_3

AU7

VDDCR_FCH_S5_4

AJ11

VDDP_S5_1

AL11

VDDP_S5_2

AL13

VDDP_S5_3

AJ21

VDDP_1

AJ23

VDDP_2

AJ25

VDDP_3

AJ27

VDDP_4

AL23

VDDP_5

AL25

VDDP_6

AL27

VDDP_7

AL29

VDDP_8

AM11

VDDBT_RTC_G

AM13

VDDIO_AUDIO

SP@AMD_SR_FT4

R572 1K_1%_4

12

G1

*SHORT_PAD

POWER

1.9A

29A

0.4A

0.8A 1.5A

0.5A

0.2A

7A

0.2A

0.2A

20MIL

+1.5V_RTC

+5V_S5

R347 4.7K_5%_4

R337

68.1K_1%_4

R345

150K_1%_4

24A

VDDCR_NB

E9

VDDCR_NB_1

E11

VDDCR_NB_2

E13

VDDCR_NB_3

E15

VDDCR_NB_4

E17

VDDCR_NB_5

E19

VDDCR_NB_6

G7

VDDCR_NB_7

J7

VDDCR_NB_8

K11

VDDCR_NB_9

K13

VDDCR_NB_10

K15

VDDCR_NB_11

K17

VDDCR_NB_12

K19

VDDCR_NB_13

L7

VDDCR_NB_14

L10

VDDCR_NB_15

L15

VDDCR_NB_16

L17

VDDCR_NB_17

N7

VDDCR_NB_18

N11

VDDCR_NB_19

N13

VDDCR_NB_20

N15

VDDCR_NB_21

N17

VDDCR_NB_22

N19

VDDCR_NB_23

R7

VDDCR_NB_24

U7

VDDCR_NB_25

U11

VDDCR_NB_26

U13

VDDCR_NB_27

U15

VDDCR_NB_28

U17

VDDCR_NB_29

U19

VDDCR_NB_30

U21

VDDCR_NB_31

W7

VDDCR_NB_32

AA11

VDDCR_NB_33

AA13

VDDCR_NB_34

AA15

VDDCR_NB_35

AA17

VDDCR_NB_36

AA19

VDDCR_NB_37

AA21

VDDCR_NB_38

AA23

VDDCR_NB_39

AE11

VDDCR_NB_40

AE13

VDDCR_NB_41

AE15

VDDCR_NB_42

AE17

VDDCR_NB_43

AE19

VDDCR_NB_44

AE21

VDDCR_NB_45

AE23

VDDCR_NB_46

AE25

VDDCR_NB_47

AE27

VDDCR_NB_48

AE29

VDDCR_NB_49

AE31

VDDCR_NB_50

VDD_18

AJ15

VDD_18_1

AL17

VDD_18_2

VDD_18_S5_1

VDD_18_S5_2

VDD_33_1

VDD_33_2

VDD_33_S5_1

VDD_33_S5_2

1

2

Q29

AP2138N-1.5TRG1

VDD_18_S5C

AJ13

AL15

AJ19

3VC

AL21

3V_S5C VDDIO_AZ

AJ17

AL19

VOUT

GND

+VCCRTC_4 +VCCRTC_3

+VCCRTC_5

20MIL

3

VIN

R348 4.7K_5%_4

Charge function

Place under APU

VDD_18_S5C

3VC

3V_S5C

C437

1u/6.3V_4

C54

22u/6.3V_6

BU

C45

22u/6.3V_6

BU

C41

1000p/50V_4

C29

1000p/50V_4

C75

1000p/50V_4

C57

1000p/50V_4

C26

1000p/50V_4

D36

BAT54CW

13

Q15PMST3904

2

+VCCRTC_2

C43

22u/6.3V_6

BU

Place under APU

C33

22u/6.3V_6

BU

+3VRTC

20MIL20MIL

20MIL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

C11

22u/6.3V_6

BU

C12

22u/6.3V_6

BU

C42

1u/6.3V_4

BU

R37 *short_4

C28

1u/6.3V_4

BU

R77 *short_4

C74

1u/6.3V_4

BU

R60 *short_4

C56

1u/6.3V_4

BU

R33 *short_4

C25

1000p/50V_4

+3VPCU

20MIL

R339

1K_1%_4

20MIL

+BAT

CN12

12

AAA-BAT-046-K03

+ -

34

Friday, March 24, 2017

Friday, March 24, 2017

Friday, March 24, 2017

C44

22u/6.3V_6

BU

C34

22u/6.3V_6

C38

22u/6.3V_6

BU BU

C13

22u/6.3V_6

C81

22u/6.3V_6

C23

1u/6.3V_4

BU BU

VDD_18

C40

10u/6.3V_4

C27

10u/6.3V_4

C73

10u/6.3V_4

C55

10u/6.3V_4

C24

1u/6.3V_4

BU

CRB:22u*1, 1u*X2

CL: 10u*1, 1u*1, 1n*1

VDD_18_S5

CRB:22u*1, 1u*X2

CL: 10u*1, 1u*1, 1n*1

+3V

CRB:22u*1, 1u*X2

CL: 10u*1, 1u*1, 1n*1

+3V_S5

CRB:22u*1, 1u*X2

CL: 10u*1, 1u*1, 1n*1

+1.5V

CRB:22u*11, 1u*X1

CL: 1u*1, 1n*2

RTC (RTC)

Charge function

1220 charge function

ZHP RTC BATTERY

AHL03001031

AHL03001057

ZHP RTC connector

DFHS02FS032

DFHS02FS083

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

FT4 POWER(6/7)

FT4 POWER(6/7)

FT4 POWER(6/7)

ZAS

ZAS

ZAS

07

CRB:22u*11, 180p*X1

CL: 22u*11, 1u*1

C32

180p/50V_4

BU BU

7 35

7 35

7 35

1A

1A

1A

(CPU)

08

AJ31

R19

H23

A13

A18

A23

A32

A35

A39

B13

B32

B39

C11

C13

C15

C17

C19

C21

C23

C25

C27

C29

C31

C33

C35

C37

C39

C41

E21

E25

E29

E35

E38

E39

G11

G13

G23

G27

G31

G35

G37

G39

G41

J39

U19G

A2

A8

B8

C3

C5

C7

C9

E1

E2

E3

G1

G2

G3

J3

J8

L3

L8

VSS_215

VSS_214

VSS_213

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

GND

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

L13

L19

L21

L23

L25

L27

L29

L31

L39

L41

N1

N2

N3

N39

R3

R11

R13

R15

R17

R21

R23

R25

R27

R29

R31

R39

R41

U1

U2

U3

U10

U39

W3

W10

W11

W13

W15

W17

W19

W21

W23

W25

W27

W29

W31

W39

W41

AA1

AA2

AA3

AA5

AA10

AA39

AC3

AC7

AC10

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AC25

AC27

AC29

AC31

AC38

AC39

AC41

AE3

AE5

AE10

AE39

AG3

AG7

AG10

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AG25

AG27

AG29

AG31

AG39

AG41

AJ3

AJ5

AJ10

AJ29

AJ39

AL1

AL2

AL3

AL7

AL10

AL31

AL39

AL41

AM25

AM27

AM29

AM31

AN3

AN5

AN39

AR3

AR11

AR19

AR23

AR27

AR31

AR39

AR41

AU3

AU9

AU21

AU25

AU29

U19H

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

GND

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

AU39

AW3

AW5

AW7

AW9

AW11

AW13

AW15

AW17

AW19

AW21

AW23

AW25

AW27

AW29

AW31

AW33

AW35

AW37

AW39

AW41

AY1

AY11

BA7

BA11

BA15

BA19

BA23

BA31

BA35

BA39

SP@AMD_SR_FT4

SP@AMD_SR_FT4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

PROJECT :

FT4 GND(7/7)

FT4 GND(7/7)

FT4 GND(7/7)

ZAS

ZAS

ZAS

8 35

8 35

8 35

1A

1A

1A

5

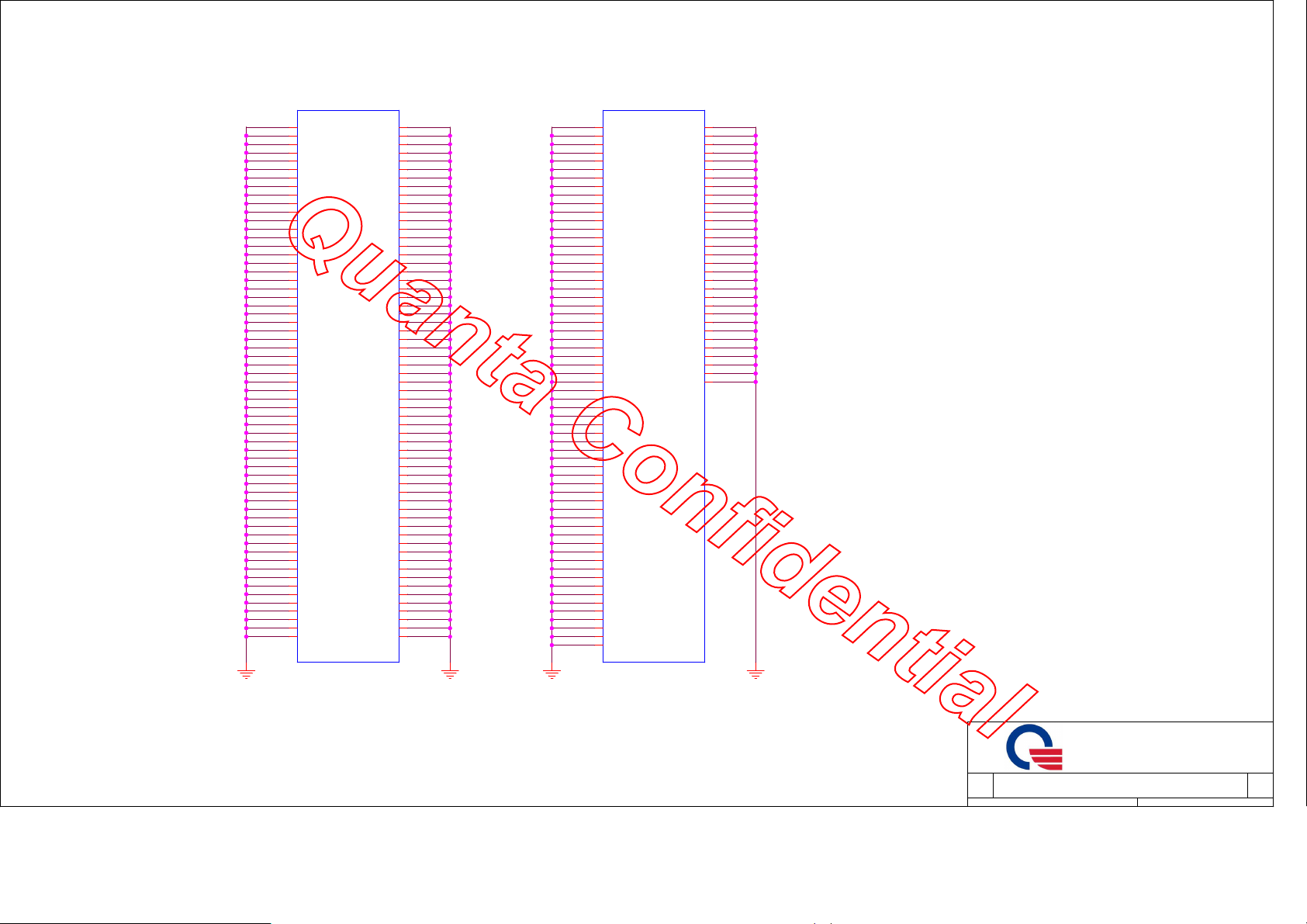

SODIMM (SDM)

Address A0

D D

+1.2VSUS

R169 1K_1%_4

R144 1K_1%_4

M_A_ALERT#

M_A_EVENT#

EXT-11723:ALERT# PU need mount

C C

B B

M_A_A[13:0][3,10]

M_A_WE#[3,10]

M_A_CAS#[3,10]

M_A_RAS#[3,10]

M_A_ACT#[3,10]

R101 *short_4

M_A_EVENT#[3]

M_A_RST#[3,10]

M_A_BANK0[3,10]

M_A_BANK1[3,10]

M_A_BG0[3,10]

M_A_BG1[3,10]

M_A0_CS#0[3]

M_A0_CS#1[3]

M_A0_CKE0[3]

M_A0_CKE1[3]

M_A0_CLK0[3]

M_A0_CLK0#[3]

M_A0_CLK1[3]

M_A0_CLK1#[3]

M_A0_ODT0[3]

M_A0_ODT1[3]

CLK_SCLK[5,19]

CLK_SDATA[5,19]

M_A_DM[7..0][3,10]

R201 *short_4

4

SA2

JDIM1A

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10/AP

120

A11

119

A12

158

A13

151

A14/WE#

156

A15/CAS#

152

A16/RAS#

162

CS2#/C0

165

CS3#/C1

114

ACT#

143

PARITY

116

ALERT#

134

EVENT#

108

RESET#

150

BA0

145

BA1

115

BG0

113

BG1

149

CS0#

157

CS1#

109

CKE0

110

CKE1

137

CK0

139

CK0#

138

CK1

140

CK1#

155

ODT0

161

ODT1

253

SCL

254

SDA

256

SA0

260

SA1

166

SA2

92

CB0

91

CB1

101

CB2

105

CB3

88

CB4

87

CB5

100

CB6

104

CB7

12

DM0

33

DM1

54

DM2

75

DM3

178

DM4

199

DM5

220

DM6

241

DM7

96

DBI8#

D4AS0-26001-1P52

8

DQ0

7

DQ1

20

DQ2

21

DQ3

4

DQ4

3

DQ5

16

DQ6

17

DQ7

28

DQ8

29

DQ9

41

DQ10

42

DQ11

24

DQ12

25

DQ13

38

DQ14

37

DQ15

50

DQ16

49

DQ17

62

DQ18

63

DQ19

46

DQ20

45

DQ21

58

DQ22

59

DQ23

70

DQ24

71

DQ25

83

DQ26

84

DQ27

66

DQ28

67

DQ29

79

DQ30

80

DQ31

174

DQ32

173

DQ33

187

DQ34

186

DQ35

170

DQ36

169

DQ37

183

DQ38

182

DQ39

195

DQ40

194

DQ41

207

DQ42

208

DQ43

191

DQ44

190

DQ45

203

DQ46

204

DQ47

216

DQ48

215

(260P)

DDR4 SODIMM 260 PIN

DQ49

228

DQ50

229

DQ51

211

DQ52

212

DQ53

224

DQ54

225

DQ55

237

DQ56

236

DQ57

249

DQ58

250

DQ59

232

DQ60

233

DQ61

245

DQ62

246

DQ63

13

DQS0

34

DQS1

55

DQS2

76

DQS3

179

DQS4

200

DQS5

221

DQS6

242

DQS7

97

DQS8

11

DQS#0

32

DQS#1

53

DQS#2

74

DQS#3

177

DQS#4

198

DQS#5

219

DQS#6

240

DQS#7

95

DQS#8

M_A_DQ0

M_A_DQ1

M_A_DQ3

M_A_DQ2

M_A_DQ4

M_A_DQ5

M_A_DQ7

M_A_DQ6

M_A_DQ8

M_A_DQ9

M_A_DQ15

M_A_DQ14

M_A_DQ12

M_A_DQ13

M_A_DQ11

M_A_DQ10

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ23

M_A_DQ22

M_A_DQ25

M_A_DQ29

M_A_DQ26

M_A_DQ27

M_A_DQ24

M_A_DQ28

M_A_DQ31

M_A_DQ30

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ39

M_A_DQ32

M_A_DQ33

M_A_DQ38

M_A_DQ34

M_A_DQ41

M_A_DQ40

M_A_DQ47

M_A_DQ43

M_A_DQ45

M_A_DQ44

M_A_DQ46

M_A_DQ42

M_A_DQ48

M_A_DQ49

M_A_DQ51

M_A_DQ50

M_A_DQ53

M_A_DQ52

M_A_DQ55

M_A_DQ54

M_A_DQ60

M_A_DQ56

M_A_DQ59

M_A_DQ58

M_A_DQ61

M_A_DQ57

M_A_DQ63

M_A_DQ62

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

TP76

TP75

M_A_PARITY

M_A_ALERT#

M_A_EVENT#

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7 M_A_DQS#7

3

M_A_DQ[63:0]

0-7

8-15

16-23

24-31

33-39

40-47

48-55

56-63

M_A_DQS[7:0] [3,10]

M_A_DQS#[7:0] [3,10]

2250mA

+1.2VSUS

2

JDIM1B

111

VDD1

112

VDD2

117

VDD3

118

VDD4

123

VDD5

124

VDD6

129

VDD7

130

VDD8

135

VDD9

136

VDD10

141

VDD11

142

VDD12

147

VDD13

148

VDD14

153

VDD15

154

VDD16

159

VDD17

160

VDD18

163

VDD19

1

VSS1

5

VSS2

9

VSS3

15

VSS4

19

VSS5

23

VSS6

27

VSS7

31

VSS8

35

VSS9

39

VSS10

43

VSS11

47

VSS12

51

VSS13

57

VSS14

61

VSS15

65

VSS16

69

VSS17

73

VSS18

77

VSS19

81

VSS20

85

VSS21

89

VSS22

93

VSS23

99

VSS24

103

VSS25

107

VSS26

167

VSS27

171

VSS28

175

VSS29

181

VSS30

185

VSS31

189

VSS32

193

VSS33

197

VSS34

201

VSS35

205

VSS36

209

VSS37

213

VSS38

217

VSS39

223

VSS40

227

VSS41

231

VSS42

235

VSS43

239

VSS44

243

VSS45

247

VSS46

251

VSS47

263

263

264

264

D4AS0-26001-1P52

1

+3V

09

R92

*short_4

255

257

259

258

164

2

6

10

14

18

22

26

30

36

40

44

48

52

56

60

64

68

72

78

82

86

90

94

98

102

106

168

172

176

180

184

188

192

196

202

206

210

214

218

222

226

230

234

238

244

248

252

261

262

C108 1u/6.3V_4

C127 1u/6.3V_4

M_A0_VREFCA

C149

1000p/50V_4

+2.5VSUS

+SMDDR_VTT

0.5A

0.6A

VDDSPD

VPP1

VPP2

VTT

VREFCA

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

(260P)

DDR4 SODIMM 260 PIN

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

GND#1

GND#2

Place these Caps near So-Dimm A

+1.2VSUS

5

C121

0.1u/16V_4

C123

*0.1u/16V_4

C137

0.1u/16V_4

C143

*0.1u/16V_4

C133

0.1u/16V_4

A A

+1.2VSUS

C132

*0.1u/16V_4

C119

0.1u/16V_4

C118

*0.1u/16V_4

C131

0.1u/16V_4

C120

*0.1u/16V_4

C105

0.1u/16V_4

C136

0.1u/16V_4

+SMDDR_VTT

+1.2VSUS

4

C115

180p/50V_4

C144

4.7u/6.3V_4

C129

22u/6.3V_6

C135

0.1u/16V_4

C141

22u/6.3V_6

(+MEM_VPP)

+2.5VSUS

C142

22u/6.3V_6

C117

180p/50V_4

DECOUPLING CAPS

C128

22u/6.3V_6

C114

0.1u/16V_4

C122

22u/6.3V_6

C126

0.1u/16V_4

3

C138

22u/6.3V_6

C124

22u/6.3V_6

From Power Chip (+0.6V)

+SMDDR_VREF

R203 *0_5%_6

3mA

2

+1.2VSUS

R199

1K_1%_4

M_A0_VREFCA

R200

1K_1%_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

Date: Sheet of

Friday, March 24, 2017

C148

0.1u/16V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

DDR4 DIMM CHA0 (STD)

DDR4 DIMM CHA0 (STD)

DDR4 DIMM CHA0 (STD)

1

ZAS

ZAS

ZAS

9 35

9 35

9 35

1A

1A

1A

On board memory(OBM)

Address A2

M_A_DQ[63:0][3,9]

5

4

15ohm Series resistor to DRAM Placed between DIMM

and DRAM at a distance of <10mm from the DIMM.

3

2

1

10

DQ bit swapping is allowed in a byte lane

BYTE7(56-63)

D D

M_A_A[13:0]

M_A_WE#[3,9]

M_A_CAS#[3,9]

M_A_RAS#[3,9]

M_A_BANK0[3,9]

M_A_BANK1[3,9]

M_A_BG0[3,9]

M_A1_CLK0[3]

M_A1_CLK0#[3]

M_A1_CKE0[3]

M_A1_ODT0[3]

C C

M_A_DQS7[3,9]

M_A_DQS6[3,9]

M_A_DQS#7[3,9]

M_A_DQS#6[3,9]

M_A_DM7[3,9]

M_A_DM6[3,9]

B B

CMD

A A

CTL

M_A1_CS#0[3]

R188 15_5%_4

R123 15_5%_4

R189 15_5%_4

R122 15_5%_4

M_A_RST#[3,9]

R216 240_1%_4

DRAM SPEC :TEN is Test Mode Enable

M_A_ACT#[3,9]

R287 SP@0_5%_4

MICRON DDP 16Gb:GND

Other:NC

M_A_BANK0

R267 39_1%_4

M_A_BANK1

R305 39_1%_4

M_A_BG0

R258 39_1%_4

M_A_BG1

R257 DDP@39_1%_4

M_A_A0

R294 39_1%_4

M_A_A1

R295 39_1%_4

M_A_A2

R284 39_1%_4

M_A_A3

R293 39_1%_4

M_A_A4

R291 39_1%_4

M_A_A5

R304 39_1%_4

M_A_A6

R310 39_1%_4

M_A_A7

R303 39_1%_4

M_A_A8

R273 39_1%_4

M_A_A9

R300 39_1%_4

M_A_A10

R221 39_1%_4

M_A_A11

R278 39_1%_4

M_A_A12

R292 39_1%_4

M_A_A13

R302 39_1%_4

M_A_WE#

R219 39_1%_4

M_A_CAS#

R298 39_1%_4

M_A_RAS#

R299 39_1%_4

M_A_ACT#

R250 39_1%_4

M_A1_CS#0

R296 39_1%_4

M_A1_ODT0

R297 39_1%_4

M_A1_CKE0

R234 39_1%_4

U10

M_A1_VREFCA

M1

VREFCA

B1

VPP#B1

R9

VPP#R9

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_DQS7_C

M_A_DQS6_C

M_A_DQS#7_C

M_A_DQS#6_C

M_A_DMC7

M_A_DMC6

M_A1_ZQ0 M_A1_ZQ2

M_A1_ALERT# M_A1_ALERT#

M_A1_PAR M_A1_PAR

t : P

P3

c : N

A0

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC

T8

A13

L2

WE_n/A14

M8

CAS_n/A15

L8

RAS_n/A16

N2

BA0

N8

BA1

M2

BG0

K7

CK_t

K8

CK_c

K2

CKE

K3

ODT

L7

CS

G3

DQSL_t

B7

DQSU_t

F3

DQSL_c

A7

DQSU_c

E7

DML_n/DBIL_n

E2

DMU_n/DBIU_n

P1

RESET_n

F9

ZQ

N9

TEN

P9

ALERT_n

L3

ACT_n

T3

PAR

T7

MIC0 MIC1 MIC2 MIC3

NC

96-BALL

DDR4

SP@DDR4_96P

+SMDDR_VTT

x16(DDP): Stuff

x16(SDP): DNI

M_A_DQC56 M_A_DQ56

G2

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B3

VDD#B9

VDD#D1

VDD#G7

VDD#J1

VDD#J9

VDD#L1

VDD#L9

VDD#R1

VDD#T9

VDDQ#A1

VDDQ#A9

VDDQ#C1

VDDQ#D9

VDDQ#F2

VDDQ#F8

VDDQ#G1

VDDQ#G9

VDDQ#J2

VDDQ#J8

VSS#B2

VSS#E1

VSS#E9

VSS#G8

VSS#K1

VSS#K9

VSS#M9

VSS#N1

VSS#T1

VSSQ#A2

VSSQ#A8

VSSQ#C9

VSSQ#D2

VSSQ#D8

VSSQ#E3

VSSQ#E8

VSSQ#F1

VSSQ#H1

VSSQ#H9

M_A1_CLK0

M_A1_CLK0#

M_A1_ALERT#

EXT-11723:ALERT# PU to +1.2VSUS

M_A1_PAR

M_A_RST#

R187 15_5%_4

M_A_DQC62 M_A_DQ62

F7

R190 15_5%_4

M_A_DQC57 M_A_DQ57

H3

R175 15_5%_4

M_A_DQC58 M_A_DQ58

H7

R191 15_5%_4

M_A_DQC60 M_A_DQ60

R147 15_5%_4

H2

M_A_DQC63

H8

R139 15_5%_4

M_A_DQC61 M_A_DQ61

J3

R194 15_5%_4

M_A_DQC59

J7

R142 15_5%_4

A3

B8

R185 15_5%_4

C3

R182 15_5%_4

C7

R116 15_5%_4

M_A_DQC49

R111 15_5%_4

C2

M_A_DQC54

C8

R128 15_5%_4

M_A_DQC48

D3

R183 15_5%_4

M_A_DQC51

D7

R186 15_5%_4

+1.2VSUS +1.2VSUS +1.2VSUS +1.2VSUS

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

E9 DRAM SPEC

G1

x16(DDP):UZQ

G9

other :GND

J2

240ohm: CS12402FB03 240ohm: CS12402FB03 240ohm: CS12402FB03 240ohm: CS12402FB03

J8

x16(DDP):240ohm

B2

x16(SDP):0ohm

E1

E9

R212 *shortSP@0_5%_4

G1

G8

K1

K9

R243 *shortSDP@0_5%_4R124 15_5%_4

M9

G1A

N1

T1

R242 DDP@0_5%_4

x16(DDP):BG1

x16(SDP):GND

A2

A8

M9 DRAM SPEC

C9

x4/x8/x16(DDP):have BG0 and BG1

D2

x16 :have only BG0

D8

E3

Note

E8

x4/x8 :76 ball

F1

x16/x16(DDP):96 ball

H1

H9

R226 39_1%_4

R223 39_1%_4

R269 1K_1%_4

R306 *short_4

C110 *0.1u/16V_4

CLK_A1_PN

+1.2VSUS

+1.2VSUS

M_A_DQ63

M_A_DQ59

M_A_DQ53M_A_DQC53

M_A_DQ55M_A_DQC55

M_A_DQ52M_A_DQC52

M_A_DQ50M_A_DQC50

M_A_DQ49

M_A_DQ54

M_A_DQ48

M_A_DQ51

M_A_BG1 [3,9]

C194

0.01u/50V_4

M_A_DQS2[3,9]

M_A_DQS3[3,9]

M_A_DQS#2[3,9]

M_A_DQS#3[3,9]

M_A_DM2[3,9]

M_A_DM3[3,9]

R141 15_5%_4

R171 15_5%_4

R140 15_5%_4

R170 15_5%_4

R163 15_5%_4

R131 15_5%_4R184 15_5%_4

R214 240_1%_4

R307 SP@0_5%_4

MICRON DDP 16Gb:GND

Other:NC

+1.2VSUS

C191 0.22u/10V_4

C166 0.22u/10V_4

C190 0.22u/10V_4

C182 0.22u/10V_4

C199 0.22u/10V_4

C161 0.22u/10V_4

C162 0.22u/10V_4

C179 0.22u/10V_4

C160 0.22u/10V_4

C203 0.22u/10V_4

C202 0.22u/10V_4

C164 0.22u/10V_4

C167 0.22u/10V_4

C170 0.22u/10V_4

C180 0.22u/10V_4

C154 0.22u/10V_4

C158 0.22u/10V_4

C165 0.22u/10V_4

C151 0.22u/10V_4

C163 0.22u/10V_4

BYTE6(48-55)

M_A1_VREFCA

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_WE#

M_A_CAS#

M_A_RAS#

M_A_BANK0

M_A_BANK1

M_A_BG0

M_A1_CLK0

M_A1_CLK0#

M_A1_CKE0

M_A1_ODT0

M_A1_CS#0

M_A_DQS2_C

M_A_DQS3_C

M_A_DQS#2_C

M_A_DQS#3_C

M_A_DMC2

M_A_DMC3

M_A_RST#

M_A1_ZQ1

M_A_ACT#

U8

M1

VREFCA

B1

VPP#B1

R9

VPP#R9

P3

A0

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC

T8

A13

L2

WE_n/A14

M8

CAS_n/A15

L8

RAS_n/A16

N2

BA0

N8

BA1

M2

BG0

K7

CK_t

K8

CK_c

K2

CKE

K3

ODT

L7

CS

G3

DQSL_t

B7

DQSU_t

F3

DQSL_c

A7

DQSU_c

E7

DML_n/DBIL_n

E2

DMU_n/DBIU_n

P1

RESET_n

F9

ZQ

N9

TEN

P9

ALERT_n

L3

ACT_n

T3

PAR

T7

NC

SP@DDR4_96P

+SMDDR_VTT

96-BALL

DDR4

+1.2VSUS

+2.5VSUS

t : P

c : N

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B3

VDD#B9

VDD#D1

VDD#G7

VDD#J1

VDD#J9

VDD#L1

VDD#L9

VDD#R1

VDD#T9

VDDQ#A1

VDDQ#A9

VDDQ#C1

VDDQ#D9

VDDQ#F2

VDDQ#F8

VDDQ#G1

VDDQ#G9

VDDQ#J2

VDDQ#J8

VSS#B2

VSS#E1

VSS#E9

VSS#G8

VSS#K1

VSS#K9

VSS#M9

VSS#N1

VSS#T1

VSSQ#A2

VSSQ#A8

VSSQ#C9

VSSQ#D2

VSSQ#D8

VSSQ#E3

VSSQ#E8

VSSQ#F1

VSSQ#H1

VSSQ#H9

C246 0.22u/10V_4

C252 0.22u/10V_4

C232 0.22u/10V_4

C178 0.22u/10V_4

C185 0.22u/10V_4

C177 0.22u/10V_4

C171 0.22u/10V_4

C168 0.22u/10V_4

C169 0.22u/10V_4

C172 0.22u/10V_4

C243 0.22u/10V_4

C245 0.22u/10V_4

C250 0.22u/10V_4

C248 0.22u/10V_4

C157 10u/6.3V_4

C156 10u/6.3V_4

pute cap near every chip.

5

4

BYTE2(16-23)

BYTE3(24-31) BYTE4(32-39)

+SMDDR_VREF

M_A_DQ16

M_A_DQ23M_A_DQC23

M_A_DQ20M_A_DQC20

M_A_DQ19

M_A_DQ21M_A_DQC21

M_A_DQ22M_A_DQC22

M_A_DQ17M_A_DQC17

M_A_DQ18M_A_DQC18

M_A_DQ24

M_A_DQ27M_A_DQC27

M_A_DQ25M_A_DQC25

M_A_DQ31

M_A_DQ29M_A_DQC29

M_A_DQ26M_A_DQC26

M_A_DQ28M_A_DQC28

M_A_DQ30M_A_DQC30

M_A_BG1

R241 *0_5%_6

M_A_DQS5[3,9]

M_A_DQS4[3,9]

M_A_DQS#5[3,9]

M_A_DQS#4[3,9]

M_A_DM5[3,9]

M_A_DM4[3,9]

R173 15_5%_4 R133 15_5%_4

R126 15_5%_4 R198 15_5%_4

R174 15_5%_4

R127 15_5%_4

R120 15_5%_4

R178 15_5%_4

R220 240_1%_4

R289 SP@0_5%_4

MICRON DDP 16Gb:GND

Other:NC

+1.2VSUS

R265

1K_1%_4

R266

1K_1%_4

C210

0.1u/16V_4

M_A1_VREFCA

G2

F7

H3

H7

H2

H8

J3

J7

A3

B8

C3

C7

C2

C8

D3

D7

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

G1

G9

J2

J8

B2

E1

E9