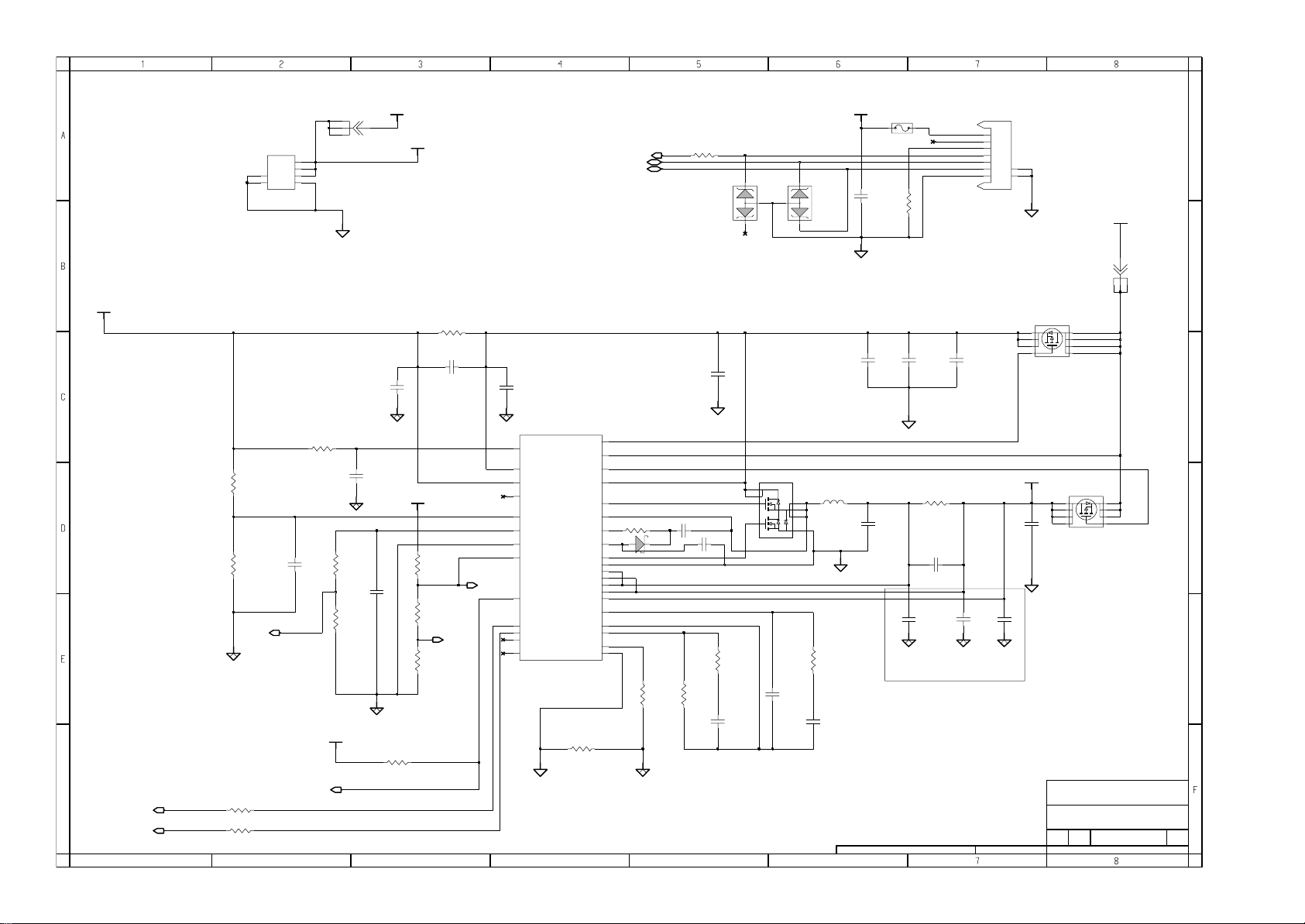

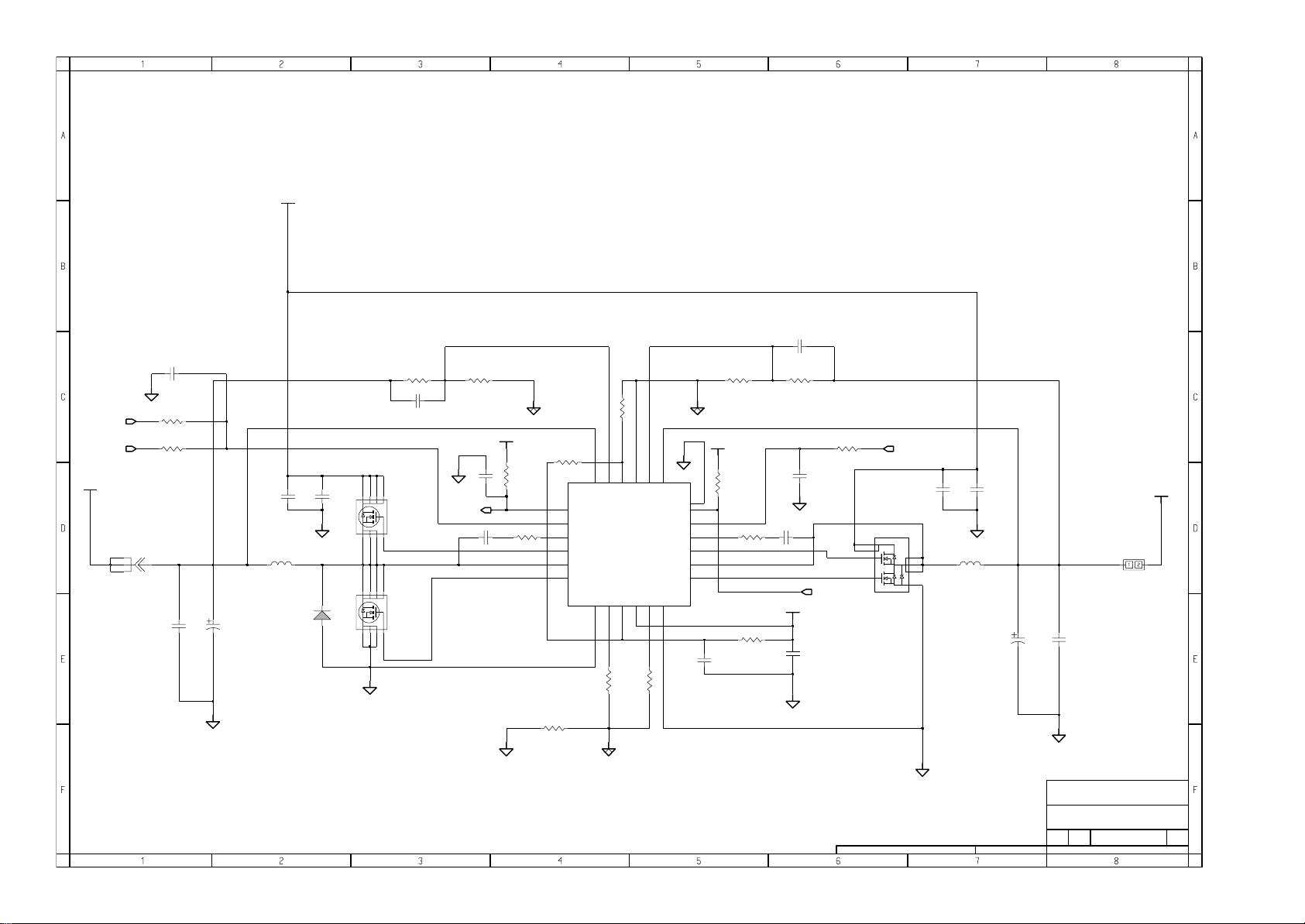

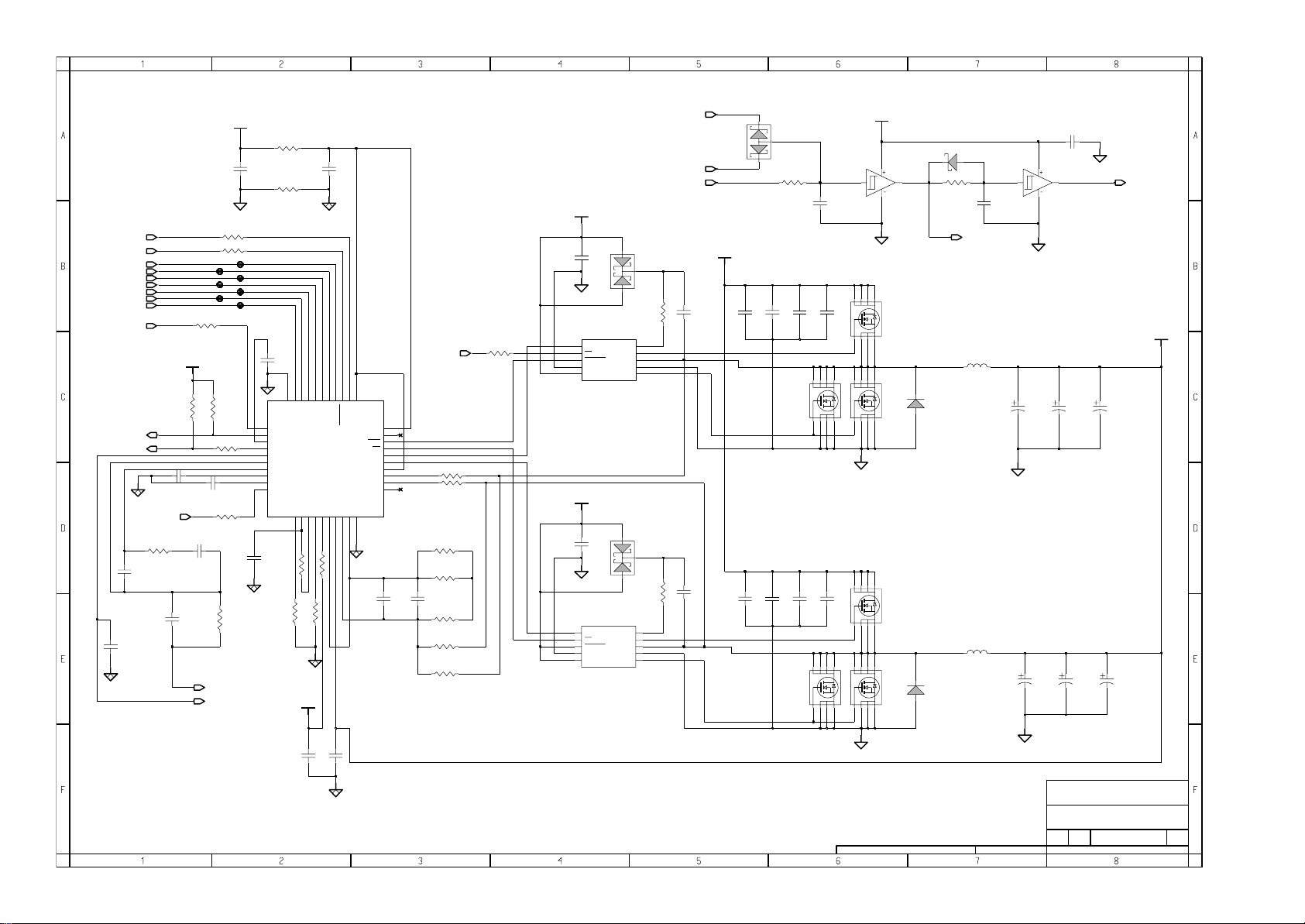

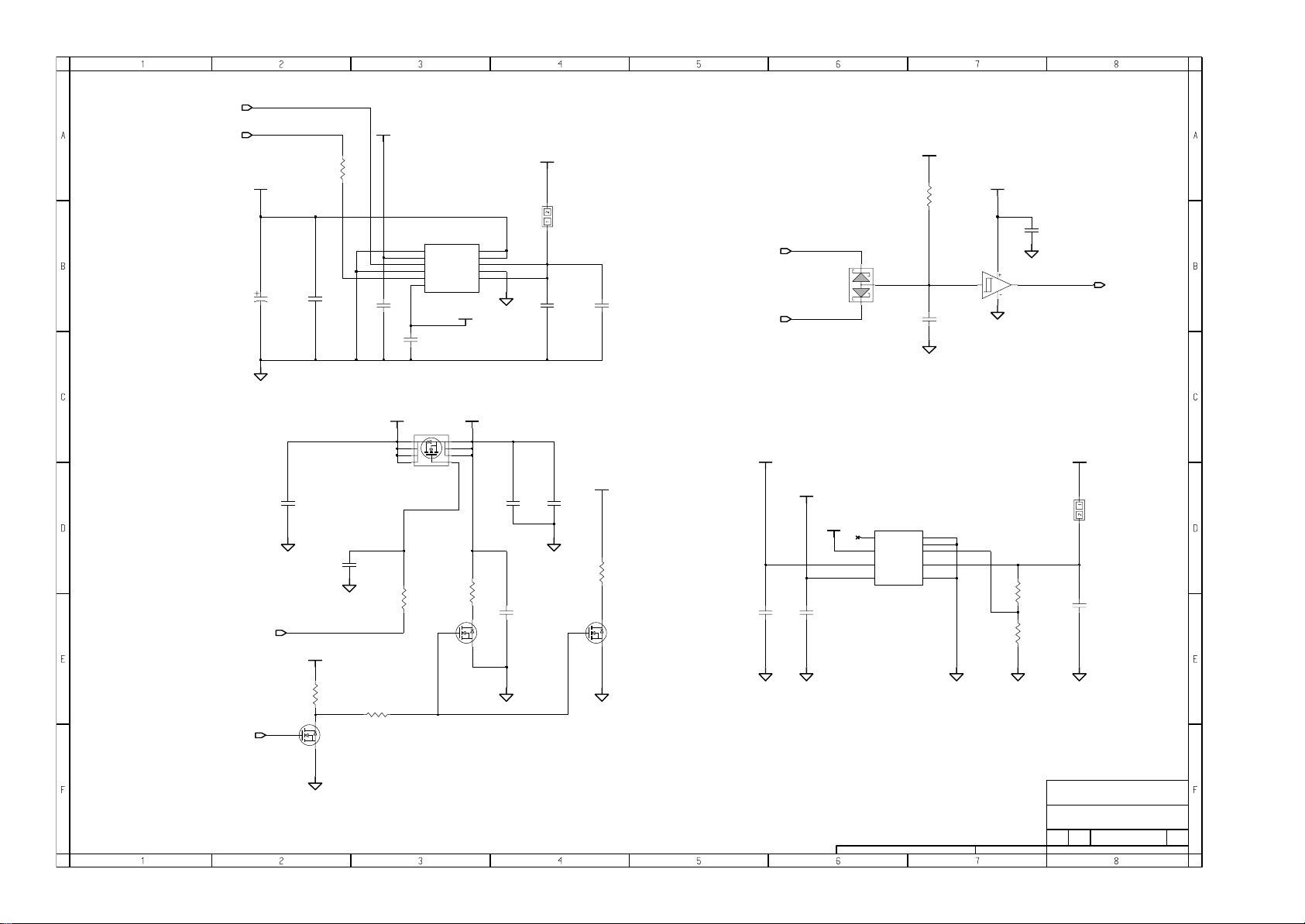

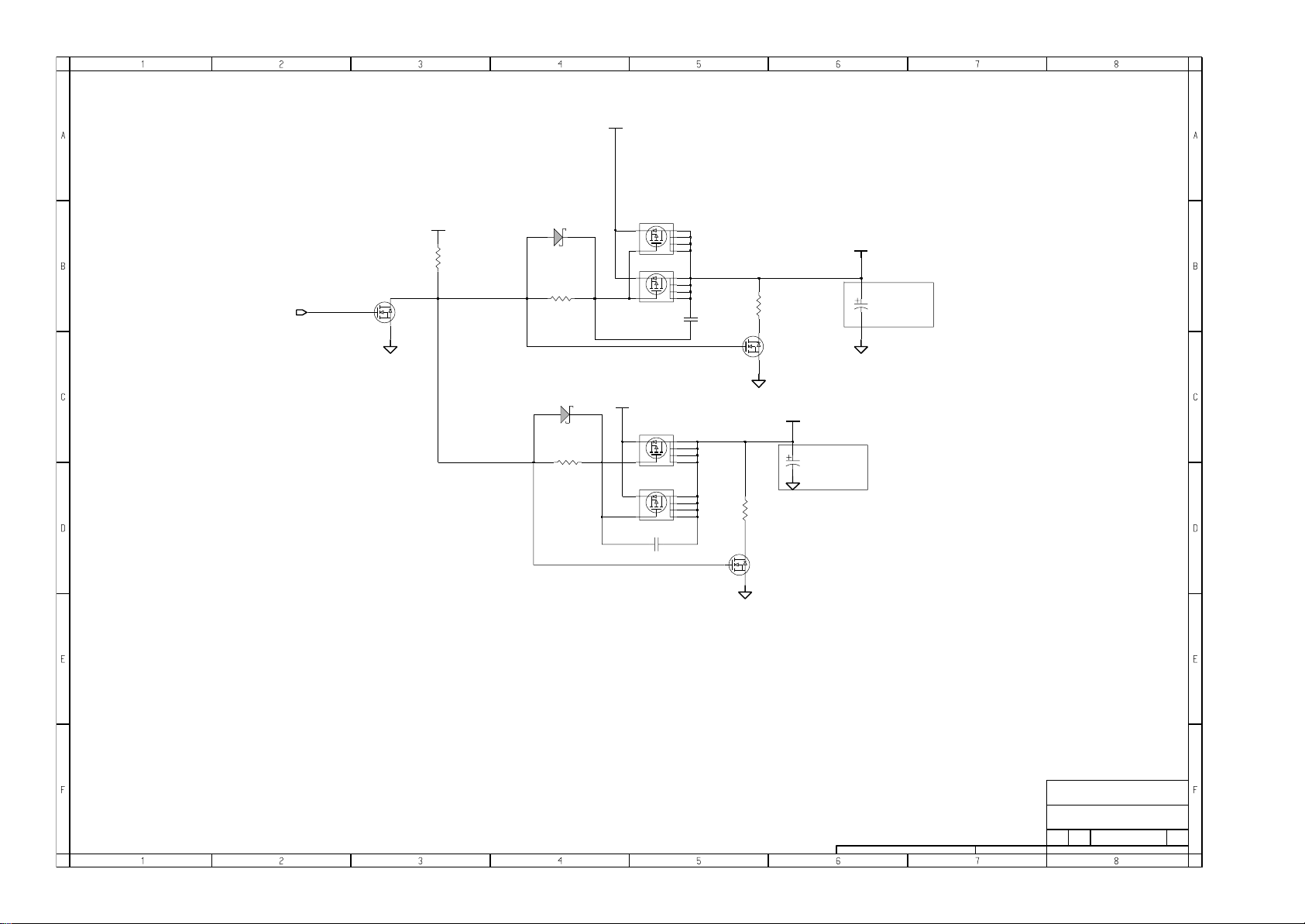

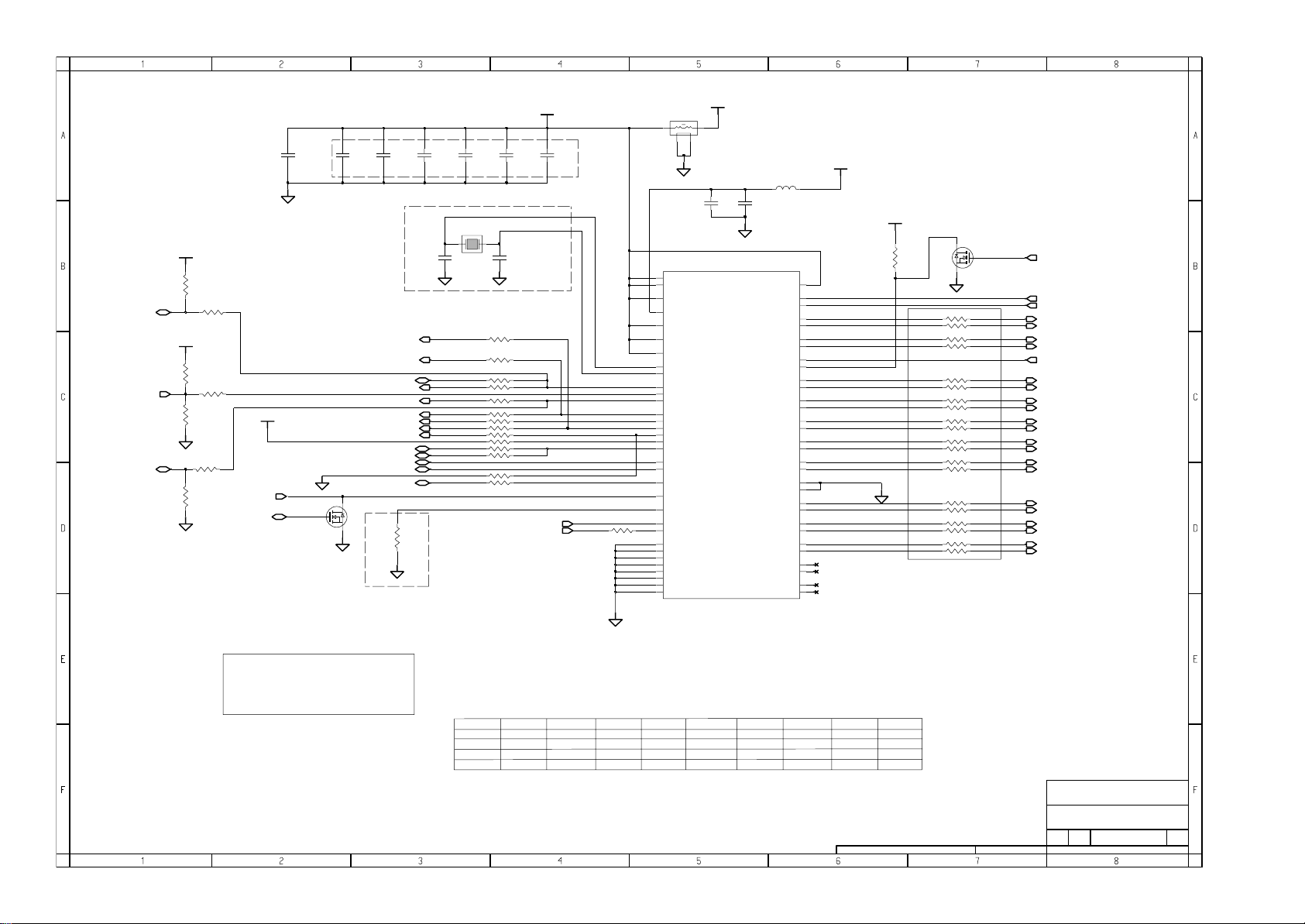

Acer Aspire 9800, Aspire 9810, Aspire 9920 Schematics

Cheela

ES BUILD

2006 0101

DATE

CHANGE NO.

REV

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE =

FILE NAME :

XXXXXXXXXXXX

P/N

EE

3

XXXX-XXXXXX-XX

POWER

DATEDATE

INVENTEC

TITLE

Cheela

CODEVER :

SIZE

A3

CS

SHEET

DOC. NUMBER

165

REV

000Model_No

OF

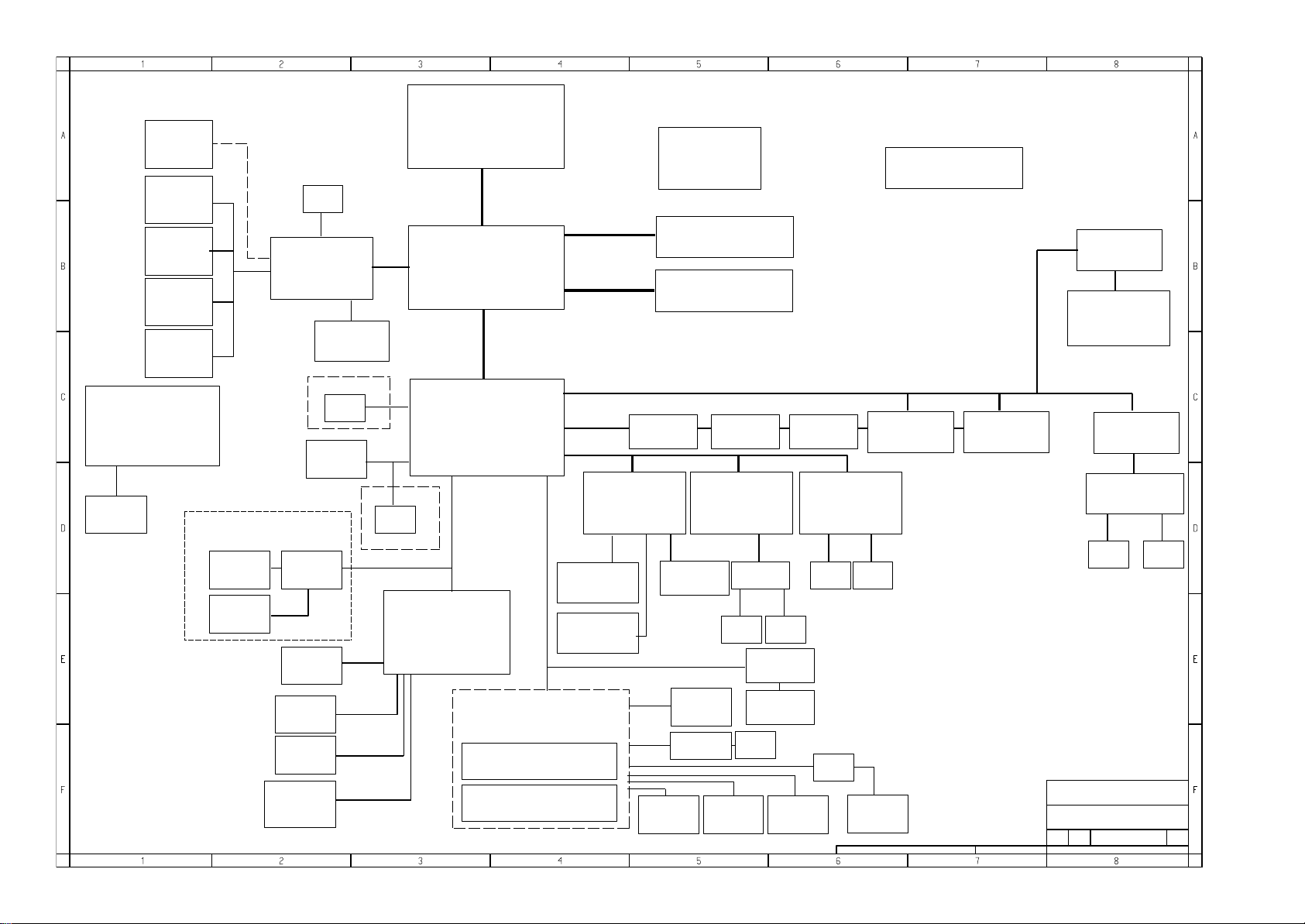

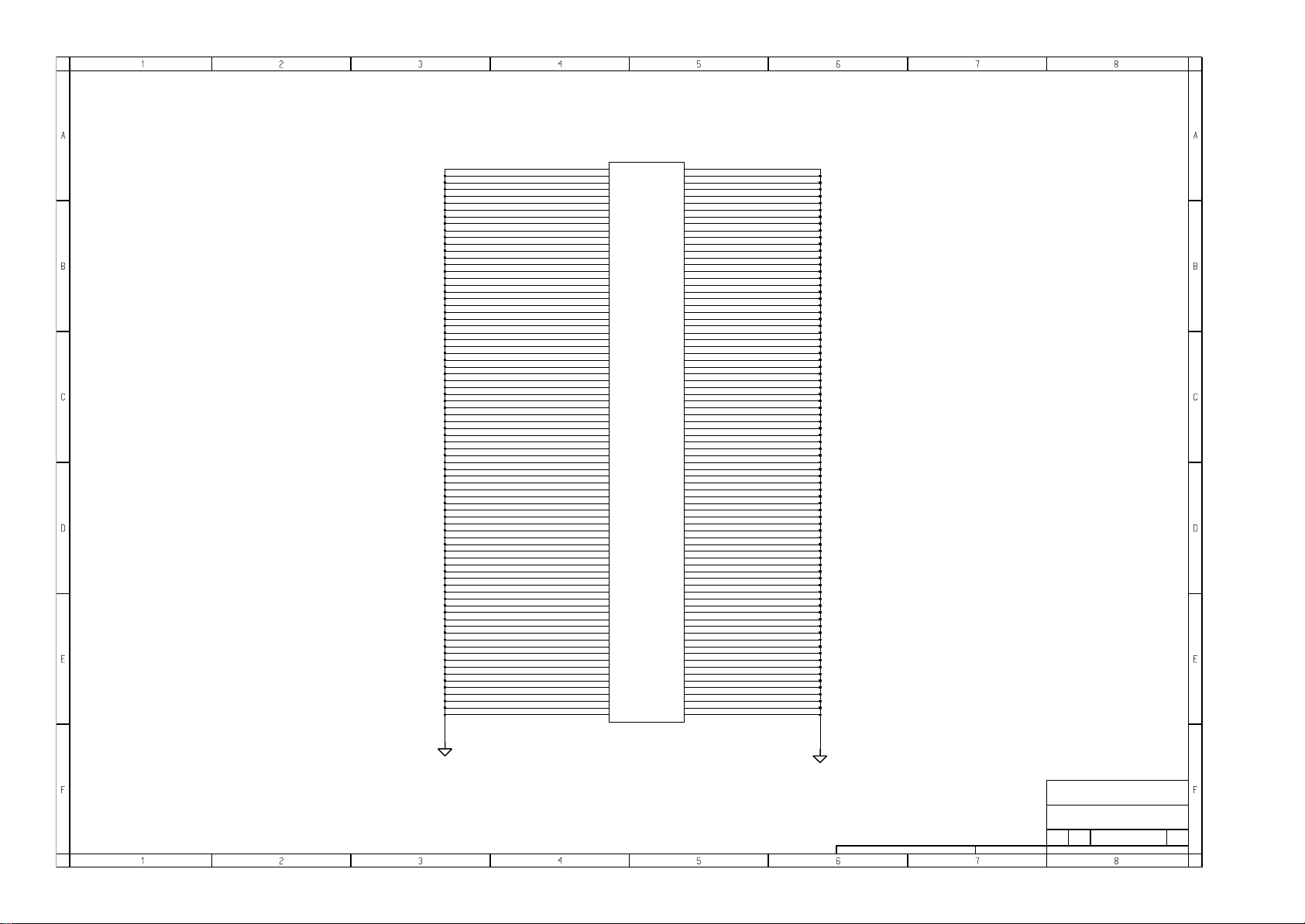

TABLE OF CONTENTS

PAGE

MAINBOARD

1.COVER PAGE

2.INDEX

3.BLOCK DIAGRAM

4.POWER SEQUENCE BLOCK

5-12.SYSTEM POWER

13.CLOCK GENERATOR

14-17.CPU Yonah

18.FAN & THERMAL CONTROLLER

19-24.N/B Calistoga

25.DDR2 DIMM0

26.DDR2 DIMM1

27.DDR DAMPING

28-31.VGA

32-36.GDDR2

37.CRT CONN

38.SVIDEO & HDMI & DVI CONN

39.LCD CONN

40-44.S/B ICH7

45.CARDBUS CONTROLLER

46.PCMCIA & EXPRESS CARD

47.6 IN 1 CARD SLOT

48.1394 CONTROLLER

49.LAN CONTROLLER

PAGE

50.RJ45 & TRANSFORMER

51.MINI CARD CONN

52.RAID CONTROLLER

53.ODD & HDD CONN

54.USB CONN

55.BLUE TOOTH CONN

56.MINIPCI

57.SUPER I/O

58.CODEC

59.AUDIO AMP

60.TV CONN & DC IN

61.SCREW

62.TO OTHER BOARD CONN

I/O BOARD

1.USB CONN

2.MDC CONN

3.PRT & COM PORT CONN

AUDIO BOARD

1.IR/CIR

2.BT&WIRELESS SW

HOTKEY BOARD

1.HOTKEY BUTTON

MEDIA BOARD

1.MEDIA BUTTON

PAGE

TOUCHPAD BOARD

1.TOUCHPAD

CHANGE by

Arthur_Chen

19-Dec-2005

INVENTEC

TITLE

Cheela

DOC. NUMBER

CODE

SIZE

A3

CS

SHEET

265

REV

000Model_No

OF

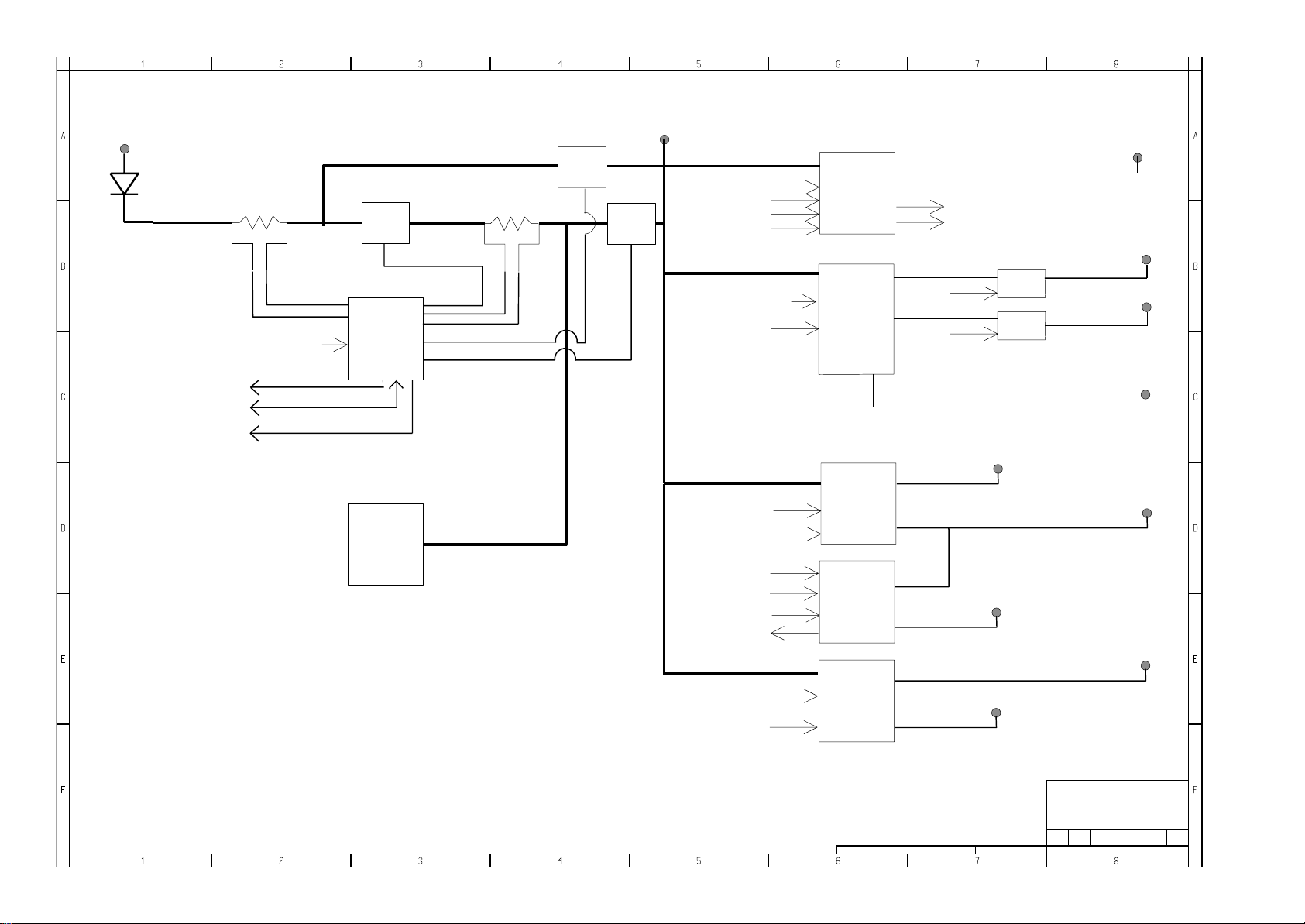

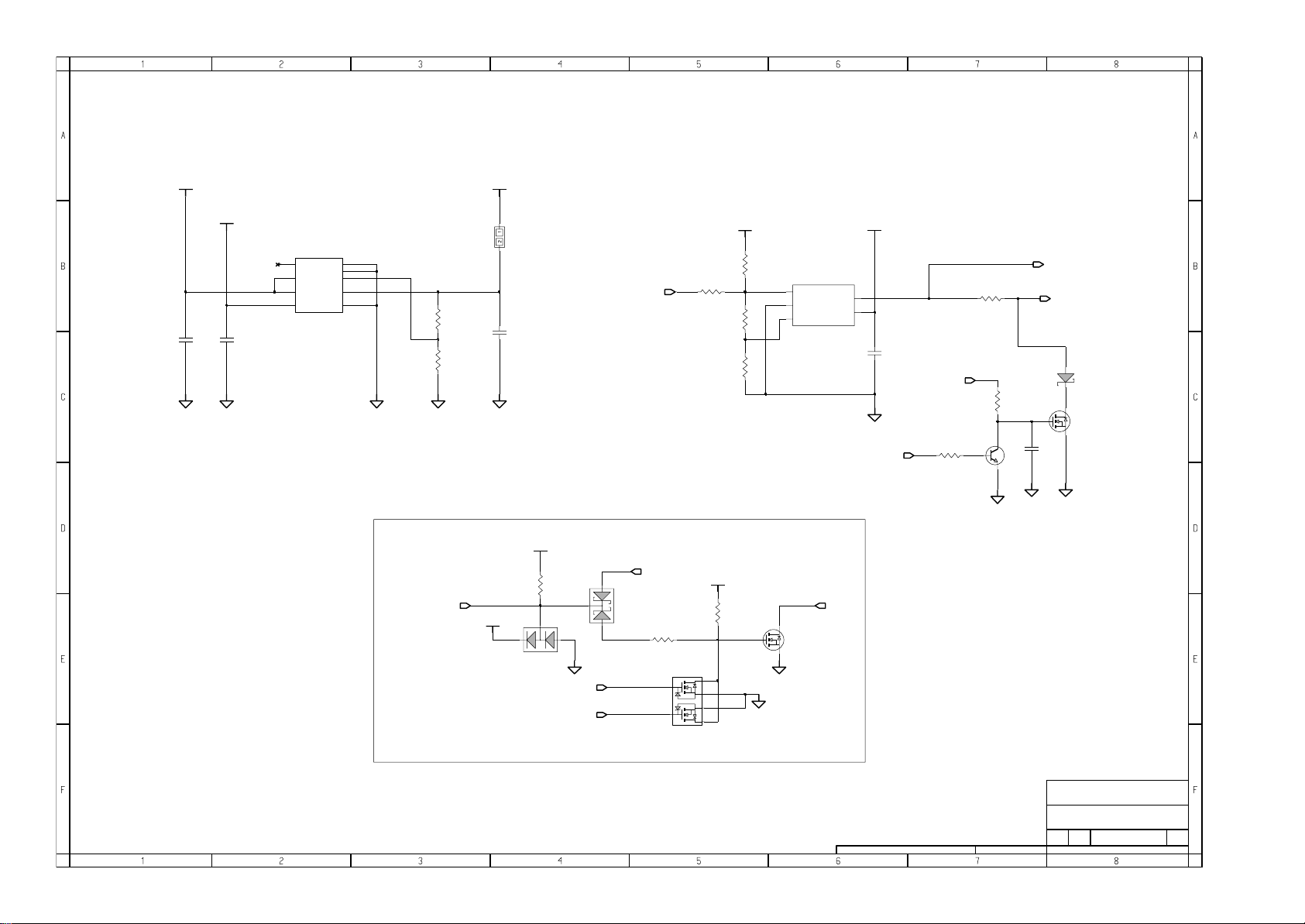

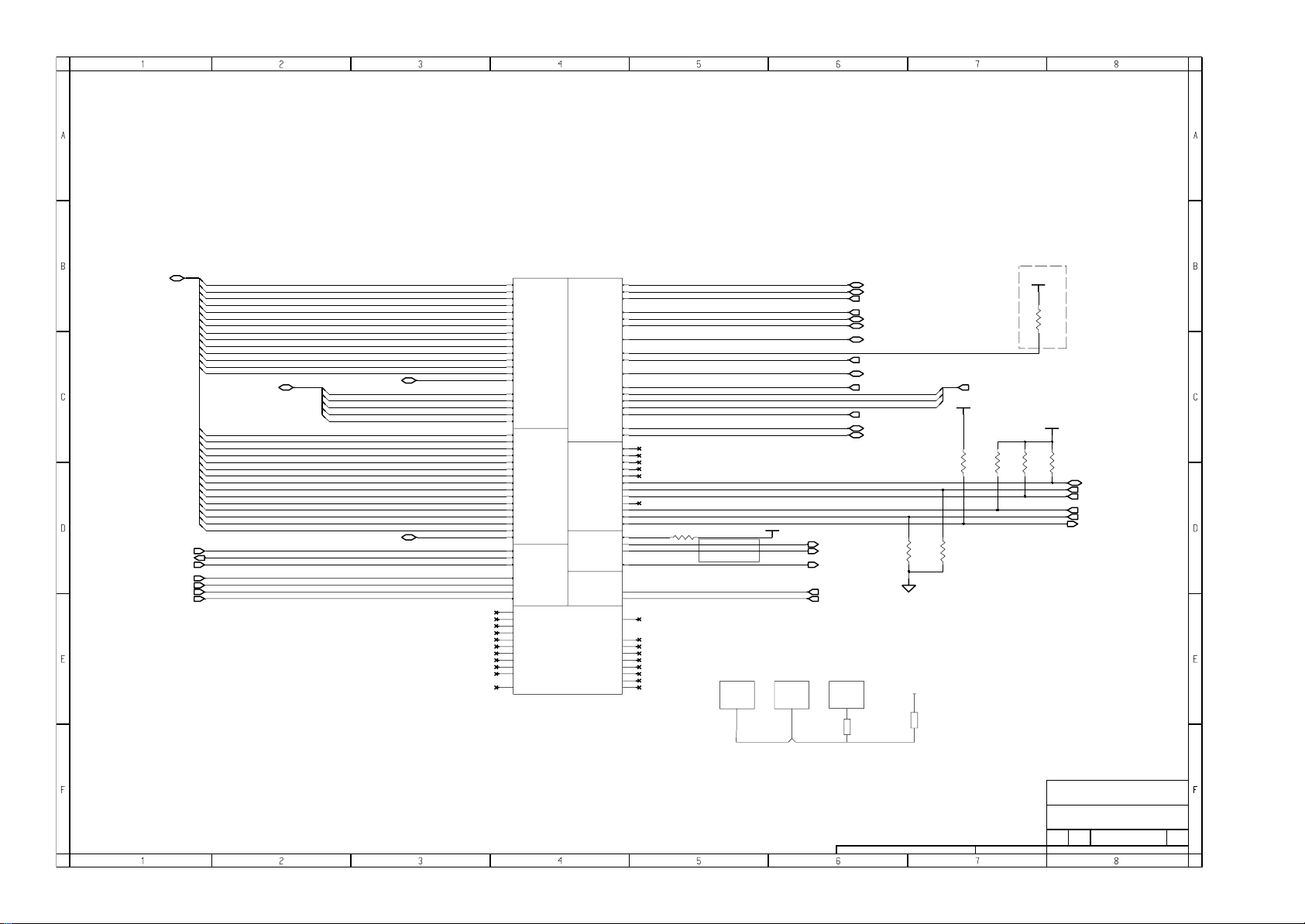

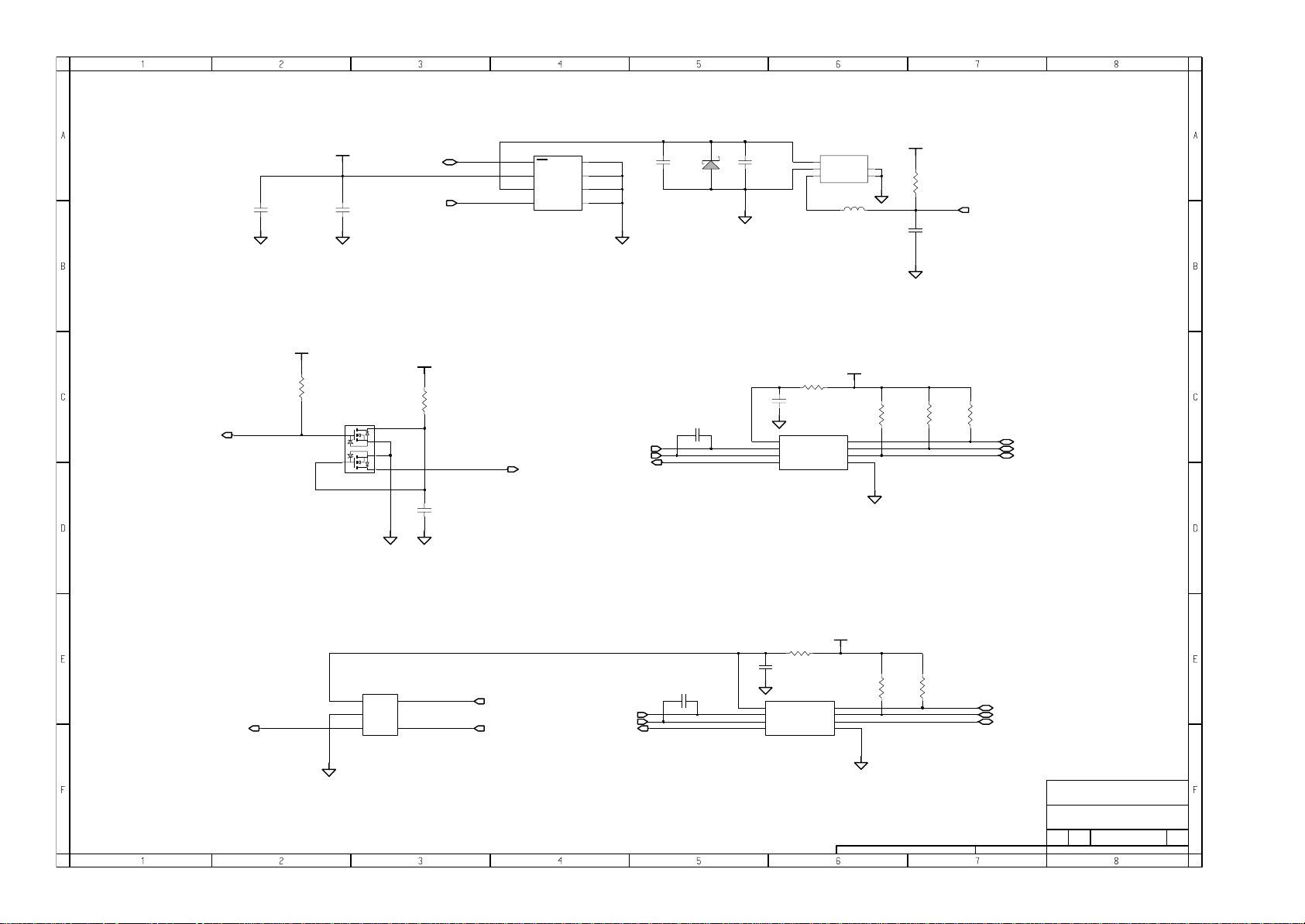

PWR Board

Batt Charger

MAIN BATT

8 Cell

HDMI

LCM

DVI

CRT

S-Video

M P.38

M P.39

M P.38

M P.37

M P.38

I/O BOARD

PRINTER

I P.3

PORT

COM

PORT

HDCP

ROM

M P.30

VGA

Controller

NVG73M/G72MV

OPTION

CD-ROM

SMSC

LPC47N217

BIOS

M P.57

CIR / FIR

A P.1

KB / LED

TOUCH PAD

2 PICK BUTTON/

4 WAY

T P.1

M P.28-31

VRAM

* 8(4) PCS

HDD

I P.3I P.3

PCIE

M P32-36

SATA

M P.53

Ultra ATA-100

M P.53

PATA

HDD

M P.53

LPC 3.3V 33MHZ

SUPER I/O & KBC

CPU

YONAH/MEROM

31W/34W

North Bridge

Calistoga

1466 uFCBGA

South Bridge

ICH7-M

652 BGA

LPC 3.3V 33MHZ

OPTION

KBC1122

M P.14-17

PSB

DDR2 533/667

DDR2 533/667

M P19-24

DMI

PCI_Express Bus

USB 2.0

PCI Bus

1394 CONN X 1

M P.57

Azalia

Audio Board

HD Codec

REAL_ALC883DD-GR

AMP

MAX_MAX9714

CardBus

Controller

TI PCI7412

PCMCIA

TYPE II

A P.2

A P.3

USB2.0 PORT

M P.48

M P.46

LINE IN

CLK GEN

ICS9LPR316

M P.13

DDR2_SODIMM0

DDR2_SODIMM1

x4

DSC

M P.56

MINI PCI

M P.45

M P.47

MS,MS-P,SD.SD-IO,XD,MMC

Jack

1.5*3A TAPE

6 IN 1 SLOT

Two

Speakers

MAX_9713

A P.3

TV TUNER

M P.58

ANT

Azalia

Internal Array

MIC

M P.25

M P.26

M P.39M P54 & I P.1

M P.58

AV IN

MDC

MDC 1.5

RJ11 CNTR

Sub

Woofer

BLUETOOTH

VER 2.0

SUPPORT 0,1

HDD

I P.2

MIC IN

Jack

M P.55

RAID

SIL3512E

SATA

HDD

M P.53 M P.53

MAX

9722

A P.3

HP Jack

\SPDIF\

LINE OUT

CHANGE by

THERMAL SENSOR

& FAN

ADM1032

Express Card

M P.52

SATA

RDEE3

Mini Card

M P.46

M P.18

24-Nov-2005

Controller

M P.51

INVENTEC

TITLE

CHEELA

CODE

SIZE

A3

CS

SHEET

LOM

MARVELL

88E8055

M P.49

RJ45

CONN

M P.50

M P.51

Mini Card

(No USB)

INTEL PRO

WIRELESS 3945ABG

ANT

DOC. NUMBER

OF

365

ANT

REV

000Model_No

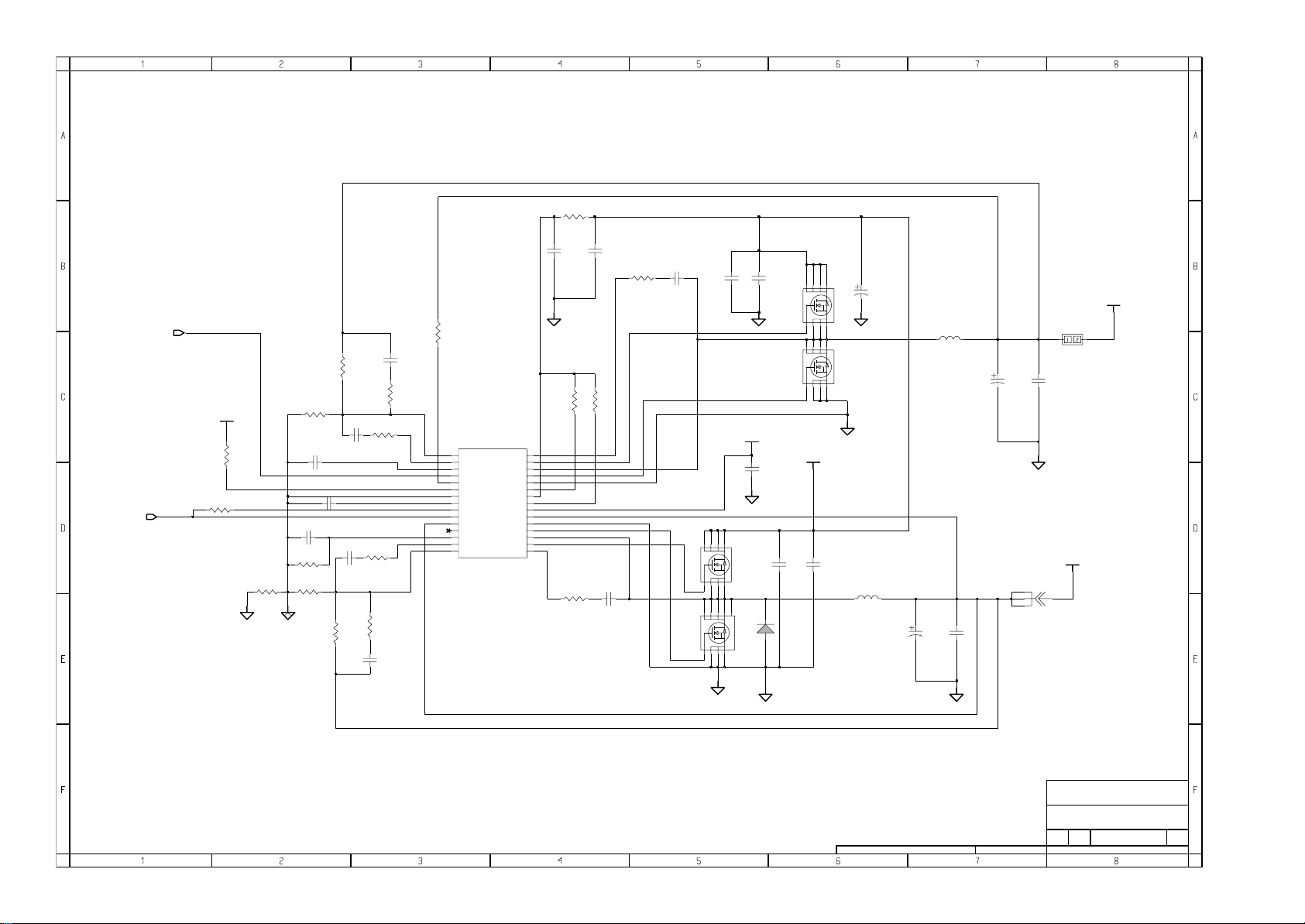

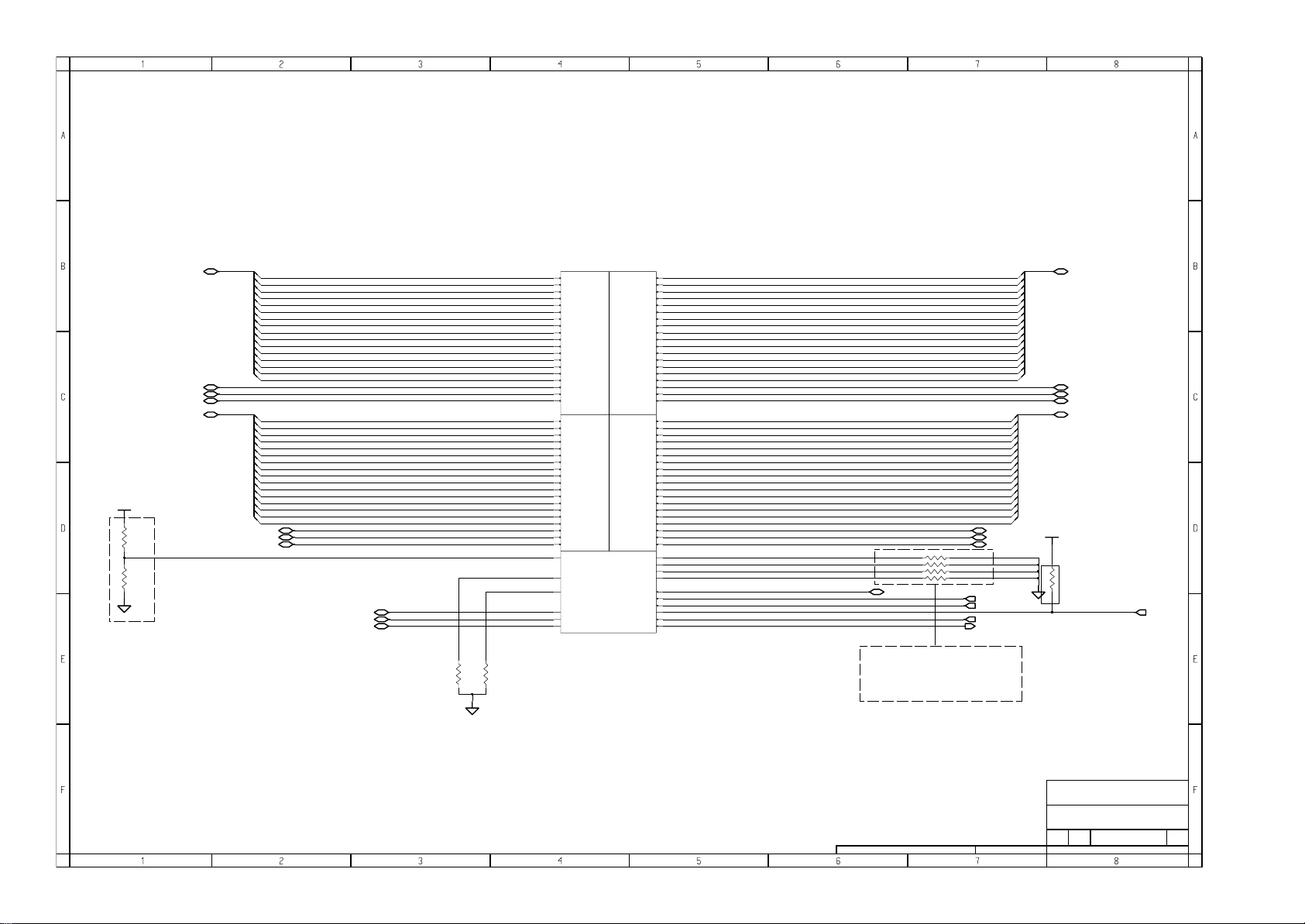

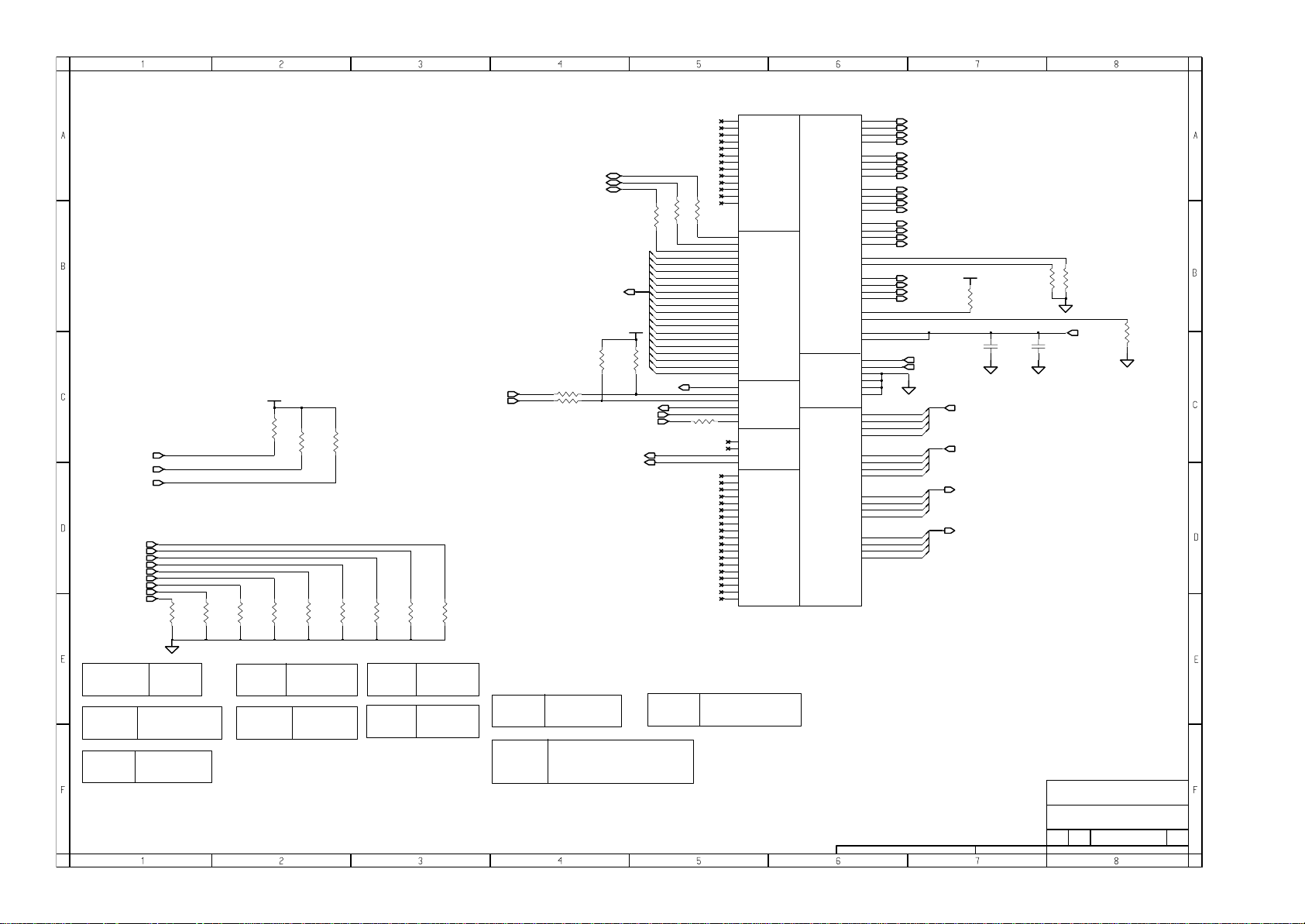

+ADAPTOR

CHG_EN

ACPPRES

I2C

BATT_IN

NMOS

BQ24721

CHGEN#

CHARGE

CHGDRV

BATDRV

ACDRV

PMOS

PMOS

+VBAT

SYSTEM LOAD

MCH_GOOD

+V5AUXON

+V5A

ADP3207

SHDN#

PSI#

DPRSTP#

DPRSLPVR

TPS51020

ENBL1

ENBL2

+VCC_CORE

CLKEN#

PWRGD

+V3A

+V5A

+V5AL

IMVP_CKEN#

VR_PWRGD_CK410

SLP_S3#_3R

SLP_S3#_3R

PMOS

ON

PMOS

ON

PMOS

+V3S

+V5S

+VCC_CORE

+V3S

+V5S

+V5AL

PACK

SLP_S3#_3R

SLP_S4#_3R

SLP_S3#_3R

SLP_S4#_3R

+V5A

M_VREF

SLP_S3#_3R

PWR_GOOD_3

TPS51124

EN1

EN2

GMT_G2997

S3

S5

VIN

VTTREF

TPS51124

EN1

EN2

CHANGE by

VGAVCC

+V1.8

VLDOIN

VTT

+V1.5S

+VCCP

RDEE3 24-Nov-2005

VGAVCC

+V0.9S

+VCCP

INVENTEC

TITLE

CHEELA

CODE

SIZE

A3

Model_No 000

CS

SHEET

+V1.8

+V1.5S

OF

REVDOC. NUMBER

654

+VADPTR

5-

BATT_CLK

BATT_DATA

57-,5-

57-,5-

CN27

1

1

2

2

3

5

G

3

4

G

6

4

4

E&T_4510_4P

1

R417

432K_1%

2

1

R418

30.9K_1%

2

ACPRES

CHARGE_GND

62-,60-,57-,51-,50-,49-,46-,43-,42-,41-,40-,12-,11-,7-

C434

OPEN12

57-,6-

CHG_EN

R425

12

10_5%

R424

12

10_5%

2

3

4

POWERPAD_4A

R423

12

10_5%

CHARGE_GND

1

R421

47K_5%

2

1

R422

100K_5%

2

+V3A

57-

PAD11

C479

1

2

2.2uF_25v

C478

1uF_10v

CHARGE_GND

1

D27

AZ23C6V2

2

L41

12

PLFC1045R_10uH

1

R416

10K_5%

2

C475

1

2

1500pF_50v

+VPACK

LITTLEFUSE_R451012_12A_65V

FUSE1

5-

12

C483

1

2

1000pF_50v

1

C803

2

0.1uF_25v

C408

1

2

10uF_25v_K_X5R

CHARGE_GND

1

R459

1K_5%

2

C802

1

2

10uF_25v_K_X5R

R323

12

0.01_1%_1W

Kevin Sense

C480

12

0.1uF_25v

C438

1

2

0.1uF_25v

NEAR IC

CN31

1

1

2

2

3

3

4

4

5

5

6

G1

6

G

7

G2

7

G

SYN_200275MR007G102ZL_7P

1

2

C801

1

2

10uF_25v_K_X5R

3

AM4825P_AP

+VPACK

1

2

C481

0.1uF_25v

CHARGE_GND

1

2

C482

0.1uF_25v

1

2

CHARGE_GND

POWERPAD_4A

Q30

8

S

D

7

6

54

G

5-

Q31

8

D

7

6

54

AM4825P_AP

C439

10uF_25v_K_X5R

PAD8

G

1

S

2

3

+VBAT

59-,39-,10-,9-,8-,7-,6-

1

2

3

4

+V19S

60-

1

+VADPTR

5-

THRM1

BATT_DATA

BATT_CLK

557-,557-,5-

1K_1%

R458

12

1

D28

AZ23C6V2

3

3

2

R369

12

0.01_1%_1W

1

2

1

1

2

R370

10K_5%

C431

0.1uF_25v

Kevin Sense

+V5LA

12-,11-,7-,6-

1

R428

8.06K_1%

2

1

R426

39.2K_1%

2

57-

1

R429

22.6K_1%

2

2

C435

12

0.1uF_25v

BATT_IN

C432

1

2

0.1uF_25v

CHARGE_GNDCHARGE_GND

U35

12

VCC

3

ACN

4

ACP

6

BYPASS#

5

ACDET

11

VREF5

10

AGND

15

TS

5-

THRM1

1

CHGEN#

14

SCL

13

SDA

25

ALARM#

17

IOUT

ACDRV#

BATDRV#

PVCC

HIDRV

BTST

REGN

LODRV

PGND

SYNP

SYNN

ISYNSET

SYS

SRP

SRN

BAT

EAO

FBO

TML

PH

EAI

2

23

24

32

30

29

31

28

27

26

22

21

20

19

18

7

8

9

16

33

R371

10_5%

12

13

BAT54D24

0.1uF_25v

TI_BQ24721_QFN_32P

1

R427

100K_5%

2

R430

12

0_5%

CHARGE_GND

C436

12

1

R420

200K_5%

2

1

2

10uF_25v_K_X5R

C437

12

1uF_25v

1

2

1

2

C433

R419

18K_5%

C477

100pF_50v

Q511

D1

1

2

5

S1_D2

G1

8

6

7

G2

3

4

S2

SP8K10SFD5_ROHM

C476

1

2

56pF_50v

INVENTEC

TITLE

CHEELA

RDEE3

24-Nov-2005

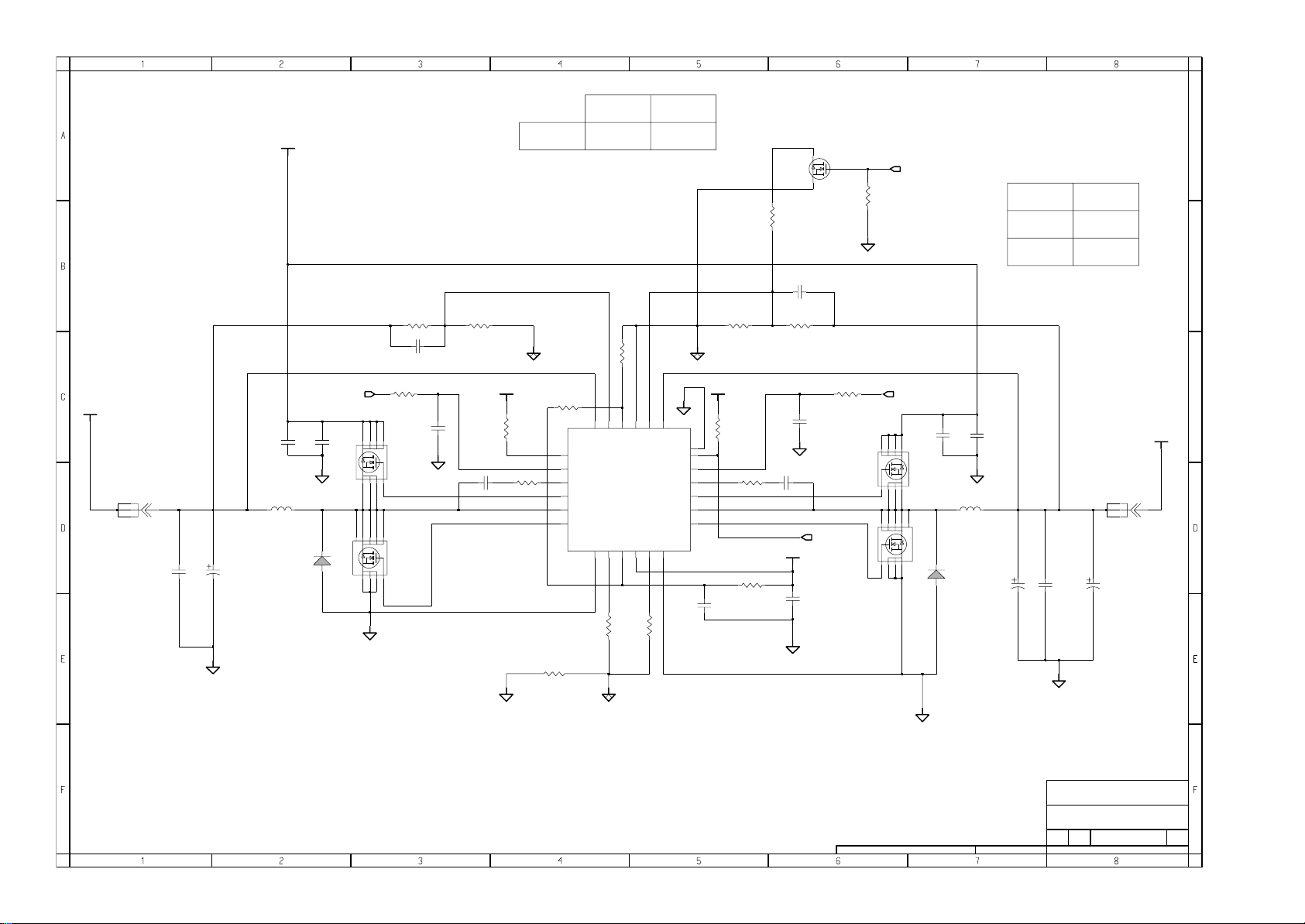

DC &BATTERY CHANGER

CODE DOC. NUMBERSIZE

CS

SHEET

Model_No

565

A3

REV

000

OF

C128

10uF_6.3v

+V3S

1

2

+V5S

1

2

2

3

4

GMT_G966_25ADJF1Uf_SOP_8P

C125

0.1uF_10v

U16

POK1TML

VEN

VIN VO

VPP

+V2.5S

31-,28-,23-

1A

PAD3

62-

+V5LA

1

2

12-,11-,7-,5-,6-

POWERPAD_2_0610

C124

10uF_6.3v

+V5LA

3

1

D505

BATT_PWRKEEP

12-,11-,7-,5-,6-

1

R674

100K_5%

2

BAV99

2

ACPRES

3

BAT54C

12

57-,5-

57-

57-,41-

D506

THER_SD#

PWR_SWIN#_3

12

R672

0_5%

18-

Q515

2

G1

5

G2

FDG6301N

9

8

GND

7

ADJ

6

5

NC

1

2

1

2

R116

OPEN

R114

0_5%

PWR_SWIN#

ALL POWER TURN OFF WHEN BATTERY MODE

R409

12

0_5%

16.2K_1%

180K_1%

+V5LA

6

D1

1

S1

4

S2

3

D2

+VBAT

R410

R408

12-,11-,7-,5-,6-

1

R673

100K_5%

2

SSM3K17FU

59-,39-,10-,9-,8-,7-,5-

1

R411

1M_5%

2

1

2

1

2

Q514

D

D

G

G

S

S

U38

LTH

3

GND

2

HTH

1

GMT_G680LT1_SOT23_5P

7-,6-

RESET#

VCC

PM_THRMTRIP#

+V5AUXON

4

5

+V5LA

12

12-,11-,7-,5-,6-

0.1uF_10v

C472

VR_PWRGD_CK410

40-,19-,14-

R684

1

330_5%

12

47K_5%

13-,10-

Q520

2

2SC2411K

R412

2

10-

+V5AUXON_1

7-,6-

+V5AUXON

BAT54

1

C9983

1

2

0.47uF_6.3v

G

D507

G

3

D

Q518

D

S

S

SSM3K17FU

1

R683

2M_1%

2

3

C

B

E

1

CHANGE by

RDEE3

24-Nov-2005

INVENTEC

TITLE

CHEELA

+V2.5S / RESET

SIZE

CODE

CS

SHEET

DOC. NUMBER

665

A3

REV

000Model_No

OF

SLP_S3#_3R

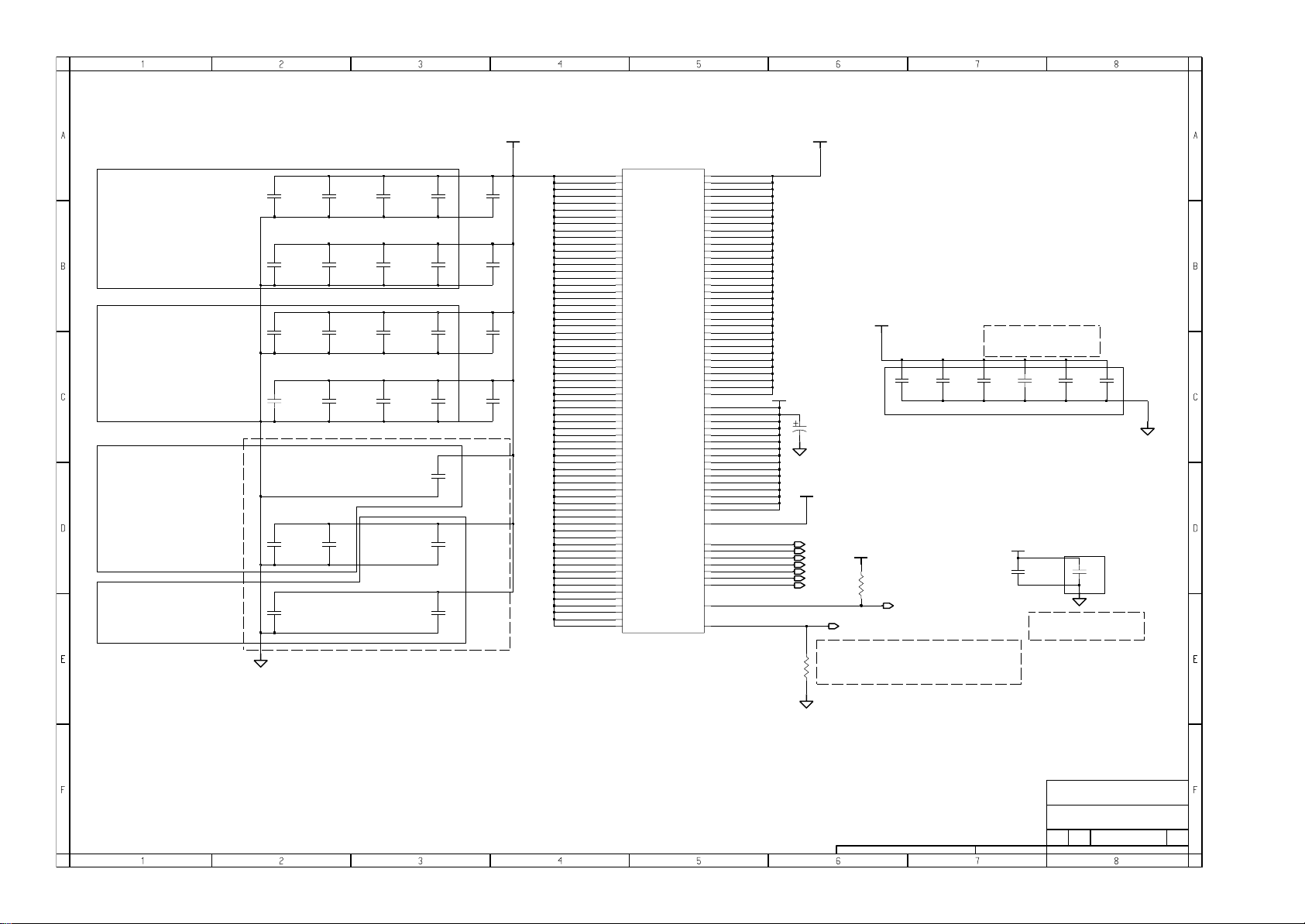

+V5AUXON

6-

57-,41-,31-,12-,11-,10-,9-,8-

+VBAT

59-,39-,10-,9-,8-,6-,5-,7-

2

R235

100K_5%

1

R5009

12

0_5%

R232

0_5%

0.01uF_16v

12

TPS51020

R233

10K_1%

12

C323

0.01uF_16v

1

2

C321

1

C342

12

R269

2

1

1M_5%

R273

12

10K_1%

1

R230

29.4K_1%

2

C322

1

0.033uF_16v

0.1uF_16v

2

1

C344

3900pF_50v

2

R271

1

51.1K_1%

2

2

2

1.8K_5%

1

2

1

2

R234

2.7K_5%

R270

1

1

R272

220_5%

2

C343

6800pF_25v

C320

4700pF_50v

1

R231

330_5%

2

12

1

R229

0_5%

2

U26

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

TI_TPS51020DBT_TSSOP_30P

INV1

COMP1

SSTRT1

SKIP#

VO1_VDDQ

DDR#

GND

REF_X

ENBL1

ENBL2

VO2

PGOOD

SSTRT2

COMP2

INV2

VBST1

OUT1_U

OUT1_D

OUTGND1

TRIP1

TRIP2

VREG5

REG5_IN

OUTGND2

OUT2_D

OUT2_U

VBST2

LL1

VIN

LL2

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

1

2

C326

4.7uF_25v

R238

15.8K_1%

R237

1

2

4.7_5%

1

2

1

1

2

2

R274

12

2.2_5%

0.1uF_25v

C767

2.2uF_25v

R239

10K_1%

C345

12

C324

R236

12

12

2.2_5%

0.1uF_25v

5

G

4

G

41

ROHM_RQW200N03FD5_PSOP_8P

1

2

4.7uF_25v

8D76

S

1

23

9

8765

D

S

23

C800

+V5LA

Q507

FDS6294

Q506

1

2

12-,11-,6-,5-

1

2

C799

4.7uF_25v

C325

1uF_6.3v

D21

1

SSM34_3A40V2

C774

1

2

10uF_25v

8

765

D

G

S

12

3

4

765

8

D

G

S

123

4

+VBAT

59-,39-,10-,9-,8-,6-,5-,7-

C773

1

2

4.7uF_25v

1

C290

2

68uF_25v

Q512

RSS090N03_ROHM

Q510

FDS6690AS

L38

12

PCMB104E_4R7MS

1

C347

2

330uF_6.3v

L42

12

PCMB104E_4R7MS

C346

1

2

1uF_10v

1

C407

2

330uF_6.3v

62-,60-,57-,51-,50-,49-,46-,43-,42-,41-,40-,12-,11-,5-

PAD9

1

POWERPAD_2_0610

1

C382

2

1uF_10v

+V5A

62-,59-,58-,54-,43-,12-,11-,9-,8-

2

PAD6

3

1

4

POWERPAD_4A

2

+V3A

MAX 8A

MAX 6A

CHANGE by

RDEE3 22-Dec-2005

INVENTEC

TITLE

CHEELA

SYSTEM POWER(3V/5V)

CODE

SIZE REV

A3

DOC. NUMBER

Model_No 000

CS

OFSHEET

657

G73M

G72M-V

+V1.8

26-,25-,24-,19-,11-

2

PAD1

3

1

4

POWERPAD_4A

Max : 15A

C66

10uF_6.3v

1

2

4.7uF_25v

1

PCMB104E_2R2MS

1

C67

2

330uF_2.5v_15mR_NEC

+VBAT

59-,39-,10-,9-,7-,6-,5-

1

2

C579

L17

2

SSM34_3A40V

SLP_S4#_3R

C577

10uF_25v_K_X5R

1

2

D11

1

2

4

TONSEL

V5FILT

15

R509

3

2

GND

VFB1

TRIP1

V5IN

17

16

12

16.9K

1

VO1

PGOOD1

VBST1

DRVH1

DRVL1

PGND1

18

GND

EN1

LL1

VGA_1.8V_GND

25

24

238

22

21

20

19

1

2

16.9K_1%

12

R522

+V5A

62-,59-,58-,54-,43-,12-,11-,9-,7-,8-

1

R512

100K_5%

2

R510

1

2.2_5%

R67

2

10_5%

C550

1uF_6.3v

R522

43.2K_1%

1

R523

1

2

OPENC65

57-,41-,11-

R521

1

2

0_5% 0_5%

5

876

D

G

Q503

FDS6294

41S23

8765

9

D

Q502

G

ROHM_RQW200N03FD5_PSOP_8P

41S2

3

30.1K_1%

1

2

62-,59-,58-,54-,43-,12-,11-,9-,7-,8-

C551

1

2

OPEN

R69

C64

12

0.1uF_25v

2

+V5A

VGA_1.8V_GND

1

R518

OPEN

2

R68

12

2.2_5%

22.6K

2

R70

OPEN

1

R524

OPEN

12

5

6

VO2

7

9

10

11

12

VFB2

U505

PGOOD2

TI_TPS51124RGER_QFN_24P

EN2

VBST2

DRVH2

LL2

DRVL2

PGND2

TRIP2

13

14

1

R519

13.3K_1%

13.3K_1%

2

C525

2

0.1uF_25v

1

1

2

SSM3K17FU_OPEN

D

S

R45

OPEN

2

1

OPEN

C527

6.04K_1%

2

R43

C526

1

2

12

+V5A

C63

1

4.7uF_6.3v

2

Q12

D

G

G

S

1

57-,41-,31-,12-,11-,10-,9-,7-

R511

1

OPEN

11-

+VGAVCC_PWRGD

1

2

2

30-

PWR_PLAY

R513

10K_5%

SLP_S3#_3R

765

8

D

Q504

G

FDS6294

S

4

123

9

8765

D

Q505

G

ROHM_RQW200N03FD5_PSOP_8P

S

1

23

41

2

C578

C580

1

1

10uF_25v_K_X5R

2

2

4.7uF_25v

L22

12

PCMC104T_1R0MN

D12

SSM34_3A40V

C151

220uF_2v_15mR_Panasonic

PWR_PLAY

1

0

1

1

2

2

+VGAVCC

1.025V

0.95V

28-

1

C620

C150

2

10uF_6.3v

330uF_2v_15mR_Panasonic

+VGAVCC

2

PAD4

3

1

4

POWERPAD_4A

Max : 17A

R520

12

0_5%

VGA_1.8V_GND

CHANGE by

RDEE3 2-Jan-2006

INVENTEC

TITLE

CHEELA

SYSTEM POWER (+V1.8 / +VGAVCC)

SIZE REV

A3

DOC. NUMBER

CODE

Model_No 000

CS

SHEET

OF

658

57-,41-,31-,12-,11-,10-,8-,7-,9-

SLP_S3#_3R

PWR_GOOD_3

+VCCP

43-,40-,24-,23-,21-,20-,16-,15-,14-,13-

MAX 10A

2

PAD7

3

4

POWERPAD_4A

C442

1

11-

1

C348

10uF_6.3v

1

2

OPEN

R372

OPEN

12

R374

2

0_5%

1

1

2

2

330uF_2v_15mR_Panasonic

C384

+VBAT

59-,39-,10-,8-,7-,6-,5-

1

2

C410

4.7uF_25v

L39

12

PCMC104T_2R2MN

SSM34_3A40V

C804

10uF_25v_K_X5R

1

2

D22

1

2

8

765

D

S

123

8D7

S

123

G

4

6

C409

54

G

15pF_50V

Q508

FDS6294

Q509

FDS6676AS

12.4K_1%

1

R324

12

1

2

R325

62-,59-,58-,54-,43-,12-,11-,8-,7-,9-

C440

OPEN

MCH_GOOD

C441

30.1K_1%

1

2

12

0.1uF_25v

2

+V5A

10-

1

R375

100K_5%

2

R373

12

2.2_5%

2

R327

OPEN

1

R326

OPEN

12

5

6

VO2

7

8

9

10

11

12

VFB2

U36

PGOOD2

TI_TPS51124RGER_QFN_24P

EN2

VBST2

DRVH2

LL2

DRVL2

PGND2

TRIP2

14

13

12

11.8K_1%

11.8K_1%

R376

4

TONSEL

V5FILT

15

R378

2

3

GND

VFB1

TRIP1

V5IN

17

16

12

1

VO1

PGOOD1

VBST1

DRVH1

DRVL1

PGND1

18

VCCP_1.5V_GNDVCCP_1.5V_GND

25

GND

24

23

EN1

22

21

20

LL1

19

R328

12

30.1K_1%

+V5A

62-,59-,58-,54-,43-,12-,11-,8-,7-,9-

1

R331

100K_5%

2

R380

12

2.2_5%

R377

2

10_5%

1

C443

1uF_6.3v

2

C446

0.1uF_25v

1

C411

12

15pF_50V

R330

12

30.9K_1%

C445

1

2

12

+V5A

C444

1

4.7uF_6.3v

2

57-,41-,31-,12-,11-,10-,8-,7-,9-

R379

1

0_5%

OPEN

11-

+V1.5_PWRGD

2

SLP_S3#_3R

Q513

D1

1

2

5

S1_D2

G1

8

6

7

G2

3

4

S2

SP8K10SFD5_ROHM

C805

1

1

10uF_25v_K_X5R

2

2

4.7uF_25v

L43

12

PLFC0735P_3.3uH

C412

1

C447

2

220uF_4v_15mR_NEC

1

2

C413

10uF_6.3v

+V1.5S

51-,46-,43-,24-,23-,20-,16-,11-

PAD10

POWERPAD_2_0610

MAX 5A

R329

12

0_5%

VCCP_1.5V_GND

CHANGE by

RDEE3

2-Jan-2006

INVENTEC

TITLE

CHEELA

SYSTEM POWER(+V1.5S / +VCCP)

CODE

SIZE REVDOC. NUMBER

A3

CS

SHEET OF

965

000Model_No

PSI#

H_DPRSTP#

H_VID6

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

MCH_GOOD

VR_PWRGD_CK410

IMVP_CKEN#

CPU_SINGNAL_GROUND

PM_DPRSLPVR

C222

1

2

18pF_50v

C696

1

1000pF_50v

2

CPU_SINGNAL_GROUND

15-

40-,15-

16161616161616-

9-,10-

13-,6-,10-

13-

C695

R159

12

28K_1%

C223

330pF_50v

R180

R166

12

R164

+V3S

1

R163

3K_5%

2

0.012uF_16v

1

12

C694

41-,19-

C221

12

220pF_25v

1

R160

1.65K_1%

2

16-

VCCSENSE

16-

VSSSENSE

Kevin Sense

+V5S

C248

1

2

1uF_10v

12

12

TP9028

TP9027

TP9026

TP9025

TP9024

TP9023

TP9022

0_5%

0.0047uF_50v

1

CPU_SINGNAL_GROUND

R162

3K_5%

2

R161

12

0_5%

2

680pF_50v

R558

12

499_1%

1

2

1000pF_50v

CPU_SINGNAL_GROUND

1

2

R181

12

10_5%

R557

12

0_5%

CPU_SINGNAL_GROUND

0_5%

0_5%

12

C697

41

40

TML

VID0

1

EN

2

PWRGD

3

PGDELAY

4

CLKEN

5

U22

FBRYN

ADI_ADP3207_LFCSP_40P

6

FB

7

COMP

8

SS

9

STSET

10

DPRSLP

ILIMIT

11

C219

R156

82.5K_1%

1

R158

133K_1%

2

CPU_SINGNAL_GROUND

+VBAT

59-,39-,9-,8-,7-,6-,5-,10-

C218

1000pF_50v

C247

1uF_10v

38

37

VID139VID2

VID336VID4

VRPM

RRPM

12

13

14

1

2

1

2

1

2

1

2

VID535VID6

LLSET

RAMPADJ

RT

16

15

1

R157

274K_1%

2

R155

237K_1%

1

2

31

34

33

32

PSI

VCC

DPRSTP

TTSENSE

VRTT

DCM

PWM1

PWM2

PWM3

SW1

SW2

SW3

GND

CSCOMP

CSREF

CSSUM

20

19

17

18

CPU_SINGNAL_GROUND

C245

OPEN

C220

1000pF_50v

30

29

28

27

OD

26

25

24

23

22

21

1

2

1500pF_50v

C246

MCH_GOOD

R179

R178

12

12

73.2K_1%

1

2

12

165K_1%

12

191K_1%

12

191K_1%

12

12

R173

OPEN

R175

R174

R176

R177

9-,10-

0_5%

0_5%

57-,41-,31-,12-,11-,9-,8-,7-

SLP_S3#_3R

+V5AUXON_1

VR_PWRGD_CK410

+V5S

C706

4.7uF_10v

BAT54C_30V_0.2A

R165

2

1

0_5%

ADI_ADP3419_RM_MSOP_10P

U508

1

2

3

4

5

1

2

IN

SD

DRVLSD

CROWBAR

VCC

D502

DRVH

DRVL

1

3

2

1

1

C707

R583

2.2_5%

2

0.22uF_10v

2

10

BST

9

8

SW

7

GND

6

6-

13-,6-,10-

+VBAT

59-,39-,9-,8-,7-,6-,5-,10-

1

2

12

D15

3

BAT54A

R154

12

470K_5%

C216

0.22uF_16v

10uF_25v_K_X5R

C293

C292

1

2

0.01uF_50v

FDS6676AS

C294

1

2

0.01uF_50v

Q19

1

2

1

2

G

4S123

+V3S

5

1

2

FAIR_NC7WZ17_SC70_6P

C295

8

765

D

G

S

Q21

123

4

FDS6294

8765

8

765

D

D

G

Q18

41S23

FDS6676AS

D14

U21-A

12

6

470K_5%

57-,41-

MPC1040LR45_TOKIN

D16

1

2

SSM34_3A40V_OPEN

BAT54

13

R153

2

SB_3S_VRMPWRGD

L33

12

330uF_2v_6mR

C2151

0.22uF_16v

5

U21-B

3

FAIR_NC7WZ17_SC70_6P

2

1

C708

2

330uF_2v_6mR

12

C217

0.1uF_16v

41-,19-

4

1

1

C306

2

2

330uF_2v_6mR_OPEN

C249

PM_PWROK

+VCC_CORE

16-

+V5S

C775

4.7uF_10v

BAT54C_30V_0.2A

ADI_ADP3419_RM_MSOP_10P

U510

1

2

3

4

5

1

2

IN

SD

DRVLSD

CROWBAR

VCC

D504

DRVH

DRVL

1

3

1

2

BST

SW

GND

R644

2.2_5%

10

9

8

7

6

2

1

C776

0.22uF_10v

2

10uF_25v_K_X5R

C329

C328

1

1

2

2

0.01uF_50v

FDS6676AS

Q25

C327

1

2

0.01uF_50v

C291

1

2

765

G

4

8765

D

G

Q22

4S123

FDS6294

765

8

8

D

D

D18

S

Q24

23

1

FDS6676AS

1

2

SSM34_3A40V_OPEN

G

S

4

123

L35

12

MPC1040LR45_TOKIN

330uF_2v_6mR

1

C256

2

330uF_2v_6mR

1

1

C768

2

2

330uF_2v_6mR_OPEN

C330

CPU_SINGNAL_GROUND

CHANGE by

RDEE3 8-Dec-2005

INVENTEC

TITLE

CHEELA

CPU POWER(VCC_CORE)

DOC. NUMBER REV

CODE

SIZE

A3

Model_No 000

CS

SHEET

OF

6510

SLP_S4#_3R

SLP_S3#_3R

+VGAVCC_PWRGD

57-,41-,31-,12-,10-,9-,8-,7-,11-

SLP_S3#_3R

57-,41-,8-

57-,41-,31-,12-,10-,9-,8-,7-,11-

+V1.8

26-,25-,24-,19-,8-,11-

1

C204

2

10uF_2.5v

C11

1

2

0.1uF_10v

8-

+V5LA

Q5

G

G

SSM3K17FU

C177

1

2

10uF_6.3v

12-,7-,6-,5-

1

2

D

D

S

S

R7

10K_5%

+V5A

1

R133

0_5%

2

1

2

26-,25-,24-,19-,8-,11-

C12

1

2

0.1uF_16v

R6

12

0_5%

62-,59-,58-,54-,43-,12-,9-,8-,7-

GMT_G2997F6U_MSOP10_10P

11 1

TML

VDDQSNS

10

VIN VLDOIN

9

S5

84

GND

7

S3

VTTSNS

6

VTTREF

C148

1uF_6.3v

+V1.8

1

2

C149

1uF_6.3v

Q4

8

D

7

6

5

FDS8426A

1

R5

270K_5%

2

G

M_VREF

35-,34-,33-,32-,31-,29-,11-

+V1.8S

1

S

2

3

4

Q500

G

G

SSM3K17FU

PGND

U18

VTT

26-,25-,19-

1

R500

470_5%

2

D

D

S

S

BAT54A

3

+V3S

1

2

1

R635

100K_5%

2

C784

0.1uF_16v

+V3A

62-,60-,57-,51-,50-,49-,46-,43-,42-,41-,40-,12-,7-,5-

5

U511-A

1

6

FAIR_NC7WZ17_SC70_6P

2

1

2

C778

0.1uF_10v

9-

PWR_GOOD_3

+V0.9S

36-,29-,27-

MAX 3A

PAD5

POWERPAD_2_0610

2

3

5

C205

10uF_6.3v

1

2

C178

10uF_6.3v

1

2

+V1.5_PWRGD

SLP_S3#_3R

9-

57-,41-,31-,12-,10-,9-,8-,7-,11-

D503

12

MAX 8A

1

2

1

2

C13

22uF_6.3v

C10

22uF_6.3v

C9795

1

2

0.1uF_16v

SSM3K17FU

G

+V1.2S

Q3

G

29-,28-,11-

1

R4

470_5%

2

D

D

S

S

C107

10uF_6.3v

+V1.5S

51-,46-,43-,24-,23-,20-,16-,9-

1

2

+V5S

35-,34-,33-,32-,31-,29-,11-

+V1.8S

C106

1

2

0.1uF_10v

U17

2

3

4

POK1TML

GND

VEN

VIN VO

VPP

9

8

7

ADJ

6

5

NC

GMT_G966_25ADJF1Uf_SOP_8P

1

2

1

2

R115

51K_1%

R113

100K_1%

+V1.2S

29-,28-,11-

POWERPAD_2_0610

C105

1

2

10uF_6.3v

MAX 2A

PAD2

CHANGE by

INVENTEC

TITLE

CHEELA

+V0.9S / POWER GOOD

CODE

SIZE

24-Nov-2005RDEE3

A3

DOC. NUMBER REV

CS

SHEET OF

11 65

000Model_No

+V5A

62-,59-,58-,54-,43-,11-,9-,8-,7-

SLP_S3#_3R

57-,41-,31-,11-,10-,9-,8-,7-

SSM3K17FU

+V5LA

11-,7-,6-,5-

1

R413

10K_5%

2

Q38

D

D

G

G

S

S

D19

13

BAT54

R275

12

220K_5%

D25

13

BAT54

R415

12

220K_5%

Q29

4

1

D

S

2

5

3

6

G

FDC602P

Q28

1

4

S

D

2

5

3

6

G

FDC602P

+V3A

62-,60-,57-,51-,50-,49-,46-,43-,42-,41-,40-,11-,7-,5-

4

S

3

FDC602P

4

S

3

FDC602P

C474

12

Q39

G

Q516

G

D

D

OPEN

1

2

5

6

1

2

5

6

C383

1

2

1000pF_50v

SSM3K17FU

Q27

G

G

SSM3K17FU

Q37

D

G

G

S

1

2

D

S

1

2

D

D

S

S

R414

200_5%

R297

200_5%

+V3S

1

2

C473

MAX 6A

10uF_10v

+V5S

1

2

MAX 8A

C381

22uF_10v

CHANGE by

RDEE3 24-Nov-2005

INVENTEC

TITLE

CHEELA

POWER(SLEEP)

CODE

SIZE REV

A3

DOC. NUMBER

Model_No 000

CS

SHEET

OF

6512

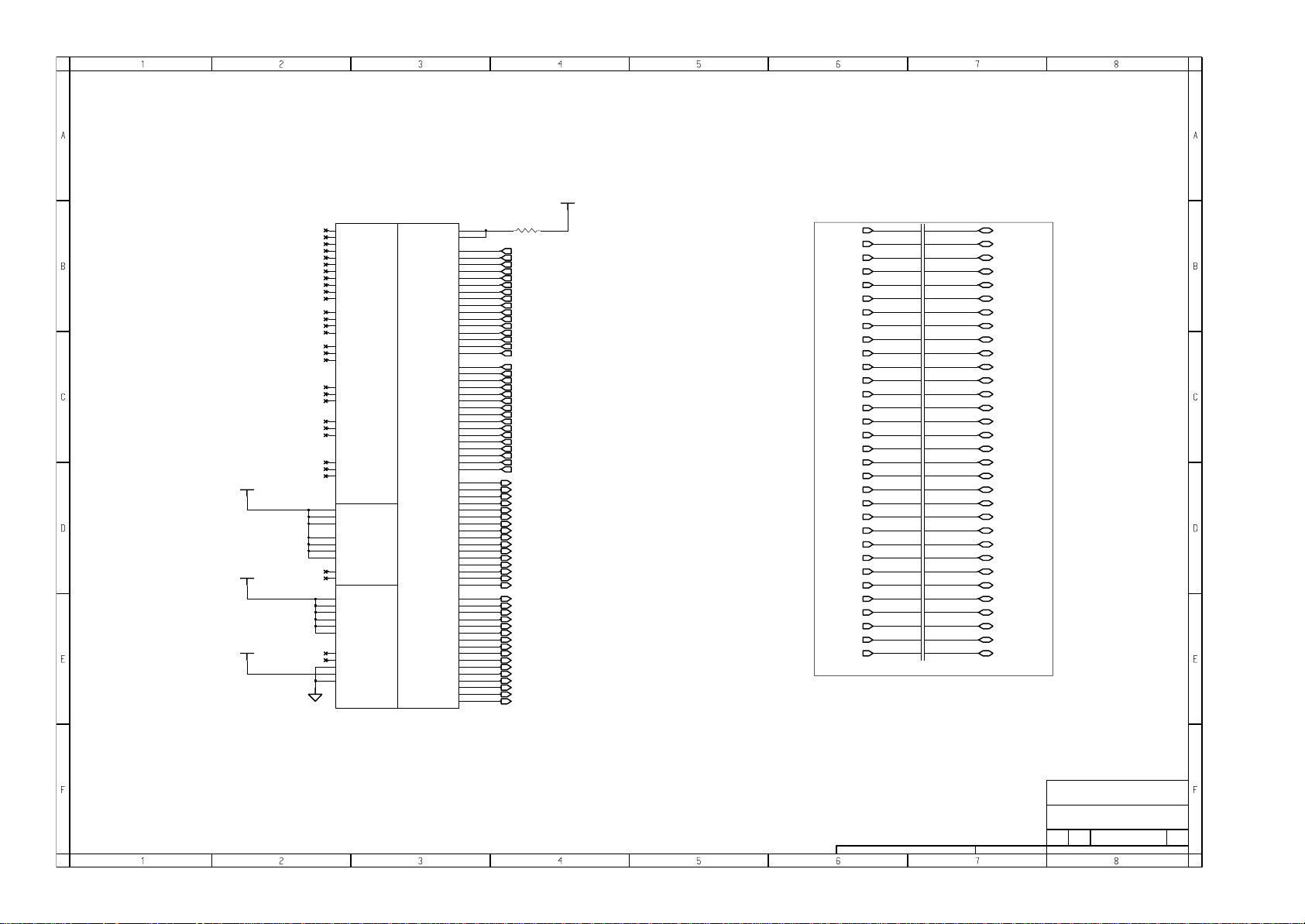

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

+VCCP

2

R393

OPEN

1

R391

12

19-,15-

10K_5%

+VCCP

43-,40-,24-,23-,21-,20-,16-,15-,14-,9-,13-

2

R396

OPEN

1

R392

19-,15-

2

10K_5%

R394

OPEN

12

R337

19-,15-

1

10K_5%

R336

OPEN

12

VR_PWRGD_CK410

1

2

IMVP_CKEN#

1

2

+V3S

10-

10-,6-

SSM3K17FU_OPEN

C418

22uF_6.3v

Layout note: All decoupling 0.047uF disperse closed to pin

1

2

C452

0.047uF_10v

1

2

C417

0.047uF_10v

1

2

C448

0.047uF_10v

1

2

C451

0.047uF_10v

Please place close to CLKGEN within 500mils

X4

12

C414

1

14.31818MHZ

2

33pF_50v

30PPM

R385

CLK_R3S_SIOPCI

CLK_R3S_RAIDPCI

CLK_R3S_ICH48

CLK_R3S_CARD48

CLK_R3S_ICH14

CLK_R3S_CBPCI

CLK_R3S_MINICARDPCI

CLK_R3S_KBPCI

CLK_R3S_MINIPCI

CLK_R3S_KBC14

CLK_R3S_SIO14

ICH_3S_SMDATA

ICH_3S_SMCLK

CLK_R3S_ICHPCI

Q36

D

D

G

G

S

S

62-

R387

52-

41-

R389

45-

455157-

56-

5762-

41-,26-,25-

41-,26-,25-

42-

R390

R338

R386 12.1_1%

R383

R384

R381 33_5%

R333

R335

R334

R382

R388

41-

LAYOUT NOTES : THE IREF(PIN_46) VIA R CONNECT TO GND DIRECTLY.

1

R343

4.7K_1%

2

C419

1

2

0.047uF_10v

C415

1

2

33pF_50v

CLK_3S_KBPCI

12

12.1_1%

CLK_3S_CBPCI

12

12.1_1%

12

12.1_1%

12

12.1_1%

12

33_5%

12

2

1

33_5%

12

12.1_1%

12

12

10K_5%

12

12.1_1%

12

12.1_1%

10K_5%

1

2

12

33_5%

CLK_REQA#

CLK_REQB#

+V3S_CLKVDD

C416

1

2

0.047uF_10v

CLK_3S_ICH48

CLK_BSEL1

CLK_3S_ICH14

CLK_3S_CBPCI

CLK_3S_MINICARDPCI

CLK_3S_KBPCI

CLK_3S_MINIPCI

CLK_3S_KBC14

CLK_3S_ICHPCI

5151-

+V3S

L45

1

2

3

4

NFM40P12C223

+V3S

L44

1

C449

1

2

0.047uF_10v

U37

24

VDDSRC

41

VDDSRC

5

VDDPCI

10

VDD48

16

VDD

33

VDDSRC

50

VDDCPU

57

X1

56

X2

11

FSLA_USB_48MHZ

15

FSLB_TEST_MODE

59

REF1_FSLC_TEST_SEL

6

PCICLK6

2

PCICLK4

3

PCICLK5

1

PCI_REFSEL_PCICLK3

62

SEL_REQ_PCICLK2

60

REF0_PCICLK1

54

SDATA

53

SCLK

7

SELSRC_LCDCLK#_PCICLK_F1

9

Vtt_PwrGd#_PD

46

VREF

64

R332

1

0_5%

CLKREQA#

2

63

CLKREQB#

4

GND

12

GND

40

GNDSRC

58

GND

17

GND

25

GNDSRC

32

GNDSRC

47

GNDCPU

CPUCLKT2_ITP_CLKREQC#

CPUCLKC2_ITP_CLKREQD#

ICS_ICS9LPR316_TSSOP_64P

2

C450

1

BLM11A121S

2

10uF_6.3v

VDDREF

PCI_SRC_STOP#

CPU_STOP#

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPICLKC1

SRCCLKT5

SRCCLKC5

SRCCLKT8

SRCCLKC8

SRCCLKT7

SRCCLKC7

SRCCLKT6

SRCCLKC6

SRCCLKT4

SRCCLKC4

GNDSRC

GNDSRC

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT1

SRCCLKC1

LCDCLK_SST_SRCCLKT0

LCDCLK_SSC_SRCCLKC0

DOTT_96MHZ

DOTC_96MHz

55

8

61

CLK_CPUBCLK

52

CLK_CPUBCLK#

51

CLK_MCHBCLK

49

CLK_MCHBCLK#

48

45

44

CLK_PEG_REF

35

CLK_PEG_REF#

34

CLK_PEG_MCH

43

CLK_PEG_MCH#

42

CLK_PCIE_CARD

39

38

CLK_PCIE_CARD#

CLK_PCIE_ICH

37

CLK_PCIE_ICH#

36

CLK_SATA1

30

CLK_SATA1#

31

28

29

CLK_PCIE_MINI1

26

27

CLK_PCIE_MINI1#

CLK_PCIE_MINI2

22

23

CLK_PCIE_MINI2#

CLK_PCIE_LAN

20

CLK_PCIE_LAN#

21

18

19

13

14

+V3S

1

R344

10K_5%

2

Q32

D

D

G

G

S

S

SSM3K17FU

12

24_5%R339

12

24_5%R340

12

R341 24_5%

12

R342 24_5%

12

24_5%R351

12

24_5%R352

12

R345 24_5%

12

R346 24_5%

12

R347 24_5%

12

R348 24_5%

12

R349 24_5%

12

R350 24_5%

12

24_5%R402

12

24_5%R403

12

24_5%R400

12

24_5%R401

12

R398 24_5%

12

R399 24_5%

12

R395 24_5%

12

R397 24_5%

Close to CLKGEN

46-

ICH_NEWCARD_CLKEN

41-

PCISTOP#_3

41-

CPUSTOP#_3

14-

CLK_R_CPUBCLK

14-

CLK_R_CPUBCLK#

21-

CLK_R_MCHBCLK

21-

CLK_R_MCHBCLK#

19-

MCH_CLK_REQ#

28-

CLK_R_PEG_REF

28-

CLK_R_PEG_REF#

19-

CLK_R_PEG_MCH

19-

CLK_R_PEG_MCH#

46-

CLK_R_PCIE_CARD

46-

CLK_R_PCIE_CARD#

41-

CLK_R_PCIE_ICH

41-

CLK_R_PCIE_ICH#

40-

CLK_R_SATA1

40-

CLK_R_SATA1#

51-

CLK_R_PCIE_MINI1

51-

CLK_R_PCIE_MINI1#

51-

CLK_R_PCIE_MINI2

51-

CLK_R_PCIE_MINI2#

49-

CLK_R_PCIE_LAN

49-

CLK_R_PCIE_LAN#

(ICS_ICS9LPR316)

BSEL0

FSA

1 0 0

1 1 0

BSEL1

FSB

BSEL2

FSC

FSB CLOCK

FREQUENCY

533

667

HOST CLOCK

FREQUENCY

133

166

CLKREQA#

CLKREQB#

CLKREQC#

CLKREQD#

SRCCLK8

X

SRCCLK7

X

SRCCLK6

SRCCLK5 SRCCLK3

X

X

SRCCLK4

X

SRCCLK2

X

SRCCLK1

X

SRCCLK0

X

X

INVENTEC

TITLE

CHEELA

CLOCK_GENERATOR

DOC. NUMBER

CHANGE by

RDEE3 6-Dec-2005

SIZE

A3

CODE

Model_No 000

CS

SHEET

REV

OF

6513

H_A#(31:3)

H_STPCLK#

H_A20M#

H_FERR#

H_IGNNE#

H_INTR

H_NMI

H_SMI#

21-

H_A#(3)

H_A#(4)

H_A#(5)

H_A#(6)

H_A#(7)

H_A#(8)

H_A#(9)

H_A#(10)

H_A#(11)

H_A#(12)

H_A#(13)

H_A#(14)

H_A#(15)

H_A#(16)

H_A#(17)

H_A#(18)

H_A#(19)

H_A#(20)

H_A#(21)

H_A#(22)

H_A#(23)

H_A#(24)

H_A#(25)

H_A#(26)

H_A#(27)

H_A#(28)

H_A#(29)

H_A#(30)

H_A#(31)

404040-

40404040-

H_REQ#(4:0)

H_REQ#(0)

H_REQ#(1)

H_REQ#(2)

H_REQ#(3)

H_REQ#(4)

H_ADSTB#0

21-

H_ADSTB#1

21-

21-

CN13-1

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

ADDR GROUP 0ADDR GROUP 1

ADSTB0#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB1#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD01

RSVD02

RSVD03

RSVD04

RSVD05

RSVD06

RSVD07

RSVD08

RSVD09

RSVD10

RSVD11

MLX_YONAH_SOCKET_M478A_478P

DEFER#

CONTROL

RESET#

XDP/ITP SIGNALS

PROCHOT#

THERMDA

THERMDC

THERM

THERMTRIP#

H CLK

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RESERVED

RSVD17

RSVD18

RSVD19

RSVD20

BPRI#

DRDY#

DBSY#

IERR#

LOCK#

TRDY#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TRST#

BCLK0

BCLK1

ADS#

BNR#

BR0#

DBR#

INIT#

RS0#

RS1#

RS2#

HIT#

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

TCK

AA6

TDI

AB3

TDO

AB5

TMS

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

12

R242

56_5%

43-,40-,24-,23-,21-,20-,16-,15-,13-,9-,14-

10mils/10mils

+VCCP

40-,19-,6-

CPU

18-

H_THERMDA

18-

H_THERMDC

PM_THRMTRIP#

13-

CLK_R_CPUBCLK

13-

CLK_R_CPUBCLK#

212121-

212121-

21-

40-

21-

21-

21-

2121-

ICH7GMCH

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BREQ#0

H_INIT#

H_LOCK#

H_CPURST#

H_TRDY#

H_HIT#

H_HITM#

H_RS#(0)

H_RS#(1)

H_RS#(2)

1

R585

56_5%

2

+VCCP

21-

1

R562

56_5%

2

+V3S

H_RS#(0:2)

1

R243

240_5%

2

+VCCP

43-,40-,24-,23-,21-,20-,16-,15-,13-,9-,14-

1

2

CLOSED TO CPU

+VCCP

1

1

R560

R559

56_5%

56_5%

2

2

R244

56_5%

43-,40-,24-,23-,21-,20-,16-,15-,13-,9-,14-

1

R561

56_5%

2

H_BPM5_PREQ#

H_TCK

TDI_FLEX

H_TMS

H_TRST#

41-

ITP_DBRESET#

PM_THRMTRIP# should be without T at CPU

CHANGE by

RDEE3

6-Dec-2005

INVENTEC

TITLE

CHEELA

Yonah-1

CODE

SIZE

A3

DOC. NUMBER

Model_No 000

CS

SHEET OF

REV

6514

H_D#(63:0)

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#(63:0)

+VCCP

43-,40-,24-,23-,21-,20-,16-,14-,13-,9-,15-

1

R277

1K_1%

2

H_GTLREF

1

R276

2K_1%

CLOSED TO CPU WITHIN 0.5"

2

21-,15-

212121-

21-,15-

H_DSTBN#1

H_DSTBP#1

H_DINV#1

CN13-2

H_D#(0)

H_D#(1)

H_D#(2)

H_D#(3)

H_D#(4)

H_D#(5)

H_D#(6)

H_D#(7)

H_D#(8)

H_D#(9)

H_D#(10)

H_D#(11)

H_D#(12)

H_D#(13)

H_D#(14)

H_D#(15)

H_D#(16)

H_D#(17)

H_D#(18)

H_D#(19)

H_D#(20)

H_D#(21)

H_D#(22)

H_D#(23)

H_D#(24)

H_D#(25)

H_D#(26)

H_D#(27)

H_D#(28)

H_D#(29)

H_D#(30)

H_D#(31)

212121- 21-

CPU_BSEL0

CPU_BSEL2

19-,1319-,1319-,13-

1

R280

OPEN

2

1

R281

51_5%

2

E22

D0#

F24

D1#

E26

D2#

H22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H26

D12#

DATA GRP 0DATA GRP 1

F26

D13#

K22

D14#

H25

D15#

H23

DSTBN0#

G22

DSTBP0#

J26

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L25

D20#

L22

D21#

L23

D22#

M23

D23#

P25

D24#

P22

D25#

P23

D26#

T24

D27#

R24

D28#

L26

D29#

T25

D30#

N24

D31#

M24

DSTBN1#

N25

DSTBP1#

M26

DINV1#

AD26

GTLREF

C26

TEST1

TEST2

BSEL0

BSEL1

BSEL2

MISC

D25

B22

B23

C21

MLX_YONAH_SOCKET_M478A_478P

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

DATA GRP 2DATA GRP 3

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#(32)

H_D#(33)

H_D#(34)

H_D#(35)

H_D#(36)

H_D#(37)

H_D#(38)

H_D#(39)

H_D#(40)

H_D#(41)

H_D#(42)

H_D#(43)

H_D#(44)

H_D#(45)

H_D#(46)

H_D#(47)

H_D#(48)

H_D#(49)

H_D#(50)

H_D#(51)

H_D#(52)

H_D#(53)

H_D#(54)

H_D#(55)

H_D#(56)

H_D#(57)

H_D#(58)

H_D#(59)

H_D#(60)

H_D#(61)

H_D#(62)

H_D#(63)

2

1

27.4_1%R279

12

R278 54.9_1%

12

27.4_1%R146

12

R145 54.9_1%

40-,10-

H_DPRSTP#

NOTE: COM0, COM2, trace impedance

should be 27.4 ohm

COM1, COM3, trace impedance

should be 55 ohm

CLOSED TO CPU

4021-

40-,21-

10-

2121-

H_DSTBN#3

H_DSTBP#3

H_DINV#3

H_DPSLP#

H_DPWR#

H_CPUSLP#CPU_BSEL1

PSI#

21-,15-

H_D#(63:0)

21-

H_DSTBN#2

21-

H_DSTBP#2

21-

H_DINV#2

21-,15-

H_D#(63:0)

+VCCP

43-,40-,24-,23-,21-,20-,16-,14-,13-,9-,15-

2

R167

OPEN

1

CLOSED TO CPU

40-

H_PWRGD

CHANGE by

INVENTEC

TITLE

CHEELA

Yonah-2

SIZE CODE

A3

CS

24-Nov-2005RDEE3

SHEET

15 65

REVDOC. NUMBER

000Model_No

OF

PLACE THESE INSIDE SOCKET

CAVITY ON L8 (NORTH SIDE

SECONDARY)

PLACE THESE INSIDE SOCKET

CAVITY ON L8 (SOUTH SIDE

SECONDARY)

PLACE THESE INSIDE SOCKET

CAVITY ON L1 (NORTH SIDE

PRIMARY)

PLACE THESE INSIDE SOCKET

CAVITY ON L1 (SOUTH SIDE

PRIMARY)

1

2

1

2

1

2

1

2

1

2

1

2

C255

22uF_6.3v

C304

22uF_6.3v

C305

22uF_6.3v

C297

22uF_6.3v

C741

OPEN

C714

OPEN

1

2

1

2

1

2

1

2

1

2

C254

22uF_6.3v

C303

22uF_6.3v

C302

22uF_6.3v

C296

22uF_6.3v

C742

OPEN

1

2

1

2

1

2

1

2

C253

22uF_6.3v

C300

22uF_6.3v

C301

22uF_6.3v

C251

22uF_6.3v

1

2

2

1

2

1

2

1

2

1

2

1

2

C252

22uF_6.3v

22uF_6.3v

C298

22uF_6.3v

22uF_6.3v

C299

22uF_6.3v

22uF_6.3v

C250

22uF_6.3v

22uF_6.3v

C713

OPEN

C715

OPEN

C743

OPEN

1

2

11

2

1

2

1

2

NOTE:

NO_STUFF

22UF X 12

+VCC_CORE

10-,16-

C711

C710

C739

C738

CN13-3

A7

VCC001

A9

VCC002

A10

VCC003

A12

VCC004

A13

VCC005

A15

VCC006

A17

VCC007

A18

VCC008

A20

VCC009

B7

VCC010

B9

VCC011

B10

VCC012

B12

VCC013

B14

VCC014

B15

VCC015

B17

VCC016

B18

VCC017

B20

VCC018

C9

VCC019

C10

VCC020

C12

VCC021

C13

VCC022

C15

VCC023

C17

VCC024

C18

VCC025

D9

VCC026

D10

VCC027

D12

VCC028

D14

VCC029

D15

VCC030

D17

VCC031

D18

VCC032

E7

VCC033

E9

VCC034

E10

VCC035

E12

VCC036

E13

VCC037

E15

VCC038

E17

VCC039

E18

VCC040

E20

VCC041

F7

VCC042

F9

VCC043

F10

VCC044

F12

VCC045

F14

VCC046

F15

VCC047

F17

VCC048

F18

VCC049

F20

VCC050

AA7

VCC051

AA9

VCC052

AA10

VCC053

AA12

VCC054

AA13

VCC055

AA15

VCC056

AA17

VCC057

AA18

VCC058

AA20

VCC059

AB9

VCC060

AC10

VCC061

AB10

VCC062

AB12

VCC063

AB14

VCC064

AB15

VCC065

AB17

VCC066

AB18

VCC067

MLX_YONAH_SOCKET_M478A_478P

VCC068

VCC069

VCC070

VCC071

VCC072

VCC073

VCC074

VCC075

VCC076

VCC077

VCC078

VCC079

VCC080

VCC081

VCC082

VCC083

VCC084

VCC085

VCC086

VCC087

VCC088

VCC089

VCC090

VCC091

VCC092

VCC093

VCC094

VCC095

VCC096

VCC097

VCC098

VCC099

VCC0100

VCCP01

VCCP02

VCCP03

VCCP04

VCCP05

VCCP06

VCCP07

VCCP08

VCCP09

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCA

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

VID0

AF5

VID1

AE5

VID2

AF4

VID3

AE3

VID4

AF2

VID5

AE2

VID6

AF7

AE7

+VCC_CORE

10-,16-

+VCCP

43-,40-,24-,23-,21-,20-,15-,14-,13-,9-

1

C352

330uF_2.5v

2

+V1.5S

51-,46-,43-,24-,23-,20-,11-,9-,16-

10-

H_VID0

10-

H_VID1

10-

H_VID2

10-

H_VID3

10-

H_VID4

10-

H_VID5

10-

H_VID6

10-

LAYOUT NOTE:

1

R586

ROUTE VCCSENSE AND VSSSENSE TRACE AT

27.4 OHM WITH 50 MIL SPACING.

100_1%

PLACE PU AND PD WITHIN 1 INCH OF CPU

2

+VCCP

+VCC_CORE

10-,16-

1

R584

100_1%

2

VSSSENSE

43-,40-,24-,23-,21-,20-,15-,14-,13-,9-

C744

1

2

0.1uF_10v

10-

VCCSENSE

C740

1

2

0.1uF_10v

PLACE THESE INSIDE SOCKET

CAVITY ON L8 SIDE (NORTH SIDE

SECONDARY)

C712

C737

1

2

0.1uF_10v

+V1.5S

1

2

1

1

2

2

0.1uF_10v

51-,46-,43-,24-,23-,20-,11-,9-,16-

C350

10uF_6.3v

LAYOUT NOTE:

PLACE C119 NEAR PIN B26

C716

0.1uF_10v

C349

1

2

0.01uF_16v

C709

1

2

0.1uF_10v

CHANGE by

INVENTEC

TITLE

CHEELA

Yonah-3

SIZE

24-Nov-2005RDEE3

A3

CODE

CS

SHEET

DOC. NUMBER

16 65

REV

000Model_No

OF

CN13-4

A4

VSS001

A8

VSS002

A11

VSS003

A14

VSS004

A16

VSS005

A19

VSS006

A23

VSS007

A26

VSS008

B6

VSS009

B8

VSS010

B11

VSS011

B13

VSS012

B16

VSS013

B19

VSS014

B21

VSS015

B24

VSS016

C5

VSS017

C8

VSS018

C11

VSS019

C14

VSS020

C16

VSS021

C19

VSS022

C2

VSS023

C22

VSS024

C25

VSS025

D1

VSS026

D4

VSS027

D8

VSS028

D11

VSS029

D13

VSS030

D16

VSS031

D19

VSS032

D23

VSS033

D26

VSS034

E3

VSS035

E6

VSS036

E8

VSS037

E11

VSS038

E14

VSS039

E16

VSS040

E19

VSS041

E21

VSS042

E24

VSS043

F5

VSS044

F8

VSS045

F11

VSS046

F13

VSS047

F16

VSS048

F19

VSS049

F2

VSS050

F22

VSS051

F25

VSS052

G4

VSS053

G1

VSS054

G23

VSS055

G26

VSS056

H3

VSS057

H6

VSS058

H21

VSS059

H24

VSS060

J2

VSS061

J5

VSS062

J22

VSS063

J25

VSS064

K1

VSS065

K4

VSS066

K23

VSS067

K26

VSS068

L3

VSS069

L6

VSS070

L21

VSS071

L24

VSS072

M2

VSS073

M5

VSS074

M22

VSS075

M25

VSS076

N1

VSS077

N4

VSS078

N23

VSS079

N26

VSS080

P3

VSS081

MLX_YONAH_SOCKET_M478A_478P

VSS082

VSS083

VSS084

VSS085

VSS086

VSS087

VSS088

VSS089

VSS090

VSS091

VSS092

VSS093

VSS094

VSS095

VSS096

VSS097

VSS098

VSS099

VSS0100

VSS0101

VSS0102

VSS0103

VSS0104

VSS0105

VSS0106

VSS0107

VSS0108

VSS0109

VSS0110

VSS0111

VSS0112

VSS0113

VSS0114

VSS0115

VSS0116

VSS0117

VSS0118

VSS0119

VSS0120

VSS0121

VSS0122

VSS0123

VSS0124

VSS0125

VSS0126

VSS0127

VSS0128

VSS0129

VSS0130

VSS0131

VSS0132

VSS0133

VSS0134

VSS0135

VSS0136

VSS0137

VSS0138

VSS0139

VSS0140

VSS0141

VSS0142

VSS0143

VSS0144

VSS0145

VSS0146

VSS0147

VSS0148

VSS0149

VSS0150

VSS0151

VSS0152

VSS0153

VSS0154

VSS0155

VSS0156

VSS0157

VSS0158

VSS0159

VSS0160

VSS0161

VSS0162

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

CHANGE by

RDEE3 24-Nov-2005

INVENTEC

TITLE

CHEELA

Yonah-4

CODE

SIZE

A3

DOC. NUMBER

Model_No 000

CS

SHEET

REV

OF

6517

1

2

C244

10uF_6.3v

+V5S

1

2

C243

0.1uF_16v

VGA_THERM_ALERT#

FAN1_DAC0_3

30-,18-

57-

U20

1

2

3

4

GMT_G995P1U_SOP8_8P

FON

VIN

VO

VSET

8

GND

7

GND

6

GND

5

GND

1

2

C214

2.2uF_16v

D1313

BAT54

C213

1

2

0.01uF_16v

FAN CN

CN12

1

VCC

2

GND

3

REFENCE

MLX_53398_0371_3P

L28

12

BLM11A121S

+V3S

4

G

5

G

1

R152

10K_5%

2

C212

1

2

0.01uF_50v

57-

FAN_TACH1

THRM_SHUTDWN#

BBUS

57-,18-

+V3S

1

R246

10K_5%

2

U28

6

D1

2

G1

1

S1

4

S2

5

G2

3

D2

FDG6301N_SC70_6

+V3S

1

2

1

R205

220K_5%

2

C307

0.1uF_10v

6-

THER_SD#

VGA_THERMDA

VGA_THERMDC

THRM_SHUTDWN#

C95

2

1

30-

OPEN

3057-,18-

A&D_ADM1032ARM_MICRO_SO_8P

Thermal Sensor For VGA

C68

1

0.1uF_16v

2

U12

1

VDD

2

D+

3

D-

4

THERM#

R89

12

22_5%

SCLK

SDATA

ALERT#

GND

+V3S

8

7

6

5

1

R75

2.2K_5%

2

1

R20

2.2K_5%

2

1

R41

2.2K_5%

2

30-,18-

3030-

VGA_THERM_CLK

VGA_THERM_DATA

VGA_THERM_ALERT#

+V3S

R245

12

22_5%

C331

1

2

0.1uF_16v

U29

5

1

DN

VDD

2

57-

GND

3

4

BBUS

SMSC_EMC1212_SOT23_5P

DP

14-,18-

14-,18-

H_THERMDC

H_THERMDA

H_THERMDA

H_THERMDC

THRM_SHUTDWN#

14-,1814-,1857-,18-

C332

12

OPEN

U27

1

VDD

2

D+

3

D-

4

THERM#

SCLK

SDATA

ALERT#

GND

8

7

6

5

A&D_ADM1032ARM_MICRO_SO_8P_OPEN

1

R240

4.7K_5%

2

1

R241

4.7K_5%

2

575741-

THERM_CLK

THERM_DATA

THERM_SCI#

Thermal Sensor For CPU

INVENTEC

TITLE

CHEELA

THERMAL&FAN CONTROLLER

DOC. NUMBERSIZE

CODE REV

CHANGE by

RDEE3

24-Nov-2005

A3

Model_No 000

CS

SHEET

OF

18

65

MCH_CFG(18)

MCH_CFG(19)

MCH_CFG(20)

MCH_CFG(12)

MCH_CFG(13)

MCH_CFG(16)

MCH_CFG(11)

MCH_CFG(10)

MCH_CFG(9)

MCH_CFG(7)

MCH_CFG(6)

MCH_CFG(5)

+V3S

19-

19-

19-

CFG(18:20) HAS INTERNAL PULL DOWN

191919191919191919-

1

1

1

R210

OPEN

2

R208

OPEN

2

R212

OPEN

2

1

R183

OPEN

2

1

R209

OPEN

2

1

2

R186

OPEN

1

R200

OPEN

2

1

2

R185

OPEN

1

R204

OPEN

2

1

R203

OPEN

2

1

R211

OPEN

2

PM_EXTTS#0

PM_DPRSLPVR

1

R202

OPEN

2

26-,2541-,10-

R188

R182

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

MCH_CFG(20:3)

R187

OPEN

12

0_5%

12

0_5%

MCH_ICH_SYNC#

MCH_CLK_REQ#

15-,1315-,1315-,13-

+V3S

1

R184

10K_5%

2

PM_THRMTRIP#

PM_PWROK

PLT_RST#

19-

1

2

BM_BUSY#

R201

R207

1

1

2

2

1K_5%

1K_5%

MCH_CFG(3)

MCH_CFG(4)

MCH_CFG(5)

MCH_CFG(6)

MCH_CFG(7)

MCH_CFG(8)

MCH_CFG(9)

MCH_CFG(10)

MCH_CFG(11)

MCH_CFG(12)

MCH_CFG(13)

MCH_CFG(14)

MCH_CFG(15)

MCH_CFG(16)

MCH_CFG(17)

MCH_CFG(18)

MCH_CFG(19)

MCH_CFG(20)

40-,14-,641-,1057-,42-,28-

100_5%

4213-

U23-2

T32

RSVD_1

R32

RSVD_2

F3

RSVD_3

F7

RSVD_4

AG11

RSVD_5

AF11

RSVD_6

H7

RSVD_7

J19

RSVD_8

A41

RSVD_9

A35

RSVD_10

A34

RSVD_11

D28

R206

RSVD_12

1

D27

RSVD_13

2

1K_5%

K16

CFG_0

K18

CFG_1

J18

CFG_2

F18

CFG_3

E15

CFG_4

F15

CFG_5

E18

CFG_6

D19

CFG_7

D16

CFG_8

G16

CFG_9

E16

CFG_10

D15

CFG_11

G15

CFG_12

K15

CFG_13

C15

CFG_14

H16

CFG_15

G18

CFG_16

H15

CFG_17

J25

CFG_18

K27

CFG_19

J26

41-

CFG_20

G28

PM_BMBUSY#

F25

PM_EXTTS#_0

H26

PM_EXTTS#_1

G6

PM_THRMTRIP#

AH33

PWROK

12

AH34

RSTIN#

R150

H28

SDVO_CTRLCLK

H27

SDVO_CTRLDATA

K28

ICH_SYNC#

H32

CLK_REQ#

D1

NC0

C41

NC1

C1

NC2

BA41

NC3

BA40

NC4

BA39

NC5

BA3

NC6

BA2

NC7

BA1

NC8

B41

NC9

B2

NC10

AY41

NC11

AY1

NC12

AW41

NC13

AW1

NC14

A40

NC15

A4

NC16

A39

NC17

A3

NC18

ITL_945PM_MICRO_FCBGA_ACER_1466P

RSVDCFG

CLK

PM

MISC

NC

AY35

SM_CK_0

AR1

SM_CK_1

AW7

SM_CK_2

AW40

SM_CK_3

AW35

SM_CK#_0

AT1

SM_CK#_1

AY7

SM_CK#_2

AY40

SM_CK#_3

AU20

G_CLKIN

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

DMI_TXN(0)

AE35

DMI_TXN(1)

AF39

DMI_TXN(2)

AG35

DMI_TXN(3)

AH39

DMI_TXP(0)

AC35

DMI_TXP(1)

AE39

DMI_TXP(2)

AF35

DMI_TXP(3)

AG39

DMI_RXN(0)

AE37

DMI_RXN(1)

AF41

DMI_RXN(2)

AG37

DMI_RXN(3)

AH41

DMI_RXP(0)

AC37

DMI_RXP(1)

AE41

DMI_RXP(2)

AF37

DMI_RXP(3)

AG41

27-,2527-,2527-,2627-,26-

27-,2527-,2527-,2627-,26-

27-,2527-,2527-,2627-,26-

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

DDR MUXING

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

25-

M_CLK_DDR0

25-

M_CLK_DDR1

26-

M_CLK_DDR2

26-

M_CLK_DDR3

25-

M_CLK_DDR0#

25-

M_CLK_DDR1#

26-

M_CLK_DDR2#

26-

M_CLK_DDR3#

M_CKE0

M_CKE1

M_CKE2

M_CKE3

M_CS0#

M_CS1#

M_CS2#

M_CS3#

M_ODT0

M_ODT1

M_ODT2

M_ODT3

MCH_SMRCOMPN

13-

CLK_R_PEG_MCH#

13-

CLK_R_PEG_MCH

26-,25-,24-,11-,8-

80.6_1%

41-

41-

41-

41-

+V1.8

1

R214

2

DMI_TXN(3:0)

DMI_TXP(3:0)

DMI_RXN(3:0)

DMI_RXP(3:0)

M_OCDCOMP1

C364

1

2

0.47uF_6.3v

OPEN

1

2

1

R626

2

26-,25-,11-

C201

0.1uF_16v

1

2

R213

OPEN

M_VREF

1

R251

2

80.6_1%

MCH_CFG(5)

MCH_CFG(9)

PCIE Graphics

Lane

MCH_CFG(16)

(FSB Dynamic

CFG(3:17) HAS INTERNAL PULL UP

LOW=DMIx2

HIGH=DMIx4

LOW=Reverse Lane

HIGH=Normal operation

LOW=Dynamic ODT

Disable

HIGH=Dynamic ODT

Enable

MCH_CFG(6)

(DDR)

MCH_CFG(10)

HOST PLL VCO

SELECT

LOW=Moby Dick

HIGH=Calistoga

LOW=RESERVED

HIGH=MOBILITY

MCH_CFG(7)

(CPU Strap)

MCH_CFG(11)

LOW=RSVD

HIGH=Mobile CPU

LOW=Calistoga

HIGH=Reserved

MCH_CFG(18)

(VCC Select)

MCH_CFG(20)

(PCIE Backward

Interpoerability

mode)

LOW=1.05V

HIGH=1.5V

LOW=Only SDVO or PCIE x1 is

operational

HIGH=SDVO and PCIE x1 are operating

simultaneously via the PEG port

MCH_CFG(19)

(DMI LANE

REVERSAL)

LOW=Normal

HIGH=LANES REVERSED

CHANGE by

RDEE3

24-Nov-2005

INVENTEC

TITLE

CHEELA

Calistoga-1

SIZE

A3

DOC. NUMBER

CODE

Model_No 000

CS

SHEET

REV

OF

6519

+V1.5S

51-,46-,43-,24-,23-,16-,11-,9-

+VCCP

43-,40-,24-,23-,21-,16-,15-,14-,13-,9-,20-

+VCCP

43-,40-,24-,23-,21-,16-,15-,14-,13-,9-,20-

U23-3

D32

L_BKLTCTL

J30

L_BKLTEN

H30

L_CLKCTLA

H29

L_CLKCTLB

G26

L_DDC_CLK

G25

L_DDC_DATA

B38

L_IBG

C35

L_VBG

F32

L_VDDEN

C33

L_VREFH

C32

L_VREFL

A33

LA_CLK#

A32

LA_CLK

E27

LB_CLK#

E26

LB_CLK

C37

LA_DATA#_0

B35

LA_DATA#_1

A37

LA_DATA#_2

B37

LA_DATA_0

B34

LA_DATA_1

A36

LA_DATA_2

G30

LB_DATA#_0

D30

LB_DATA#_1

F29

LB_DATA#_2

F30

LB_DATA_0

D29

LB_DATA_1

F28

LB_DATA_2

A16

TV_DACA_OUT

C18

TV_DACB_OUT

A19

TV_DACC_OUT

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

K30

TV_DCONSEL0

J29

TV_DCONSEL1

E23

CRT_BLUE

D23

CRT_BLUE#

C22

CRT_GREEN

B22

CRT_GREEN#

A21

CRT_RED

B21

CRT_RED#

C26

CRT_DDC_CLK

C25

CRT_DDC_DATA

G23

CRT_HSYNC

J22

CRT_IREF

H23

CRT_VSYNC

ITL_945PM_MICRO_FCBGA_ACER_1466P

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

LVDS

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

PCI-EXPRESS GRAPHICS

EXP_A_TXN_9

EXP_A_TXN_10

TV

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

VGA

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

+V1.5S_PCIE

R149

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

12

24.9_1%

28-

PEG_C_RXN0

28-

PEG_C_RXN1

28-

PEG_C_RXN2

28-

PEG_C_RXN3

28-

PEG_C_RXN4

28-

PEG_C_RXN5

28-

PEG_C_RXN6

28-

PEG_C_RXN7

28-

PEG_C_RXN8

28-

PEG_C_RXN9

28-

PEG_C_RXN10

28-

PEG_C_RXN11

28-

PEG_C_RXN12

28-

PEG_C_RXN13

28-

PEG_C_RXN14

28-

PEG_C_RXN15

28-

PEG_C_RXP0

28-

PEG_C_RXP1

28-

PEG_C_RXP2

28-

PEG_C_RXP3

28-

PEG_C_RXP4

28-

PEG_C_RXP5

28-

PEG_C_RXP6

28-

PEG_C_RXP7

28-

PEG_C_RXP8

28-

PEG_C_RXP9

28-

PEG_C_RXP10

28-

PEG_C_RXP11

28-

PEG_C_RXP12

28-

PEG_C_RXP13

28-

PEG_C_RXP14

28-

PEG_C_RXP15

20-

PEG_TXN0

20-

PEG_TXN1

20-

PEG_TXN2

20-

PEG_TXN3

20-

PEG_TXN4

20-

PEG_TXN5

20-

PEG_TXN6

20-

PEG_TXN7

20-

PEG_TXN8

20-

PEG_TXN9

20-

PEG_TXN10

20-

PEG_TXN11

20-

PEG_TXN12

20-

PEG_TXN13

20-

PEG_TXN14

20-

PEG_TXN15

20-

PEG_TXP0

20-

PEG_TXP1

20- 28-

PEG_TXP2

20-

PEG_TXP3

20-

PEG_TXP4

20-

PEG_TXP5

20-

PEG_TXP6

20-

PEG_TXP7

20-

PEG_TXP8

20-

PEG_TXP9

20-

PEG_TXP10

20-

PEG_TXP11

20-

PEG_TXP12

20-

PEG_TXP13

20-

PEG_TXP14

20-

PEG_TXP15

23-

PEG_TXP0

PEG_TXN0 PEG_C_TXN0

PEG_TXP1

PEG_TXN1 PEG_C_TXN1

PEG_TXN2 PEG_C_TXN2

PEG_TXN3

PEG_TXP4

PEG_TXN4 PEG_C_TXN4

PEG_TXP5

PEG_TXN5 PEG_C_TXN5

PEG_TXP6

PEG_TXN6 PEG_C_TXN6

PEG_TXN7 PEG_C_TXN7

PEG_TXP8 PEG_C_TXP8

PEG_TXN8 PEG_C_TXN8

PEG_TXP9 PEG_C_TXP9

PEG_TXN9 PEG_C_TXN9

PEG_TXP10 PEG_C_TXP10

PEG_TXN10 PEG_C_TXN10

PEG_TXP11 PEG_C_TXP11

PEG_TXN11 PEG_C_TXN11

PEG_TXP12 PEG_C_TXP12

PEG_TXN12 PEG_C_TXN12

PEG_TXP13 PEG_C_TXP13

PEG_TXN13 PEG_C_TXN13

PEG_TXP14 PEG_C_TXP14

PEG_TXN14 PEG_C_TXN14

PEG_TXP15 PEG_C_TXP15

PEG_TXN15 PEG_C_TXN15

20-

C156

20-

C157

20-

C184

20-

C185

20-

C158

20-

C159

20-

C186

20-

C187

20-

C160

20-

C161

20-

C188

20-

C189

20-

C162

20-

C163

20-

C190

20-

C191

20-

C164

20-

C165

20-

C192

20-

C193

20-

C166

20-

C167

20-

C194

20-

C195

20-

C168

20-

C169

20-

C196

20-

C197

20-

C170

20-

C171

20-

C198

20-

C199

Place to near NB

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v

0.1uF_16v