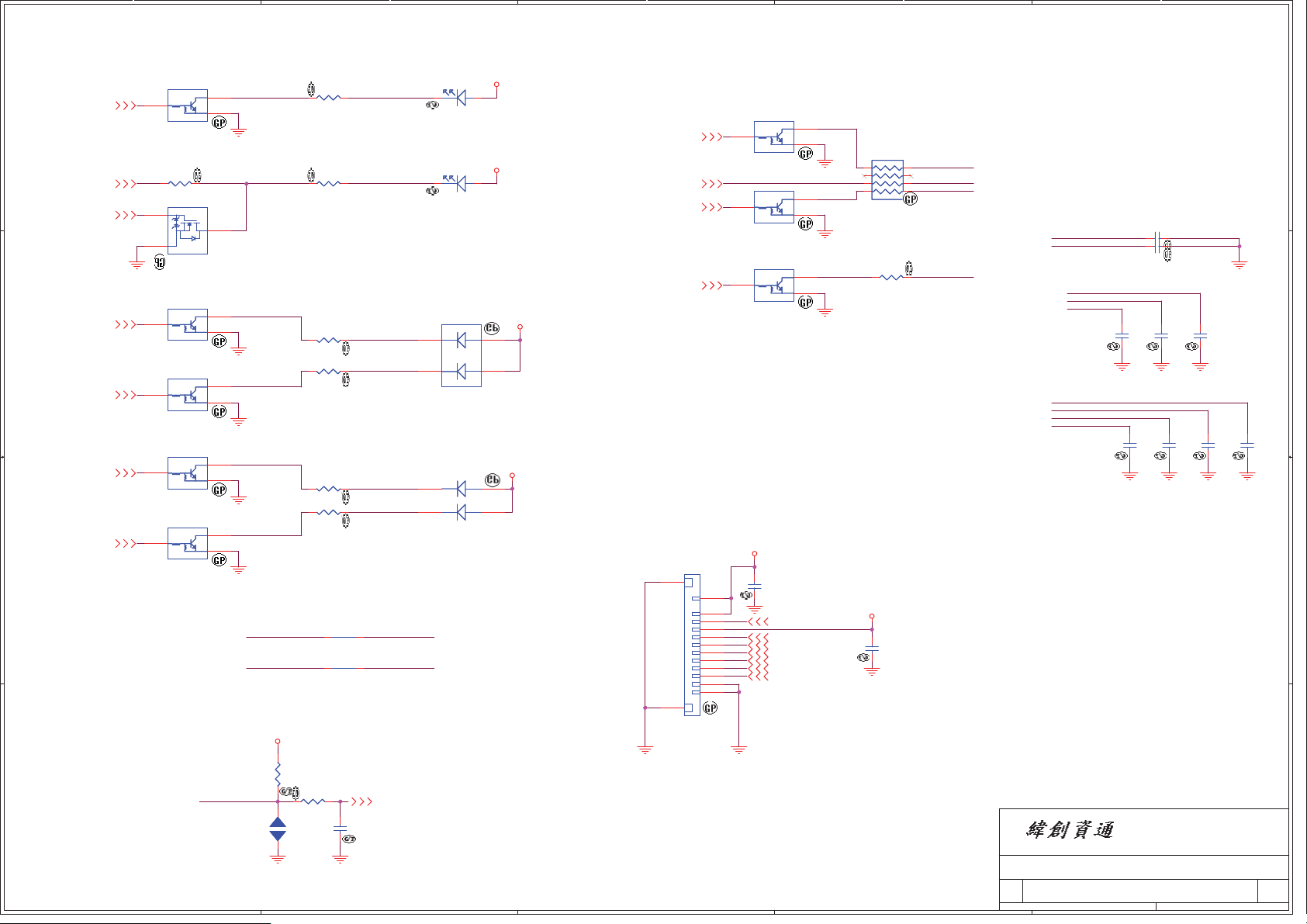

Acer Aspire 8530 Schematics

5

4

3

2

1

Project code: 91.4AJ01.001

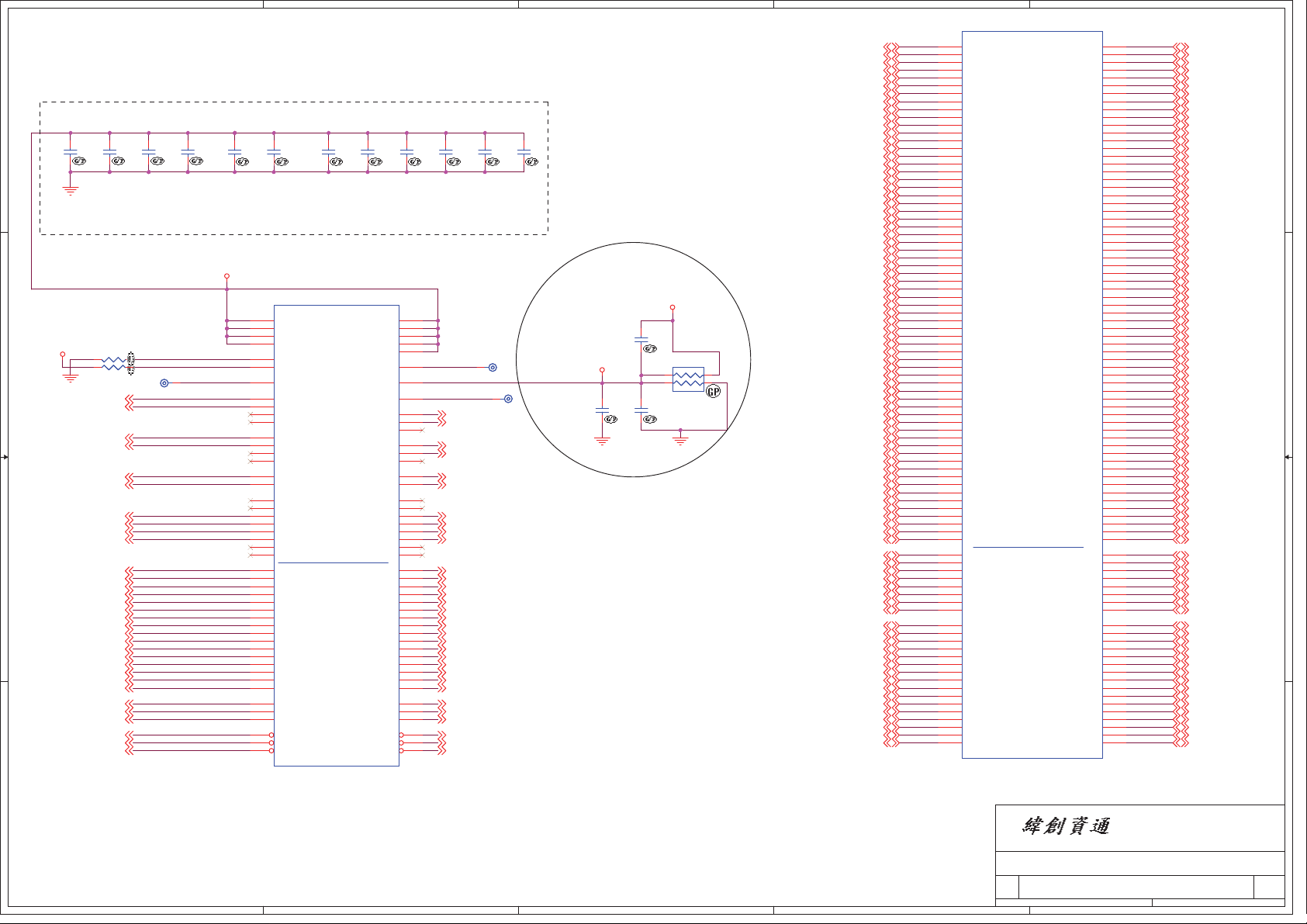

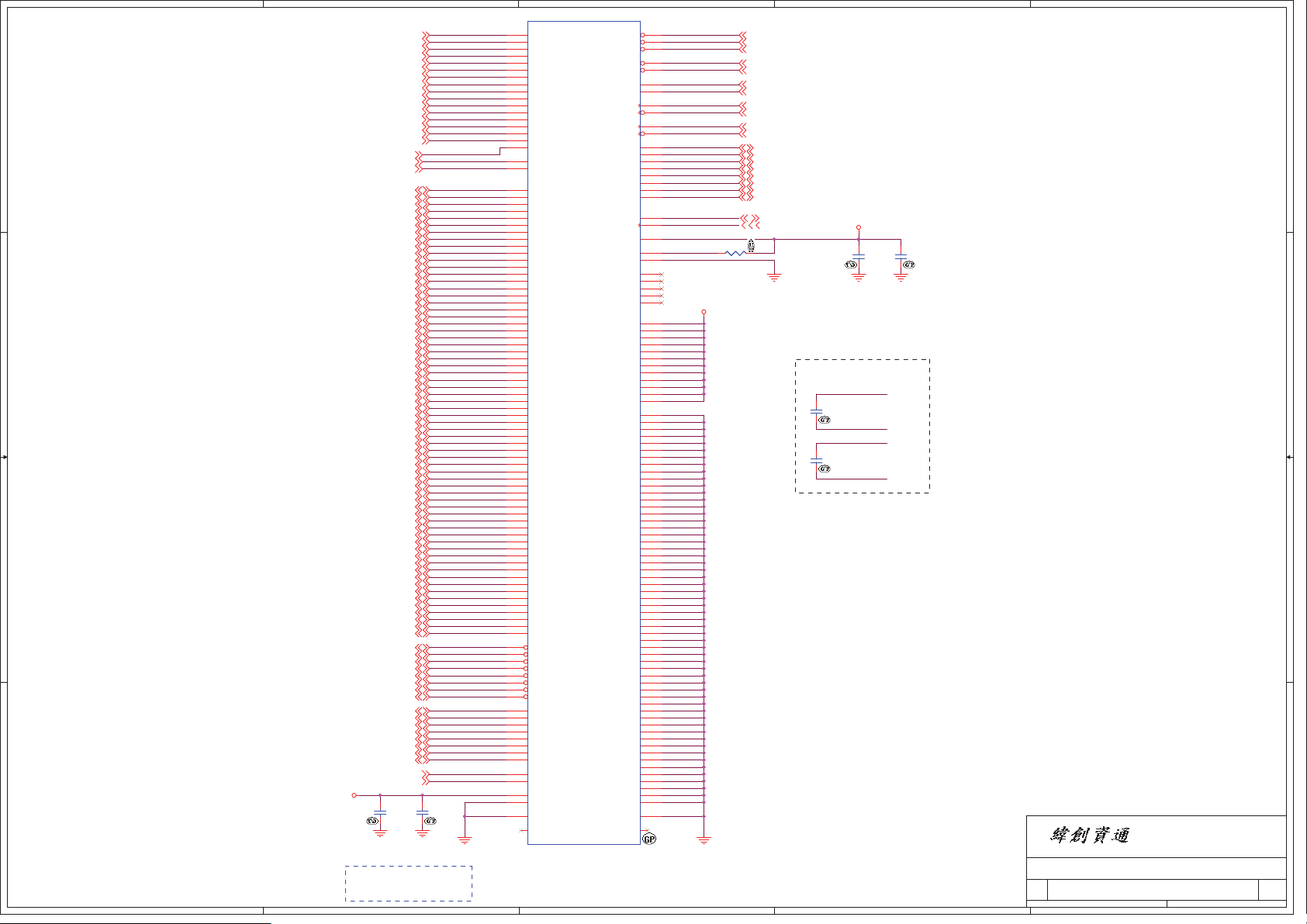

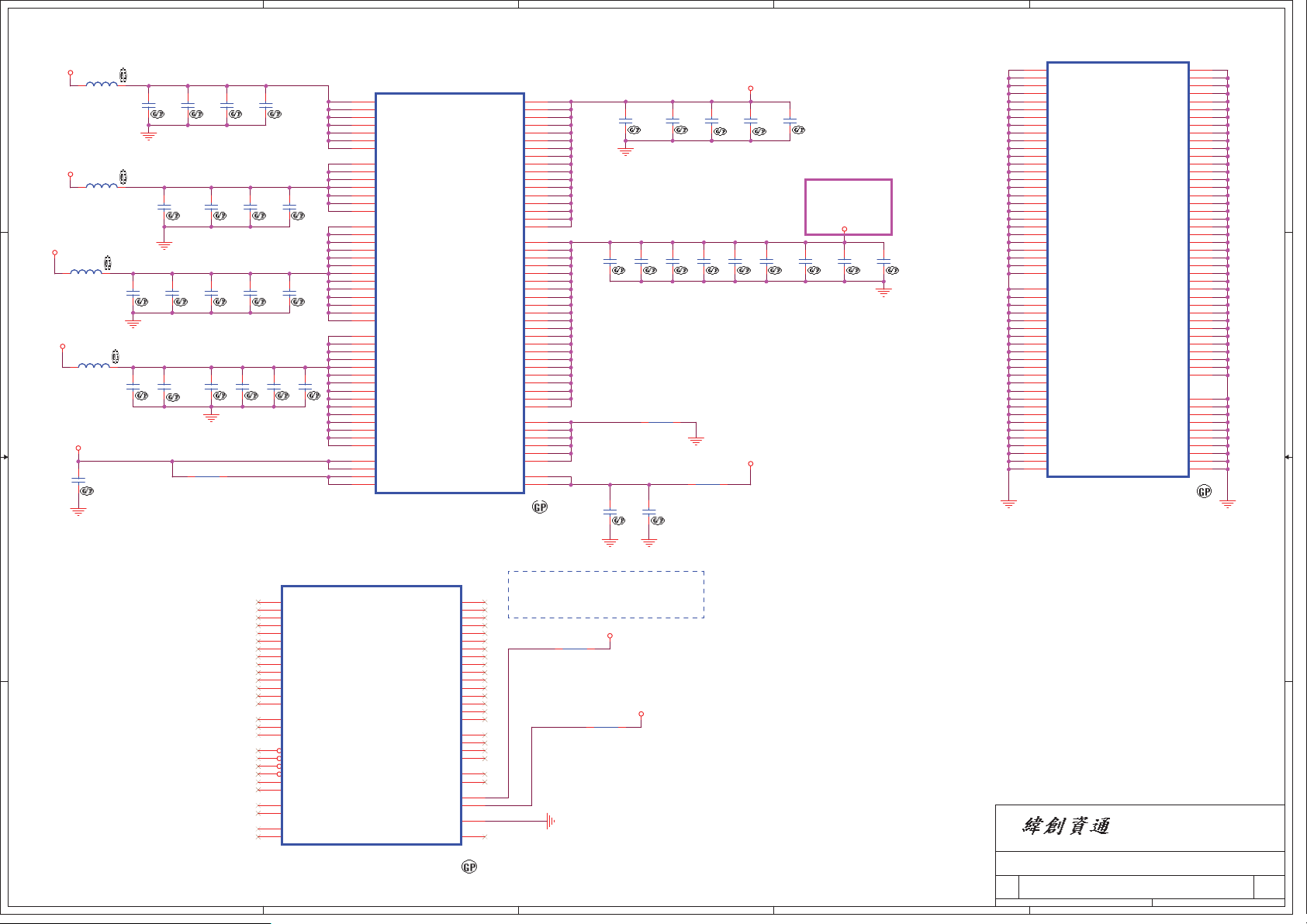

Big Bear 2A (AS 18") Block Diagram

PCB P/N : 48.4AJ01.001

REVISION : 08208-1

3

38

667/800MHz

667/800MHz

AZALIA

AMD Giffin CPU

S1G2 (35W)

638-Pin uFCPGA638

OUT

4,5,6,7

16X16

IN

North Bridge

AMD RS780M

CPU I/F

INTEGRATED GRAHPICS

LVDS, CRT I/F

11,12,13

G792

PCIex16

25

CRT

18

LCD

16

HDMI

19

VGA Borad

35

DDR2

D D

667/800 MHz

8,9

DDR2

667/800 MHz

CLK GEN.

ICS ICS9LPRS480

Line In

40

C C

MIC In

8,9

Codec

ALC888S

40

LAN

Giga LAN

BCM5764MKMLG

New card

SD/SD IO/MMC/MMC

/MS/MS PRO/XD

7 in 1

(10/100/1000Mb)ETHERNET

A-Link

4X4

USB

PCIex1

CardReader

RTS5158E

LPC BUS

Line Out(With-SPDIF)

40

Front.SPKR

40

SUBWOOFER

B B

40

OP AMP

G1412R

OP AMP

G1454R

OP AMP

G1442R

39

39

39

South Bridge

AMD SB700

USB 2.0 12 ports

USB 1.1 2 ports

High Definition Audio

ATA 66/100

ACPI 1.1

LPC I/F

PCI/PCI BRIDGE

20,21,22,23,24

USB

SATA

Mini USB

Blue Tooth

28

RJ11

MODEM

MDC Card

29

Finger

A A

27

HDD SATA I

Printer

31

Camera

USB

4 Port

16

30

KBC

Winbond

WPC773L

Touch

Pad

41 41

41

INT.

KB

TXFM RJ45

33

36 36

BIOS

Winbond

W25X80

Launch

Button

CIR

42

34 34

PWR SW

W83L351

Mini Card

Kedron

Mini Card

TV tuner

42

a/b/g/n

3232

LPC

DEBUG

CONN.

15

37

37

42

ODD SATA

26

HDD SATA II

27

5

4

3

2

PCB STACKUP

TOP

VCC

S

S

GND

BOTTOM

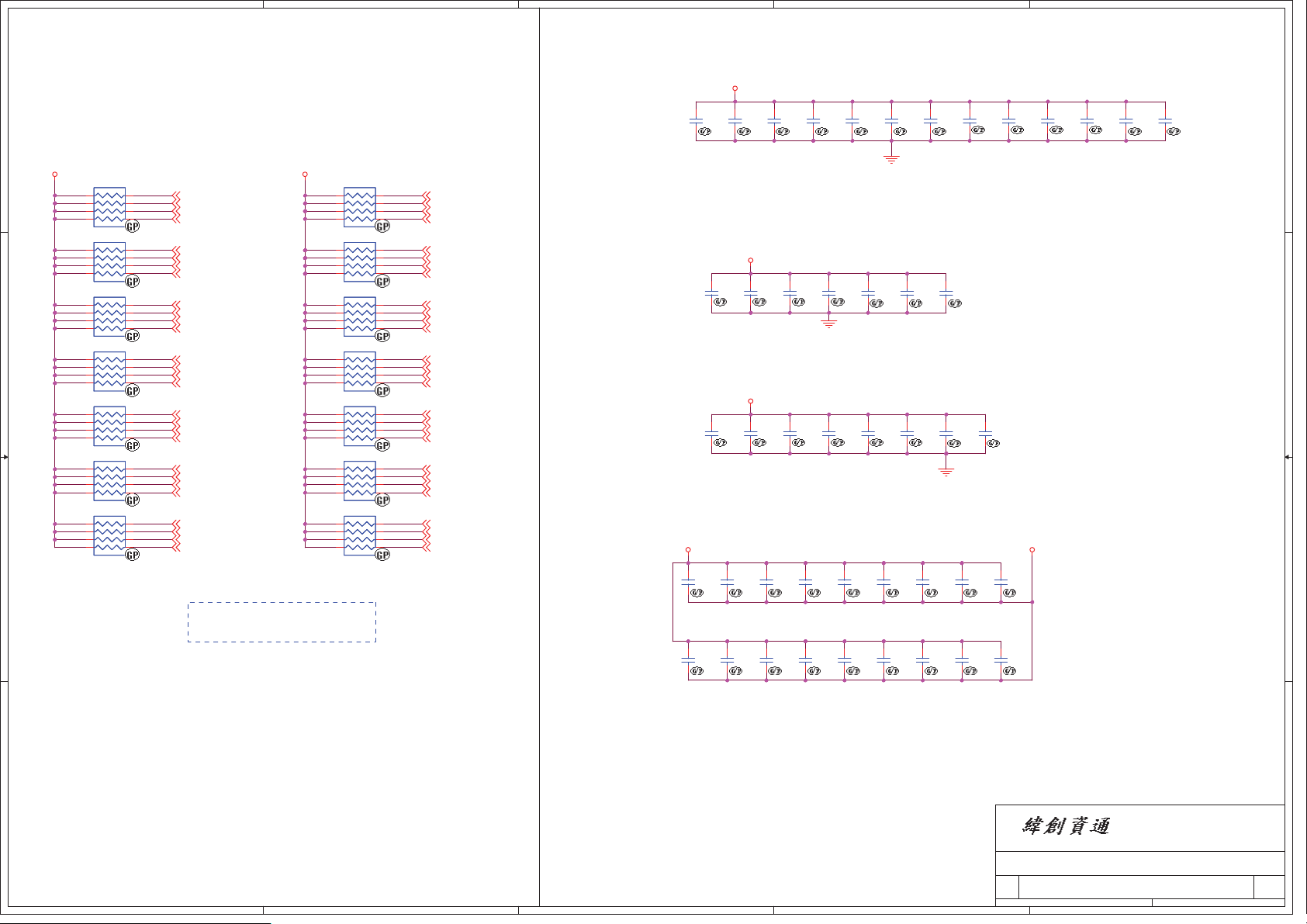

SYSTEM DC/DC

TPS51125

INPUTS

DCBATOUT

SYSTEM DC/DC

TPS51124

INPUTS OUTPUTS

DCBATOUT

SYSTEM DC/DC

TPS51117

INPUTS OUTPUTS

DCBATOUT 1D8V_S3(10A)

RT9026PFP

1D8V_S3

RT9166

3D3V_S0 2D5V_S0

G957

3D3V_S0

G9161

3D3V_S5

CHARGER

DCBATOUT

CPU DC/DC

INPUTS

DCBATOUT

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

A3

A3

A3

Big Bear 2A

Big Bear 2A

Big Bear 2A

1

OUTPUTS

5V_S5(7A)

3D3V_S5(7A)

1D1V_S0(8A)

1D2V_S0(5A)

DDR_VREF_S3

0D9V_S3(1A)

(300mA)

1D5V_S0(1A)

1D2V_S5

(400mA)

MAX8731A

OUTPUTSINPUTS

CHG_PWR

18V 6.0A

UP+5V

5V 100mA

ISL6265HR

OUTPUTS

VCC_CORE_S0_0

0~1.55V 18A

VCC_CORE_S0_1

0~1.55V 18A

VDDNB

0~1.55V 18A

of

155Monday, October 27, 2008

of

155Monday, October 27, 2008

of

155Monday, October 27, 2008

47

48

49

50

50

50

50

51

46

SC

SC

SC

5

D D

C C

4

3

2

1

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

HISTORY

HISTORY

HISTORY

Big Bear 2A

Big Bear 2A

Big Bear 2A

of

255Monday, October 27, 2008

of

255Monday, October 27, 2008

of

255Monday, October 27, 2008

1

SA

SA

SA

5

4

3

2

1

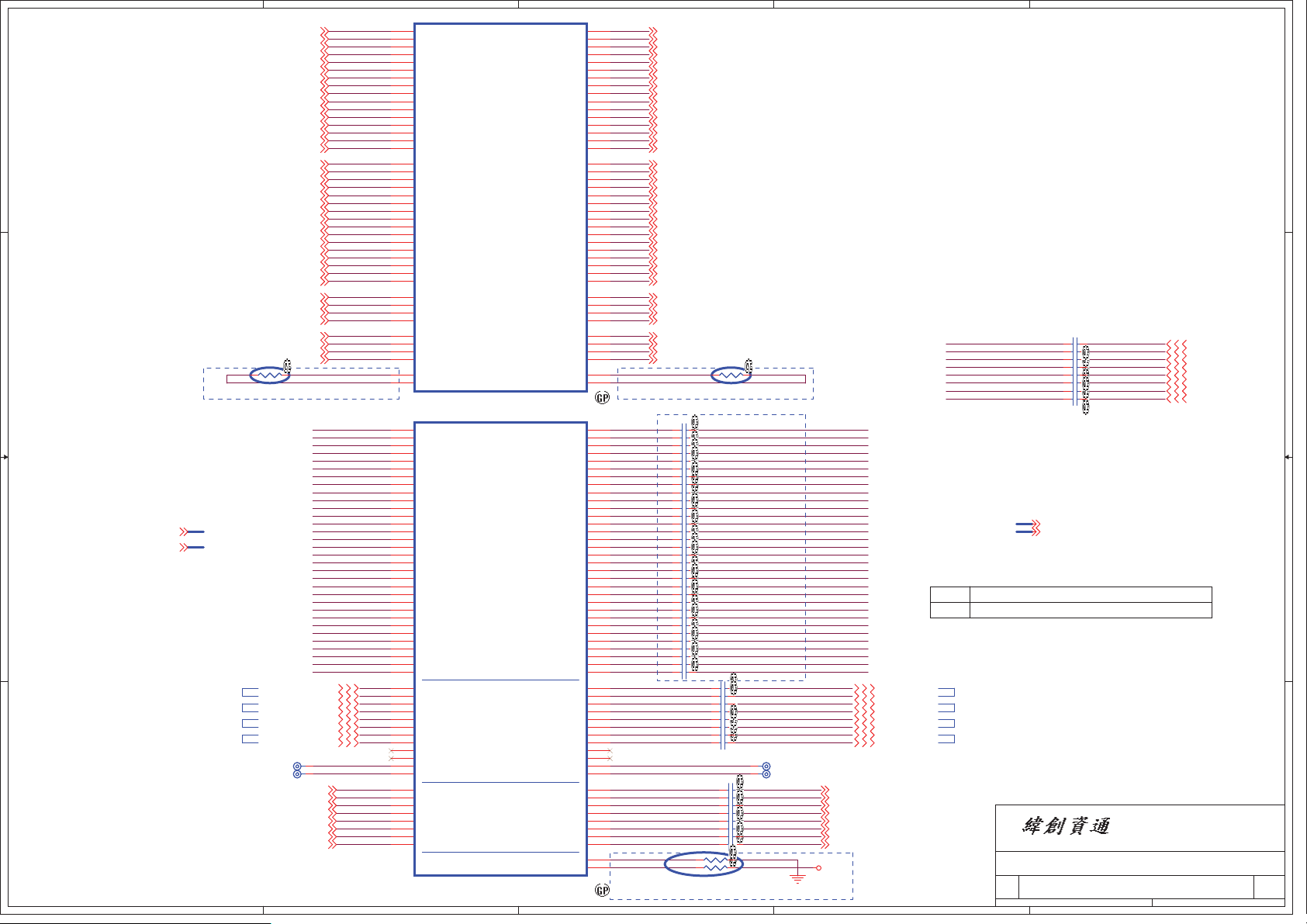

3D3V_S0 3D3V_CLK_VDD

0R0603-PAD

0R0603-PAD

1 2

R138

R138

-1_1014

D D

-1_1014

3D3V_S0

0R0603-PAD

0R0603-PAD

1 2

R150

R150

1D1V_S0 1D1V_CLK_VDDIO

DY

DY

R151

R151

1 2

0R3-0-U-GP

0R3-0-U-GP

C C

B B

DY

DY

R144

R144

10KR2J-3-GP

10KR2J-3-GP

A A

DY

DY

R146

R146

10KR2J-3-GP

10KR2J-3-GP

DY

DY

10KR2J-3-GP

10KR2J-3-GP

1 2

DY

DY

10KR2J-3-GP

10KR2J-3-GP

1 2

R147

R147

R149

R149

12

C361

C361

CLK_PCIE_MINI137

CLK_PCIE_MINI1#37

CLK_PCIE_NEW36

CLK_PCIE_NEW#36

CLK_PCIE_LAN#33

CLK_PCIE_MINI237

CLK_PCIE_MINI2#37

3D3V_S0

12

12

C343

C343

C340

C340

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

12

C362

C362

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

CLK_PCIE_SB20

CLK_PCIE_SB#20

CLK_PCIE_LAN33

CLK_NB_GPPSB12

CLK_NB_GPPSB#12

TP152TPAD14-GP TP152TPAD14-GP

TP153TPAD14-GP TP153TPAD14-GP

CLK_NBHT_CLK12

CLK_NBHT_CLK#12

DY

DY

R145

R145

10KR2J-3-GP

10KR2J-3-GP

1 2

DY

DY

R143

R143

10KR2J-3-GP

10KR2J-3-GP

1 2

5

12

C344

C344

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

12

12

C352

C352

C347

C347

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

3D3V_CLK_VDD

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1 2

1 2

12

C341

C341

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C356

C356

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

0R0603-PAD

0R0603-PAD

1 2

R141

R141

-1_1014

-1_1014

-1_1014

-1_1014

-1_1014

-1_1014

REF2

REF1

REF0

12

12

C357

C357

C354

C354

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C342

C342

C358

C358

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

-1_1014

12

C353

C353

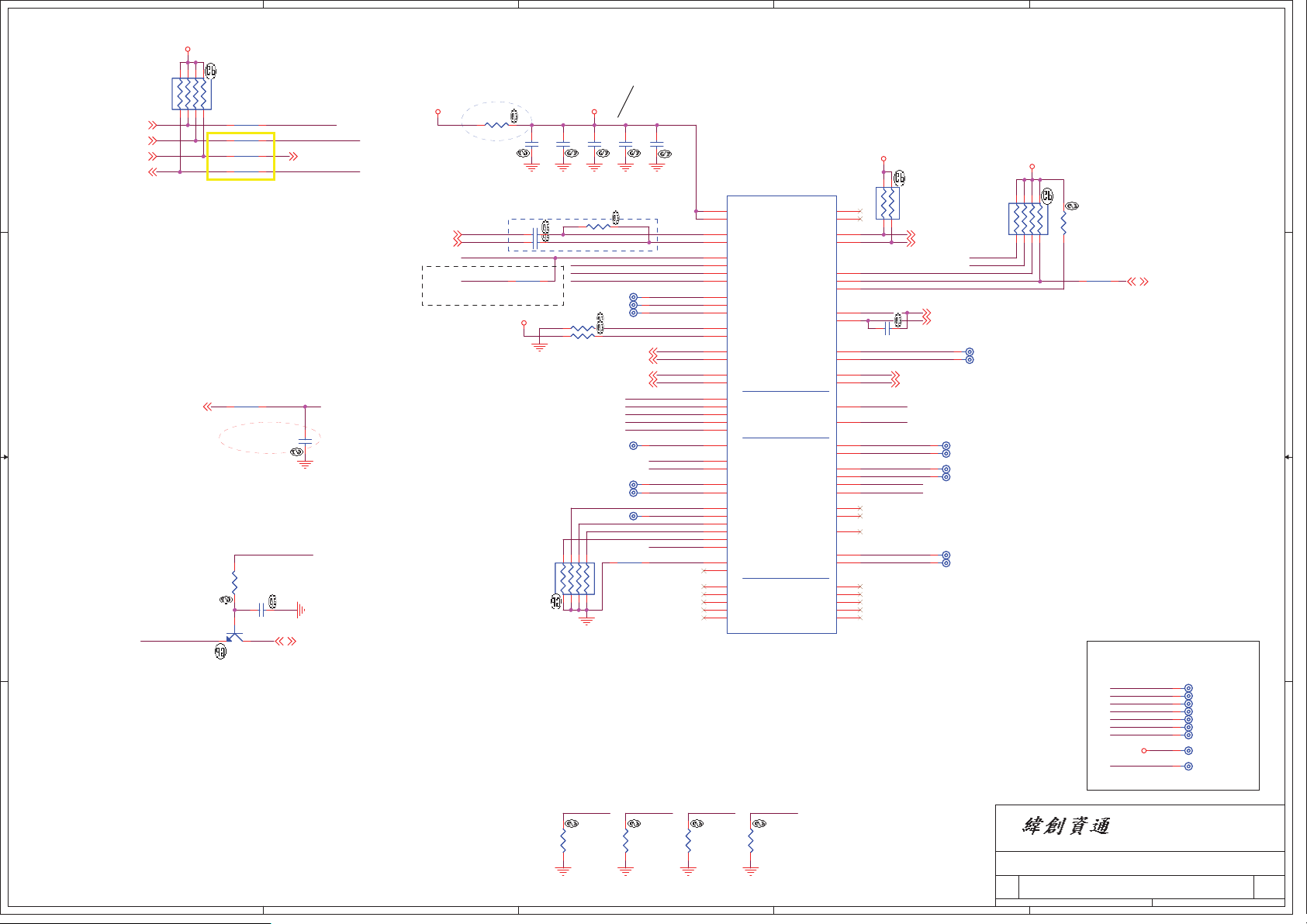

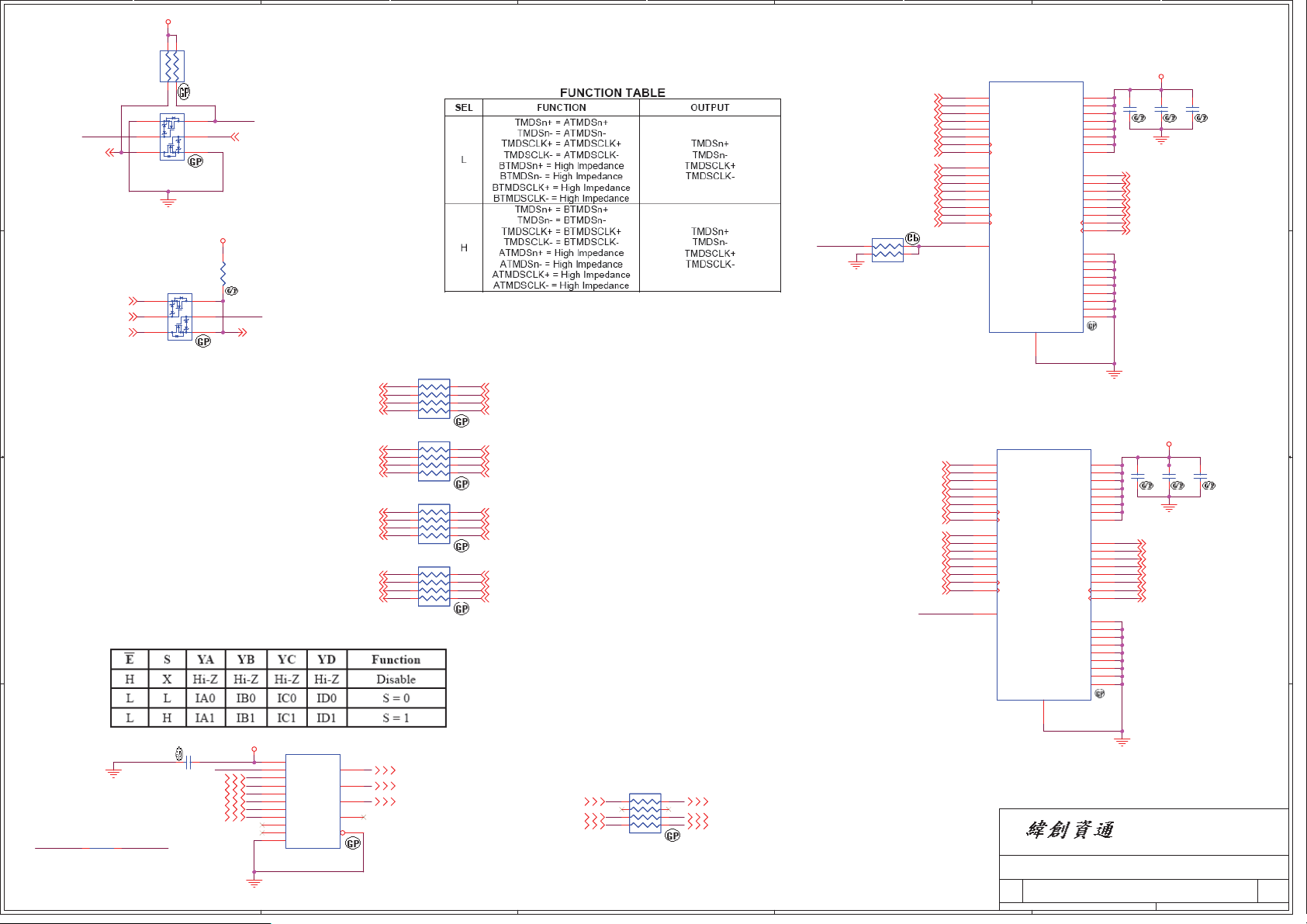

CLK_SRC0T_LPRS

CLK_SRC0C_LPRS

-1_1014

3D3V_S0

R142 10KR2J-3-GPR142 10KR2J-3-GP

SEL_27

REF2

SEL_SATA

REF1

SEL_HTT66

REF0

* default

CPU_CLK(200MHz)

12

C359

C359

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1D1V_CLK_VDDIO

3D3V_48MPWR_S0

1

0

*

1

*0

1

0 * 100MHz differential HTT clock

12

12

C360

C360

C355

C355

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

3D3V_CLK_VDD

26

25

48

47

16

17

11

35

34

40

4

PD#

55

56

63

51

22

21

20

19

15

14

13

12

9

8

41

6

5

37

36

32

31

54

53

VDD_REF

PD#

12

27MHz non-spreading singled clock on pin 5

and 27MHz spread clock on pin 6

100MHz differential spreading SRC clock

100MHz non-spreading differential SATA clock

100MHz differential spreading SRC clock

66MHz 3.3V single ended HTT clock

4

U13

U13

VDDATIG

VDDATIG_IO

VDDCPU

VDDCPU_IO

VDDSRC

VDDSRC_IO

VDDSRC_IO

VDDSB_SRC

VDDSB_SRC_IO

VDDSATA

VDD

VDDHTT

VDDREF

VDD48

PD#

SRC0T_LPRS

SRC0C_LPRS

SRC1T_LPRS

SRC1C_LPRS

SRC2T_LPRS

SRC2C_LPRS

SRC3T_LPRS

SRC3C_LPRS

SRC4T_LPRS

SRC4C_LPRS

SRC6T/SATAT_LPRS42GNDSATA

SRC6C/SATAC_LPRS

SRC7T_LPRS/27MHZ_SS

SRC7C_LPRS/27MHZ_NS

SB_SRC0T_LPRS

SB_SRC0C_LPRS

SB_SRC1T_LPRS

SB_SRC1C_LPRS

HTT0T_LPRS/66M

HTT0C_LPRS/66M

ICS9LPRS480BKLFT-GP

ICS9LPRS480BKLFT-GP

71.09480.A03

71.09480.A03

2nd = SLG:71.08628.003

2nd = SLG:71.08628.003

SMBCLK

SMBDAT

ATIG0T_LPRS

ATIG0C_LPRS

ATIG1T_LPRS

ATIG1C_LPRS

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

CPUKG0T_LPRS

CPUKG0C_LPRS

48MHZ_0

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

GNDATIG

GNDHTT

GNDREF

GNDCPU

GND48

GNDSRC

GNDSRC

GNDSB_SRC

REF0

GND

GND

61

X1

62

X2

2

3

30

29

28

27

23

45

44

39

38

50

49

64

59

58

57

43

24

7

52

60

46

1

10

18

33

65

3D3V_S0

GEN_XTAL_IN

GEN_XTAL_OUT

CLK_SMBCLK

CLK_SMBDAT

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

CPU_CLK_R

CPU_CLK#_R

CLK_48

REF0

REF1

REF2

OSC_14M_NB

1.1V 158R/90.9RRS780M

3

R139

R139

1 2

2R3J-GP

2R3J-GP

3000mA.80ohm

R140

R140

1 2

DY

DY

10MR2J-L-GP

10MR2J-L-GP

CL=20pF±0.2pF

G8

G8

G9

G9

GAP-CLOSE

GAP-CLOSE

GAP-CLOSE

GAP-CLOSE

-1_1014

TP257 TPAD14-GPTP257 TPAD14-GP

TP157 TPAD14-GPTP157 TPAD14-GP

TP156 TPAD14-GPTP156 TPAD14-GP

TP155 TPAD14-GPTP155 TPAD14-GP

TP154 TPAD14-GPTP154 TPAD14-GP

-1_1014

RN50

RN50

1

4

2 3

SRN10J-7-GP

SRN10J-7-GP

R148150R2F-1-GP R148150R2F-1-GP

12

R15275R2F-2-GP R15275R2F-2-GP

12

12

12

C345

C345

DY

DY

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC33P50V2JN-3GP

SC33P50V2JN-3GP

X-14D31818MHZ-4-GP

X-14D31818MHZ-4-GP

82.30005.A41

82.30005.A41

2ND = 82.30005.891

2ND = 82.30005.891

12

SMBC0_SB 8,9,21

12

SMBD0_SB 8,9,21

-1_1014

CLKREQ# Internal

pull high

CPU_CLK 6

CPU_CLK# 6

12

EC108

EC108

SC5P50V2CN-2GP

SC5P50V2CN-2GP

CLK_NB_14M 12

3D3V_48MPWR_S0

C348

C348

SC1U10V2KX-1GP

SC1U10V2KX-1GP

X2

X2

12

SC33P50V2JN-3GP

SC33P50V2JN-3GP

CLK_PCIE_PEG 35

CLK_PCIE_PEG# 35

CLK_NB_GFX 12

CLK_NB_GFX# 12

12

EC109

EC109

SC5P50V2CN-2GP

SC5P50V2CN-2GP

C351

C351

12

C346

C346

12

CLK48_USB 21

CLK48_5158E 32

Due to PLL issue on current clock chip, the SBlink clock

need to come from SRC clocks for RS740 and RS780.

Future clock chip revision will fix this.

Clock chip has internal serial terminations

for differencial pairs, external resistors are

reserved for debug purpose.

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK 100M DIFF 100M DIFF

* RS780 can be used as clock buffer to output two PCIE referecence clocks

By deault, chip will configured as input mode, BIOS can program it to output mode.

2

RS740 RX780 RS780

66M SE(SINGLE END)

NC

14M SE (3.3V) 14M SE (1.8V) 14M SE (1.1V)

NC NC vref

100M DIFF

NC

100M DIFF

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

100M DIFF

100M DIFF

100M DIFF

100M DIFF

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CLKGEN_ICS9LPRS480

CLKGEN_ICS9LPRS480

CLKGEN_ICS9LPRS480

Big Bear 2A

Big Bear 2A

Big Bear 2A

100M DIFF

100M DIFF

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

355Monday, October 27, 2008

355Monday, October 27, 2008

355Monday, October 27, 2008

1

of

of

of

SA

SA

SA

5

D D

1D2V_S0

Place close to socket

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SCD22U6D3V2KX-1GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

12

C436

C436

C434

C434

DY

DY

C C

B B

SCD22U6D3V2KX-1GP

12

C468

C468

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

12

C472

C472

4

12

C433

C433

3

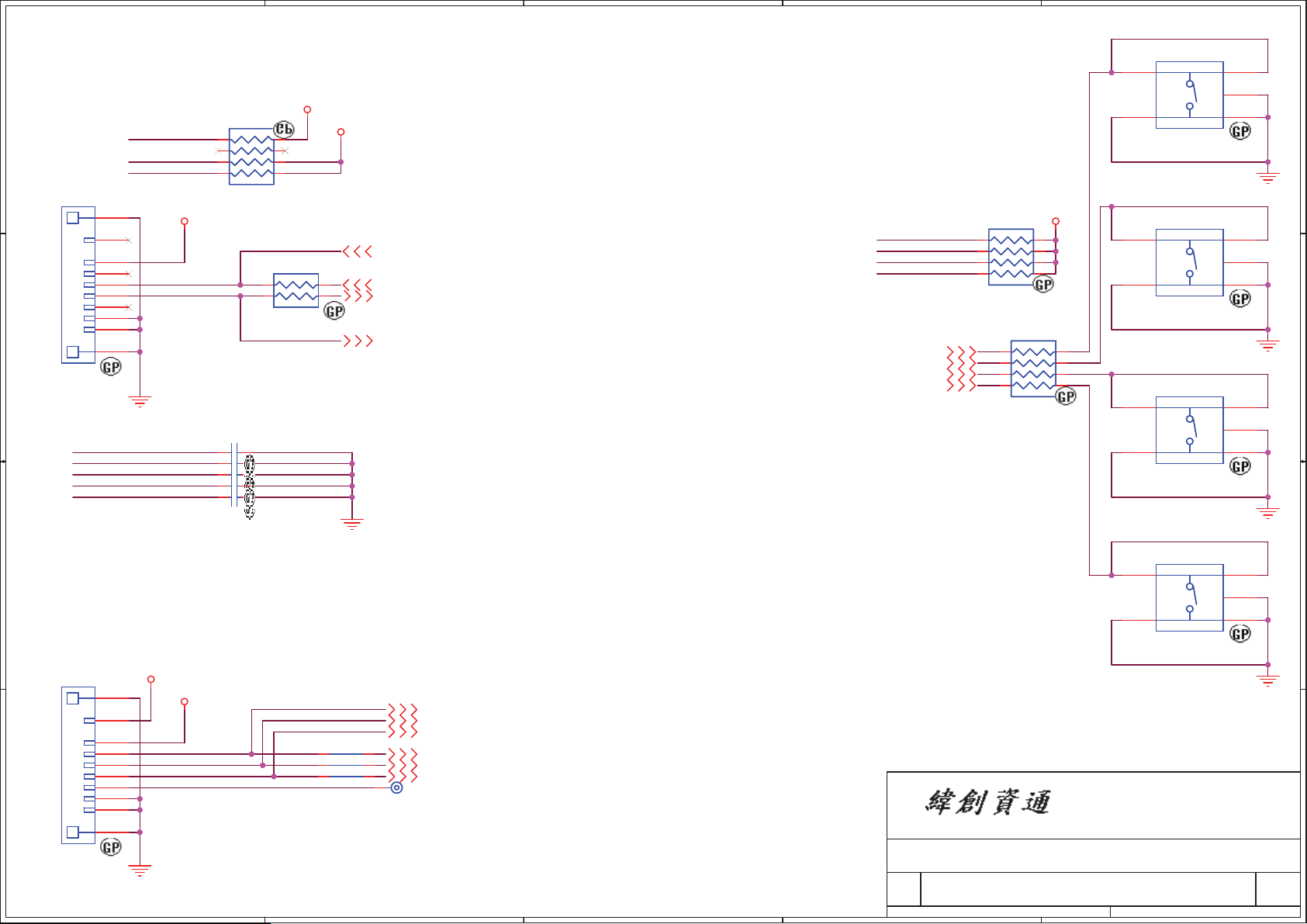

U38A

U38A

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

1.5Amp

HT LINK

HT LINK

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

HT_CPU_NB_CAD_H0 11

HT_CPU_NB_CAD_L0 11

HT_CPU_NB_CAD_H1 11

HT_CPU_NB_CAD_L1 11

HT_CPU_NB_CAD_H2 11

HT_CPU_NB_CAD_L2 11

HT_CPU_NB_CAD_H3 11

HT_CPU_NB_CAD_L3 11

HT_CPU_NB_CAD_H4 11

HT_CPU_NB_CAD_L4 11

HT_CPU_NB_CAD_H5 11

HT_CPU_NB_CAD_L5 11

HT_CPU_NB_CAD_H6 11

HT_CPU_NB_CAD_L6 11

HT_CPU_NB_CAD_H7 11

HT_CPU_NB_CAD_L7 11

HT_CPU_NB_CAD_H8 11

HT_CPU_NB_CAD_L8 11

HT_CPU_NB_CAD_H9 11

HT_CPU_NB_CAD_L9 11

HT_CPU_NB_CAD_H10 11

HT_CPU_NB_CAD_L10 11

HT_CPU_NB_CAD_H11 11

HT_CPU_NB_CAD_L11 11

HT_CPU_NB_CAD_H12 11

HT_CPU_NB_CAD_L12 11

HT_CPU_NB_CAD_H13 11

HT_CPU_NB_CAD_L13 11

HT_CPU_NB_CAD_H14 11

HT_CPU_NB_CAD_L14 11

HT_CPU_NB_CAD_H15 11

HT_CPU_NB_CAD_L15 11

HT_CPU_NB_CLK_H0 11

HT_CPU_NB_CLK_L0 11

HT_CPU_NB_CLK_H1 11

HT_CPU_NB_CLK_L1 11

HT_CPU_NB_CTL_H0 11

HT_CPU_NB_CTL_L0 11

HT_CPU_NB_CTL_H1 11

HT_CPU_NB_CTL_L1 11

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

12

C473

C473

HT_NB_CPU_CAD_H011

HT_NB_CPU_CAD_L011

HT_NB_CPU_CAD_H111

HT_NB_CPU_CAD_L111

HT_NB_CPU_CAD_H211

HT_NB_CPU_CAD_L211

HT_NB_CPU_CAD_H311

HT_NB_CPU_CAD_L311

HT_NB_CPU_CAD_H411

HT_NB_CPU_CAD_L411

HT_NB_CPU_CAD_H511

HT_NB_CPU_CAD_L511

HT_NB_CPU_CAD_H611

HT_NB_CPU_CAD_L611

HT_NB_CPU_CAD_H711

HT_NB_CPU_CAD_L711

HT_NB_CPU_CAD_H811

HT_NB_CPU_CAD_L811

HT_NB_CPU_CAD_H911

HT_NB_CPU_CAD_L911

HT_NB_CPU_CAD_H1011

HT_NB_CPU_CAD_L1011

HT_NB_CPU_CAD_H1111

HT_NB_CPU_CAD_L1111

HT_NB_CPU_CAD_H1211

HT_NB_CPU_CAD_L1211

HT_NB_CPU_CAD_H1311

HT_NB_CPU_CAD_L1311

HT_NB_CPU_CAD_H1411

HT_NB_CPU_CAD_L1411

HT_NB_CPU_CAD_H1511

HT_NB_CPU_CAD_L1511

HT_NB_CPU_CLK_H011

HT_NB_CPU_CLK_L011

HT_NB_CPU_CLK_H111

HT_NB_CPU_CLK_L111

HT_NB_CPU_CTL_H011

HT_NB_CPU_CTL_L011

HT_NB_CPU_CTL_H111

HT_NB_CPU_CTL_L111

C432

C432

D1

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

SKT-CPU638P-GP-U2

SKT-CPU638P-GP-U2

62.10055.111

62.10055.111

2ND = 62.10055.251

2ND = 62.10055.251

2

1

SKT-BGA638H176

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

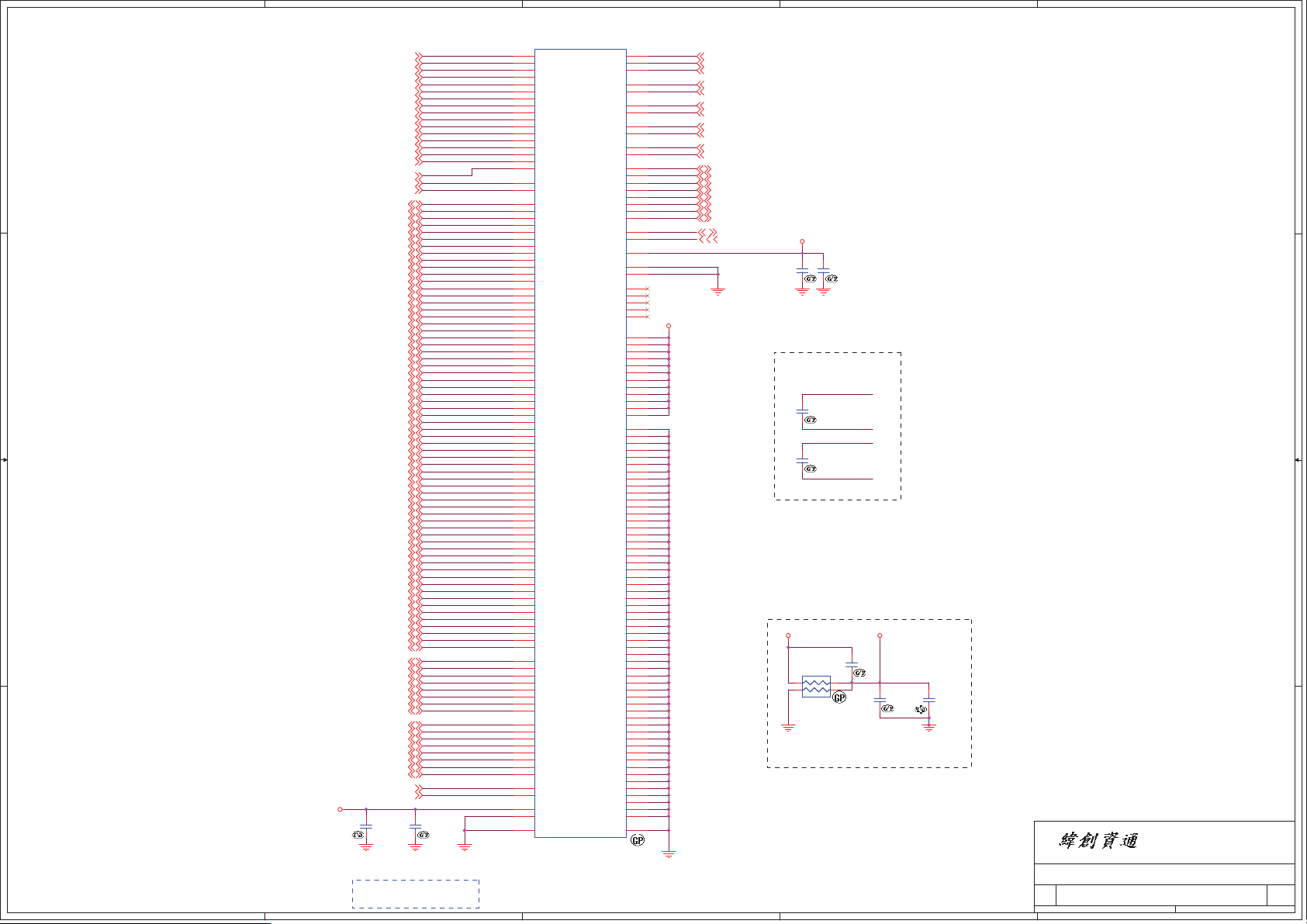

CPU_HT_LINK I/F_(1/4)

CPU_HT_LINK I/F_(1/4)

CPU_HT_LINK I/F_(1/4)

Big Bear 2A

Big Bear 2A

Big Bear 2A

455Monday, October 27, 2008

455Monday, October 27, 2008

455Monday, October 27, 2008

1

of

of

of

SA

SA

SA

5

Place near to CPU

D D

C51

C51

1D8V_S3

C C

B B

A A

4.7u x 4 0.22u X 2 180P x 6

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

12

12

C191

C191

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

R221

R221

39D2R2F-L-GP

39D2R2F-L-GP

1 2

1 2

R225

R225

39D2R2F-L-GP

39D2R2F-L-GP

MEM_MA0_ODT08,10

MEM_MA0_ODT18,10

MEM_MA0_CS#08,10

MEM_MA0_CS#18,10

MEM_MA_CKE08,10

MEM_MA_CKE18,10

MEM_MA_CLK0_P8

MEM_MA_CLK0_N8

MEM_MA_CLK1_P8

MEM_MA_CLK1_N8

MEM_MA_ADD08,10

MEM_MA_ADD18,10

MEM_MA_ADD28,10

MEM_MA_ADD38,10

MEM_MA_ADD48,10

MEM_MA_ADD58,10

MEM_MA_ADD68,10

MEM_MA_ADD78,10

MEM_MA_ADD88,10

MEM_MA_ADD98,10

MEM_MA_ADD108,10

MEM_MA_ADD118,10

MEM_MA_ADD128,10

MEM_MA_ADD138,10

MEM_MA_ADD148,10

MEM_MA_ADD158,10

MEM_MA_BANK08,10

MEM_MA_BANK18,10

MEM_MA_BANK28,10

MEM_MA_RAS#8,10

MEM_MA_CAS#8,10

MEM_MA_WE#8,10

12

C192

C192

C50

C50

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

TP48TP48

SCD22U6D3V2KX-1GP

12

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

0D9V_S3

MEMZP

MEMZN

MEM_RSVD_M1

1

12

C53

C53

D10

C10

B10

AD10

AF10

AE10

H16

T19

V22

U21

V19

T20

U19

U20

V20

N19

N20

E16

F16

Y16

AA16

P19

P20

N21

M20

N22

M19

M22

M24

K22

R21

K20

V24

K24

K19

R20

R23

R19

T22

T24

J22

J20

L20

L21

L19

L22

J21

12

C156

C156

U38B

U38B

VTT1

VTT2

VTT3

VTT4

MEMZP

MEMZN

RSVD_M1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

SKT-CPU638P-GP-U2

SKT-CPU638P-GP-U2

62.10055.111

62.10055.111

2ND = 62.10055.251

2ND = 62.10055.251

12

C187

C187

SC180P50V2JN-1GP

SC180P50V2JN-1GP

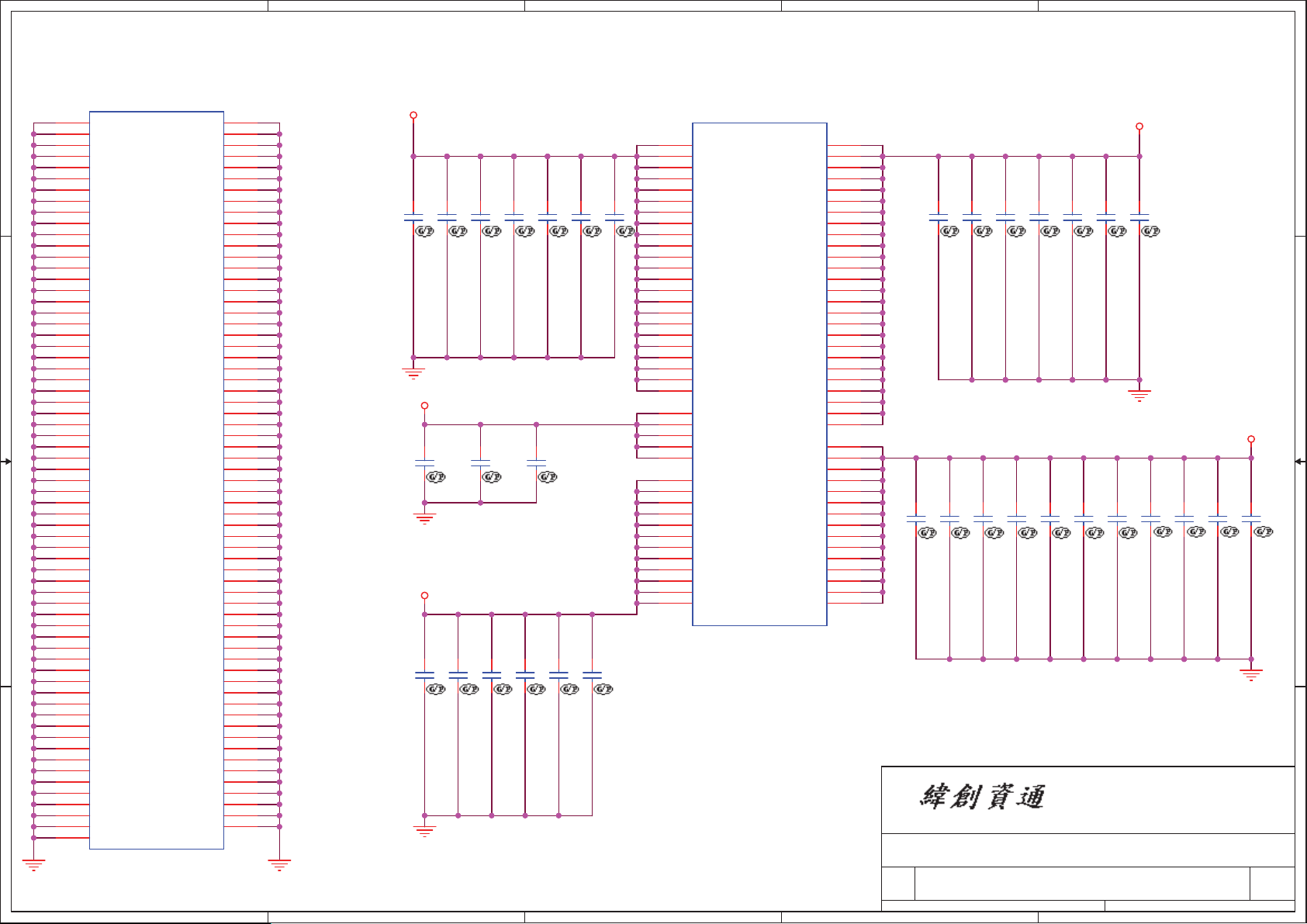

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

C189

C189

12

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

C56

C56

4

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

DY

DY

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

12

C54

C54

SC180P50V2JN-1GP

SC180P50V2JN-1GP

VTT_SENSE

MEM_RSVD_M2

MEM_MB0_ODT0 9,10

MEM_MB0_ODT1 9,10

MEM_MB0_CS#0 9,10

MEM_MB0_CS#1 9,10

MEM_MB_CKE0 9,10

MEM_MB_CKE1 9,10

MEM_MB_CLK0_P 9

MEM_MB_CLK0_N 9

MEM_MB_CLK1_P 9

MEM_MB_CLK1_N 9

MEM_MB_ADD0 9,10

MEM_MB_ADD1 9,10

MEM_MB_ADD2 9,10

MEM_MB_ADD3 9,10

MEM_MB_ADD4 9,10

MEM_MB_ADD5 9,10

MEM_MB_ADD6 9,10

MEM_MB_ADD7 9,10

MEM_MB_ADD8 9,10

MEM_MB_ADD9 9,10

MEM_MB_ADD10 9,10

MEM_MB_ADD11 9,10

MEM_MB_ADD12 9,10

MEM_MB_ADD13 9,10

MEM_MB_ADD14 9,10

MEM_MB_ADD15 9,10

MEM_MB_BANK0 9,10

MEM_MB_BANK1 9,10

MEM_MB_BANK2 9,10

MEM_MB_RAS# 9,10

MEM_MB_CAS# 9,10

MEM_MB_WE# 9,10

C185

C185

SC180P50V2JN-1GP

SC180P50V2JN-1GP

1

12

1

12

C61

C61

SC180P50V2JN-1GP

SC180P50V2JN-1GP

TP24 TPAD14-GPTP24 TPAD14-GP

TP71TP71

CLOSE TO CPU

C55

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

VREF_DDR_CLAW

C55

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C60

C60

12

C62

C62

12

3

1D8V_S3

RN4

RN4

1

2 3

SRN1KJ-7-GP

SRN1KJ-7-GP

2

U38C

U38C

MEM_MA_DATA08

MEM_MA_DATA18

MEM_MA_DATA28

MEM_MA_DATA38

MEM_MA_DATA48

MEM_MA_DATA58

MEM_MA_DATA68

MEM_MA_DATA78

MEM_MA_DATA88

MEM_MA_DATA98

MEM_MA_DATA108

MEM_MA_DATA118

MEM_MA_DATA128

MEM_MA_DATA138

MEM_MA_DATA148

MEM_MA_DATA158

MEM_MA_DATA168

MEM_MA_DATA178

MEM_MA_DATA188

MEM_MA_DATA198

MEM_MA_DATA208

MEM_MA_DATA218

MEM_MA_DATA228

MEM_MA_DATA238

MEM_MA_DATA248

MEM_MA_DATA258

MEM_MA_DATA268

MEM_MA_DATA278

MEM_MA_DATA288

MEM_MA_DATA298

MEM_MA_DATA308

MEM_MA_DATA318

MEM_MA_DATA328

MEM_MA_DATA338

MEM_MA_DATA348

MEM_MA_DATA358

MEM_MA_DATA368

MEM_MA_DATA378

MEM_MA_DATA388

MEM_MA_DATA398

MEM_MA_DATA408

4

MEM_MA_DATA418

MEM_MA_DATA428

MEM_MA_DATA438

MEM_MA_DATA448

MEM_MA_DATA458

MEM_MA_DATA468

MEM_MA_DATA478

MEM_MA_DATA488

MEM_MA_DATA498

MEM_MA_DATA508

MEM_MA_DATA518

MEM_MA_DATA528

MEM_MA_DATA538

MEM_MA_DATA548

MEM_MA_DATA558

MEM_MA_DATA568

MEM_MA_DATA578

MEM_MA_DATA588

MEM_MA_DATA598

MEM_MA_DATA608

MEM_MA_DATA618

MEM_MA_DATA628

MEM_MA_DATA638

MEM_MA_DM08

MEM_MA_DM18

MEM_MA_DM28

MEM_MA_DM38

MEM_MA_DM48

MEM_MA_DM58

MEM_MA_DM68

MEM_MA_DM78

MEM_MA_DQS0_P8

MEM_MA_DQS0_N8

MEM_MA_DQS1_P8

MEM_MA_DQS1_N8

MEM_MA_DQS2_P8

MEM_MA_DQS2_N8

MEM_MA_DQS3_P8

MEM_MA_DQS3_N8

MEM_MA_DQS4_P8

MEM_MA_DQS4_N8

MEM_MA_DQS5_P8

MEM_MA_DQS5_N8

MEM_MA_DQS6_P8

MEM_MA_DQS6_N8

MEM_MA_DQS7_P8

MEM_MA_DQS7_N8

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

SKT-CPU638P-GP-U2

SKT-CPU638P-GP-U2

2ND = 62.10055.251

2ND = 62.10055.251

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

62.10055.111

62.10055.111

<Core Design>

<Core Design>

<Core Design>

MEM:DATA

MEM:DATA

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

Y11

AE14

AF14

AF11

AD11

A12

B16

A22

E25

AB26

AE22

AC16

AD12

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

1

MEM_MB_DATA0 9

MEM_MB_DATA1 9

MEM_MB_DATA2 9

MEM_MB_DATA3 9

MEM_MB_DATA4 9

MEM_MB_DATA5 9

MEM_MB_DATA6 9

MEM_MB_DATA7 9

MEM_MB_DATA8 9

MEM_MB_DATA9 9

MEM_MB_DATA10 9

MEM_MB_DATA11 9

MEM_MB_DATA12 9

MEM_MB_DATA13 9

MEM_MB_DATA14 9

MEM_MB_DATA15 9

MEM_MB_DATA16 9

MEM_MB_DATA17 9

MEM_MB_DATA18 9

MEM_MB_DATA19 9

MEM_MB_DATA20 9

MEM_MB_DATA21 9

MEM_MB_DATA22 9

MEM_MB_DATA23 9

MEM_MB_DATA24 9

MEM_MB_DATA25 9

MEM_MB_DATA26 9

MEM_MB_DATA27 9

MEM_MB_DATA28 9

MEM_MB_DATA29 9

MEM_MB_DATA30 9

MEM_MB_DATA31 9

MEM_MB_DATA32 9

MEM_MB_DATA33 9

MEM_MB_DATA34 9

MEM_MB_DATA35 9

MEM_MB_DATA36 9

MEM_MB_DATA37 9

MEM_MB_DATA38 9

MEM_MB_DATA39 9

MEM_MB_DATA40 9

MEM_MB_DATA41 9

MEM_MB_DATA42 9

MEM_MB_DATA43 9

MEM_MB_DATA44 9

MEM_MB_DATA45 9

MEM_MB_DATA46 9

MEM_MB_DATA47 9

MEM_MB_DATA48 9

MEM_MB_DATA49 9

MEM_MB_DATA50 9

MEM_MB_DATA51 9

MEM_MB_DATA52 9

MEM_MB_DATA53 9

MEM_MB_DATA54 9

MEM_MB_DATA55 9

MEM_MB_DATA56 9

MEM_MB_DATA57 9

MEM_MB_DATA58 9

MEM_MB_DATA59 9

MEM_MB_DATA60 9

MEM_MB_DATA61 9

MEM_MB_DATA62 9

MEM_MB_DATA63 9

MEM_MB_DM0 9

MEM_MB_DM1 9

MEM_MB_DM2 9

MEM_MB_DM3 9

MEM_MB_DM4 9

MEM_MB_DM5 9

MEM_MB_DM6 9

MEM_MB_DM7 9

MEM_MB_DQS0_P 9

MEM_MB_DQS0_N 9

MEM_MB_DQS1_P 9

MEM_MB_DQS1_N 9

MEM_MB_DQS2_P 9

MEM_MB_DQS2_N 9

MEM_MB_DQS3_P 9

MEM_MB_DQS3_N 9

MEM_MB_DQS4_P 9

MEM_MB_DQS4_N 9

MEM_MB_DQS5_P 9

MEM_MB_DQS5_N 9

MEM_MB_DQS6_P 9

MEM_MB_DQS6_N 9

MEM_MB_DQS7_P 9

MEM_MB_DQS7_N 9

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CPU_DDR_(2/4)

CPU_DDR_(2/4)

CPU_DDR_(2/4)

Big Bear 2A

Big Bear 2A

Big Bear 2A

SA

SA

of

555Monday, October 27, 2008

of

555Monday, October 27, 2008

of

555Monday, October 27, 2008

1

SA

5

4

3

2

1

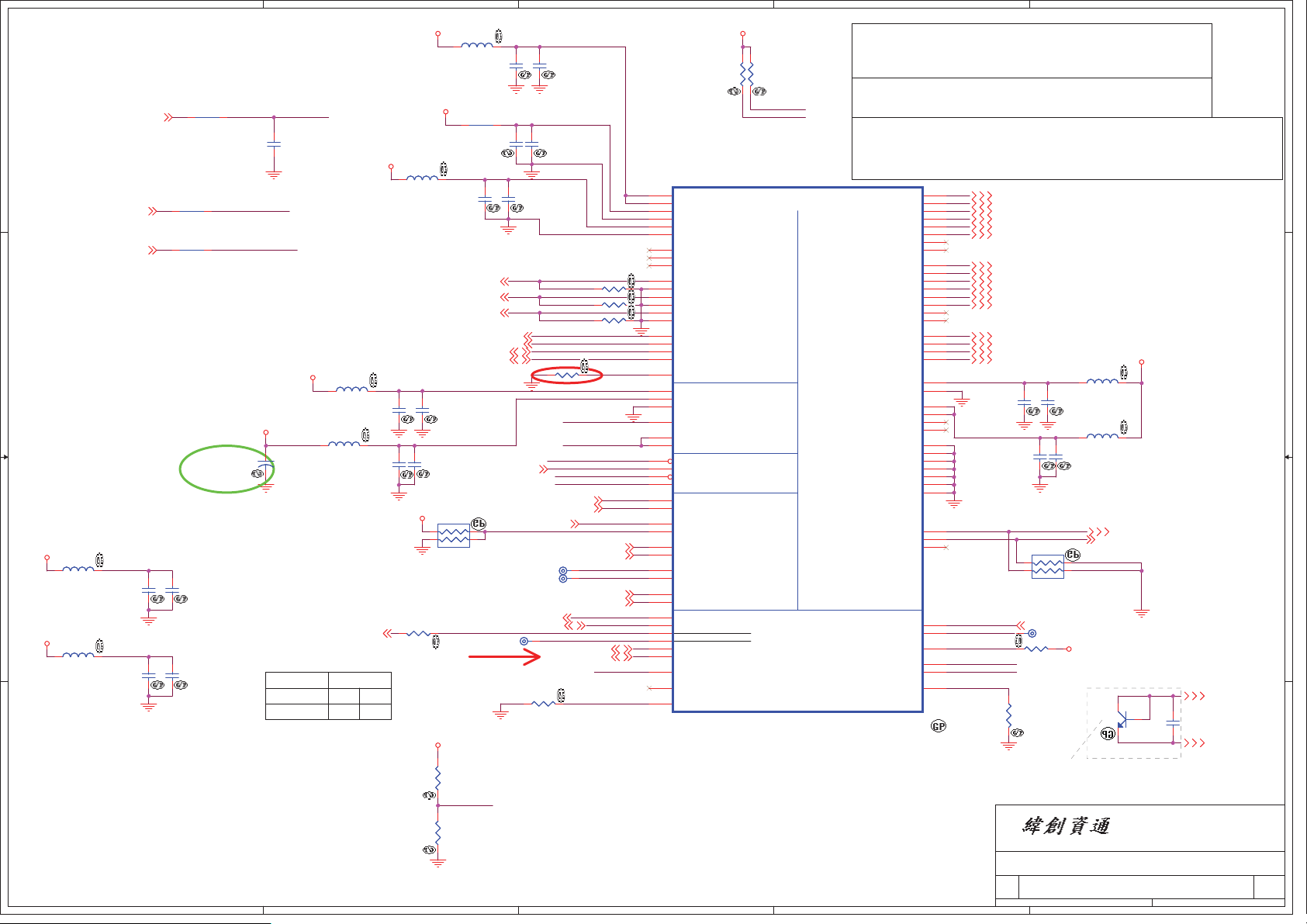

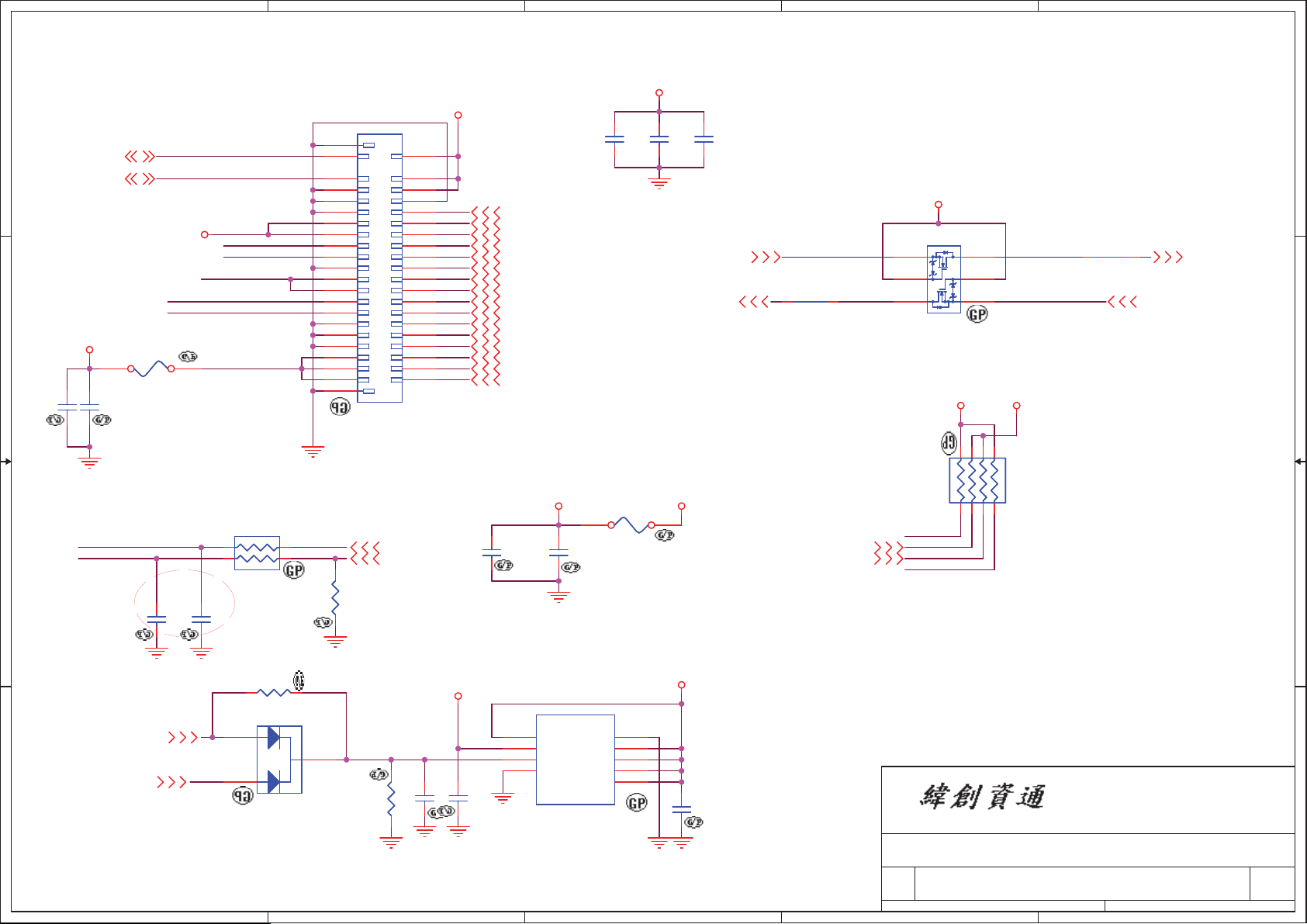

1D8V_S0

678

RN31

RN31

SRN300J-1-GP

SRN300J-1-GP

123

D D

CPU_LDT_RST#20,53

CPU_PWRGD20,53

CPU_LDT_STOP#20

ALLOW_LDTSTOP12,20

4 5

R257

R257

1 2

0R0402-PAD

0R0402-PAD

R258

R258

1 2

0R0402-PAD

0R0402-PAD

R62

R62

1 2

0R0402-PAD

0R0402-PAD

R255

R255

1 2

0R0402-PAD

0R0402-PAD

-1_1014

LDT_RST#_CPU

CPU_LDT_REQ#_CPU

LDT_PWROK

LDT_STP#_CPU 12

IF 0 ohm IS NOT GOOD ENOUGH, TRY 68.00082.491

R55

R55

1 2

0R3-0-U-GP

0R3-0-U-GP

2D5V_VDDA_S02D5V_S0

12

12

C163

C163

C162

C162

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

DY

DY

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

C153

C153

SB with 0402 PAD

Cloce To CPU

CPU_CLK3

CPU_CLK#3

LDT_RST#_CPU

HDT_RST#

For HDT DBG

C C

1 2

C481 SC3900P50V2KX-2GPC481 SC3900P50V2KX-2GP

1 2

C488 SC3900P50V2KX-2GPC488 SC3900P50V2KX-2GP

1 2

R256

R256

0R0402-PAD

0R0402-PAD

1D2V_S0

-1_1014

LDT_PWROK

R259

R259

CPU_PWRGD_SVID_REG46

B B

THERMTRIP#

CPU exceeds to 125

1 2

0R0402-PAD

0R0402-PAD

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Near CPU PIN

LDT_PWROK

12

R261

R261

2K2R2J-2-GP

2K2R2J-2-GP

C482

C482

1 2

1D8V_SUS_Q2

B

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Q21

Q21

C

E

MMBT3904-4-GP

MMBT3904-4-GP

84.T3904.C11

84.T3904.C11

2ND = 84.03904.T11

2ND = 84.03904.T11

12

C483

C483

DY

DY

KBC_THERMTRIP# 25,41

к

RN84

RN84

SRN300J-1-GP

SRN300J-1-GP

1 2

R263 169R2F-GPR263 169R2F-GP

LDT_PWROK

LDT_STP#_CPU

CPU_LDT_REQ#_CPU

1 2

R48 44D2R2F-GPR48 44D2R2F-GP

1 2

R49 44D2R2F-GPR49 44D2R2F-GP

CPU_VDD0_RUN_FB_H46

CPU_VDD0_RUN_FB_L46

CPU_VDD1_RUN_FB_H46

CPU_VDD1_RUN_FB_L46

123

45

678

LYAOUT:ROUTE VDDA TRACE APPROX.

50mils WIDE(USE 2X25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

C161

C161

SCD22U10V3KX-2GP

12

C164

C164

SC3300P50V2KX-1GP

SC3300P50V2KX-1GP

TP180TPAD14-GPTP180TPAD14-GP

TP175TPAD14-GPTP175TPAD14-GP

TP174TPAD14-GPTP174TPAD14-GP

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

TP69TP69

TP65TP65

TP64TP64

TP176TP176

R254

R254

1 2

0R0402-PAD

0R0402-PAD

SCD22U10V3KX-2GP

12

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

CLKCPU_IN

CLKCPU#_IN

CPU_SIC

1

CPU_SID

1

CPU_ALERT#

1

CPU_HTREF0

CPU_HTREF1

CPU_TEST23

1

CPU_TEST18

CPU_TEST19

CPU_TEST25_H

1

CPU_TEST25_L

1

CPU_TEST21

CPU_TEST20

1

CPU_TEST24

CPU_TEST22

CPU_TEST12

CPU_TEST27

CPU_TEST9

U38D

U38D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

AB6

VDD1_FB_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

SKT-CPU638P-GP-U2

SKT-CPU638P-GP-U2

62.10055.111

62.10055.111

2ND = 62.10055.251

2ND = 62.10055.251

KEY1

KEY2

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

1D8V_S3

4

RN30

RN30

SRN1KJ-7-GP

M11

W18

A6

A4

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

SRN1KJ-7-GP

SRN300J-1-GP

1

2 3

THERMTRIP#

PROCHOT#

CPU_MEMHOT#

internal pull high 300 ohm

1 2

DY

DY

C58

C58

SC100P50V2JN-3GP

SC100P50V2JN-3GP

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_VDDNB_RUN_FB_H 46

CPU_VDDNB_RUN_FB_L 46

CPU_DBREQ#

CPU_TDO

CPU_TEST28_H

CPU_TEST28_L

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST29H

CPU_TEST29L

SRN300J-1-GP

CPU_SVC 46

CPU_SVD 46

H_THERMDC 25

H_THERMDA 25

1

1

LAYOUT: Route FBCLKOUT_H/L

differentially impedance 80

1

TP52TP52

1

TP54TP54

1

TP68TP68

1

TP63TP63

1

TP184TP184

1

TP185TP185

RN65

RN65

CPU_TEST27

CPU_DBREQ#

TP28TP28

TP27TP27

1D8V_S3

678

123

4 5

R433

R433

300R2J-4-GP

300R2J-4-GP

DY

DY

1 2

-1_1014

R227

R227

1 2

0R0402-PAD

0R0402-PAD

HDT Connectors

1D8V_S3

The Processor has

reached a preset

maximum operating

temperature. 100

I=Active HTC

O=FAN

PROCHOT#_SB 20

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

HDT_RST#

1

1

1

1

1

1

1

1

1

TP17 TPAD14-GPTP17 TPAD14-GP

TP50 TPAD14-GPTP50 TPAD14-GP

TP21 TPAD14-GPTP21 TPAD14-GP

TP23 TPAD14-GPTP23 TPAD14-GP

TP20 TPAD14-GPTP20 TPAD14-GP

TP19 TPAD14-GPTP19 TPAD14-GP

TP18 TPAD14-GPTP18 TPAD14-GP

TP29 TPAD14-GPTP29 TPAD14-GP

TP183TPAD14-GPTP183TPAD14-GP

к

A A

R45

R226

R226

300R2J-4-GP

300R2J-4-GP

DY

DY

1 2

5

4

R45

300R2J-4-GP

300R2J-4-GP

DY

DY

1 2

CPU_TEST14 CPU_TEST15CPU_TEST18CPU_TEST19

R432

R431

R431

300R2J-4-GP

300R2J-4-GP

DY

DY

1 2

3

R432

300R2J-4-GP

300R2J-4-GP

DY

DY

1 2

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

CPU_Control&Debug_(3/4)

CPU_Control&Debug_(3/4)

CPU_Control&Debug_(3/4)

Big Bear 2A

Big Bear 2A

Big Bear 2A

655Monday, October 27, 2008

655Monday, October 27, 2008

655Monday, October 27, 2008

1

of

of

of

SC

SC

SC

5

U38F

U38F

AA4

D D

C C

B B

A A

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

SKT-CPU638P-GP-U2

SKT-CPU638P-GP-U2

62.10055.111

62.10055.111

2ND = 62.10055.251

2ND = 62.10055.251

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

5

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

4

VCC_CORE_S0_0

Bottom Side Decoupling Bottom Side Decoupling

C118

C118

C130

C130

12

12

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VDDNB

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1D8V_S3

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C76

C76

Bottom Side Decoupling

C158

C158

C93

C93

12

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

4

C119

C119

C117

C117

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C120

C120

12

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

3A for VDDNB

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

C102

C102

C127

C127

12

C64

C64

12

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

12

C89

C89

DY

DY

C157

C157

12

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C116

C116

12

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C84

C84

12

DY

DY

3

36A for VDD0&VDD1

C100

C100

12

SC180P50V2JN-1GP

SC180P50V2JN-1GP

3

U38E

U38E

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

SKT-CPU638P-GP-U2

SKT-CPU638P-GP-U2

62.10055.111

62.10055.111

2ND = 62.10055.251

2ND = 62.10055.251

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

2

C86

C86

C85

12

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

C85

12

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C65

C65

12

Place near to CPU

C77

C83

C83

12

SC180P50V2JN-1GP

SC180P50V2JN-1GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

2

C77

C98

C98

DY

DY

12

12

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

CPU_Power_(4/4)

CPU_Power_(4/4)

CPU_Power_(4/4)

Big Bear 2A

Big Bear 2A

Big Bear 2A

SCD01U50V2KX-1GP

SCD01U50V2KX-1GP

C72

C72

DY

DY

12

1

VCC_CORE_S0_1

C80

C79

C79

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C63

C63

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C78

C78

12

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C80

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

3A for VDDIO

C90

C90

C112

C121

C121

12

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

C112

C74

C74

C71

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

DY

DY

12

755Monday, October 27, 2008

755Monday, October 27, 2008

755Monday, October 27, 2008

C71

DY

DY

12

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

1

DY

DY

12

12

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

SCD22U6D3V2KX-1GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

of

of

of

1D8V_S3

C108

C108

12

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C106

C106

12

SA

SA

SA

5

D D

MEM_MA_DATA05

MEM_MA_DATA15

MEM_MA_DATA25

MEM_MA_DATA35

MEM_MA_DATA45

MEM_MA_DATA55

MEM_MA_DATA65

MEM_MA_DATA75

MEM_MA_DATA85

MEM_MA_DATA95

MEM_MA_DATA105

MEM_MA_DATA115

MEM_MA_DATA125

MEM_MA_DATA135

MEM_MA_DATA145

MEM_MA_DATA155

MEM_MA_DATA165

MEM_MA_DATA175

MEM_MA_DATA185

MEM_MA_DATA195

C C

B B

A A

5

VREF_DDR_MEM

MEM_MA_DATA205

MEM_MA_DATA215

MEM_MA_DATA225

MEM_MA_DATA235

MEM_MA_DATA245

MEM_MA_DATA255

MEM_MA_DATA265

MEM_MA_DATA275

MEM_MA_DATA285

MEM_MA_DATA295

MEM_MA_DATA305

MEM_MA_DATA315

MEM_MA_DATA325

MEM_MA_DATA335

MEM_MA_DATA345

MEM_MA_DATA355

MEM_MA_DATA365

MEM_MA_DATA375

MEM_MA_DATA385

MEM_MA_DATA395

MEM_MA_DATA405

MEM_MA_DATA415

MEM_MA_DATA425

MEM_MA_DATA435

MEM_MA_DATA445

MEM_MA_DATA455

MEM_MA_DATA465

MEM_MA_DATA475

MEM_MA_DATA485

MEM_MA_DATA495

MEM_MA_DATA505

MEM_MA_DATA515

MEM_MA_DATA525

MEM_MA_DATA535

MEM_MA_DATA545

MEM_MA_DATA555

MEM_MA_DATA565

MEM_MA_DATA575

MEM_MA_DATA585

MEM_MA_DATA595

MEM_MA_DATA605

MEM_MA_DATA615

MEM_MA_DATA625

MEM_MA_DATA635

4

MEM_MA_ADD05,10

MEM_MA_ADD15,10

MEM_MA_ADD25,10

MEM_MA_ADD35,10

MEM_MA_ADD45,10

MEM_MA_ADD55,10

MEM_MA_ADD65,10

MEM_MA_ADD75,10

MEM_MA_ADD85,10

MEM_MA_ADD95,10

MEM_MA_ADD105,10

MEM_MA_ADD115,10

MEM_MA_ADD125,10

MEM_MA_ADD135,10

MEM_MA_ADD145,10

MEM_MA_ADD155,10

MEM_MA_BANK25,10

MEM_MA_BANK05,10

MEM_MA_BANK15,10

MEM_MA_DQS0_N5

MEM_MA_DQS1_N5

MEM_MA_DQS2_N5

MEM_MA_DQS3_N5

MEM_MA_DQS4_N5

MEM_MA_DQS5_N5

MEM_MA_DQS6_N5

MEM_MA_DQS7_N5

MEM_MA_DQS0_P5

MEM_MA_DQS1_P5

MEM_MA_DQS2_P5

MEM_MA_DQS3_P5

MEM_MA_DQS4_P5

MEM_MA_DQS5_P5

MEM_MA_DQS6_P5

MEM_MA_DQS7_P5

MEM_MA0_ODT05,10

MEM_MA0_ODT15,10

SCD1U10V2KX-4GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SCD1U10V2KX-4GP

C216

C216

12

C217

C217

DY

DY

4

12

Place C2.2uF and 0.1uF <

500mils from DDR connector

DIMM1

DIMM1

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

11

29

49

68

129

146

167

186

13

31

51

70

131

148

169

188

114

119

1

2

202

SKT-SODIMM20022U2GP

Main Source:

SKT-SODIMM20022U2GP

LOW 5.2 mm

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16/BA2

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

NC#163/TEST

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

/DQS0

/DQS1

/DQS2

/DQS3

/DQS4

/DQS5

/DQS6

/DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

ODT0

ODT1

VREF

VSS

GND

62.10017.691

62.10017.691

2ND = 62.10017.911

2ND = 62.10017.911

3

108

/RAS

109

/WE

113

/CAS

110

/CS0

115

/CS1

79

CKE0

80

CKE1

30

CK0

32

/CK0

164

CK1

166

/CK1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

195

SDA

197

SCL

199

VDDSPD

198

SA0

200

SA1

50

NC#50

69

NC#69

83

NC#83

120

NC#120

163

1D8V_S3

81

VDD

82

VDD

87

VDD

88

VDD

95

VDD

96

VDD

103

VDD

104

VDD

111

VDD

112

VDD

117

VDD

118

VDD

3

VSS

8

VSS

9

VSS

12

VSS

15

VSS

18

VSS

21

VSS

24

VSS

27

VSS

28

VSS

33

VSS

34

VSS

39

VSS

40

VSS

41

VSS

42

VSS

47

VSS

48

VSS

53

VSS

54

VSS

59

VSS

60

REVERSE TYPE

VSS

65

VSS

66

VSS

71

VSS

72

VSS

77

VSS

78

VSS

121

VSS

122

VSS

127

VSS

128

VSS

132

VSS

133

VSS

138

VSS

139

VSS

144

VSS

145

VSS

149

VSS

150

VSS

155

VSS

156

VSS

161

VSS

162

VSS

165

VSS

168

VSS

171

VSS

172

VSS

177

VSS

178

VSS

183

VSS

184

VSS

187

VSS

190

VSS

193

VSS

196

VSS

201

GND

3

(A0)

MEM_MA_RAS# 5,10

MEM_MA_WE# 5,10

MEM_MA_CAS# 5,10

MEM_MA0_CS#0 5,10

MEM_MA0_CS#1 5,10

MEM_MA_CKE0 5,10

MEM_MA_CKE1 5,10

MEM_MA_CLK0_P 5

MEM_MA_CLK0_N 5

MEM_MA_CLK1_P 5

MEM_MA_CLK1_N 5

MEM_MA_DM0 5

MEM_MA_DM1 5

MEM_MA_DM2 5

MEM_MA_DM3 5

MEM_MA_DM4 5

MEM_MA_DM5 5

MEM_MA_DM6 5

MEM_MA_DM7 5

SMBD0_SB 3,9,21

SMBC0_SB 3,9,21

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

3D3V_S0

12

C47

C47

DY

DY

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

MEM_MA_CLK0_P

12

C132

C132

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

MEM_MA_CLK0_N

MEM_MA_CLK1_P

12

C57

C57

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

MEM_MA_CLK1_N

DDR_VREF

1D8V_S3

RN39

RN39

1

2 3

SRN1KJ-7-GP

SRN1KJ-7-GP

LAYOUT: Locate close to DIMM

12

C45

C45

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

VREF_DDR_MEM

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C224

C224

4

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

2

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

C215

C215

C218

C218

2

12

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR_SO-DIMM SKT_1

DDR_SO-DIMM SKT_1

DDR_SO-DIMM SKT_1

Big Bear 2A

Big Bear 2A

Big Bear 2A

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

of

of

of

855Monday, October 27, 2008

855Monday, October 27, 2008

855Monday, October 27, 2008

1

SA

SA

SA

5

D D

C C

B B

A A

5

VREF_DDR_MEM

4

MEM_MB_ADD05,10

MEM_MB_ADD15,10

MEM_MB_ADD25,10

MEM_MB_ADD35,10

MEM_MB_ADD45,10

MEM_MB_ADD55,10

MEM_MB_ADD65,10

MEM_MB_ADD75,10

MEM_MB_ADD85,10

MEM_MB_ADD95,10

MEM_MB_ADD105,10

MEM_MB_ADD115,10

MEM_MB_ADD125,10

MEM_MB_ADD135,10

MEM_MB_ADD145,10

MEM_MB_ADD155,10

MEM_MB_BANK25,10

MEM_MB_BANK05,10

MEM_MB_BANK15,10

MEM_MB_DATA05

MEM_MB_DATA15

MEM_MB_DATA25

MEM_MB_DATA35

MEM_MB_DATA45 SMBD0_SB 3,8,21

MEM_MB_DATA55

MEM_MB_DATA65

MEM_MB_DATA75

MEM_MB_DATA85

MEM_MB_DATA95

MEM_MB_DATA105

MEM_MB_DATA115

MEM_MB_DATA125

MEM_MB_DATA135

MEM_MB_DATA145

MEM_MB_DATA155

MEM_MB_DATA165

MEM_MB_DATA175

MEM_MB_DATA185

MEM_MB_DATA195

MEM_MB_DATA205

MEM_MB_DATA215

MEM_MB_DATA225

MEM_MB_DATA235

MEM_MB_DATA245

MEM_MB_DATA255

MEM_MB_DATA265

MEM_MB_DATA275

MEM_MB_DATA285

MEM_MB_DATA295

MEM_MB_DATA305

MEM_MB_DATA315

MEM_MB_DATA325

MEM_MB_DATA335

MEM_MB_DATA345

MEM_MB_DATA355

MEM_MB_DATA365

MEM_MB_DATA375

MEM_MB_DATA385

MEM_MB_DATA395

MEM_MB_DATA405

MEM_MB_DATA415

MEM_MB_DATA425

MEM_MB_DATA435

MEM_MB_DATA445

MEM_MB_DATA455

MEM_MB_DATA465

MEM_MB_DATA475

MEM_MB_DATA485

MEM_MB_DATA495

MEM_MB_DATA505

MEM_MB_DATA515

MEM_MB_DATA525

MEM_MB_DATA535

MEM_MB_DATA545

MEM_MB_DATA555

MEM_MB_DATA565

MEM_MB_DATA575

MEM_MB_DATA585

MEM_MB_DATA595

MEM_MB_DATA605

MEM_MB_DATA615

MEM_MB_DATA625

MEM_MB_DATA635

MEM_MB_DQS0_N5

MEM_MB_DQS1_N5

MEM_MB_DQS2_N5

MEM_MB_DQS3_N5

MEM_MB_DQS4_N5

MEM_MB_DQS5_N5

MEM_MB_DQS6_N5

MEM_MB_DQS7_N5

MEM_MB_DQS0_P5

MEM_MB_DQS1_P5

MEM_MB_DQS2_P5

MEM_MB_DQS3_P5

MEM_MB_DQS4_P5

MEM_MB_DQS5_P5

MEM_MB_DQS6_P5

MEM_MB_DQS7_P5

MEM_MB0_ODT05,10

MEM_MB0_ODT15,10

SCD1U10V2KX-4GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

Place C2.2uF and 0.1uF <

500mils from DDR connector

SCD1U10V2KX-4GP

12

12

C219

C219

C220

C220

4

DIMM2

DIMM2

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16/BA2

107

BA0

106

BA1

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

11

DQS0#

29

DQS1#

49

DQS2#

68

DQS3#

129

DQS4#

146

DQS5#

167

DQS6#

186

DQS7#

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

114

OTD0

119

OTD1

1

VREF

2

VSS

202

GND

MH1

MH1

DDR2-200P-23-GP-U1

DDR2-200P-23-GP-U1

62.10017.A71

62.10017.A71

2ND = 62.10017.B51

2ND = 62.10017.B51

HI 9.2mm

NC#163/TEST

REVERSE TYPE

RAS#

WE#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

VDDSPD

NC#50

NC#69

NC#83

NC#120

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

MH2

SDA

SCL

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3

108

109

113

110

115

79

80

30

CK0

32

164

CK1

166

10

26

52

67

130

147

170

185

195

197

199

DIMM2_SA1

198

200

50

69

83

120

163

81

82

87

88

95

96

103

104

111

112

117

118

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

59

60

65

66

71

72

77

78

121

122

127

128

132

133

138

139

144

145

149

150

155

156

161

162

165

168

171

172

177

178

183

184

187

190

193

196

201

MH2

3

R220 10KR2J-3-GPR220 10KR2J-3-GP

1D8V_S3

1 2

(A2)

MEM_MB_RAS# 5,10

MEM_MB_WE# 5,10

MEM_MB_CAS# 5,10

MEM_MB0_CS#0 5,10

MEM_MB0_CS#1 5,10

MEM_MB_CKE0 5,10

MEM_MB_CKE1 5,10

MEM_MB_CLK0_P 5

MEM_MB_CLK0_N 5

MEM_MB_CLK1_P 5

MEM_MB_CLK1_N 5

MEM_MB_DM0 5

MEM_MB_DM1 5

MEM_MB_DM2 5

MEM_MB_DM3 5

MEM_MB_DM4 5

MEM_MB_DM5 5

MEM_MB_DM6 5

MEM_MB_DM7 5

SMBC0_SB 3,8,21

2

3D3V_S0

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

MEM_MB_CLK0_P

12

C190

C190

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

MEM_MB_CLK0_N

MEM_MB_CLK1_P

12

C49

C49

SC1D5P50V2CN-1GP

SC1D5P50V2CN-1GP

MEM_MB_CLK1_N

12

12

C48

C48

DY

DY

C46

C46

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

2

1

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR_SO-DIMM SKT_2

DDR_SO-DIMM SKT_2

DDR_SO-DIMM SKT_2

Taipei Hsien 221, Taiwan, R.O.C.

Big Bear 2A

Big Bear 2A

Big Bear 2A

1

of

955Monday, October 27, 2008

of

955Monday, October 27, 2008

of

955Monday, October 27, 2008

SA

SA

SA

5

4

3

2

1

Decoupling Capacitor

0D9V_S3

12

12

C113

C113

SCD1U16V2ZY-2GP

D D

PARALLEL TERMINATION

SCD1U16V2ZY-2GP

Put decap near power(0.9V) and pull-up resistor

12

C70

C70

C92

C92

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

12

C75

C75

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C155

C155

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C87

C87

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C105

C105

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C81

C81

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

C99

C99

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

C104

C104

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

DY

DY

12

C67

C67

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

12

12

C154

C154

C69

C69

SC10P50V2JN-4GP

SC10P50V2JN-4GP

SC10P50V2JN-4GP

SC10P50V2JN-4GP

Put decap near power(0.9V) and pull-up resistor

0D9V_S30D9V_S3

RN20

RN6

RN6

1

8

2

7

3

6

4 5

SRN47J-4-GP

SRN47J-4-GP

RN14

RN14

1

8

2

7

3

6

4 5

SRN47J-4-GP

SRN47J-4-GP

RN12

RN12

1

8

2

7

3

6

4 5

SRN47J-4-GP

C C

B B

SRN47J-4-GP

RN23

RN23

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN10

RN10

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN21

RN21

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN7

RN7

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

8

7

6

8

7

6

8

7

6

8

7

6

MEM_MA0_CS#1 5,8

MEM_MA0_ODT1 5,8

MEM_MA_WE# 5,8

MEM_MA_CAS# 5,8

MEM_MA_ADD5 5,8

MEM_MA_ADD8 5,8

MEM_MA_ADD9 5,8

MEM_MA_ADD12 5,8

MEM_MA_ADD2 5,8

MEM_MA_ADD4 5,8

MEM_MA_ADD0 5,8

MEM_MA_BANK1 5,8

MEM_MA_CKE0 5,8

MEM_MA_BANK2 5,8

MEM_MA_CKE1 5,8

MEM_MA_ADD15 5,8

MEM_MA_ADD10 5,8

MEM_MA_BANK0 5,8

MEM_MA_ADD3 5,8

MEM_MA_ADD1 5,8

MEM_MA_ADD14 5,8

MEM_MA_ADD11 5,8

MEM_MA_ADD7 5,8

MEM_MA_ADD6 5,8

MEM_MA0_CS#0 5,8

MEM_MA_RAS# 5,8

MEM_MA0_ODT0 5,8

MEM_MA_ADD13 5,8

RN20

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN11

RN11

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN9

RN9

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN22

RN22

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN24

RN24

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN13

RN13

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

RN8

RN8

1

2

3

4 5

SRN47J-4-GP

SRN47J-4-GP

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

MEM_MB_ADD14 5,9

MEM_MB_ADD7 5,9

MEM_MB_ADD11 5,9

MEM_MB_ADD6 5,9

MEM_MB_ADD2 5,9

MEM_MB_ADD4 5,9

MEM_MB_ADD0 5,9

MEM_MB_RAS# 5,9

MEM_MB_BANK1 5,9

MEM_MB0_CS#0 5,9

MEM_MB0_ODT0 5,9

MEM_MB_ADD13 5,9

MEM_MB_ADD5 5,9

MEM_MB_ADD8 5,9

MEM_MB_ADD9 5,9

MEM_MB_ADD12 5,9

MEM_MB_ADD15 5,9

MEM_MB_CKE0 5,9

MEM_MB_BANK2 5,9

MEM_MB_CKE1 5,9

MEM_MB_BANK0 5,9

MEM_MB_ADD10 5,9

MEM_MB_ADD1 5,9

MEM_MB_ADD3 5,9

MEM_MB0_ODT1 5,9

MEM_MB0_CS#1 5,9

MEM_MB_CAS# 5,9

MEM_MB_WE# 5,9

Place these Caps near DM1

1D8V_S3

12

12

Place these Caps near DM2

12

C456

C456

C494

C494

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

1D8V_S3

12

C452

C452

C114

C114

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

Place these Caps near PARALLEL TERMINATION

12

12

12

C82

C82

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C97

C97

C109

C109

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

12

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C463

C463

C444

C444

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C446

C446

C443

C443

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

12

C111

C111

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C442

C442

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

12

C478

C478

SCD01U50V2KX-1GP