Page 1

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

A

1 1

B

C

D

E

Compal Confidential

2 2

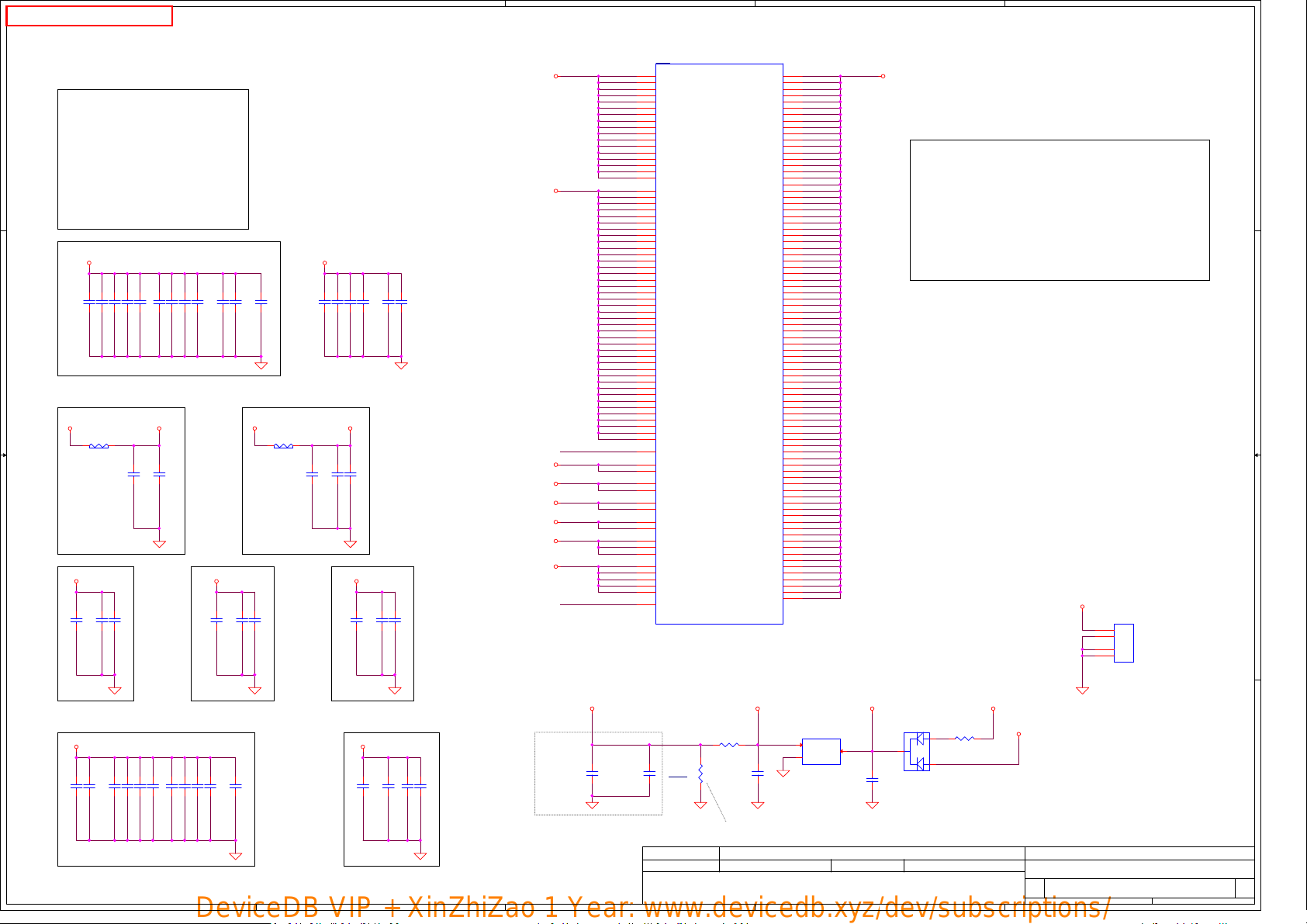

EH5LP/AP Schematics Document

AMD Picasso Ridge Platform

AMD R19M-M18-70

3 3

LA-H801P REV:1.A

2019-03-29

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Shared with acer CSD

Shared with acer CSD

A

B

Shared with acer CSD

2020/03/ 29 2020/03/ 29

2020/03/ 29 2020/03/ 29

2020/03/ 29 2020/03/ 29

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

COVER PAGE

COVER PAGE

COVER PAGE

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

E

1 48Tuesday, April 30, 2019

1 48Tuesday, April 30, 2019

1 48Tuesday, April 30, 2019

1.A

1.A

1.A

Page 2

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

A

Compal Confidential

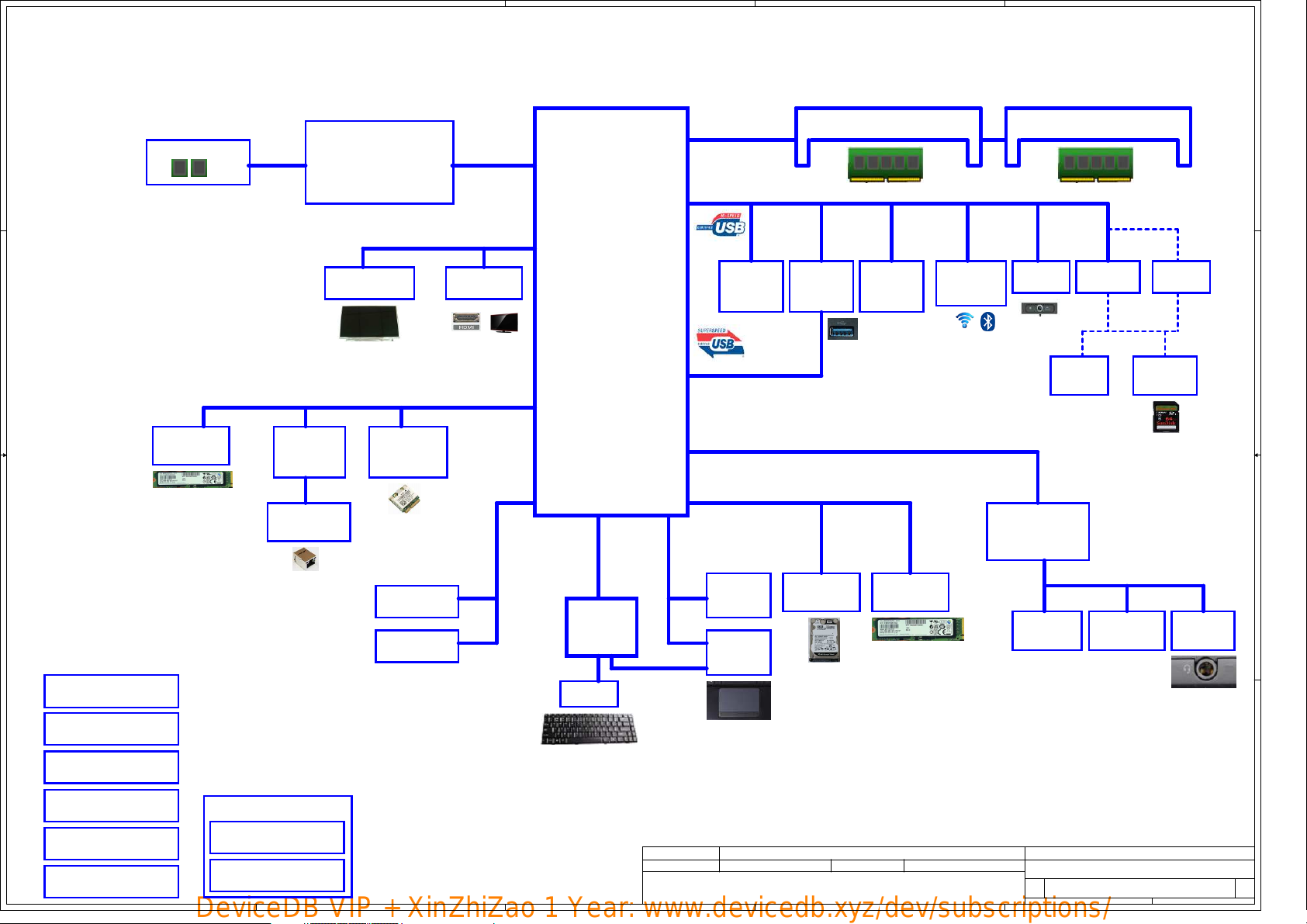

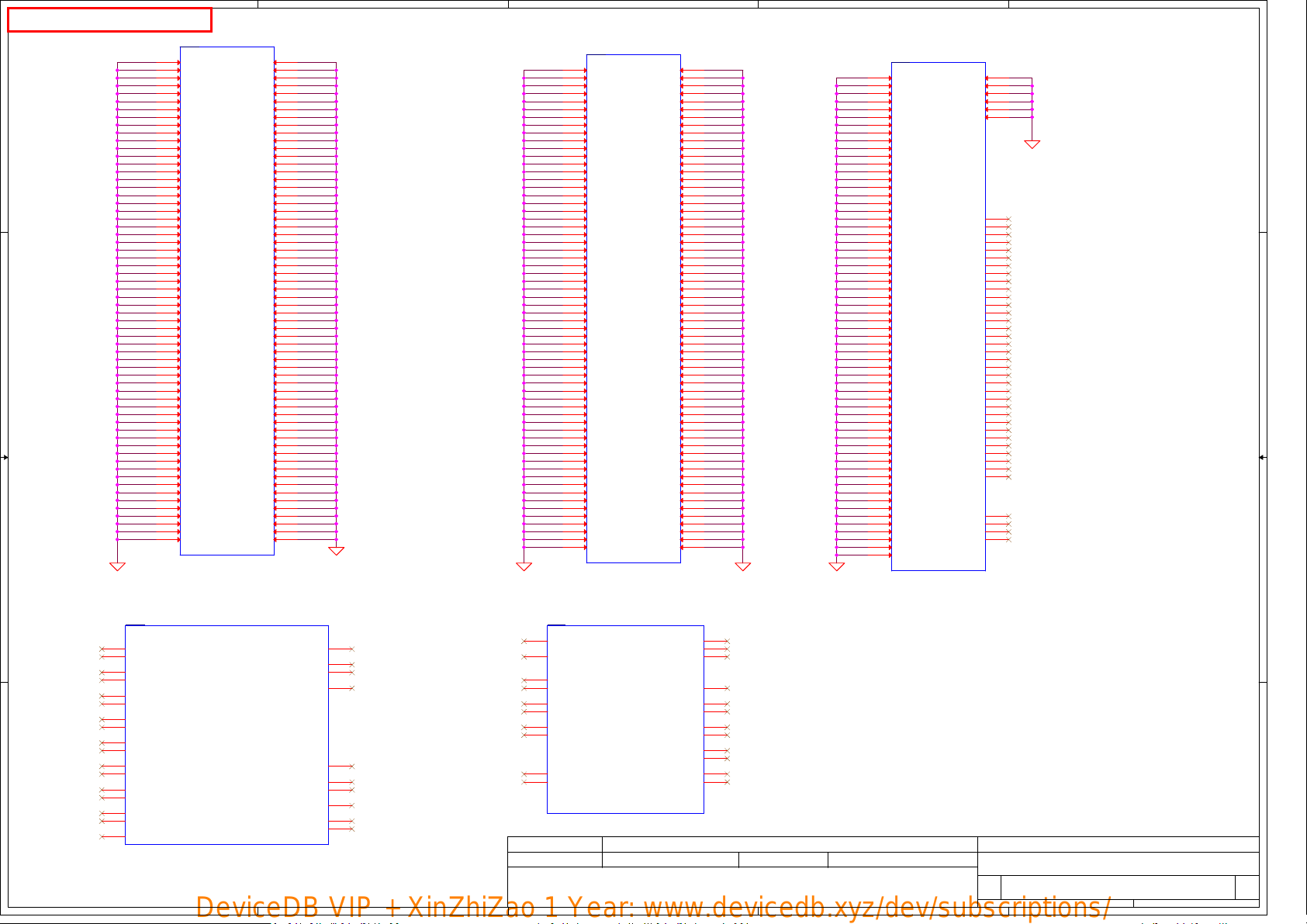

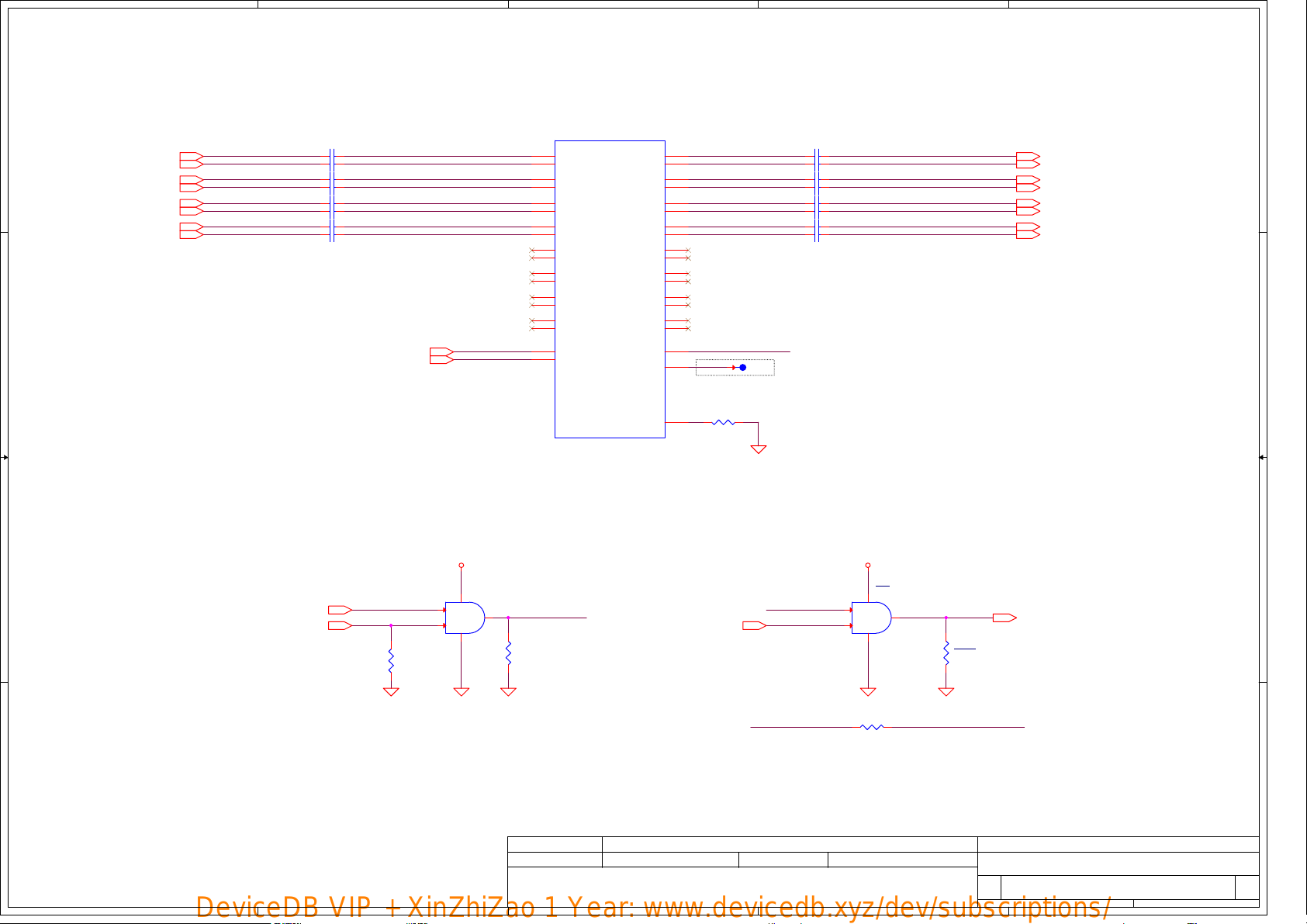

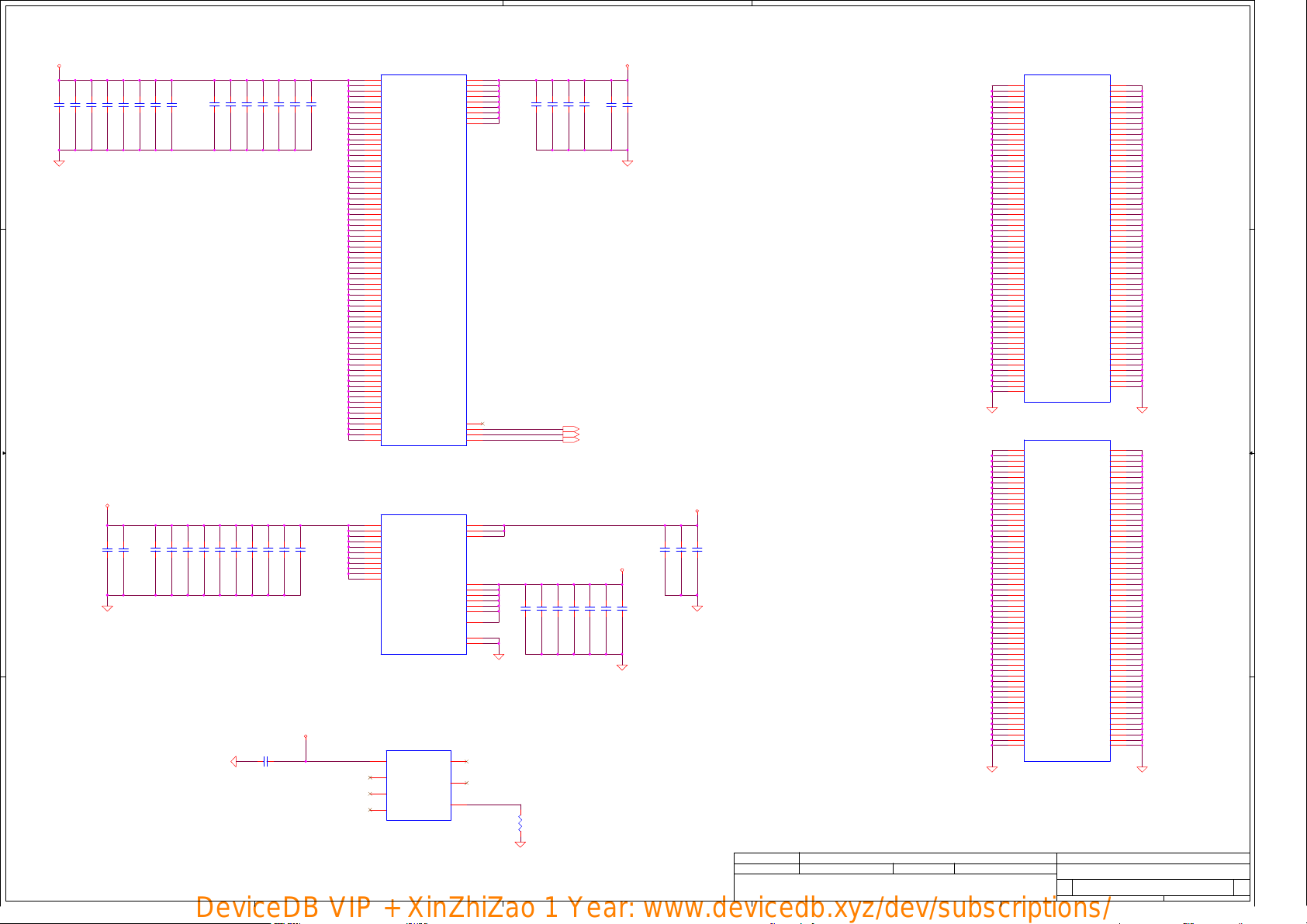

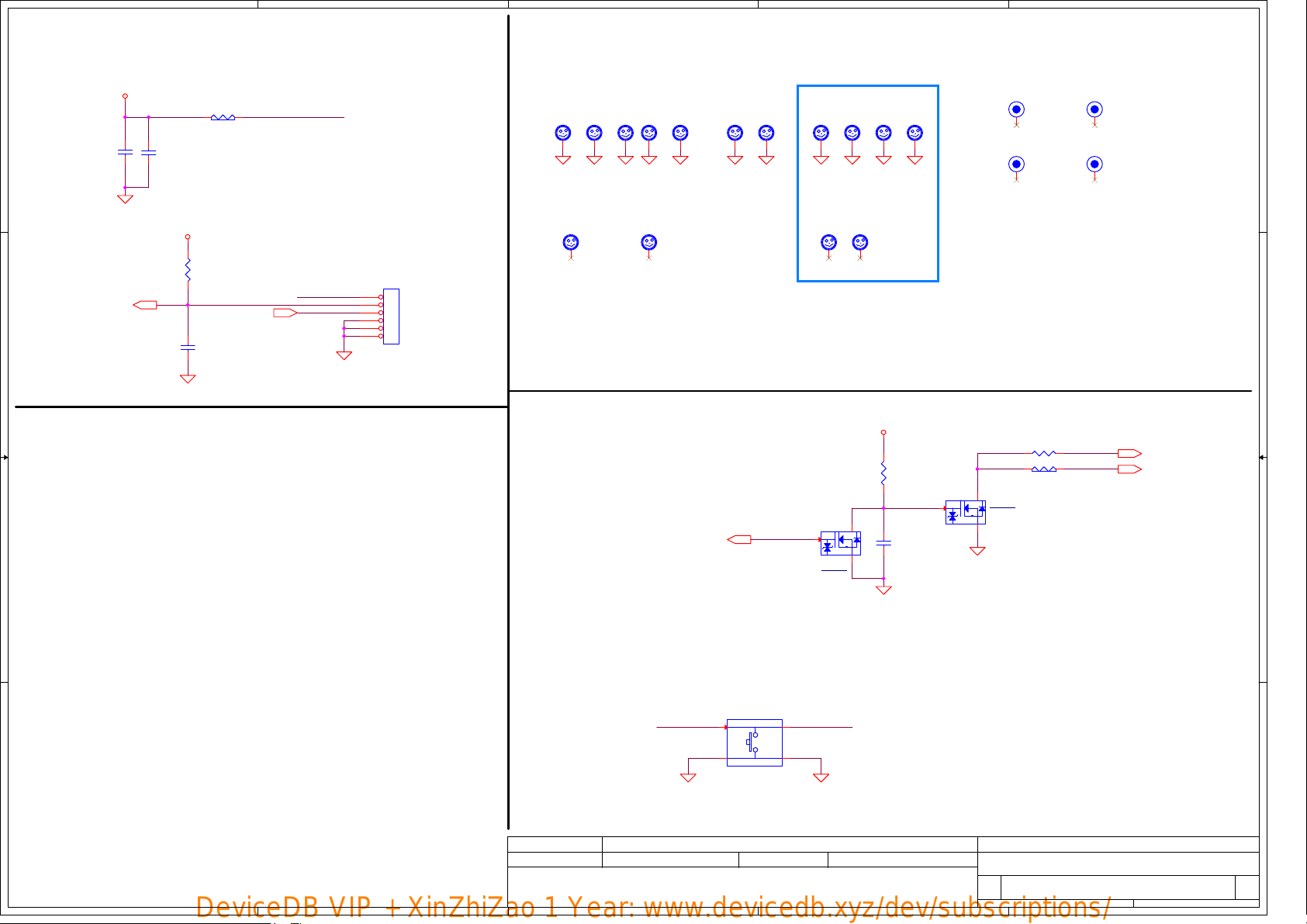

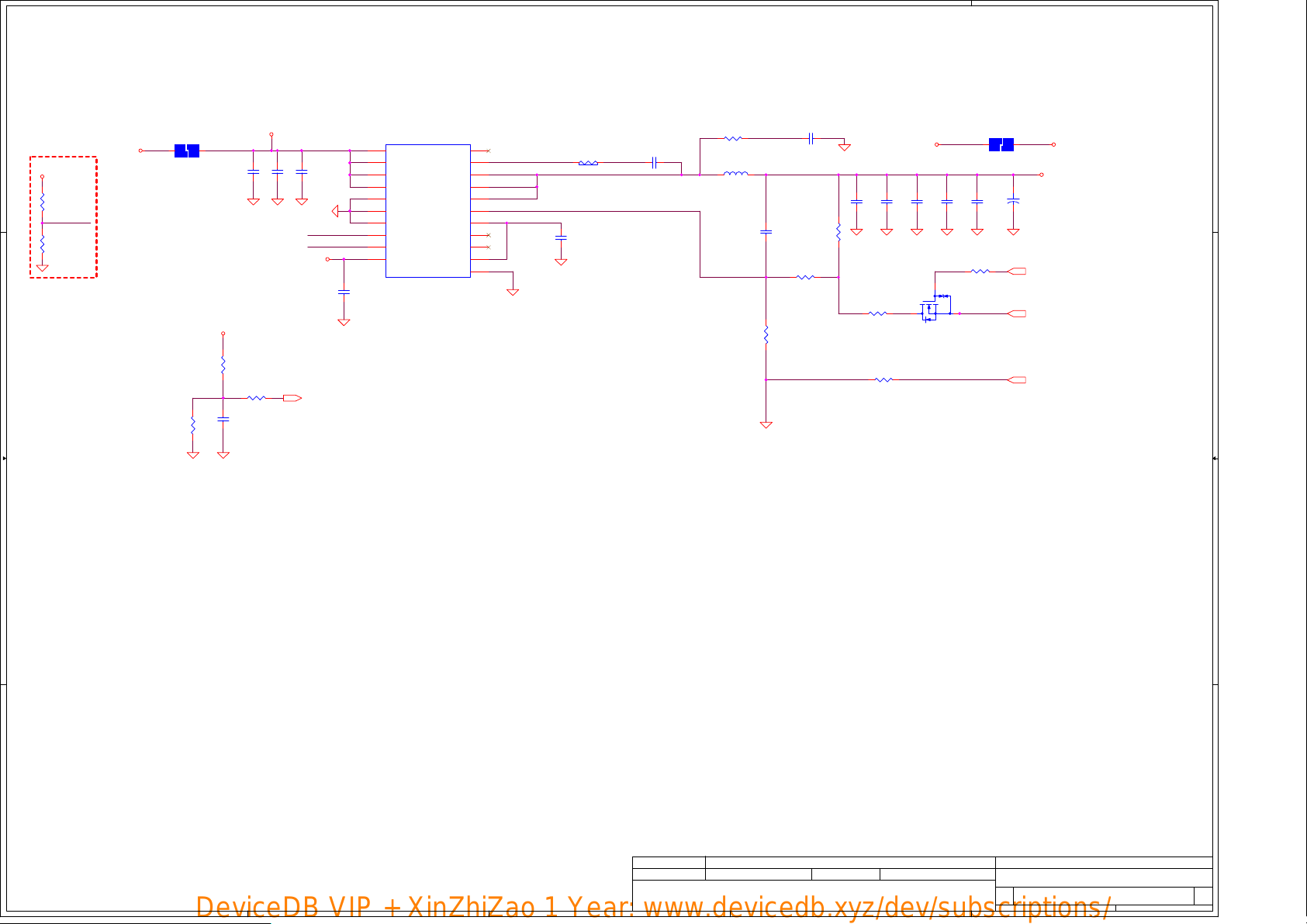

Model Name : EH5LP/AP

B

C

D

E

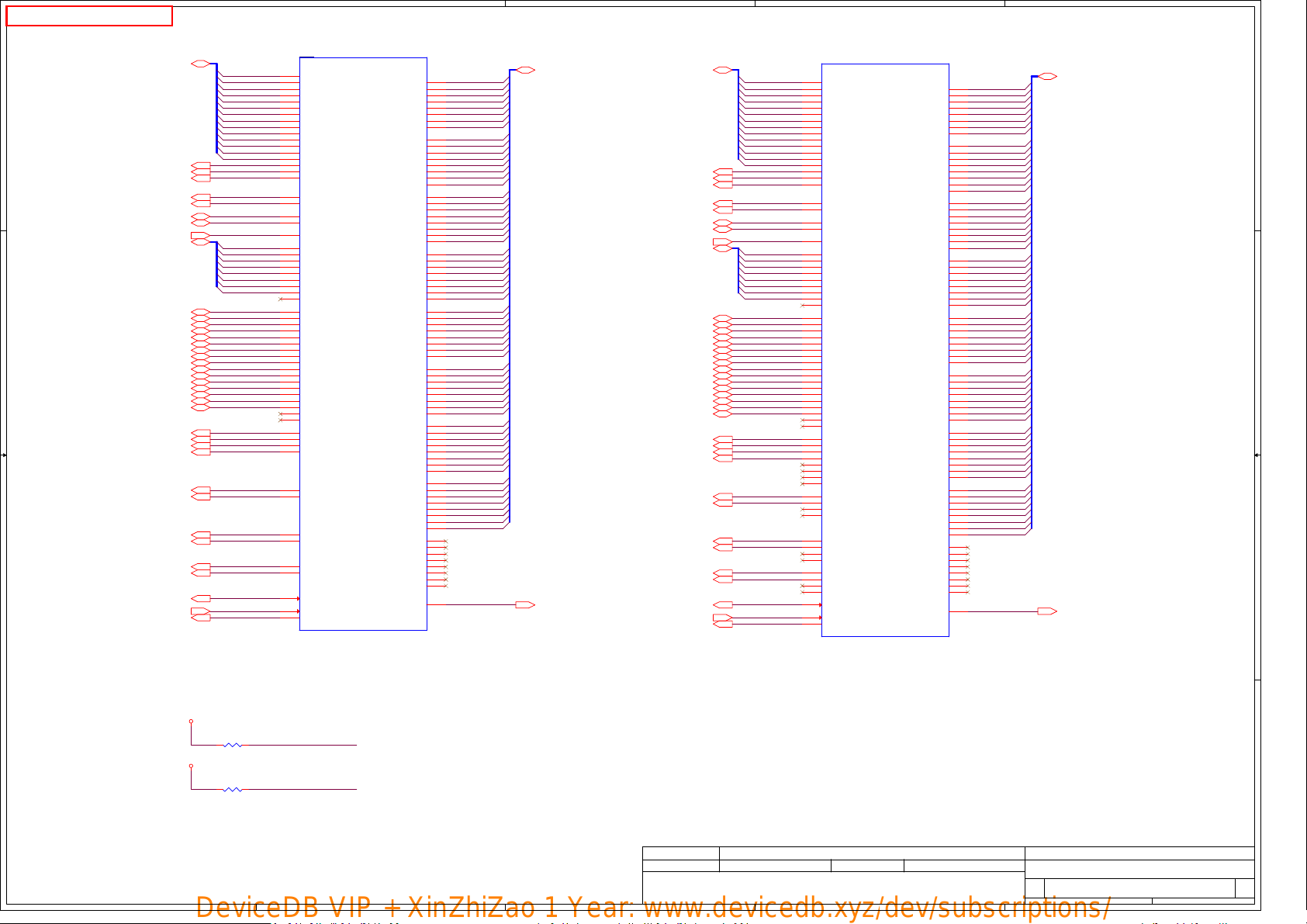

(Channel A)

1 1

GPU

GDDR5 x2pcs

2 2

64-b it s

page 21

S4 Package

R540X : R19M-M18-70

page 15~22

Port 1

eDP Conn.

page 23 page 24

PEG x4

Display Port

Port 0

HDMI Conn.

AMD

PICASSO RIDGE

AMD FP5 APU

Memory BUS(DDR4)

1.2V DDRIV

2400Mhz

USB2 .0

Type-A

2.0 Conn.

page 32 page 32

USB3 .1

260pin DDRIV SO-DIMM

Port 1

Type-A

3.0 Conn.

Port 1

Port 2Port 0

USB S/B

2.0 Conn.

page 32

page 13

WLAN/BT

Combo

BGA 1140-balls

PCI E

Port 1

page 27

SSD

NGFF Conn.

LAN

RTL8 111

page 25

Transformer

RJ45

page 25

3 3

Fan Control

page 31

Port 0Port 4,5

WLAN/BT

NGFF Conn.

page 26

Discrete TPM

page 30

BIOS (8M)

page 10

page 6~12

HD Audio(AZ)

I2C

Port 1

Port 3

SATA III

G-Sensor

(Reserve)

PTP

page 27

page 30

HDD

Conn .

Port 0

page 27

Port 1

page 27

SSD

NGFF Conn.

SPI

LPC

ENE

KBC902 2

page 29

PS2

page 30

Int.KBD

(Channel B)

260pin DDRIV SO-DIMM

Camera

Audio

ALC255

page 23

Int. DMIC

on Camera

Port 4

page 23

Touch

Screen

page 28

Port 3

page 26

page 14

Port 5

Co-Lay

HUB Port1

USB2.0 Hub

Card Reader

RTS51 40

Finger Print

page 30

HUB Port2 HUB Port3

page 23

Int. Speaker

Conn.

page 28 page 28

page 32

page 32

UAJ

Conn.

RTC CKT.

Power On/Off CKT.

4 4

DC/DC Interface CKT.

Power Circuit DC/DC

VRAM Config Table

page 11

page 30

page 33

page 34-46

page 22

A

Sub Board

LS-H801P IO/B

LS-H802P HDD/B

page 32

page 27

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Nu mber Re v

Size Document Nu mber R ev

Size Document Nu mber R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

D

Date : Sheet of

Compal Electronics, Inc.

BLOCK DIAGRAMS

BLOCK DIAGRAMS

BLOCK DIAGRAMS

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

E

1.A

1.A

2 48Friday, March 29, 2019

2 48Friday, March 29, 2019

2 48Friday, March 29, 2019

1.A

Page 3

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

A

B

C

D

E

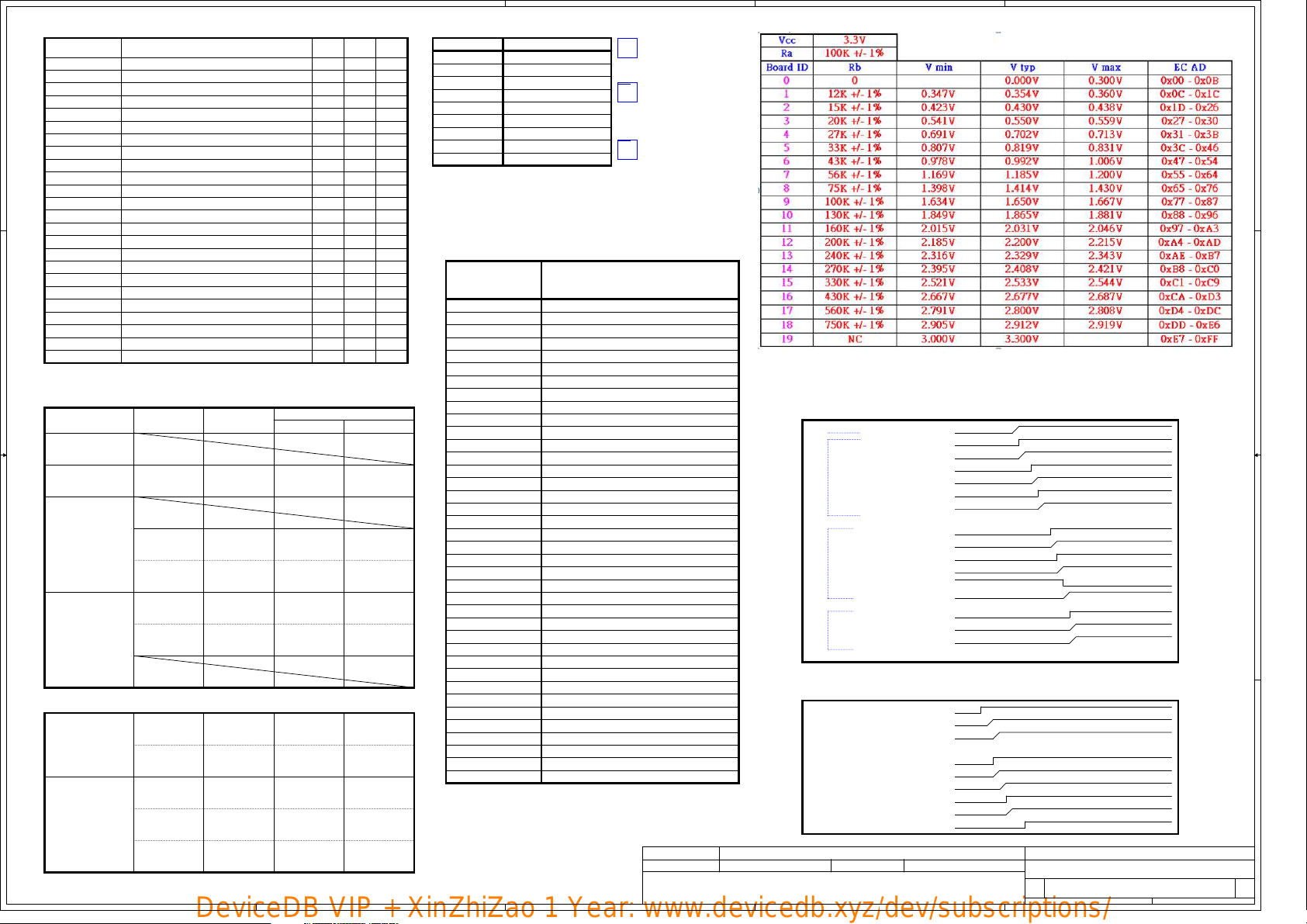

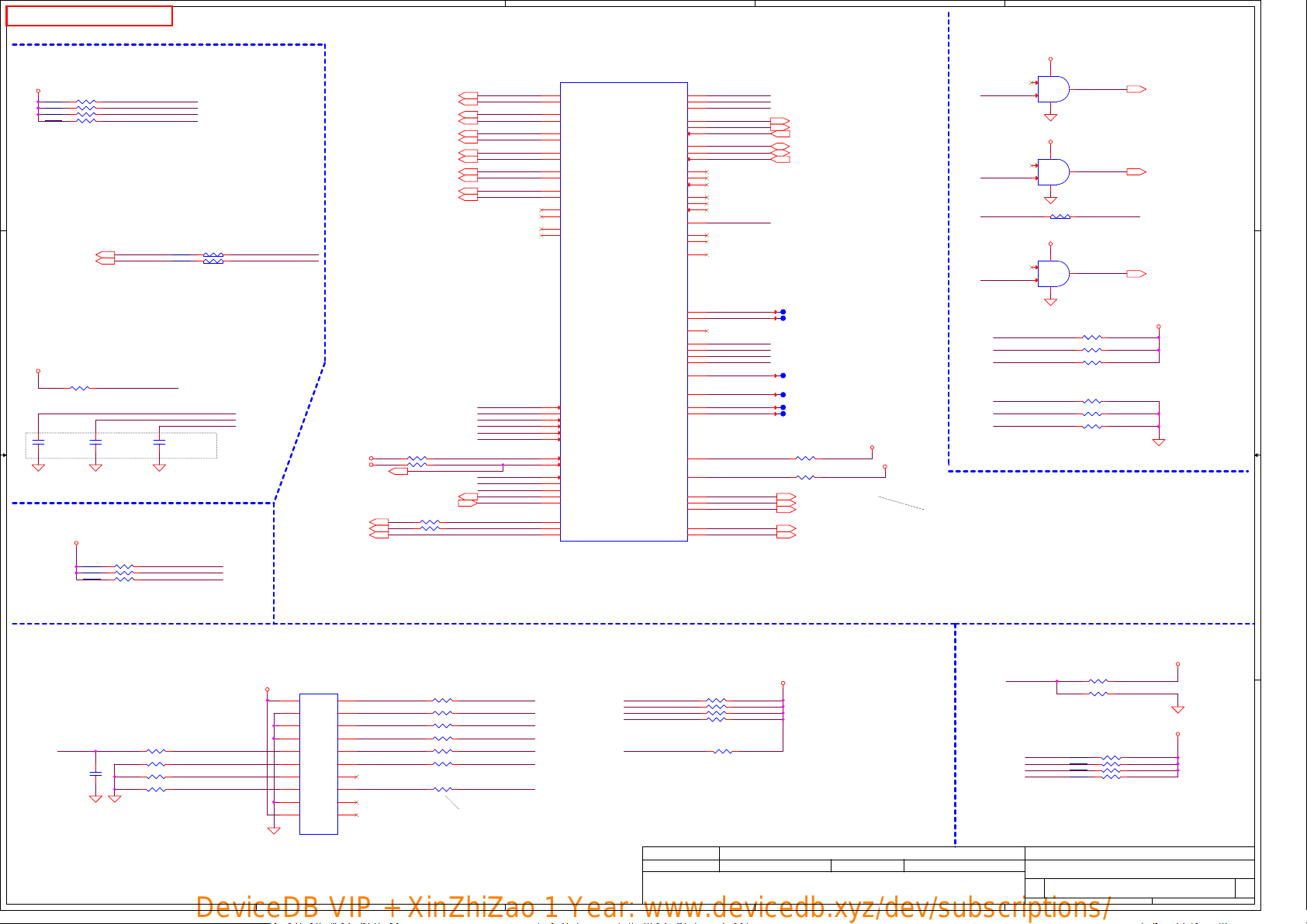

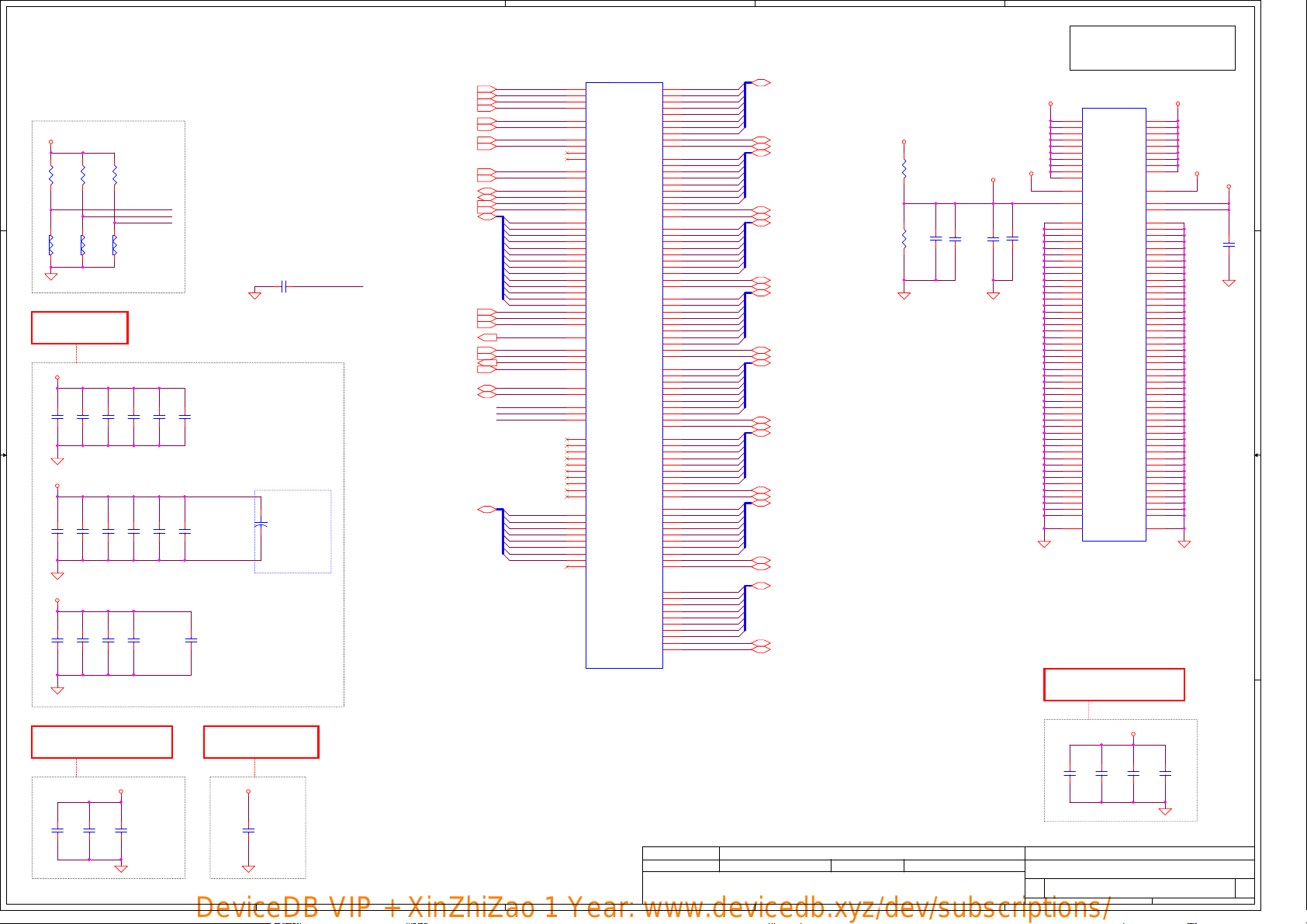

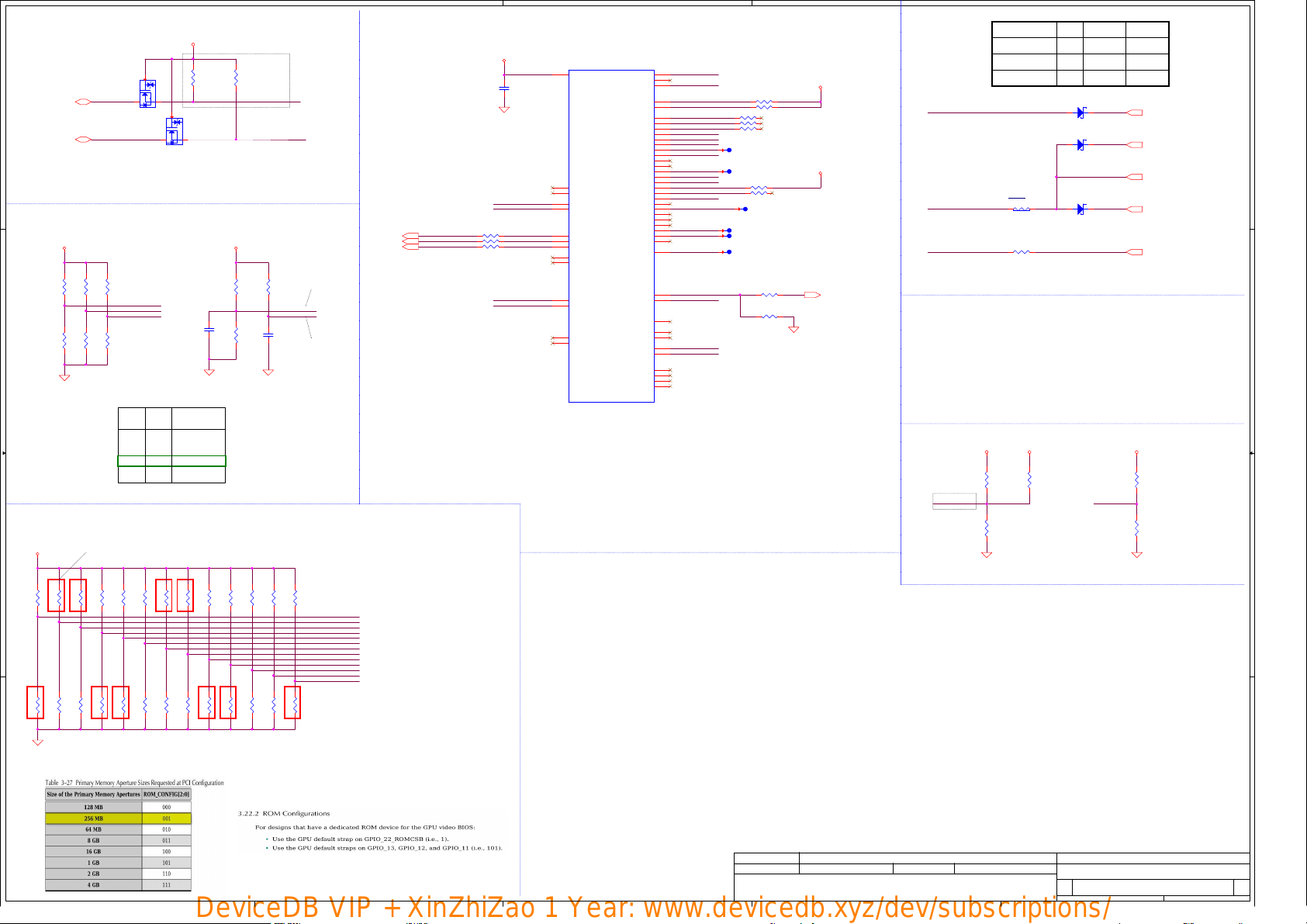

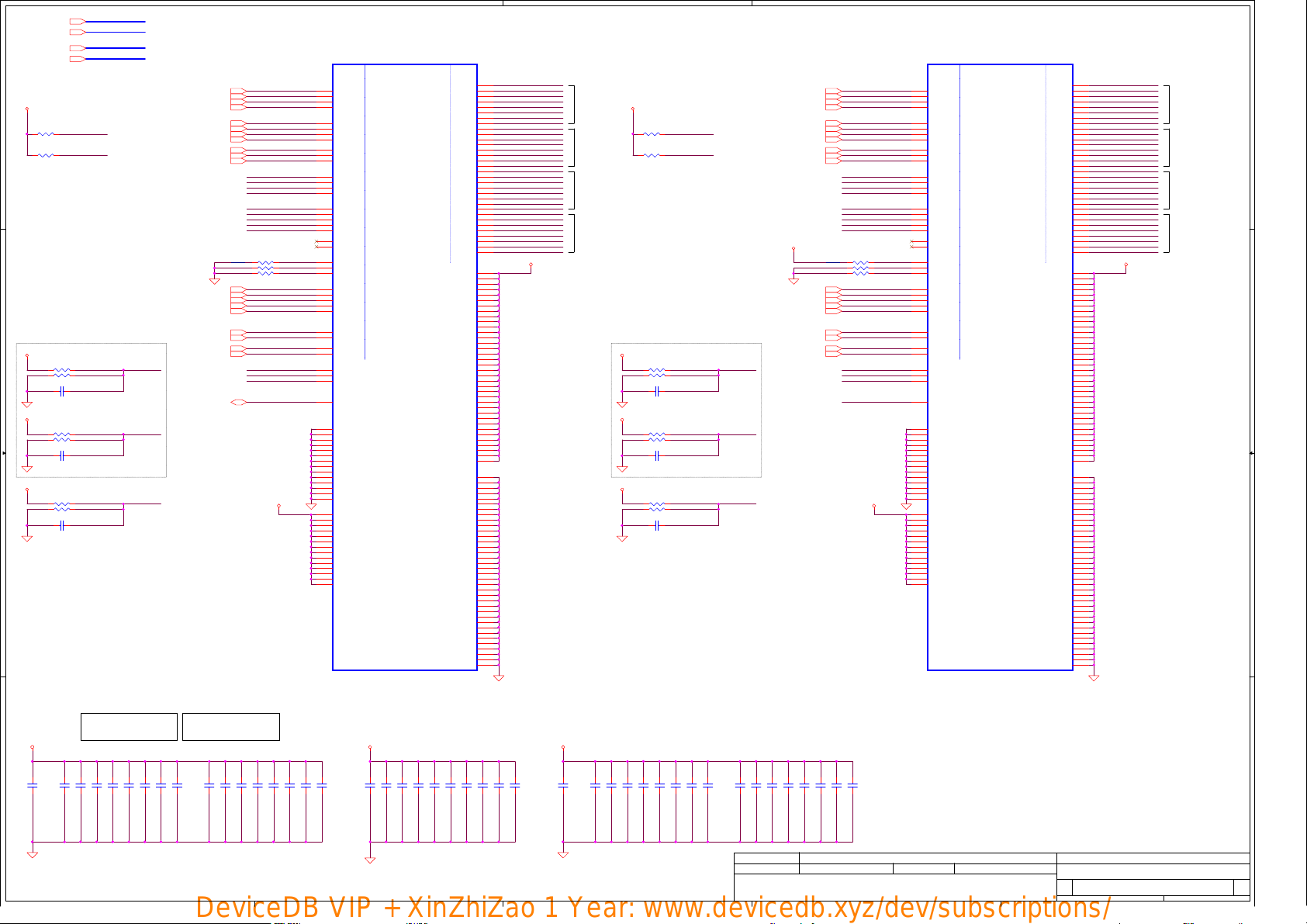

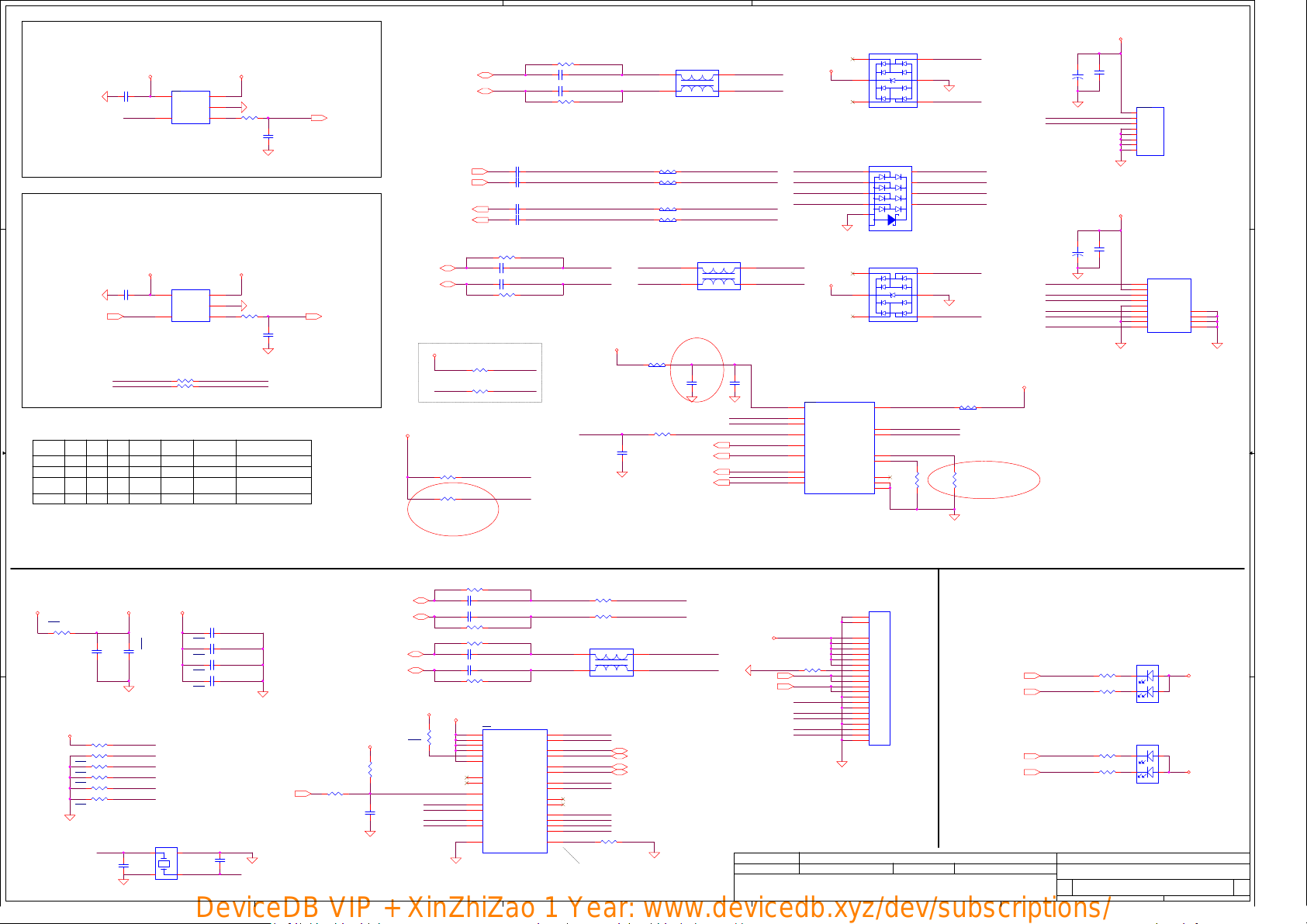

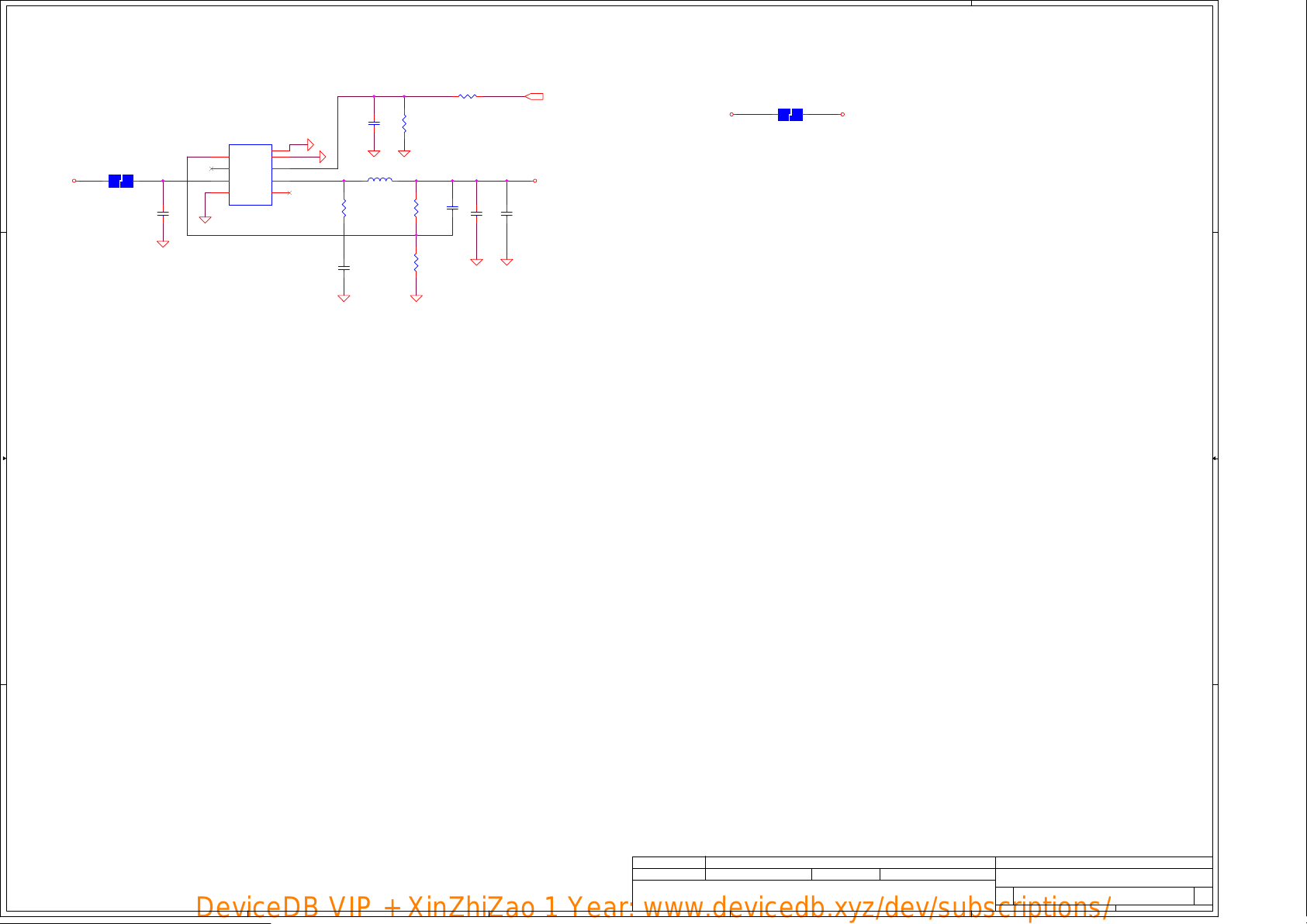

Voltage Rails

Power Plane

+19V_VIN

+19VB

+APU_CORE

1 1

2 2

+0.8VALW

+0.8VS

+1.8VALW

+1.8VS

+2.5V

+1.2V

+0.6VS

+3VALW

+3VS

+5VALW

+5VS

+RTC_APU

+3V_LAN 3.3V LAN IC power

+TP_VCC 3.3V Touch Pad power

+3VSDGPU

+1.8VSDGPU

+VDDCI

+VGA_CORE

+FP_VCC ON

APU SMBus/I2C Address Table

Master

I2C Port 0

(+1.8VS)

I2C Port 1

(+1.8VS)

I2C Port 2

(+3VS)

SBMus Port 0

3 3

(+3VS)

I2C Port 3

(+3VALW)

SMBus Port 1

(+3VALW)

Description

Adapter power supply (19V)

AC or battery power r ail for power circuit.

Core voltage for APU

Voltage for On-die VGA of APU

0.8V always on power rail

0.8V switched power rail

1.8V always on power rail

1.8V switched power rail

2.5V power rail for APU and DDR

1.2V power rail for APU and DDR

0.6V switched power r ail for DDR terminator

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

VGA power

VGA power

VGA power

VGA power

3.3V Finger Print power

Device

G-Sensor

(Reserver)

JDIMM1

JDIMM2

PTP

(Synaptics)

PTP

(ELAN)

Address[7: 1]

0001 1000b

18h

0101 0000b

50h

0101 0001b

51h

0010 1100b

2Ch

0001 1111b

15h

Address [7:0]

Write

0011 0000b

30h

1010 0000b

A0h

1010 0010b

A2h

0101 1000b

58h

0011 1110b

3Eh

ON

ON

ON+APU_CORE_NB

ON

ON

ON

ON ON

ON

ON

ON

ON

ON ON

ON ON

ON

ON

ON

ON

ON

0011 0001b

31h

1010 0001b

A1h

1010 0011b

A3h

0101 1001b

59h

0011 1111b

3Fh

ON ON

OFF

OFF OFF

ONON

OFF OFF

ON

OFF OFF

ONON

OFF OFF

ONON

OFF OFF

AC:ON

ON

DC:OFF

OFF OFF

OFF OFF

Read

EC SMBus Address Table

SMBus Port 1

(+3VALW)

Smart Battery

Charger IC

4 4

SMBus Port 2

(+3VS)

APU Temp.

GPU Temp.

A

0000 1011b

0Bh

0000 1001b

09h

0100 1100b

4Ch

0100 0001b

41h

0001 0110b

16h

0001 0010b

12h

1001 1000b

98h

1000 0010b

82h

0001 0111b

17h

0001 0011b

13h

1001 1001b

99h

1000 0011b

83h

B

BOARD ID Table

S5S3S0

ONONON

OFF

OFF

OFF

OFF

OFF

OFF

ONONON

OFF

OFF

OFFOFF

OFFOFF

OFFOFF

OFF

Board ID

0

1

2

PCB Revision

EVT

DVT

PVT

3

BOM Structure Table

BTO ItemBOM Structure

@

EMC@ /@E MC @

45@

CON N@

JP@

RS@

TP@

TPM @

PCI E@

SAT A@

GS@

EH5L P@/E H5 AP @

PAR @

CR@

CHG@ /NC HG @

255 @

256@ /256 EM C@

UMA @

R3/R 5/R7 AP U@

T1@/ T2 @

DIS @

M18 70

HUB@ /NH UB @

FP@/ FPE MC @/

HDT @

Unpop

EMI/ESD Pop/Unpop

HDMI Royalty

Mechanical Connector

Jump

R-Shor t

Test Point

TPM Circuits

PCIE SSD

SATA SSD

G-Sensor Circuits

Aspire3/Aspire5 Config.

SATA Redriver PARADE solution

Card Reader Config.

USB Charger/Non-Charger

Audio Codec AL255 Design

Audio Codec AL256 Design

UMA Config

APU PN Refer p.6

APU Type Config

VGA Circuits

GPU and VRAM Config Refer p.23

R19M-M18-70 GPU

USB20 HUB/Non-HUB

Finger Print

HDT Circuits

@

ZZZ

DA60025X000

PCB 2MK LA-H801P REV0 MB 3

@

ZZZ

DAZ2MK00100

PCB EH5LP LA-H801P LS-H801 P/H802P

PCB1A@

ZZZ

DAZ2MK00101

PCB EH5LP LA-H801P LS-H801 P/H802P

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Board ID / SKU ID Table for AD channel

POWER SEQUENCE

G-A

G-B

G-C

G-D

+RTC BAT T

EC_O N

+5VA LW

3V_E N

+3VA LW

0.9_ 1.8 VAL W_P WRE N

+1.8 VAL W/+ 0.9 VAL W

SYSO N

+1.2 V/+ 2.5 V

SUSP #

+5VS /+3 VS/ +1. 8VS /+0 .6VS

0.9V S_P WR_ EN #

+0.9 VS

VR_O N

+APU _CO RE

+APU _CO RE_ SO C

VGA POWER SEQUENCE

PE_G PIO 1/V GA_ ON

+3VS DGP U

+1.8 VSD GP U

VGA_ ON_ B

+VDD CI

+VGA _CO RE

DGPU _PW RGO OD

+1.3 5VS DGP U

PE_G PIO 0

Compal Secret Data

Compal Secret Data

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Nu mber R ev

Size Document Nu mber R ev

Size Document Nu mber R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

NOTES LIST

NOTES LIST

NOTES LIST

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

E

3 48Friday, March 29, 2019

3 48Friday, March 29, 2019

3 48Friday, March 29, 2019

1.A

1.A

1.A

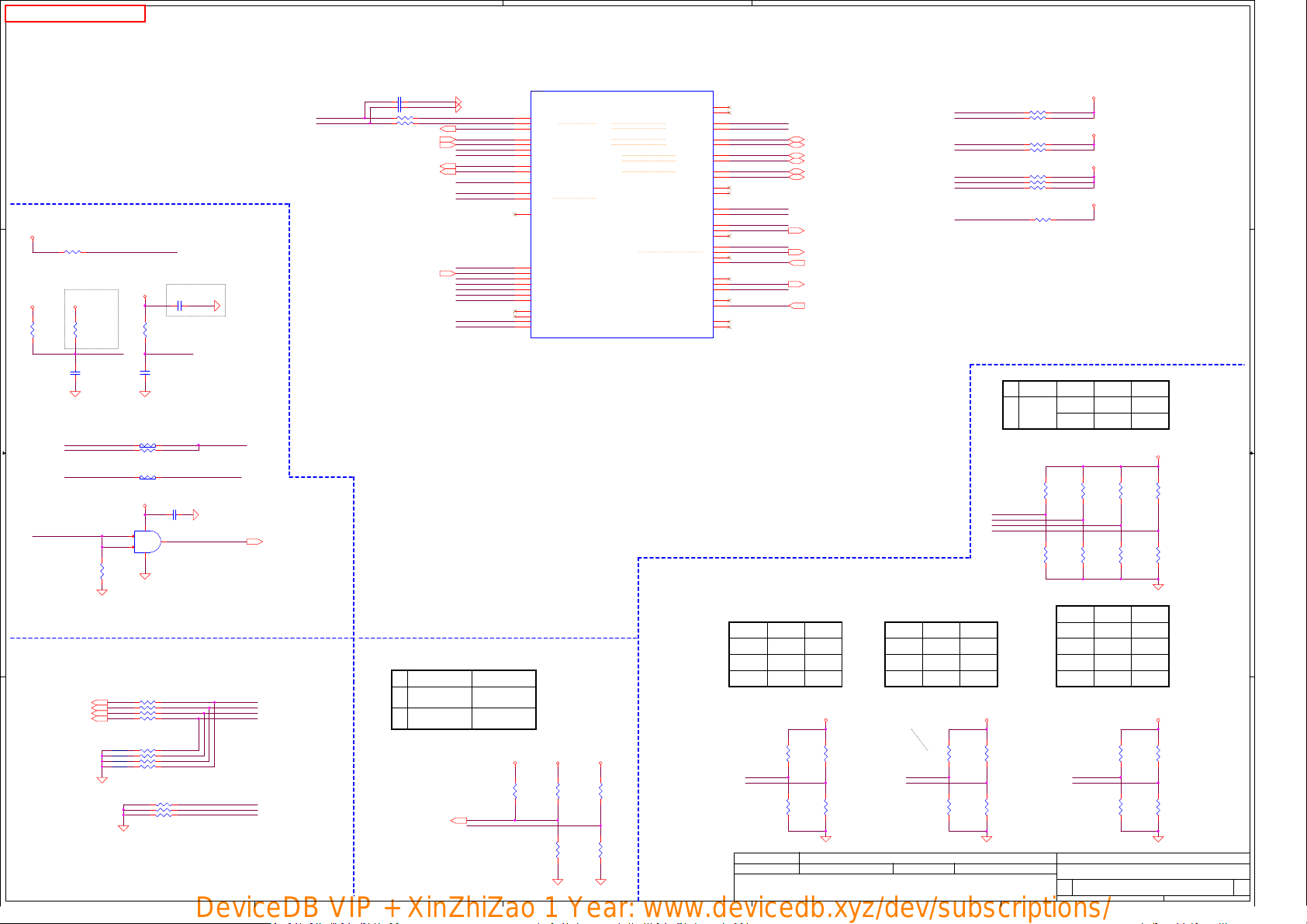

Page 4

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

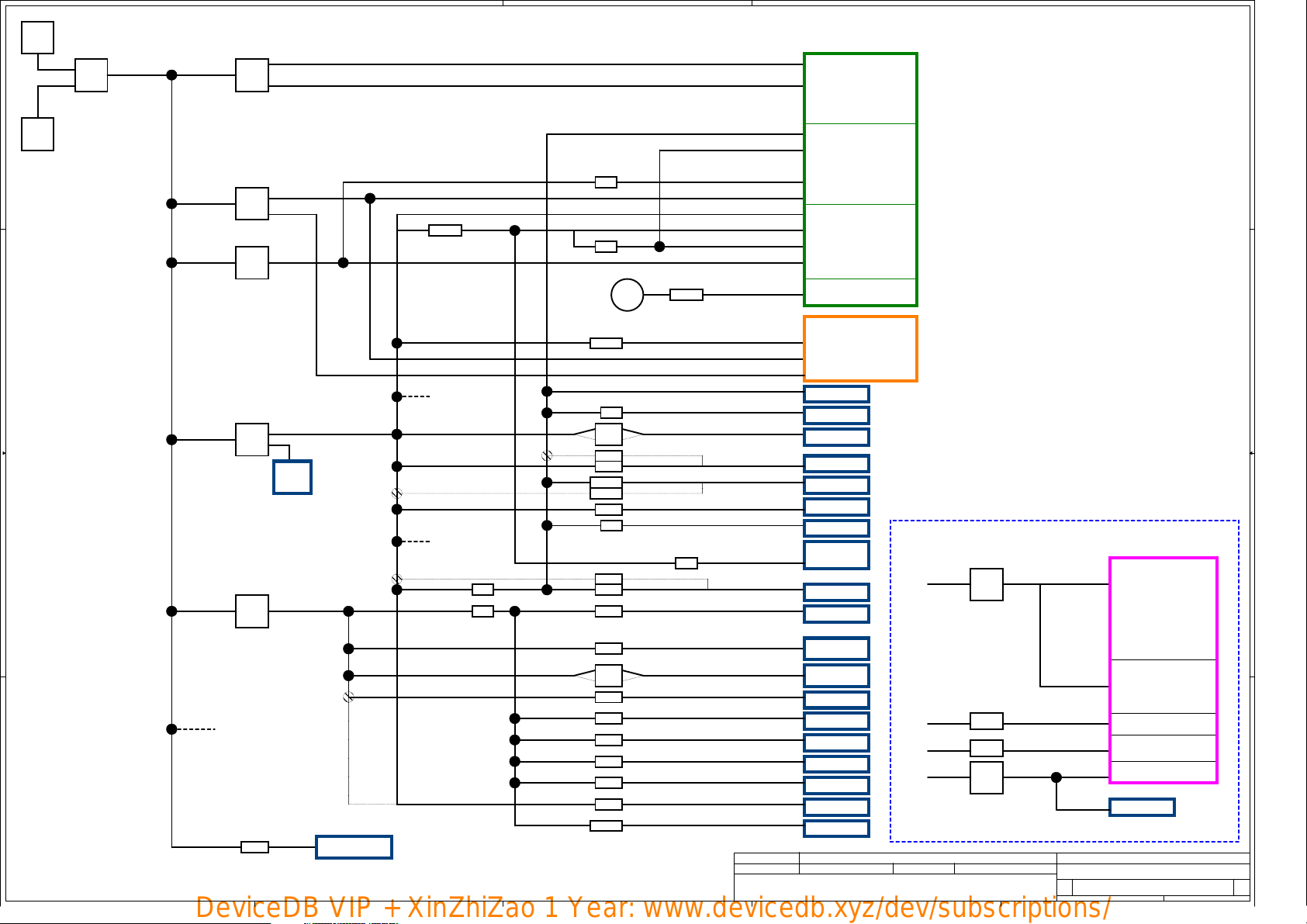

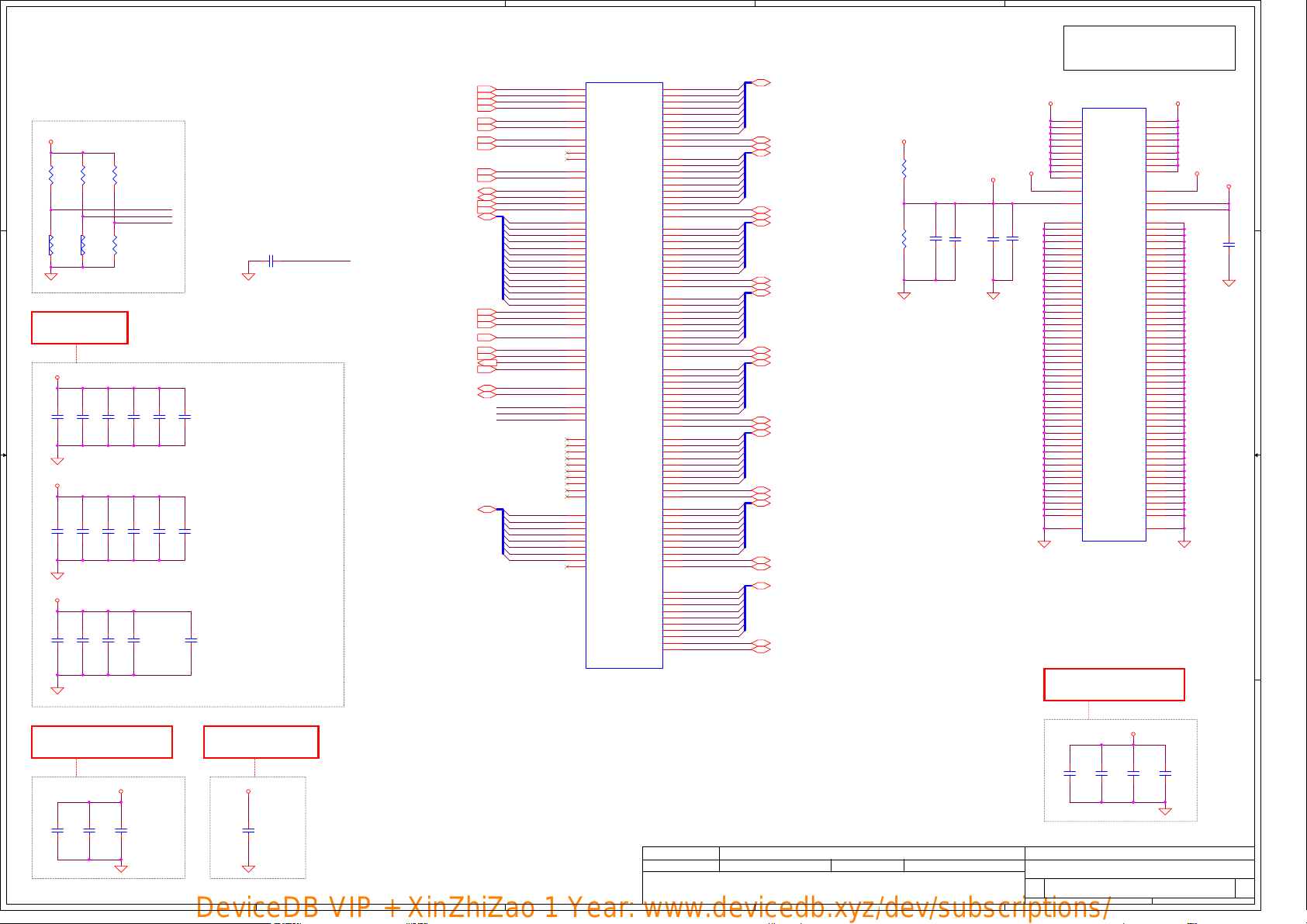

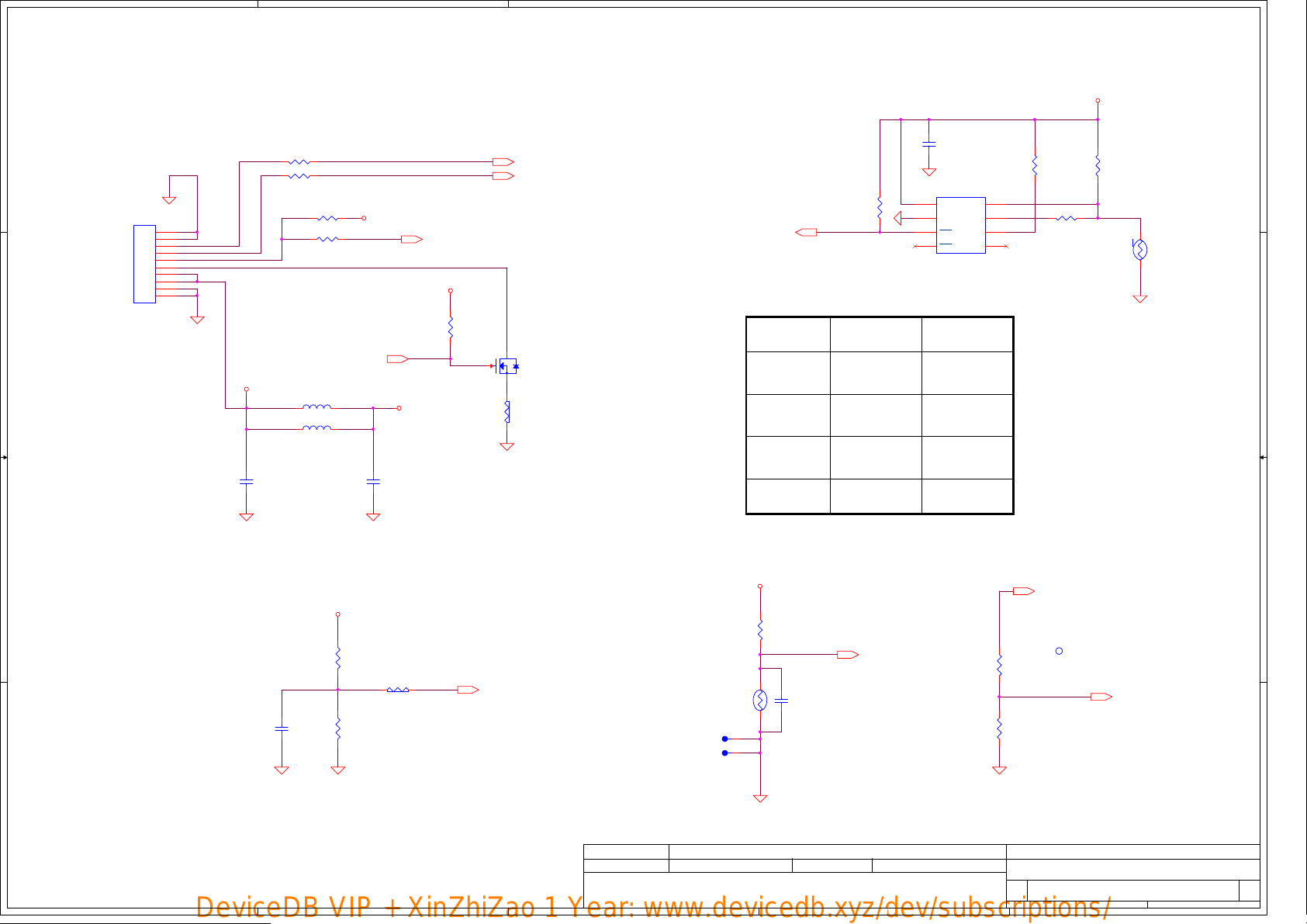

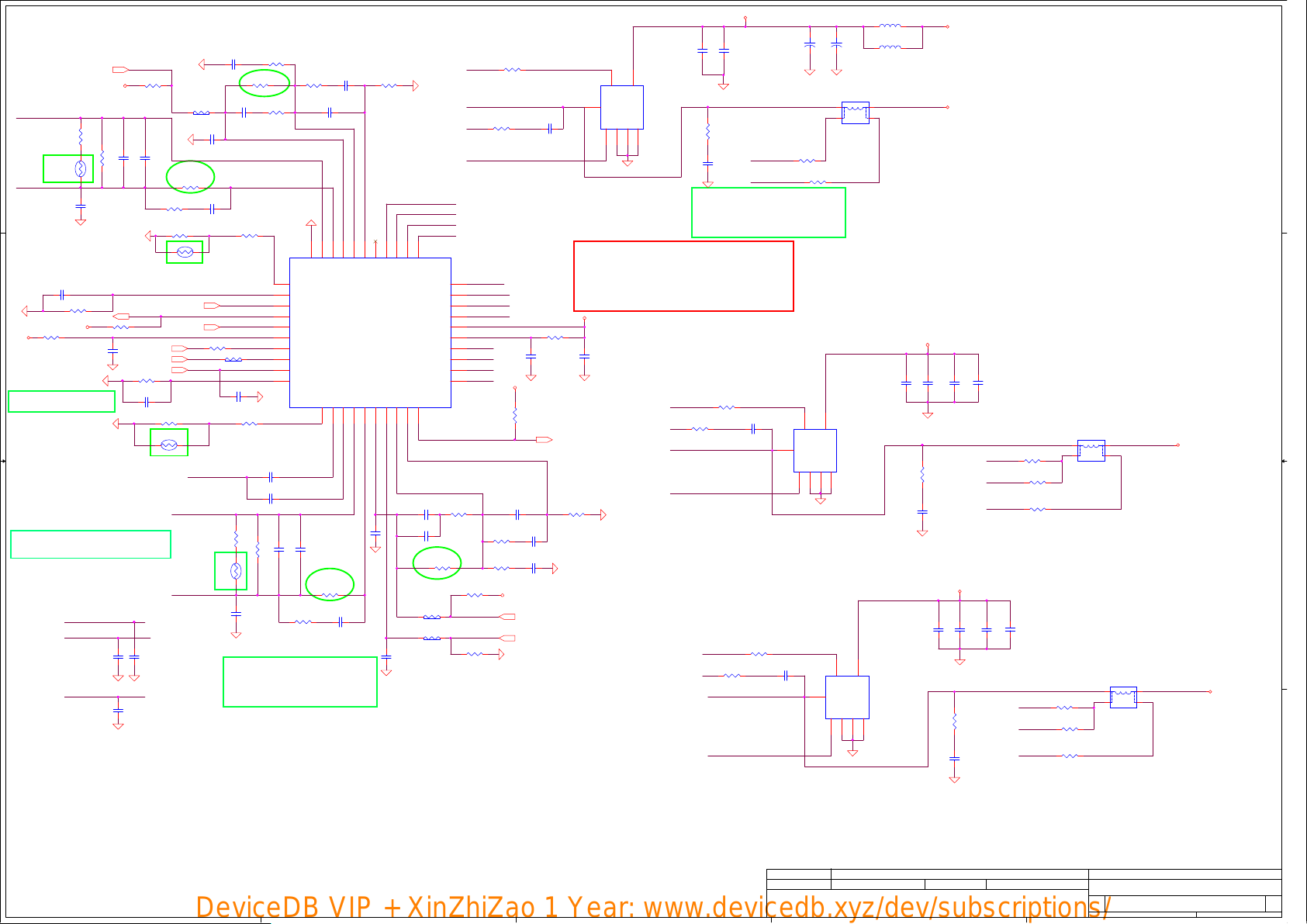

5

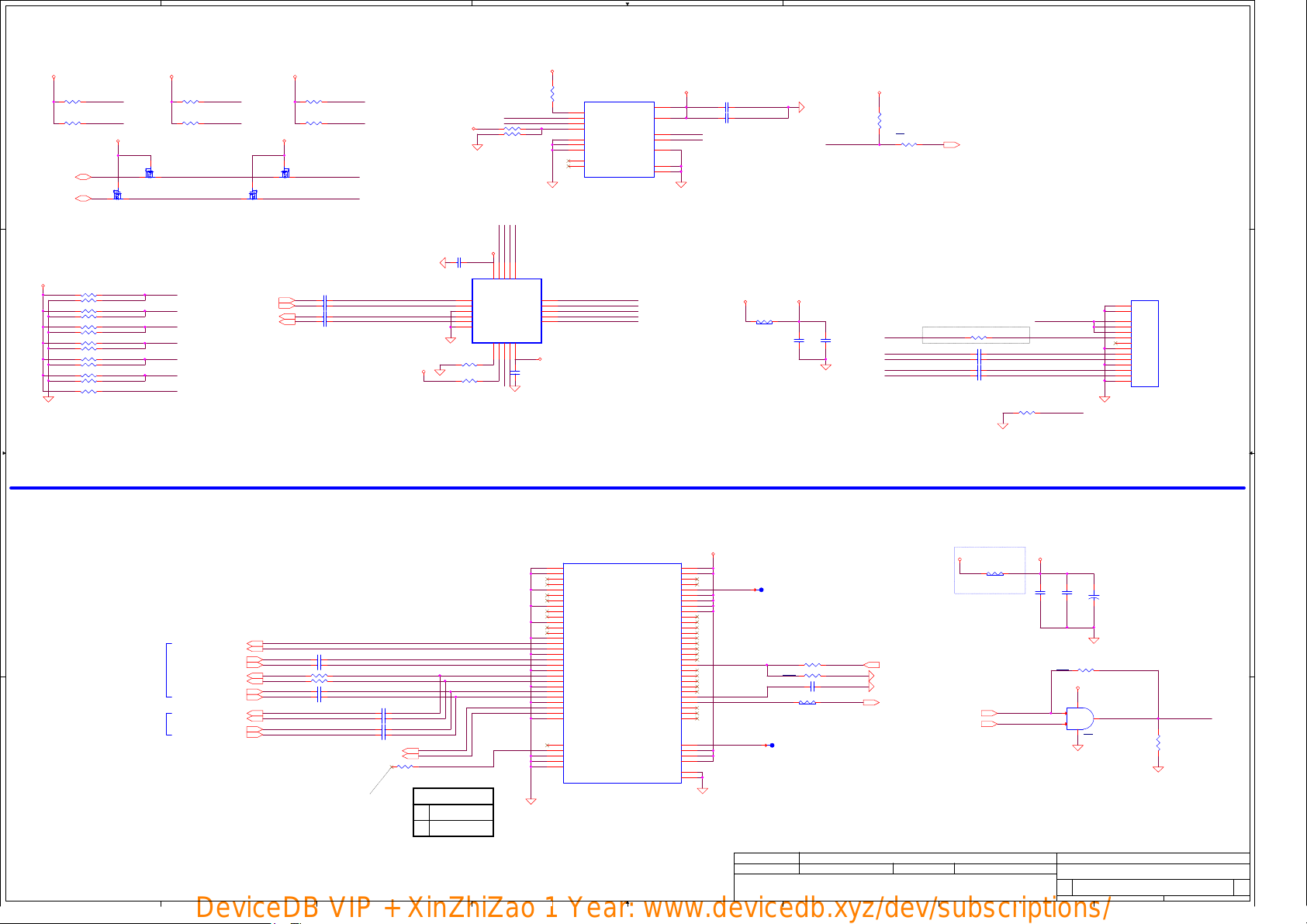

PJP101

AC-IN

PUB1

2705 7mA

+19V B

4827 mA

1515 mA

563m A

5415 mA

+19V _VI N

+12. 6V_BA TT +

D D

PJP201

DC-IN

C C

PUZ1

PUM1

PUF1

PU301

+APU _COR E

+APU _CORE _S OC

+1.2 V

9500 mA

+0.6 VS

1200m A

5000 mA

+0.9 VAL W

+3VL P

KB9022

B B

+5VA LW

1361 0mA8507 mA 7010 mA

PU501

To VGA

+VGA _COR E

+VDD CI/VD D_ 08

+1.3 5VSDG PU

A A

1500 mA

5

L11

3829 mA

226m A

675m A

+INV PWR_ B+

Panel BackLight

1312 7mA

4

+3VA LW

4

1473 mA

546m A

25mA

PU1801

To +1.8VSDGPU

To +3VSDGPU

7075 mA

2700 mA

3

+3VS

+1.8 VS

+0.9 VS

+1.2 V

+3VA LW

+1.8 VAL W

+1.8 VS

+0.9 VAL W

+RTC _APU _R

+2.5 V

+1.2 V

+0.6 VS

+3V_ LAN

+TP_ VCC

+3VS _WLA N

+3V_ HUB

+LCD VDD

+TPM _VC C

+3VS _CA M

+5VS _BL

+USB 2_VC CB

+USB 3_VC CA

+5VS _HD D

+VCC _FAN 1

+VDD A

+5VS _DIS P

+FP_ VCC

+TS_ PWR

APU Power Rail

VDDCR_VDD @0.65-TBD

VDDCR_SOC @0.72-TBD

VDD_33 @0.25A

VDD_18 @2.0A

VDDP @4.0A

VDDIO_MEM_S3 @6.0A

VDD_33_S5 @0.25A

VDD_18_S5 @0.5A

VDDIO_AUDIO @0.2A

VDDP_S5 @1.0A

VDDBT_RTC_G @0.045mA

DDR4 SO-DIMM/MEM-DOWN

+2.5V

+1.2V

+0.6VS

SATA Redriver

SSD

LAN RTL8411

Touch Pad

WLAN

USB HUB

Panel Logic

TPM

Camera

KB Light

USB2.0

USB3.0

(Charger )

USB/B

HDD

FAN1

Audio

HDMI Logic

Finger Print

Touch Screen

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

+APU _COR E

4500 0mA

+APU _CORE _S OC

13000 mA

250m A

2000 mA

UC8

RW1

4000 mA

6000 mA

250m A

500m A

200m A

1000 mA

0.04 5mA

400m A

3500 mA

1200 mA

125m A

3500 mA

+3VS _SSD_ NG FF

1400 mA

200m A

1500 mA

53.7 mA

1500 mA

40mA +5m A

200m A

500m A

2000 mA

2000 mA

2500 mA

2000 mA

2000 mA

1500 mA

1000 mA

100m A

100m A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT B E TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PALELEC TRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PALELEC TRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PALELEC TRONICS, INC. NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAYB E USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT P RIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAYB E USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT P RIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAYB E USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT P RIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

4000 mA

+0.9 VS

U4

+1.8 VS+1.8V AL W

U2

JRTC1

304m A

PUM2

+2.5 V

RM9

UL1

RL27

R463

U13

R212

U2606

R269

U8

+SPI _VC C

+3VS

U2

+5VS

U3

U45

R110

U1

U28

U25

US10

JIO1

RO3

RF1

JPA1

U74

UK6

R3986

3

2

Group C, S 0 domain

Group B, S 0 domain

Group B, S 3 domain

Group A, S 5 domain

R19M-M 18- 70

546m A

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

+19V B

3829 mA

+3VA LW 25mA

+3VA LW

+19V B

675m A

PUV1

UV8

PU701

PUW1

2200 0mA+8 000 mA

1000m A

3000 mA

1

GPU Power Rail

+VGA _COR E

VDDC+VDD CI

+VDD CI

VDD_08

+3VS DGP U

+1.8 VSDG PU

1000 mA

+1.3 5VSDG PU

2000 mA

+1.3 5VSDG PU

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

VDD_GPIO 33

VDD_18

TSVDD

VMEMIO

VRAM x2pcs

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

POWER MAP

POWER MAP

POWER MAP

Document Number Re v

Document Number Re v

Document Number Re v

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

1

@22A 1.225V

@8A 0.95V

@0.025 A

@1A

@1A 1.35V

4 48Friday, March 29, 2019

4 48Friday, March 29, 2019

4 48Friday, March 29, 2019

1.A

1.A

1.A

Page 5

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

5

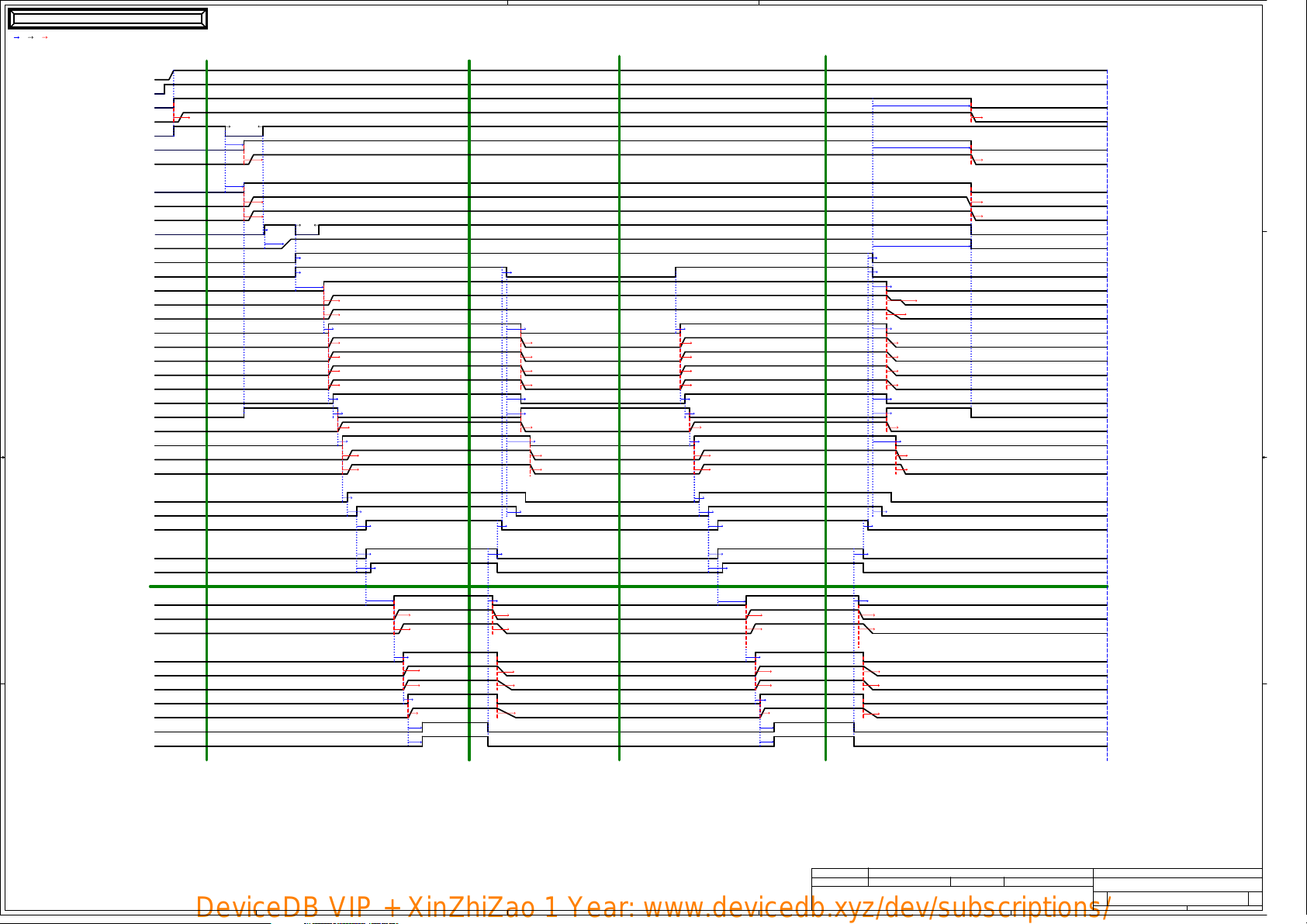

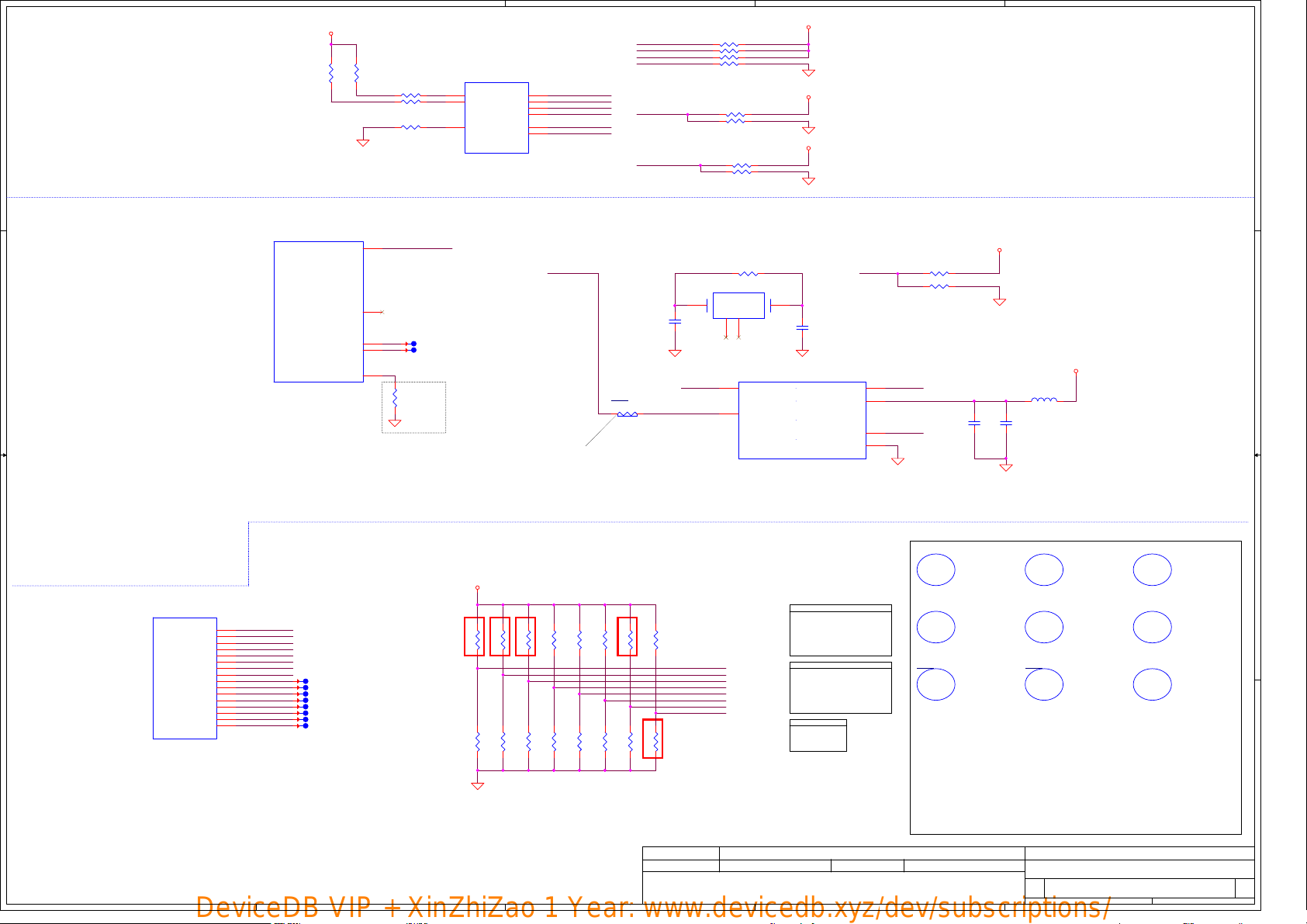

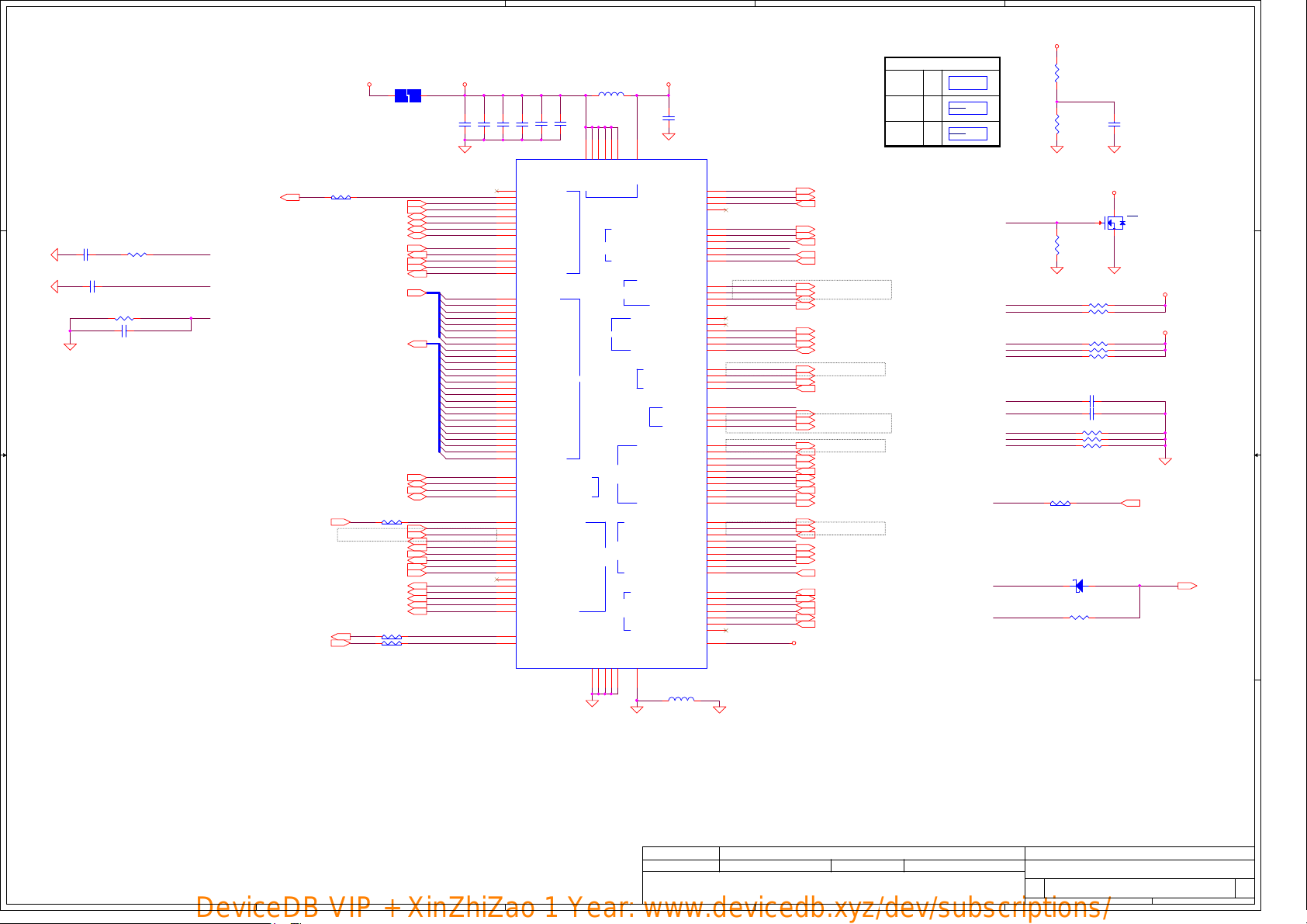

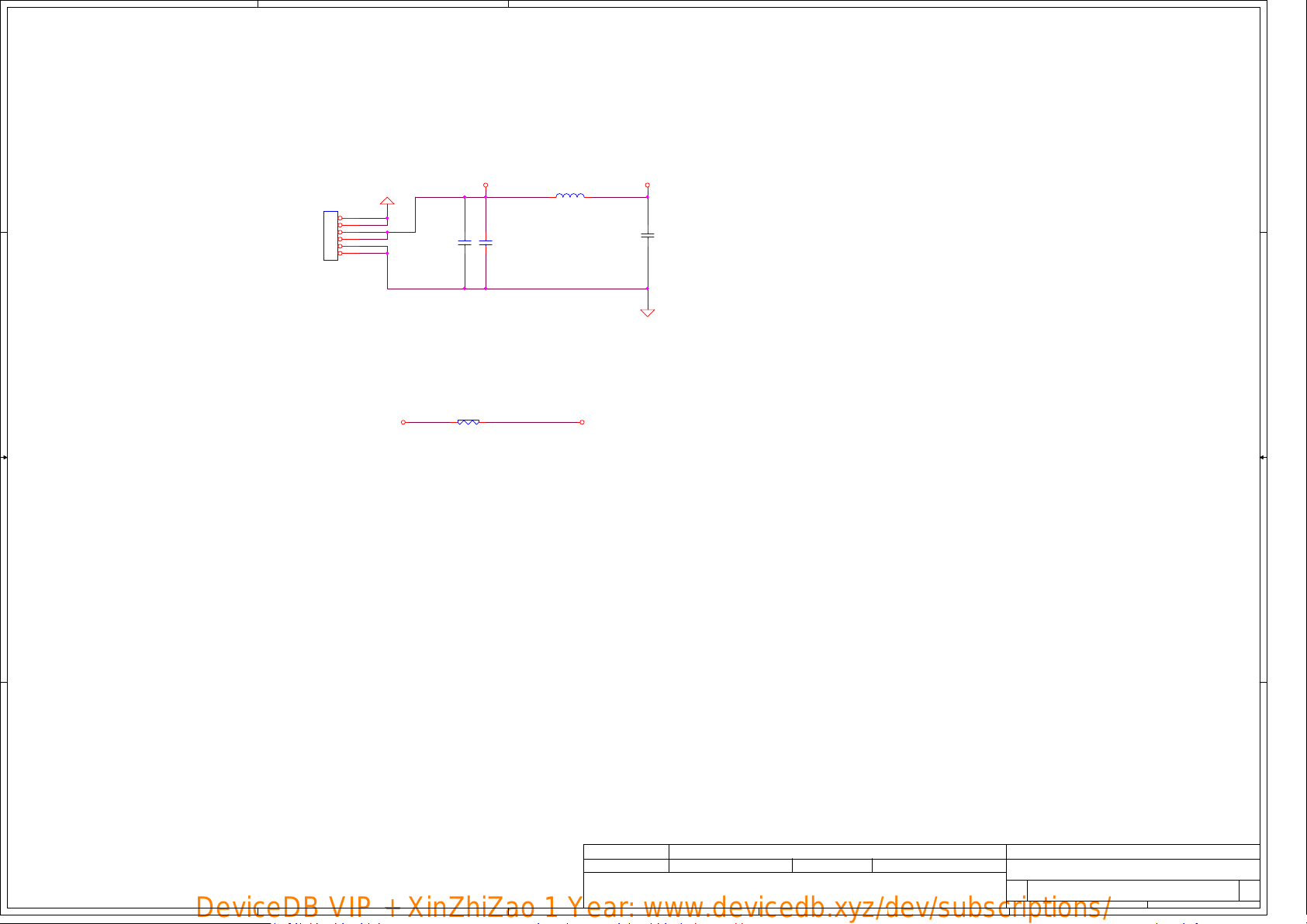

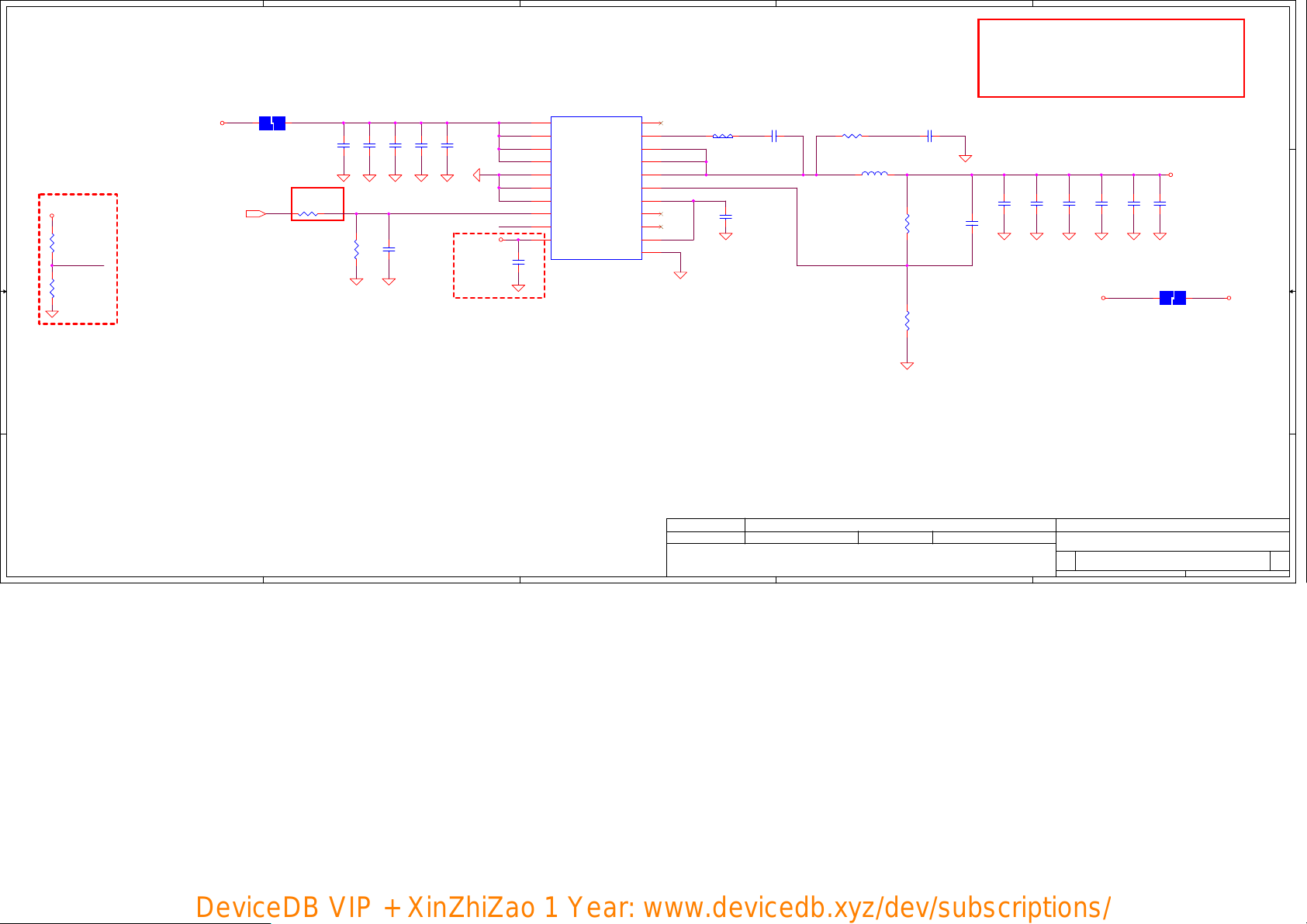

Picasso Ridge Platform Power Sequence

4

3

2

1

AC-IN G3 --> S0

+3VL P

ACIN

EC_O N

D D

+5VAL W

ON/OFF BTN #

3V_E N

+3VAL W

0.9_1. 8VALW_ PWR EN

+1.8VA LW

+0.9VA LW

PBTN_O UT#

EC_RSM RST #

SLP_S 5#

SLP_S 3#

SYSO N

+1.2 V

+2.5 V

SUSP #

C C

+5VS

+3VS

+1.8V S

+0.6V S

KBRST #

0.9VS_ PWR_E N#

+0.9V S

VR_O N

+APU_C ORE

+APU_C ORE_S OC

VGAT E

SYS_PW RGD_ EC

APU_PW ROK

2.423ms, Tr = 640us

250.5ms

91ms

Tr = 1.084ms

91ms

Tr = 1.129ms

Tr = 466.7us

101ms

1.729ms

110ms

160us

160us

105ms

Tr = 280us

Tr = 1.416ms

20.11ms

Tr = 561us

Tr = 593us

Tr = 210us

20.04ms

19.75ms

Tr = 121us Tr = 106.2usTf = 1.836ms Tf = 1.686ms

20.20ms

Tr = 89.7us

Tr = 89.7us

6.121ms

35.42ms

17.99ms

S0 --> S3 S3 --> S0

1.187ms

51.6ms

Tf = 16.15ms

Tf = 29.83ms

Tf = 19.65ms

51.94ms

51.98ms

82.14ms

Tf = 15.49ms

Tf = 3.865ms

24.02ms

3.620ms

18.94ms

Tr = 590us

Tr = 624us

Tr = 235us

Tr = 31.26usTr = 30.4us Tf = 2.91ms Tf = 750us

20.07ms

19.99ms

20.29ms

Tr = 88.14us

Tr = 89.08us

6.099ms

35.49ms

17.79ms

S0 --> S5

8.252s

8.252s

8.252s

1.925ms

1.925ms

66.08ms

Tf = 36.78ms

Tf = 16.34ms

66.04ms

Tf = 15.8ms

Tf = 31.78ms

Tf = 20.94ms

53.88ms

53.92ms

84.04ms

Tf = 9.612ms

Tf = 2.29ms

28.05ms

3.063ms

Tf = 3.903ms

Tf = 5.052ms

Tf = 8.952ms

Tf = 3.453ms

+3VL P

ACIN

EC_O N

+5VAL W

ON/OFF BTN #

3V_E N

+3VAL W

0.9_1. 8VALW_ PWR EN

+1.8VA LW

+0.9VA LW

PBTN_O UT#

EC_RSM RST #

SLP_S 5#

SLP_S 3#

SYSO N

+1.2 V

+2.5 V

SUSP #

+5VS

+3VS

+1.8V S

+0.6V S

KBRST #

0.9VS_ PWR_E N#

+0.9V S

VR_O N

+APU_C ORE

+APU_C ORE_ NB

VGAT E

SYS_PW RGD_ EC

APU_PW ROK

APU_PC IE_RS T#

B B

APU_RS T#

15.59ms

24.78ms

VGA Sequence

PE_GPI O1

+3VSDG PU

+1.8VS DGP U

VGA_ON _B

+VDDC I +VDDC I

+VGA_C ORE

DGPU_P WRGO OD

+1.35V SDGP U

PLT_RS T_VG A#

DGPU_P WRO K

A A

5

491ms

Tr = 854us

4.619ms

Tr = 92.46us

6.120ms

Tr = 385us Tr = 366.1us

133.6ms

133.6ms

4

11.04ms

555.6ms

Tf = 284.8us

Tf = 3.125ms

Tf = 6.844ms

Tf = 3.342ms

Tf = 5.959ms

15.53ms

24.52ms

4.859s

APU_PC IE_RS T#

APU_RS T#

VGA Sequence

212ms

Tr = 927.3us

Tr = 1.413msTr = 1.43ms

4.61ms

Tr = 81.16us

Tr = 84.57usTr = 83.32us

6.122ms

101.7ms

101.7ms

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENTEXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS, INC. NEITHER THIS SHEETNOR THEINFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS, INC. NEITHER THIS SHEETNOR THEINFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZEDBY COMPAL ELECTRONICS, INC. NEITHER THIS SHEETNOR THEINFORMATION IT CONTAINS

MAY BEUSED BY OR DISCLOSED TO ANY THIRD PARTYWITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS,I NC.

MAY BEUSED BY OR DISCLOSED TO ANY THIRD PARTYWITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS,I NC.

3

MAY BEUSED BY OR DISCLOSED TO ANY THIRD PARTYWITHOUT PRIOR WRITTEN CONSENTOF COMPAL ELECTRONICS,I NC.

Issued Date

Issued Date

Issued Date

11.02ms

Tf = 357.5us

Tf = 3.206ms

Tf = 5.884ms

Tf = 2.973ms

Tf = 5.981ms

Compal Secret Data

Compal Secret Data

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

PE_GPI O1

+3VSDG PU

+1.8VS DGP U

VGA_ON _B

+VGA_C ORE

DGPU_P WRGO OD

+1.35V SDGP U

PLT_RS T_VG A#

DGPU_P WRO K

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

Document Number Re v

Document Number Rev

Document Number Rev

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

1

5 48Friday, March 29, 2019

5 48Friday, March 29, 2019

5 48Friday, March 29, 2019

1.A

1.A

1.A

Page 6

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

5

Main Func = CPU

4

3

2

1

UC1B CPU@

D D

PEG_ARX _GTX_P0<15>

PEG_ARX _GTX_N0<15>

PEG_ARX _GTX_P1<15>

PEG PEG

C C

WLAN

LAN

PEG_ARX _GTX_N1<1 5>

PEG_ARX _GTX_P2<15>

PEG_ARX _GTX_N2<1 5>

PEG_ARX _GTX_P3<15>

PEG_ARX _GTX_N3<1 5>

PCIE_ARX_ DTX_P0<26>

PCIE_ARX_ DTX_N0<2 6>

PCIE_ARX_ DTX_P1<25>

PCIE_ARX_ DTX_N1<2 5>

PCIE_ARX_ DTX_P4<27> PCIE_ATX_ DRX_P4 <27>

PCIE_ARX_ DTX_N4<2 7>

PCIE_ARX_ DTX_N5<2 7>

SATA_AR X_DTX_P0<27>

SATA_AR X_DTX_N0<27>

SSD SSD

B B

SATA_AR X_DTX_P1<27>

SATA_AR X_DTX_N1<27>

PEG_ARX _GTX_P0

PEG_ARX _GTX_N0

PEG_ARX _GTX_P1

PEG_ARX _GTX_N1

PEG_ARX _GTX_P2

PEG_ARX _GTX_N2

PEG_ARX _GTX_P3

PEG_ARX _GTX_N3

PCIE_ARX_ DTX_P0

PCIE_ARX_ DTX_N0

PCIE_ARX_ DTX_P1

PCIE_ARX_ DTX_N1

PCIE_ARX_ DTX_P4

PCIE_ARX_ DTX_N4

PCIE_ARX_ DTX_P5

PCIE_ARX_ DTX_N5

SATA_AR X_DTX_P0 SATA_AT X_DRX_P0

SATA_AR X_DTX_N0

SATA_AR X_DTX_P1

SATA_AR X_DTX_N1 SATA_ATX_ DRX_N1

P8

P_GFX_RXP0

P9

P_GFX_RXN0

N6

P_GFX_RXP1

N7

P_GFX_RXN1

M8

P_GFX_RXP2

M9

P_GFX_RXN2

L6

P_GFX_RXP3

L7

P_GFX_RXN3

K11

P_GFX_RXP4

J11

P_GFX_RXN4

H6

P_GFX_RXP5

H7

P_GFX_RXN5

G6

P_GFX_RXP6

F7

P_GFX_RXN6

G8

P_GFX_RXP7

F8

P_GFX_RXN7

N10

P_GPP_RXP0

N9

P_GPP_RXN0

L10

P_GPP_RXP1

L9

P_GPP_RXN1

L12

P_GPP_RXP2

M11

P_GPP_RXN2

P12

P_GPP_RXP3

P11

P_GPP_RXN3

V6

P_GPP_RXP4

V7

P_GPP_RXN4

T8

P_GPP_RXP5

T9

P_GPP_RXN5

R6

P_GPP_RXP6/SATA_RXP0

R7

P_GPP_RXN6/SATA_RXN0

R9

P_GPP_RXP7/SATA_RXP1

R10

P_GPP_RXN7/SATA_RXN1

PCIE

FP5 REV 0.90

PART 2 OF 13

FP5_BGA _1140P

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_GPP_TXP4

P_GPP_TXN4

P_GPP_TXP5

P_GPP_TXN5

P_GPP_TXP6/SATA_TXP0

P_GPP_TXN6/SATA_TXN0

P_GPP_TXP7/SATA_TXP1

P_GPP_TXN7/SATA_TXN1

N1

N3

M2

M4

L2

L4

L1

L3

K2

K4

J2

J4

H1

H3

H2

H4

N2

P3

P4

P2

R3

R1

T4

T2

W2

W4

W3

V2

V1

V3

U2

U4

PEG_ATX _GRX_P0

PEG_ATX _GRX_N0

PEG_ATX _GRX_P1

PEG_ATX _GRX_N1

PEG_ATX _GRX_P2

PEG_ATX _GRX_N2

PEG_ATX _GRX_P3

PEG_ATX _GRX_N3

PCIE_ATX_ DRX_P0

PCIE_ATX_ DRX_N0

PCIE_ATX_ DRX_P1

PCIE_ATX_ DRX_N1

PCIE_ATX_ DRX_P4

PCIE_ATX_ DRX_N4

PCIE_ATX_ DRX_P5

PCIE_ATX_ DRX_N5

SATA_AT X_DRX_N0

SATA_AT X_DRX_P1

1 2

CC1 .1U_0402_16V7 K

1 2

CC2 .1U_0402_16V7 K

1 2

CC3 .1U_0402_16V7 K

1 2

CC4 .1U_0402_16V7 K

PEG_ATX _GRX_P0 <15>

PEG_ATX _GRX_N0 <15 >

PEG_ATX _GRX_P1 <15>

PEG_ATX _GRX_N1 <15 >

PEG_ATX _GRX_P2 <15>

PEG_ATX _GRX_N2 <15 >

PEG_ATX _GRX_P3 <15>

PEG_ATX _GRX_N3 <15 >

PCIE_ATX_ C_DRX_P0 <26 >

PCIE_ATX_ C_DRX_N0 <26>

PCIE_ATX_ C_DRX_P1 <25 >

PCIE_ATX_ C_DRX_N1 <25>

PCIE_ATX_ DRX_N4 <27>

PCIE_ATX_ DRX_P5 <27>PCIE_ARX_ DTX_P5<27>

PCIE_ATX_ DRX_N5 <27>

SATA_AT X_DRX_P0 <27>

SATA_AT X_DRX_N0 <27>

SATA_AT X_DRX_P1 <27>

SATA_AT X_DRX_N1 <27>

WLAN

LAN

SSDSSD

HDDHDD

APU PN Table

APU Platform

UC1 R3APUDC@

UC1 R3APUQC@

UC1 R5APUQC@

Picas so

S IC RYZEN3 YM3200C4T2OFG 2.6G BGA APU

SA0000CCS20

A A

5

S IC RYZEN3 YM3300C4T4MFG 2.1G BGA 1140 APU

SA0000CCV10

4

S IC RYZEN5 YM3500C4T4MFG 2.1G BGA APU

SA0000CCR20

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Customer PNCustomer PNCustomer PNCustomer PN Compal PNCustomer PN

UC1 R7APUQC@

S IC RYZEN7 YM3700C4T4MFG 2.3G BGA APU

SA0000C7640

Compal Secret Data

Compal Secret Data

2020/03/ 29 2020/03/ 29

2020/03/ 29 2020/03/ 29

2020/03/ 29 2020/03/ 29

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

UC1 Athlon@

S IC ATHLON YM300UC4T2OFG 2.4G APU AB O!

SA0000CFE40

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

FP5_(1/7)_PEG/PCIE/SATA

FP5_(1/7)_PEG/PCIE/SATA

FP5_(1/7)_PEG/PCIE/SATA

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

6 48Friday, March 29, 201 9

6 48Friday, March 29, 201 9

6 48Friday, March 29, 201 9

1

1.A

1.A

1.A

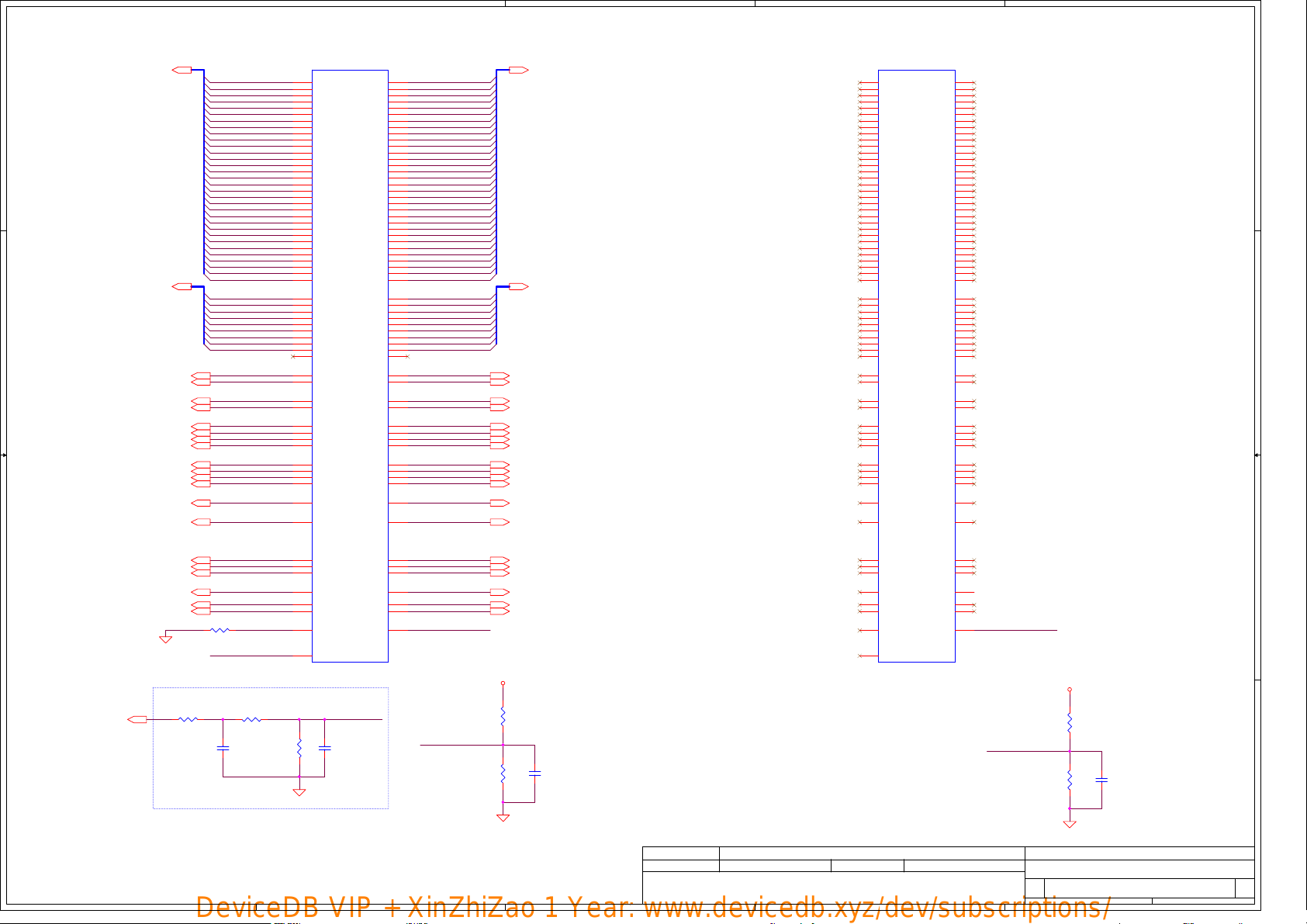

Page 7

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

5

Main Func = CPU

4

3

2

1

DDR_A_MA[13..0]<13>

D D

DDR_A_MA14_W E#< 13>

DDR_A_MA15_CAS#<13>

DDR_A_MA16_RAS#<13>

DDR_A_BA0<13>

DDR_A_BA1<13>

DDR_A_BG0<13>

DDR_A_BG1<13>

DDR_A_ACT#< 13>

DDR_A_DM[7..0]<13>

DDR_A_DQS0<13>

DDR_A_DQS0#<13>

DDR_A_DQS1<13>

DDR_A_DQS1#<13>

DDR_A_DQS2<13>

C C

B B

DDR_A_DQS2#<13>

DDR_A_DQS3<13>

DDR_A_DQS3#<13>

DDR_A_DQS4<13>

DDR_A_DQS4#<13>

DDR_A_DQS5<13>

DDR_A_DQS5#<13>

DDR_A_DQS6<13>

DDR_A_DQS6#<13>

DDR_A_DQS7<13>

DDR_A_DQS7#<13>

DDR_A_CLK0<13>

DDR_A_CLK0#<13>

DDR_A_CLK1<13>

DDR_A_CLK1#<13>

DDR_A_CS0#<13>

DDR_A_CS1#<13>

DDR_A_CKE0<13>

DDR_A_CKE1<13>

DDR_A_ODT0<13>

DDR_A_ODT1<13>

DDR_A_ALERT#<13>

DDR_A_EVENT#<13>

DDR_A_RST#<13>

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14_W E#

DDR_A_MA15_CAS#

DDR_A_MA16_RAS#

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDR_A_BG1

DDR_A_ACT#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS0#

DDR_A_DQS1

DDR_A_DQS1#

DDR_A_DQS2

DDR_A_DQS2#

DDR_A_DQS3

DDR_A_DQS3#

DDR_A_DQS4

DDR_A_DQS4#

DDR_A_DQS5

DDR_A_DQS5#

DDR_A_DQS6

DDR_A_DQS6#

DDR_A_DQS7

DDR_A_DQS7#

DDR_A_CLK0

DDR_A_CLK0#

DDR_A_CLK1

DDR_A_CLK1#

DDR_A_CS0#

DDR_A_CS1#

DDR_A_CKE0

DDR_A_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_ALERT#

DDR_A_EVENT#

DDR_A_RST#

AF25

AE23

AD27

AE21

AC24

AC26

AD21

AC27

AD22

AC21

AF22

AA24

AC23

AJ25

AG27

AG23

AG26

AF21

AF27

AA21

AA27

AA22

AL24

AN27

AW25

AT21

AM26

AM27

AN24

AN25

AU23

AT23

AV20

AW20

AD25

AD24

AE26

AE27

AG21

AJ27

AG24

AJ22

AA25

AE24

F21

G27

N24

N23

T27

F22

G22

H27

H26

N27

N26

R21

P21

V24

V23

Y23

Y26

Y24

UC1A CPU@

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13_BANK2

MA_WE_L_ADD14

MA_CAS_L_ADD15

MA_RAS_L_ADD16

MA_BANK0

MA_BANK1

MA_BG0

MA_BG1

MA_ACT_L

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

RSVD_36

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

RSVD_41

RSVD_40

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CS_L0

MA_CS_L1

MA_CKE0

MA_CKE1

MA_ODT0

MA_ODT1

MA_ALERT_L

MA_EVENT_L

MA_RESET_L

MEMORY A

FP5 REV 0.90

PART 1 OF 13

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

RSVD_34

RSVD_35

RSVD_51

RSVD_52

RSVD_27

RSVD_28

RSVD_43

RSVD_42

MA_PAROUT

J21

H21

F23

H23

G20

F20

J22

J23

G25

F26

L24

L26

L23

F25

K25

K27

M25

M27

P27

R24

L27

M24

P24

P25

M22

N21

T22

V21

L21

M20

R23

T21

AL27

AL25

AP26

AR27

AK26

AK24

AM24

AP27

AM23

AM21

AR25

AU27

AL22

AL21

AP24

AP23

AW26

AV25

AV22

AW22

AU26

AV27

AW23

AT22

AW21

AU21

AP21

AN20

AR22

AN22

AT20

AR20

T24

T25

W25

W27

R26

R27

V27

V26

AF24

DDR_A_DQ0

DDR_A_DQ1

DDR_A_DQ2

DDR_A_DQ3

DDR_A_DQ4

DDR_A_DQ5

DDR_A_DQ6

DDR_A_DQ7

DDR_A_DQ8

DDR_A_DQ9

DDR_A_DQ10

DDR_A_DQ11

DDR_A_DQ12

DDR_A_DQ13

DDR_A_DQ14

DDR_A_DQ15

DDR_A_DQ16

DDR_A_DQ17

DDR_A_DQ18

DDR_A_DQ19

DDR_A_DQ20

DDR_A_DQ21

DDR_A_DQ22

DDR_A_DQ23

DDR_A_DQ24

DDR_A_DQ25

DDR_A_DQ26

DDR_A_DQ27

DDR_A_DQ28

DDR_A_DQ29

DDR_A_DQ30

DDR_A_DQ31

DDR_A_DQ32

DDR_A_DQ33

DDR_A_DQ34

DDR_A_DQ35

DDR_A_DQ36

DDR_A_DQ37

DDR_A_DQ38

DDR_A_DQ39

DDR_A_DQ40

DDR_A_DQ41

DDR_A_DQ42

DDR_A_DQ43

DDR_A_DQ44

DDR_A_DQ45

DDR_A_DQ46

DDR_A_DQ47

DDR_A_DQ48

DDR_A_DQ49

DDR_A_DQ50

DDR_A_DQ51

DDR_A_DQ52

DDR_A_DQ53

DDR_A_DQ54

DDR_A_DQ55

DDR_A_DQ56

DDR_A_DQ57

DDR_A_DQ58

DDR_A_DQ59

DDR_A_DQ60

DDR_A_DQ61

DDR_A_DQ62

DDR_A_DQ63

DDR_A_PAR

DDR_A_DQ[63..0] <1 3>

DDR_A_PAR <13>

DDR_B_MA[13..0]<14>

DDR_B_MA14_ WE#<14>

DDR_B_MA15_ CAS#<14>

DDR_B_MA16_ RAS#<14>

DDR_B_BA0<14>

DDR_B_BA1<14>

DDR_B_BG0<14>

DDR_B_BG1<14>

DDR_B_ACT#< 14>

DDR_B_DM[7 ..0]<14>

DDR_B_DQS0<14>

DDR_B_DQS0 #<14>

DDR_B_DQS1<14>

DDR_B_DQS1 #<14>

DDR_B_DQS2<14>

DDR_B_DQS2 #<14>

DDR_B_DQS3<14>

DDR_B_DQS3 #<14>

DDR_B_DQS4<14>

DDR_B_DQS4 #<14>

DDR_B_DQS5<14>

DDR_B_DQS5 #<14>

DDR_B_DQS6<14>

DDR_B_DQS6 #<14>

DDR_B_DQS7<14>

DDR_B_DQS7 #<14>

DDR_B_CLK 0<14>

DDR_B_CLK 0#<14>

DDR_B_CLK 1<14>

DDR_B_CLK 1#<14>

DDR_B_CS0 #<14>

DDR_B_CS1 #<14>

DDR_B_CKE0<14>

DDR_B_CKE1<14>

DDR_B_ODT 0<14>

DDR_B_ODT 1<14>

DDR_B_ALERT #<14>

DDR_B_EVENT #<14>

DDR_B_RST #<14>

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14_ WE#

DDR_B_MA15_ CAS#

DDR_B_MA16_ RAS#

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_BG1

DDR_B_ACT#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS0 #

DDR_B_DQS1

DDR_B_DQS1 #

DDR_B_DQS2

DDR_B_DQS2 #

DDR_B_DQS3

DDR_B_DQS3 #

DDR_B_DQS4

DDR_B_DQS4 #

DDR_B_DQS5

DDR_B_DQS5 #

DDR_B_DQS6

DDR_B_DQS6 #

DDR_B_DQS7

DDR_B_DQS7 #

DDR_B_CLK 0

DDR_B_CLK 0#

DDR_B_CLK 1

DDR_B_CLK 1#

DDR_B_CS0 #

DDR_B_CS1 #

DDR_B_CKE0

DDR_B_CKE1

DDR_B_ODT 0

DDR_B_ODT 1

DDR_B_ALERT #

DDR_B_EVENT #

DDR_B_RST #

FP5_BGA_1140P

AG30

AC32

AC30

AB29

AB31

AA30

AA29

AA31

W29

AH29

W31

AL30

AK30

AK32

AJ30

AH31

AG32

AP30

AW31

BB26

BD22

AR29

AR31

AW30

AW29

BC25

BA25

BC22

BA22

AC31

AD30

AD29

AD31

AE30

AE32

AF29

AF31

AJ31

AM31

AJ29

AM29

AL31

AM32

AL29

AM30

W30

AG29

Y30

Y32

V31

V29

V30

C21

C25

E32

K30

N32

D22

B22

D25

B25

F29

F30

K31

K29

N31

N29

U29

T30

V32

U31

T31

UC1I CPU@

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13_BANK2

MB_WE_L_ADD14

MB_CAS_L_ADD15

MB_RAS_L_ADD16

MB_BANK0

MB_BANK1

MB_BG0

MB_BG1

MB_ACT_L

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

RSVD_21

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

RSVD_20

RSVD_18

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB1_CS_L1

MB0_CKE0

MB0_CKE1

MB1_CKE0

MB1_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB_ALERT_L

MB_EVENT_L

MB_RESET_L

MEMORY B

FP5 REV 0.90

PART 9 OF 13

FP5_BGA_1140P

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

RSVD_17

RSVD_19

RSVD_26

RSVD_29

RSVD_16

RSVD_15

RSVD_25

RSVD_24

MB_PAROUT

B21

D21

B23

D23

A20

C20

A22

C22

D24

A25

D27

C27

C23

B24

C26

B27

C30

E29

H29

H31

A28

D28

F31

G30

J29

J31

L29

L31

H30

H32

L30

L32

AP29

AP32

AT29

AU32

AN30

AP31

AR30

AT31

AU29

AV30

BB30

BA28

AU30

AU31

AY32

AY29

BA27

BC27

BA24

BC24

BD28

BB27

BB25

BD25

BC23

BB22

BC21

BD20

BB23

BA23

BB21

BA21

M31

N30

P31

R32

M30

M29

P30

P29

AG31

DDR_B_DQ0

DDR_B_DQ1

DDR_B_DQ2

DDR_B_DQ3

DDR_B_DQ4

DDR_B_DQ5

DDR_B_DQ6

DDR_B_DQ7

DDR_B_DQ8

DDR_B_DQ9

DDR_B_DQ10

DDR_B_DQ11

DDR_B_DQ12

DDR_B_DQ13

DDR_B_DQ14

DDR_B_DQ15

DDR_B_DQ16

DDR_B_DQ17

DDR_B_DQ18

DDR_B_DQ19

DDR_B_DQ20

DDR_B_DQ21

DDR_B_DQ22

DDR_B_DQ23

DDR_B_DQ24

DDR_B_DQ25

DDR_B_DQ26

DDR_B_DQ27

DDR_B_DQ28

DDR_B_DQ29

DDR_B_DQ30

DDR_B_DQ31

DDR_B_DQ32

DDR_B_DQ33

DDR_B_DQ34

DDR_B_DQ35

DDR_B_DQ36

DDR_B_DQ37

DDR_B_DQ38

DDR_B_DQ39

DDR_B_DQ40

DDR_B_DQ41

DDR_B_DQ42

DDR_B_DQ43

DDR_B_DQ44

DDR_B_DQ45

DDR_B_DQ46

DDR_B_DQ47

DDR_B_DQ48

DDR_B_DQ49

DDR_B_DQ50

DDR_B_DQ51

DDR_B_DQ52

DDR_B_DQ53

DDR_B_DQ54

DDR_B_DQ55

DDR_B_DQ56

DDR_B_DQ57

DDR_B_DQ58

DDR_B_DQ59

DDR_B_DQ60

DDR_B_DQ61

DDR_B_DQ62

DDR_B_DQ63

DDR_B_PAR

DDR_B_DQ[63 ..0] <14>

DDR_B_PAR <14>

EVENT# pull high

+1.2V

1 2

RC1 1K_0402_5%

+1.2V

1 2

A A

5

RC2 1K_0402_5%

DDR_B_EVENT #

DDR_A_EVENT#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Nu mber R ev

Size Document Nu mber R ev

Size Document Nu mber R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

Compal Electronics, Inc.

FP5_(2/7)_DDR4

FP5_(2/7)_DDR4

FP5_(2/7)_DDR4

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

1.A

1.A

7 48Friday, March 29, 2019

7 48Friday, March 29, 2019

1

7 48Friday, March 29, 2019

1.A

Page 8

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

A

Main Func = CPU

EC/THERM

+3VS

1 2

RC105 1K_0402_ 5%

1 2

RC106 1K_0402_ 5%

1 2

RC107 1K_0402_ 5%

1 2

RC108 1K_0402_ 5%

1 1

EC_SMB_CK2<16 ,29>

EC_SMB_DA2<16 ,29>

2 2

+3VS

1 2

RC664 1K_0402_5%

1

@EMC@

CC1202

.1U_0402_1 6V7K

2

1

EMC@

CC5

33P_0402_5 0V8J

2

Close to APU

SVID

+1.8VS

1 2

3 3

RC109 1K_0402_ 5%@

1 2

RC110 1K_0402_ 5%@

1 2

RC111 1K_0402_ 5%@

EC_SMB_CK2

EC_SMB_DA2

THERMTRIP#

APU_SID

APU_ALERT#

APU_SIC

APU_PROCHOT#

RC616 0_0402_ 5%@

RC617 0_0402_ 5%@

1

EMC@

CC6

33P_0402_5 0V8J

2

APU_SVT_R

APU_SVC

APU_SVD

1 2

1 2

APU_PROCHOT#

APU_RST#

APU_PWROK

APU_SIC

APU_SID

APU_SVT_R<41>

HDMI

EDP

+1.8VS

+1.8VS

APU_PWROK<41>

APU_SVC<41>

APU_SVD<41>

B

APU_DP0_P0<24>

APU_DP0_N0<24>

APU_DP0_P1<24>

APU_DP0_N1<24>

APU_DP0_P2<24>

APU_DP0_N2<24>

APU_DP0_P3<24>

APU_DP0_N3<24>

EDP_TXP0<23>

EDP_TXN0<23>

EDP_TXP1<23>

EDP_TXN1<23>

1 2

RC80 300_0402_ 5%

1 2

RC81 300_0402_ 5%

THERMTRIP#<29>

APU_PROCHOT#<29,36,41>

1 2

RC669 0_0402_5%

1 2

RC670 0_0402_5%

APU_DP0_P0

APU_DP0_N0

APU_DP0_P1

APU_DP0_N1

APU_DP0_P2

APU_DP0_N2

APU_DP0_P3

APU_DP0_N3

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

APU_RST#

APU_PWROK

APU_SIC

APU_SID

APU_ALERT#

THERMTRIP#

APU_PROCHOT#

APU_SVC_R

APU_SVD_R

APU_SVT_R

AW3

AW4

AW2

AP16

C8

A8

D8

B8

B6

C7

C6

D6

E6

D5

E1

C1

F3

E4

F4

F2

AU2

AU4

AU1

AU3

AV3

H14

J14

J15

L19

F16

H16

J16

UC1C CPU @

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

TDI

TDO

TCK

IO18S5

TMS

TRST_L

DBREQ_L

RESET_L

IO18

PWROK

SIC

SID

ALERT_L

THERMTRIP_L

PROCHOT_L

SVC0

IO18

SVD0

SVT0

C

DISPLAY/SVI2/ JTAG/TE ST

DP3:

DP2:

DP1: eDP

DP0: HDMI

IO33

FP5 REV 0.90

PART 3 OF 13

FP5_BGA_1140P

IO18

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP_STEREOSYNC

SMU_ZVDD

CORETYPE

VDDP_SENSE

VDDCR_SOC_SENSE

VDDCR_SENSE

VSS_SENSE_A

VSS_SENSE_B

DP_BLON

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

RSVD_4

RSVD_3

RSVD_2

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST31

TEST41

TEST470

TEST471

ENBKL_R

G15

ENVDD_R

F15

INVTPWM_R

L14

APU_DP0_CTR L_CLK

D9

APU_DP0_CTR L_DATA

B9

APU_DP0_HPD

C10

EDP_AUXP

G11

EDP_AUXN

F11

EDP_HPD

G13

J12

H12

K13

J10

H10

K8

DP_STEREOSYNC

K15

F14

F12

F10

APU_TEST4

AP14

APU_TEST5

AN14

F13

APU_TEST14

G18

APU_TEST15

H19

APU_TEST16

F18

APU_TEST17

F19

APU_TEST31

W24

APU_TEST41

AR11

APU_TEST470

AJ21

APU_TEST471

AK21

SMU_ZVDDP

V4

AW11

CORETYPE

APU_VDDP_SEN_H

AN11

APU_CORESOC_SE N_H

J19

APU_CORE_SEN_ H

K18

APU_VSS_SEN_L

J18

APU_VDDP_SEN_L

AM11

APU_DP0_CTR L_CLK <2 4>

APU_DP0_CTR L_DATA <24 >

APU_DP0_HPD <24>

EDP_AUXP < 23>

EDP_AUXN <23>

EDP_HPD <23>

TP@

T4949

TP@

T4948

TP@

T4942

TP@

T4941

TP@

T4940

TP@

T4939

1 2

RC1682 196_040 2_1%

1 2

RC1681 1K_0402 _5%@

APU_VDDP_SEN_H <39>

APU_CORESOC_SE N_H <41>

APU_CORE_SEN_ H <41>

APU_VSS_SEN_L <41>

APU_VDDP_SEN_L < 39>

D

HDMI

EDP

+0.9VS

+3VALW

Leakage prevent from power side

DISP

ENBKL_R

ENVDD_R

ENVDD_R

INVTPWM_R

ENBKL

ENVDD

INVTPWM

ENBKL_R

ENVDD_R

INVTPWM_R

+1.8VALW

5

UC66

1

P

NC

4

ENBKL

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

SA00004BV00

+1.8VALW

5

UC64

1

P

NC

4

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

SA00004BV00

@

1 2

RC690 0_0402_5%RS @

+1.8VALW

5

UC65

1

P

NC

4

Y

2

A

G

NL17SZ07DFT 2G_SC70-5

3

SA00004BV00

1 2

RC3 4.7K_0402_5 %

1 2

RC4 4.7K_0402_5 %@

1 2

RC5 4.7K_0402_5 %

1 2

RC6130 100K_04 02_5%

1 2

RC6131 100K_04 02_5%

1 2

RC6132 100K_04 02_5%@

ENVDD

INVTPWM

E

ENBKL <2 9>

ENVDD <23>

ENVDD

INVTPWM <23>

+3VS

HDT+

+1.8VALW

1 2

RH21 33_0402_5%

RH38 10K_0402_5%

2

CH2

0.01U_0402 _16V7K

4 4

RH39 10K_0402_5%

1

RH40 10K_0402_5%

12

12

12

A

APU_TRST#_R

HDT_P11 APU_RST#

HDT_P13

HDT_P15

JHDT1

CONN@

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

SAMTE_ASP-13644 6-07-B

2

4

6

8

10

12

14

16

18

20

APU_TCK_R

APU_TMS_R

APU_TDI_R

APU_TDO_R

APU_PWROK_R

APU_RST#_R

APU_DBREQ#_R

B

1 2

RH27 0_0402_5%HDT @

1 2

RH28 0_0402_5%HDT @

1 2

RH29 0_0402_5%HDT @

1 2

RH30 0_0402_5%HDT @

1 2

RH31 0_0402_5%HDT @

1 2

RH32 0_0402_5%HDT @

1 2

RH33 33_0402_5%

Follow C5V08

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWROK

APU_DBREQ#

APU_TCK

APU_TMS

APU_TDI

APU_DBREQ#

APU_TRST#APU_TRST#

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

1 2

RH34 1K_0402_5%

1 2

RH35 1K_0402_5%

1 2

RH36 1K_0402_5%

1 2

RH37 1K_0402_5%

1 2

RH26 1K_0402_5 %

Issued Date

Issued Date

Issued Date

+1.8VALW

Compal Secret Data

Compal Secret Data

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

TESTPOINT

DP_STEREOSYNC

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

Title

Title

Title

Size Document Nu mber R ev

Size Document Nu mber R ev

Size Document Nu mber R ev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

1 2

RC155 1K_0402_5%

1 2

RC154 1K_0402_5%@

RC112 10K_0201 _5%@

RC113 10K_0201 _5%@

RC114 10K_0201 _5%@

RC115 10K_0201 _5%@

12

12

12

12

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

(3/7)_DISP/MISC/HDT

(3/7)_DISP/MISC/HDT

(3/7)_DISP/MISC/HDT

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

E

+1.8VS

+1.8VS

1.A

1.A

8 48Friday, March 29, 2019

8 48Friday, March 29, 2019

8 48Friday, March 29, 2019

1.A

Page 9

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

Main Func = CPU

A

B

C

D

E

1 2

CC7 150P_0402_50V8J

1 2

CC100 150P_04 02_50V8J@

1 2

1 1

RC29 33_0402_5%

1 2

RC704 33_0402_5%@

EC_RSMRST#<29>

PBTN_OUT#<29>

SYS_PWRGD_EC<29 >

SLP_S3#<29>

SLP_S5#<29>

APU_PCIE_RST#_RAPU_PCIE_RST#_C

APU_PCIE1_RST#_RAPU_PCIE1_RST#_C

EC_RSMRST#

PBTN_OUT#

SYS_PWRGD_EC

SYS_RST#

APU_PCIE_WAKE#

SLP_S3#

SLP_S5#

AGPIO10

AGPIO23

AGPIO12

ACPI

+3VALW

1 2

RC6133 10K_0402_5%

CRB use S0-rail

+3VALW

2 2

3 3

+3VS

12

12

RC28

RC6165

10K_0402_1%

10K_0402_1%@

2

CC8

0.22U_0402_16V7K

1

APU_PCIE_RST#_C APU_PCIE_RST#_U

APU_PCIE1_RST#_C

APU_PCIE_RST#_U APU_PCIE_RST#

APU_PCIE_RST#_U

RC6160

10K_0402_5% @

APU_PCIE_WAKE#

Reserve for MBDG/CRB

+1.8VALW

CC1210

10U_0603_6.3V6M

1 2

@

12

RC54

22K_0402_1%

SYS_PWRGD_EC EC_RSMRST#

1 2

RC700 0_0402_5%RS@

1 2

RC701 0_0402_5%@

1 2

RC30 0_0402_5%RS@

+3VALW

1

IN1

2

IN2

@

1

CC16

1U_0201_6.3V6M

2

CC14

0.1U_0201_10V6K

1 2

@

5

P

4

O

G

UC4

SA00000OH00

3

MC74VHC1G08DFT2G_SC70-5

APU_PCIE_RST#

APU_PCIE_RST# <15,25,26,27>

HDA_BIT_CLK

HDA_SDIN0<28>

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_RST#

HDA_SYNC

HDA_SDOUT

AGPIO7

AGPIO8

UC1D CPU@

BD5

PCIE_RST0_L/EGPIO26

BB6

PCIE_RST1_L/EGPIO27

AT16

RSMRST_L

AR15

PWR_BTN_L/AGPIO0

AV6

PWR_GOOD

AP10

SYS_RESET_L/AGPIO1

AV11

WAKE_L/AGPIO2

AV13

SLP_S3_L

AT14

SLP_S5_L

AR8

S0A3_GPIO/AGPIO10

AT10

AC_PRES/AGPIO23

AN6

LLB_L/AGPIO12

AW8

EGPIO42

AR2

AZ_BITCLK/TDM_BCLK_MIC

AP7

AZ_SDIN0/CODEC_GPI

AP1

AZ_SDIN1/SW_DATA1B/TDM_BCLK_PLAYBACK

AP4

AZ_SDIN2/SW_DATA2/TDM_DATA_PLAYBACK

AP3

AZ_RST_L/SW_DATA1A/SW_DATA3/TDM_DATA_MIC

AR4

AZ_SYNC/TDM_FRM_MIC

AR3

AZ_SDOUT/TDM_FRM_PLAYBACK

AT2

SW_MCLK/TDM_BCLK_BT

AT4

SW_DATA0/TDM_DOUT_BT

AR6

AGPIO7/FCH_ACP_I2S_SDIN_BT

AP6

AGPIO8/FCH_ACP_I2S_LRCLK_BT

1 2

SW PU/PD

SW PU/PD

ACPI/AUDIO/I2C/GPI O/MISC

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

FP5 REV 0.90

PART 4 OF 13

FP5_BGA_1140P

EGPIO41/SFI_S5_EGPIO41

AGPIO39/SFI_S5_AGPIO39

I2C0_SCL/SFI0_I2C_SCL/EGPIO151

1.8V_S5

I2C0_SDA/SFI0_I2C_SDA/EGPIO152

I2C1_SCL/SFI1_I2C_SCL/EGPIO149

1.8V_S5

I2C1_SDA/SFI1_I2C_SDA/EGPIO150

I2C2_SCL/EGPIO113/SCL0

3.3V

I2C2_SDA/EGPIO114/SDA0

I2C3_SCL/AGPIO19/SCL1

3.3V_S5

I2C3_SDA/AGPIO20/SDA1

SATA_ACT_L/AGPIO130

3.3VALW input

SW PU/PD

3.3VS input

3.3VS input

3.3VS Output

3.3VS input

3.3VS input

3.3VS input

3.3VS input

GPIO Table

PSA_I2C_SCL

PSA_I2C_SDA

AGPIO4/SATAE_IFDET

AGPIO5/DEVSLP0

AGPIO6/DEVSLP1

INTRUDER_ALERT

SPKR/AGPIO91

BLINK/AGPIO11

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

FANIN0/AGPIO84

FANOUT0/AGPIO85

AGPIO40

AGPIO69

AGPIO86

AW12

AU12

I2C_0_SCL

AR13

I2C_0_SDA

AT13

I2C_1_SCL

AN8

I2C_1_SDA

AN9

SMB_0_SCL

BC20

SMB_0_SDA

BA20

I2C_3_SCL

AM9

I2C_3_SDA

AM10

L16

M16

AT15

AW10

AP9

AU10

AV15

AU7

AU6

AW13

AW15

AU14

AU16

AV8

AW16

BD15

AR18

AT18

AGPIO3

AGPIO4

AGPIO5

DEVSLP1

AGPIO9

AGPIO40

G_INT#_APU

APU_SPKR

AGPIO11

TP_I2C_INT#_APU

AGPIO3

AGPIO9

I2C_1_SCL <27>

I2C_1_SDA <27>

SMB_0_SCL < 13,14>

SMB_0_SDA <13,14>

I2C_3_SCL <30>

I2C_3_SDA <30>

DEVSLP1 < 27>

AGPIO40 <27>

G_INT#_APU <27>

APU_SPKR <28>

TP_I2C_INT#_APU <30>

G-SENSOR

DDR4

Touch Pad

I2C_0_SCL

I2C_0_SDA

SMB_0_SCL

SMB_0_SDA

I2C_3_SCL

I2C_3_SDA

AGPIO8

DEVSLP1

1 2

RC6139 2.2K_0402_5%@

1 2

RC6140 2.2K_0402_5%@

1 2

RC6157 2.2K_0402_5%

1 2

RC6156 2.2K_0402_5%

1 2

RC6159 2.2K_0402_5%

1 2

RC6158 2.2K_0402_5%

RC6167 10K_0402_5%@

RC663 10K_0402_5%@

AGPIO4 0

PCIE

H

RST

SSD

L

RC693

10K_0402_5%

AGPIO40

AGPIO9

AGPIO12

AGPIO23

RC692

10K_0402_5%

@

@

12

12

12

10K_0402_5%

12

10K_0402_5%

AGPIO9

DIS

UMA

DIS@

RC6147

UMA@

RC6148

+1.8VALW

+3VS

+3VALW

+3VS

AGPIO1 2 A GPIO23

RSV

RSV

12

@

RC6135

10K_0402_5%

12

RC6136

10K_0402_5%

12

10K_0402_5%

12

10K_0402_5%

RC6175

RC6174

RSV

RSV

@

@

+3VALW

12

12

AGPIO1 0 AG PIO11

AGPIO3 AGPIO 4AGPIO7A GPIO5

HDA

Strap Pin

H

L

APU_SPI_ CLK_R SYS_RST#

USE 48MHZ CRYSTAL

B

H

CLOCK

(Default)

USE 100MHZ PCIE

L

CLOCK AS

REFERENCE CLOCK

APU_SPI_CLK_R< 10>

1 2

HDA_RST#_R< 28>

HDA_BIT_CLK_R< 28>

HDA_SYNC_R<28>

HDA_SDOUT_R<28>

4 4

RC116 33_0402_5%E MC@

1 2

RC117 33_0402_5%E MC@

1 2

RC118 33_0402_5%E MC@

1 2

RC119 33_0402_5%E MC@

1 2

RC120 1K_0402_5%

1 2

RC121 1K_0402_5%

1 2

RC122 1K_0402_5%

1 2

RC123 1K_0402_5%

1 2

RC695 10K_0402_5%@

1 2

RC696 10K_0402_5%@

1 2

RC703 10K_0402_5%@

A

HDA_RST#

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

HDA_SDIN1

HDA_SDIN2

HDA_SDIN0

NORMAL RESET MODE

(Default)

SHORT RESET MODE

+1.8VS +1.8VALW +3VALW

12

RC622

10K_0402_5%

10K_0402_5% @

APU_SPI_CLK_R

SYS_RST#

RC1703

2K_0402_5% @

+3VALW

12

12

@

@

RC6172

10K_0402_5%

12

12

@

@

RC6173

10K_0402_5%

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

EH5LP/AP_LA-H801P

E

9 48Friday, March 29, 2019

9 48Friday, March 29, 2019

9 48Friday, March 29, 2019

@

12

10K_0402_5%

12

10K_0402_5%

RC6168

RC6169

+3VALW+3VALW

12

@

12

@

RC619

10K_0402_5%

AGPIO10

AGPIO11

RC6134

10K_0402_5%

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FP5_(4/7)_GPIO/HDA/STRAP

FP5_(4/7)_GPIO/HDA/STRAP

FP5_(4/7)_GPIO/HDA/STRAP

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

12

12

@

@

RC6137

RC6145

10K_0402_5%

10K_0402_5%

12

12

RC951

RC47

10K_0402_5%

12

12

RC929

2K_0402_5% @

C

AGPIO5

12

12

@

@

RC6138

RC6146

10K_0402_5%

10K_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION.THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION.THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION.THIS SHEET MAYNOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAYBE USED BY OR DISCLOSEDTO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSEDTO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAYBE USED BY OR DISCLOSEDTO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2020/03/29 2020/03/29

2020/03/29 2020/03/29

2020/03/29 2020/03/29

DVT no seperate PCB

10K_0402_5%

AGPIO3

AGPIO4AGPIO7

10K_0402_5%

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

RC6170

RC6171

1.A

1.A

1.A

Page 10

DeviceDB VIP + XinZhiZao 1 Year: www.devicedb.xyz/dev/subscriptions/

A

B

C

D

E

Main Func = CPU

RC602

UC1E CPU@

T115 TP@

CLKREQ_PCIE#0

CLKREQ_PEG#1

CLKREQ_PCIE#2

CLKREQ_PCIE#4

CLK_PCIE_P0

CLK_PCIE_N0

CLK_PEG_P1

CLK_PEG_N1

CLK_PCIE_P2

CLK_PCIE_N2

CLK_PCIE_P4

CLK_PCIE_N4

48M_X1

48M_X2

RTCCLK

32K_X1

32K_X2

AV18

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AN19

CLK_REQ1_L/AGPIO115

AP19

CLK_REQ2_L/AGPIO116

AT19

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AU19

CLK_REQ4_L/OSCIN/EGPIO132

AW18

CLK_REQ5_L/EGPIO120

AW19

CLK_REQ6_L/EGPIO121

AK1

GPP_CLK0P

AK3

GPP_CLK0N

AM2

GPP_CLK1P

AM4

GPP_CLK1N

AM1

GPP_CLK2P

AM3

GPP_CLK2N

AL2

GPP_CLK3P

AL4

GPP_CLK3N

AN2

GPP_CLK4P

AN4

GPP_CLK4N

AN3

GPP_CLK5P

AP2

GPP_CLK5N

AJ2

GPP_CLK6P

AJ4

GPP_CLK6N

AJ3

48M_OSC

BB3

X48M_X1

BA5

X48M_X2

AF8

RSVD_76

AF9

RSVD_77

AW14

RTCCLK

AY1

X32K_X1

AY4

X32K_X2

+3VS

1 2

RC1695 10K_0402_5%

1 2

RC6149 10K_0402_5%

1 2

1 1

RC1696 10K_0402_5%

1 2

RC1697 10K_0402_5%

CLKREQ_PCIE#0

CLKREQ_PCIE#2

CLKREQ_PCIE#4

CLKREQ_PEG#1

48MHz CRYSTAL

48M_X2

1

1

YC2

48MHZ_8PF_X3S048000D81H-W

SJ10000AF00

4

4

1

C797

3.9P_0402_50V8C

2

12

YC3

CC682

18P_0402_50V8J

48M_X1

32K_X1

32K_X2

1 2

RC939

1M_0402_5%

2

2

3

3

1

C796

3.9P_0402_50V8C

2

2 2

32.768KHz CRYSTAL

SJ100001K00

32.768KHZ_12.5PF_CM31532768DZFT

12

RC914

20M_0402_5%

1

CC686

18P_0402_50V8J

2

1

2

SSD

DGP U

LAN

WLAN

SSD

DGP U

LAN

WLAN

CLKREQ_PCIE#0<27>

CLKREQ_PEG#1<16>

CLKREQ_PCIE#2<25>

CLKREQ_PCIE#4<26>

CLK_PCIE_P0<27>

CLK_PCIE_N0<27>

CLK_PEG_P1<15>

CLK_PEG_N1<15>

CLK_PCIE_P2<25>

CLK_PCIE_N2<25>

CLK_PCIE_P4<26>

CLK_PCIE_N4<26>

CLK/LPC/EMMC/SD/SPI/eSPI/ UART

SW PU/PD

M.2 WLAN/BT

GBE LAN

M.2 WWAN

M.2 WLAN

PCIE X4 DT SLOT

M.2 PCIE SSD

EVAL GFX SLOT

FP5 REV 0.90

PART 5 OF 13

FP5_BGA_1140P

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

EGPIO70/SD_CLK

LPC_PD_L/SD_CMD/AGPIO21

LAD0/SD_DATA0/EGPIO104

LAD1/SD_DATA1/EGPIO105

LAD2/SD_DATA2/EGPIO106

LAD3/SD_DATA3/EGPIO107

LPCCLK0/EGPIO74

LPC_CLKRUN_L/AGPIO88

LPCCLK1/EGPIO75

SERIRQ/AGPIO87

LFRAME_L/EGPIO109

LPC_RST_L/SD_WP_L/AGPIO32

AGPIO68/SD_CD

LPC_PME_L/SD_PWR_CTRL/AGPIO22

SPI_ROM_REQ/EGPIO67

SPI_ROM_GNT/AGPIO76

ESPI_RESET_L/KBRST_L/AGPIO129

ESPI_ALERT_L/LDRQ0_L/EGPIO108

SPI_CLK/ESPI_CLK

SPI_DI/ESPI_DATA

SPI_WP_L/ESPI_DAT2

SPI_HOLD_L/ESPI_DAT3

SPI_CS1_L/EGPIO118

SPI_CS2_L/ESPI_CS_L/AGPIO30

SPI_CS3_L/AGPIO31

SPI_TPM_CS_L/AGPIO29

UART0_RXD/EGPIO136

UART0_TXD/EGPIO138

UART0_RTS_L/UART2_RXD/EGPIO137

UART0_CTS_L/UART2_TXD/EGPIO135

UART0_INTR/AGPIO139

EGPIO141/UART1_RXD

EGPIO143/UART1_TXD

EGPIO142/UART1_RTS_L/UART3_RXD

EGPIO140/UART1_CTS_L/UART3_TXD

AGPIO144/UART1_INTR

SPI_DO

BD13

BB14

BB12

BC11

BB15

BC15

BA15

BC13

BB13

BC12

BA12

BD11

BA11

BA13

BC8

BB8

BB11

BC6

BB7

BA9

BB10

BA10

BC10

BC9

BA8

BA6

BD8

BA16

BB18

BC17

BA18

BD18

BC18

BA17

BC16

BB19

BB16

LPCPD#

LPC_AD0

RC101 0_0402_5%

LPC_AD1

RC102 0_0402_5%

LPC_AD2

RC103 0_0402_5%

LPC_AD3

RC104 0_0402_5%

LPC_CLK0

RC449 22_0402_5%

LPC_CLK1

SERIRQ

LPC_FRAME#

LPC_RST_A#

EC_SCI#

KBRST#

EGPIO108

APU_SPI_CLK

APU_SPI_MISO

APU_SPI_MOSI

APU_SPI_WP#

APU_SPI_HOLD#

APU_SPI_CS#1

UART_0_ARXD_DTXD

UART_0_ATXD_DRXD

PE_GPIO1

DGPU_PWRGOOD

PE_GPIO0

T103TP@

12

12

12

12

1 2

SERIRQ <29>

LPC_FRAME# <29>

EC_SCI# <29>

KBRST# <29>

RC74 10_0402_5%

1 2

EMC@

UART_0_ARXD_DTXD <26>

UART_0_ATXD_DRXD <26>

PE_GPIO1 <33>

DGPU_PWRGOOD <1 5,43,45>

PE_GPIO0 <15>

RC449 close to UC1

APU_SPI_CLK_R <9>

LPC_AD0_R <29>

LPC_AD1_R <29>

LPC_AD2_R <29>

LPC_AD3_R <29>

LPC_CLK0_EC <29>

8MB SPI ROM

APU_SPI_CS#1

APU_SPI_MISO

APU_SPI_WP#

USB Function

+1.8VALW

1 2

3 3

RC94 4.7K_0402_5%

1 2

RC95 4.7K_0402_5%

+3VALW

1 2

RC905 100K_0402_5%@

1 2

RC906 100K_0402_5%@

4 4

APU_USBC_SCL

APU_USBC_SDA

USB_OC0#

USB_OC1#

CAMERA

Type-A MB USB3.0

Type-A SUB USB2.0

WLAN/B T

Type-A MB USB2.0

USB Hub/FP

USB20_P0<23>

USB20_N0<23>

USB20_P1<32>

USB20_N1<32>

USB20_P2<32>

USB20_N2<32>

USB20_P3<26>

USB20_N3<26>

USB20_P4<32>

USB20_N4<32>

USB20_P5<32>

USB20_N5<32>

USB_OC0#<32>

USB_OC1#<32>

USB20_P0

USB20_N0

USB20_P1

USB20_N1

USB20_P2

USB20_N2

USB20_P3

USB20_N3

USB20_P4

USB20_N4

USB20_P5

USB20_N5

APU_USBC_SCL

APU_USBC_SDA

USB_OC0#

USB_OC1#

AG10

AF12

AF11

AE10

AK10

AT12

AE7

AE6

AG9

AE9

AJ12