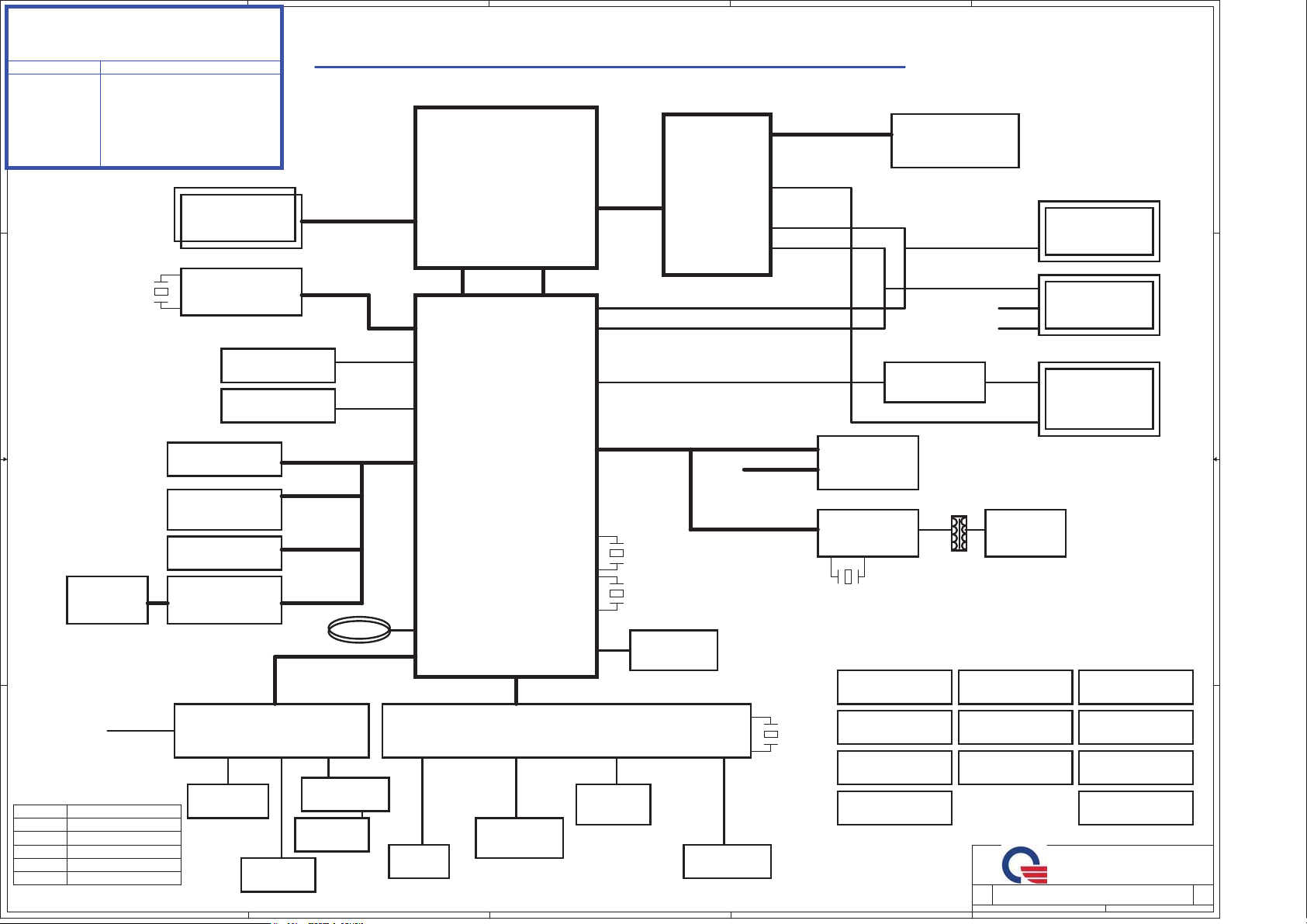

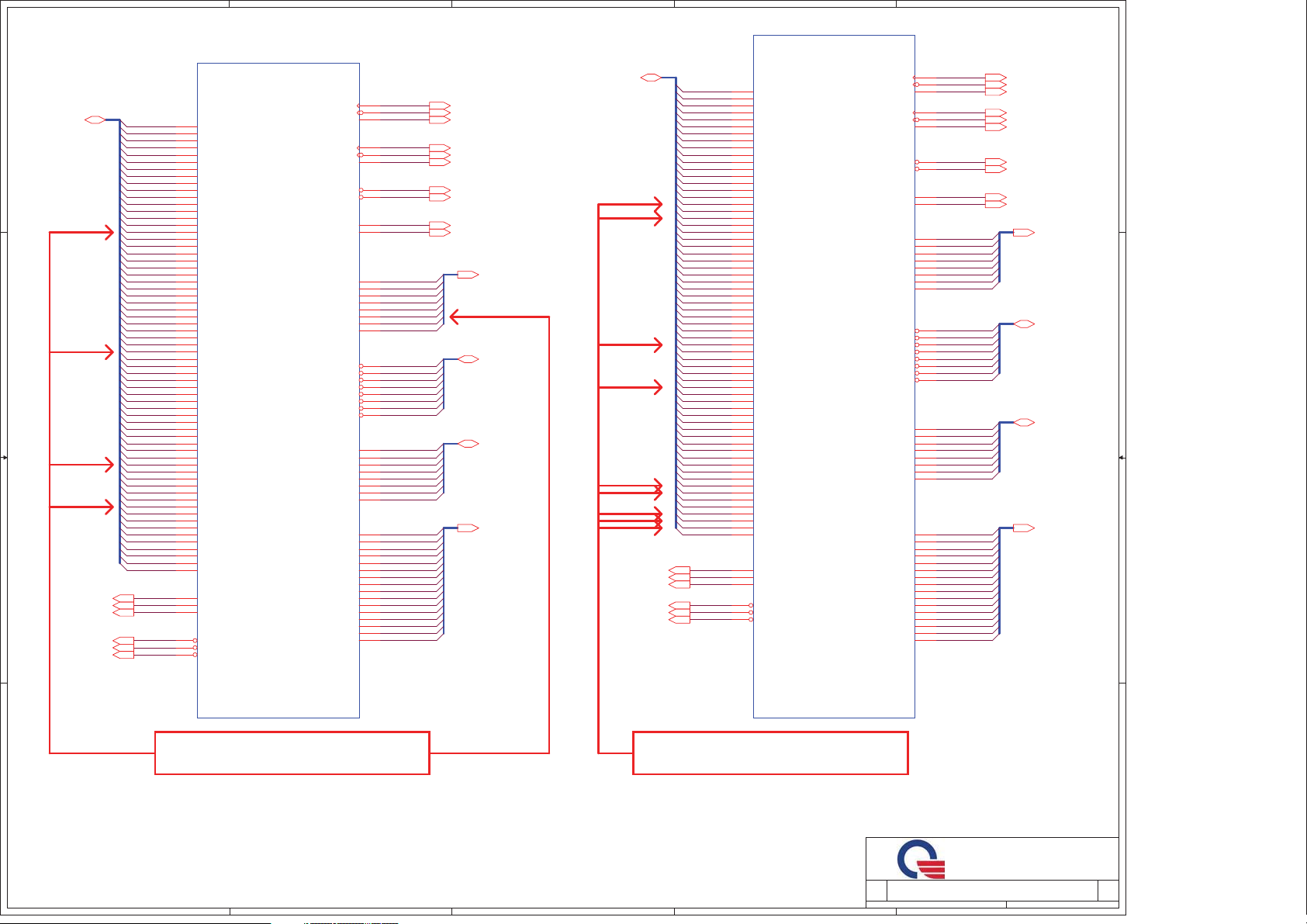

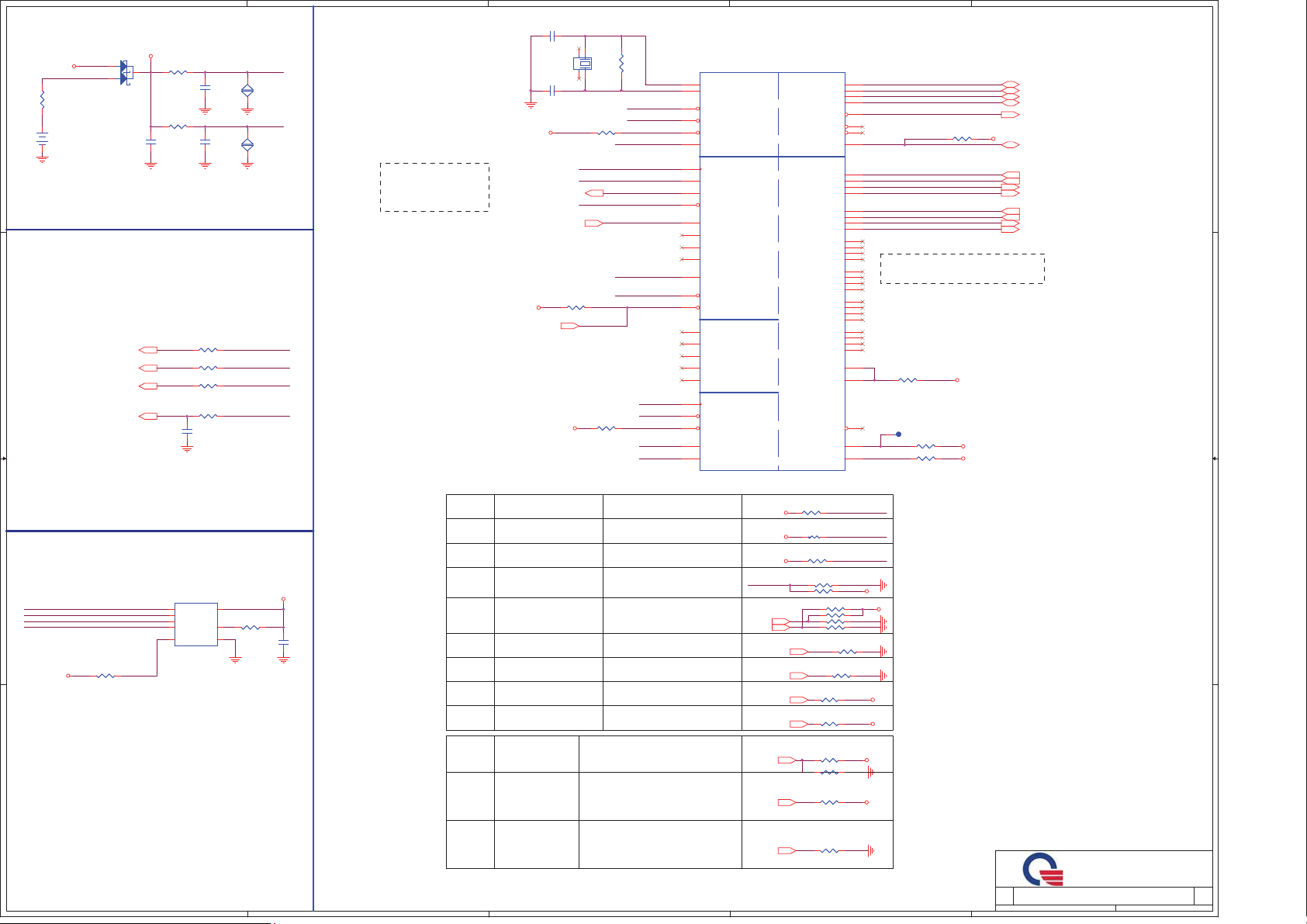

Acer Aspire 4339, Aspire 4739, Aspire 4739z Schematics

VER : 1A

5

4

3

2

1

BOM P/N

D D

Description

DDRIII-SODIMM1

DDRIII-SODIMM2

X'TAL

14.318MHz

SLG8LV595

CLOCK

GENERATOR

C C

P14,15

P3

SATA - HDD

SATA - ODD

USB Port

USB/B Con.

(USB Port x2)

Bluetooth Con.

B B

Cardreader

P31

AU6437-GBL

Cardreader control

P33

P33

P33

P31

=4+6<67(0%/2&.',$*5$0

Dual Channel DDR III

800/1066 MHZ

SATA 0

P28

P9

SATA 1

BATTERY

P28

USB-1

USB-3/9/11

USB-4

USB-12

Azalia

FDI

FDI

CLK

SATA

Ibex Peak-M

USB

PCH

P8, 9, 10, 11, 12, 13

RTC

IHDA

Arrandale

rPGA 989

P4, 5, 6, 7

LPC

LPC

DMI

DMI

PCI-E x16

GFXIMC

DMI(x4)

INT_CRT

INT_LVDS

Display

INT_HDMI

PCI-E x1

SPI

X'TAL

32.768KHz

X'TAL 25MHz

SPI ROM

ATI-Park

VRAM DDRIII

512MB

P16, 17, 18, 21, 22, 23

P9

PCIE-6

USB-13

PCIE-1

Channel B

EXT_HDMI

EXT_CRT

EXT_LVDS

MINI CARD

WLAN

BRM 57780

GIGA LAN

PS8101

LS

P27

P26

X'TAL

25MHz

ISL88731A

Batery Charger

64Mb * 16 *4 pc

P22

P24

EXT_HDMI

RJ45

UP6111AQDD

+1.05V

P36

USB-8

Int. MIC

CRT Con.

LVDS/CCD/MIC

Con.

HDMI Con.

P26

P39

P23

P23

P24

ISL62881HRZ-T

+VGFX_AXG

P41

Int. MIC

BOM Option Table

A A

Reference

IV@

EV@

VRAM@

* do not stuff

Description

for UMA only SKU

for Discrete Graphic only SKU

for different VRAM parts

5

ALC272X

AUDIO CODEC

MIC JACK

P30

HP

P30

GMT 1453L amp

P29

Speaker

P30

P30

4

K/B Con.

P34

NPCE781

EC

W25X40BVSSIG

SPI FLASH

P35

P37

Touch Pad

Board Con.

3

P34

Fan Driver

(PWM Type)

P34

X'TAL

32.768KHz

RT8206B

3V/5V

ADP3212

CPU core

RT9018A

+1V

2

RT8207A

+1.5V_SUS

P37

MAX8792ETD+T

+VGPU_CORE

P38

P44

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

HPA00835RTER

+1.8V

P40

Discharger

P42

Thermal Protection

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Block Diagram

Block Diagram

Block Diagram

1

ZQH

ZQH

ZQH

P43

P43

P44

1A

1A

1A

of

135Monday, March 14, 2011

of

135Monday, March 14, 2011

of

135Monday, March 14, 2011

1

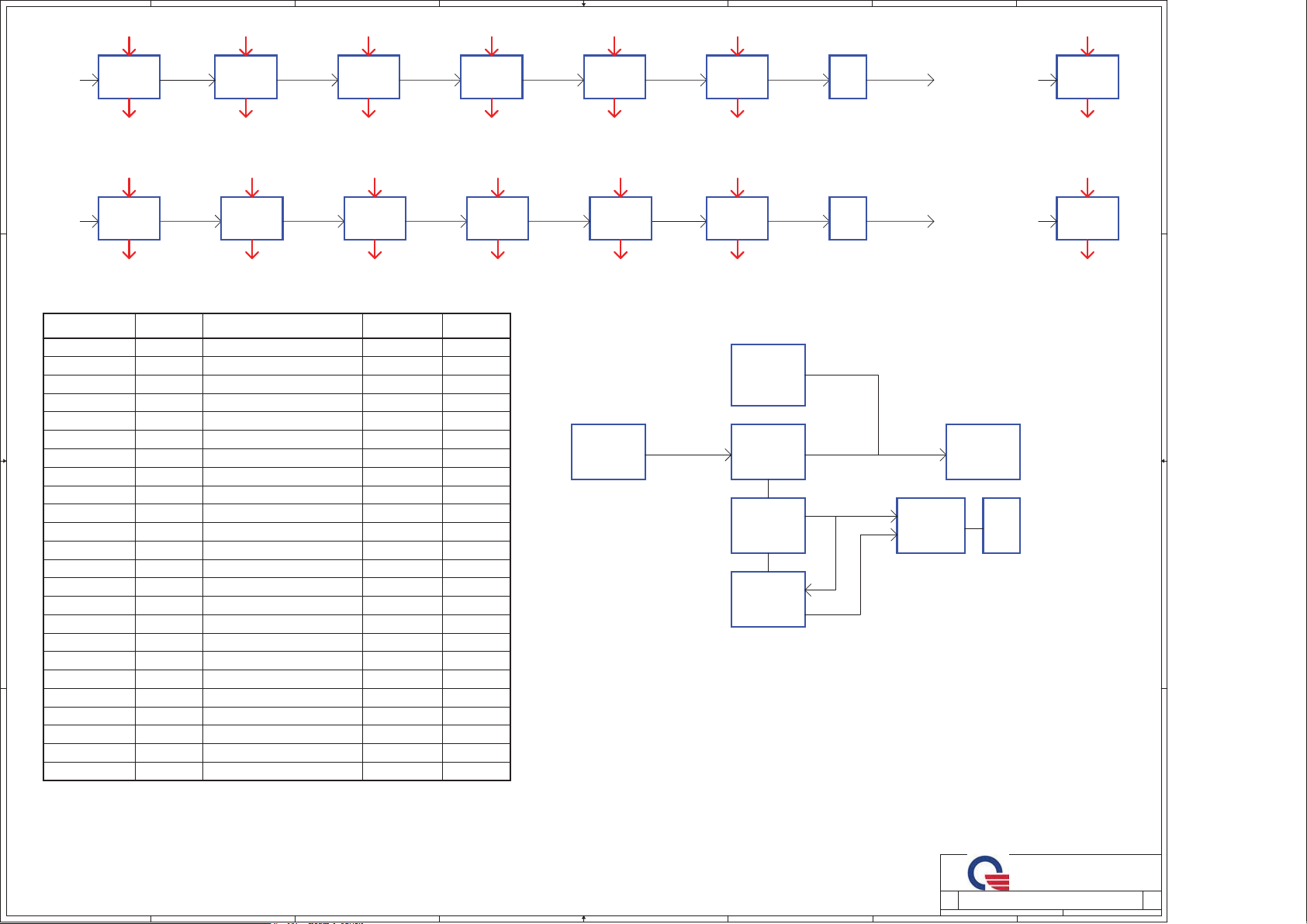

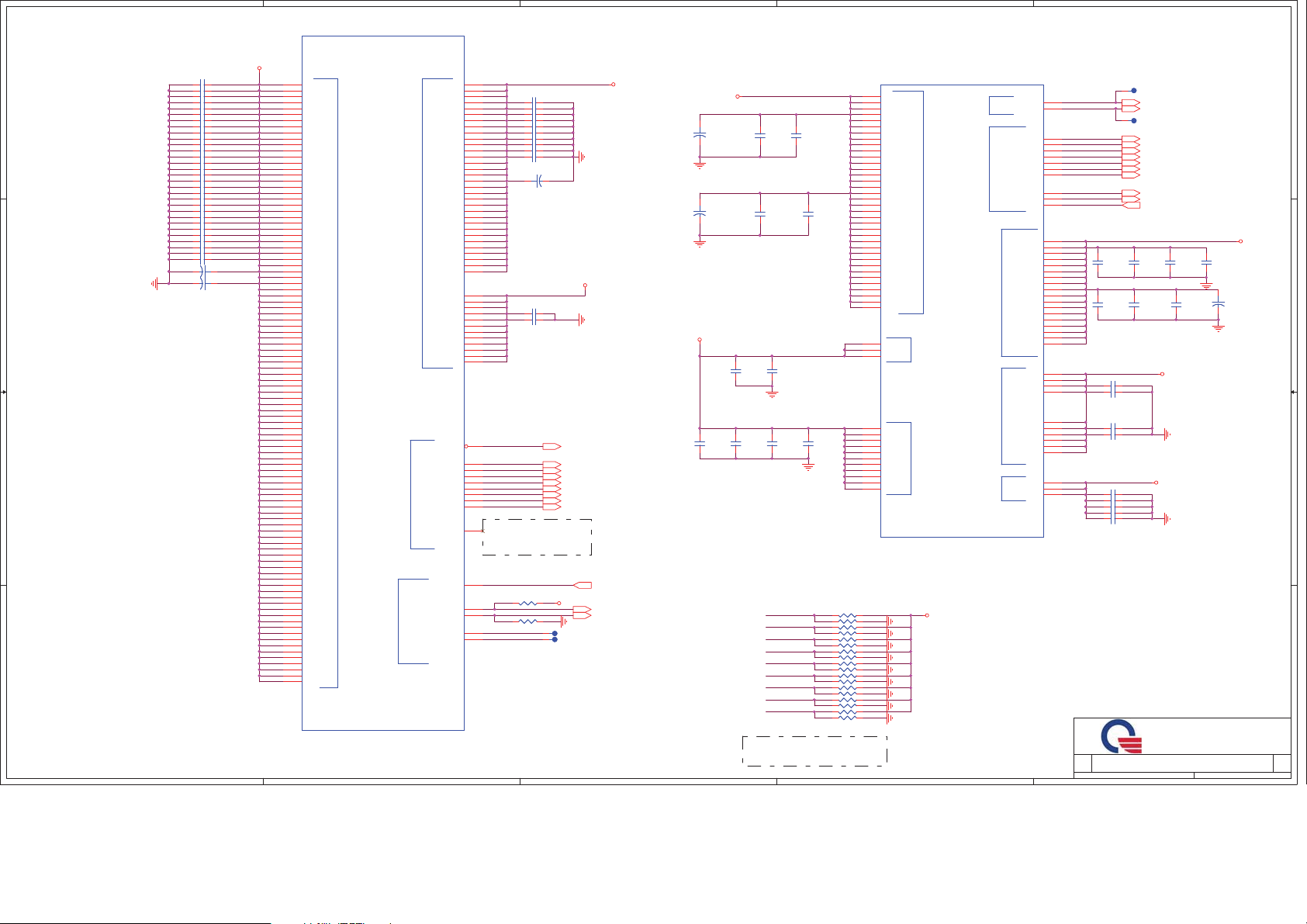

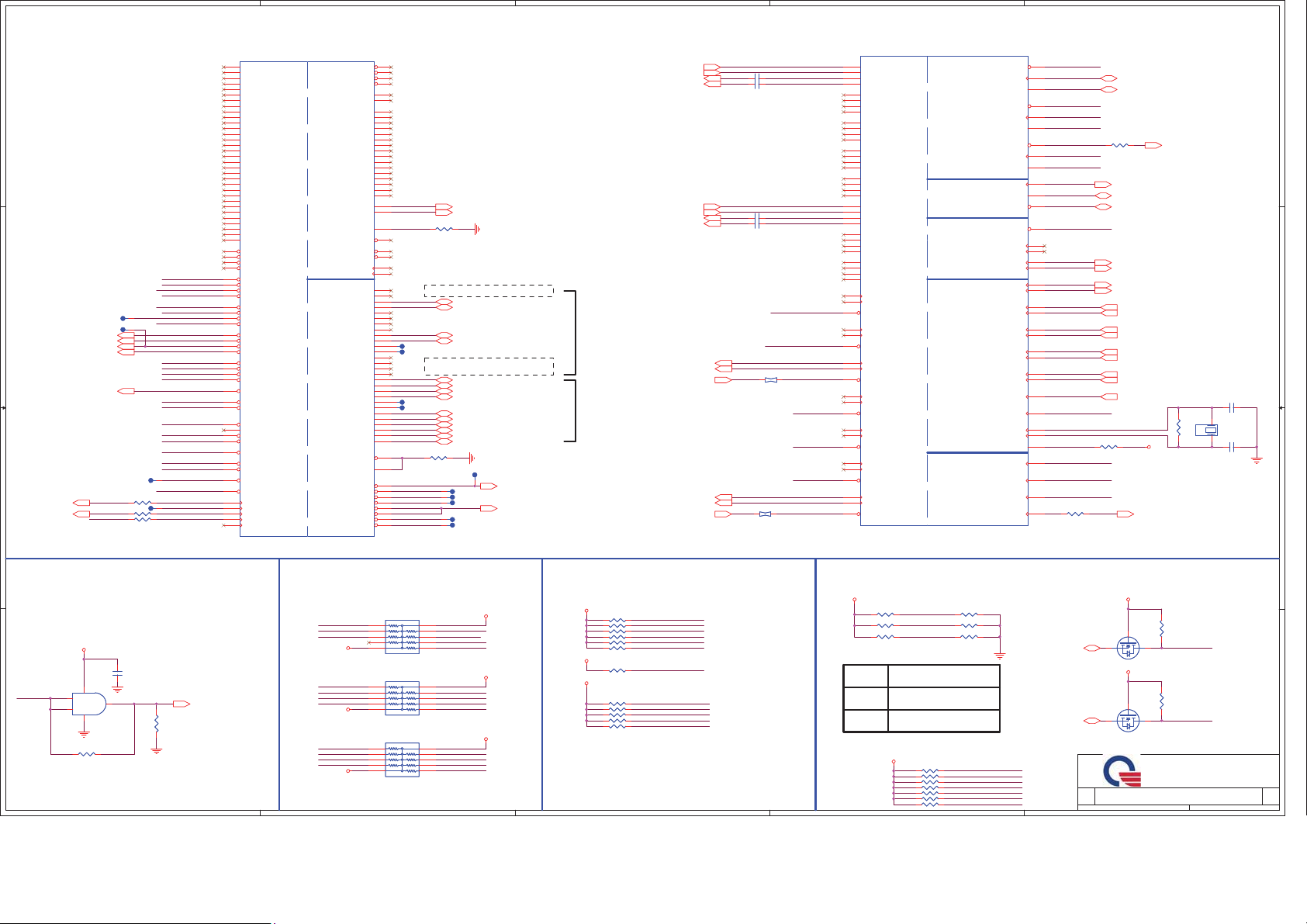

GPU PWR CTRL Option 1 (Default/ VDDR3 before VDDC)

+3.3V

2

VIN

VIN

3

+1.5V

4

+1.5V_SUS

5

+1.8V

6

7

8

+5V

dGPU_VRON

A A

VDDR3

MOS (AO3413)

+3_D (0.5A)

+3V_D

P22

VDDC

ISL6264

+VGPU_CORE (20A)

P44

PG_GPUIO_EN

VDDCI

ISL62872

P45

+VGPU_IO (4.5A)

PG_1V_EN

(DP PLL PWR)

+1V

G9334ADJ & MOS

+1V (3A)

P47

PG_1.5V_EN

VDDR1

MOS (AO4710)

P43

+1.5V_GPU (10A)

PG_1.5V_EN

VDDR4

MOS (AO6402)

P43

+1.8V_GPU (3A)

PG_1.5V_EN

BJT

P22

dGPU_PWROK

dGPU_PWR_EN#

MOS

AO3413

+5_GPU

P22

GPU PWR CTRL Option 2 (VDDR3 after VDDR1)

VIN

VDDCI

ISL62872

P45

+VGPU_IO (4.5A)

PG_1V_EN

dGPU_VRON

VIN

VDDC

ISL6264

P44

+VGPU_CORE (20A)

Power States

POWER PLANE

B B

C C

VIN

+VCCRTC

+3VPCU

+5VPCU

+15V

+3V_S5

+5V_S5

+5V

+1.5VSUS

+0.75V_DDR_VTT

+VGFX_AXG S0GFX_ONInternal GPU POWER

+1.8V

+1.5V

+1.1V_VTT S0

+1.05V

+VCC_CORE

LCDVCC

+5V_GPU

+GPU_CORE

+GPU_IO PG_GPUIO_EN+0.9V~+1.1V

VOLTAGE

+10V~+19V

+3V~+3.3V

+3.3V

+5V

+15V

+3.3V

+5V

+5V

+3.3V

+1.5V

+0.75V

variation

+1.8V

+1.5V

+1.05V or +1.1V

+1.05V

variation

+3.3V

+5V Discrete enableSWITCHABLE PWM IC POWER

DESCRIPTION

RTC POWER

EC POWER

CHARGE POWER

CHARGE PUMP POWER

LAN/BT/CIR POWER

USB POWER

HDD/ODD/Codec/TP/CRT/HDMI POWER

PCH/GPU/Peripheral component POWER+3V

CPU/SODIMM CORE POWER

SODIMM Termination POWER

CPU/PCH/Braidwood POWER

MINI CARD/NEW CARD POWER

PCH CORE POWER MAINON

CPU CORE POWER

LCD POWER

+1.5V

(DP PLL PWR)

+1V

G9334ADJ & MOS

+1V (3A)

CONTROL

SIGNAL

ALWAYSMAIN POWER

ALWAYS

ALWAYS

ALWAYS

S5_ON

S5_ON

MAINON

MAINON

SUSON

MAINON

MAINON

MAINON

MAINONCPU VTT POWER

VRON

LVDS_VDDEN

dGPU_PWR_EN#

PG_1.5V_EN+1.5V+1.5V_GPU

+1.5V_GPU+1.8V+1.8V_GPU

PG_1V_EN+1V+1V Discrete enableDP/PEG POWER

P47

PG_1.5V_EN

+1.5V_SUS

VDDR1

MOS (AO4710)

+1.5V_GPU (10A)

ACTIVE IN

ALWAYS

ALWAYS

ALWAYS

ALWAYS

ALWAYSALWAYS

S0-S5

S0-S5

S0

S0

S0-S3

S0

S0

S0

S0

S0

S0

Discrete enable+3V_DGPU CORE POWER+0.9V~+1.1V

Discrete enableGPU I/O POWER

Discrete enableVRAM CORE POWER

Discrete enableGPU_CRE/LVDS/PLL POWER

+1.5V_GPU

P43

Thermal Follow Chart

CPU

CORE PWR

+3.3V

VDDR3

MOS (AO3413)

P22

+3_D (0.5A)

+3V_DPG_GPUIO_EN

H_ORICHOT#

H/W Throttling

+1.8V

VDDR4

MOS (AO6402)

P43

+1.8V_GPU (3A)

NTC

Thermal

Protection

CPU

PCH

SM-Bus

EC

PG_1.5V_EN

BJT

P22

PM_THRMTRIP#

SML1ALERT#

CPUFAN#

dGPU_PWROK

SYS_SHDN#

WIRE-AND

dGPU_PWR_EN#

3V/5 V

SYS PWR

FANFAN Driver

+5V

MOS

AO3413

+5_GPU

P22

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

PWR Status & GPU PW R CRL & T HRM

PWR Status & GPU PW R CRL & T HRM

PWR Status & GPU PW R CRL & T HRM

Date: Sheet

Date: Sheet

1

2

3

4

5

6

Date: Sheet

7

PROJECT :

ZQH

ZQH

ZQH

1A

1A

1A

of

of

of

245Monday, March 14, 2011

245Monday, March 14, 2011

245Monday, March 14, 2011

8

5

4

3

2

1

D D

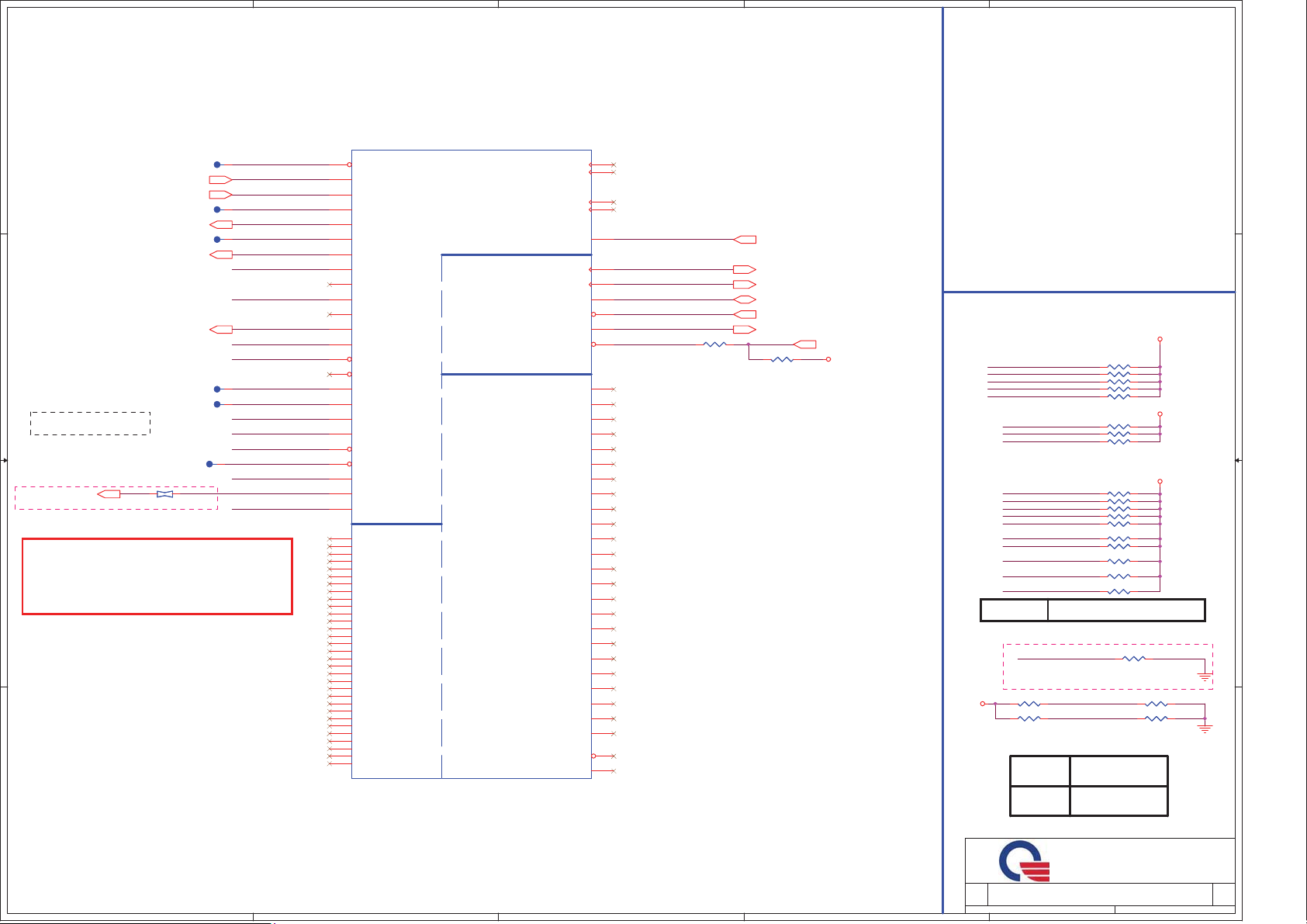

L50 *PBY160808T-181Y-N/2A/180ohm_6L50 *PBY160808T-181Y-N/2A/180ohm_6

+1.5V

+1.05V

C267

C267

.1u/16V_4

.1u/16V_4

R451

R451

*10K_4

*10K_4

R446

R446

10K_4

10K_4

20mil

CPU_SEL

L23 BLM18AG601SN1D/200mA/600ohm_6L23 BLM18AG601SN1D/200mA/600ohm_6

+3V

C238

C238

4.7u/10V_8

4.7u/10V_8

C C

B B

150mA(30mil)

C243

C243

.1u/16V_4

.1u/16V_4

C251

C251

.1u/16V_4

.1u/16V_4

CLK_ICH_14M<10>

C627

C627

.1u/16V_4

.1u/16V_4

+3V_CLK

+1.5V_CLK

C246

C246

.1u/16V_4

.1u/16V_4

C614 33p/50V_4C614 33p/50V_4

C612 33p/50V_4C612 33p/50V_4

0_6

0_6

R455 33_4R455 33_4

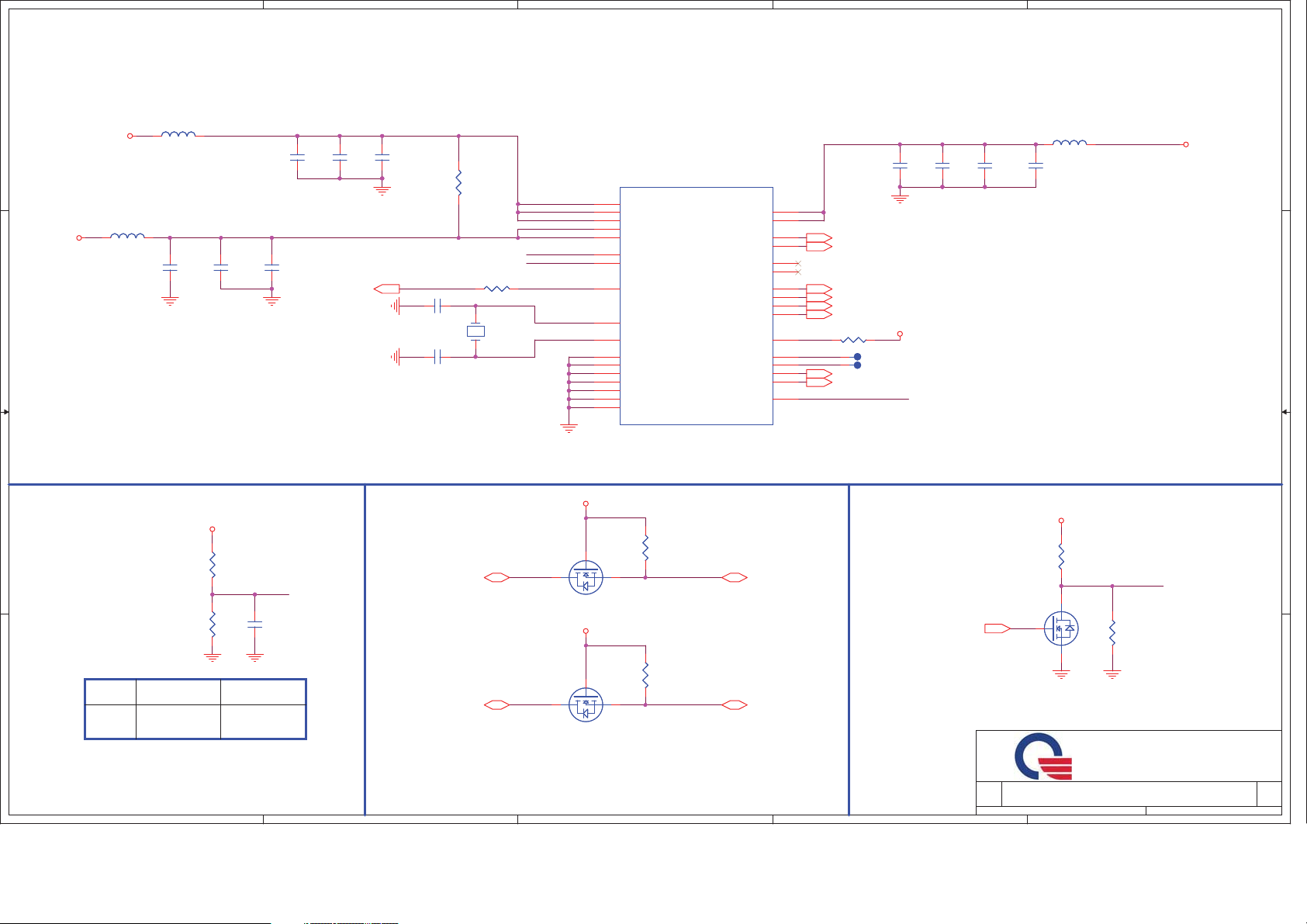

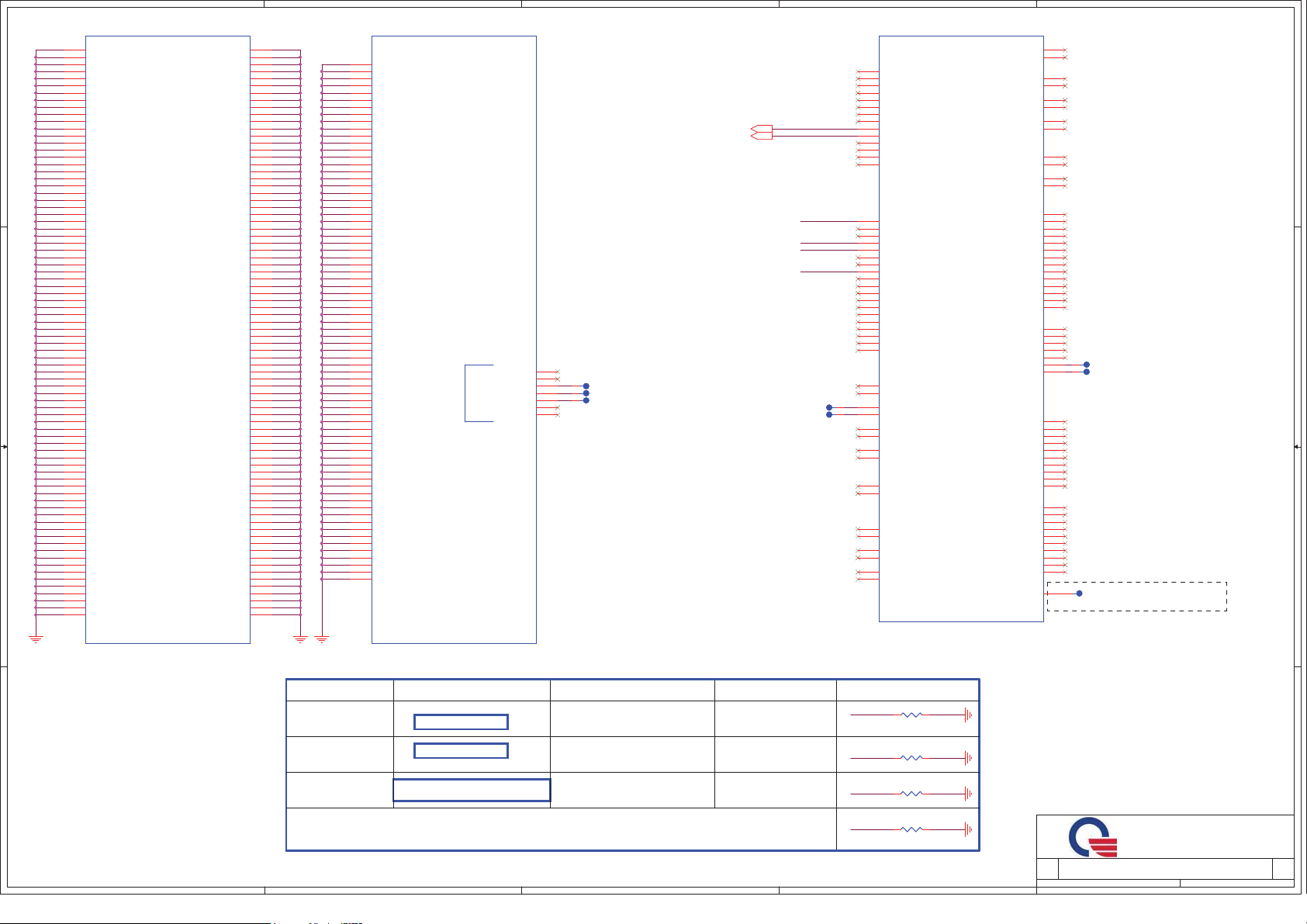

IDT: AL003197001 (ICS9LVS3197AKLFT)

Realtek: AL000890000 (RTM890N-632-GRT)

Silego: AL000595000 (SLG8LV595VTR)

SMBusCPU_CLK select

ICH_SMBDATA<10>

C617

C617

*10p/50V/COG_4

*10p/50V/COG_4

R565

R565

Y6

Y6

14.318MHz

14.318MHz

CLK_SDATA

CLK_SCLK

CPU_SEL

XTAL_IN

XTAL_OUT

3

+3V

2

+3V

U20

U20

1

VDD_DOT

17

VDD_SRC

24

VDD_CPU

5

VDD_27

29

VDD_REF

31

SDA

32

SCL

30

REF_0/CPU_SEL

28

XTAL_IN

27

XTAL_OUT

2

VSS_DOT

8

VSS_27

9

VSS_SATA

12

VSS_SRC

21

VSS_CPU

26

VSS_REF

33

GND

ICS9LRS3197AKLFT

ICS9LRS3197AKLFT

1

Q18

Q18

2N7002K

2N7002K

R543

R543

2.2K_4

2.2K_4

CLK_SDATA

VDD_SRC_I/O

VDD_CPU_I/O

DOT_96

DOT_96#

27M

27M_SS

SRC_1/SATA

SRC_1#/SATA#

SRC_2

SRC_2#

*CPU_STOP#

CPU_1

CPU_1#

CPU_0

CPU_0#

CKPWRGD/PD#

CLK_SDATA <14,15,19>

15

18

3

4

6

7

10

11

13

14

16

20

19

23

22

25

+VDDIO_CLK

CLK_BUF_DREFCLK <10>

CLK_BUF_DREFCLK# <10>

CLK_BUF_DREFSSCLK <10>

CLK_BUF_DREFSSCLK# <10>

CLK_BUF_PCIE_3GPLL <10>

CLK_BUF_PCIE_3GPLL# <10>

R130 10K_4R130 10K_4

TP23TP23

TP24TP24

CLK_BUF_BCLK <10>

CLK_BUF_BCLK# <10>

CK_PWRGD_R

CLK Enable

80mA(20mil)

C244

C244

C613

C613

.1u/16V_4

.1u/16V_4

.1u/16V_4

.1u/16V_4

Place each 0.1uF cap as close as

possible to each VDD IO pin. Place

the 10uF caps on the VDD_IO plane.

+3V

VR_PWRGD_CK505#<30>

L48 PBY160808T/2A/180ohm_6L48 PBY160808T/2A/180ohm_6

C607

C607

10u/Y5V_8

10u/Y5V_8

2

C609

C609

10u/Y5V_8

10u/Y5V_8

+3V

3

Q19

Q19

2N7002K

2N7002K

R545

R545

1K/F_4

1K/F_4

CK_PWRGD_R

R544

R544

100K/F_4

100K/F_4

+1.05V

R542

01

A A

CPU_SEL

CPU0/1=133MHz

(default)

5

CPU0/1=100MHz

ICH_SMBCLK<10>

4

2

3

Q17

Q17

2N7002K

2N7002K

R542

2.2K_4

2.2K_4

CLK_SCLK

1

3

CLK_SCLK <14,15,19>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Generator

Clock Generator

Clock Generator

Date: Sheet

Date: Sheet

2

Date: Sheet

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZQH

ZQH

ZQH

345Monday, March 14, 2011

345Monday, March 14, 2011

345Monday, March 14, 2011

1

1A

1A

1A

of

of

of

5

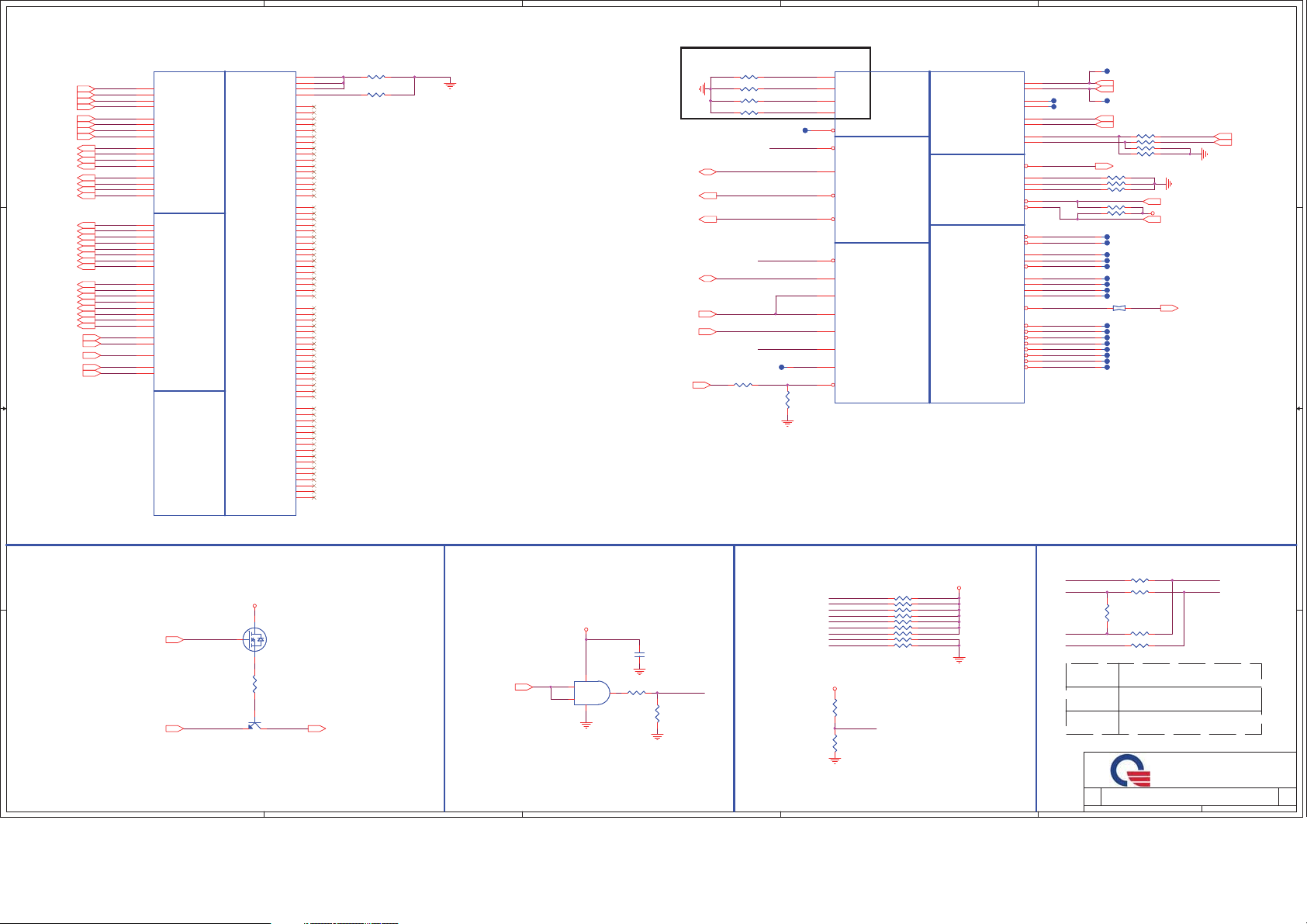

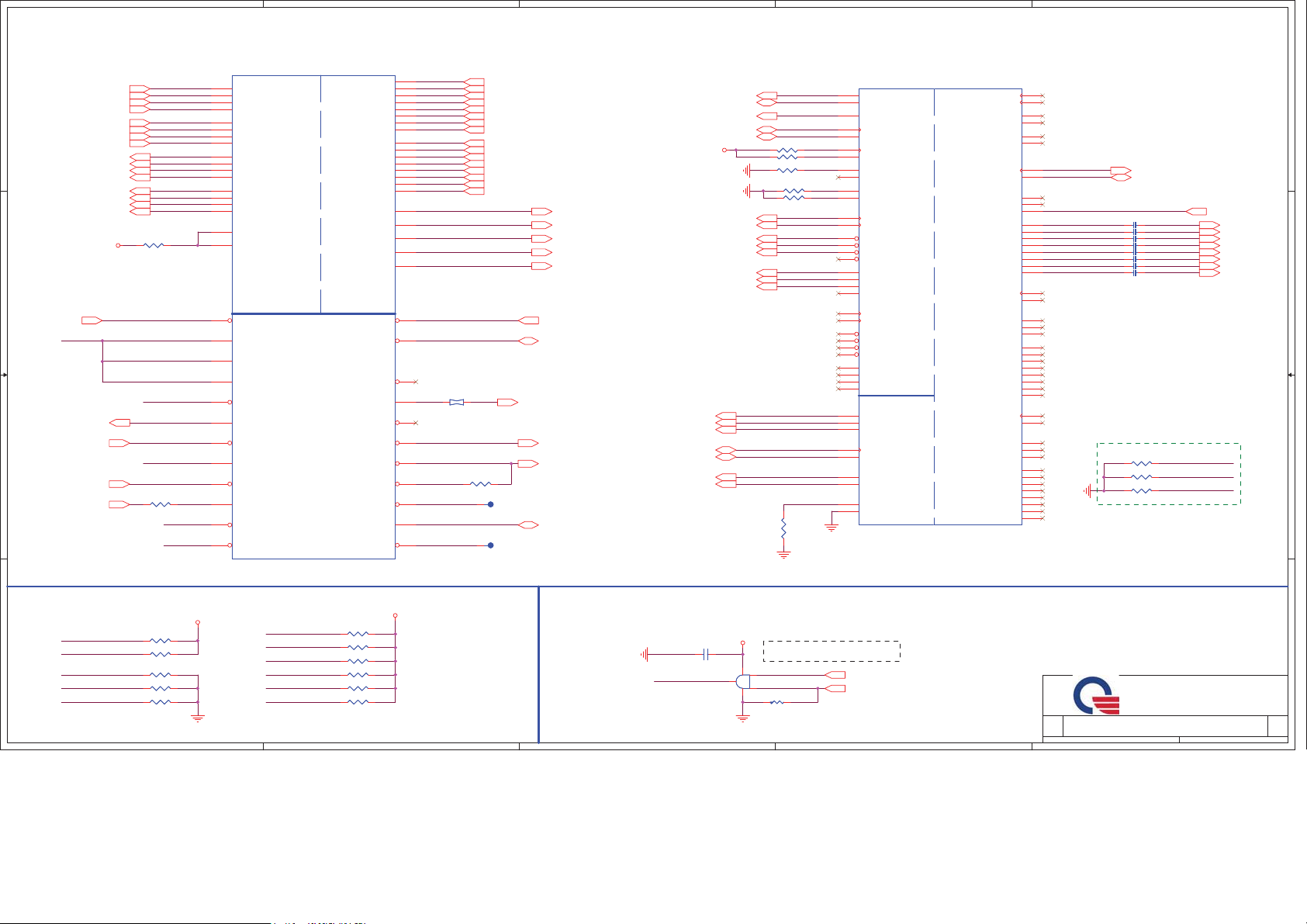

AUBURNDALE/CLARKSFIELD PROCESSOR (DMI,PEG,FDI)

U22A

U22A

DMI_TXN0<8>

DMI_TXN1<8>

DMI_TXN2<8>

DMI_TXN3<8>

D D

DMI_TXP0<8>

DMI_TXP1<8>

DMI_TXP2<8>

DMI_TXP3<8>

DMI_RXN0<8>

DMI_RXN1<8>

DMI_RXN2<8>

DMI_RXN3<8>

DMI_RXP0<8>

DMI_RXP1<8>

DMI_RXP2<8>

DMI_RXP3<8>

FDI_TXN0<8>

FDI_TXN1<8>

FDI_TXN2<8>

FDI_TXN3<8>

FDI_TXN4<8>

FDI_TXN5<8>

FDI_TXN6<8>

FDI_TXN7<8>

FDI_TXP0<8>

FDI_TXP1<8>

FDI_TXP2<8>

FDI_TXP3<8>

FDI_TXP4<8>

C C

FDI_TXP5<8>

FDI_TXP6<8>

FDI_TXP7<8>

FDI_FSYNC0<8>

FDI_FSYNC1<8>

FDI_INT<8>

FDI_LSYNC0<8>

FDI_LSYNC1<8>

B B

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

Clarksfield/Auburndale

Clarksfield/Auburndale

DMI Intel(R) FDI

DMI Intel(R) FDI

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

4

R436 49.9/F_4R436 49.9/F_4

R437 750/F_4R437 750/F_4

3

Processor Compensation Signals

R444 20/F_4R444 20/F_4

R442 20/F_4R442 20/F_4

R173 49.9 /F_ 4R173 4 9 .9 /F_ 4

R440 49.9/F_4R440 49.9/F_4

H_PECI<11>

H_PROCHOT#<27,30>

PM_THRMTRIP#<11>

PM_SYNC<8>

H_PWRGOOD<11,27>

PM_DRAM_PWRGD<8>

PLTRST#<10,18,19,23,27>

R193 1.5K/F_4R193 1.5K/F_4

2

AUBURNDALE/CLARKSFIELD PROCESSOR (CLK,MISC,JTAG)

DPLL_REF_SSCLK and DPLL_REF_SSCLK# can be connected to GND on Arrandale

directly if motherboard only supports discrete graphics. If motherboard supports

integrated graphics but without eDP, these pins can also be connected to GND directly.

U22B

R196

R196

750/F_4

750/F_4

U22B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

Clarksfield/Auburndale

Clarksfield/Auburndale

MISC THERMAL

MISC THERMAL

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TCK

TMS

TDI

TDO

A16

B16

AR30

AT30

E16

D16

DPLL_REF_SSCLK_R

A18

DPLL_REF_SSCLK#_R

A17

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

AN15

AP15

AT28

XDP_PREQ#

AP27

XDP_TCLK

AN28

AP28

XDP_TRST#

AT27

XDP_TDI_R

AT29

XDP_TDO_R

AR27

XDP_TDI_M

AR29

XDP_TDO_M

AP29

H_DBR#_R

AN25

XDP_OBS0

AJ22

XDP_OBS1

AK22

XDP_OBS2

AK24

XDP_OBS3

AJ24

XDP_OBS4

AJ25

XDP_OBS5

AH22

XDP_OBS6

AK23

XDP_OBS7

AH23

T62T62

T67T67

H_COMP3

H_COMP2

H_COMP1

H_COMP0

T10T10

H_CATERR#

H_PROCHOT#

H_CPURST# XDP_TMS

H_VTTPWRGD

T14T14

CPU_PLTRST#

T20T20

CLK_CPU_BCLK <11>

CLK_CPU_BCLK# <11>

T21T21

CLK_PCIE_3GPLL <10>

CLK_PCIE_3GPLL# <10>

DDR3_DRAMRST# <14,15>

R254 100/F_4R254 100/F_4

R253 24.9/F_4R253 24.9/F_4

R252 130/F_4R252 130/F_4

R187 10K _4R187 10K _4

R183 10K _4R183 10K _4

T68T68

T69T69

T8T8

T9T9

T71T71

T70T70

T66T66

T65T65

T64T64

R149 *Short_4R149 *Short_4

T19T19

T18T18

T17T17

T13T13

T11T11

T15T15

T16T16

T12T12

R465 *0_4R465 *0_4

R471 *0_4R471 *0_4

R472 0_4R472 0_4

R463 0_4R463 0_4

+1.05V

1

Layout Note: Place

these resistors

near Processor

PM_EXTTS#0 <14>

PM_EXTTS#1 <15>

XDP_DBRST# <8>

DPLL_REF_SSCLK <10>

DPLL_REF_SSCLK# <10>

VTT PWR_GoodThermaltrip protect

+1.05V

3

Q16

Q16

PM_THRMTRIP#

2

1 3

FDV301N

FDV301N

1

R209

R209

1K_4

1K_4

2

Q15

Q15

MMBT3904

MMBT3904

SYS_SHDN# <29,34>

4

MPWROK<27>

DELAY_VR_PWRGOOD<8,30>

A A

PM_THRMTRIP#<11>

5

+3V

C309

C309

0.1u/10V_4

0.1u/10V_4

R176

3 5

4

U5

TC7SH0 8FUU5TC7SH0 8FU

R176

2K/F_4

2K/F_4

3

H_VTTPW RGD

R179

R179

1K_4

1K_4

2

1

Processor pull-up

+1.5VSUS

R205

R205

1.1K/F_4

1.1K/F_4

R199

R199

3K/F_4

3K/F_4

XDP_TDO

H_CATERR#

H_PROCHOT#

H_CPURST#

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

XDP_TRST#

PM_DRAM_PWRGD

R420 51/F_4R420 51/F_4

R192 49.9/F_4R192 49.9/F_4

R137 68_4R137 68_4

R438 *68_4R438 *68_4

R135 *51_4R135 *51_4

R435 *51_4R435 *51_4

R434 *51_4R434 *51_4

R133 *51_4R133 *51_4

R439 51/F_4R439 51/F_4

Use a voltage divider with VDDQ

(1.5V) rail (ON in S3) and

resistor combination of 4.75K (to

VDDQ)/12K(to GND) to generate the

required voltage.

Note: CRB uses a 3.3V (always ON)

rail with 2K and 1K combination.

+1.05V

2

JTAG MAPPING

XDP_TDI_R XDP_TDI

XDP_TDO_M

XDP_TDI_M

XDP_TDO_R

Scan Chain

(Default)

CPU Only

GMCH Only

R433 0_4R433 0_4

R429 *0_4R429 *0_4

R431

R431

0_4

0_4

R432 *0_4R432 *0_4

R430 0_4R430 0_4

STUFF -> R469, R491, R507

NO STUFF -> R489, R490

STUFF -> R490, R491

NO STUFF -> R469, R489, R507

STUFF -> R489, R507

NO STUFF -> R491, R490, R469

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AUBURNDA 1/4

AUBURNDA 1/4

AUBURNDA 1/4

Date: Sheet

Date: Sheet

Date: Sheet

XDP_TDO

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZQH

ZQH

ZQH

445Monday, March 14, 2011

445Monday, March 14, 2011

445Monday, March 14, 2011

1A

1A

1A

of

of

of

5

AUBURNDALE/CLARKSFIELD PROCESSOR (DDR3)

U22C

U22C

M_A_DQ[63:0]<14>

D D

C C

B B

M_A_BS#0<14>

M_A_BS#1<14>

M_A_BS#2<14>

M_A_CAS#<14>

M_A_RAS#<14>

M_A_WE#<14>

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

B10

E10

F10

AJ7

AJ6

AJ9

AL7

AL8

J10

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

J8

G7

J7

L7

M6

M8

L9

L6

K8

N8

P9

U7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

4

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLK0 <14>

M_A_CLK0# <14>

M_A_CKE0 <14>

M_A_CLK1 <14>

M_A_CLK1# <14>

M_A_CKE1 <14>

M_A_CS#0 <14>

M_A_CS#1 <14>

M_A_ODT0 <14>

M_A_ODT1 <14>

M_A_DM[7:0] <14>

M_A_DQS#[7:0] <14>

M_A_DQS[7:0] <14>

M_A_A[15:0] <14>

3

M_B_DQ[63:0]<15>

M_B_BS#0<15>

M_B_BS#1<15>

M_B_BS#2<15>

M_B_CAS#<15>

M_B_RAS#<15>

M_B_WE#<15>

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AG1

AG4

AG3

AH4

AM6

AN2

AM4

AM3

AN5

AN6

AN4

AN3

AN7

AR10

AT10

AC5

AC6

AF3

AJ3

AK1

AJ4

AK3

AK4

AK5

AK2

AP3

AT4

AT5

AT6

AP6

AP8

AT9

AT7

AP9

AB1

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

W5

R7

Y7

U22D

U22D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

2

W8

SB_CK[0]

W9

SB_CK#[0]

M3

SB_CKE[0]

V7

SB_CK[1]

V6

SB_CK#[1]

M2

SB_CKE[1]

AB8

SB_CS#[0]

AD6

SB_CS#[1]

AC7

SB_ODT[0]

AD1

SB_ODT[1]

M_B_DM0

D4

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

1

M_B_CLK0 <15>

M_B_CLK0# <15>

M_B_CKE0 <15>

M_B_CLK1 <15>

M_B_CLK1# <15>

M_B_CKE1 <15>

M_B_CS#0 <15>

M_B_CS#1 <15>

M_B_ODT0 <15>

M_B_ODT1 <15>

M_B_DM[7:0] <15>

M_B_DQS#[7:0] <15>

M_B_DQS[7:0] <15>

M_B_A[15:0] <15>

Clarksfield/Auburndale

Clarksfield/Auburndale

Channel A DQ[15,32,48,54], DM[5]

Requires minimum 12mils spacing

with all other signals, including data signals.

A A

5

4

3

Channel B DQ[16,18,36,42,56,57,60,61,62]

Requires minimum 12mils spacing

with all other signals, including data signals.

Clarksfield/Auburndale

Clarksfield/Auburndale

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

AUBURNDA 2/4

AUBURNDA 2/4

AUBURNDA 2/4

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

ZQH

ZQH

ZQH

545Monday, March 14, 2011

545Monday, March 14, 2011

545Monday, March 14, 2011

of

of

1

of

1A

1A

1A

5

U22F

CPU Core Power

ARD:48A

CFD:52A

C568 10U/6.3V_8C568 10U/6.3V_8

C626 22U/6.3V_8C626 22U/6.3V_8

C234 10U/6.3V_8C234 10U/6.3V_8

D D

C C

B B

A A

C589 22U/6.3V_8C589 22U/6.3V_8

C623 22U/6.3V_8C623 22U/6.3V_8

C643 10U/6.3V_8C643 10U/6.3V_8

C642 10U/6.3V_8C642 10U/6.3V_8

C590 22U/6.3V_8C590 22U/6.3V_8

C567 22U/6.3V_8C567 22U/6.3V_8

C640 10U/6.3V_8C640 10U/6.3V_8

C230 10U/6.3V_8C230 10U/6.3V_8

C588 22U/6.3V_8C588 22U/6.3V_8

C235 10U/6.3V_8C235 10U/6.3V_8

C569 10U/6.3V_8C569 10U/6.3V_8

C297 10U/6.3V_8C297 10U/6.3V_8

C624 10U/6.3V_8C624 10U/6.3V_8

C621 10U/6.3V_8C621 10U/6.3V_8

C638 10U/6.3V_8C638 10U/6.3V_8

C625 10U/6.3V_8C625 10U/6.3V_8

C566 10U/6.3V_8C566 10U/6.3V_8

C622 10U/6.3V_8C622 10U/6.3V_8

C266 10U/6.3V_8C266 10U/6.3V_8

C265 10U/6.3V_8C265 10U/6.3V_8

C236 10U/6.3V_8C236 10U/6.3V_8

C641 10U/6.3V_8C641 10U/6.3V_8

C287 10U/6.3V_8C287 10U/6.3V_8

C232 10U/6.3V_8C232 10U/6.3V_8

C633 10U/6.3V_8C633 10U/6.3V_8

C275 0.1u/10V_4_X7RC275 0.1u/10V_4_X7R

C271 0.1u/10V_4_X7RC271 0.1u/10V_4_X7R

C284 330u/2V_7343

C284 330u/2V_7343

C285 330u/2V_7343

C285 330u/2V_7343

+VCC_CORE

+

+

+

+

U22F

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

Clarksfield/Auburndale

Clarksfield/Auburndale

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

AUBURNDALE/CLARKSFIELD PROCESSOR (POWER)

5

4

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

4

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

H_PSI#

AN33

PSI#

H_VID0

AK35

H_VID1

AK33

H_VID2

AK34

H_VID3

AL35

H_VID4

AL33

H_VID5

AM33

H_VID6

AM35

H_DPRSLPVR

AM34

G15

H_VTTVID1=Low, 1.1V

H_VTTVID1=High, 1.05V

AN35

AJ34

AJ35

VTT_SENSE

B15

VSS_SENSE_VTT

A15

C658 10U/6.3V_8C658 10U/6.3V_8

C657 10U/6.3V_8C657 10U/6.3V_8

C634 10U/6.3V_8C634 10U/6.3V_8

C327 10U/6.3V_8C327 10U/6.3V_8

C648 10U/6.3V_8C648 10U/6.3V_8

C649 10U/6.3V_8C649 10U/6.3V_8

C644 10U/6.3V_8C644 10U/6.3V_8

C659 10U/6.3V_8C659 10U/6.3V_8

C652 10U/6.3V_8C652 10U/6.3V_8

C331 10U/6.3V_8C331 10U/6.3V_8

C316

C316

+

+

330u/2V_7343

330u/2V_7343

C313 22U/6.3V_8C313 22U/6.3V_8

C326 22U/6.3V_8C326 22U/6.3V_8

R104 100/F_4R104 100/F_4

R103 100/F_4R103 100/F_4

VTT Rail Values are

Auburndal VTT=1.05V

Clarksfield VTT=1.1V

18A

+1.05V

+1.05V

H_PSI# <30>

H_VID0 <30>

H_VID1 <30>

H_VID2 <30>

H_VID3 <30>

H_VID4 <30>

H_VID5 <30>

H_VID6 <30>

H_DPRSLPVR <30>

I_MON <30>

+VCC_CORE

VCCSENSE <30>

VSSSENSE <30>

T75T75

T74T74

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GRAPHICS POWER)

U22G

22A

+VGFX_AXG

+

+

C635

C635

*330U/2V_7343

*330U/2V_7343

+

+

C651

C651

*330U/2V_7343

*330U/2V_7343

+1.05V

C311

C311

10U/6.3V_8

10U/6.3V_8

C332

C332

C656

C656

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

1

1

1

0

0

1

0

1

0

Note:

For Validating IMVP VR R6451 should be STUFF

and R2N1 NO_STUFF

3

C281

C281

22u/6.3V_8

22u/6.3V_8

C298

C298

10u/6.3V_8

10u/6.3V_8

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_DPRSLPVR

H_PSI#

C655

C655

22u/6.3V_8

22u/6.3V_8

C312

C312

22u/6.3V_8

22u/6.3V_8

C280

C280

22u/6.3V_8

22u/6.3V_8

10u/6.3V_8

10u/6.3V_8

C299

C299

C330

C330

22u/6.3V_8

22u/6.3V_8

R388 1K_4R388 1K_4

R395 *1K/F_4R395 *1K/F_4

R387 1K_4R387 1K_4

R394 *1K/F_4R394 *1K/F_4

R389 1K_4R389 1K_4

R396 *1K/F_4R396 *1K/F_4

R400 *1K/F_4R400 *1K/F_4

R409 1K_4R409 1K_4

R401 *1K/F_4R401 *1K/F_4

R410 1K_4R410 1K_4

R404 1K_4R404 1K_4

R413 *1K/F_4R413 *1K/F_4

R402 *1K/F_4R402 *1K/F_4

R411 1K_4R411 1K_4

R403 1K_4R403 1K_4

R412 *1K/F_4R412 *1K/F_4

R419 *1K/F_4R419 *1K/F_4

R418 1K_4R418 1K_4

U22G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

Clarksfield/Auburndale

Clarksfield/Auburndale

HFM_VID : Max 1.4V

LFM_VID : Min 0.65V

2

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

+1.05V

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAPHICS VIDs

GRAPHICS VIDs

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

1.1V1.8V

1.1V1.8V

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

C660 10U/6.3V_8C660 10U/6.3V_8

L10

C654 10U/6.3V_8C654 10U/6.3V_8

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

T72T72

VCC_AXG_SENSE <33>

VSS_AXG_SENSE <33>

T73T73

GFX_VID0 <33>

GFX_VID1 <33>

GFX_VID2 <33>

GFX_VID3 <33>

GFX_VID4 <33>

GFX_VID5 <33>

GFX_VID6 <33>

GFX_ON <33>

GFX_DPRSLPVR <33>

GFX_IMON <33>

C356

C356

C355

C358

C358

1U/6.3V_4

1U/6.3V_4

C417

C417

1U/6.3V_4

1U/6.3V_4

AUBURNDA 3/4 (PWR)

AUBURNDA 3/4 (PWR)

AUBURNDA 3/4 (PWR)

C355

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C360

C360

22U/6.3V_8

22U/6.3V_8

+1.05V

C61810U/6.3V_8 C61810U/6.3V_8

C63010U/6.3V_8 C63010U/6.3V_8

0.6A

+1.8V

C25822U/6.3V_8 C25822U/6.3V_8

C2744.7U/6.3V_6 C2744.7U/6.3V_6

C2312.2U/6.3V_6 C2312.2U/6.3V_6

C2331U/6.3V_4 C2331U/6.3V_4

C2391U/6.3V_4 C2391U/6.3V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

C357

C357

22U/6.3V_8

22U/6.3V_8

ARD:3A

CFD:6A

C352

C352

1U/6.3V_4

1U/6.3V_4

ZQH

ZQH

ZQH

+

+

C363

C363

330U/2V_7343

330U/2V_7343

645Monday, March 14, 2011

645Monday, March 14, 2011

645Monday, March 14, 2011

+1.5VSUS

of

of

of

1A

1A

1A

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GND) AUBURNDALE/CLARKSFIELD PROCESSOR( RESERVED, CFG)

U22H

U22H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

VSS8

AR17

VSS9

AR15

VSS10

D D

C C

B B

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

Clarksfield/Auburndale

Clarksfield/Auburndale

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

Processor Strapping

CFG0

(PCI-Epress

Configuration Select)

CFG3

(PCI-Epress Static

Lane Reversal)

A A

5

CFG4

(Embended

Display Port Presence)

7

V

K

,

S

H

D

Q

H

F

Q

W

F

&

R

G

H

L

O

P

O

I

D

S

%

L

U

R

*

U

F

N

U22I

U22I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

Clarksfield/Auburndale

Clarksfield/Auburndale

VSS

VSS

Single PEG

Normal Operation Lane Numbers Reversed

Disabled; No Physical Display Port

attached to Embedded Diplay Port

4

VREF_DQ_DIMM0<14>

VREF_DQ_DIMM1<15>

AT35

VSS_NCTF1

AT1

VSS_NCTF2

AR34

VSS_NCTF3

B34

VSS_NCTF4

B2

VSS_NCTF5

B1

VSS_NCTF6

A35

VSS_NCTF7

NCTF

NCTF

10

TP20TP20

TP22TP22

TP34TP34

Bifurcation enabled

DEFAULT

1

1

Enabled; An external Display port

device is connected to the Embedded

Display port

3

1

TP25TP25

TP26TP26

CFG0

CFG3

CFG4

CFG7

U22E

U22E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

SA_DIMM_VREF

H17

SB_DIMM_VREF

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

Clarksfield/Auburndale

Clarksfield/Auburndale

CFG0

R128 *3.01K_NCR128 *3.01K_NC

CFG3

R125 3.01K/F_4R125 3.01K/F_4

CFG4

R127 *3.01KR127 *3.01K

CFG7

R126 *3.01K/F_4R126 *3.01K/F_4

AJ13

RSVD32

AJ12

RSVD33

AH25

RSVD34

AK26

RSVD35

AL26

RSVD36

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD_TP_59

RSVD_TP_60

RESERVED

RESERVED

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

2

AR2

AJ26

RSVD38

AJ27

RSVD39

AP1

AT2

AT3

AR1

AL28

RSVD45

AL29

RSVD46

AP30

RSVD47

AP32

RSVD48

AL27

RSVD49

AT31

RSVD50

AT32

RSVD51

AP33

RSVD52

AR33

RSVD53

AT33

AT34

AP35

AR35

AR32

RSVD58

E15

F15

A2

KEY

D15

RSVD62

C15

RSVD63

AJ15

RSVD64

RSVD65

VSS

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet

Date: Sheet

Date: Sheet

TP8TP8

AH15

TP9TP9

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

TP19TP19

AP34 can be NC on CRB; EDS/DG suggestion to GND

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

AUBURNDA 4/4

AUBURNDA 4/4

AUBURNDA 4/4

1

ZQH

ZQH

ZQH

745Monday, March 14, 2011

745Monday, March 14, 2011

745Monday, March 14, 2011

1A

1A

1A

of

of

of

5

IBEX PEAK-M (DMI,FDI,GPIO)

4

3

2

1

AC-coupling CAP place close to PCH

U21C

U21C

ACIN_R

PM_BATLOW#

PM_RI#

BC24

DMI0RXN

BJ22

DMI1RXN

AW20

DMI2RXN

BJ20

DMI3RXN

BD24

DMI0RXP

BG22

DMI1RXP

BA20

DMI2RXP

BG20

DMI3RXP

BE22

DMI0TXN

BF21

DMI1TXN

BD20

DMI2TXN

BE18

DMI3TXN

BD22

DMI0TXP

BH21

DMI1TXP

BC20

DMI2TXP

BD18

DMI3TXP

BH25

DMI_ZCOMP

BF25

DMI_IRCOMP

T6

SYS_RESET#

M6

SYS_PWROK

B17

PWROK

K5

MEPWROK

A10

LAN_RST#

D9

DRAMPWROK

C16

RSMRST#

M1

SUS_PWR_DN_ACK / GPIO30

P5

PWRBTN#

P7

ACPRESENT / GPIO31

A6

BATLOW# / GPIO72

F14

RI#

IbexPeak-M_R1P0

IbexPeak-M_R1P0

DMI

FDI

DMI

FDI

CLKRUN# / GPIO32

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

System Power Management

System Power Management

SLP_LAN# / GPIO29

DMI_RXN0<4>

SYS_PWROK

ICH_RSMRST#<27>

DNBSWON#<27>

PCH_ACIN<27>

DMI_RXN1<4>

DMI_RXN2<4>

DMI_RXN3<4>

DMI_RXP0<4>

DMI_RXP1<4>

DMI_RXP2<4>

DMI_RXP3<4>

DMI_TXN0<4>

DMI_TXN1<4>

DMI_TXN2<4>

DMI_TXN3<4>

DMI_TXP0<4>

DMI_TXP1<4>

DMI_TXP2<4>

DMI_TXP3<4>

+1.05V

R441 49.9/F_4R441 49.9/F_4

XDP_DBRST#

RSV_ICH_LAN_RST#

SUS_PWR_ACK_R

R246 *0_4R246 *0_4

D D

C C

XDP_DBRST#<4>

PM_DRAM_PWRGD<4>

B B

FDI_RXN0

FDI_RXN1

FDI_RXN2

FDI_RXN3

FDI_RXN4

FDI_RXN5

FDI_RXN6

FDI_RXN7

FDI_RXP0

FDI_RXP1

FDI_RXP2

FDI_RXP3

FDI_RXP4

FDI_RXP5

FDI_RXP6

FDI_RXP7

FDI_INT

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

WAKE#

SLP_S4#

SLP_S3#

SLP_M#

TP23

PMSYNCH

BA18

BH17

BD16

BJ16

BA16

BE14

BA14

BC12

BB18

BF17

BC16

BG16

AW16

BD14

BB14

BD12

BJ14

BF13

BH13

BJ12

BG14

J12

Y1

P8

F3

E4

H7

P12

K8

N2

BJ10

F6

R234 *Short_4R234 *Short_4

SLP_M#

PM_SLP_LAN#

FDI_TXN0 <4>

FDI_TXN1 <4>

FDI_TXN2 <4>

FDI_TXN3 <4>

FDI_TXN4 <4>

FDI_TXN5 <4>

FDI_TXN6 <4>

FDI_TXN7 <4>

FDI_TXP0 <4>

FDI_TXP1 <4>

FDI_TXP2 <4>

FDI_TXP3 <4>

FDI_TXP4 <4>

FDI_TXP5 <4>

FDI_TXP6 <4>

FDI_TXP7 <4>

R225 *0_4R225 *0_4

TP32TP32

TP18TP18

FDI_INT <4>

FDI_FSYNC0 <4>

FDI_FSYNC1 <4>

FDI_LSYNC0 <4>

FDI_LSYNC1 <4>

PCIE_WAKE# <18,19>

CLKRUN# <27>

ICH_SUSCLK <27>

SUSC# <27>

SUSB# <27>

PM_SYNC <4>

INT_LVDS_BLON<16>

INT_LVDS_DIGON<16>

INT_LVDS_BRIGHT<16>

INT_LVDS_EDIDCLK<16>

INT_LVDS_EDIDDATA<16>

INT_TXLCLKOUT-<16>

INT_TXLCLKOUT+<16>

INT_TXLOUT0-<16>

INT_TXLOUT1-<16>

INT_TXLOUT2-<16>

INT_CRT_BLU<16>

INT_CRT_GRN<16>

INT_CRT_RED<16>

INT_CRT_DDCCLK<16>

INT_CRT_DDCDAT<16>

INT_HSYNC<16>

INT_VSYNC<16>

+3V

INT_TXLOUT0+<16>

INT_TXLOUT1+<16>

INT_TXLOUT2+<16>

R119 10K_4R119 10K_4

R120 10K_4R120 10K_4

R144 2.37K/F_4R144 2.37K/F_4

R111 0_4R111 0_4

R112 0_4R112 0_4

INT_TXLCLKOUTINT_TXLCLKOUT+

INT_TXLOUT0INT_TXLOUT1INT_TXLOUT2-

INT_TXLOUT0+

INT_TXLOUT1+

INT_TXLOUT2+

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

DAC_IREF

R134

R134

1K/F_4

1K/F_4

IBEX PEAK-M (LVDS,DDI)

U21D

U21D

AB48

AB46

AP39

AP41

AT43

AT42

AV53

AV51

BB47

BA52

AY48

AV47

BB48

BA50

AY49

AV48

AP48

AP47

AY53

AT49

AU52

AT53

AY51

AT48

AU50

AT51

AA52

AB53

AD53

AD48

AB51

T48

T47

Y48

Y45

V48

V51

V53

Y53

Y51

L_BKLTEN

L_VDD_EN

L_BKLTCTL

L_DDC_CLK

L_DDC_DATA

L_CTRL_CLK

L_CTRL_DATA

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#0

LVDSA_DATA#1

LVDSA_DATA#2

LVDSA_DATA#3

LVDSA_DATA0

LVDSA_DATA1

LVDSA_DATA2

LVDSA_DATA3

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#0

LVDSB_DATA#1

LVDSB_DATA#2

LVDSB_DATA#3

LVDSB_DATA0

LVDSB_DATA1

LVDSB_DATA2

LVDSB_DATA3

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_VSYNC

DAC_IREF

CRT_IRTN

IbexPeak-M_R1P0

IbexPeak-M_R1P0

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_STALLN

SDVO_STALLP

SDVO_CTRLCLK

SDVO_CTRLDATA

LVDS

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

Digital Display Interface

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

CRT

CRT

SDVO_INTN

SDVO_INTP

DDPB_AUXN

DDPB_AUXP

DDPB_HPD

DDPB_0N

DDPB_0P

DDPB_1N

DDPB_1P

DDPB_2N

DDPB_2P

DDPB_3N

DDPB_3P

DDPC_AUXN

DDPC_AUXP

DDPC_HPD

DDPC_0N

DDPC_0P

DDPC_1N

DDPC_1P

DDPC_2N

DDPC_2P

DDPC_3N

DDPC_3P

DDPD_AUXN

DDPD_AUXP

DDPD_HPD

DDPD_0N

DDPD_0P

DDPD_1N

DDPD_1P

DDPD_2N

DDPD_2P

DDPD_3N

DDPD_3P

BJ46

BG46

BJ48

BG48

BF45

BH45

T51

T53

BG44

BJ44

AU38

BD42

BC42

BJ42

BG42

BB40

BA40

AW38

BA38

Y49

AB49

BE44

BD44

AV40

BE40

BD40

BF41

BH41

BD38

BC38

BB36

BA36

U50

U52

BC46

BD46

AT38

BJ40

BG40

BJ38

BG38

BF37

BH37

BE36

BD36

INT_HDMITX2N_R

INT_HDMITX2P_R

INT_HDMITX1N_R

INT_HDMITX1P_R

INT_HDMITX0N_R

INT_HDMITX0P_R

INT_HDMICLK-_R

INT_HDMICLK+_R

SDVO_CTRLCLK <17>

SDVO_CTRLDAT <17>

C249 0.1u/10V_4_X7RC249 0.1u/10V_4_X7R

C247 0.1u/10V_4_X7RC247 0.1u/10V_4_X7R

C242 0.1u/10V_4_X7RC242 0.1u/10V_4_X7R

C245 0.1u/10V_4_X7RC245 0.1u/10V_4_X7R

C253 0.1u/10V_4_X7RC253 0.1u/10V_4_X7R

C250 0.1u/10V_4_X7RC250 0.1u/10V_4_X7R

C237 0.1u/10V_4_X7RC237 0.1u/10V_4_X7R

C241 0.1u/10V_4_X7RC241 0.1u/10V_4_X7R

R place close to PCH

R425 150_4R425 150_4

R426 150_4R426 150_4

R427 150_4R427 150_4

INT_HDMI_HPD < 17>

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

INT_HDMITX2N <17>

INT_HDMITX2P <17>

INT_HDMITX1N <17>

INT_HDMITX1P <17>

INT_HDMITX0N <17>

INT_HDMITX0P <17>

INT_HDMICLK- <17>

INT_HDMICLK+ <17>

PCH Pull-high/low System PWR_OK

+3V

CLKRUN#

A A

XDP_DBRST#

ICH_RSMRST#

RSV_ICH_LAN_RST#

SYS_PWROK ACIN_R

R523 8.2K_4R523 8.2K_4

R226 1K_4R226 1K_4

R482 10K_4R482 10K_4

R499 10K_4R499 10K_4

R477 10K_4R477 10K_4

5

PM_RI#

PM_BATLOW#

PCIE_WAKE#

PM_SLP_LAN#

SUS_PWR_ACK_R

R184 10K_4R184 10K_4

R514 10K_4R514 10K_4

R230 10K_4R230 10K_4

R248 *10K_4R248 *10K_4

R530 10K_4R530 10K_4

R227 10K_4R227 10K_4

+3V_S5

4

3

C636 *.1u_4C636 *.1u_4

SYS_PWROK

U24

U24

TC7SH08FU

TC7SH08FU

+3V_S5

'(/$<B95B3:5*22'QHHG38.WR9

38DWSRZHUVLGH

53

1

4

2

R538 100K_4R538 100K_4

DELAY_VR_PWRGOOD <4,30>

PWROK_EC <27>

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

ZQH

ZQH

ZQH

of

845Monday, March 14, 2011

of

845Monday, March 14, 2011

of

1

845Monday, March 14, 2011

1A

1A

1A

5

RTC Circuitry

+VCCRTC

CR1

+3VPCU

VCCRTC_1

R473

R473

1K_4

1K_4

N18608864

D D

12

BT1

BT1

RTC_CONN

RTC_CONN

CR1

BAT54C

BAT54C

R483 20K/F_4R483 20K/F_4

R474 20K/F_4R474 20K/F_4

C663

C663

1u/10V_4

1u/10V_4

C662

C662

1u/10V_4

1u/10V_4

C650

C650

1u/10V_4

1u/10V_4

RTC_RST#

12

J2

J2

*SHORT_ PAD1

*SHORT_ PAD1

SRTC_RST#

12

J1

J1

*SHORT_ PAD1

*SHORT_ PAD1

HDA Bus

C C

PCH_AZ_CODEC_SYNC<21>

PCH_AZ_CODEC_RST#<21>

PCH_AZ_CODEC_SDOUT<21>

PCH_AZ_CODEC_BITCLK<21>

R453 33_4R453 33_4

R449 33_4R449 33_4

R456 33_4R456 33_4

R450 33_4R450 33_4

C628

C628

*27p_4

*27p_4

ACZ_SYNCACZ_SYNC

ACZ_RST#

ACZ_SDOUTACZ_SDOUT

ACZ_BIT_CLKACZ_BIT_CLK

4

HDA_SYNC (PCH strap pin)

Internal weak pull-down

VCCVRM=>+1.8V (default)

external pull-up

VCCVRM=>+1.5V

+VCCRTC

PCH_AZ_CODEC_SDIN0<21>

+3V_S5

HDMI_HPD_PCH#<17>

C335

C335

15p/50V_4

15p/50V_4

23

Y1

32.768KHZY132.768KHZ

4 1

C328

C328

15p/50V_4

15p/50V_4

R479 1M_4R479 1M_4

ACZ_BIT_CLK

ACZ_SYNC

SPKR<21>

ACZ_RST#

R460 *10K_4R460 *10K_4

R525 *10K_4R525 *10K_4

+3VPCU

3

R195

R195

10M_4

10M_4

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

SPKR

ACZ_SDOUT

PCH_GPIO33

RTC_X1

RTC_X2

PCH_GPIO13

SPI_CLK_R

SPI_CS0#_R

SPI_CS1#

SPI_SI_R

SPI_SO_R

U21A

U21A

B13

RTCX1

D13

RTCX2

C14

RTCRST#

D17

SRTCRST#

A16

INTRUDER#

A14

INTVRMEN

A30

HDA_BCLK

D29

HDA_SYNC

P1

SPKR

C30

HDA_RST#

G30

HDA_SDIN0

F30

HDA_SDIN1

E32

HDA_SDIN2

F32

HDA_SDIN3

B29

HDA_SDO

H32

HDA_DOCK_EN# / GPIO33

J30

HDA_DOCK_RST# / GPIO13

M3

JTAG_TCK

K3

JTAG_TMS

K1

JTAG_TDI

J2

JTAG_TDO

J4

TRST#

BA2

SPI_CLK

AV3

SPI_CS0#

AY3

SPI_CS1#

AY1

SPI_MOSI

AV1

SPI_MISO

IbexPeak-M_R1P0

IbexPeak-M_R1P0

RTCIHDA

RTCIHDA

SPI JTAG

SPI JTAG

FWH4 / LFRAME#

LDRQ1# / GPIO23

LPC

LPC

SATA

SATA

SATA0GP / GPIO21

SATA1GP / GPIO19

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

LDRQ0#

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

2

D33

B33

C32

A32

C34

A34

F34

AB9

SATA_RXN0_C

AK7

SATA_RXP0_C

AK6

AK11

AK9

SATA_RXN1_C

AH6

SATA_RXP1_C

AH5

AH9

AH8

AF11

AF9

AF7

Note:

AF6

SATA port2/3 may not be available on all PCH sku

AH3

(HM55 support 3 port only)

AH1

AF3

AF1

AD9

AD8

AD6

AD5

AD3

AD1

AB3

AB1

AF16

R182 37.4/F_4R182 37.4/F_4

AF15

T3

Y9

V1

R222 10K_4R222 10K_4

TP13TP13

R240 43K/F_4R240 43K/F_4

R521 43K/F_4R521 43K/F_4

+1.05V

1

LPC_LAD0 <19,27>

LPC_LAD1 <19,27>

LPC_LAD2 <19,27>

LPC_LAD3 <19,27>

LPC_LFRAME# <19,27>

+3V

IRQ_SERIRQ <27>

SATA_RXN0_C <20>

SATA_RXP0_C <20>

SATA_TXN0 <20>

SATA_TXP0 <20>

SATA_RXN1_C <20>

SATA_RXP1_C <20>

SATA_TXN1 <20>

SATA_TXP1 <20>

+3V

+3V

3&+6WUDS3LQ&RQILJXUDWLRQ7DEOH

INTVRMEN

SPI_MOSI

PCH SPI

B B

SPI_CS0#_R

SPI_CLK_R

SPI_SI_R

SPI_SO_R

R541 3.3K/F_4R541 3.3K/F_4

+3V

U25

U25

1

CE#

6

SCK

5

SI

2

SO

3

WP#

W25Q32BVSSIG

W25Q32BVSSIG

HOLD#

VDD

VSS

8

R539 3.3K/F_4R539 3.3K/F_4

7

4

+3V

C671

C671

.1u/10V_4

.1u/10V_4

SPKR

HDA_DOCK_EN

#/GPIO33

GNT0#,

GNT1#

GNT2#/

GPIO53

GNT3#/

GPIO55

NV_ALE

NV_CLE

Integrated 1.05V VRM Enable /

Disable

TPM Functionality

Disable

Reboot option at power-up 0 = Default Mode (Internal weak Pull-down)

Flash Descriptor

Security Override

Boot BIOS Strap

ESI Strap

(Server Only)

Top-Block

Swap Override

IntelR Anti-Theft Technology

HDD Data Protection

(Intel AT-d) Enable

DMI Termination

Voltage

1 = Integrated VRM is enabled

0 = Integrated VRM is disabled

1 = Enabled

0 = Disable

1 = No Reboot Mode with TCO Disabled

0 = Flash Descriptor Security will be overridden

1 = Security measure defined in the Flash

Descriptor will be enabled.

(0,0) = LPC (0,1) = Reserved NAND

(1,0) = PCI (1,1) = SPI

ESI compatible mode is for server

platforms only

0 = Top Block Swap Mode

1 = Default Mode (Internal pull-up)

1 = Enabled

0 = Disabled (Default)

DMI termination voltage. Weak

internal pull-up. Do not pull low.

PCI_GNT0#<10>

PCI_GNT1#<10>

+VCCRTC

+3V

+3V

PCH_GPIO33

PWM_SELECT#<10>

PCI_GNT3#<10>

NV_ALE<10>

NV_CLE<10>

R489 330K_6R489 330K_6

R540 *1K_4R540 *1K_4

R532 *1K/F_4R532 *1K/F_4

R164 *1K/F_4R164 *1K/F_4

R145 *10K_4R145 *10K_4

R129 1K_4R129 1K_4

R122 1K_4R122 1K_4

R123 *1K_4R123 *1K_4

R131 *1K_4R131 *1K_4

R158 *1K/F_4R158 *1K/F_4

R421 *10K/F_4R421 *10K/F_4

R202 *1K/F_4R202 *1K/F_4

R206 *1K/F_4R206 *1K/F_4

PCH_INVRMEN

SPI_SI_R

SPKR

+3V

+3V

+1.8V

+1.8V

GPIO8

A A

GPIO15

GPIO27

5

4

Reserved This signal has a weak internal pull up.

Reserved

On-Die PLL Voltage

Regulator

<internal weak pull-up>

NOTE: This signal should not be pulled low

0 = Intel ME Crypto Transport Layer Security

(TLS) cipher suite with no confidentiality

1 = Intel ME Crypto Transport Layer Security

(TLS) cipher suite with confidentiality

0 = Disables the VccVRM.

1 = Enables the internal VccVRM to have

a clean supply for analog rails.

3

RSV_GPIO8<11>

CR_WAKE#<11>

PCH_GPIO27<11>

R204 10K_4R204 10K_4

R203 *1K_4R203 *1K_4

R244 1K_4R244 1K_4

R221 *10K_4R221 *10K_4

+3V_S5

+3V_S5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZQH

ZQH

ZQH

945Monday, March 14, 2011

945Monday, March 14, 2011

1

945Monday, March 14, 2011

1A

1A

1A

5

U21E

U21E

H40

AD0

N34

AD1

C44

AD2

A38

AD3

C36

AD4

J34

AD5

A40

AD6

D45

D D

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

TP15TP15

R423 22_4R423 22_4

TP21TP21

R105 22_4R105 22_4

R117 22_4R117 22_4

PCI_REQ0#

PCI_REQ1#

dGPU_SELECT#

PCI_REQ3#

PCI_GNT0#

PCI_GNT1#

PWM_SELECT#

PCI_GNT3#

PCI_PIRQE#

PCI_PIRQF#

PCI_PIRQG#

PCI_PIRQH#

PCI_RST#

PCI_SERR#

PCI_PER R#

PCI_IRDY#

PCI_DEVSEL#

PCI_FRAME#

PCI_PLO CK#

PCI_STOP#

PCI_TRDY#

ICH_PME#

PCI_PLTRST#

CLK_LPC_DEBUG_C

CLK_PCI_PCCARD

CLK_PCI_775_CCLK_PCI_775_C

C C

CLK_LPC_DEBUG<19>

B B

CLK_PCI_775<27>

TP1TP1

TP3TP3

PCI_GNT0#<9>

PCI_GNT1#<9>

PWM_SELECT#<9>

PCI_GNT3#<9>

PCI_RST#<19>

CLK_PCI_FB CLK_PCI_FB_C

AD7

E36

AD8

H48

AD9

E40

AD10

C40

AD11

M48

AD12

M45

AD13

F53

AD14

M40

AD15

M43

AD16

J36

AD17

K48

AD18

F40

AD19

C42

AD20

K46

AD21

M51

AD22

J52

AD23

K51

AD24

L34

AD25

F42

AD26

J40

AD27

G46

AD28

F44

AD29

M47

AD30

H36

AD31

J50

C/BE0#

G42

C/BE1#

H47

C/BE2#

G34

C/BE3#

G38

PIRQA#

H51

PIRQB#

B37

PIRQC#

A44

PIRQD#

F51

REQ0#

A46

REQ1# / GPIO50

B45

REQ2# / GPIO52

M53

REQ3# / GPIO54

F48

GNT0#

K45

GNT1# / GPIO51

F36

GNT2# / GPIO53

H53

GNT3# / GPIO55

B41

PIRQE# / GPIO2

K53

PIRQF# / GPIO3

A36

PIRQG# / GPIO4

A48

PIRQH# / GPIO5

K6

PCIRST #

E44

SERR#

E50

PERR#

A42

IRDY#

H44

PAR

F46

DEVSEL#

C46

FRAME#

D49

PLOCK#

D41

STOP#

C48

TRDY#

M7

PME#

D5

PLTRST#

N52

CLKOUT_PCI0

P53

CLKOUT_PCI1

P46

CLKOUT_PCI2

P51

CLKOUT_PCI3

P48

CLKOUT_PCI4

IbexPeak-M_R1P0

IbexPeak-M_R1P0

PCI

PCI

NV_DQ0 / NV_IO0

NV_DQ1 / NV_IO1

NV_DQ2 / NV_IO2

NV_DQ3 / NV_IO3

NV_DQ4 / NV_IO4

NV_DQ5 / NV_IO5

NV_DQ6 / NV_IO6

NV_DQ7 / NV_IO7

NV_DQ8 / NV_IO8

NV_DQ9 / NV_IO9

NV_DQ10 / NV_IO10

NV_DQ11 / NV_IO11

NVRAM

NVRAM

NV_DQ12 / NV_IO12

NV_DQ13 / NV_IO13

NV_DQ14 / NV_IO14

NV_DQ15 / NV_IO15

NV_WR#0_RE#

NV_WR#1_RE#

NV_WE#_CK0

NV_WE#_CK1

USB

USB

OC0# / GPIO59

OC1# / GPIO40

OC2# / GPIO41

OC3# / GPIO42

OC4# / GPIO43

OC5# / GPIO9

OC6# / GPIO10

OC7# / GPIO14

NV_CE#0

NV_CE#1

NV_CE#2

NV_CE#3

NV_DQS0

NV_DQS1

NV_ALE

NV_CLE

NV_RCOMP

NV_RB#

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

USBP8N

USBP8P

USBP9N

USBP9P

USBP10N